Kenwood DPFK-6010-V Service manual

MULTIPLE VIDEO CD PLAYER

i

I

È

0

73

4

¢

8

PAL

NTSC

L

R

1

1

S -VIDEO

2

2

VARIABLE

AUDIO OUTPUT

VIDEO OUTPUT

DPF-K6010V

SERVICE MANUAL

© 1998-8/B51-5471-00 (K/K) 399

KENWOOD badge

(B43-0302-04)

Knob

(K29-7352-03)

Knob

(K27-2178-04)

Phone jack

(E11-0224-05)

Phono jack

(E63-0120-05)

Knob

(K29-7354-14)

Cylindrical receptacle

(E56-0014-05)

Front glass

(B10-3403-03)

Panel (CD)

(A29-1016-02)

Knob

(K29-7351-03)

Power cord bushing

(J42-0083-05)

Panel *

(A60-)

Knob

(K29-7353-02)

Phono jack

(E63-0128-05)

In compliance with Federal Regulations, following are reproduc-

Slide switch

(S31-2132-05)

tions of labels on, or inside the product relating to laser product

safety.

• Refer to page 12 between Adjustment and Pc

board if you want to know CD mechanism

exploded View.

AC power cord *

(E30-)

* Refer to parts list on page 25.

KENWOOD-Corp. certifies this equipment conforms to DHHS

Regulations No. 21 CFR 1040. 10, Chapter 1, Subchapter J.

DANGER : Laser radiation when open and interlock defeated.

AVOID DIRECT EXPOSURE TO BEAM.

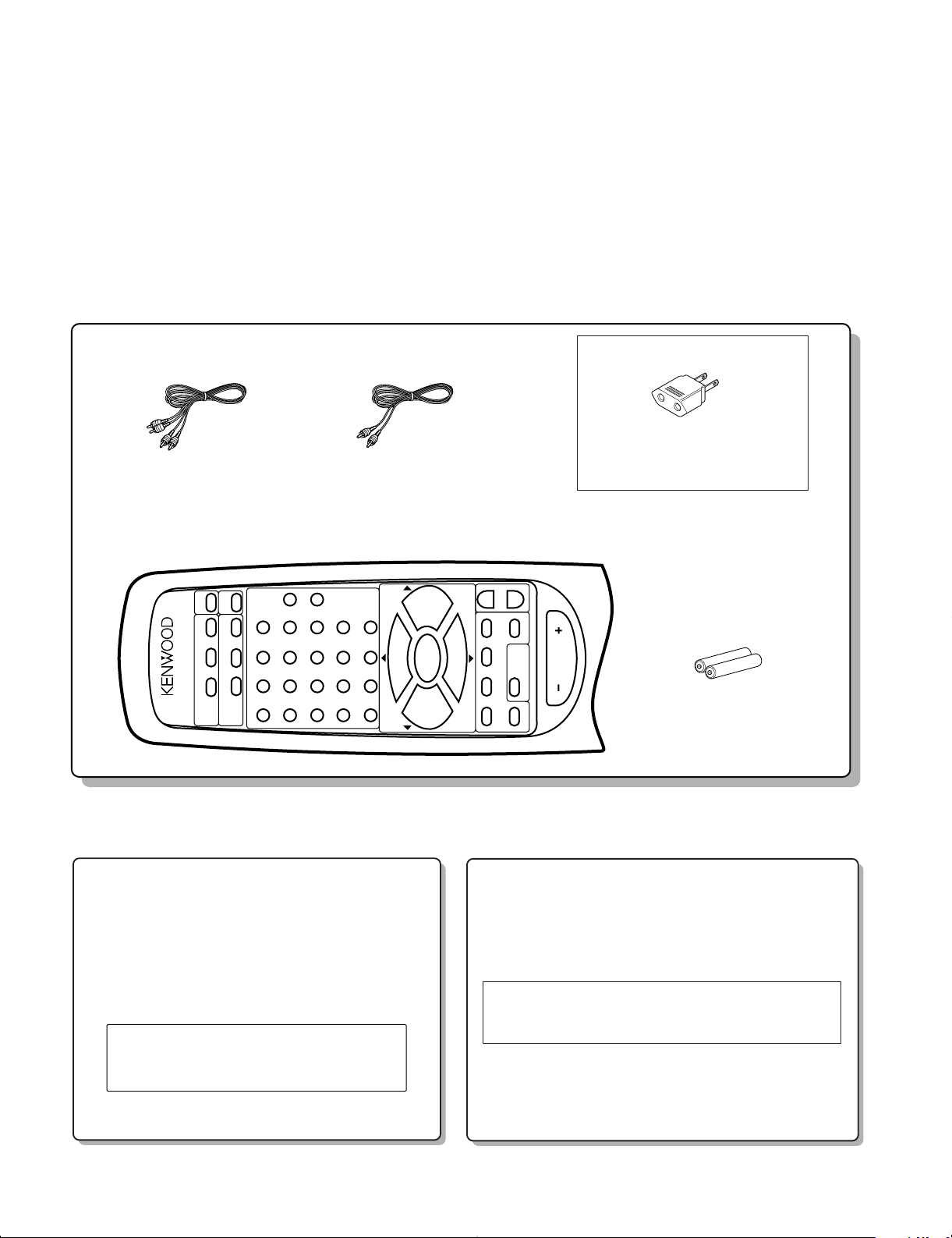

Audio

(E30-0505-05) (E30-1427-05)

(E03-0115-05)

(A70-1226-05) : RC-P0610

Battery cover (A09-1104-08)

cord .................. (1)

Remote control unit .............(1)

Batteries (R03/AAA) ........(2)

Video cord ................... (1)

AC plug adaptor .............(1)

Use to adapt the plug on the power cord

to the shape of the wall outlet.

(Accessory only for regions where

use is necessary.)

VOLUME

REMOTE CONTROL UNIT

RC-P0610

DISC

KEY

CONTROL

1

2

3 0

SLOW

8

7

RETURN

E

SURROUND

ECHO

+

-

GAME

ZOOM

1

AUDIO

MODE

2

3 4

5 6

7 8

9 0

+10 PBC

DISPLAY

RESUME

TIME P.MODE

DIGEST MEMORY

REPEAT CLEAR

A-B

REPEAT

4/PREV.

NEXT/

¢

¡

1

3/ SELECT

RANDOM

i

I

È

DPF-K6010V

Before transporting or moving this unit, carry out the following

operations.

1. Turn the unit ON but do not load a disc.

2. Wait a few seconds and verify that the display shown appears.

3. Wait until “no disc” is displayed and turn off the unit.

Note related to transportation and movement

Operation to reset

The microcomputer may malfunction (impossibility to operate,

erroneous display, etc.) when the connection cords are unplugged while the unit is ON or due to an external factor. In this

case, execute the following method to reset the microcomputer

and return it to normal condition.

¶ Please be aware that resetting the unit will erase all stored informa-

tion and return it to the factory settings.

Set the POWER switch to OFF, and after several seconds,

set the POWER switch back to ON.

CONTENTS / ACCESSORIES / CAUTIONS

Contents

CONTENTS / ACCESSORIES / CAUTIONS.............2

DISASSEMBLY FOR REPAIR...................................3

BLOCK DIAGRAM.....................................................4

CIRCUIT DESCRIPTION...........................................5

ADJUSTMENT........................................................ 10

EXPLODED VIEW ...................................................12

Accessories

PC BOARD ..............................................................13

SCHEMATIC DIAGRAM..........................................17

EXPLODED VIEW ...................................................24

PARTS LIST.............................................................25

SPECIFICATIONS .....................................Back cover

Cautions

2

n

n

O

dI SC:

DPF-K6010V

REAR

SIDE

Friction

Arm

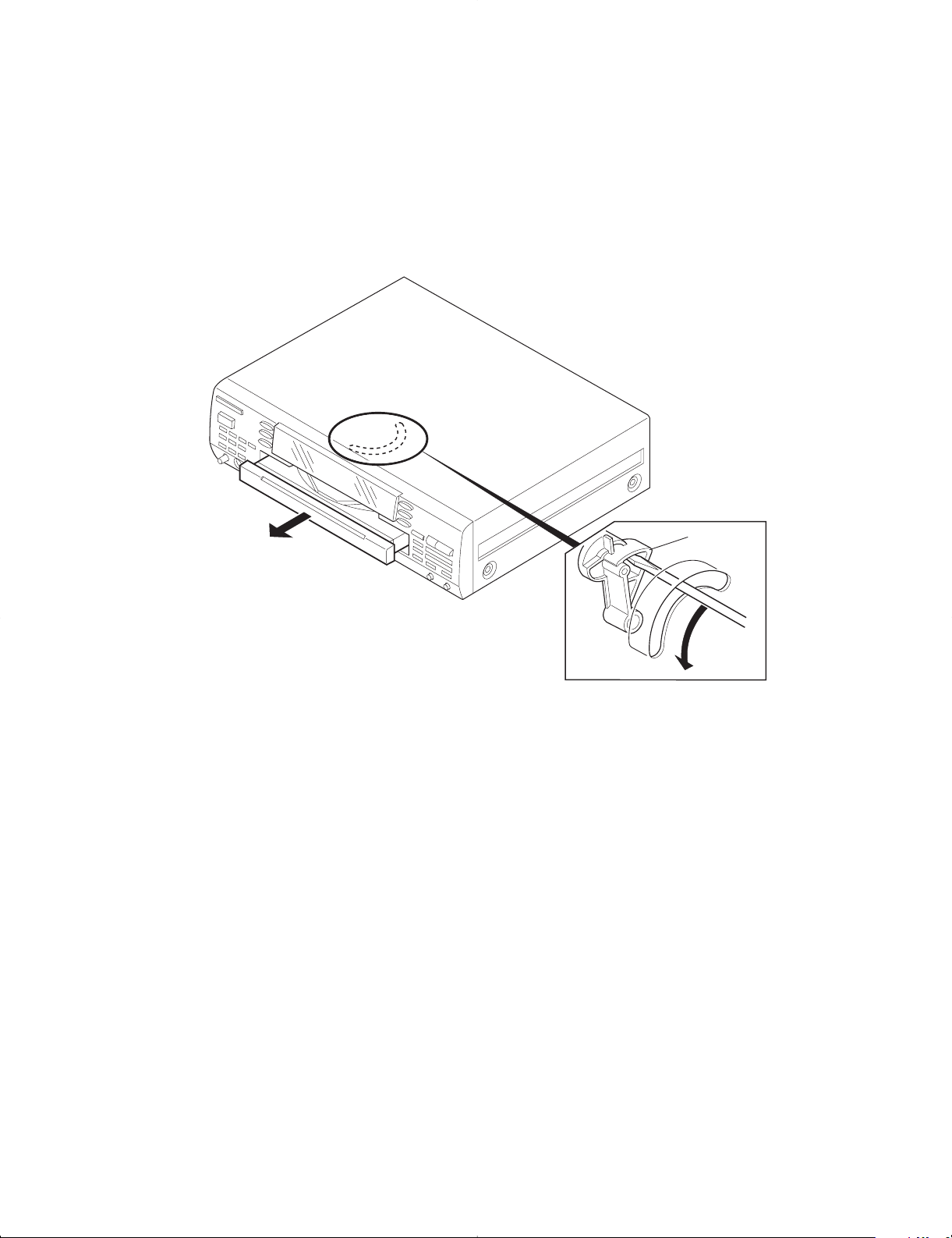

DISASSEMBLY FOR REPAIR

How to open the tray if not comes out.

(1) From the rear side of the CD mechanism, use a screw driver or the like to turn the friction arm fully counterclockwise.

(2) Pull out the tray front wards by hand when the tray comes just out.

* As for details of items in the below, refer to RXD-F3 service manual (B51-5091-00).

(1) How to detach the tray.

(2) How to attach the tray.

(3) Replacing the pickup.

3

(CDM-27)

(D40-1562-15)

(X25- )

DPF-K6010V

PD1

PD2

E

F

LD

FEO

TAO

SLO

RF

FEI

TEO

VR1

F. B

MDP

RF

C4M

SQCK

DATA

XTAI

VR2

TE-B

TRACKING

COIL

FOCUS

COIL

VR3

T. G

TEI

DATA

LRCK LRCK

BCKBCK

YUV7

YUV0

A IN

MIC1/2

A OUT

NTSC

PAL

Lch

Rch

RMR/RMF/BRKM

Y

C

+9.5V

F

AB

DC

E

LD

SW

IC1 CXA1782BQ

RF/SERVO

DRIVER

FOCUS COIL

IC3 (1/6)

TRACKING COIL

DRIVER

IC3 (2/6)

FEED MOTOR

DRIVER

IC3 (3/6)

DISC MOTOR

DRIVER

IC3 (4/6)

ROTAR Y TRAY

DRIVER

LOADING MOTOR

DRIVER

DSP

IC2 CXD2500BQ

M

M

M

M

PICKUP

Q2,3

LD

BA6198S

IC3 (5/6)

IC3 (6/6)

M3 LOADING MOTOR

M4 ROTARY MOTOR

M1 DISC MOTOR

M2 FEED MOTOR

IC11 ES3210F

FL DRIVER

u-COM

CONTROL/

MPEG/

IC12 ES3209F

VIDEO

ENCODER

AUDIO

D.A.C

IC8

Q31

VIDEO

AMP

Q32,33

AMP

VIDEO

S1

S OUT

VIDEO

OUT

J3

J2

L.P.F

IC9 (1/2)

L.P.F

IC9 (2/2)

MUTE

J1

OUT

AUDIO

MIC

AMP

IC1

J1J2MIC1

MIC2

HM514260

4M DRAM

IC13

4M ROM

IC14

LOGIC

PROGRAMMED

IC16

DIVIDER

SENSOR

REMOTE

CONTROL

A1

I/O EXPANDER

74HC166

IC17

FL DISPLAY

6-BT-267GK

FL DRIVER

uPD16311

IC2

KEY MATRIX

+3.3V

AVR

IC15

SL SW

LD SW

UP/DOWN SW

UNLD SW

PS SW

ST SW

+5.0V

AVR

Q14

+6.5V

AVR

IC5

24.0V

AVR

Q13

D38

D36

D37

12.7V

AC

F1,2

TRANSFORMER

AC IN

4

DPF-K6010V

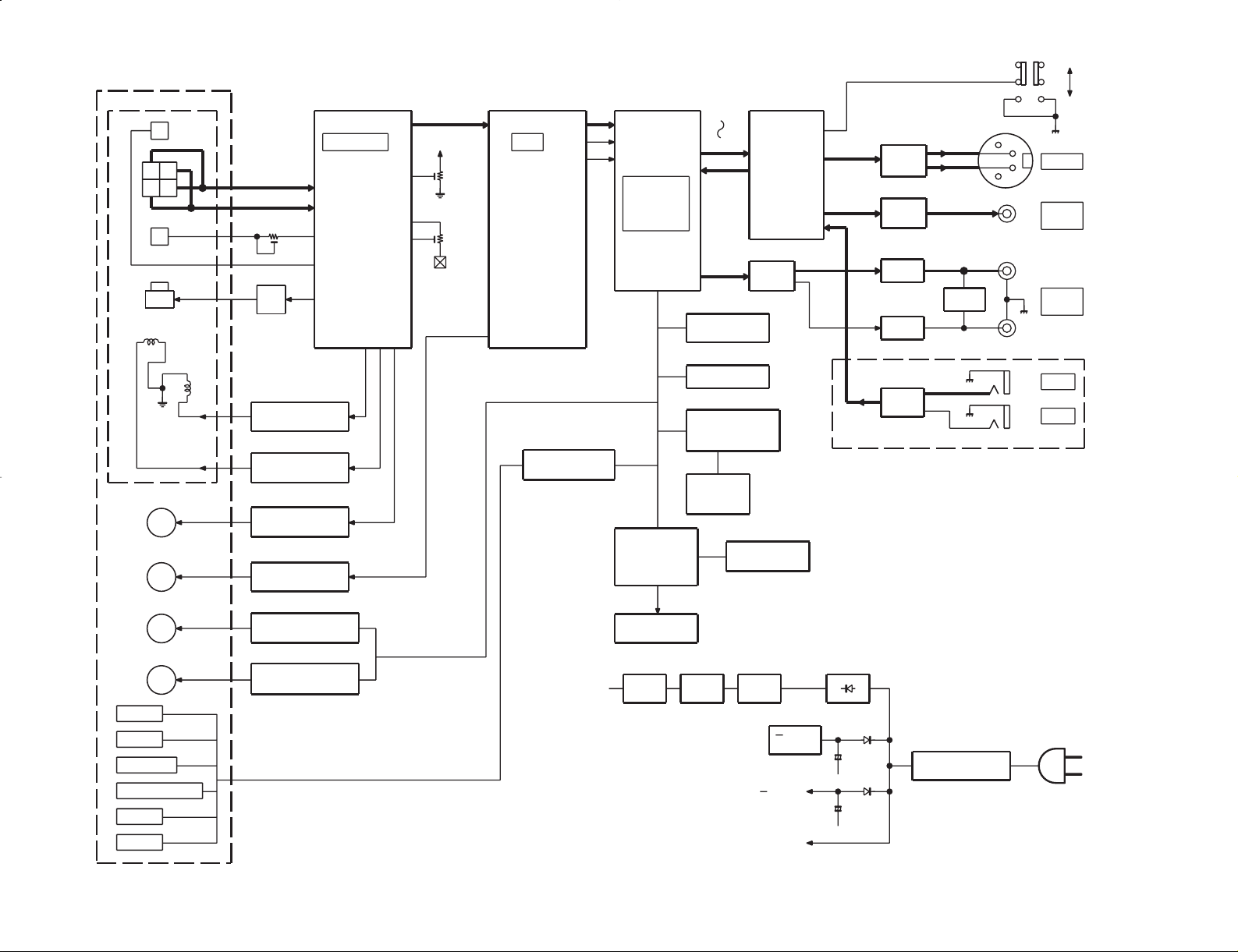

BLOCK DIAGRAM

DPF-K6010V

CIRCUIT DESCRIPTION

1. MPEG Microprocessor : IC11 (E3210F)

Pin description

No. Name I/O Description

1 VDD – Voltage supply for 3.3V.

2 RAS O DRAM row address strobe (active low).

3 DWE O DRAM write enable (active low).

4~12 MA0~MA8 O DRAM multiplexed row and column address bus.

13~28 DBUS0~DBUS15 I/O DRAM data bus.

29 RESET I System reset (active low).

30 VSS – Ground.

31 VDD – Voltage supply for 3.3V.

32~39 YUV0~YUV7 O

40 VSYNC I/O Vertical sync for screen video interface, programmable for rising or falling edge.

41 HSYNC I/O Horizontal sync for screen video interface, programmable for rising or falling edge.

42 CPUCLK I

43 PCLK2X I/O Pixel clock ; two times the actual pixel clock for screen video interface.

44 PCLK I/O Pixel clock qualifier in for screen video interface.

45 (GFS) AUX0 I/O GFS input from IC2 (CXD2500BQ).

46 (SQSO) AUX1 I/O Inputs 80 bit Sub Q and 16 bit PCM peak-level data.

47 (VFD D) AUX2 I/O Auxiliary control pins.

48 (MUTE) AUX3 I/O "H" for muting, "L" for release.

49 (IRQ) AUX4 I/O Auxiliary control pins.

50 VSS – Ground.

51 VDD – Voltage supply for 3.3V.

52 VFD L I/O Auxiliary control pins.

53 STB I/O Auxiliary control pins.

54 VFD CK I/O Auxiliary control pins.

55~62 LD0~LD7 I/O RISC interface data bus.

63 LWR O RISC interface write enable (active low).

64 LOE O RISC interface output enable (active low).

65~67 LCS (3, 1, 0) O RISC interface chip select (active low).

68~79 LA0~LA11 O RISC interface address bus.

80 VSS – Ground.

81 VPP – Digital supply voltage for 5V.

82~87 LA12~LA17 O RISC interface address bus.

88 ACLK I/O

89 AOUT/SEL PLL0 I 01 = 54MHz PLL.

90 ATCLK I/O Audio transmit bit clock.

91 ATFS/SEL PLL1

92 DOE O DRAM output enable (active low).

93 AIN I Audio interface serial data input.

94 ARCLK I Audio receive bit clock.

95 ARFS I Audio interface receive frame sync.

96 TD MCLK I TDM interface serial clock.

97 TD MDR I TDM interface serial data receive.

98 TD MFS I TDM interface frame sync.

99 CAS O DRAM column address strobe bank 0 (active low).

100 VSS – Ground.

Y is luminance, UV are chrominance data bus for screen

Video interface. YUV (0~7) for 8 bit YUV mode.

RISC and system clock input.

CPUCLK is used only if SEL PLL [1 : 0] = 00.

Master clock for external audio DAC (8.192MHz, 11.2896MHz, 12.288MHz, 16.9344

MHz, and 18.432MHz).

O Dual-purpose pin. AOUT is the audio interface serial data output

Pins SEL PLL [1 : 0] select phase-lock loop (PLL) clock frequency CPUCLK for the

ES3210 : 00 = bypass PLL.

10 = 67.5MHz PLL.

11 = 81MHz PLL.

O Dual-purpose pin. ATFS is the audio interface transmit frame sync.

Pins SEL PLL [1 : 0] select phase-lock loop (PLL) clock frequency CPUCLK for the

I

ES3210. See the SEL PLL0 pin above for the settings.

5

DPF-K6010V

CIRCUIT DESCRIPTION

2. VIDEO DAC : IC12 (ES3209F)

Pin description

No. Name I/O Description

1, 2 VSS – Ground.

3 NC – No used.

4, 5 VCC – Voltage supply, 5V.

6 DISC C I Clock for programming to access internal registers.

7 AUX0 (CLOCK) O Outputs serial data transfer clock to IC2 (D.S.P).

8 DSC D0 I/O Data for programming to access internal registers.

9 AUX1 (FOK) O Focus OK output. Used for SENS output and servo auto sequencer.

10 DISC S I Strobe for programming to access internal registers.

11 AUX2 (RMR) O Loading motor forward direction output.

12 DCLK/EXT CLK

13 RST I Video reset (active low).

14 AUX7 (RML) O Loading motor reverse direction output.

15 MUTE O No used.

16 VCC – Voltage supply, 5V.

17 MCLK – No used.

18 AUX8 (LMR) O Load motor opposite direction (taking out) output.

19 TWS/SPLL OUT – No used.

20 AUX9 (LMF) O Load motor positive direction (dragging) output.

21, 22 TSD/TBCK – No used.

23 RWS/SEL PLL1 I 0 0 Bypass PLL (Input Mode)

24 RST OUT O Reset output (active low).

25~31 VSS – Ground.

32 VCC – Voltage supply, 5V.

33 RSD/SEL PLL0

34 AUX10 (LDON) O Laser ON/OFF control.

35 AUX11 (BRKM) O Rotary motor deceleration output.

36 AUX12 (A18) O Address output to IC14 (4M DRAM).

37 RBCK/SER IN SER IN is serial input DSC mode.

38 AUX13 (166L) O IC17 (TC74HC166AF), Shift/Load.

39 AUX14 (166CK) O IC17 (TC74HC166AF), clock.

40 AUX15 (R MUTE) O Digital mute control terminal.

41 VSSA – Analog ground.

42 VREF M I

43 VREF P I

44, 45 VCCA – Analog VCC, 5V.

46, 47 AOR/AOL – No used.

O Dual-purpose pin. DCLK is the MPEG decoder clock.

I EXT CLK is the external clock. EXT CLK input during bypass PLL mode.

O Dual purpose pin. RWS is the receive audio frame sync.

O Dual purpose pin. RSD is the receive audio data input.

I SEL PLL0 is the select PLL. See the table for pin no. 23.

O Dual purpose pin. RBCK is the receive audio bit clock.

I 0 = Parallel DSC mode.

Pins SEL PLL [1 : 0] select the PLL clock frequency for DCLK output.

SEL PLL1 SEL PLL0 DCLK

0 1 27MHz (Output Mode)

1 0 32.4MHz (Output Mode)

1 1 40.5MHz (Output Mode)

1 = Serial DSC mode.

DAC and ADC minimum reference. Bypass to VCMR with 10uF in parallel with 0.1uF.

DAC and ADC minimum reference. Bypass to VCMR with 10uF in parallel with 0.1uF

.

6

CIRCUIT DESCRIPTION

No. Name I/O Description

48, 49 MIC1/MIC2 I Microphone (1, 2) input.

50, 51 VSSA – Analog ground.

52 VREF I

53 VCM I

54 RSET I Full scale DAC current adjustment.

55 COMP I Com pen station pin.

56, 57 VSSAV – Analog ground.

58 CDAC O Modulated chrominance output.

59 VCCAV – Analog VCC, 5V.

60 VCCAV – No used.

61 YDAC O Y luminance data bus for screen video port.

62, 63 VSSAV – Analog ground.

64 VDAC O Composite video output.

65 NC – No used.

66 VCC – Voltage supply, 5V.

67 AUX6 (XLAT) O Latches serial data output to IC2 (CXD2500BQ).

68 AUX5 (DATA) O Outputs serial data to IC2 (CXD2500BQ).

69 AUX4 (NT/PAL) O NTSC/PAL video control.

70 AUX3 (SENS) I SENS input from IC2 (CXD2500BQ).

71 XOUT O Crystal output.

72 VSS – Ground.

73 VCC – Voltage supply, 5V.

74 XIN I 27MHz crystal input.

75~77 VSS – Ground.

78 VCC – Voltage supply, 5V.

79 PCLK I/O 13.5MHz pixel clock.

80 PCLK2X I/O 27MHz (2 times pixel clock).

81 DSC D7 I/O Data for programming to access internal registers.

82 HSYNC O Horizontal sync (active low).

83 DSC D6 I/O Data for programming to access internal registers.

84 VSYNC O Vertical sync (active low).

85 DSC D5 I/O Data for programming to access internal registers.

86~89 YUV7~YUV4 I YUV data bus for screen video port.

90 VCC – Voltage supply, 5V.

91 VSS – Ground.

92 YUV3 I YUV data bus for screen video port.

93 DSC D4 I/O Data for programming to access internal registers.

94 YUV2 I YUV data bus for screen video port.

95 DSC D3 I/O Data for programming to access internal registers.

96 YUV1 I YUV data bus for screen video port.

97 DSC D2 I/O Data for programming to access internal registers.

98 YUV0 I YUV data bus for screen video port.

99 DSC D1 I/O Data for programming to access internal registers.

100 VSS – Ground.

Internal resistor divider generates Common Mode Reference (CMR) voltage.

Bypass to analog ground with 0.1 uF.

ADC Common Mode Reference (CMR) buffer output. CMR is approximately 2.25V.

Bypass to analog ground with 47 uF electrolytic in parallel with 0.1 uF.

DPF-K6010V

7

DPF-K6010V

YUV(0~7)

Misc.

Controller

PCLK

AUX(0~7)

DOE

DBUS(0~15)

DA(0~8)

DRAM

Decoder

Processor

64x32 ROM

Serial Audio

interface

TDM

ATCLK

LCS(0,1)

LD(0~7)

LA(0~17)

RAS

Processor

DRAM

Interface

Huffman

interface

DWE

2Kx32 ROM

LWR

LCS3,

CAS

RlSC

LOE

AUX

512x32 SRAM

MPEG

ACLK

Screen

Processor

AIN

AOUT

Serial

Audio

Display

PCLK2X

SRAM

32x32

interface

ATFS

ARFS

Interface

VSYNC

HSYNC

Video Output

ARCLK

On Screen

Registers

SEL PLL(1,0)

CPUCLK

Display

TDMDR

TOMCLK

TDM

Interface

RESET

TDMFS

DRAM DMA

Video CD Companion Chip

256Kx16

NTSC/PAL

Audio

Microphone

Panel

Control/

Remote

Interface

Keypad

Echo

TDM

CD ROM

ES3210

DRAM

Speakers

Audio

DRAM

DAC

Television

Encoder

Video :

ROM

VFD

VFD

Driver

ES3209

Speakers

Audio DAC

Remote

Receiver

NTSC/PAL Video

DSC

ES3210

CD-ROM

Television

PLL

Drive

ROM

3D/Echo/Surround

Pre-amp

Volume Control

Mic 1

Pre-amp

Panel

DRAM

Volume Control

Mic 2

CIRCUIT DESCRIPTION

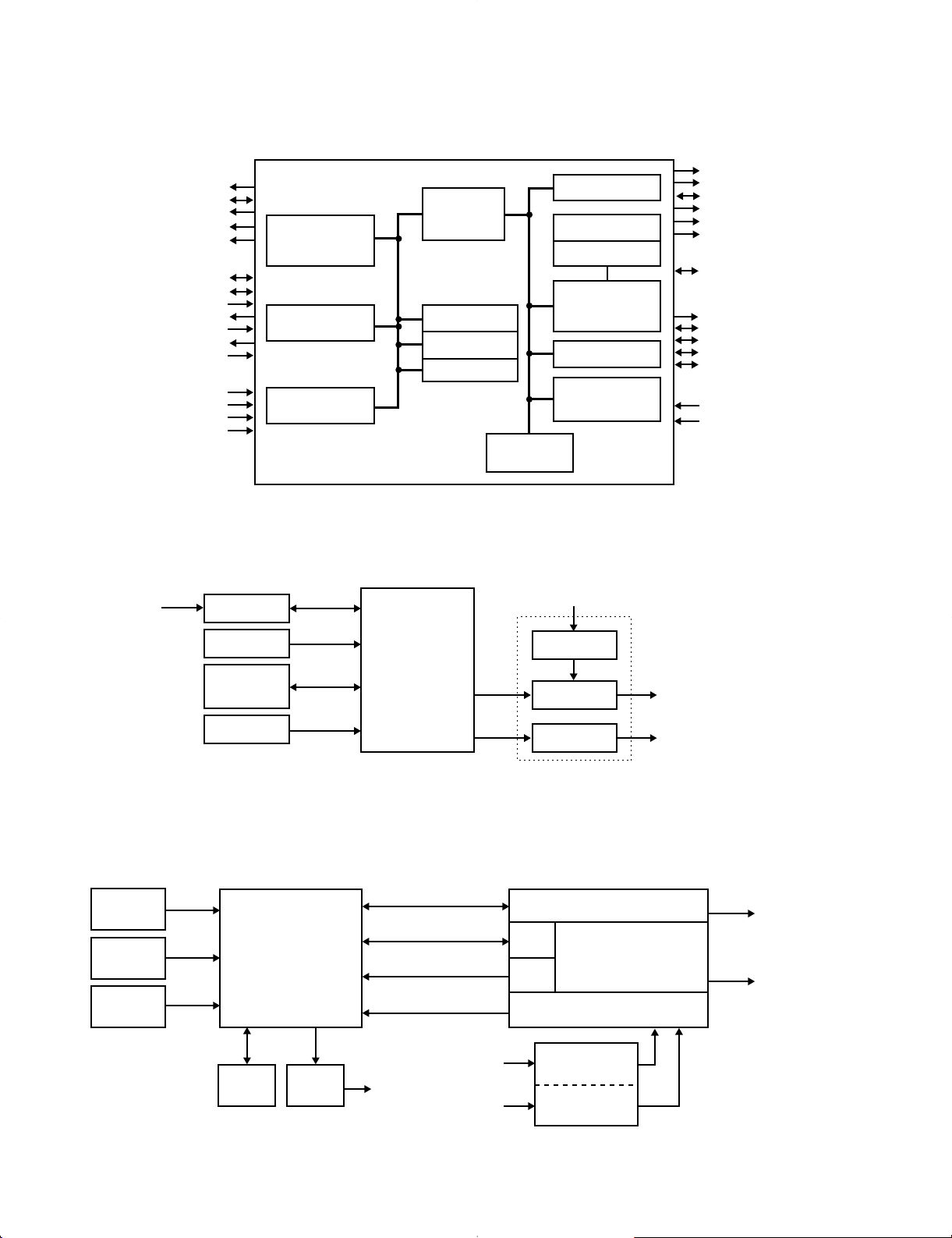

3. ES3210 Video CD PC Block Diagram

4. ES3210 Video CD Processor Chip System Block Diagram

5. ES3209 Video CD Companion Chip System Block Diagram

8

Loading...

Loading...