Page 1

INSTRUCTION MANUAL

Automatic Ranging Digital Picoamneter

Model 445

COPYRIGHT 1974, KEITHLEY INSTRUMENTS, INC.

PRINTED JULY,

1978,

DOCUMENT NO. 29105

CLEVELAND, OHIO U. S. A.

Page 2

CONTENTS

MODEL 445

SBCCiOU

SPEClFIMTI(JNS ---------------_--------------------------

1. GENERAL DESCRIPTION -----------'PEmTION ---------------_-_--_______________I____---

2.

3. CIRCUIT DESCRIPTION __-_------------------------------~p~‘-~LE PARTS ________________----_____I________-_

4.

5. C&TBmTl,,N __-______---__-__----------------------------------

SCHEMATICS __-_----_------__---______ll______l_____------

-------------------

PM,.2

ii

1

3

11

29

51

57

PRINTrn JUL 74

0174

Page 3

ILLUSTRATIONS

iLLUSTF.ATIONS

Fiu. No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

1B

19

20

21

22

23

lb

25

26

27

25

:i

31

32

33

::

Title

Front Panel.

Front Panel Conrrols.

Rear Panel.

Triaxial Receptacle.

Reading Time.

Digital Display.

Prfnter/Control ConneccLr.

Timing

Diagram.

Feedback titer.

Range Calibration.

Overall Block Diagram.

Autoranging Block Diagram.

A-Lo-D Converter Diagram.

Delay Hold Diagram.

Integrator Block Diagram.

zero cro**ing DetacLor.

Model 4401 Buffer stage.

Chassis, Top View.

PC Board Locationa.

Componanr Layout, PC-207.

cMnponenc Layout, PC-208.

COmponent Leyout, PC-209.

Component Layout, PC-212.

Component Layour. PC-214.

cmponent Layout, PC-217.

Colnponent LayoUr, PC-218.

component Layout, PC-219.

component

Layout,

PC-221.

corQpon.nt Layout. PC-229.

Componenr Layout, PC-230.

Mechanical Assembly.

Test Equipment Set-up for A/D Calibration.

AID

Converter Zero Adjuetmenrs

Test Cover Template, Top Panel.

Teat

Cover Template, Bottom Panel.

Page

1

2

2

3

4

5

9

10

11

11

12

13

14

15

15

15

17

19

20

21

21

22

22

23

23

24

24

25

27

27

31

54

55

57

58

0714

Page 4

SPECIFICATIONS

HODEL 445

SPECIFICATIONS

RANQE:

DISPLAI: Four digits from 000 to 1999: range ~4.

POLARITY SELECTION: Automatic.

RANQE

ACCURACY AND RESWNSE TIME:

I~ C,llbr.l~.l1.c1011 IllT .n*.nlb. bl.m,l Id,“Itmmnt.On 10.. to ,w

1. I1 dW1 “4” ‘1l1.1 WI .“d 100 Wol.l.dS Y”Ml”, m. mow

1. WI” “0 10 $00 P’cOlll.as %h”nlm, tn. l”D”l l * rllt” wt.

FILTER: Improves .c rsiection by Ikngthening rise tim.

LEN0

DISPLAY RATE: 24 r..dings per

INPUT VOLTAQE DROP: Less than 1 millivolt for full.

LINE

MAXIMUM INPUT OVERLOAD: 1000 volt. using .

ANALOG OUTPUT: tl volt from . 500.ohm sourc.

lo-’ amper. full scale (lo-” ampere. least

significant digit) to 104 ampsra in eight decade

ranges with 100% ov.rr.nging on all ranges.

pon.nt digit from 2 lo 9: paerity. overload and

Range Changing indication.

SELECTION:

Automatk: Range change possible after each A to

D conversion. An undrrrangscondition (<lOOdigits)

causer one range change to next more sewdive

rsng.. An overr.nge condition (21999 digit.) on

any range ca”ses rang. change to IO-’ A range.

Mmu~l: Front panel swi1ch.s permit manual r.nga

control.

&lw,,. ran,,, to, loc.1,~1.llO”.

to approximately 3/4 son lO-’ to IO-* A ranger.

DRIFT: Lass than 0.5% of full scale per week;

le.1 than O.OS%/‘C. after %.hour warm-up with

source volt.ge greater than 2 volts.

per second with 50+lz units), adiusbble toapproxi.

mstely 1 reading per two seconds.

With Filter in. m.ximum display rate is abeut l/s.

scale display on all r.ng.s when properly zeroed.

FREQUENCV REJECTION: 60 dS (ratio of peak.

to.pe.k current of power line frequency or multiple

which will cause less than 1 digit of error, to that

error). 100 dEon LO-rto 10-v A rmges with Filter

in. P..k input current should not .xc.ed 20 mA.

Keithlay or other current lim#t.d (up to 20 mifli.

amperes)

autorange mod.. Inst.ntaneous input current must

never exceed 125 m~lliamp.res.

for full.scale display. Maximum output. 1 millian.

per*. Output polarity is opposit. input polarity.

High Voltage Supply with Model 445 in

second

maximum (20

PRINTER OUTPUTS AN0 REMOTE CONTROLS:

Printer Output.: SCD positive output represents

each of the four digits, rang.. polarity. overrange.

r.nge changing and zero check. Standard cod. is

1.2.4.8. “0”<+0.4 volt: “l”>+ 10 volts at up to

one milliampw.: O=OOOO.

Print bmm.nd A: Positive pulse of 14 volts from.

2200.ohm source with 1 volt per mlcros.cond rise

time. 100 mkroseconds minimum pulse width. Print

commrnd given after each A to 0 conversion.

Print Commend 0: Same .s Print Command A ax.

cept pres.nt only when displaying an onrsnge

reading.

Remote Control.:

Hold # 1: Closure*

conversion .t that instant.

Hold # 2: Closure* to ground inhibits A to D

conversion .fter r..ding h.s been compl.t.d.

Trigger: Cbsure* to ground initiates one conv.rsn)n

when in Hold #2. Integration period starts 8.3

millisecond. (10 milliseconds on 50.H~ models)

.fter “Trigger” or r.le.se of Hold # 2.

R.nSr HoM: Closure* to ground prevents range

change.

2ero Check: Closure* to ground places instrument

in zero check mode and prewnts range change.

101 Range: Cbsure’ to ground places instrument

in 10-a ampere r.nge and holds until lo-* Range

rolnsed.

ISOLATION: Circuit ground to chassis ground: Greatsr

th.n l(r ohm. shunted by .02 microfarad. Circuit

ground mey bi floated up to 100 volts with respect

to ch.s.is ground.

COMMON MODE REJECTION: 100 V de or 200 V

pe.k.to.p..k rt line frequency will not affect resdmg.

CONNLCTORS: Input: Teflon.insul.ted triaxi.1. Analog

output: Amphenol SO.PCZF. Printer outputs and

rrmote controls: 50.pin Amphenol Micro.Ribbon..

Low md C.S. ground: Binding posts.

FOWEL

DIMENSIONS. WEIQHT: 5’1,” high x 19” wd. by lo”

ACCESSORIES SUPPLIED:

105.125 or 210.240 volts (switch selectsd).

60 Hz. 50.H~ models .v.il.bl.. 30 watts.

deep; nrt weight, I5 pounds.

Model 4451 Input Cable: 48” triaxial cable wth

triaxi.1 connector and 3 alligator clips.

M.ting digit.1 output connector.

to ground inhibits A to D

IV

0874

Page 5

MODEL 445

GENERAL DESCRIPTION

SECTION 1. GENERAL DESCRIPTION

1-1.

GENERAL. The Model 445 is B sensitive Automatic

Ran

ing Digital Picoammeter with eight ranges from

8

lo-

to 10-2 ampere plus 100% cwerranging.

l-2.

FEATURES.

a. Stability. Zero drift with time is less than 1

digit per day; drift with temperature is less than one

digit per O/C, making frequent adjustment unnecessary.

b. Overload Protection.

A transient overload of

1000 volts at up to 20 r,A will not damage the instru-

nlent.

C. Damping. A front panel FILTER Switch selects

additional damping of noisy signals on the 10-7. lo:*.

and 1O-g amp& r&es. - -

d. Digital Display. The digital display provides

3 digits with lo-= ampere resolution.

e. Variable Dieplay Kate. A front panel DISPLAY

RATE control adjusts from 24 readingslsec. to 1 read-

ing/Z eec, to accommodate the mode of data retrieval.

f. Autorsnning. Autorange circuit sense8 the input current and automatically selects the proper

range far each meaeurement.

g. Complete BCD Output and Control Lines. BinaryCoded-Decimal Outputs are provided on a rear panel

connector for significant digits, range, polarity,

overrange, and zero check. Cantrr,l lines are also

provided for remote control of ranging and A/D conver*ions.

,

Control

POWER witch (S102)

ZERO CHgCK (S1204)

ZERO ADJUST (R1207)

FILTER Switch (S1201)

RANGE-HOLD/AUTOMATIC (51203)

RANGE - lo-Z/DOWN (51202)

DISPLAY FATE (R1237)

0971

TABLE

l-l.

Front Panel Contr018.

Functional Description

Controls power to instrument.

Selects Zero Check Made.

Adjusts the zero offset.

Selects additional filtering.

Selects HOLD or AUTOMATIC modes.

Permits manual range selection.

Adjusts the AID conversion rate.

Paragraph

2-3, B

2-3, b

2-3, c

2-3, d

2-3, a

2-3, f

2-3, 8

1

Page 6

GENERAL DESCRIPTION

MODEL 445

PO&R

Switch

s102

DISPLA; RATE PI<TER

Switch 51205

Switch

51201

FIGURE 2.

ZERO ADJUST

Control R1207

RANGE

CHANGING

Lamp DS1201

Front Panel Controls.

ZERO CHECK

Switch S1204

I I

P&&E

HOLD/AUTO

10-2/DowN~

Switch 51203 Switch S1202

Terminal

INPUT Receptacle (51213)

LO Binding Post (51215)

GND Binding Post (51217)

PRINTER/CONTROL Connector (51214)

ANALOG OUTPU'I (51218)

2

TABLE 1-2.

Rear Panel Terminals.

Functional Description

Input connector, triaxial type.

Input LO connector.

Chassis Ground connector

Provides BCD outputs and control lines; 50 pins.

Analog Output connector, Mates with Keithley

Part NO. a-33.

Paragraph

2-1, a

2-1, a

2-1, a

2-8, a

2-7

I

0971

Page 7

MODEL 445

OPERATION

SECTION 2.

OPERATION

LOW

CASE

1NPUT

HIGH

Page 8

OPERATION

MODEL 445

Accurecv. The accuracy is specified in terme

!L

of a

percent of reading on esch range. A” addition-

al 2

1 digit is specified since the A/o conversion

has-e” inherent 2 1 digit uncertainty. Noise and

saurce~resistance conditions should be evaluated es

additianal meeeurement considerations.

a. Source Resistance.

The value of eowce resist-

ance can affect the measurement if the loading effect

of the picoammeter is significant. To avoid a de-

gradation of zero drift, the picoammetee range should

be selected so that the range feedback resisrar is

much lesa than the e~urce resistance. The zero drift

epecificseio” is valid only for e~urce voltagee greafer the” 2 volts.

f. Overloads.

A unique input circuit provides

complete overload protection with feet recovery. The

maximum overload is 1000 volts using e current limited supply (up to 2OmA) such as Keithley Models 240.4,

245, or 246.

Instantaneous input current mwt “ever

exceed 125 milliamperes. With a” input voltage up

to 1000 volts use e current limited supply or a series limiting resistor (8000 ohms minimum).

TABLE 2-1.

Typical Reading Time With Filter “OUT”.

g. Reading

Time.

The time interval for a new

reading to take place depends on the Model 445 front

panel Settings as well as the chareceeristics of the

input signal. The various time intervals which co”etitute the total reading time are described es

follows. The intervals are graphically shown in

Figure 5.

1. T1 = A/D Conversion Time until first range change.

2. T2 = Total Time for all successive range changes.

3. Tj

= A/D Conversion Time to first an-scale reading.

4. Tq = Total Settling Time until reading is final.

h. Off-Ground Measurements. The Model 445 can be

used far off-ground meeeurements with the circuit low

floated up to 100 volts with respect to chassis ground.

Circuit low to chassis ground isolation is greater

then 106 ahms shunted by .02 microfarad. When making

off-ground meeeuremente discannect the LO to GND

shorting link on the rear panel. A triaxial cable

should be used to maintain noise shieldine and to

provide ueer safety., The BCD autputs are”co”“ected

to circuit low and therefore muet be used with devices which ce” be Operated off-ground.

Input

Signal

10-9

10-g

Initial Sampling Range Ranging Final Range

Range

A 10-2 A .042 7

10-2 (1)

A A

Time Tl Sec.

.042

(1)

A 10-2 A .042 (1) 5

10-7

10-6

10-5

10-4

10-2

A A .042 (‘1) 4

A 10-2 A .042 (1) 3

A 10-2 A .042 (1) 2

:;I; ; .042 .042 (1) 0 1

(1)

Changes

6

Time T2 Sec. Time Tg Sec. Time Tq Sec.

Settling Total

.120 (3) .498 (12)

.294

(7) .042 (1)

.252

(6)

,042

(1)

.210 (5) ,042 (1)

.168 (4) .042 (1)

.126 (3) ,042 (1)

.084 (2) .042 (1)

,042 0 (1) ,042 ,042 (1)

,060

(3)

.OlS (3) .312

,015 - .267 (6)

,012 - .222 (5)

.003 - ,171 (4)

,003 .003 - - ,129 ,087 (3)

(0) (1)

Time Sec.

.396

(11)

(10)

(2)

4

PIGoRE 5.

Reading Time.

0971

Page 9

MODEL 445

FRONT PANEL CONTROLS.

2-3.

POWER Switch (S1021. This switch controls the

a.

line power to the instrument.

A rear panel fuse

PlOl protects the instrument in case of malfunction

of the power supply or power switch.

OPERATING PROCEDURE.

2-4.

Preliminary Pracedure.

a.

1. Check the 117-234" Switch (SlOl) on the rear

panel for proper line voltage.

OPERATION

b. ZERO CHECK Switch (S1204L This switch selects

either "NORMAL" or "ZERO CHECK" modes of operation.

I" "ZERO CHECK" "asitio", B relay is activated which

places a short across the feedback of the picoammeter.

Zero Controls R1238 and Rl207 ca" be used to adjust

the zero offset as necessary.

c. ZERO ADJUST (R12071. This control provides

"FINE" adjustment of the zero offset. The internal

zero control Rl23S provides "COARSE" adjustment.

d. FILTER Switch (51201). This switch selects

either mininu,, damping ("OUT" position) or additional

A

damping ("IN" position).

more complete diacussio"

of the "FILTER" mode is give" L" paragraphs 2-2, c

and 2-2, g.

e. RANGE - HOLD/AUTOMATIC Switch (51203). This

switch selects automatic re."e.i".z weratio" in "ADTO-

_ _

MATIC" position or manual ranging in "HOLD" position.

I,, "HOLD", the range is held at the existing range

displayed until the switch is changed or the range

is manually changed by either S1202 or the external

control lines.

f. RANGE - 10-2/DOWN Switch (51202). This switch

is a nomentary-contact, "armally open switch for ma"-

ual range changes.

This switch should be used with

Switch 51203 in the HOLD position. When Switch S1202

is nmentarily set to "lo-2", the Picaawneter resets

the range display t" 10e2. However, each time the

switch is set to "DOWN" Lmsition. the Dicoammeter down

w to a more sensitive range:

The'sequence afdawn ranging would be typically 10-2, lo- , 10 4, 10-5,

;riO$ith

a reset after 1O-g range is reached, that

) 10-9, 10-q.

2. Check for proper rated fuse.

3. Connect the power cord, place the POWER Switch

ON, and allow a 30-minute warmup for critical measurements.

4. Adjust the ZERO Contra1 (R1207) as necessary.

Zero is indicated by alternately flashing + polarity

lights.

5. Connect the source as described in paragraph

2-l.

b. Measurements. The Model 445 measures current

over a full-ran e 6 from 10 milliamperes (10m2A) to 1

"anoampere (lo- A) with resolution to 1 picoampere

(lo-12A). The display will indicate either a positive or negative input current autamatically. (A

p"sitive current is defined as a positive "conven-

tional current" applied at Input High with respect

to Input LOW).

DIGITAL DISPLAY. The display has three digits

2-5.

plus one for overrange indication. The range is

displayed in scientific notation where the exponent

is automatically displayed for ranges 10-2 through

10-9 amperes, To interpret the display refer LO

Figure 6.

A" overload condition will cause the display cubes to blank o"t so that "o ambiguous display

is possible.

This

situation is described under 2-4,

d Autoranging.

g. DISPLAY RATE (R12371. This control adjusts the

A/D Converter conversion rate from 24 readingslsec.

(MAX) to 1 reading/Z sec. (approx).

How to Interpret the Digital Display

The reading shown in Figure 6 above should be

interpreted as follows. The polarity is dis-

played by a lighted "f" or "-" indicator. The

decimal point remains fixed with respect to the

digits.

I,, the example, the reading is 1.676

(three digits plus a "one" for overrange). The

range multiplier is 10-9 (the exponent is a"to-

matically selected by the autorangi" circuit).

The complete reading is +1.676 x lo- 8 amperes.

FIGURE 6.

0971

Digital Display.

5

Page 10

OPERATION

TABLE 2-2.

Output Information and Controls.

lode1 4401 Printer Output Cards: Provide SCD outp"t

and external control of Model 445; may be purchased

installed or separately for field installation (no

wiring required).

Printer Outputs: SC0 pwitive o"tp"t represents

each of the four digits, exponent, range, zero,

polarity and averrange. Standard code is l-2-4-8.

"O"< +0.4 volt; "1" 5 +lO volts at up to one milliampere; O=OOOO.

Print Command: Positive pulse of 14 volts from a

2200-ohm source with 1 volt per microsecond rise

time, 100 microseconds minimum pulse width.

Remote Controls:

Hold #l: Closure to ground inhibits A to D conver-

sion at that iridtant.

Hold 82: Closure to ground inhibits A to D canver-

sion after reading has been completed.

Trigger: Closure to ground initiates one conversior

when in Hold 112. Integration period starts 8.3 ms

(10 ms on SO-Hz models) after

"Trigger"

or release

of Hold i/Z.

Connector: SO-pin Amphenal Micro-Ribbon mounted on

Model 445.

Output mating connector supplied with

4401.

MODEL 445

NOTE

The term "Closure to Ground" or "Grounded control

line" means a short to commn directly or

a saturated NPN transistor (VC, <

+0.4V).

the "COMMON" as supplied at the PRINTER/CONTROL

connector should be used for closures to ground.

TABLE

2-3.

Full Scale Magnitude.

Connector

Pi" No. Output

1

2

26

27

3

4

28

29

5

6

30

31

.l x 10" 1

2

x 10"

4 x 10"

8 x 10"

1 x 101 1

2

x 101

4 x 101

8 x 101

1 x 102 1

2 x 102

4 x 102

8

102

x

Decimal Digits

2

4

8

2

4

8

2

4

8

through

Only

0971

Page 11

MODEL 445

OPERATION

2-6. A!JTORANGING. The sutomatic ranging feature of

the Model 445 permits rapid measurements of B wide

range of currents.

a. AUTOMATIC Mode. In this made the Model 445 will

automatically select the full-range that permits a

display from 0.100 to 1.999. The Model 445 changes

range in decade steps from .a less sensitive range to

a mare sensitive range. This process is defined as

“down-ranging”. If the input current causes the dis-

play to exceed 1.999, the” the Model 445 will a”tomatically change to “10-2” range and “down-range”

until the display Is between 0.100 and 1.999.

1. DOWN Range Control. The “se of Switch S1202

permits manual range changing. This switch is a

momentary-contact type switch. Each time the switch

is depressed to “DOWN” position, the range will

“down-range” from a less sensitive range to a more

sensitive range.

When the 10-V range is reached,

actuation of the switch will cause the range to go

to 10-2 or “reset” position.

10-2 Range Control.

2.

When switch 51202 is set

to “10-Z” position, the range will be “reset” to

the lo-2 range regardless of the current input.

Once the switch is released the Model 445 will re-

vert to normal operation.

b. HOLD Mode. When switch 51203 is set to “HOLD”

position, the full range of the instrument will hold

regardless of the input current. This switch position inhibits the operation of the DOWN/lo-2 switch.

NOTE

If the input current exceeds 1.999 for the

range in “HOLD”, the display tubes will

blank indicating a” overload on that range.

If Switch 51203 is set CO “AUTOMATIC” the

Model 445 will change to 10m2. Then if the

input current does not exceed 1.999 on the

10-2 range, the display will indicate

normally when the final range is selected.

b. Output Codes and Levels. The PRINTER/CONTROL

0ut”uts are Sinarv Coded Decimal sianels with l-2-4-

8 S&da-d Code. .

The Standard signal levels are as

follows:

Logic “0” < +0.4 volt

Logic “1” > +lO volts at up to 1 milliampere.

c. Output Information. The various Output Informa-

tion and Controls sre surmnarized in Table 2-2.

1. Full Scale Magnitude. The Magnitude of the

reading is indicated by SCD o”tp”ts which correspond to the three front panel display lights (three

significant digits) as shown in Table 2-3.

2. Overrange Indication. Overrange is indicated

by the fourth (from the right) display light and

corresponding SCD output as shown in Table 2-4.

Overload is indicated by a blanked display and

corresponding BCD output. The output at pin 33

will be a logic “1” while the magnitude will be

represented by logic “0” as shown in Table 2-4.

TABLE 2-4.

Overrange and Overload Outputs

Connector Decimal

Pi” NO. output Digits

7

8

1 x 103

Gammon 0

32 COSDIIO”

33

Polarity and Zero Check Indication. The

3.

Overload (8 x 103) 8

1

0

polarity is indicated automatically by the Polarity

indicator and corresponding BCD output as shown in

Table 2-5. Additional BCD levels are available at

pins 14 and 39 for use with some printers. The

zero check mode is indicated by a BCD o”tput from

pin 38.

TABLE 2-5.

Polarity output

ANALOG OUTPUT. The analog OUtput on the rear

2-7.

panel (51218) provides a voltage of 1.05 volts corresponding to 1.000 o” any range. Since this output has

a source resistance of 499 ohms, the recording device

must have a load resistance greater than 10 kilohms

to obtain 1.000 volt for full range.

If a recorder

such as the Keithley Model 370 is available, an Isolation Amplifier (such as Keithley Model 399) must be

used to provide up to 1 milliampere current for full

range.

2-8. DIGITAL OUTPUT.

8. General. The Model 445 has o”tp”t buffer print-

ed circuit boards which provide Binary Coded Decimal

(BCD) outputs.

A factory wired SO-pin PRINTER/CONTROL

connector is provided on the rear panel (51214). A

spare cutout is provided on the rear panel for installation of an additional PRINTER/CONTROL connector.

bnnector

‘in No.

13

14

38

output

Polaritv

+15v .

Zero Check

Decimal

Digits

39 + 15v

4. Range Indication (Exponent). The range or

exponent has a corresponding BCD output as shown

in Table 2-6.

TABLE 2-6.

Lange or Exponent Indication

onnector

Pi” No. output

9

10

34

35

1 x 10 Range

2 x 10 Range

4 x 10 Range

8 x 10 Range

Decimal

Digits

1

2

4

8

7

Page 12

OPERATION

MODEL 445

5.

Ranging Signal.

A single binary signal is

available at pin 49 which corresponds to 8. ranging

signal.

The logic level is “1” whenever range

changes are occurring so as to indicate invalid

readings.

d. External Control.

1. General. To obtain aptim~ system perform-

ance, Ft is often desirable t” “perate the Model

445 synchronously with other digital equipment such

as printers, paper tape punches, computers, and

other data handling devices.

2. Applications. Several approaches may be used

in designing the overall syetem contra1 scheme.

The Model 445 can be used to provide master

*).

control of external devices so that maximum poss-

ible conversion rates ca” be obtained.

An external device can be used far master

b).

control; such as a high speed printer.

A completely independent “master clack”

Cl.

can be used for system caner01 for maximum flex-

ibility.

3. Description,

“HOLD 1”. This control inhibits A to D

=).

conversion at the instant a closure to ground is

made.

The conversia” cycle will resume immediate-

ly when the “HOLD 1” line is opened.

“HOLD 2”. This control inhibits A to D

b).

conversion after a complete reading cycle. Further

conversions are inhibited as long as a closure to

ground is made. The conversion cycle will resume

immediately when the “HOLD 2” line is opened.

“TRIGGER”. This control initiates one com-

Cl.

plete conversion when “HOLD 2” line is grounded.

Closure t” ground may be momentary or any longer

duration to initiate a conversion.

“PRINT COMMAND A”. This control provides

d).

* positive going pulse of 14 volts after * cornplete A to D conversion is made and all data outputs are final readings.

No change can take place

(except Zero Check) for 25 milliseconds. This

“Print Command” signal is present regardless of

the mode (ADTOMATIC or HOLD).

“PRINT COMMAND 8”

This control is similar

toe)‘Print Command A” except that na signal is

present if the instrument is changing range.

f). Zero Check. This control places the Model

445 in Zero Check and prevents automatic range

change when a closure to ground is made.

Range Hold Control. This control prevents

9).

automatic range change when a closure to grand is

made.

10e2 Range Hold Contral. This contra1

h).

causes the range t” change to low2 when a closure

to ground is made.

The range is held until the

line is released.

i). High and Law References. Two reference

voltages are provided t” define the “HIGH” and

“LOW” digital output states far external printers

or other devices; “HIGH”** +Bv, “LOW” = +2v.

Summary of Digital 0”tp”ts and Controls.

e.

Standard Output Codes and Levels. The sta”-

1.

dard output code for Model 4401 Printer Output Cards

is l-2-4-S Binary Coded Decimal (BCD). A binary

coded decimal digit is represented by a four-bit

binary code as shown in Table 2-7.

TABLE 2-7

Decimal

Number

0

1

2 0 0

3

4

bit 3 bit

0 0 0

0

0 0

2

bit

0 0

1 0

1

1 bi,

4 0 1 0

5

6 0

7

8

9

0 1 0

1 1 0

0

1

1 1

0

0 0

1 0 0

Refer to Figure 17 for a circuit diagram of the

Model.4401 Standard Printer 0”tput buffer stage.

0

1

1

0

1

1

1

TABLE 2-8.

Typical Digital Outputs.

Fr”“t Panel

Digital Display

+ 0.275

+ 1.347

- (blank)

+ (blank) +

- 0.023 0 023 3 0 - ,023 x 10-3 A

+ 1.962 10-6 +

- 0.586 10-4 0 586 4

Range

Exponent Polarity or overload gag.

10-5

10-9

+ 0

* 1

10‘2

10-7

10-3

Sign. Digit

Range

EXP.

275 5 0 + ,275 x 10-5 A

347 9 0 + 1.347

8 000

8 000 7 0

1

962 6

Ranging

Signal Interpretation

2 0

negative overload

positive overload

1 ranging

1 ranging

8

x 10-V A

I

0971

Page 13

MODEL 445

OPERATION

in No.

1 1 x 100

2 2 x 100

2 1 2 x x 101

5

6

7

8 Caman

9

10

Output

1 x 102

2 x 102

1 x 103

1 x 100

2

x 100

11 Blank

12 Common

13

14

1 x 100

+ 15"

15 Blank

16 Blank

101

PRINTER/CONTROL Connector Pi" Identification.

TABLE 2-9.

F"llCtiOll

oata

Data

Data

Data

oata

oata

oara

Range

Range

---

--_

P&WiQ

___

___

___

Pin No. Output

26

27

28 29

30

31

32

33

34

35

36

37

38

39 + 15v

40

41

4 x 100

8 x 100

4 8 x x 101 101

4

x 102

8 x

102

Comon

8 x 103

4

x 100

8 x 100

Common

cormnon

1 x 100

Blank

Blank

Function

mea

oaea

Data Data

oata

oata

___

Overload

Range

Range

___

___

Zero Check

___

___

-_-

17 + 15v

18

19

20

21

22

23

24 + BV

25 + 2"

+ 3.6V

Grounded

Grounded

Grounded

"lank

+ 14"

Pulse

___

___

Remote Zero Check

Remote w2

Remote Range Hold

--_

Print Command A

Hi Reference

Law Reference

42

43

44

45

46

47

48

49

50

- 15"

COllllTlO"

Grounded

Grounded

Grounded

Blank

+ 14"

Pulse

1 x 100

Blank

___

_-_

Hold ii 1

Hold ii 2

Trigger

___

Print Command B

Ranging Signal

0971

FIGoRE 7.

Printer/Control

connector.

Page 14

OPEBATION

MODEL 44s MODEL 44s

PRINTER/CONTROL Connector. The PRINTER/CON-

2.

TROL Connector used on the Model 445 provides for

connectiom to 50 ~,ins as shown in Table 2-9. The

mating connector supplied is an Amphenol Part No.

57-30500 or Keithley Part Number CS-220.

3. Analog-to-Digital Conversion Cycle,

The analog-to-digital conversion cycle

a).

can be initiated in any one of three ways.

1. DISPLAY RATE Control Set at MAX. With

the DISPLAY RATE Control set at MAX, the end

of one complete conversion triggers a second

conversion to obtain the maximum conversion

rate of 24 readings per second.

2. DISPLAY SATE Control Set at Other Than

MAX. With the DISPLAY RATE Control set at

some position other than MAX, (uncalibrated

control setting) the end of one complete conversion triggers a second conversion which is

delayed by a specific time interval (DELAY).

The time delay is a function of the position

of a continuously variable control to provide

a conversion rate from 24 readings per second

to 2 readings per minute.

3. ‘HOLD 2” With TRIGGER Control. With the

‘TlOLD 2” camand grounded, a closure to ground

of the “TRIGGER” command initiates one complete

conversion cycle. A second convereion will

fallow only if the TRIGGER command is removed

and reapplied a second time. The maximum conversion rate using an external trigger is 24

readings per second.

Conversion Cycle Timing. The Conversion Conversion Cycle Timing. The Conversion

b). b).

Cycle is composed of three timing periods, namely Cycle is composed of three timing periods, namely

Integrator Zero, Integrator Sampling, and AD Integrator Zero, Integrator Sampling, and AD

Counting period. Counting period. Refer to Timing Diagram Figure Refer to Timing Diagram Figure

1. Integrator Zero Period (ZERO). When a

trigger pulse initiates a new conversion cycle,

the Integrator circuit is zeroed for a period

not to exceed 8.33 milliseconds for 60 Hz operation. (The Integrator Zero Period is 10.00

milliseconds for 50 Hz operation).

2. neegratOr sampling Period (INTEGRATE).

The Integrator Sampling Period follows automat-

ically the Integrator Zero Period and lasts for

the duration of 16.67 milliseconds for 60 Hz

operation. The Integrator Sampling Period lasts

for B duration of 20.00 milliseconds for 50 Hz

operation.

3. AD Counting Period (COUNT). The AD Counting Period is initiated immediately following

the Ineegratar Sampling Period. The actua$

counting time duration will depend on the actual

integrator voltage up to a maxilll”m Of 2000 clock

pulses of 16.67 milliseconds. Following the

counting period a Buffer/Storage command is

automatically generated in order to store the

new reading in the output registers.

2-9.

117-234V LINE POWER OPERATION. The Model 445

is shipped far use with 117V ac line power unless

ordered for 234V operation. TO cO”“ert any inserunlent

for either 117V or 234V operation, use a screwdriver

to set the 117-234” Switch on the rear panel. The

10

0971

Page 15

MODEL 445

CIRCUIT DESCRIPTION

SECTION 3.

CIRCUIT DESCRIPTION

3-l. GENERAL. The Model 445 consists of three sec-

eions packaged together in one chassis: a sensitive

picoameter, an automatic ranging circuit, and an analog-to-digital converter.

a. Picoammeeer. The picoammeter is a linear dc

amplifier connected as a feedback anmxeter with eight

current ranges.

b. Autarangina Circuit. The autoranging circuit

senses the magnitude of the display so 88 to trigger

the range changing circuits and cycle from 10-2~ through

lob9 amperes full scale.

C, Analog-to-Digital Converter. The A/D converter

is a dual slow, integratina t”Pe converter with medium conversion &ace, cold cathi& readout tubes, BCD

outputs end optional external controls.

3-2. PICOAMMETER.

a. Operation. The picoammeter consists of a linear

dc amplifier with a 1 volt full scale

mensitivity.

The

amplifier provides an analog output up to Z~volts for

100% overrange display. The RANGE resistors are connected across the feedback of the amplifier.. A simplified diagram of a feedback ammeter is shown in

Figure

9.

b. Circuitry.

The

amplifier input stage is a pair

of insulated-gate, field-effect transistors (IGFET)

designated 91201 and Q1202 connected in a differential

configuration. The circuit designated 234308 is a

spedlal overload

protection

circuit

on

the Input PET

board. The gate,of Q1201 is connected to the input

through 10 Megohms while the gate of Q1202 is referenced to ground.

Potentiometer R1238 is an internal

COARSE ZERO adjustment. Potentiometer R1202 is an

internal BALANCE control. Transistors Q1203-Q1204

form a second differential amplifier stage. Potentio-

meeer RI207

is a front panel ZERO adjustment.

TrZl”Sistors Q1205 and Q1206 (emitter-follower) provide

sufficient gain for the analog output and A/D can”eTter. The analog output is connected through R614

(499CL)

R1215 and 01212).

to the dc amplifier output (the junction of

The full scale current sensitivity

is determined by the RANGE resistor connected across

the feedback. The RANGg resistance RP is composed of

a fixed resistance 81 plus a calibration adjustment

resistance K2 as shown in Figure 11. The RANGE resistors are arranged in “parallel” such that, an the

“1O-2’1

range, all eight RANGE resistors are connected.

Range selection and zero check are performed using

reed relays which are electrostatically shielded from

the high impedance circuitry to preve?f.coupling of

switching transients. The FILTER Switch

“ides additional damping on the 10-7, lo-

51201) pro-

$

, and 10-9

ampere ranges with an additional 40 dB rejection of

60 Hz frequency.

With the FILTER Switch set to “IN”,

the A/D conversion rate is set to 1 reading per second

max inlum .

3-3.

AUTORANGING.

a. operation.

FIGURE 9.

FIGURE 10.

Feedback Ammeter.

Range Calibration.

The autoranging circuit operates

from the BCD outputs of the A/D converter. If the

reading is less than O-l-O-0, then an “Under-range”

command is generated and the range relays are operated

to “Down-range” to a more sensitive range. If the

reading is greater than l-9-9-9, then an “Over-range”

command is generated and the range relays are operated so as to “reset” and then “Down-range”.

If the

HOLD/AUTOMATIC Switch is set to “HOLD”, the autorang-

ing circuit is inhibited and the range will hold regardless of the current being measured.

b. Circuitrv. Integrated circuits QA703, QA704A,

and QA704B code the BCD outputs to generate “Underrange” and “Overrange’! c,ommsnds. The “Buffer-stare”

command is delayed for approximately 5 microseconds

by Mono stable gates QA705A and QA705B, to allow

signals to settle. The range counter gates (QA801,

QA802) is a three-bit binary counter (“000” corres-

ponds to 1O-2, “111”

corresponds to 10-9 ampere). The

output of the range counter is decoded by gates QA803,

QA804 and QASOS into an “eight-line” code. The eight-

lines are encoded by gates QA806 and QA807 to yield

BCD range information. Gates QA809 and QAEIO store

the range information. The range display tube is

driven by transistors Q901 through Q908. Gates

QA902

and QA903 drive transistors 9909 through Q915

QA901,

to operate the read relays.

0971

11

Page 16

CIRCUIT DESCRIPTION

MODEL 445

ANALOG-TO-DIGITAL CONVERTER OPERATION.

3-4.

a. General,

cO”“erter is shown in Figure 13.

digital converter aperates using a dual slope inte-

gration technique which has inherent line frequency

noise rejection. The analog signal is applied to the

integrator far one complete line frequency cycle.

The analog signal is ehen removed from the integrator

input.

to zerc, to complete the voltage-to-time conversion.

The time interval to reach a “Zero Grassing” is counted and displayed on the “Readout” in proportion ta

the original analog signal. The sequence is then repeated for a second reading. A Timing Diagram is

shown in Figure 8.

major circuits which perform the analog-to-digital

conversions and provide various control commands.

pulses at a rate of 120 kilohertz for Electrometer

using 60 Hz line power. (The 50 Hz units have e pulse

rate of 100 kilohertz).

The voltage on the integrator is then driven

b. Circuits.

1. Oscillator or Clock

2. BCD counter

3. Delay Hold

4. Program/Decoder

5. Integrator

zero crossing Detector

6.

7. Buffer/Storage Register

8. DecaderfDriver

9. Numerical Readout

C. Oscillet~r or Clock.

A detailed block diagram of the A/D

The analog-to-

The A/D Converter is composed of nine

The Oscillaear praduces

d. BCD counter.

pulses with a Wea.1 range of 5000 c~unte. The C~unec

is composed of 4 individual cwnters designated 1, 10,

100, and 1000,

e. Delay Hold. The Delay Hold circ”it controls the

DISPLAY BATE function and external Hold and Trigger

commands as shown in Figure 14. It determines ehe

length of time between A/D conversions when the front

panel DISPLAY RATE Control is set t0 any position

other than MAX. The clock is stopped at the beginning

of the ZERO (2) period for a time determined by the

rotation of the DISPLAY RATE Central. If eneures thee

when the Hold 2 Fe grounded the conversion in process

will be completed and new data will be stored in the

output storage register.

hibited at ebe beginning of the ZERO period (2). The

instrument will remain in this condition indefinitely

until Hold 2 %s released or until Trigger is shorted

to ground. After cowersian, the instrument will

again be inhibited at the beginning of the period (2).

If both Switches Sl and S2 are closed, the canversion

cycle works in the following manner. After the previous conversion has been completed, the leading

edge of the program co,+,nd (2) reeete the flip-flop.

In this new condition Q is high and, therefore, the

clack gives no output. At that time, the unijunction

timer begins its cycle and, after the appropriate

time, produces e pulse that sets the flip-flop. This

changes Q to a low state and a new converslan cycle

begins.

(2) command again reeets the flip-flop and the timer

again issues a new pulse to set the flip-flop.

After the reading has bee,, completed, the

The BCD Ccuneer counts the Clock

Then the clock will be in-

12

INPUT+

r

FEEDBACK

PICOAMMETER

rc

b A-TO-D CONVERTER OUTPUT

AUTO RANGE

RANGE

DISPLAY

FIGURE 11.

DIGITAL

DISPLAY

T ’

a---

RANGE

overall Black Diagram.

0971

Page 17

1 .-

-

Page 18

CONVERTER

Page 19

MODEL 445

CIRCUIT DESCRIPTION

f. Program/Decoder.

The Program/Decoder circuit

produces event canrmands to control the overall sequence of events for a complete A/D conversion.

g. Integrator. The Integrator circuit operation

is composed of three periods.

1. Zero Period.

During this period the integra-

tor amplifier is zeroed by the closure of switch Sb,

Switches S,, S,,

and Sd are open to prevene inte-

grator charging es shown in Figure 15.

2. Integration

switch Sb, S,,

Period. During this period,

and Sd ere open. Switch S, is closed

to permit charging by the analog voltage for a period of one line cycle.

Discharge Period. During this period, switch

3.

S, is open to prevent further charging by the ana-

log signal. Either switch S, or Sd is closed to

drive the Integrator voltage to zero. A reference

current of opposite polarity to the input current

is applied through either switch SC or Sd. The

Discharge Period ends when the Zero Crossing Detector circuit detects a zero Integrator output.

h. Zero Crossing Detector. The Zero Crossing De-

tector circuit provides a “High” or “Low” level output depending on the polarity of the detected input.

Refer to Table 3-l for e description of voltage outputs.

FIGURE 14.

Delay

Hold Diagram.

Zero Crossing Detector Output Levels.

TABLE 3-l.

0”

0”

-0.5v

+3.5v

+1.5v 0”

0”

+1.5v

i. Buffer/Storage Regisfer. The Buffer/Storage

Register is composed of “flip-flops” arranged to copy

the states of the various BCD counters. The Buffer/

Scarege Register requires e Buffer Store command be-

fare any information can be transferred. The “flipflap” circuits provide coded information for Decoder/

Driver and the BCD outputs.

j. Decoder/Driver. The Decoder/Driver circuit Qe-

codes the BCD information from the Storage Register

into ten-line decimal code. The Driver circuit then

drives the proper numeral in each of the Numerical

Readout tubes,

k. Numerical Readout. The Numerical Readout consists of four numerical indicators and one polar,ty

indicator driven by the Decoder/Driver, Polarity ad

Overload Drivers.

FIGURE 15.

Integrator Block Diagram.

1. Summery of Operation. The operation of the A/D

Converter ten be described by considering a typical

conversion cycle.

1. The

Oscillator or Clock provides pulses at a

rate of 120 kilohertz.

0971

FIGURE 16. Zero Crossing Detector.

Page 20

CIRCUIT DESCRIPTION

2.

The Delay Hold circuit gates the output of

the Oscillator depending on the state of the "RS

flip-flop" and elle "Hold 1" control line. A unijunction timing circuit provides a delay period

before a conversion is initiated. The time delay

is selected by the front panel DISPLAY RATE Control.

3. The BCD counter serves as a master timing

control for the A/D conversion cycle. The timing

is accomplished by the "1000" co"neer which has

five

coded

4:

states, namely 0, 1, 2, 3,

The

Program/Decoder controls the sequence Of

and

4.

commands based an the coded etatee from the BCD

counter.

shown in Table 3-2.

The decoded commands are described as

the "2"

command initiates the

integrator ZERO period which removes any residual

charge on the integrator capacitor. The "3,4" CO",mand initiates the

INTEGRATE

period which permits

an integration of the analog signal. At the end of

the INTEGRATE period, the "0,l" command initiates

the COUNT period.

TABLE 3-2.

Command

F""ction

MODEL 445

ANALOG-TO-DIGITAL CONVERTER CIRCUITRY.

3-5.

a. General. The circuits described in this aectio

are located on the various Sub-Assemblies listed beloh

and in Table 7-2 of Section 7.

1. Oscillator Board, K-217.

2.

Integrator Board, K-219.

3. Display/Overload Board, X-241.

4.

Readout Board, PC-229.

5.

Polarity Board, K-207.

6.

Output Buffer Board, X-218.

7. Output Buffer Board, X-209.

b. Oscillator Board.

The Oscillator Board contains

portions of three circuits: the Oscillator (clock)

circuit, the Delay/Hold circuit, and the Discharge-

Voltage CUrrent source circuit.

1. Oscillator Circ"if.

Transistor Q501, crystal

Y501, and phase shift capacitors C501, and C502 farm

a "Colpitts"

C504

are used for trimming the oscillator frequency.

type oscillator. Capacitors C503

and

The output is taken from the collector of transistor

Q510 which is a common emitter gain stage'used for

squarLng the output.

Transistor

Q507 serves as an

emitter-follower to reduce output impedance.

2

3,4

031

When the "3,4" command is given, the integra-

5.

ZERO

INTEGRATE

COUNT

tor is charged by the analog signal for B period of

1 line cycle of 16.67 milliseconds.

6,

When the "O,l" command is given, the analog

signal is removed and the integrator output is driv-

en to zero by a reference current. The Zero Cross-

ing detector senses a zero crossing of the Ineegratar output and removes the reference cuxene. The

Detector provides outputs as shown in Table 3-1. The

+1.5 volt levels are provided for control of the

Integrator and Polarity Storage Register. A pulse

command is also produced to initiate a Buffer/Store

and Print Command o"tp"t.

7. When the Buffer/Store command is given, the

Buffer/Storage Register copies the BCD COUnterStateS

at that instant of time.

The BCD coded information

in the RegFster is then available for the Decoder/

Driver and external printout.

The

8.

Decoder/Driver decodes then Buffer/Storage

output and drives the'Numerica1 Readout for a digit-

al display.

9. The RCD Output information is available at the

Model 4401 Buffer Card o"tp"ts in the form of posi-

tive (+lO volt) tr"e logic (l-2-4-6 BCD Code).

The conversion cycle is completed when the BCD

10.

Counter reaches 2000 co"nt~ and the Program/Decoder

provides a "2" command to initiate a new con"ersFon

cycle.

The Unijunction Timing Circ"it will initiate

11.

the ZERO period after a present time delay controlled

by the front panel DISPLAY

RATE

Control.

2. Delay/Hold Circuit. There are three major

components in ehe Delay/Hold circuit: an "RS" type

flip-flop circuit, a "Unijunction" timing circuit

and a "Hold" gate circuit.

"RS" Type Flip-Flop Circuit. The flip-flop

a).

gafes ehe output of the clock depending an the

input8 Bt pins R and S.

The RS flip-flop is constructed of gates QA5OlB and QASOlC. The pins

are identified as shown in Figure 16.

"Unijunction

b).

tion timing circuit determines the time delay be-

" Timing Circuit. The "nijunc-

tween conversion cycles to obtain the desired conversion rate as determined by the front panel DIS-

PLAY RATE Control.

The circuit is composed of

transistors Q513 and 0514, timing capacitor C507,

and timing resistors R532 and R1269 (DISPLAY RATE

Control potentiometer located on the front panel.

"HOLD" Gate Circuit

C).

for identification of switches Sl and S2). The

. (Refer to Figure 16

"HOLD" gate circuit is composed of gates QA501A,

QASOlD, and QA502 (A, B, C, and D). Switch Sl is

gate QA501A and is controlled by eirher~the "HOLD

2"

external line or the "MAX" position on the DIS-

PLAY RATE Control.

Switch S2 is transistor Q513

which is controlled by either the "Q" output of

the flip-flop or the "HOLD 2" external line. The

"HOLD

1" circuit is composed of gates

QA502B

and

QA502C.

3. Discharge-Voltage Current Source Circuit.

The positive current source composed of transiseors

Q502 and Q506 delivers a constant current of ~7.5

milliamperes to drive a 9-volt zener diode D602

(located on the Integrator Board, W-246) "hen +REF

Terminal (Pin 13) is greater than +0.7 volt. The

negative current source composed of transistors

QSOS and Q509 delivers a constant current of -7.5

milliamperes to drive a g-volt zener diode ~601

(also located on the Integrator Board, X-219).

16

0971

Page 21

MODEL 445

CIRCUIT DESCRIP’fION

C. Integrator Board.

The Integrator Board consists

of two major circuits: the Integrator circuit and the

Zero Crossing Detector circuit.

1. Integrator Circuit.

The operation of the In-

tegrator is controlled by the positions of switches

s,, sb, SC> and sd.

Switch S, is transistor Q605.

Switch Sb is transistor Q606. Tranststors Q601

through 9604 are control circuits arranged to turn

off the proper FET switches depending on the signals

at pins 11 and 12. The integrator amplifier consists

of transistors 9607 and Q608 and integrated circuit

QA601. The feedback capacitor is C603. Switches S,

and Sd (located on the Oscillator Board, PC-217)

control the current for 9-volt zener diodes D601 and

0602. Resistors R602 through R611 are full-scale

calibration resistors.

2. Zero Crossing Detector Circuit. (Refer to

Figure 18).

The high gain amplifier is composed of

cascaded amplifiers QA602 and QA603. The zero ad-

justment network consFsts of resistors R645, R646,

R648, R649, and R650, and diodes D611 and D612.

Transistor Q609 and other components form a 6-vole

supply far QA603 and the zero circuit. The levelsplitter circuit consists of diodes 0613 and D614,

resistors R651, K652, and R653 and gates QA604 (A,

B, C).

d. Display/Overload Board. The Display/Overload

Board contains a BCD Counter (“1000” counter), a Program Decoder circuit, and an Overload Control circuit.

1. The BCD Counter L8 composed of “J-K” flip-flop

circuits QA301 and QA302.

2. The Program Decoder circuit is composed of

gates QA303C and qA303D (3.4 Cownand) and QA304A,

QA304B, QA304C, QA304D, QA305A, QA305B, QA305C,

QA305D, QA303E, QA306A, QA306B. and QA306C (0,l &

2 Commands).

f. Polarity Board, The Polarity Board contains

various circuits which are controlled by signal “B”

and “C” from the Zero Crossing Detector signal as

shown in Figure 16.

1. Polarity Indicator Control Circuit. This

circuit drives the Polarity Indicator DS201 to provide a Polarity display. QA201A and QA206.4 are J-

K Flip-Flop circuits which control transistors Q201

and Q202,

2. Polarity Print Signal Circuit. The Polarity

Print signal is determined by the Q output of J-K

flip flap QA206A.

3. Discharge Voltage Polarity Control Circuit,

The +REF Control signal is determined by QA201.4 and

gate QA204A.

The -REF Control signal is determined

by QAZOZA, QA203A, QA203B, QAZOZB, QAZOZC, QA203C,

QA203D,

and QA204B.

4. Buffer Store Command Circuit. The Buffer Store

coormand is provided by J-K flip QAZOIB and gates’

QA204C and QA207A.

5. Overload Blanking Circuit. A portion of the

Overload Blanking circuit QA204D, QA206B, and QA207B

is located on the Polarity Board. The remainder of

the circuit is located on the Display/Overload Board

PC-241.

g. Output Buffer Board, PC-218. This board contains 15 buffer circuits to provide BCD Data and Overload and Polarity Print signals. Buffer circuits “A”

through

“P”

consist of transistor buffer stages as

shown in Figure 17.

3. The Overload Control circuit provides an over-

load signal if a zero crossing does not occur in the

Discharge Period (0,l).

It controls the Numerical

Blanking circuit and provides an Overload Print

eiglL¶l.

e. Readout Board.

The Readout Board contains Decade Counter circuits, Buffer Storage clrwlts, and

Decoder Driver and Display clrcults.

1. Decade Counter Circuits. Each decade co”nter

is composed of four J-K flip-flops. Circuits QA401

through QA406 are Dual J-K Flip-Flop integrated cir-

cuits.

Buffer Storage Circuits. The Buffer Storage

2.

register is composed of Dual J-K Flip-Flop integrated

circuits qA409 through QA414.

3. Decoder Driver Circuits. QA415, QA416, and

QA417 are Decimal Decoder Driver integrated circuits.

4. Display Circuits. V401, V402, and V403 are

Readout Tubes for Units,

Tens,

and Hundreds respec-

tively.

Page 22

CIRCUIT DESCRIPTION

MODEL 445

h. 0”tp”t Buffer Board, X-209. This board contains six buffer circuits and various gate circuits to

provide Print Cornnand and Range Signal Print signals.

1. Buffer Circuits. Buffer circui~ts “A” through

“E” provide BCD Range information.

2. Print Command Circuits. Buffer circuits com-

posed of transistors Q1101, Q1102, Q1104, Q1105,

Q1106, and 91107 provide Print Cooanand signals as

determined by gates QAllOl (A, B, C, and D) and

QA1102 (A, B, C, and D).

3. Range Signal circuit. Translseors QllOS,

QllOV, end QlllO comprise a Range Signal Buffer

stage controlled by the Range Signal.

4.

Reference Voltages. A High and Low Reference

valtage is provided by resistor divider R1114, R1115,

and R1116. The voltages are +S volts (High) and +2

volts (Low),

POWER SUPPLIES. (Schematic 234483).

3-6.

a. h.15 Volt Supply. The +I5 volt supplies tap ac

power from a secondary of transformer T101. Diodes

D103, D105, D107 and DlOS and capacitors Cl04 and Cl05

compose a fullwave rectifier with filtering. Transistors Q114 and Q115 form a differential amplifier

which campares the voltage at R115 with the voltage of

zener diode D110. The difference voltage is amplified

by transistor Q109 and fed to Darlington transistor

pair, Q106 and Q107, which series regulate the output

voltage.

amplifier which compares the voltage at R123 with respect to lo.

transistor 9113 and fed to Darlingtan transistor pair,

QllO and Qlll, which series regulate the -15 volt o”tput.

rent ‘CO about 200 milliamperes.

Transistors Q116 and 4117 form a differential

The difference voltage is amplified by

Transistors QlOS and 9112 limit the output cur-

b. C3.6 Volt Supply. The +3.6 volt supply taps ac

power from a secondary of transformer TlOl. Diodes

DlOl and D102 and capacitor Cl01 farm a full-wave rec-

tifier with filtering.

difference between the +3.6 volt output and a refer-

ence voltage derived from the +15 volt supply and de-

termined by resistors R103 and R104. The difference

voltage is amplified by transistor 9104 which drives a

Darlington transistor pair, QlOl and Q102. The Dar-

lington pair series regulates the +3.6 volt output.

Transi.stor 9103 limits the o”tp”t current to about 3

*lllp*i-6% .

c. +170 Volt Sup”ly. The t17OV supply taps ac power

from a secondary of transformer TlOl. Diode Dill and

ca”acitor Cl12 form a half-wave recitifier with filter-

Transistor 9119 amplifies the voltage developed

ini.

by the resistor divider R12S and R129. The output of

Q119 controls the w-3 regulator transist?r QllS to

maintain the +170 volt output. When the electrometer

is overloaded, and overload signal drives transistor

Ql20 which in turn controls the voltage at the base of

transistor QllV.

transistor Q120, and resistors R130, R131 and R132

reduces the +170 volt output to +SO volts when over-

loading occurs. Grounding the

off transistor Q120 causing diode D112 to conduct and

drive QllV. The reduced +SO volt o”tp”t causes blank-

ing on all Numerical Readout Tubes connected to the

+170 volt supply.

d. +210 Volt Output. The CZlO volt supply is an

unregulated voltage supply “sing the half-wave filtere,

voltage at diode Dill and capacitor C112.

e. t17 Volt Supply. The cl7 volt supply is an “n-

regulated voltage “sing the half-wave filtered voltage

at diode 0113 and capacitor C113.

Transistor QlO5 amplifies the

The circuit composed of diode D‘l12,

overload

input turns

1s

0971

Page 23

MODEZ 445

SERVICING

FIGURE 18.

Chassis, Top View.

Page 24

SERVICING

MODEL 445

20

FIGURE l.9.

PC Board Locations.

0971

Page 25

MODEL 445 DIGITAL PICOAMKETER

SERVICING

I

FIGURE 20.

+ TP (S&ape Trigger)

Component Layout, PC-20%

I

0171

FIGURE 21.

Component Layout, PC-208.

21

Page 26

SERVICING

MODEL 445 DIGITAL PIC@WMETER

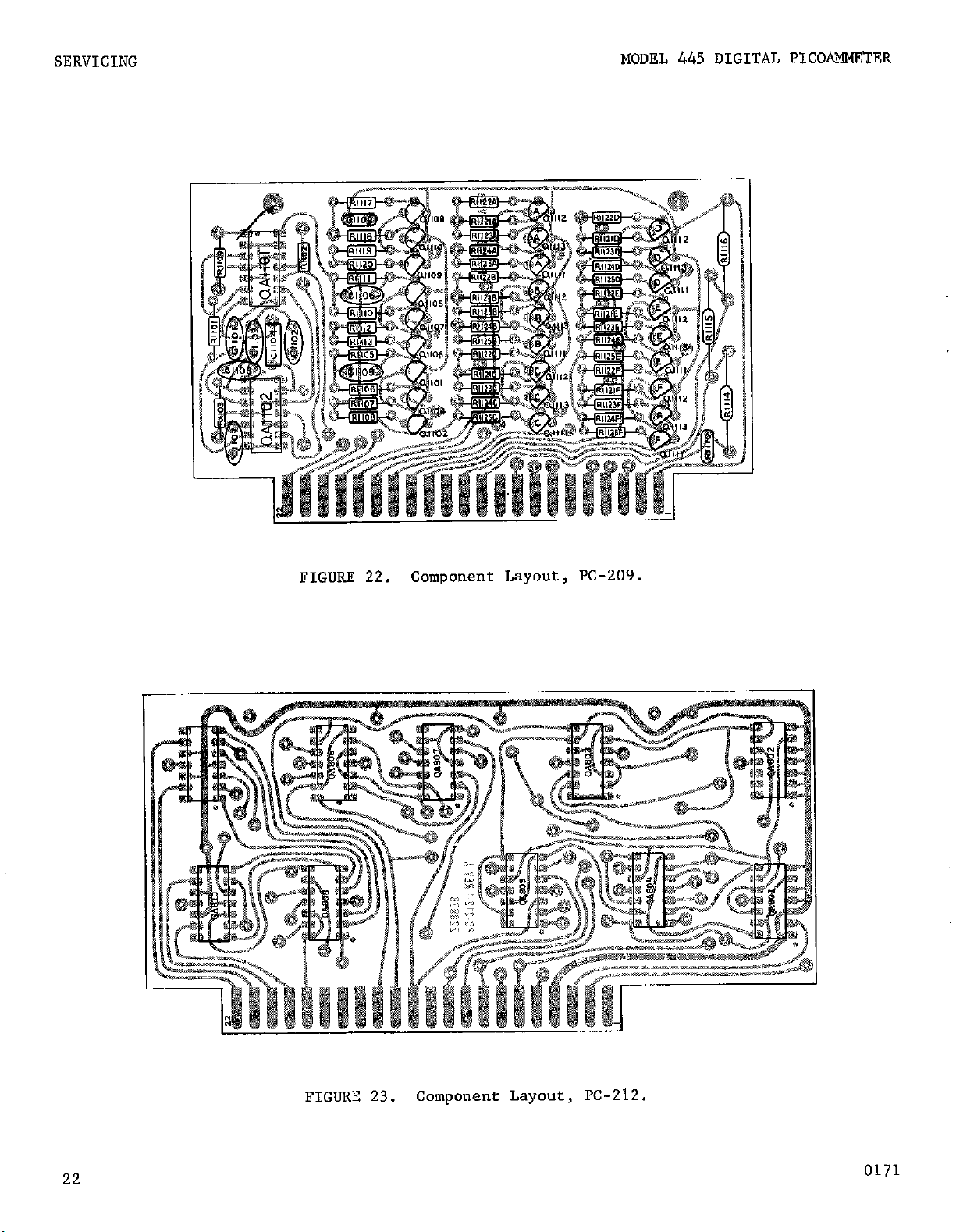

FIGURE 22.

component Layout, PC-209.

22

FIGURE 23.

component Layout, PC-212.

0171

Page 27

MODEL 445 DIGITAL PICOAMMETER

SERVICING

FIGURE 24. Component Layout, PC-214.

FIGURE 25.

0171 23

Component Layout, PC-217.

Page 28

SERVICING

MODEL 445 DIGITAL PICOAMMETER

FIGURE 26.

Component Layout, PC-218.

24

FIGURE 27.

component Layout, PC-219.

0171

Page 29

Page 30

MODEL 445 DIGITAL PICOAMMETER

SERVICING

FIGURE 29.

Component Layout, PC-229.

0171

FIGURE 30. Component Layout, PC-230.

27

Page 31

Page 32

MODEL 445 PICOAMMETER

REPLACEABLE PARTS

REPLACEABLE PARTS

4-l.

REPLACEABLE PARTS LIST.

SECTION 4.

This section contains

a list of components used in this instrument for "ser

reference. The Replaceable Parts List describes the

individual parts giving Circuit Designation, Description, Suggested Manufacturer (Code Number), Manufac-

Abbreviations and Symbols

TABLE 4-l.

A

ampere

F

Fig.

Cb"ar

cero

Cer Trimmer

COtlIP

DCb

oesig.

EAL

ETB

ETT

Carbon Variable

ceramic Disc

ceramic Trimmer

Composition

Deposited Carbon

Designation

Electrolytic, Aluminum

Electrolytic, tubular

Electrolytic, tantalum

CCb

k

I-I

M

Mfr.

MtF

MY

NO.

turer's Part Number, and the Keithley Part Number.

Also included is a Figure Reference Number where

applicable. The complete name and address of each

Manufacturer is listed in the CODE-TO-NAME Listing

following the parts list.

farad

n

ohm

Fig"t-e

pica (10-12)

Class enclosed Carbon

;c

Poly

Printed Circ"if

Polystyrene

kilo (10-3)

Ref. Reference

micro (104)

TC" Tinner Capperweld

leg

(106)

M**“f*Ct”PSr

" "Olt

Metal Film

l.fyl*r

Number

w

NW

WW"*r

watt

Wirewound

Wirewound Variable

4-i. ELECTRICAL SCHEMATICS AND DIAGRAMS. Schematics

and diagranls are included to describe the electrical

circuits as discussed in Section 3. Refer to Table

4-2 which identifies all schematic part numbers in-

cluded.

4-3. HOW TO "SE THE REPLACEABLE PARTS LIST. This

Parts List is arranged such that ehe individual types

of components are listed in alphabetical order. The

parts far the i"str"ment's Main Chassis are listed

folrzed by printed circuit boards and other sub-

assemblies.

4-4. HOW TO ORDER PARTS.

a. Replaceable parts may be ordered through the

TABLE 4-2.

CirC"it Description

Main Chassis

power supply

Polarity Board

Thousand Board

Readout Board

Oscillator Board

Integrator Board

Range Control Board

Range Counter/Decoder

Tube & Driver Board

Output Buffer

output Buffer

Sales Service Department, Keithley Instruments, Inc.

or your nearest Keithley representative.

b. When ordering parts, include the following in-

formation.

1. Instrument Model Number.

2. Instrument Serial Number.

3. Part Description.

4. Schematic Circ"it Designation.

5. Keithley Part Number.

C. All parts listed are maintained in Keiehley

spare parts Stock.

Any part not listed can be made

akilable upon request; -Parts identified by the

Keithley Manufacturing Code Number 80164 should be

ordered directly from Keithley Instruments, Inc.

Schematic Pare No

PC-221

234883

PC-221 234483

PC-207

PC-208

PC-229

234490

234501)

23451E

PC-217 234520

PC-219 234533

PC-214 23454E

PC-212 234553

PC-230

23456D

PC-218 234570

PC-209

234813

0971

29

Page 33

REPLACEABLE PARTS

MODEL 445

r

Series

100

200

300

400

500

600

700

800

900

1000

1100

1200

PC Board Designation Series

Description

Power Supply

Polarity

Board

Thousand Board

Readout Board

08cillator Board

Integrator Board

Range Control Board

Range Counter/Decoder

Tube & Driver Board

Output Buffer Board

Output Buffer Board

MEIF" Chsssis

TABLE 4-3.

Designation Connector

PC-221

PC-207

PC-208

PC-229

PC-217

PC-219

PC-214

PC-212

PC-230

PC-218

PC-209

51204

51205

J1206/51207 41

J1208

51209

51212

51211

51210

.J1216

51202

PC-221

Page No.

37

39

40

i:

46

46

47

i,"

33

30

0971

Page 34

MODEL 445 DIGITAL PICOAMMRTER

REPLACEABLE PARTS

TABLE 4-4.

Mechanical Parts Lisa.

Item No.

1

2

Description

Top Cover Assembly

Cover

Fastener

Bottom Cover’ Assembly

Cover

Fastener

Angle, Rack Assembly

Screw,

Slotted, 10 - 32

Front Panel

Chassis

x l/4

Quantity Per Assembly

Keithley Part No.

17958C

17162C

FA-54

17960C

17957c

FA-54

146248

23000C

230038

0171

FIGURE 31. Mechanical Assembly.

31

Page 35

s (I

j

Page 36

MAIN CHASSIS PARTS LIST

(“1200” Series, E-221)

CAP.4CITORS

REPLACEABLE PARTS

Circuit

msig. Value Rating

Cl201

Cl202 10 @ 20 v

Cl203 10 p 20 "

Cl204 ,004, fl 600 "

Cl205 .047 NF 200 "

Cl206 ,022 fl 400 "

Cl207 .022 p 400 v

Cl208

Cl209 1000 pP 500 v

Cl210 390 pF 500 v

Cl211 .033 p!s 600 "

Cl212 150 pF 500 "

Cl213 3600 pF 500 "

Cl214 22 PF 500 "

Cl215 10 PF 500 "

CU.16 .Ol pF 600 "

Circuit

msig.

.l1201**

5 pF 60" "

.Ol @

600 "

DWXiptiO”

Plug-in contacts

Mfr. Mfr.

TYPe

CerD 72982 ED-5 C22-5P 28

ETT 17554 TSDZ-20-106 C179-10M 28

ETT 17554 TSDZ-20-106 C179-10M 28

CerD 72982 ED-.047 C22-.0047M 28

MY 13050

MY 1305D SMlA C73-.022&l 28

MY 13050

cerD 72982 ED-.01 C22-.OlM 28

POlY 71590 CPR-1000J C138-1OOOP 28

POlY 71590 CPR-3903 C138-39OP 28

MY

Poly 71590 cm-15OJ C138-15OP 28

Poly 71590 CPR-3600J Cl38-3600P '28

POlY 71590

Poly 71590 cm-1O.T C138-IOP 28

cem 72982 m-.01 c22-.OIM 28

CONNECTORS

Code

56289 CPS-550 C62-.033M 28

Mfr.

Part NO. Part NO.

SMlA

SW.4

CPR-22J

Mfr.

Code Part NO.

80164

Keithley

C143-.047M 28

C73-.022M 28

C138-22P 28

Keithley

Part NO.

Fig.

Ref.

see FET Lnput

Fig.

Ref.

28

Card

PI201

51202

51203

.I1204

51205

J1206

51207

51208

51209

Printed circuit contacts, mate

of n201

Receptacle, 44 pins, Rear Card

of 0”tput Buffer Stage PC-209

Not Used

Receptacle, 15

Board PC-207

pins, Polarity

Receptacle, 15 pins, Thousand

Board PC-208

Receptacle, 6

Board PC-229

Receptacle, 15

Board PC-229

pins, Readoue

pins, Readout

91662 02-005-113-6-200

09922

09922

09922

73690 02-006-105-6-200

73690 02-015-105-6-200

09922

09922

09922

09922

PSC 4DD22-12

PSC 45515-12

PSC 4SS15-12

PSC 4SS15-12

PSC 4SS15-12

PSC 4ss**-12

PSC 4SS22-12

m-199

CS-205

cs-175 28

cs-175 28

CS-223 28

CS-222 28

cs-175 28

cs-175 28

CS-182 28

cs-182 28

28

28

0971

33

Page 37

REPLACEABLE PARTS

MODEL 445 DIGITAL PICOAMMETER

MAIN CHASSIS (Cont'd)

CONNECTORS (Cont'd.)

Gil-C"it.

rlesig.

51212

51213

---

51214

__-

51215

51216

51217

---

51218

__-

P1202

Description

Receptacle, 22 pins, Range

Mfr.

Mfr.

code Part NO.

09922 PSC 4SS22-12 CS-182

Keithley

Part No.

Control Board PC-214

Receptacle, triaxie1, INPUT

95712

Plug, triaxisl, mate of 51213 95712

Receptacle, 50 pins, PRINTER/

02660

33050-2-m-34

30197-l

CS-181

m-141

57-40500-1 CS-221

CONTROL Connector

'Plug, mate of J1214

02660

57-30500-l CS-220

Binding Post, LO 58474 DF21BC BP-11B

Receptacle, 44 pins, Front

09922 PSC 4DD22-12 CS-205

Card of Output Buffer Stage, PC-21Q

Binding Post, GND 58474 DFZlGC BP-116

Shorting Link for LO & GND Posts 24655 938-L BP-6

Receptacle, Microphone, ANALOG

02660

SO-PCZF CS-32

OUTPUT

Plug, mate of 51218 (Supplied) 02660 SO-MCZM CS-33

1 pin connector, mete to .I501

80164

CS-185 lx-185

FFg.

Ref.

28

3

3

3

28

Circuit

Des&.

TYPe

Mfr. Mfr.

Cade

Part No. PaIT NO. Ref.

Keithley Fig.

L!lZOl Silicon 01295 lN64.5 RF-14 28

D1202 Silicon 01295 lN645 RF-14 28

D1203 Silicon 01295 lN645 RF-14 28

~1204 Silicon 01295 1~645 RF-14 28

01205 SilkOIl 01295

D1206

D1207

D1208

~1209

01210

DlZll Silicon

D1212

01213 Silicon

D1214

01215 Silicon

D1216 SiliClXl

01217 SiliCOl?

Dl218 Silicon

Silicon 01295

SFliCOlI

Silicon

Silicon

Silicon

01295

01295

01295

01295

02735

Silicon

02735

02735

zener

84970 VR47

01295 113645

01295

02735

02735

1~645

lN645

18645

lN914

lA645

lN3255

lN3255

1133255

1~645

lN3255

IN3255

RF-14 28

RF-14

28

RF-14 28

RF-14

RF-28

RF-14

RF-17

RF-17

RF-17

DZ-30

RF-14

RF-14

RF-17

RF-17

28

28

28

28

28

28

28

28

28

28

28

LAMPS

circuit

Desig.

DS1201

Description

Range Changing Pilot Light,

Mfr. Mfr.

Code Part No. Part NO. Ref.

91802 2100 series

Keithley

PL-46

Fig.

2

34

Page 38

MODEL 445

REPLACEABLE PARTS

MAIN CHASSIS (Cont’d)

RELAYS

~1201(A

K1202 (1

8. B) Reed

K1203 ‘1

K1204 PI

K1205 ”

K1206

”

K1207 ta

K12OS ”

circuit

oesig.

23430B

PC-207

Mfr.

Cade

Relay

Reed Relay

Reed Relay

Reed Relay

Reed Relay

Reed Relay

Reed Relay

Reed Relay

27682

27682

27682

27682

27682

27682 525-0002

27682

27682

PRINTED CIRCUIT SUB-ASSSMBLIES

Description

Input FET P.C. Board, with components.

Polarity P.C. Board, with componenes.

less components.

Mfr.

Part No.

525-0002

525-0002

525-0002

525-0002

525-0002

525-0002

525-0002

Eceithley

Part No.

RL-34

RL-34

RL-34

RL-34

RL-34

RL-34

RL-34

RL-34

Fig.

Ref.

28

2s

28

2s

28

28

28

28

lceithley

Part NO.

23730B

PC-207

22875B

PC-208

PC-209

PC-212

PC-214

PC-217

PC-218

PC-219

PC-229

PC-230

Thousand P.C. Board, with ccqmnents.

Output Suffer P.C. Board, Model 4401, vith components.

less components.

Range Counter/Decoder P.C. Board, with components.

less companencs.

Range Control P.C. Board, with components.

less components.

Oscillator P.C. Board, with components.

less components.

Output Buffer P.C. Board, Model 4401, with components.

leas components.

Integrator P.C. Board, with com,,one”ts.

less componenes.

Readout P.C. Board, with coqmnents.

less components.

Tube & Driver P.C. Board, with components.

less camponents.

PC-208

2287SB

Iv-209

228828

PC-212

22892B

PC-214

22895B

PC-217

230618

PC-218

23065B

PC-219

230bSB

PC-229

23628C

PC-230

23633B

0971

35

Page 39

REPLACEABLE PARTS

MAIN CHASSIS (Cont'd)

RESWI'ORS

MODEL

445 DIGITAL PICOAMMETER

R1201

R1202

R1203**

R1204

R1205

R1206

R1207

R1208

R1209

R1210

R1211

R1212

R1213

R1214

R1215

R1216

R1217

R121S

R1219

R1220

R1221

R1222

R1223

R1224

R1225

Value

10 MO

10 kn

100 kR

15 kn

100 n

18.2 ki,

500 n

18.2 kn

22 kn

4.7 kn

4.7 kfl

680 0

3.3 k0

100 n

470 n

100 R

116.67 il

4.75 kR

1.1667 kfl

11.667 ki7

115

k0

1.15 Mn

10 Mn

1.5 Mn

100 Mil

Rating

l%, l/2 W

20%, 2 w

lO%, l/4 w

l%, l/0 W

lO%, l/2 w

l%, l/8 w

?20%, 2 w

1%.

1/a w

lO%, l/4 w

lO%, l/4 w

lO%, l/4 w

lO%, l/4 w

lo%, l/2 w

lO%, 2 w

lO%, 2 w

lO%, l/2 w

O.l%, 1 "

l%, l/2 w

O.l%, 1 w

O.l%, 1 w

l%, l/2 w

l%, l/2 w

l%, l/2 w

l%, l/2 w

l%, 2 w

Mfr.

Type

DCb

Code

91637

WWVtW 71450

camp

MfF

camp

MW

Cermet

MtF

camp

07716

01121

07716

71450

07716

44655

COl"p 44655

camp

COIBP

COlllp

COtlIP

CO¶V

COtlIP

ww

MU

WI?

ww

MtF

Mm

DCb

DCb

DCb

44655

44655

01121

01121

01121

01121

01686

07716

01686

01686

07716

07716

91637

91637

91637

Mfr.

PBrt No.

DCF-l/2

INS 115

CEA

EB

CEA

551

CEA

RC07

RC07

RC07

RC07

EB

HB

HB

EB

7040

CEC

7040

7040

CEC

CEC

DCF-l/2

DCF-l/2

DC-2

Keithley

Part No.

RlZ-10M

RPSO-1OK

R88-15K

Rl-100

R88-18.2K

RP72-500

R88-18.2K

R76-22K

R76-4.7K

R76-4.7K

R76-680

Rl-3.3K

R3-100

R3-470

Rl-100

R70-116.67

R94-4.75K

R70-1.1667K

R70-11.667K

R94-115K

R94-1.15M

RlZ-10M

RlZ-1.5M

R14-100M

Fig.

Ref.

28

28

28

28

28

28

28

28

28

28

28

28

2s

28

28

28

28

28

28

28

2s

28

2s

28

R1226

R1227

R1228

R1229

R1230

R1231

R1232

R1233

R1234

R1235

R1236

R1237

R1238

circuit

Desig.

s1201

-_-

51202

S1203

S1204

15 lm

109 n

4.75 kR

250 kfi

5 kO

50 kfl

500 kfl

560 0

1 k0

1 kn

249 kiZ

500 kfl

1 kR

l%, 1 w

+3-O%, l/R W

l%, l/2 w

?20%, 2 w

20%, 2 w

220%, 2 w

*20%, l/4 w

10%. l/2 W

20%, 2 w

20%, 2 w

lO%, 112 W

120%, 114 w

20%, 2 w

DeSCriptiO"

Rotary Switch, FILTER

Knob Assembly, Filter Switch

Toggle Switch, RANGE 10-2/DOWN

Toggle Switch, RANGE HOLD/AUTOMATIC

Toggle Switch, ZERO cHEcK/OPmATE

DCb

GCb

MtF

C~~llWt

wvar

91637

80164

07716

71450

71450

CetXEt 71450

CbVar

COIl?p

71450

0,1121

WW"X 71450

WWVU

MtF

CbVar

wwvar

SWITCHES AND CONTROLS

71450

07716

71450

71450

DC-1

230928

CEC

550

INS 115

550

Type-45

EB

INS 115