Page 1

SCHEMATIC DIAGRAMS

INTEGRATED DIGITAL TERRESTRIAL/SATELLITE LCD TELEVISION

LT-32HB1BU/AX

DVD-ROM No.SML2009Q1

COPYRIGHT © 2009 Victor Company of Japan, Limited.

No.YA705<Rev.001>

2009/7

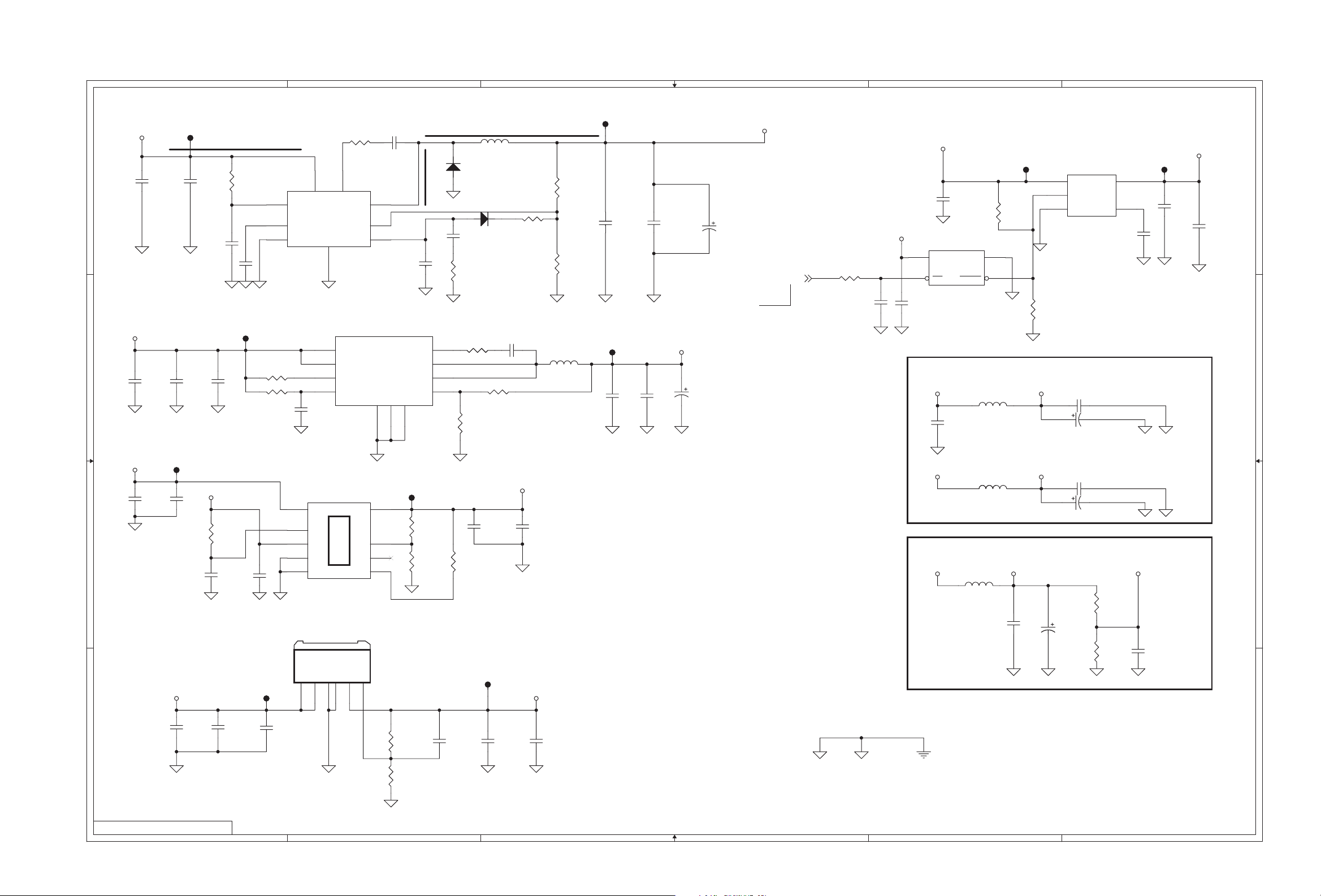

Page 2

LT-32HB1BU

/AX

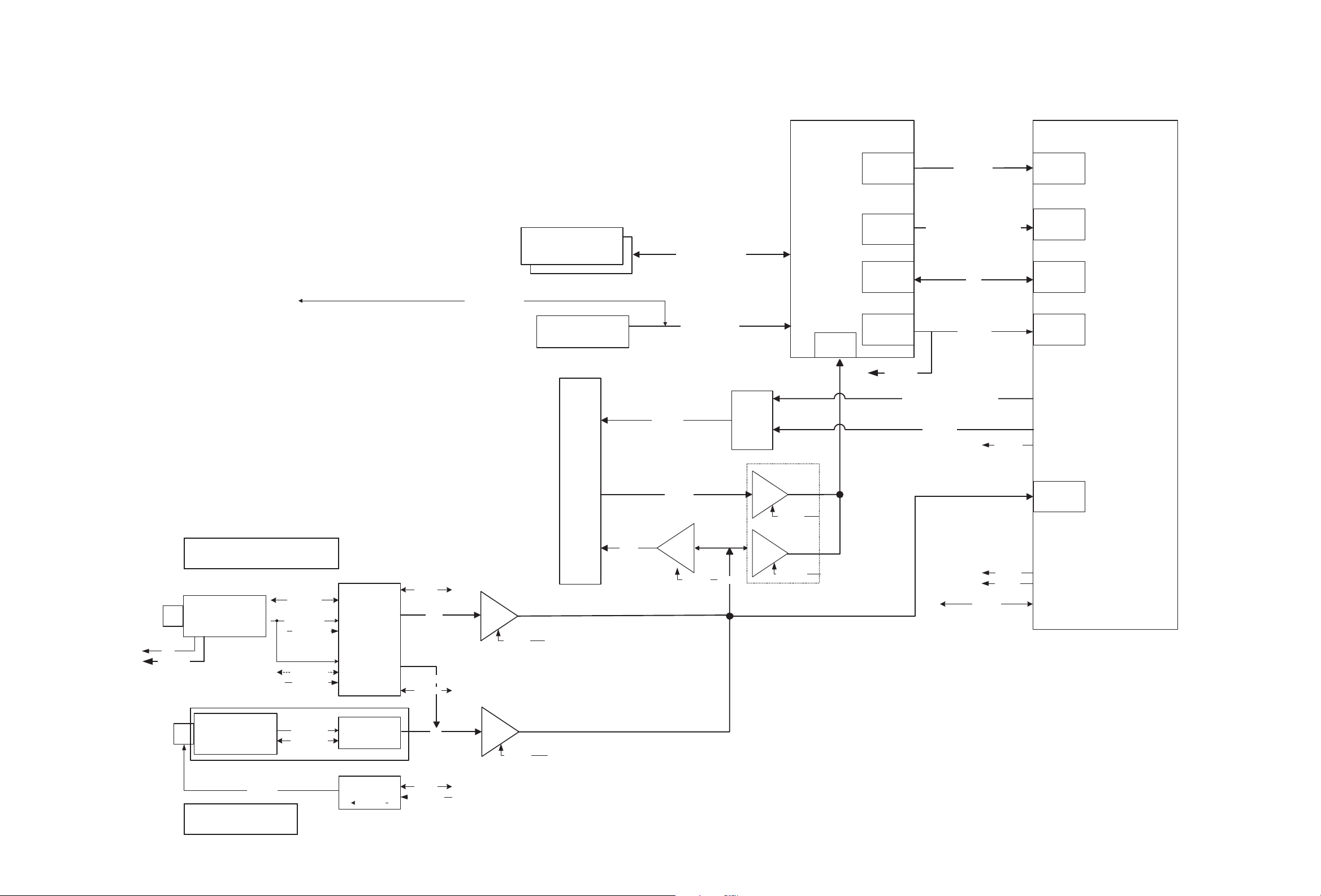

STANDARD CIRCUIT DIAGRAM

NOTE ON USING CIRCUIT DIAGRAMS

1.SAFETY

The components identified by the symbol and shading are

critical for safety. For continued safety replace safety ciritical

components only with manufactures recommended parts.

2.SPECIFIED VOLTAGE AND WAVEFORM VALUES

The voltage and waveform values have been measured under the

following conditions.

(1)Input signal : Colour bar signal

(2)Setting positions of

each knob/button and

variable resistor

(3)Internal resistance of tester

(4)Oscilloscope sweeping time

(5)Voltage values

Since the voltage values of signal circuit vary to some extent

according to adjustments, use them as reference values.

: Original setting position

when shipped

: DC 20kΩ/V

: H

: V

: Othters

: All DC voltage values

20µs / div

5ms / div

Sweeping time is

specified

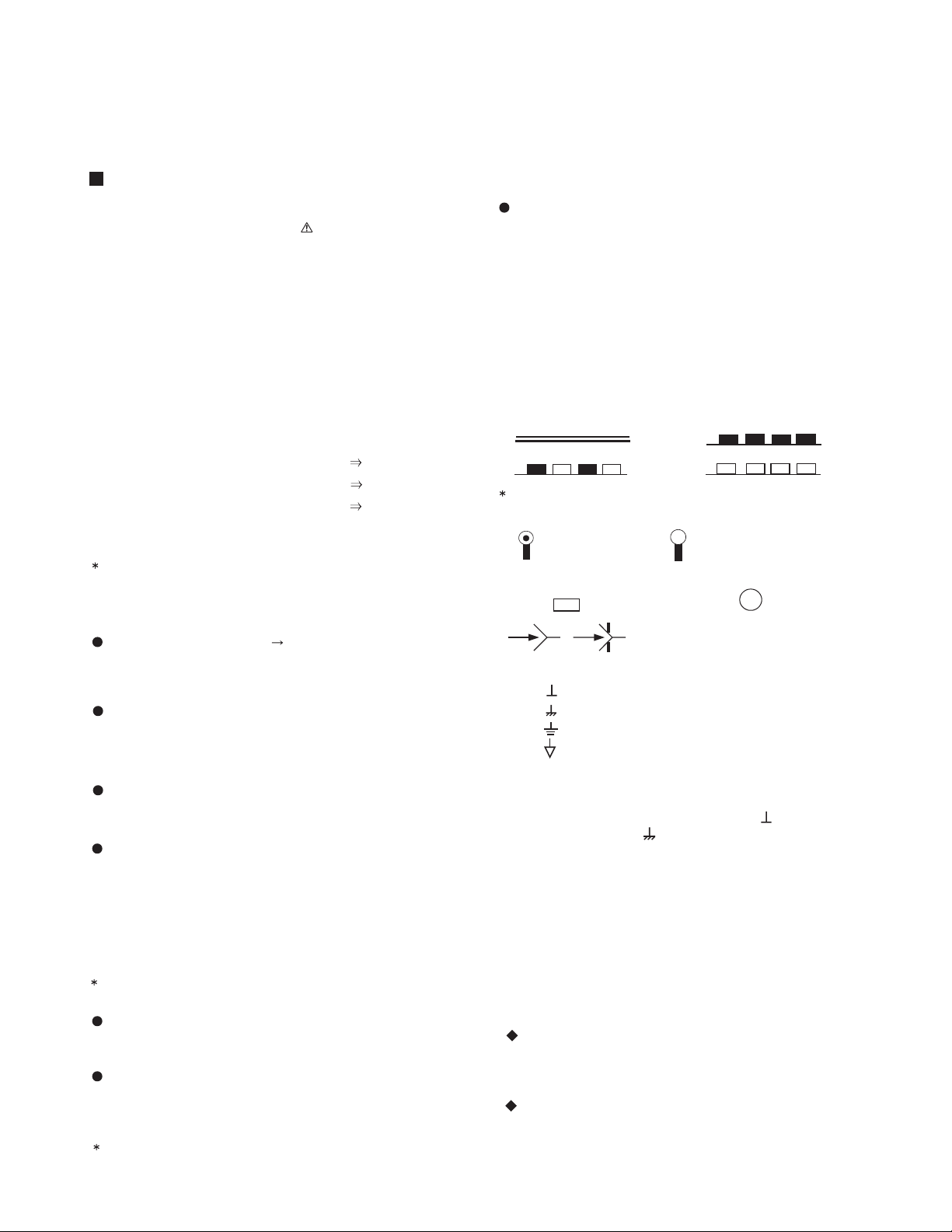

3.INDICATION OF PARTS SYMBOL [EXAMPLE]

In the PW board

: R1209

R209

Type

No indication

MM

PP

MPP

MF

TF

BP

TAN

(3)Coils

No unit

Others

(4)Power Supply

Respective voltage values are indicated

(5)Test point

: Test point

(6)Connecting method

: Ceramic capacitor

: Metalized mylar capacitor

: Polypropylene capacitor

: Metalized polypropylene capacitor

: Metalized film capacitor

: Thin film capacitor

: Bipolar electrolytic capacitor

: Tantalum capacitor

: [µH]

: As specified

: B1

: 9V

: Connector

: Receptacle

: Only test point display

: Wrapping or soldering

: B2 (12V

: 5V

)

4.INDICATIONS ON THE CIRCUIT DIAGRAM

(1)Resistors

Resistance value

No unit : [Ω]

K

M

Rated allowable power

No indication : 1/16 [W]

Others : As specified

Type

No indication

OMR

MFR

MPR

UNFR

FR

Composition resistor 1/2 [W] is specified as 1/2S or Comp.

(2)Capacitors

Capacitance value

1 or higher : [pF]

less than 1

Withstand voltage

No indication : DC50[V]

Others : DC withstand voltage [V]

AC indicated

Electrolytic Capacitors

47/50[Example]: Capacitance value [µF]/withstand voltage[V]

: [kΩ]

: [MΩ]

: Carbon resistor

: Oxide metal film resistor

: Metal film resistor

: Metal plate resistor

: Uninflammable resistor

: Fusible resistor

: [µF]

: AC withstand voltage [V]

(7)Ground symbol

: LIVE side ground

: ISOLATED(NEUTRAL) side ground

: EARTH ground

: DIGITAL ground

5.NOTE FOR REPAIRING SERVICE

This model's power circuit is partly different in the GND. The

difference of the GND is shown by the LIVE : ( ) side GND and the

ISOLATED(NEUTRAL) : ( ) side GND. Therefore, care must be

taken for the following points.

(1)Do not touch the LIVE side GND or the LIVE side GND and the

ISOLATED(NEUTRAL) side GND simultaneously. if the above

caution is not respected, an electric shock may be caused.

Therefore, make sure that the power cord is surely removed from

the receptacle when, for example, the chassis is pulled out.

(2)Do not short between the LIVE side GND and ISOLATED(NEUTRAL

side GND or never measure with a measuring apparatus measure

with a measuring apparatus ( oscilloscope, etc.) the LIVE side GND

and ISOLATED(NEUTRAL) side GND at the same time.

If the above precaution is not respected, a fuse or any parts will be broken.

Since the circuit diagram is a standard one, the circuit and

circuit constants may be subject to change for improvement

without any notice.

NOTE

Due improvement in performance, some part numbers show

in the circuit diagram may not agree with those indicated in

the part list.

When ordering parts, please use the numbers that appear

in the Parts List.

)

(No.YA705<Rev.001>)2-1

Page 3

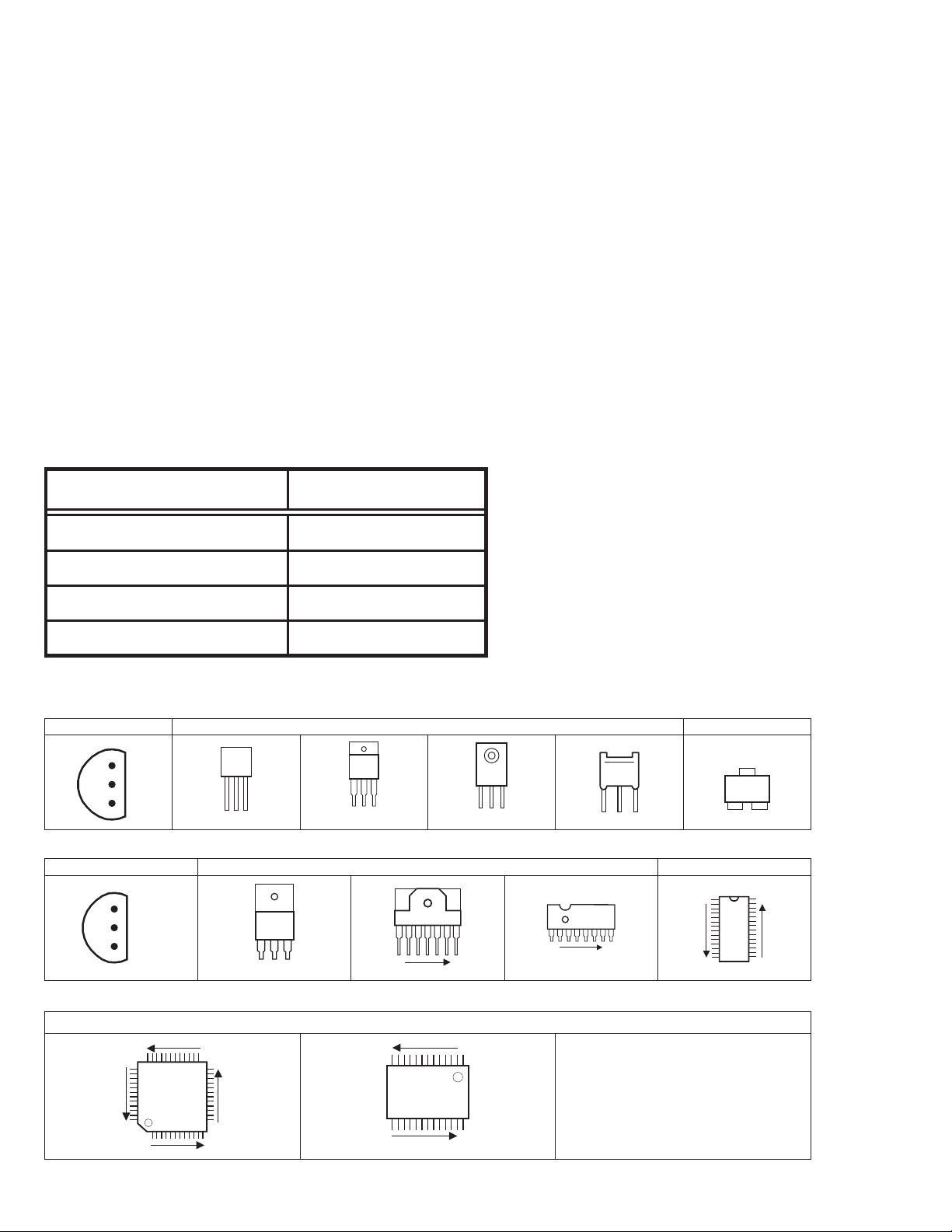

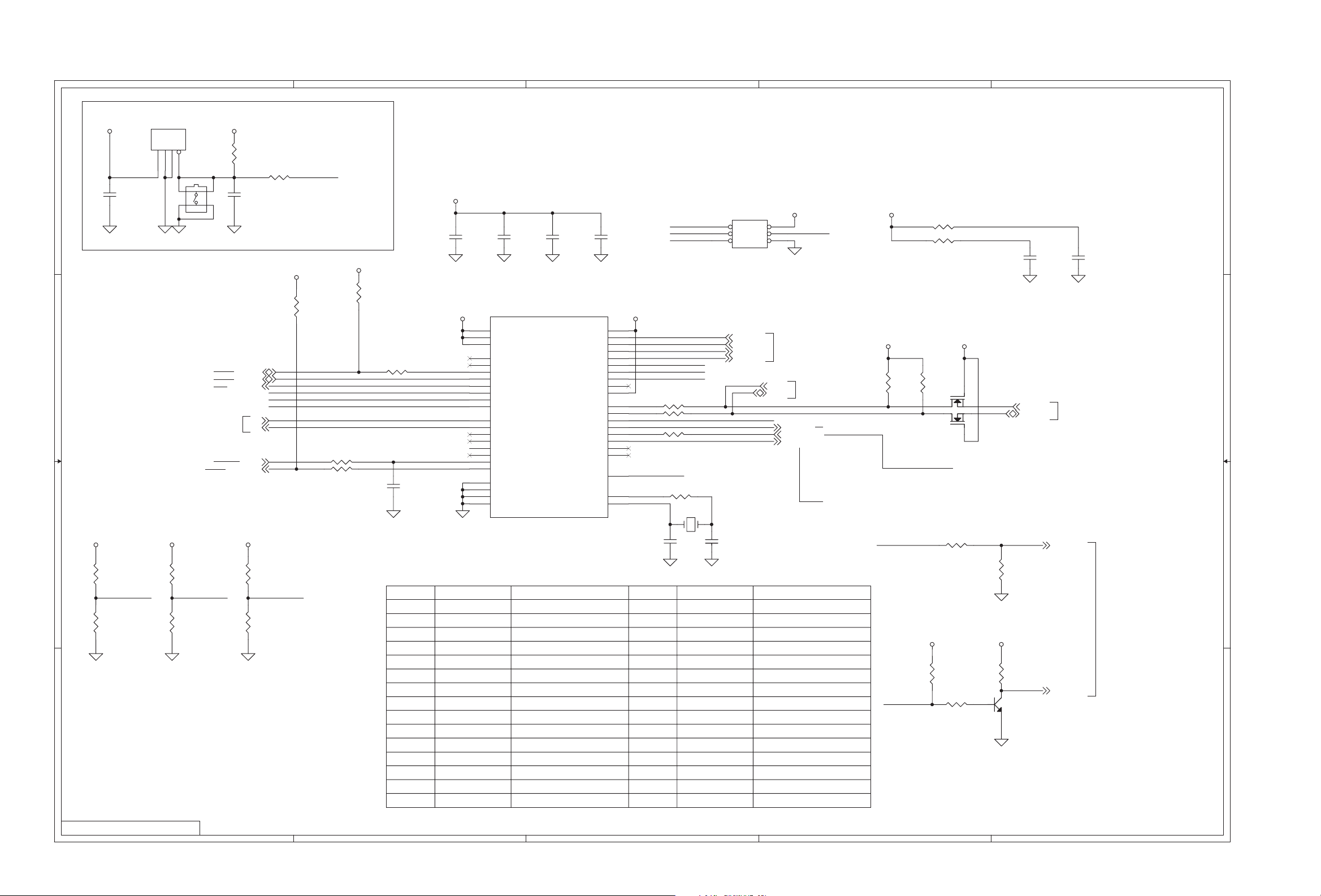

CONTENTS

SEMICONDUCTOR SHAPES ......................................................................2-2

WIRING DIAGRAM .......................................................................................2-3

BLOCK DIAGRAM ........................................................................................2-5

BLOCK DIAGRAM [MPEG4 BLOCK].........................................................2-7

CIRCUIT DIAGRAMS ...................................................................................2-9

MAIN PWB CIRCUIT DIAGRAM ................................................................................................................. 2-9

IR PWB CIRCUIT DIAGRAM .................................................................................................................. 2-101

KEY PWB CIRCUIT DIAGRAM............................................................................................................... 2-103

LED PWB CIRCUIT DIAGRAM............................................................................................................... 2-105

PATTERN DIAGRAMS ............................................................................ 2-107

MAIN PWB P ATTERN ............................................................................................................................ 2-107

IR PWB P ATTERN.................................................................................................................................. 2-111

KEY PWB P ATTERN .............................................................................................................................. 2-111

LED PWB P ATTERN .............................................................................................................................. 2-111

USING P.W. BOARD

P.W.B ASS㵭Y name LT-32HB1BU/AX

MAIN P.W. BOARD

IR P.W. BOARD

KEY P.W. BOARD

LED P.W. BOARD

HU-71100006

HU-72200004

HU-72200003

HU-72200017

SEMICONDUCTOR SHAPES

TRANSISTOR

BOTTOM VIEW FRONT VIEW TOP VIEW

CHIP TR

E

C

B

ECB

IC

BOTTOM VIEW FRONT VIEW TOP VIEW

OUT

E

IN

IN OUTE

B

(G)E(S)C(D)

1 N

ECB

ECB

1

1 N

C

BE

N

CHIP IC

N

1

2-2(No.YA705<Rev.001>)

TOP VIEW

1

N

Page 4

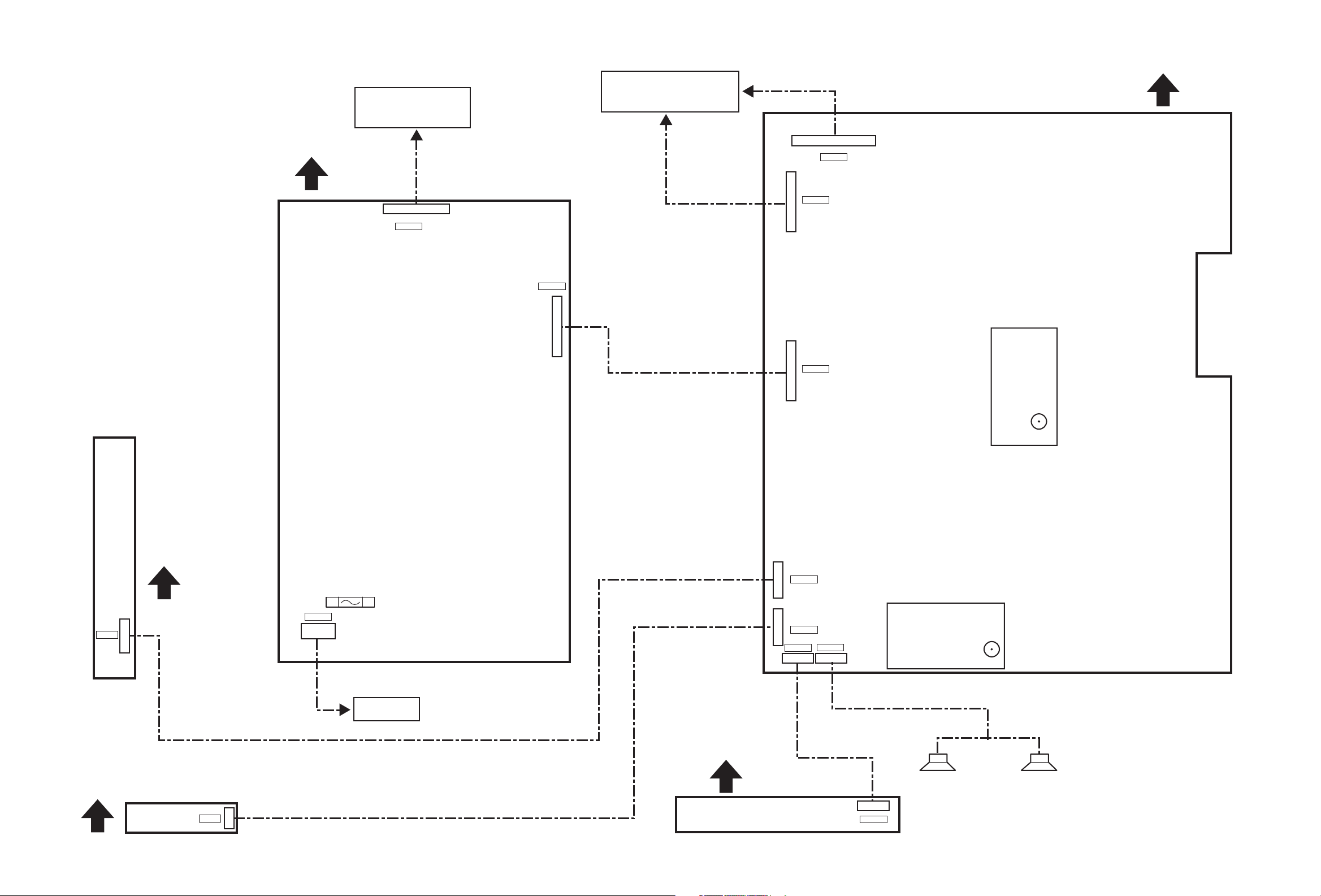

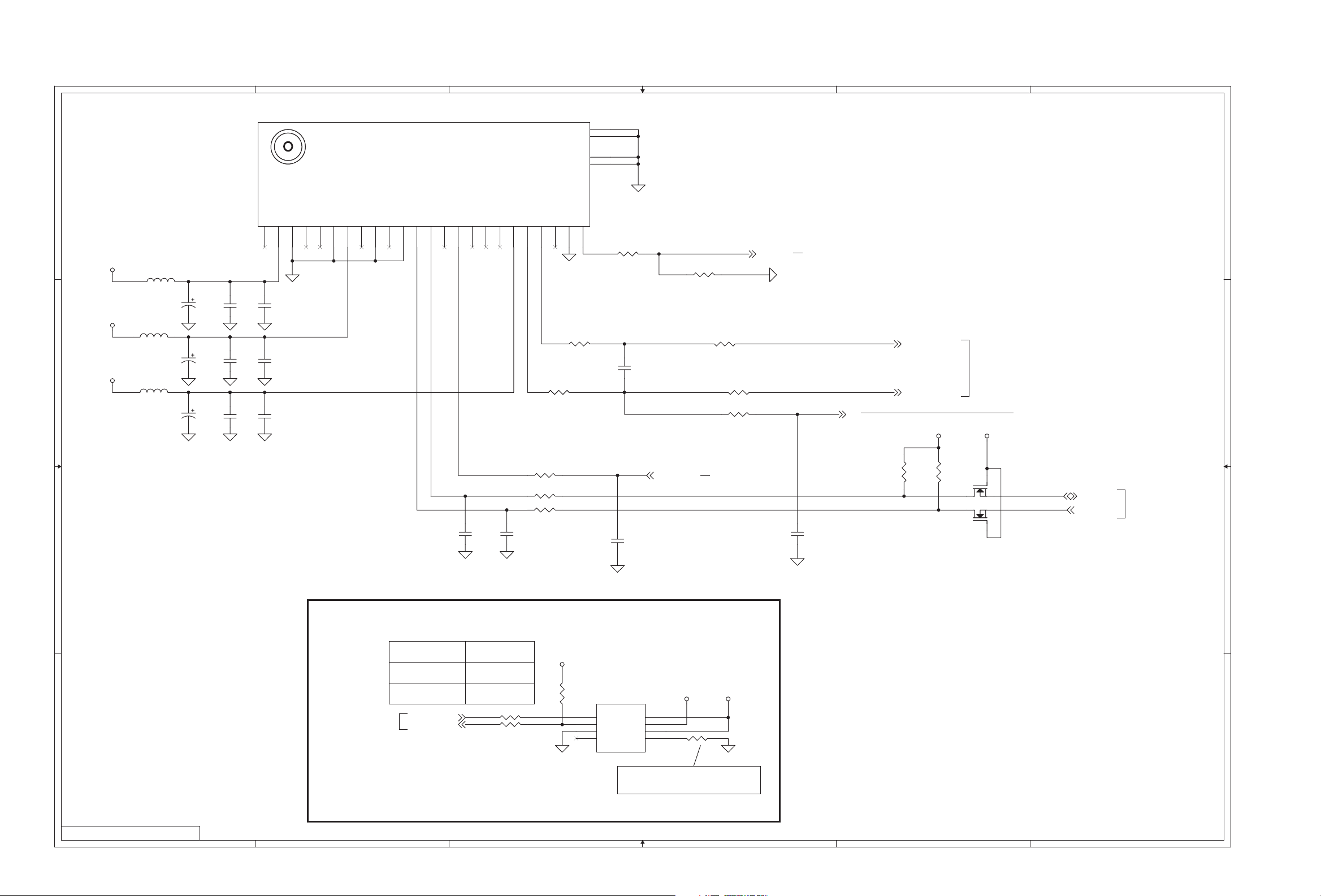

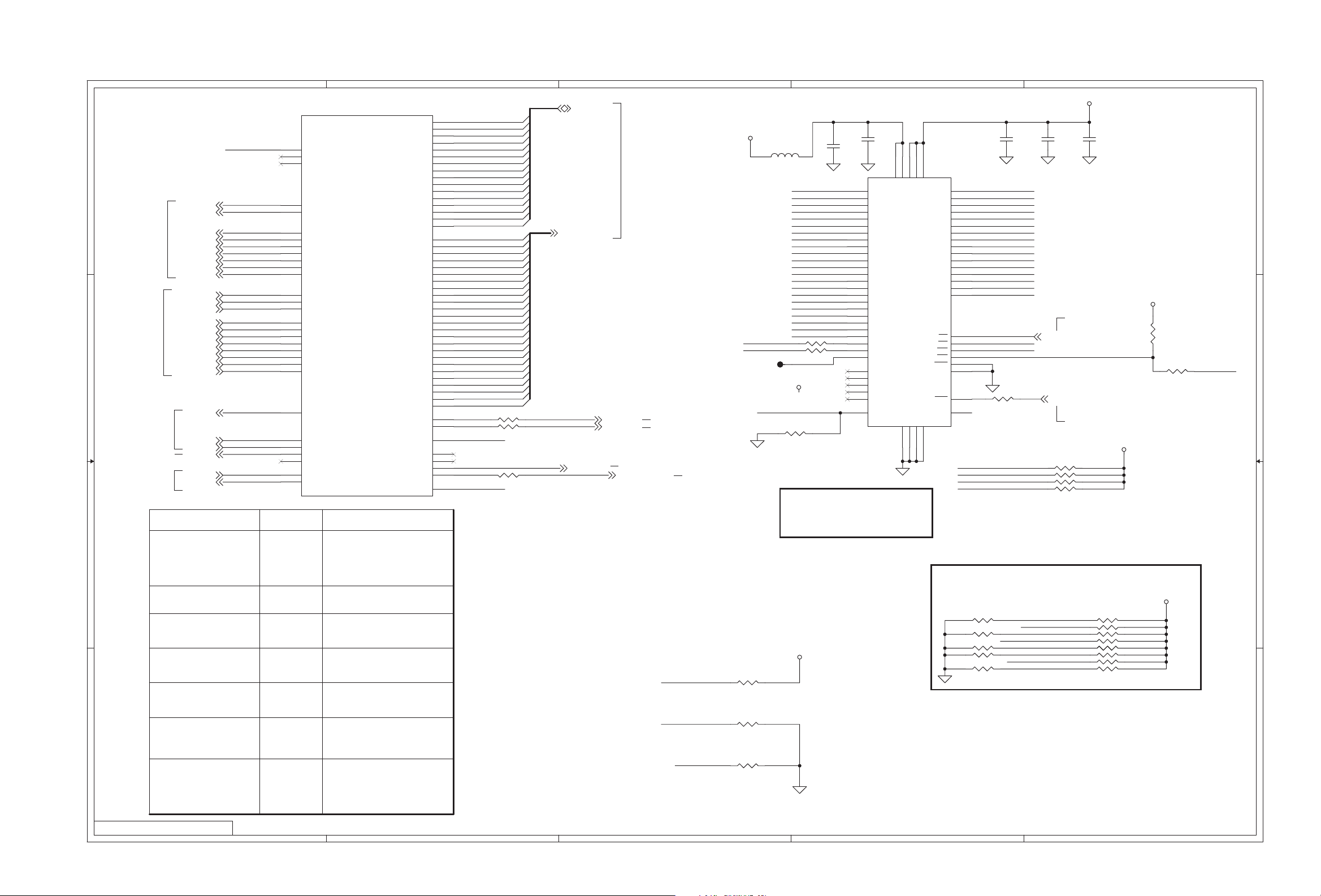

WIRING DIAGRAM

LCD PANEL UNIT

[INVERTER PWB]

LCD PANEL UNIT

[LCD CONTROL PWB]

TOP

KEY PWB

TOP

41

JP641

31

15

CN3

1

CN1

24

1

JP642

1

1

JP1

24

1

DIGITAL TUNER

(SATELLITE)

JP2

TOP

TOP

5

1

IR PWB

JP1

5

F1

250V/6.3A

CN2

N

L

POWER UNIT

AC INLET

FRONT

1

6

LED PWB

JP2

1

6

JP3

1

4

JP4

JP761

1

DIGITAL TUNER

(TERRESTRIAL)

MAIN PWB

SPEAKER(R)SPEAKER(L)

1

5

JP3

2-4(No.YA705<Rev.001>)(No.YA705<Rev.001>)2-3

Page 5

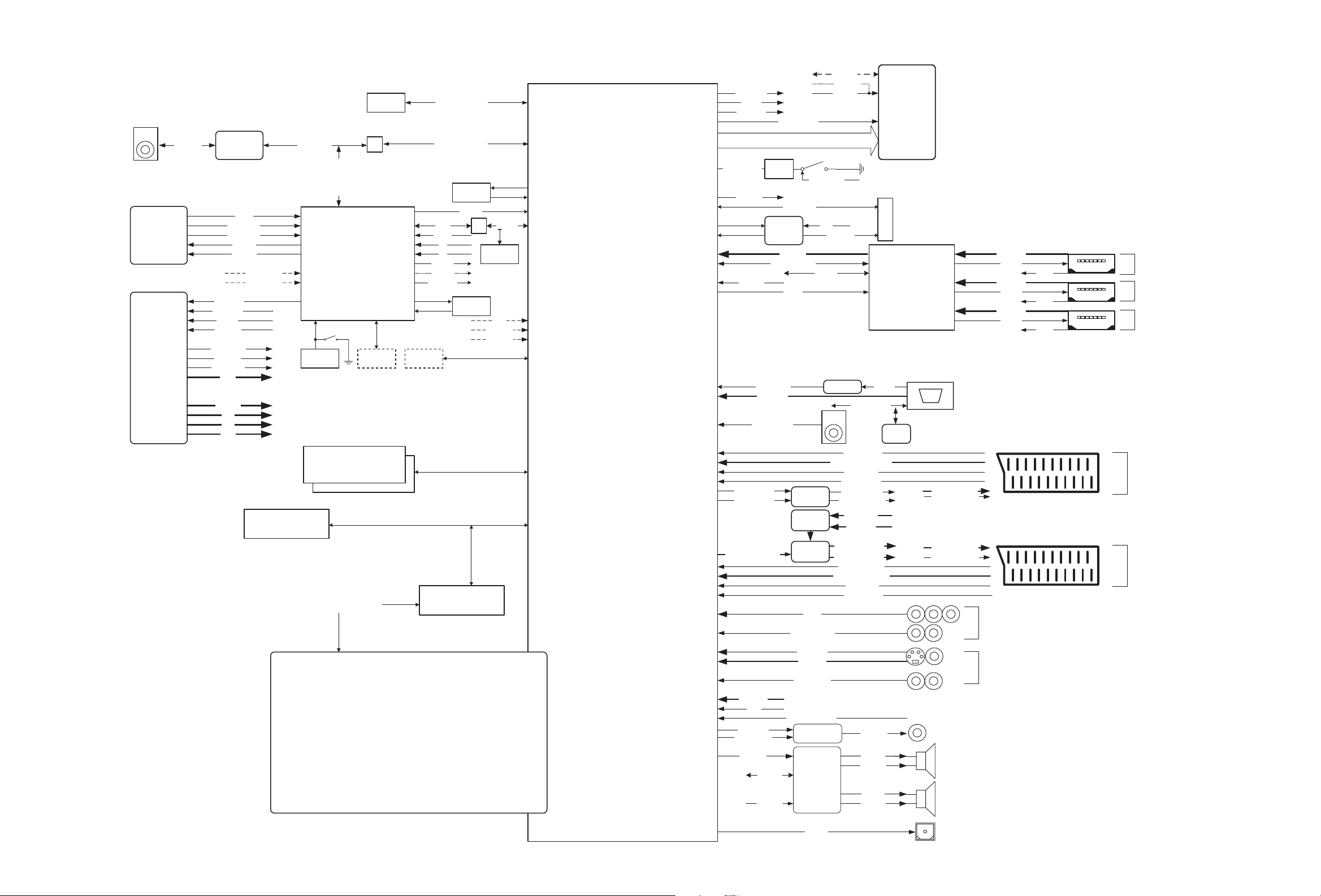

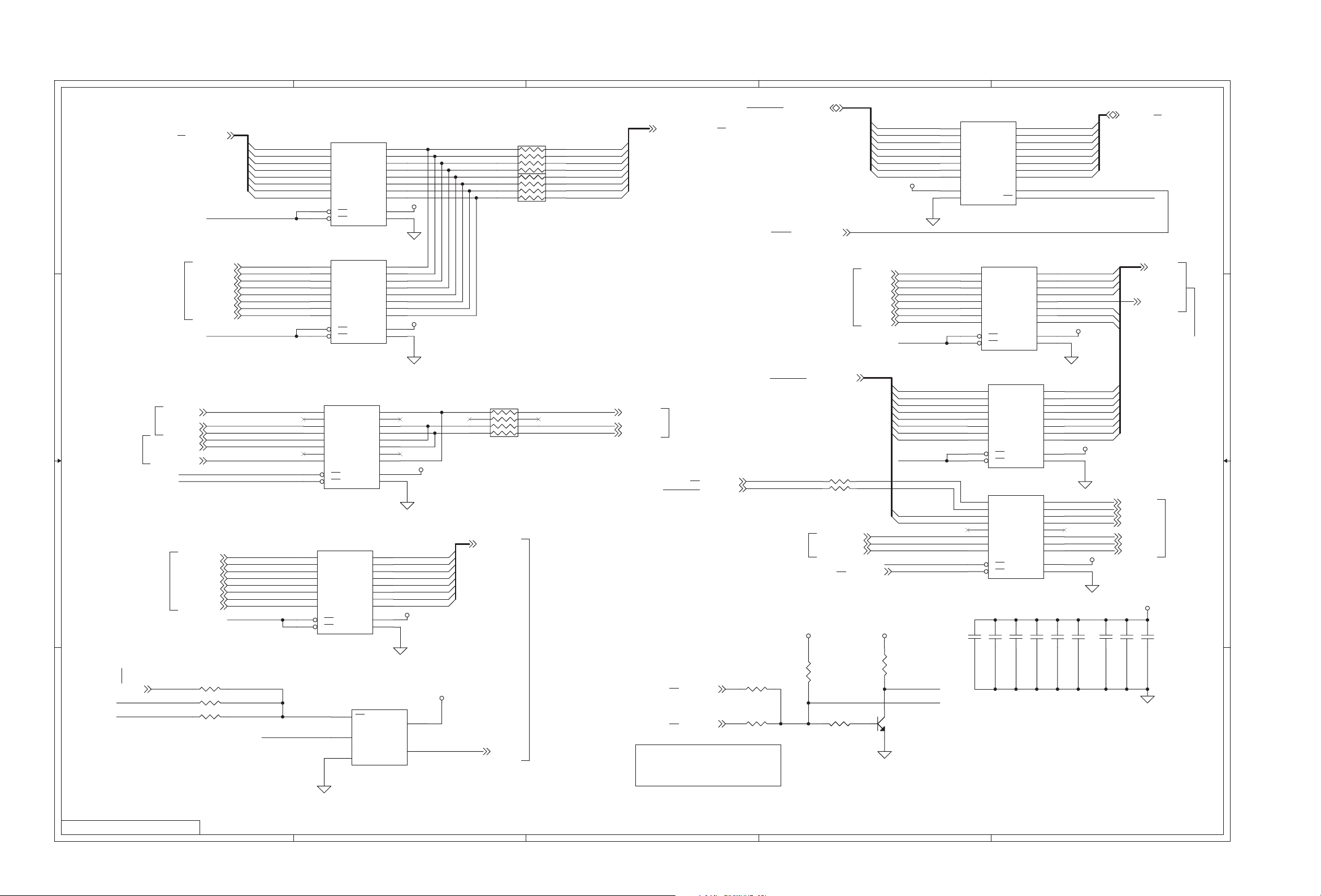

BLOCK DIAGRAM

SERVICE PORT

PC

RS232

KEY PWB

&

LED PWB

POWER UNIT

TXD/RXD

U831

ILX232

KEY_ADC1

KEY_ADC2

PWR_STB

PWM_DIM

A_DIM

BKLT_EN

P_PWM_DIM

P_A_DIM

P_BKLT_EN

+24V

+5V_STB

+5V

+7V

+12V

IR_IN

LED_B

LED_R

SCART_ID1

SCART_ID2

FLASH MEMORY

U181

TA_A/RA_A

PD6

PA1

PA0

PA2

PA3

PA5

PA6

PB4

KIA7042AF

4Pin Con.

LS

TA_A/RA_A

PD0,PD1

U82

MICOM CTRL

PB5,6,7,RESETn

JTAG

* Development Only

DDR memory

UD321, UD322

DDR2

EMI ADDR[1:23]

/EMI DATA[0:15]

PC2

PC0,PC1

PB2

PA4

PA5

PC5

PC4

PC3

LPM_RST_N

CLK IN/OUT

JTAG

HeaderHeader

HOST_A[1:24]

HOST_D[0:15]

MPEG4 (H264)

BLOCK

(TUNER & STi7103)

UART0_TXD/RXD

UART1_TXD/RXD

M_I2C

CEC_A

ID1

ID2

A_RESET

FRC_RST

DDRA[0:12]

/DDRDQ[0:31]

BUS BUFFER

Y961

XTAL

INT_OUT

LS

*I2C ADDR : 0xA2/3

Y81

XTAL

HOST_A[1:23]

HOST_D[0:15]

FLI_I2C1

U582

EEPROM

IR_IN

KEY_ADC1

KEY_ADC2

UART0

UART1

CLK IN/OUT

PWM0

I2C1

IRDATA

LBADC_IN1

LBADC_IN2

EJTAG

DDR MEM

CTL. BUS

ROM MEM

CTL. BUS

U102

SCALER & MPEG2

PWM3

PWM2

PBIAS

PPWR

LVTX_ODD

LVTX_EVN

RESET_N

UART1_CTS

UART1_RTS

USB2.0 HOST

USB_PWREN

USB_FLAG

HDMIA TDMS IN

HDMIA_I2C

HDMIA_CEC

HDMIA_HPD

HDMIB TDMS IN

HDMIB_HPD

HDMIB_I2C

AHS, AVS

VGA_R,VGA_G,VGA_B

S0_SCL/SDA

AUD_IN_L3/R3

LBADC_IN4

A1P,B1P,C1P/SV1P

SCART_FB

AUD_IN_L1/R1

AUD_OUT1R/L

AUD_OUT2R/L

VOUT

LBADC_IN5

A2P,B2P,C2P/SV2P

VXO_D7

AUD_IN_L2/R2

A3P,B3P,C3P

AUD_IN_L4/R4

B4P,A4P

SV3P

AUD_IN_L5/R5

SV4P

TNR_SIF

GPIO134

HEAD_OUT_L/R

AUDIO_MUTE

I2S_OUT

PWM_DIM

A_DIM

BKLT_EN

PANEL_PWR

LVDS_OUT

RESETn_MAIN

FRC_RST

SCART1_RO/LO

SCART2_RO/LO

SCART2_CVBS_OUT

AUDO_MUTE

USF-T

LPM_RST_N

USB_HOST

U114

USB SWITCH

TMDS_A

HDMI_SCL/SDA

CEC_A

VGA_HS/VS 74HC14 HS/VS

PC_R/G/B

SCART1_RI/LI

RF_CVBS

SIF

HP_LO/RO

I2S_OUT

FLI_I2C1

A_RESET

HPDA

U1541,U1581

OP AMP

U381,U383

VIDEO

SWITCH

U382

VIDEO FILTER

YPbPr

Component_R/L

SVHS_Y/C

AV_CVBS

AL/AR_CVBS

HEADPHONE_ID

U764

OP AMP

U761

Digital Audio AMP

FLI_I2C1

* FRC Option

FLI_I2C1

FRC_RST

FRC_RST

+5V

+5V_USB

VGA_SDA/SCL

PC

AUDIO

SCART_ID1

SCART1_R/G/B/CVBS

SCART1_FB

SCART1_RI/LI

SC1_R/L_OUT_O

SC2_R/L_OUT_O

DTT_CVBS

RF_CVBS

SCART1_CVBSO

SCART2_CVBSO

SCART_ID2

SCART2_R/G/B/CVBS

SCART2_FB

SCART2_RI/LI

HPO_L/R

AMP_R-

AMP_R+

AMP_L-

AMP_L+

LCD PANEL

USB IN

U321

HDMI SWITCH

EEPROM

PC IN

SCART1_CVBSO

SC1_R/L_OUT_O

SCART2_CVBSO

SC2_R/L_OUT_O

HEADPHONE

SPEAKER(R)

SPEAKER(L)

EXT3

EXT4

TMDS 1

HPD1

TMDS 2

HPD2

TMDS 3

HPD3

CEC

CEC

CEC

SCART1

SCART2

HDMI

HDMI

HDMI

EXT5

EXT6

EXT7

EXT1

EXT2

AUDO_SPDIF_OUT

(No.YA705<Rev.001>)2-5 2-6(No.YA705<Rev.001>)

SPDIF

DIGITAL AUDIO

Page 6

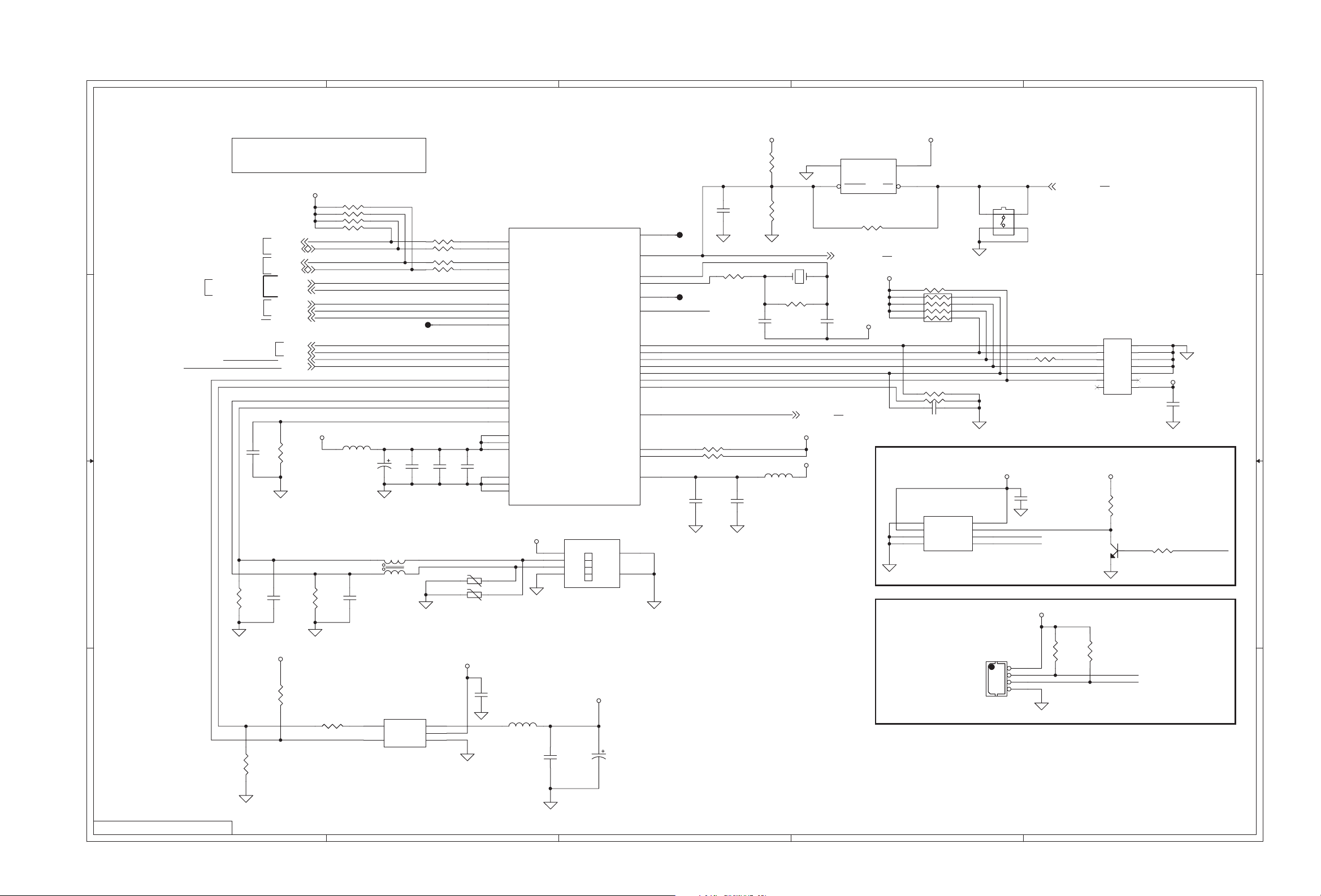

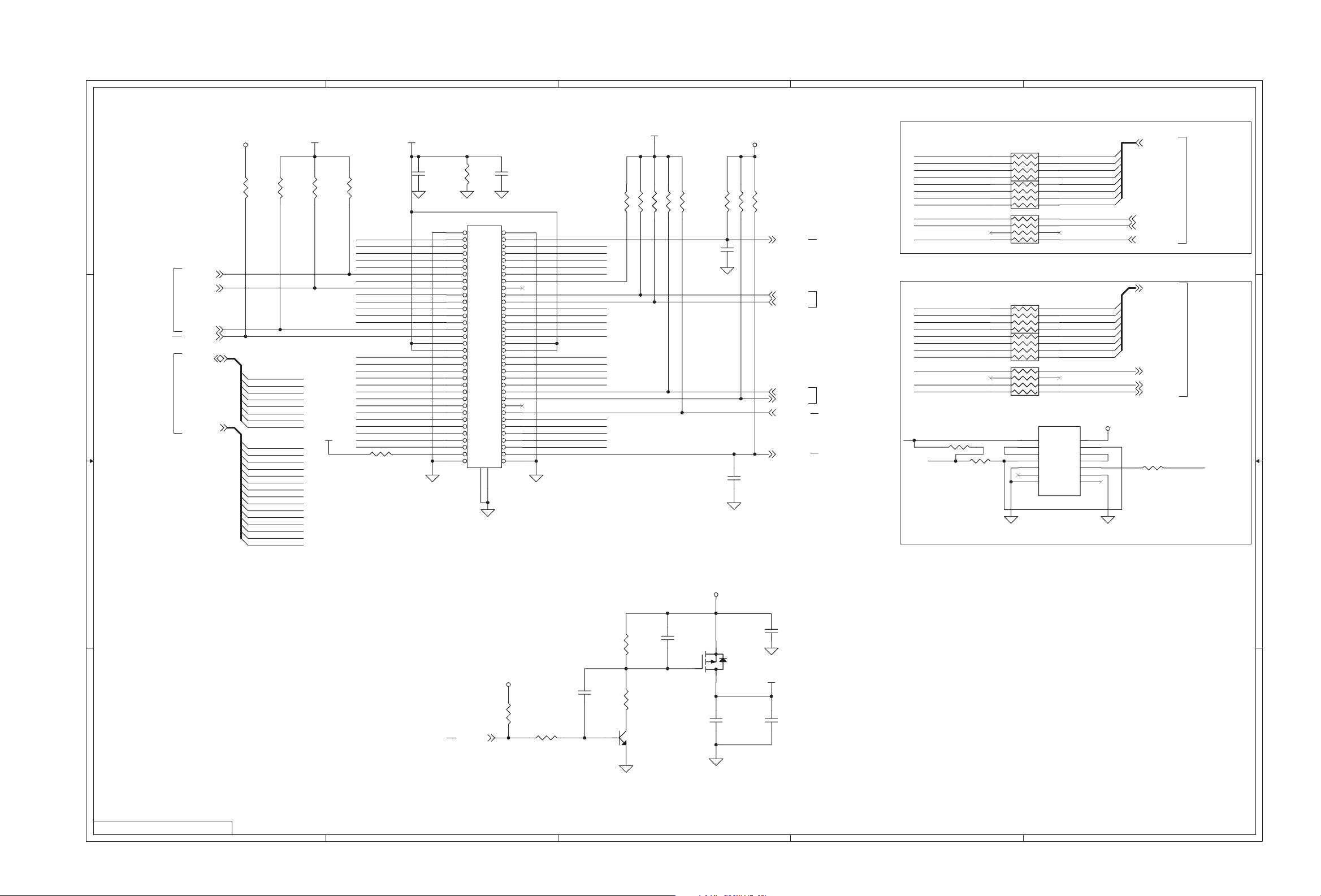

BLOCK DIAGRAM [MPEG4 BLOCK]

STI7103 System DDR memory

EMI ADDR[1:23]

/EMI DATA[0:15]

UD1261, UD1262

DDR SDRAM

PC28F320J3D75/BGA

NOR FLASH

(32Mbit(4Mx8))

Douglas DEMO B/D 256Mbit

SLMI DDRA[0:12]

/SLMI DDRDQ[0:31]

EMI ADDR[1:23]

/EMI DATA[0:15]

Cl contro

Buffer&SW

U1131

MPEG CPU

TSIN0

I2S / SPDIF

DVO

CONT

DATA

UART1

CVBS

DTT_CVBS

HOST_A[1:2]/HOST_D[0:7]

I2S / SPDIF

CLK/BLANK/HSYNC/VSYNC

DVO[0..23]

TX

RX

DTT_CVBS

POD_CTL

POD_DET

I2S / SPDIF

VXI

CONT

DATA

UART1

CVBS

ROM MEM

CTL. BUS

POD_CTL.

U102

SCALER

RF_IN1

RF_IN1

SIF

RF_CVBS

U921 TERRESTRIAL TUNER

LNB_OUT

U1021 SATELLITE TUNER

TUNER0_I2C

TNR0_IF+/-

DEV_/RESET

TUNER0_I2C

DEV_/RESET

TNR1_IF+/-

TUNER1_I2C

U961

DEMOD

U51

BCM4506

U1051

A8293(LNB)

22K_TONE

FLI_I2C0

TS0

TS

FLI_I2C0

TS

FLI_I2C0

DEV_/RESET

TS_SEL0

nTS_SEL0

JP221

CI SLOT

CII TS

CIO TS

R

POD_DET

MUX TS

TS_SEL1

nTS_SEL1

TS Selector

TS_SEL0

TS_SEL1

FLI_I2C0 I2C0

GP0132

TS_Parallel

Inputs

[POD]

2-8(No.YA705<Rev.001>)(No.YA705<Rev.001>)2-7

Page 7

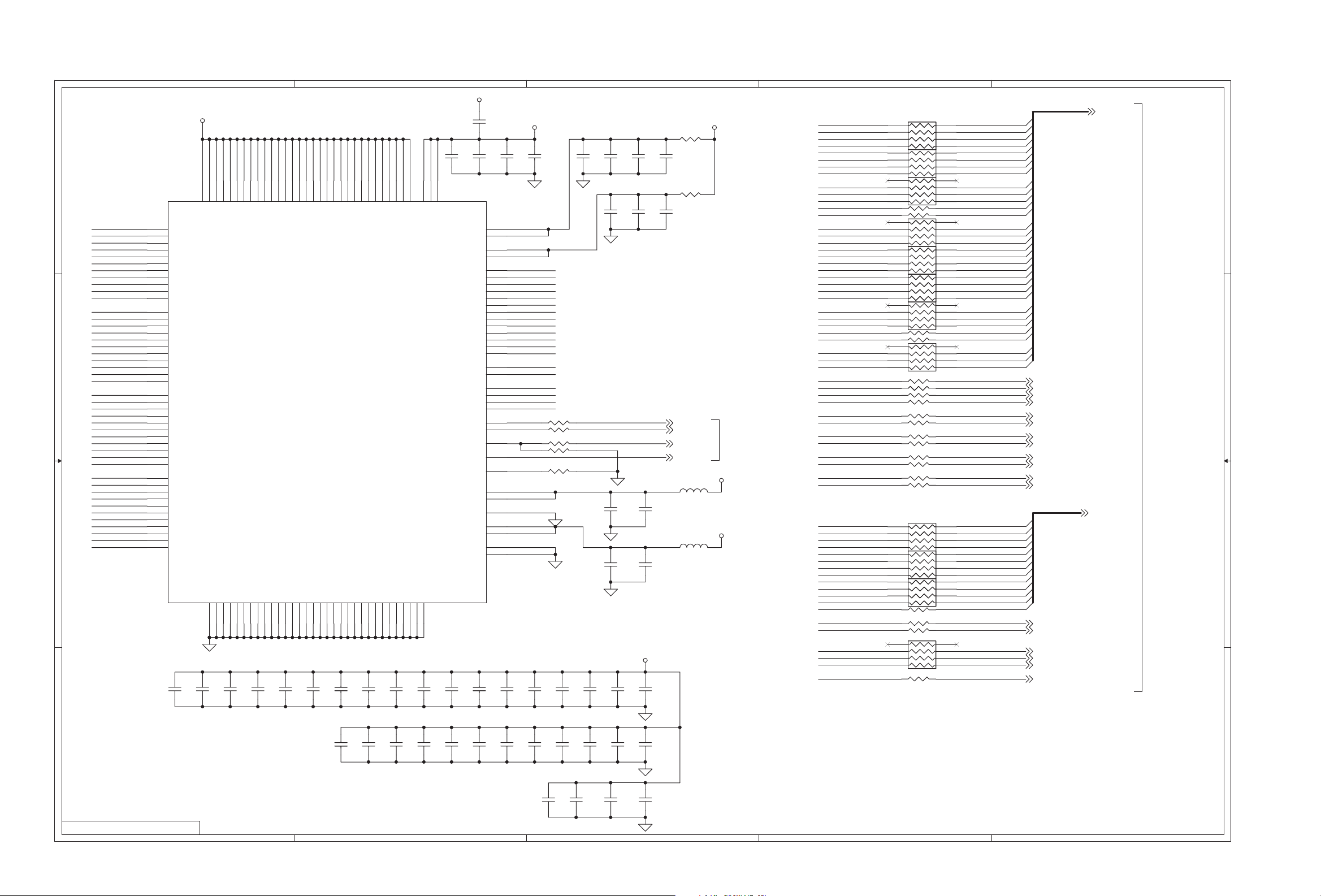

CIRCUIT DIAGRAMS

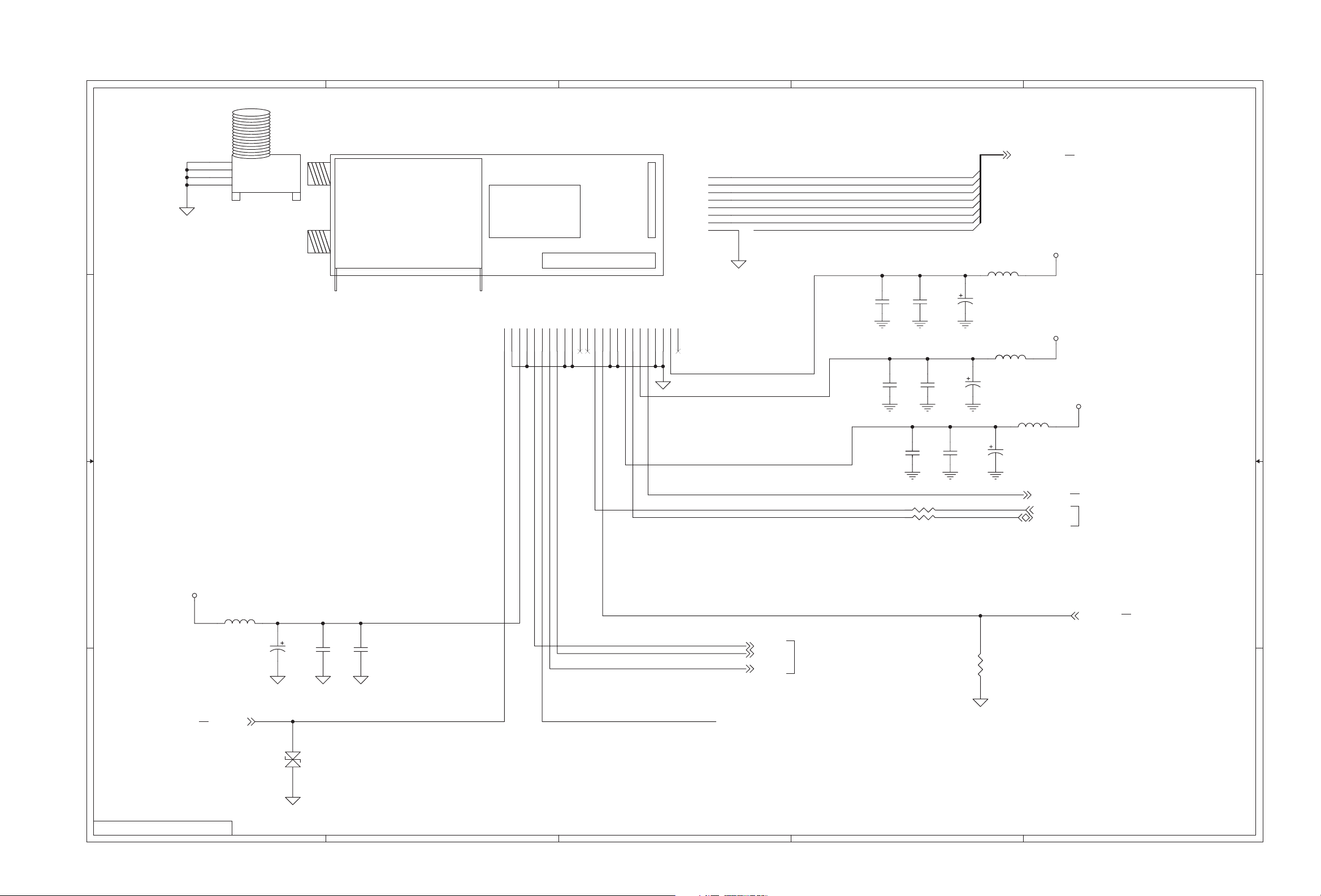

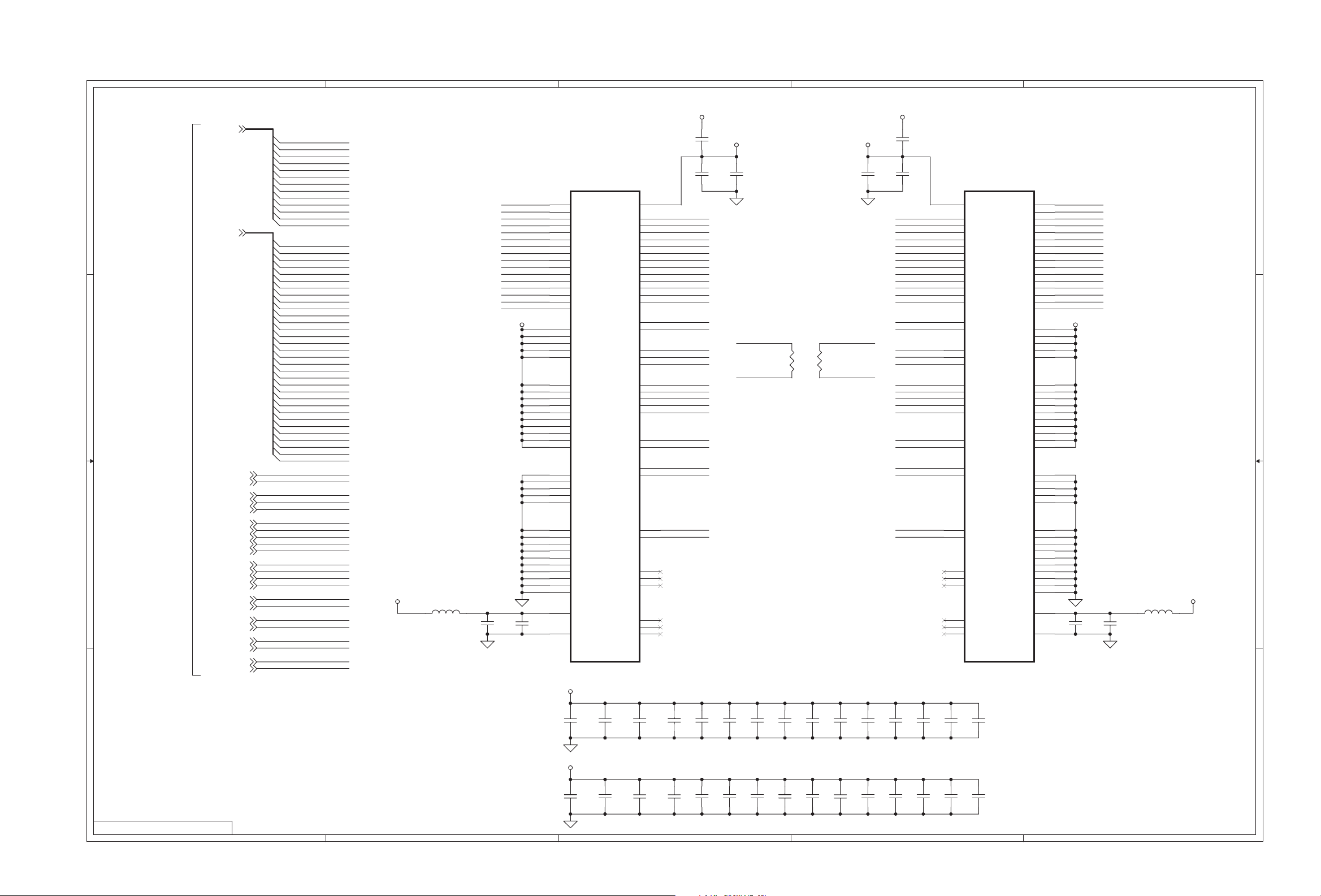

MAIN PWB CIRCUIT DIAGRAM (1/46) [TERRESTRIAL TUNER]

1

2

3

4

5

6

U921

FQD1116AME/BH

RF IN

A A

RF PIN IN/OUT(OPTION)

ANT_PWR2GND3NC4RF_AGC5GND6VP_TUN_+5v

1

+5VT_ANT

L923

BLM18PG300SN1D

220uF/16V/MVK/S

+5VTA

L921

BLM18PG300SN1D

220uF/16V/MVK/S

B B

+5VTA

L922

BLM18PG300SN1D

220uF/16V/MVK/S

C921

C927

C931

C922

104p/16V/1005

C925

104p/16V/1005

C929

104p/16V/1005

C923

102p/50V/1005

C926

102p/50V/1005

C930

102p/50V/1005

IIC AS : Tuner : 0xC0h

Analog Demod : 0x86h

GND9NC10AS11SCL12SDA13REF14IF-AGC15DIF116DIF217WIF OUT/NC

7VT8

+5V IF192nd IF SOUND/LOW DIG IF1

2nd IF SOUND/LOW DIG IF2

18

20

21NC22

R925

121/1005

R929

121/1005

GND

GND

GND

GND

AS_IF23CVBS

24

25

26

27

28

R926

000/1005

C935

4R7p/50V/1005

R928

750/F/1005

RF_CVBS

R940 201/1005

R939 201/1005

R931 330/1005

MAIN PWB(13/46)

DTT_IF_NARROW-

DTT_IF_NARROW+

SIF

DTT_IF_NARROW-

MAIN PWB(26/46)

DTT_IF_NARROW+

MAIN PWB(13/46)

+5VTA +3V3DT

R930

R932 000/1005

R933 000/1005

R934 000/1005

C932

OPEN-330p/1005

C C

Antenna Power Short Protection Circuit

Antenna Current Limiting Circuit (100mA Limiting)

ANT_PWR_EN

+5V_ANT

HIGH

LOW

MAIN PWB(7/46)

D D

ANT_PWR_EN

ANT_PWR_CHK

IF ANT_PWR_CTRL is L

--> ANT_PWR_EN L

R922 330/1005

R923 101/1005

ON

OFF

C933

OPEN-330p/1005

+3V3DT

R924

103/1005

Fault Flag (Output):

C934

104p/16V/1005

U922

1

EN

2

FLG

3

GND

NC4ILIM

POWER SW MIC2544-1YMM

Active-low, open-drain output.

Indicates overcurrent or

thermal shutdown conditions

TUNER0_AGC

+5VTA +5VT_ANT

8

OUT

7

IN

6

OUT

Current limit threshold is determined by

ILIMIT = 230V / RSET,

where : 154 < RSET < 2.29k

R927 222/1005

5

MAIN PWB(26/46)

C936

220p/50V/1005

562/1005

MAIN PWB ASS'Y(1/46)

[TERRESTRIAL TUNER]

HU-71100006

R921

562/1005

Q925

1

FDV301N_NL

32

32

Q924

FDV301N_NL

1

TUNER0_SDA

TUNER0_SCL

MAIN PWB(26/46)

All location are from 921 to 960

1

2

3

4

5

6

hb1_main_0612_24/48_0.0

(No.YA705<Rev.001>)2-9 2-10(No.YA705<Rev.001>)

Page 8

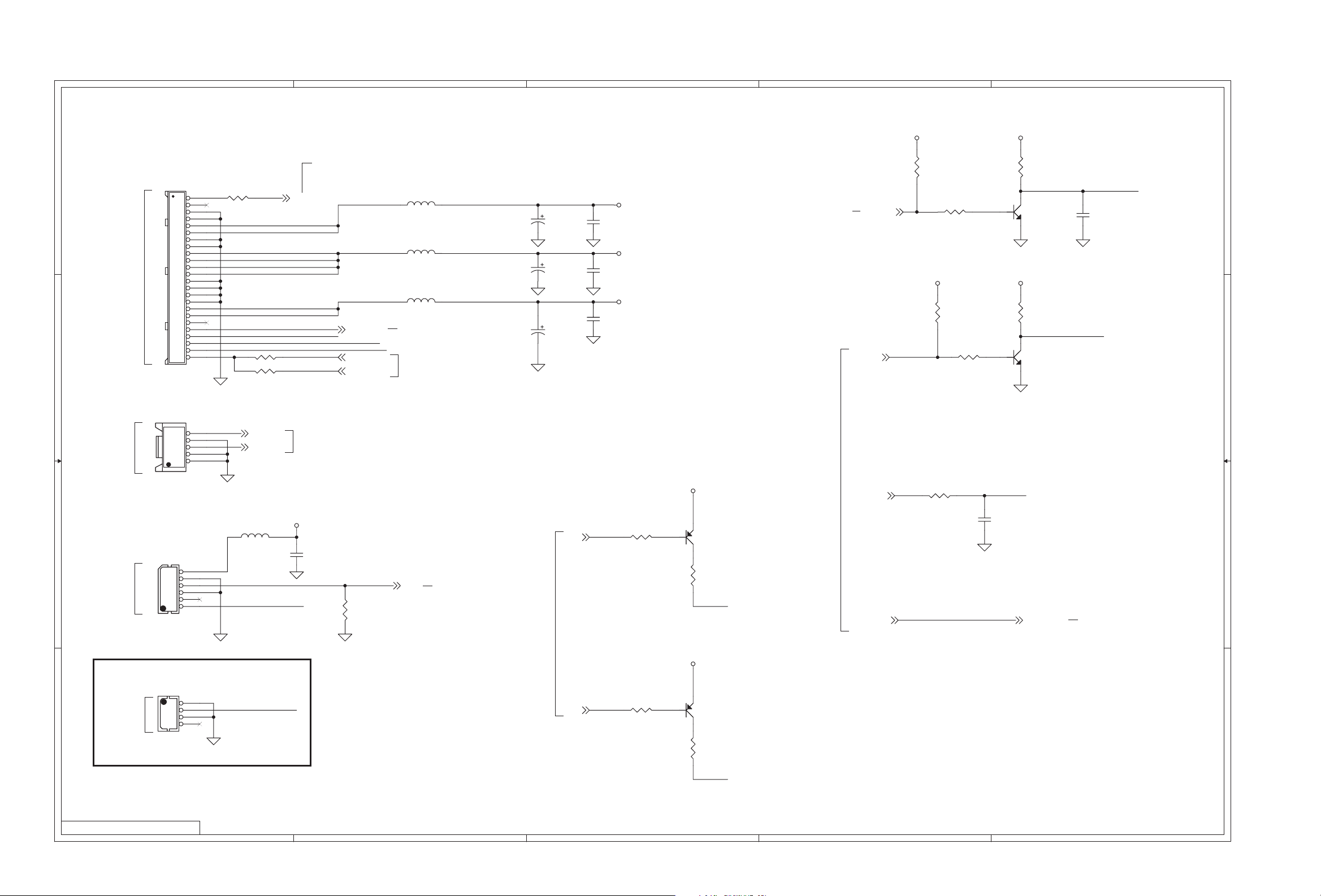

MAIN PWB CIRCUIT DIAGRAM (2/46) [SATELLITE TUNER]

5

U1021

4

3

2

1

*I2C Address : 0xD2

1

GND

2

GND

3

GND

D D

4

GND

JP230

OPEN_DK-504-039(F-CON)

LNB-IN

SHIELD CAN

U51

BCM4505

HS0_D7

HS0_D6

HS0_D5

HS0_D4

HS0_D3

HS0_D2

1X8 connector

HS0_D1

GND

25

26

27

28

29

30

31

32

TS1_DATA7

TS1_DATA6

TS1_DATA5

TS1_DATA4

TS1_DATA3

TS1_DATA2

TS1_DATA1

TS1_DATA0TS_DO0

TS1_DATA[7..0]

LNB-OUT (option)

MAIN PWB(24/46)

A1V2S_BCM4505

2X12 Connector

BLM18PG300SN1D

C1025

HSN-5000HS/DTV

LNB_A1GND23.3V3GND4HS0_VALID

C C

HS0_D06HS0_CLK7HS0_SYNC

5

8

GND9GND10IRQ011NC12SCL13nRESET0

GND15GND162.5V17SDA185V1922K_TONE0

14

GND21GND221.2V23LNB_B

20

24

102p/50V/1005

C1028

102p/50V/1005

102p/50V/1005

C1024

104p/16V/1005

C1027

104p/16V/1005

C1030

104p/16V/1005

R1022

R1023

C1031

330/1005

330/1005

C1026

220uF/16V/MVK/S

BLM18PG300SN1D

L1022

L1023

C1029

220uF/16V/MVK/S

BLM18PG300SN1D

C1032

220uF/16V/MVK/S

+5V_STUNER

2.5VS_BCM4505

L1024

22K_TONE

FLI_SCL_1

FLI_SDA_1

MAIN PWB(27/46)

MAIN PWB(6/46),(26/46),(27/46)

B B

+3.3V_STUNER

L1021

BLM18PG300SN1D

C1023

220uF/16V/MVK/S

MAIN PWB(27/46)

A A

LNB_OUT

C1022

104p/16V/1005

1

1

CD1021

OPEN-AVL26K05121

2

2

C1021

102p/50V/1005

TS_DO0

TS1_VLD

TS1_STR

TS1_CLK

MAIN PWB(24/46)

R1021

222/1005

Must be pull-down register because gpio default

high. then default voltage is about 0.3V

MAIN PWB ASS'Y(2/46)

[SATELLITE TUNER]

CH_RESET

MAIN PWB(7/46)

HU-71100006

All location are from 1021 to 1050

5

4

3

2

1

hb1_main_0612_26/48_0.0

2-12(No.YA705<Rev.001>)(No.YA705<Rev.001>)2-11

Page 9

MAIN PWB CIRCUIT DIAGRAM (3/46) [Power and Interface Connectors]

5

JP1

D D

POWER UNIT

CN1

C C

KEY PWB

JP2

SMW200-24C

1

2

3

4

5

6

7

8

9

10

11

2mm

12

13

14

15

16

17

18

19

20

21

22

23

24

JP2

SMW250-05

2.5mm

5

4

3

2

1

R5 OPEN-000/1005

R7 102/1005

R10 OPEN-102/1005

KEY_ADC2

KEY_ADC1

MAIN PWB(7/46)

AUO_Panel

SMPS_ON

MAIN PWB(5/46)

AC_DETECT

BL_EN_O

ANA_DIM

PWM_DIM_IN

PWM_DIM_OUT

4

L1

BLM41PG600SN1L

L2

BLM41PG600SN1L

L3

BLM21PG600SN1D

MAIN PWB

(4/46),(5/46),(22/46),(43/46)

MAIN PWB(14/46),(19/46)

C1

100uF/25V/BXE/S

C3

470uF/16V/MVK/S

C6

100uF/25V/BXE/S

C2

104p/50V

C4

104p/50V

C7

104p/50V

+12V

+5V

+5V4STB

3

MAX.3A

MAX.3.5A

MAX.500mA

[+12V]

AMP : 1500mA

QPSK : 400mA

PANEL : 800mA

[+5V]

USB : 500mA

CAM : 500mA

PANEL : 1200mA(Option)

[+5.8V]

MICOM : 9mA

RS232 : 10mA

TUNER : 220mA

MAIN PWB(5/46)

2

STBY_EN

BLT_EN

+5VSTB

R1

472/1005

Power on : L

Power off : H

BLT_EN

Backlight on : L

Backlight off : H

R3

103/1005

R17

472/1005

R21

103/1005

+5V4STB

1

23

+5V+5V

1

23

R2

102/1005

Q1

MMBT4401

R18

472/1005

Q5

MMBT4401

SMPS_ON

C5

OPEN-104p/16V/1005

BL_EN_O

1

+5VSTB

IR

LEDR

+5VSTB

C8

104p/16V/1005

R11

OPEN-332/1005

IR_IN

MAIN PWB(5/46)

LED_B

L : ON

H : OFF

L4

BLM18PG300SN1D

JP3

B B

IR PWB

JP1

SMW250-06

6

5

4

2.5mm

3

2

1

R8

103/1005

23

Q2

1

MMBT4403

R9

301/3216

LEDB

MAIN PWB(6/46)

A_DIM

P_DIM

R19

102/1005

ANA_DIM

C9

106p/10V/2012

PWM_DIM_IN

PWM_DIM_IN

MAIN PWB(14/46),(19/46)

MAIN PWB(5/46)

+5VSTB

JP4

53014-0410

1

2mm

2mm

LED PWB

JP3

A A

2

3

4

LEDB

LED_R

L : ON

H : OFF

FRONT BLUE LED

R12

103/1005

23

Q3

1

MMBT4403

R14

301/3216

LEDR

MAIN PWB ASS'Y(3/46)

[Power and Interface Connectors]

HU-71100006

All location are from 1 to 20

5

4

3

2

1

hb1_main_0612_1/48_0.0

(No.YA705<Rev.001>)2-13 2-14(No.YA705<Rev.001>)

Page 10

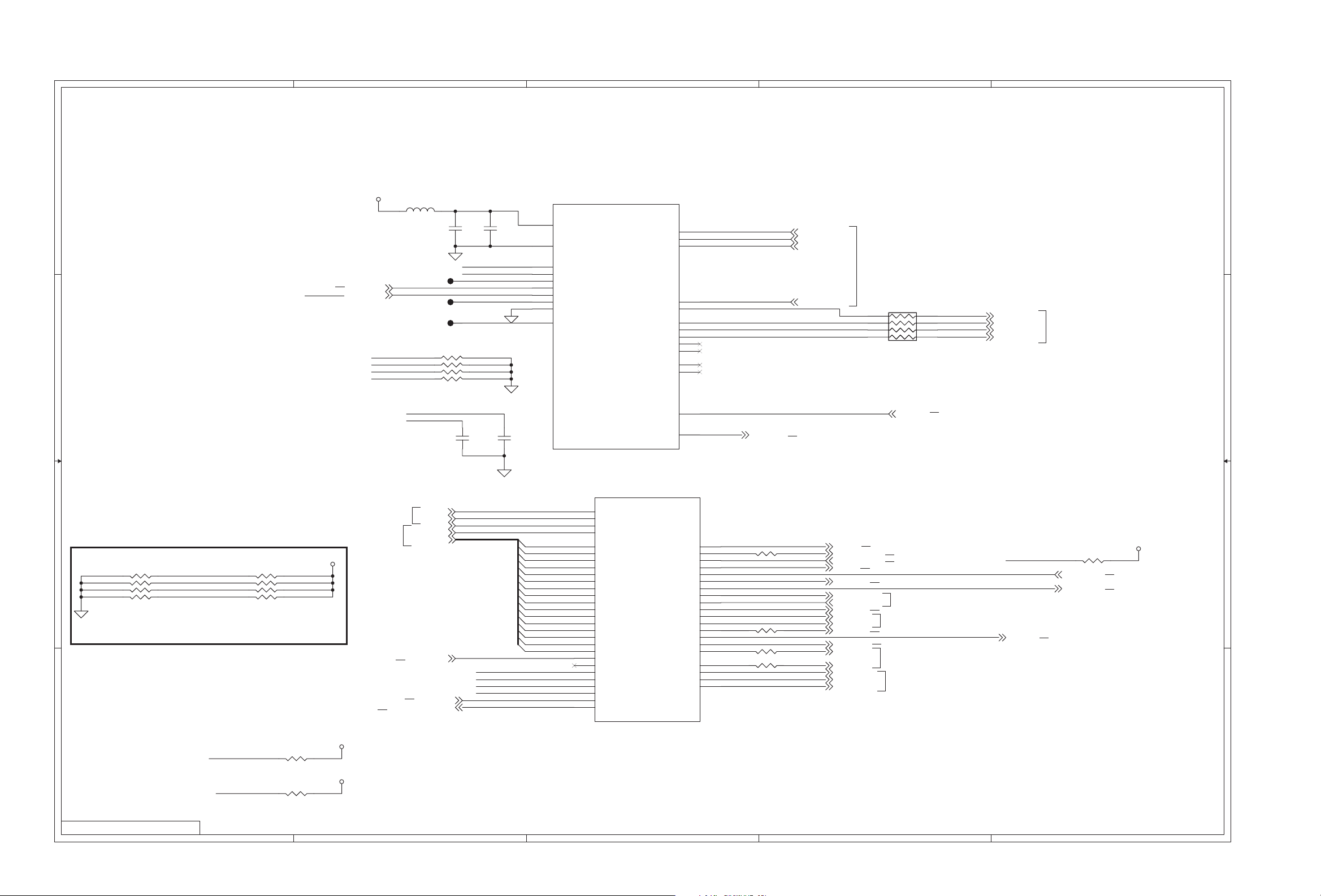

MAIN PWB CIRCUIT DIAGRAM (4/46) [Power Regulation]

1

NORMAL POWER

IN

GND_P

9

MAX: 3A

U32

MP2121DQ

4

IN

7

IN

6

POK

10

EN/SYNC

MAX 1.5A

GND

6

R52

750/F/1005

1

BS

COMP

VOUT

PGOOD

+5V

C69

A A

B B

C C

106p/10V/2012

+5V

C41

106p/10V/2012

+3V3

C52

106p/10V/2012

OPEN-105p/16V/1005

TP17

PCB_TP10

1

C71

106p/10V/2012

C58

C76

C48

104p/16V/1005

+5V

R33

104/1005

OPEN-106p/10V/2012

C42

106p/10V/2012

TP34

PCB_TP10

1

C53

104p/16V/1005

+5V

R42

104/1005

C77

104p/16V/1005

TP32

PCB_TP10

1

C59

105p/25V

7

8

4

R48

104/1005

R49

104/1005

TP36

PCB_TP10

1

2

U31

EN

SS

GND

MP2307

C50

335p/10V/2012

U33

RT9018B25PSP

3

VIN

2

EN

4

VDD

8

GND

9

TAP

Max.3A

/INH1VIN2GND3VOUT4ADJ

2

103p/50V/1005

3

SW

5

FB

6

OPEN-561p/1005

GND

2

6

7

ADJ

5

NC

1

U34

LD29150PT/P-PAK 5P

5

C70

C78

GND

9

11

TP35

PCB_TP10

R1

R2

BS

SW

SW

FB

GND-PAD

1

R34

753/F/1005

R36

593/F/1005

4.7uH/SPC7040-4R7/3.5A

D30

OPEN-B340A

12

12

C75

D31

OPEN-LL4148

822p/25V/1005

R45

4021/F/1005

R39

000/1005

5

3

8

1

R2

R31

304/F/1005

R32

6043/F/1005

Vout=0.8V(R1+R2)/R2

C54

106p/10V/2012

R37

104/1005

Vout=0.8V(R1+R2)/R2

TP37

PCB_TP10

Vout = 0.925 x (1+R1/R2)

L31

R1

R51

OPEN-104/1005

R2

C43

103p/50V/1005

R1

+1V8

[Douglas DDR]

+1.816V,

Max.781mA

C55

104p/16V/1005

+3V3_D

1

3

R43

243/F/1005

R44

912/F/1005

L32

SPC6025-1R0M

104p/16V/1005

+3.3V

MAX 642mA

TP31

PCB_TP10

1

C72

226p/6.3V/2012

TP33

PCB_TP10

1

C44

+3.366V, Max.1.3A

C73

226p/6.3V/2012

C74

220uF/16V/MVK/S

MAIN PWB

(3/46),(5/46),(22/46),(43/46)

[Douglas Core]

+1.216V,

+1V2

Max.1634mA

C62

100uF/25V/BXE/S

C61

226p/6.3V/2012

4

+3V3

AC_DETECT

R46

OPEN-103/1005

C66

OPEN-102p/50V/1005

+5V4STB

OPEN-ASM811REUSF-T

4

3

C92

OPEN-104p/16V/1005

+3V3_D

+1V8

5

+5V4STB

C30

105p/25V

U36

VCC

MR

GND

RESET

1

2

STAND-BY POWER

TP38

PCB_TP10

1

R50

104/1005

R47

OPEN-104/1005

3V3 Power Branch

+3V3 +3V3_A

L33

BLM18PG300SN1D

C46

104p/16V/1005

+3V3H

L34

BLM18PG300SN1D

1V8 Power Branch

VDDR_MEM

L35

BLM18PG300SN1D

C56

104p/16V/1005

U35 RT9167-50PB

1

3

2

C45 104p/16V/1005

C47 220uF/16V/MVK/S

C49 104p/16V/1005

C51 220uF/16V/MVK/S

C57

100uF/25V/BXE/S

VIN

EN

GND

VOUT

BP

C79

103p/50V/1005

R35

102/F/1005

R38

102/F/1005

5

4

DDR_VRF

6

TP39

PCB_TP10

1

C80

105p/25V

C60

104p/16V/1005

+5VSTB

MAX 29mA

C34

104p/16V/1005

C63

D D

106p/10V/2012

C64

104p/16V/1005

C65

OPEN-105p/16V/1005

R40

1692/F/1005

R41

103/F/1005

C31

104p/16V/1005

C67

106p/10V/2012

C68

104p/16V/1005

GND_D

DGND GND_A

MAIN PWB ASS'Y(4/46)

[Power Regulation]

HU-71100006

All location are from 30 to 80

1

2

3

4

5

6

hb1_main_0612_2/48_0.0

2-16(No.YA705<Rev.001>)(No.YA705<Rev.001>)2-15

Page 11

MAIN PWB CIRCUIT DIAGRAM (5/46) [MICRO CTRL]

5

+5VSTB +5VSTB

D D

C81

OPEN-104p/16V/1005

C C

MAIN PWB(40/46),(42/46)

U81

OPEN-KIA7042AF

VCC1GND2OUT3GND

4

S81

1

34

OPEN-JTP1127WEM

MAIN PWB(42/46)

MAIN PWB(3/46)

2

R81

103/1005

C82

104p/16V/1005

CEC_A

CEC_O

STBY_EN

MAIN PWB(23/46)

MAIN PWB(3/46)

MAIN PWB(43/46)

+5VSTB+5VSTB +5VSTB

B B

R107

103/1005

R106

Open_103/1005

R104

Open_103/1005

MOD2_IDMOD1_ID

R105

103/1005

IR_IN

SC_MUTE

System Reset

R82

101/1005

+5VSTB

MOSI

MISO

SCK

RA

TA

R109

103/1005

MOD3_ID

R108

OPEN-103/1005

RESETn

R93

OPEN_103/1005

R95 101/1005

R91 101/1005

+5VSTB

R83

OPEN_103/1005

R84 101/1005

MAIN PWB ASS'Y(5/46)

A A

[MICRO CTRL]

HU-71100006

4

+5VSTB

C87

OPEN-103p/50V/1005

PA0

PA1

PA2

PA3

KEY_ADC2

KEY_ADC1

LED_B

LED_R

PA4

PA5

PA6

MOD2_ID

MOD1_ID

PA7

PB0

PB1

PB2

CEC_A

PB3

PB4

PB5

PB6

PB7

STBY_EN

MOSI

MISO

SCK

AVCC

(ADC0) PA0

(ADC1) PA1

(ADC2) PA2

(ADC3) PA3

(ADC4) PA4

(ADC5) PA5

(ADC6) PA6

(ADC7) PA7

AREF

(SCL) PC0

(SDA) PC1

(TCK) PC2

(TMS) PC3

(TDO) PC4

(TDI) PC5

RESETn

XTAL2

XTAL1

C86

104p/16V/1005

27

37

36

35

34

33

32

31

30

29

19

20

21

22

23

24

25

26

4

7

8

200p/50V/1005

C83

106p/10V/2012

+5VSTB +5VSTB

C84

104p/16V/1005

U82

5

VCC1

17

VCC2

38

VCC3

40

PB0 (XCK/T0)

41

PB1 (T1)

42

PB2 (AIN0/INT2)

43

PB3 (AIN1/OC0)

44

PB4 (SS)

1

PB5 (MOSI)

2

PB6 (MISO)

3

PB7 (SCK)

9

PD0 (RXD)

10

PD1 (TXD)

11

PD2 (INT0)

12

PD3 (INT1)

13

PD4 (OC1B)

14

PD5 (OC1A)

15

PD6 (ICP)

16

PD7 (OC2)

6

GND1

18

GND2

28

GND3

39

GND4

ATMEGA324P-20AU

C85

104p/16V/1005

(TOSC1) PC6

(TOSC2) PC7

Front Key ADC2

Front Key ADC1

Display LED

HDD Recording LED

Model_Detect

Model_Detect

HDMI CEC Control

Stand-by ON/OFF

JTAG

JTAG

JTAG

3

MISO

SCK

RESETn

MOD3_ID

MOD2_ID

MOD1_ID

R89 330/1005

R90 330/1005

R94 101/1005

RESETn

R96 000/1005

C88

PC0

PC1

PC2

PC3

PC4

PC5

FLI_SCL1

FLI_SDA1

INT_OUT Douglas Interrupt

M_RST_N Douglas Chip Reset

AC_DETECT

A_RESET

PC6

PC7

PD0

PD1

RA

TA

PD2

PD3

PD4

PD5

PD6

PD7

IR_IN IR Input

Scart_Mute Scart Audio Output Mute

OPEN-HPH-DS06-02

KEY_ADC2

KEY_ADC1

LED_B

LED_R

Y81

16MHZ/20pF/SMD

12

C89

200p/50V/1005

JP81

12

34

56

+5VSTB +5VSTB

MAIN PWB(3/46)

M_SCL

MAIN PWB(39/46)

M_SDA

M_SCL

M_SDA

INT_OUT

M_RST_N

M_RST_N

AC_DETECT

A_RESET

I2C(to Douglas)

I2C(to Douglas)

SMPS AC Detect

AMP Reset Control(to AMP)

UART0(to RS232)

UART0(to RS232)

MOSI

MAIN PWB(37/46)

MAIN PWB(22/46)

2

+5VSTB

R87

472/1005

INT_OUT

L : Normal

H : Reset

M_RST_N

R97 162/1005

R98 162/1005

+3V3_A

R88

472/1005

1

32

32

1

MAIN PWB

(3/46),(4/46),(22/46),(23/46)

R102 103/1005

+5VSTB

R99

103/1005

R101

102/1005

KEY_ADC2

KEY_ADC1

Q81

FDV301N_NL

Q82

FDV301N_NL

+3V3_A

1

23

FLI_SCL_0

FLI_SDA_0

R103

183/F/1005

R100

103/1005

Q83

MMBT4401

1

C90

104p/16V/1005

C91

104p/16V/1005

MAIN PWB

(6/46),(17/46),(22/46),(40/46)

FLI_INT

MAIN PWB(6/46)

LPM_RST_N

All location are from 81 to 110

5

4

3

2

1

hb1_main_0612_3/48_0.0

(No.YA705<Rev.001>)2-17 2-18(No.YA705<Rev.001>)

Page 12

MAIN PWB CIRCUIT DIAGRAM (6/46) [USB,I2C,JTAG]

5

UART0 : PC Display Debug message

UART1 : G-Probe application run at PC

D D

MAIN PWB(2/46),(26/46),(27/46)

MAIN PWB(5/46),(17/46),(22/46),(40/46)

MAIN PWB(36/46)

STi7103_UART

MAIN PWB(23/46)

MAIN PWB(17/46)

MAIN PWB(3/46)

MAIN PWB(5/46)

C C

B B

A A

MAIN PWB(10/46)

C117

104p/16V/1005

R133

OPEN-153/1005

R137

103/1005

5R0p/50V/1005

FLI_SDA_1

FLI_SCL_1

FLI_SDA_0

FLI_SCL_0

UART0_RX

UART0_TX

UART1_RX

UART1_TX

FRC_/RST

P_DIM

A_DIM

CI_PWR

FLI_INT

R128

622/F/1005

C125

+5V

R138

103/1005

+3V3_A

R113 222/1005

R115 222/1005

R116 222/1005

R117 222/1005

FLI_SDA_1

FLI_SCL_1

FLI_SDA_0

FLI_SCL_0

UART0_RX

UART0_TX

UART1_RX

UART1_TX

+3V3_A +3V3_A

L111

BLM18PG300SN1D

C118

47uF/16V/MVK/S

C126

5R0p/50V/1005

R134

OPEN-153/1005

R139

000/1005

R5523N USB HIGH-SIDE POWER SWITCH

105p/16V/1005

L113

ACM2012H-900

4

U114

1

EN

3

FLG

C119

Active high

4

R120 330/1005

R118 330/1005

R119 330/1005

R121 330/1005

TP113

1

PCB_TP08

USB_D0+

USB_D0-

104p/16V/1005

C120

104p/16V/1005

21

3

RV111

OPEN-AVRL161A1R1NTB

RV112

OPEN-AVRL161A1R1NTB

5

OUT

4

IN

2

GND

C121

+5V

U102G

FLI10620H

D21

2WIRE_M1_SDA_UART2_TX

D20

2WIRE_M1_SCL_UART2_RX

F20

2WIRE_M0_SDA

E20

2WIRE_M0_SCL

A19

UART0_RXD

B19

UART0_TXD

A20

UART1_RXD

B20

UART1_TXD

C20

UART1_RTS

C19

UART1_CTS

A13

PWM3

B13

PWM2_GPIO6

C13

PWM1_GPIO5_/INT5

D13

PWM0_GPIO4_/INT4

C29

USB_FLAG

C28

USB_PWREN

AJ20

USBPHY_PADP

AH20

USBPHY_PADM

AG20

USBPHY_VRES

AG19

USB_AVDD33

AH19

USB_AVDD33

AF20

USB_AVDD33

AF19

USB_GND

AJ19

USB_GND

AD20

USB_GND

+5V_USB

C127

106p/10V/2012

L114

BLM21PG600SN1D

OTP_VDD33

OBUFC_CLK

EJ_RST_N

DFSYNC_IN_OUT_GPIO8

TESTMODE0

TESTMODE1

USB_AVDD12

JP112

KJA-UB-4-0004

1

VBUS

SGND

1

2

D-

2

3

D+

3

4

GND

SGND

4

+5V_USB

C128

104p/16V/1005

C129

100uF/16V/MVK/S

RESET_N

REF_CLK

XTAL_IN

CLKOUT

TRST

TDI

TDO

TMS

TCK

EJ_DINT

5

6

1

A26

TP112

PCB_TP08

D23

A22

A23

1

E12

NVRAM_WP

F21

TRST#

B26

TDI

B27

TDO

A27

TMS

A28

TCK

B28

EJTAG_RST#

A29

DINT

B29

E13

C27

C26

AE20

104p/16V/1005

3

C112

OPEN-680p/50V/1005

R122 000/1005

TP111

PCB_TP08

R129 OPEN-472/1005

R130 OPEN-472/1005

C123

+3V3_A

R111

OPEN-104/1005

R114

OPEN-104/1005

19.6608MHZ/

20PF/SX-1/SMD

C113

270p/50V/1005

L112

BLM18PG300SN1D

C124

106p/10V/2012

Y111

12

R124

OPEN-000

270p/50V/1005

BLT_EN

+1V2

OPEN-ASM811REUSF-T

1

GND

2

RESET

Reset Threshole

: +3.08V

PWR_/RESET

C114

U111

VCC

R112 000/1005

+3V3_A

+3V3_A

MAIN PWB(3/46)

MAIN PWB ASS'Y(6/46)

2

+3V3_A

4

3

MR

MAIN PWB(8/46)

R123 102/1005

PR111 103*4/1005

18

27

36

45

R127

R126

C115 200p/50V/1005

102/1005

103/1005

EEPROM

Address:0xA4/A5

U113

1

A0

A1

A2

VSS

24LC256

VCC

WP

SCL

SDA

2

3

4

LPM_RST_N

S111

12

34

OPEN-JTP1127WEM

R125 OPEN-200/1005

+3V3_A +3V3_A

C122

104p/16V/1005

8

7

FLI_SCL_0

6

FLI_SDA_0

5

JP113

1

2mm

2

3

4

OPEN-53014-0410

WP

+5V

R135

OPEN-472/1005

Q111

MMBT4401

R136

OPEN-472/1005

UART0_TX

UART0_RX

1

MAIN PWB(5/46)

JP111

OPEN-2110-DS14-G

1

2

3

4

5

6

7

8

9

10

11

12

13 14

EJTAG

R131

103/1005

NVRAM_WP : H = Enable write

23

NVRAM_WP : L = Disable write

+3V3_A

C116

104p/16V/1005

R132

103/1005

1

NVRAM_WP

[USB,I2C,JTAG]

All location are from 111 to 160

HU-71100006

5

4

3

2

1

hb1_main_0612_4/48_0.0

2-20(No.YA705<Rev.001>)(No.YA705<Rev.001>)2-19

Page 13

MAIN PWB CIRCUIT DIAGRAM (7/46) [I2S]

5

4

3

2

1

MAIN PWB ASS'Y(7/46)

[I2S]

HU-71100006

D D

MAIN PWB (43/46)

MAIN PWB (44/46)

C C

+3V3_A

SCART1_ID

SCART2_ID

L161

BLM18PG300SN1D

C161

106p/10V/2012

TP164 PCB_TP08

SCART1_ID

SCART2_ID

TP165 PCB_TP08

TP172

PCB_TP08

LBADC_IN1

LBADC_IN2

LBADC_IN3

LBADC_IN6

R163 103/1005

R164 103/1005

R169 103/1005

R170 103/1005

SCART1_ID

SCART2_ID

103p/50V/1005

C165

U102D

FLI10620H

C162

104p/16V/1005

LBADC_IN1

LBADC_IN2

1

1

1

LBADC_IN3

LBADC_IN6

D24

E23

C25

C24

B25

B24

A25

A24

F22

C21

C166

103p/50V/1005

LBADC_33

LBADC_GND

LBADC_IN1

LBADC_IN2

LBADC_IN3

LBADC_IN4

LBADC_IN5

LBADC_IN6

LBADC_RETURN

IRDATA

AUDIN_I2S_BCLK

AUDIN_I2S_WCLK

AUDIN_I2S_DAT

AUD_MCLK0

AUD_MCLK1

AUDO_I2SA_BCLK

AUDO_I2SA_WCLK

AUDO_I2SA_DAT0

AUDO_I2SB_DAT1

AUDO_I2SB_DAT2

AUDO_I2SB_BCLK

AUDO_I2SB_WCLK

AUDIN_SPDIF_IN

AUDO_SPDIF_OUT

AC2

AB3

AA4

AC1

AB5

AB4

AC5

AC4

AD2

AE2

AC3

AD3

AA5

AD1

SPDIF_OUT

ST_PCM_SCLK

ST_PCM_LRCLK

ST_PCMOut0

ST_PCM_MCLK

MAIN PWB(39/46)

MAIN PWB(38/46)

PR161

330*4/1005

18

27

36

45

ST_SPDIF

I2S_OUT_MCLK

I2S_OUT_CLK

I2S_OUT_WS

I2S_OUT_DAT

MAIN PWB(38/46)

MAIN PWB(22/46)

U102F

FLI10620H

MAIN PWB(36/46)

MAIN PWB(38/46)

B B

R178 103/1005

R175 103/1005

R176 103/1005

R177 OPEN-103/1005

Model1_ID

Model2_ID

Model3_ID

Model4_ID

R179 OPEN-103/1005

R171 OPEN-103/1005

R172 OPEN-103/1005

R173 103/1005

Model1_ID : Panel (H:WXGA,L:FHD)

Model2_ID : Model (H:19,20", L: More than 26")

Model3_ID :

Model4_ID : (H: HB1, L: DB1 )

+3V3_A

MAIN PWB (9/46)

MAIN PWB (3/46)

MAIN PWB (46/46)

A A

AUO_Panel

CI_ACC_EN

R174 103/1005

OPEN-103/1005

R161

+3V3_A

+3V3_A

VXI_CLK

VXI_DE

VXI_VS

VXI_HS

VXI_D[0..15]

CI_ACC_EN

AUO_Panel

ST7103_FLASH_EN

Model1_ID

Model2_ID

Model3_ID

Model4_ID

AUO_Panel

CI_ACC_EN

VXI_D0

VXI_D1

VXI_D2

VXI_D3

VXI_D4

VXI_D5

VXI_D6

VXI_D7

VXI_D8

VXI_D9

VXI_D10

VXI_D11

VXI_D12

VXI_D13

VXI_D14

VXI_D15

ST7103_FLASH_EN

A18

VXI_CLK

C18

VXI_DE

B18

VXI_VS

D18

VXI_HS

E19

VXI_D0

A17

VXI_D1

B17

VXI_D2

C17

VXI_D3

D17

VXI_D4

F17

VXI_D5

A16

VXI_D6

B16

VXI_D7

C16

VXI_D8

D16

VXI_D9

D19

VXI_D10

E16

VXI_D11

A15

VXI_D12

B15

VXI_D13

C15

VXI_D14

D15

VXI_D15

E15

VXI_D16

A14

VXI_D17

B14

VXI_D18/TS_ERR

C14

VXI_D19/DREQ_I

D14

VXI_D20/TS_VALID_O

E14

VXI_D21/TS_SYNC_O

E17

VXI_D22/TS_D_O

E18

VXI_D23/TS_CLK_O

VXO_D0

VXO_D1

VXO_D2

VXO_D3

VXO_D4

VXO_D5

VXO_D6

VXO_D7

VXO_D8

VXO_D9

VXO_D10

VXO_D11

VXO_D12

VXO_D13

VXO_D14

VXO_D15

VXO_HS

VXO_VS

VXO_CLK

VXO_DE

AF15

AH16

AJ16

AE15

AE16

AF16

AG16

AH17

AJ17

AE17

AF17

AG17

AH18

AJ18

AD15

AE18

AF18

AG18

AD19

AE19

R166 000/1005

HEADPHONE_ID HEADPHONE_ID

R165 000/1005

R167 OPEN-000/1005

R168 102/1005

TS_SEL

CH_TER_RESET

HEADPHONE_ID

BIT_SEL

CH_RESET

ANT_PWR_EN

ANT_PWR_CHK

TS_SEL_CI

SC1_SEL

SC_FB_SEL

PD_RESET

ST_RESET

PANEL_PWR

OPC_CTL

FRC_MODE0

FRC_MODE1

FRC_MODESEL

MAIN PWB(24/46)

MAIN PWB(26/46)

MAIN PWB(22/46)

MAIN PWB(14/46)

MAIN PWB(2/46)

MAIN PWB(1/46)

MAIN PWB(9/46)

MAIN PWB(13/46)

MAIN PWB(40/46)

MAIN PWB(37/46)

MAIN PWB(14/46)

MAIN PWB(17/46)

VGA_SW

R162 103/1005

EMIBUSREQ

EMIBUSGNT

MAIN PWB(39/46)

+3V3_A

MAIN PWB(35/46)

MAIN PWB(35/46),(36/46)

All location are from 161 to 180

5

4

3

2

1

hb1_main_0612_5/48_0.0

(No.YA705<Rev.001>)2-21 2-22(No.YA705<Rev.001>)

Page 14

MAIN PWB CIRCUIT DIAGRAM (8/46) [Flash and CI Interface]

5

U102C

FLI10620H

Flash_WP#

D D

POD_DET#

POD_DAT_DIR

MAIN PWB(9/46)

MAIN PWB

(9/46),(24/46)

C C

POD_A4

POD_A5

POD_A6

POD_A7

POD_A8

POD_A9

POD_A14

MUX_TSI_CLK

MUX_TSI_VAL

MUX_TSI_SYNC

MUX_TSI_D7

MUX_TSI_D6

MUX_TSI_D5

MUX_TSI_D4

MUX_TSI_D3

MUX_TSI_D2

MUX_TSI_D1

MUX_TSI_D0

CI_WAIT_N

MAIN PWB(10/46)

CI_CD1_N

MAIN PWB(9/46)

MAIN PWB(10/46)

CI_CD2_N

CI_CE1_N

CI_IRQ_N

CI_RESET

POD_DET#

POD_DAT_DIR

POD_A4

POD_A5

POD_A6

POD_A7

POD_A8

POD_A9

POD_A14

MUX_TSI_CLK

MUX_TSI_VAL

MUX_TSI_SYNC

MUX_TSI_D7

MUX_TSI_D6

MUX_TSI_D5

MUX_TSI_D4

MUX_TSI_D3

MUX_TSI_D2

MUX_TSI_D1

MUX_TSI_D0

CI_WAIT_N

CI_CD1_N

CI_CD2_N

CI_CE1_N

CI_IRQ_N

CI_RESET

W1

OOB_CTX

W2

OOB_CRX

W3

OOB_DRX

AD4

POD_DETEC_N

AD5

POD_DIR_N

AE3

POD_A4_CTX

AF3

POD_A5_ITX

AF2

POD_A6_ETX

AG2

POD_A7_QTX

AF1

POD_A8_CRX

AG1

POD_A9_DRX

W5

POD_A14_MCLKO

W6

POD_VS2_MCLKO

Y5

POD_BVD2_MOVAL

Y4

POD_BVD1_MOSTRT

AB1

POD_D15_MDO7

AA1

POD_D14_MDO6

Y1

POD_D13_MDO5

AB2

POD_D12_MDO4

AA2

POD_D11_MDO3

Y2

POD_D10_MDO2

AA3

POD_D9_MDO1

Y3

POD_D8_MDO0

V3

POD_WAIT_N

V5

POD_CD1

V4

POD_CD2

AE4

POD_CE_1

W4

POD_CE_2

V2

POD_READY_IRQ_N

V1

POD_RESET

Bootstrap Pin Name

BSTRAP_BOOT_MODE

B B

BSTRAP_EXT_OSC

BSTRAP_16BIT_FLASH

BSTRAP_NAND_FLASH_EN

BSTRAP_PAGESIZE

BSTRAP_NAND_FLASH_DWIDTH

A A

BSTRAP_NOR_FLASH_SEL

POD_HOST_A0

POD_HOST_A1

POD_HOST_A2

POD_HOST_A3

POD_HOST_A4

POD_HOST_A5

POD_HOST_A6

POD_HOST_A7

POD_HOST_D0/SPI_SDI

POD_HOST_D1

POD_HOST_D2

POD_HOST_D3

POD_HOST_D4

POD_HOST_D5

POD_HOST_D6

POD_HOST_D7

HOST_D8

HOST_D9

HOST_D10

HOST_D11

HOST_D12

HOST_D13

HOST_D14

HOST_D15

POD_HOST_A0

POD_HOST_A1

POD_HOST_A2/SPI_SDO

POD_HOST_A3/SPI_CLK

POD_REG_HOST_A4

POD_IOWR_HOST_A5

POD_IORD_HOST_A6

HOST_A7

HOST_A8

HOST_A9

POD_HOST_A10

POD_HOST_A11

POD_HOST_A12

POD_HOST_A13

HOST_A14

HOST_A15

HOST_A16

HOST_A17

HOST_A18

HOST_A19

HOST_A20

HOST_A21

HOST_A22

HOST_A23

HOST_A24

POD_WE_HOST_WR

POD_OE_HOST_RD

HOST_ACK

HOST_DEV_CS2_N

HOST_DEV_CS1_N

HOST_DEV_CS0_N

HOST_BOOT_CS_N

HOST_READY

Description

Pins POD_HOST_A[1:0] indicate on chip

hardware the host interface configuration

to use after hard reset:

A1;A0 = 00 = Function test, vendor mode.

A1;A0 = 01 = Function test, vendor mode.

A1;A0 = 10 = Boot from FLASH

A1;A0 = 11 = Boot from IROM

Pin POD_HOST_A2 indicates:

0 = Internal osc

1 = External osc

Pin POD_HOST_A3 indicates type of

memory for external boot FLASH.

0 = 8-bit FLASH

1 = 16-bit FLASH

Pin PODREG_HOST_A4 indicates type of

memory for external boot FLASH.

0 = NOR FLASH

1 = NAND FLASH

Pin POD_IOWR_HOST_A5 indicates page

size for off chip NAND FLASH.

0 = Small page NAND FLASH

1 = Large page NAND FLASH

Pin POD_IORD_HOST_A6 indicates data

width for NAND FLASH (used by IROM

boot s/w only).

0 = 8-bit NAND FLASH

1 = 16-bit NAND FLASH

Pin HOST_A[7] selects whether parallel

NOR flash or SPI flash is used for boot

when BSTRAP_BOOT_MODE=10 (IROM

bypass). Ignored if

BSTRAP_BOOT_MODE != 10.

0 = boot from parallel NOR flash

1 = boot from SPI flash

4

AG7

AJ8

AG8

AE7

AH9

AF9

AJ10

AG10

AF7

AH8

AE8

AJ9

AG9

AE9

AH10

AF10

AJ15

AH15

AG15

AE14

AF14

AG14

AH14

AJ14

AE13

AF12

AG12

AH12

AJ12

AE11

AF11

AG11

AH11

AE10

AF13

AG13

AE12

AD13

AH13

AJ11

AD9

AJ13

AF8

AG3

AE5

AF4

AJ4

AG6

AH5

HOST_D0

HOST_D1

HOST_D2

HOST_D3

HOST_D4

HOST_D5

HOST_D6

HOST_D7

HOST_D8

HOST_D9

HOST_D10

HOST_D11

HOST_D12

HOST_D13

HOST_D14

HOST_D15

HOST_A1

HOST_A2

HOST_A3

HOST_A4

HOST_A5

HOST_A6

HOST_A7

HOST_A8

HOST_A9

HOST_A10

HOST_A11

HOST_A12

HOST_A13

HOST_A14

HOST_A15

HOST_A16

HOST_A17

HOST_A18

HOST_A19

HOST_A20

HOST_A21

HOST_A22

HOST_A23

HOST_A24

R189 330/1005

R193 330/1005

HOST_ACK

R199 000/1005

HOST_RD

3

HOST_D[15..0]

+3V3_A

MAIN PWB(9/46),(45/46),(46/46)

HOST_A[24..0]

PCB_TP08

HOST_CS0#

HOST_WE#

HOST_OE#

HOST_CS0#

HOST_BOOT_CS#

HOST_WE#

HOST_OE#

MAIN PWB(45/46)

HOST_BOOT_CS#

MAIN PWB(9/46)

MAIN PWB(9/46),(46/46)

MAIN PWB(45/46),(46/46)

MAIN PWB ASS'Y(8/46)

[Flash and CI Interface]

HU-71100006

HOST_WE#

HOST_A23

HOST_A24

A24 setting default value "0" when STi7103 access flash

HOST WE# setting default value "1" when STi7103 access flash

103/1005

103/1005

L182

BLM18PG300SN1D

HOST_A23

HOST_A24

Flash_WP#

R206 472/1005

R234

R220

103/1005

R217

2

C184

104p/16V/1005

HOST_A1

HOST_A2

HOST_A3

HOST_A4

HOST_A5

HOST_A6

HOST_A7

HOST_A8

HOST_A9

HOST_A10

HOST_A11

HOST_A12

HOST_A13

HOST_A14

HOST_A15

HOST_A16

HOST_A17

HOST_A18

HOST_A19

HOST_A20

HOST_A21

HOST_A22

R203 000/1005

R204

000/1005

TP181

1

+3V3_A

NOTE.

64 MBit FLASH : R203, R204, L26 OPEN

128 MBit FLASH : R204, L26 OPEN

256 MBit FLASH : L27 OPEN(P30 Series)

+3V3_A

C185

104p/16V/1005

U181

A1

A1

B1

A2

C1

A3

D1

A4

D2

A5

A2

A6

C2

A7

A3

A8

B3

A9

C3

A10

D3

A11

C4

A12

A5

A13

B5

A14

C5

A15

D7

A16

D8

A17

A7

A18

B7

A19

C7

A20

C8

A21

A8

A22

G1

A23

H8

A24

B6

NC(A25)

H1

RFU1

G2

RFU2

F1

RFU3

E8

RFU4

B8

RFU5

A4

VPP

H3

VCCA6VCC

VCCQD5VCCQD6VCCQ

VSSB2VSSH2VSSH4VSS

104p/16V/1005

PC28F256P33BF/BGA

G4

F2

DQ0

E2

DQ1

G3

DQ2

E4

DQ3

E5

DQ4

G5

DQ5

G6

DQ6

H7

DQ7

E1

DQ8

E3

DQ9

F3

DQ10

F4

DQ11

F5

DQ12

H5

DQ13

G7

DQ14

E7

DQ15

B4

CE

F8

OE

G8

WE

C6

WP

F6

ADV

E6

CLK

D4

RST

F7

WAIT

H6

BOOT STRAP SETTING

R187 103/1005

R191 103/1005

R195 103/1005

R197 103/1005

R201 103/1005

C181

HOST_D0

HOST_D1

HOST_D2

HOST_D3

HOST_D4

HOST_D5

HOST_D6

HOST_D7HOST_A0

HOST_D8

HOST_D9

HOST_D10

HOST_D11

HOST_D12

HOST_D13

HOST_D14

HOST_D15

#CS_FLASH_DG

HOST_OE#

HOST_WE#

R181

330/1005

POD_DET#

HOST_BOOT_CS#

HOST_RD

HOST_ACK

+3V3_A

C183

104p/16V/1005

C182

106p/10V/2012

MAIN PWB(45/46)

#CS_FLASH_DG

PWR_/RESET

MAIN PWB(6/46)

R184 OPEN-103/1005

R182 103/1005

R183 472/1005

R205 103/1005

HOST_A0

HOST_A1

HOST_A2

HOST_A3

HOST_A4

HOST_A5

HOST_A6

HOST_A7

R188 OPEN-103/1005

R190 103/1005

R192 OPEN-103/1005

R194 103/1005

R196 OPEN-103/1005

R198 OPEN-103/1005

R200 103/1005

R202 OPEN-103/1005

+3V3_A

1

+3V3_A

R185

103/1005

+3V3_A

R186

Flash_WP#

All location are from 181 to 220

5

4

3

2

1

hb1_main_0612_6/48_0.0

2-24(No.YA705<Rev.001>)(No.YA705<Rev.001>)2-23

Page 15

MAIN PWB CIRCUIT DIAGRAM (9/46) [CI Select]

5

MAIN PWB(10/46)

D D

MAIN PWB(8/46),(24/46)

C C

MAIN PWB(10/46)

MAIN PWB

(8/46),(24/46)

B B

MUX_TSI_SYNC

MAIN PWB(8/46),(24/46)

PPKT_D[7..0]

PPKT_CLK

PPKT_VAL

PPKT_SYNC

MUX_TSI_VAL

MUX_TSI_CLK

MUX_TSI_D0

MUX_TSI_D1

MUX_TSI_D2

MUX_TSI_D3

MUX_TSI_D4

MUX_TSI_D5

MUX_TSI_D6

MUX_TSI_D7

TS_SEL_CI0

MUX_TSI_D0

MUX_TSI_D1

MUX_TSI_D2

MUX_TSI_D3

MUX_TSI_D4

MUX_TSI_D5

MUX_TSI_D6

MUX_TSI_D7

nTS_SEL_CI0

PPKT_CLK

PPKT_VAL

PPKT_SYNC

TS_SEL_CI0

nTS_SEL_CI0

MUX_TSI_D0

MUX_TSI_D1

MUX_TSI_D2

MUX_TSI_D3

MUX_TSI_D4

MUX_TSI_D5

MUX_TSI_D6

MUX_TSI_D7

MUX_TSI_VAL

MUX_TSI_SYNC

MUX_TSI_CLK

MUX_TSI_D1

MUX_TSI_D2

MUX_TSI_D3

MUX_TSI_D4

MUX_TSI_D5

MUX_TSI_D6

MUX_TSI_D7

POD_DET#

PPKT_D0

PPKT_D1

PPKT_D2

PPKT_D3

PPKT_D4

PPKT_D5

PPKT_D6

PPKT_D7

A1

B1

C1

D1

E3

D2

C3

B2

A2

A4

SN74LVC244AZQNR

A1

B1

C1

D1

E3

D2

C3

B2

A2

A4

SN74LVC244AZQNR

A1

1A1

B1

1A2

C1

1A3

D1

1A4

E3

2A1

D2

2A2

C3

2A3

B2

2A4

A2

1OE

A4

2OE

SN74LVC244AZQNR

A1

1A1

B1

1A2

C1

1A3

D1

1A4

E3

2A1

D2

2A2

C3

2A3

B2

2A4

A2

1OE

A4

2OE

SN74LVC244AZQNR

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

1OE

2OE

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

1OE

2OE

DGND

U213

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

VCC

DGND

DGND

DGND

U219

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

VCC

U218

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

VCC

U212

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

VCC

MAIN PWB(7/46)

CI_ACC_EN

CI_CE1_N

A A

R1024 OPEN-330/1005

R243 000/1005

R216 OPEN-000/1005

CI_BUFF_ENPOD_DET#

HOST_A6

1

2

3

U214

OE

INA

GND

74LVC1G125

4

B4

C4

D4

E4

E2

D3

C2

B3

+3V3_D

A3

E1

B4

C4

D4

E4

E2

D3

C2

B3

+3V3_D

A3

E1

B4

C4

D4

E4

E2

D3

C2

B3

+3V3_D

A3

E1

PR211

101*4/1005

PR212

101*4/1005

PR213

18

101*4/1005

27

36

45

18

27

36

45

18

27

36

45

TS_ST_DATA0

TS_ST_DATA1

TS_ST_DATA2

TS_ST_DATA3

TS_ST_DATA4

TS_ST_DATA5

TS_ST_DATA6

TS_ST_DATA7

TS_ST_CLK

TS_ST_VAL

TS_ST_SYNC

MAIN PWB(8/46),(46/46)

MDO_D0MUX_TSI_D0

B4

MDO_D1

C4

MDO_D2

D4

MDO_D3

E4

MDO_D4

E2

MDO_D5

D3

MDO_D6

C2

MDO_D7

B3

+3V3_D

A3

E1

MDO_D[7..0]

MAIN PWB(10/46)

MAIN PWB(8/46)

MAIN PWB(7/46)

VCC

+3V3_D

5

CI_IORD_N

4

Y

CI_IORD_N

3

MAIN PWB(8/46),(45/46),(46/46)

TS_ST_DATA[7..0]

MAIN PWB(34/46)

MAIN PWB(8/46)

MAIN PWB(8/46),(45/46),(46/46)

TS_ST_CLK

TS_ST_VAL

TS_ST_SYNC

MAIN PWB(8/46)

MAIN PWB(34/46)

HOST_WE#

HOST_OE#

MAIN PWB(8/46),(24/46)

POD_DET#

TS_SEL_CI

TS_SEL_CI

1 : TUNER out TS (free)

0 : CI out TS ( scramble)

OPEN-000/1005

HOST_D[15..0]

MAIN PWB(8/46)

HOST_WE#

HOST_OE#

MAIN PWB(8/46)

R212

R211

000/1005

2

POD_DAT_DIR

POD_A7

POD_A6

POD_A8

POD_A4

CI_CE1_N

POD_A5

POD_A14

POD_A9

HOST_A[24..0]

R219 330/1005

R218 330/1005

MUX_TSI_VAL

MUX_TSI_SYNC

MUX_TSI_CLK

POD_DET#

+3V3_D +3V3_D

R215

472/1005

R214

103/1005

1

Q211

MMBT4401

HOST_D0

HOST_D1

HOST_D2

HOST_D3

HOST_D4

HOST_D5

HOST_D6

HOST_D7

+3V3_D

POD_A7

POD_A6

POD_A8

POD_A4

POD_A5

POD_A14

POD_A9

CI_BUFF_EN

HOST_A0

HOST_A1

HOST_A2

HOST_A3

HOST_A13

HOST_A10

HOST_A11

HOST_A12

CI_BUFF_EN

HOST_A4

HOST_A5

MUX_TSI_VAL

MUX_TSI_SYNC

MUX_TSI_CLK

CI_BUFF_EN

POD_DET#

R213

103/1005

nTS_SEL_CI0

TS_SEL_CI0

23

1

U211

B4

B1

B2

B2

C4

B3

C3

B4

D4

B5

D2

B6

E4

B7

E3

B8

A3

VCC

E1

DGND

SN74LVC245AZQNR

A1

1A1

B1

1A2

C1

1A3

D1

1A4

E3

2A1

D2

2A2

C3

2A3

B2

2A4

A2

1OE

A4

2OE

SN74LVC244AZQNR

A1

B1

C1

D1

E3

D2

C3

B2

A2

A4

SN74LVC244AZQNR

A1

B1

C1

D1

E3

D2

C3

B2

A2

A4

SN74LVC244AZQNR

C219

104p/16V/1005

A1

A2

A3

A4

A5

A6

A7

A8

DIR

OE

U217

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

1OE

2OE

1A1

1A2

1A3

1A4

2A1

2A2

2A3

2A4

1OE

2OE

C212

104p/16V/1005

A1

B3

B1

C2

C1

D3

D1

E2

A2

A4

B4

1Y1

C4

1Y2

D4

1Y3

E4

1Y4

E2

2Y1

D3

2Y2

C2

2Y3

B3

2Y4

A3

VCC

E1

DGND

U215

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

VCC

DGND

U216

1Y1

1Y2

1Y3

1Y4

2Y1

2Y2

2Y3

2Y4

VCC

DGND

C214

C211

104p/16V/1005

CI_D0

CI_D1

CI_D2

CI_D3

CI_D4

CI_D5

CI_D6

CI_D7

POD_DAT_DIR

CI_BUFF_EN

CI_A7

CI_A6

CI_A8

CI_A4

CI_CE1_N#CI_CE1_N

CI_A5

CI_A14

CI_A9

+3V3_D

B4

C4

D4

E4

E2

D3

C2

B3

+3V3_D

A3

E1

CI_WE_N

B4

CI_OE_N

C4

CI_REG_N

D4

CI_IOWR_N

E4

E2

MDO_VAL

D3

MDO_SYNC

C2

MDO_CLK

B3

A3

E1

C213

104p/16V/1005

104p/16V/1005

CI_A0

CI_A1

CI_A2

CI_A3

CI_A13

CI_A10

CI_A11

CI_A12

+3V3_D

C215

104p/16V/1005

CI_D[7..0]

CI_WE_N

CI_OE_N

CI_REG_N

CI_IOWR_N

MDO_VAL

MDO_SYNC

MDO_CLK

C216

C217

104p/16V/1005

MAIN PWB

(10/46)

CI_A[14..0]

CI_CE1_N#

MAIN PWB

(10/46)

MAIN PWB

(10/46)

+3V3_D

C218

104p/16V/1005

104p/16V/1005

MAIN PWB ASS'Y(9/46)

All location are from 211 to 220

[CI Select]

HU-71100006

5

4

3

2

1

hb1_main_0612_7/48_0.0

(No.YA705<Rev.001>)2-25 2-26(No.YA705<Rev.001>)

Page 16

MAIN PWB CIRCUIT DIAGRAM (10/46) [CI Slot]

5

+3V3_A

D D

R221

103/1005

CI_CE1_N#

CI_OE_N

R223

103/1005

R224

103/1005

MAIN PWB(9/46)

CI_WE_N

MAIN PWB(8/46)

C C

MAIN PWB(9/46)

B B

CI_IRQ_N

CI_D[7..0]

CI_A[14..0]

CI_D0

CI_D1

CI_D2

CI_D3

CI_D4

CI_D5

CI_D6

CI_D7

CI_A0

CI_A1

CI_A2

CI_A3

CI_A4

CI_A5

CI_A6

CI_A7

CI_A8

CI_A9

CI_A10

CI_A11

CI_A12

CI_A13

CI_A14

R225

103/1005

CI_D3

CI_D4

CI_D5

CI_D6

CI_D7

CI_CE1_N#

CI_A10

CI_OE_N

CI_A11

CI_A9

CI_A8

CI_A13

CI_A14

CI_WE_N

CI_IRQ_N

CI_MIVAL

CI_MCLKI

CI_A12

CI_A7

CI_A6

CI_A5

CI_A4

CI_A3

CI_A2

CI_A1

CI_A0

CI_D0

VCC_CI

CI_D1

CI_D2

R233 103/1005

VCC_CI

4

C221

104p/16V/1005

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

1

2

3

4

5

6

7

8

9

R222

C227

121/5025

104p/16V/1005

JP221

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

696970

70

A01C5A0045P1P00/1-SLOT

CI_MDO_3

CI_MDO_4

CI_MDO_5

CI_MDO_6

CI_MDO_7

CI_IORD_N

CI_IOWR_N

CI_MISTART

CI_MDI_0

CI_MDI_1

CI_MDI_2

CI_MDI_3

CI_MDI_4

CI_MDI_5

CI_MDI_6

CI_MDI_7

CI_MCLKO

CI_RESET

CI_WAIT_N

CI_REG_N

CI_MOVAL

CI_MOSTART

CI_MDO_0

CI_MDO_1

CI_MDO_2

CI_CD2_N

R232 103/1005

R227 103/1005

VCC_CI

R228 103/1005

3

R229 104/1005

R239 103/1005

104p/16V/1005

C228

+3V3_AVCC_CI

R230 103/1005

R226 103/1005

C229

104p/16V/1005

R231 103/1005

CI_CD1_N

CI_IORD_N

CI_IOWR_N

CI_RESET

CI_WAIT_N

CI_REG_N

CI_CD2_N

MAIN PWB(8/46)

MAIN PWB(9/46)

MAIN PWB(8/46)

MAIN PWB(9/46)

MAIN PWB(8/46)

2

TS INPUT

CI_MDI_0

CI_MDI_1

CI_MDI_2

CI_MDI_3

CI_MDI_4

CI_MDI_5

CI_MDI_6

CI_MDI_7

CI_MISTART

CI_MIVAL

CI_MCLKI MDO_CLK

PR221

18

330*4/1005

27

36

45

PR222

18

330*4/1005

27

36

45

PR223

18

330*4/1005

27

36

45

MDO_D0

MDO_D1

MDO_D2

MDO_D3

MDO_D4

MDO_D5

MDO_D6

MDO_D7

MDO_SYNC

MDO_VAL

TS OUTPUT

U221

+5V

A1

O1

O6

A2

O2

O5

A3

O3

O4

DGND

OPEN-74HC14

PPKT_D0

PPKT_D1

PPKT_D2

PPKT_D3

PPKT_D4

PPKT_D5

PPKT_D6

PPKT_D7

PPKT_VAL

PPKT_SYNC

14

13

A6

12

11

A5

10

9

A4

8

+3V3_A

CI_MDO_0

CI_MDO_1

CI_MDO_2

CI_MDO_3

CI_MDO_4

CI_MDO_5

CI_MDO_6

CI_MDO_7

M_CLK PPKT_CLK

CI_MOVAL

CI_MOSTART

CI_MCLKO

R240 000/1005

M_CLK

PR224

18

330*4/1005

27

36

45

PR225

18

330*4/1005

27

36

45

PR226

18

330*4/1005

27

36

45

R241 OPEN_000/1005

1

2

3

4

5

6

7

These all of components must be located near Douglas

1

MDO_D[7..0]

MDO_SYNC

MDO_VAL

MDO_CLK

PPKT_D[7..0]

PPKT_CLK

PPKT_VAL

PPKT_SYNC

R242

OPEN_000/1005

MAIN PWB

(9/46)

MAIN PWB

(9/46)

M_CLK

+5V

R235

472/1005 --> 473/1005

+3V3_A

R237

332/1005

C225

R236

OPEN-752/1005

A A

MAIN PWB(6/46)

CI_PWR

OPEN-682p/50V/1005

1

473/1005

R238

103/1005

Q222

MMBT4401

23

C224

225p/16V

1

IRLML6402TRPBF

Q221

2

3

C226

106p/10V/2012

C223

104p/16V/1005

VCC_CI

C222

106p/10V/2012

MAIN PWB ASS'Y(10/46)

[CI Slot]

HU-71100006

All location are from 221 to 250

5

4

3

2

1

hb1_main_0612_8/48_0.0

2-28(No.YA705<Rev.001>)(No.YA705<Rev.001>)2-27

Page 17

MAIN PWB CIRCUIT DIAGRAM (11/46) [DDR Interface]

5

VDDR_MEM

D D

F25

F27

F29

H24

H27

H29

K25

K27

K29

M29

AF25

D25

SDDR_D0

SDDR_D1

SDDR_D2

SDDR_D3

SDDR_D4

SDDR_D5

SDDR_D6

SDDR_D7

SDDR_DM0

SDDR_DQS0

SDDR_DQS0#

SDDR_D8

SDDR_D9

SDDR_D10

SDDR_D11

SDDR_D12

SDDR_D13

SDDR_D14

SDDR_D15

C C

B B

SDDR_DM1

SDDR_DQS1

SDDR_DQS1#

SDDR_D16

SDDR_D17

SDDR_D18

SDDR_D19

SDDR_D20

SDDR_D21

SDDR_D22

SDDR_D23

SDDR_DM2

SDDR_DQS2

SDDR_DQS2#

SDDR_D24

SDDR_D25

SDDR_D26

SDDR_D27

SDDR_D28

SDDR_D29

SDDR_D30

SDDR_D31

SDDR_DM3

SDDR_DQS3

SDDR_DQS3#

F24

M24

J25

K26

M26

E25

L25

F26

K24

H25

H26

E29

L29

H28

J29

L27

E27

K28

F28

J27

G28

G29

Y24

AF28

AC25

AD26

AF26

W25

AE25

Y26

AD24

AB25

AB26

W29

AE29

AB28

AC29

AE27

W27

AD28

Y28

AC27

AA28

AA29

CD267

104p/16V/1005

DDR_D0

DDR_D1

DDR_D2

DDR_D3

DDR_D4

DDR_D5

DDR_D6

DDR_D7

DDR_DM0

DDR_DQS0

DDR_DQS0_N

DDR_D8

DDR_D9

DDR_D10

DDR_D11

DDR_D12

DDR_D13

DDR_D14

DDR_D15

DDR_DM1

DDR_DQS1

DDR_DQS1_N

DDR_D16

DDR_D17

DDR_D18

DDR_D19

DDR_D20

DDR_D21

DDR_D22

DDR_D23

DDR_DM2

DDR_DQS2

DDR_DQS2_N

DDR_D24

DDR_D25

DDR_D26

DDR_D27

DDR_D28

DDR_D29

DDR_D30

DDR_D31

DDR_DM3

DDR_DQS3

DDR_DQS3_N

CD268

104p/16V/1005

DDR_VDD

DDR_VDD

DDR_VDD

DDR_VDD

CVSS

CVSS

CVSS

E24

E26

E28

CD269

104p/16V/1005

DDR_VDD

DDR_VDD

CVSS

CVSS

G24

G26

G27

DDR_VDD

DDR_VDD

CVSS

CVSS

J24

J26

CD270

104p/16V/1005

M25

DDR_VDD

DDR_VDD

DDR_VDD

DDR_VDD

CVSS

CVSS

CVSS

CVSS

J28

L24

L26

CD271

104p/16V/1005

N24

DDR_VDD

CVSS

L28

N27

P28

R25

U25

DDR_VDD

DDR_VDD

DDR_VDD

DDR_VDD

U102A

FLI10620H

CVSS

CVSS

CVSS

CVSS

T24

P26

N28

CD272

104p/16V/1005

Y25

V27

Y27

DDR_VDD

DDR_VDD

DDR_VDD

CVSS

CVSS

CVSS

T26

V29

W24

Y29

AB24

AB27

AB29

AD25

DDR_VDD

DDR_VDD

DDR_VDD

DDR_VDD

DDR_VDD

CVSS

CVSS

CVSS

CVSS

CVSS

W26

W28

AA24

AA26

AA27

CD274

104p/16V/1005

CD273

104p/16V/1005

AD27

AC24

AD29

AF27

AF29

DDR_VDD

DDR_VDD

DDR_VDD

DDR_VDD

CVSS

CVSS

CVSS

CVSS

AE24

AC26

AC28

CD275

104p/16V/1005

4

D27

D29

DDR_VDD

DDR_VDD

CVSS

CVSS

CVSS

D26

AE26

AE28

CD252

104p/16V/1005

R24

AA25

G25

DDR_VDDI

DDR_VDDI

DDR_VRF_1

DDR_VRF_2

DDR_VRF_0

DLL_VAA0

DLL_VAA1

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_BA0

DDR_BA1

DDR_CAS_N

DDR_RAS_N

DDR_CS_N

DDR_WE_N

DDR_CK

DDR_CK_N

DDR_CKE

DDR_ODT

DDR_CAL

RPLL_AVDD12

DDRPLL_AVDD12

RPLL_AGND

RPLL_AVDD33

DDRPLL_AVDD33

DDRPLL_AGND

RPLL_AGND

CVSS

D28

CD276

104p/16V/1005

CD277

104p/16V/1005

VDDR_MEM

CD251

104p/16V/1005

CD253

102p/50V/1005

F23

AD23

M28

V24

P27

U29

R26

U26

P25

T28

R27

V28

R29

T29

V25

R28

V26

U28

T27

P24

N26

N25

T25

P29

N29

U27

M27

U24

C23

D22

B22

B23

E22

E21

C22

CD278

104p/16V/1005

DDR_VRF

CD255

226p/6.3V/2012

CD254

105p/16V/1005

SDDR_A0

SDDR_A1

SDDR_A2

SDDR_A3

SDDR_A4

SDDR_A5

SDDR_A6

SDDR_A7

SDDR_A8

SDDR_A9

SDDR_A10

SDDR_A11

SDDR_A12

SDDR_BA0

SDDR_BA1

SDDR_CAS

SDDR_RAS

SDDR_CS

SDDR_WE

RD262 100/1005

RD263 100/1005

RD276 103/1005

RD265 103/1005

RD268 2940/F/1005

CD280

104p/16V/1005

CD279

104p/16V/1005

CD281

104p/16V/1005

CD256

103p/50V/1005

CD263

103p/50V/1005

CD265

103p/50V/1005

CD282

104p/16V/1005

CD257

103p/50V/1005

CD260

103p/50V/1005

VDDR_MEM

CD283

104p/16V/1005

3

CD258

226p/6.3V/2012

CD261

103p/50V/1005

The CKE pull down is for power off

mode DDR self refresh

DDR2_CKE

CD264

103p/50V/1005

CD266

103p/50V/1005

CD284

104p/16V/1005

+3V3_A

RD251

1R0/2012

CD259

226p/6.3V/2012

RD252

1R0/2012

CD262

226p/6.3V/2012

DDR2_CLK

DDR2_CLK_N

DDR2_CKE

DDR2_ODT

LD251

BLM18PG300SN1D

+3V3_A

LD252

BLM18PG300SN1D

+1V2

MAIN PWB(12/46)

SDDR_D2

SDDR_D0

SDDR_D7

SDDR_D5

SDDR_D4

SDDR_D1

SDDR_D3

SDDR_D6

SDDR_D15

SDDR_D8

SDDR_D13

SDDR_D10

SDDR_D11

SDDR_D12

SDDR_D9

SDDR_D14

SDDR_D18

SDDR_D16

SDDR_D23

SDDR_D21

SDDR_D17

SDDR_D22

SDDR_D20

SDDR_D19

SDDR_D31

SDDR_D29

SDDR_D24

SDDR_D26

SDDR_D27

SDDR_D28

SDDR_D25

SDDR_D30

SDDR_DM0

SDDR_DM1

SDDR_DM2

SDDR_DQS0

SDDR_DQS0#

SDDR_DQS1

SDDR_DQS1#

SDDR_DQS2

SDDR_DQS2#

SDDR_DQS3

SDDR_DQS3#

SDDR_A11

SDDR_A2

SDDR_A8

SDDR_A0

SDDR_A5

SDDR_A4

SDDR_A9

SDDR_A6

SDDR_A10

SDDR_A12

SDDR_A3

SDDR_A7

SDDR_A1

SDDR_BA0

SDDR_BA1

SDDR_RAS

SDDR_CAS

SDDR_CS

SDDR_WE

2

PR251 100*4/1005

PR252 100*4/1005

PR254 100*4/1005

RD272 100/1005

RD273 100/1005

PR257 100*4/1005

PR258 100*4/1005

PR260 100*4/1005

PR261 100*4/1005

RD274 100/1005

RD275 100/1005

PR262 100*4/1005

RD253 100/1005

RD257 100/1005

RD264 100/1005

RD269 100/1005

RD254 100/1005

RD255 100/1005

RD259 100/1005

RD261 100/1005

RD266 100/1005

RD267 100/1005

RD270 100/1005

RD271 100/1005

PR253 100*4/1005

PR255 100*4/1005

PR256 100*4/1005

RD256 100/1005

RD258 100/1005

RD260 100/1005

PR259 100*4/1005

RD277 100/1005

45

36

27

18

45

36

27

18

18

27

36

45

18

27

36

45

45

36

27

18

45

36

27

18

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

45

36

27

18

DDR2_D2

DDR2_D0

DDR2_D7

DDR2_D5

DDR2_D4

DDR2_D1

DDR2_D3

DDR2_D6

DDR2_D15

DDR2_D8

DDR2_D13

DDR2_D10

DDR2_D11

DDR2_D12

DDR2_D9

DDR2_D14

DDR2_D18

DDR2_D16

DDR2_D23

DDR2_D21

DDR2_D17

DDR2_D22

DDR2_D20

DDR2_D19

DDR2_D31

DDR2_D29

DDR2_D24

DDR2_D26

DDR2_D27

DDR2_D28

DDR2_D25

DDR2_D30

DDR2_DM0

DDR2_DM1

DDR2_DM2

DDR2_DM3SDDR_DM3

DDR2_DQS0

DDR2_DQS0#

DDR2_DQS1

DDR2_DQS1#

DDR2_DQS2

DDR2_DQS2#

DDR2_DQS3

DDR2_DQS3#

DDR2_A11

DDR2_A2

DDR2_A8

DDR2_A0

DDR2_A5

DDR2_A4

DDR2_A9

DDR2_A6

DDR2_A10

DDR2_A12

DDR2_A3

DDR2_A7

DDR2_A1

DDR2_BA0

DDR2_BA1

DDR2_D[31:0]

DDR2_DM0

DDR2_DM1

DDR2_DM2

DDR2_DM3

DDR2_DQS0

DDR2_DQS0#

DDR2_DQS1

DDR2_DQS1#

DDR2_DQS2

DDR2_DQS2#

DDR2_DQS3

DDR2_DQS3#

DDR2_A[12:0]

DDR2_BA0

DDR2_BA1

DDR2_RAS

DDR2_CAS

DDR2_CS

DDR2_WE

1

DDR2_D[31:0]

MAIN PWB(12/46)

DDR2_A[12:0]

CD287

102p/50V/1005

A A

CD285

102p/50V/1005

CD286

102p/50V/1005

CD289

102p/50V/1005

CD288

102p/50V/1005

CD291

102p/50V/1005

CD290

102p/50V/1005

CD293

102p/50V/1005

CD292

102p/50V/1005

CD295

102p/50V/1005

CD294

102p/50V/1005

CD296

102p/50V/1005

MAIN PWB ASS'Y(11/46)

[DDR Interface]

All location are from D251 to D320

5

CD297

105p/16V/1005

CD298

4

105p/16V/1005

CD299

226p/6.3V/2012

(No.YA705<Rev.001>)2-29 2-30(No.YA705<Rev.001>)

CD300

226p/6.3V/2012

3

HU-71100006

2

1

hb1_main_0612_9/48_0.0

Page 18

MAIN PWB CIRCUIT DIAGRAM (12/46) [DDR2 Memory]

5

DDR2_A[12:0]

D D

DDR2_D[31:0]

C C

MAIN PWB(11/46)

DDR2_BA0

DDR2_BA1

DDR2_CLK

DDR2_CLK_N

DDR2_CKE

DDR2_ODT

DDR2_CS

DDR2_RAS

DDR2_CAS

B B

DDR2_WE

DDR2_DM0

DDR2_DM1

DDR2_DM2

DDR2_DM3

DDR2_DQS0

DDR2_DQS0#

DDR2_DQS1

DDR2_DQS1#

DDR2_DQS2

DDR2_DQS2#

DDR2_DQS3#

DDR2_DQS3

DDR2_A0

DDR2_A1

DDR2_A2

DDR2_A3

DDR2_A4

DDR2_A5

DDR2_A6

DDR2_A7

DDR2_A8

DDR2_A9

DDR2_A10

DDR2_A11

DDR2_A12

DDR2_D0

DDR2_D1

DDR2_D2

DDR2_D3

DDR2_D4

DDR2_D5

DDR2_D6

DDR2_D7

DDR2_D8