Page 1

SERVICE MANUAL

CD RECEIVER

KD-LX333R

KD-LX333R

Contents

Safety precaution

Preventing static electricity

Disassembly method

Adjustment method

STDM

1-2

1-3

1-4

1-13

SOURCE

ATT

7

9

8

KD-LX333R

10

12

11

Flow of finctional operation intil opelation

until TOC read

Maintenance of laser pickup

Replacement of laser pickup

Description of Major ICs

OFF

Area Suffix

E

EX

Continental Europe

Central Europe

1-14

1-16

1-16

1-17~33

COPYRIGHT 2002 VICTOR COMPANY OF JAPAN, LTD.

No.49715

Jun. 2002

Page 2

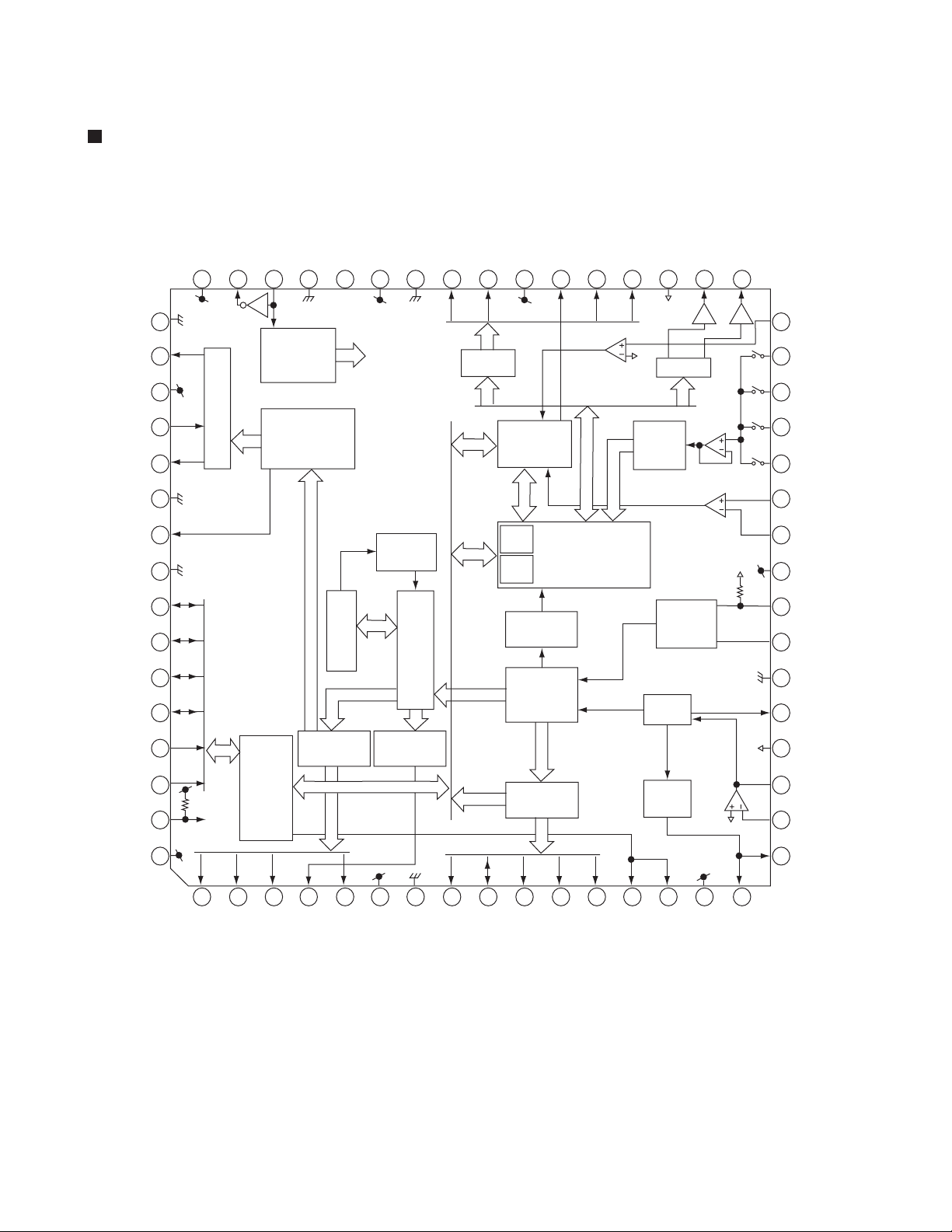

Description of major ICs

/

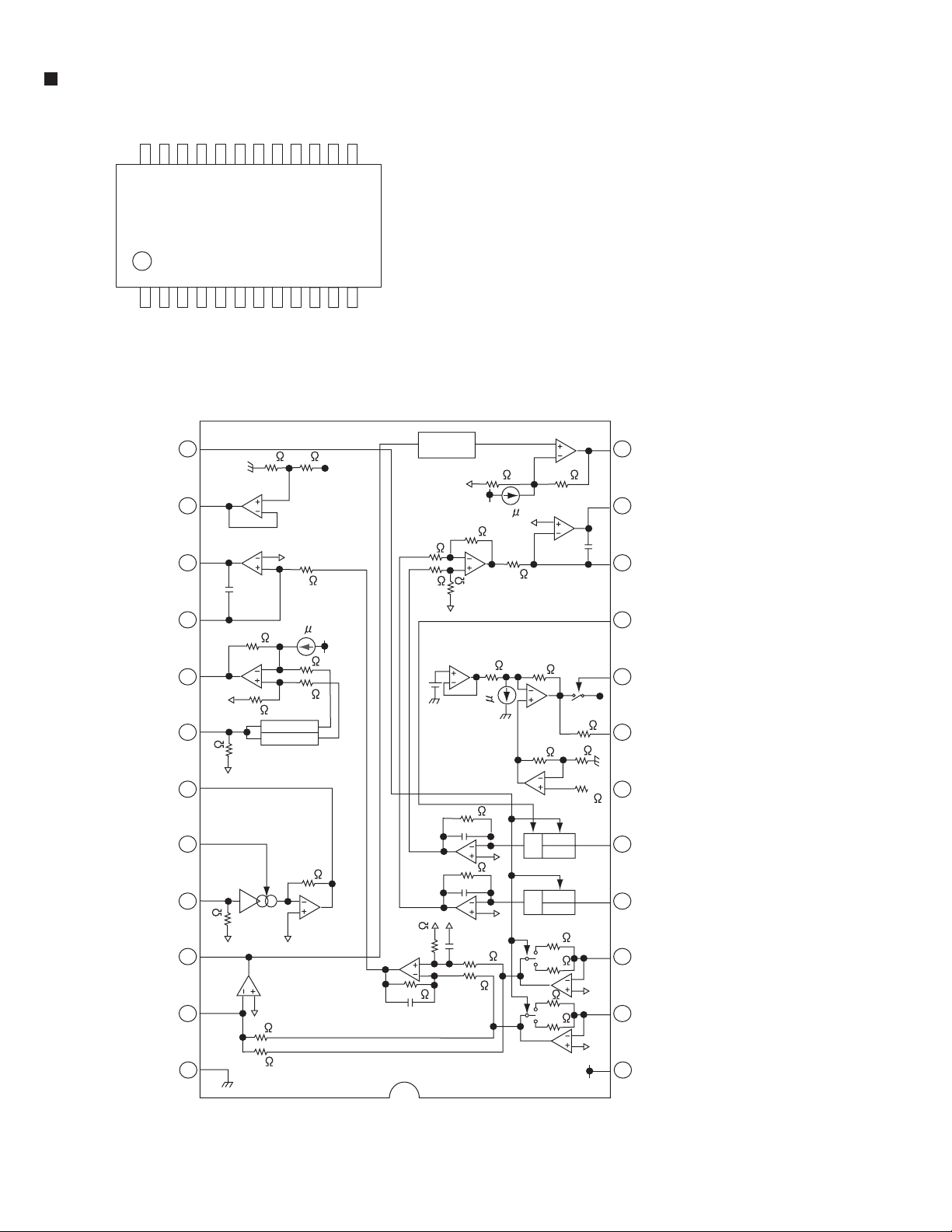

TC9490FA (IC521) : DSP & DAC

1.Pin layout & Block daiagram

KD-LX333R

DV

SS3

RO

DV

DD3

DVR

LO

DV

SS3

ZDET

SS5

V

BUS0

BUS1

BUS2

BUS3

BUCK

/CCE

/RST

VXDD3XOXI

SS3

XV

TEIN

DD3VSS3

V

DMO

FMO

DD3

AV

SEL

TEBC

RFGC

48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33

49

50

51

52

LPF

Clock

generator

1-bit

DAC

PWM

Servo control

A/D

53

54

55

56

Address

circuit

ROM

RAM

Digital equalizer

automatic

adjustment circuit

57

58

59

60

61

62

Micro-

controller

interface

circuit

Correction

Audio output

circuit

16k

RAM

Digital output

CLV servo

Sync signal

protection

EFM

Sub code

detector

63

VCO

PLL

TMAX

REF

V

D/A

Data

slicer

TRO

FOO

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

TEZI

TEI

SBAD

FEI

RFRP

RFZI

RFCT

DD3

AV

RFI

SLCO

SS3

AV

VCOF

REF

RV

LPFO

LPFN

64

DD5

V

17

TMAX

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

BCK

LRCK

AOUT

DOUT

IPF

DD3

V

V

SBOK

CLCK

DATA

SFSY

SBSY

/HSO

UHSO

DD3

PV

PDO

SS3

1-17

Page 3

KD-LX333R

2.Pin function (1/2)

Pin No.

1

2

3

4

Symbol

BCK

LRCK

AOUT

DOUT

5

6

7

8

9

10

11

12

13

14

VDD3

VSS3

SBOK

CLCK

DATA

SFSY

SBSY

/HSO

/UHSO

IPF

I/O

O

O

O

O

O

-

-

O

I/O

O

O

O

O

O

TC9490FA(2/3)

Function

Bit clock outputpin 32fs, 48fs, or 64fs selectable by command.

L/R channel clock output pin."L" for L channe and "H" for R channel.

Output polarity can be inverted by command.

Audio data output pin. MSB-first or LSB-first selectable by command.

Digital data output pin. Outputs up to double-speed playback.

Correction flag output pin.When set to "H",AOUT output cannot be corrected

by C2 correction processing.

Digital 3.3V power supply voltage pin.

Digital GND pin.

Subcode Q data CRCC result output pin."H" level when result is OK.

Subcode P-W data read clockI/O pin. I/O polarity selectable by command.

Subcode P-W data output pin.

Playback frame sync signal output pin.

Subcode block sync signal output pin. "H" level at S1 when subcode sync is

detected.

Playback speed mode flag output pins.

/HSO

H

H

L

--

H

L

L

--

Playback speed/UHSO

Normal

Double

4 times

---

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

PVDD3

PDO

TMAX

LPFN

LPFO

PVREF

VCOF

SS3

AV

SLCO

RFI

AV

RFCT

RFZI

RFRP

FEI

SBAD

TEI

TEZI

FOO

TRO

REF

V

-

PLL-only 3.3V power supply voltage pin.

O

EFM and PLCK phase difference signal output pin.

O

TMAX detection result output pin.

TMAX OutputTMAX Detection result

Longer than fixed period

Within fixed period

Shorter than fixed period

I

Inverted input pin for PLL LPF amp.

O

Output oin for PLL LPF amp.

-

PLL-only V

VCO filter pin.

O

Analog GND pin.

DAC output pin for data slice level generation.

O

RF signal input pin.Zin selectable by command.

I

Analog 3.3V power supply voltage pin.

RFRP signal center level input pin.

I

RFRP signal zero-cross input pin.

I

RF ripple signal input pin.

I

Focus error signal input pin.

I

Sub-beam adder signal input pin.

I

Tracking error input pin. Inputs when tracking servo is on.

I

Tracking error signal zero-cross input pin.

I

Focus equalizer output pin.

O

Tracking equalizer output pin.

O

Analog reference power supply voltage pin.

-

REF pin.

"PVDD3"

"HIZ"

"AV

SS3"

1-18

Page 4

KD-LX333R

2.Pin function (2/2)

Pin No.

36

37

38

39

40

41

42

43

44

45

Symbol

RFGC

TEBC

SEL

AV

FMO

DMO

V

V

TESIN

XV

46

47

48

49

XV

DV

50

51

52

DV

DVR

53

54

55

56

57

58

59

60

61

62

63

64

DV

ZDET

V

BUS0

BUS1

BUS2

BUS3

BUCK

/CCE

/RST

V

DD3

SS3

DD3

XI

XO

DD3

RO

DD3

LO

SS5

DD5

SS3

SS3

SS3

I/O

O

O

O

O

O

-

-

I

-

I

O

-

O

-

O

O

-

I/O

I

I

I

-

TC9490FA(3/3)

Function

RF amplitude adjustment control signal output pin.

Tracking balance control signal output pin.

APC circuit ON/OFF signal output pin. At laser on,high impedance with

UHS="L" ,H output with UHS="H".

Analog 3.3V power supply voltage pin.

Feed equalizer output pin.

Disc equalizer output pin.

Digital GND pin.

Digital 3.3V power supply voltage pin.

Test input pin. Normally,fixed to "L".

System clock oscillator GND pin.

System clock oscilatoe input pin.

System clock oscillator output pin.

System clock oscillator 3.3V power supply voltage pin.

DA converter GND pin.

R-channel data forward output pin.

DA converter 3.3V power supply pin.

Reference voltage pin.

L-channel data forward output pin.

DA converter GND pin.

1 bit DA converter zero data detection flag output pin.

Microcontroller interface GND pin.

Microcontroller interface data I/O pins.

Microcontroller interface clock input pin.

Microcontroller interface chip enable signal input pin.At "L".

Bus0 to BUS3 are active.

Reset signal input pin. At reset,"L".

Microcontroller interface 5V power supply pin.

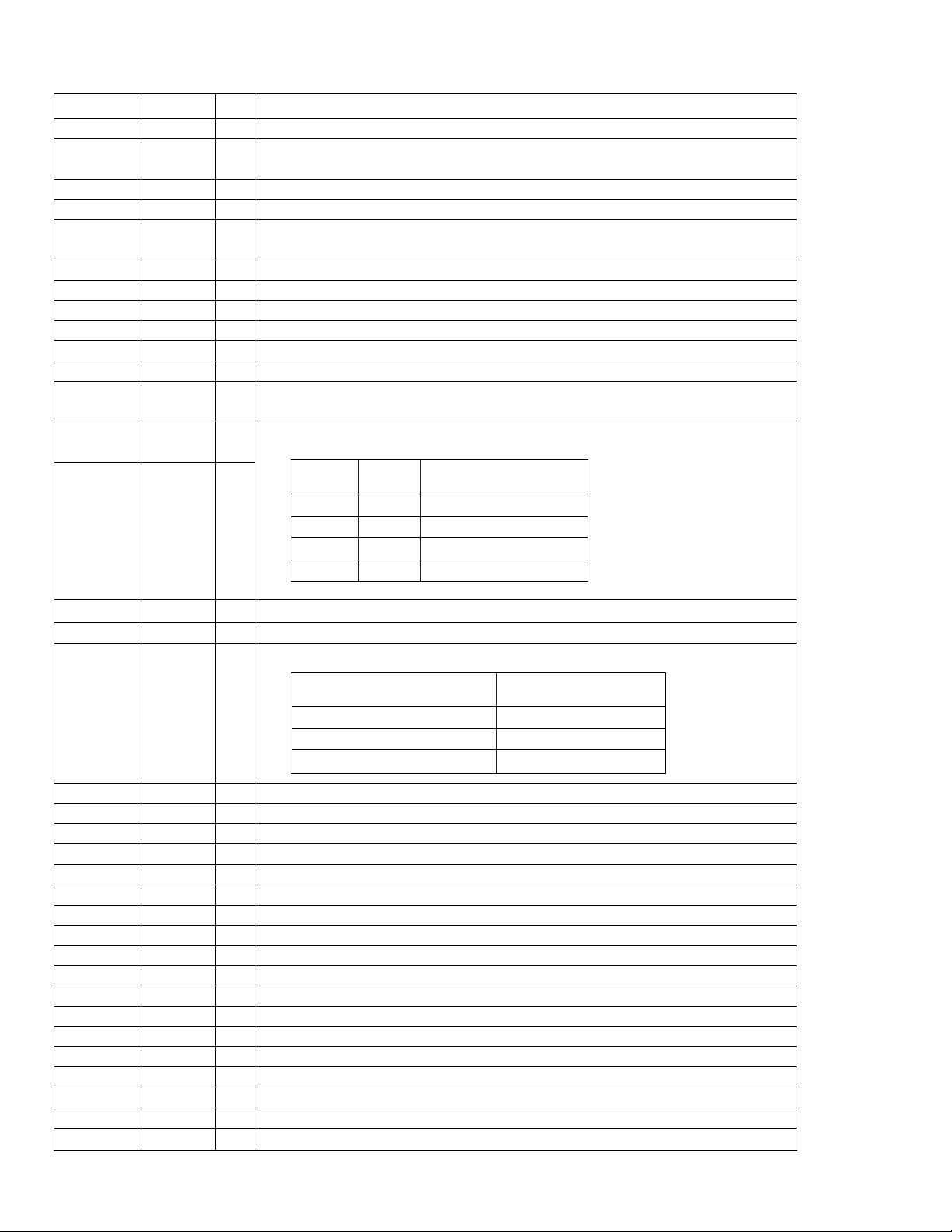

NJM4565MD (IC151,IC171,IC323) : Operational amp

+

A OUTPUT

-

A INPUT

+

A INPUT

V

1

2

3

-

4

8

V

B OUTPUT

7

B INPUT

-

6

5

+

B INPUT

1-19

Page 5

KD-LX333R

TA2147F-X (IC501) : RF amp.

1.Terminal layout

2.Block diagram

VRO

FEO

FEN

RFRP

RFRPIN

RFGO

RFGC

AGCIN

RFO

RFN

13GVSW

14

15

16

17

18

19

20

21

22

23

10pF

40k

30k

20k 20k

20k

20k

BOTTOM

3k

15k

50 A

12k

12k

PEAK

20k

180k

40pF

20k

20k

PEAK

1.3V

240k

180k

40k

40k

240k

15pF

15pF

40pF

60k

60k

50k

2k

20 A

20k

60 A

50k

14k

k

1

80k

80k

20k

20k

15k

x0.5

x2

x0.5

x2

1k

2k

1.75k

10pF

12 RFDC

11

TEO

10

TEN

TEBC

9

8

SEL

7

LDO

MDI

6

5

TNI

4

TPI

3

FPI

2

FNI

1-20

GND

24

3k

1

Vcc

Page 6

3.Pin function

Pin No.

1

2

3

4

5

6

7

8

Symbol

Vcc

FNI

FPI

TPI

TNI

MDI

LDO

SEL

I/O

Function

-

3.3V Power supply pin

I

Main-beam amp input pin

I

Main-beam amp input pin

I

Sub-beam amp input pin

I

Sub-beam input pin

I

Monitor photo diode amp input pin

O

Laser diode amp output pin

I

APC circuit ON/OFF control signal,laser diode (LDO) control signal input or

bottom/peak detection frequency change pin.

KD-LX333R

9

10

11

12

13

TEBC

TEN

TEO

RFDC

GVSW

APC

circuit

GND OFF

HIZ

Vcc

I

Tracking error balance adjustment signal pin

Adjusts TE signal balance by eliminating carrier component from

PWM signal(3-state output, PWM carrier = 88.2kHz) output from

TC9490F/FA TEBC pin using RC-LPF and inputting DC.

TEBC input voltage:GND~Vcc

I

Tracking error signal generation amp negative-phase input pin

O

Tracking error signal generation amp output pin.

Combining TEO signal and RFRP signal with TC9490F/FA configures

tracking search system.

O

RF signal peak detection output pin

I

AGC/FE/TE amp gain change pin

GND

HIZ

Vcc

Connected to Vcc

through 1k resistor

Control signal output

ON

Control signal output

ON

ModeGVSW

CD-RW

CD-DA

CD-DA

LDOSEL

14

15

16

17

18

19

20

21

22

23

24

VRO

FEO

FEN

RFRP

RFRPIN

RFGO

RFGC

AGCIN

RFO

RFN

GND

Reference voltage (VRO) output pin *VRO = 1/2 Vcc when Vcc = 3.3V

O

Focus error signal generation amp output pin

O

Focus error signal generation amp negative-phase input pin

I

Signal amp output pin for track count

O

Combining RFRP signal TEO signal with TC9490F/FA configures tracking

search system.

Signal generation amp input pin for track count

I

RF signal amplitude adjustment amp output pin

O

RF amplitude adjustment control signal input pin

I

Adjusts RF signal amplitude by eliminating carrier component from PWM

signal (3-state output, PWM carrier = 88.2kHz) output from TC9490F/FA

RFGC pin using RC-LPF and inputting DC.

*RFGC input voltage : GND-Vcc

RF signal amplitude adjustment amp input pin

I

RF signal generation amp output pin

O

RF signal generation amp input pin

I

GND pin

-

1-21

Page 7

KD-LX333R

F

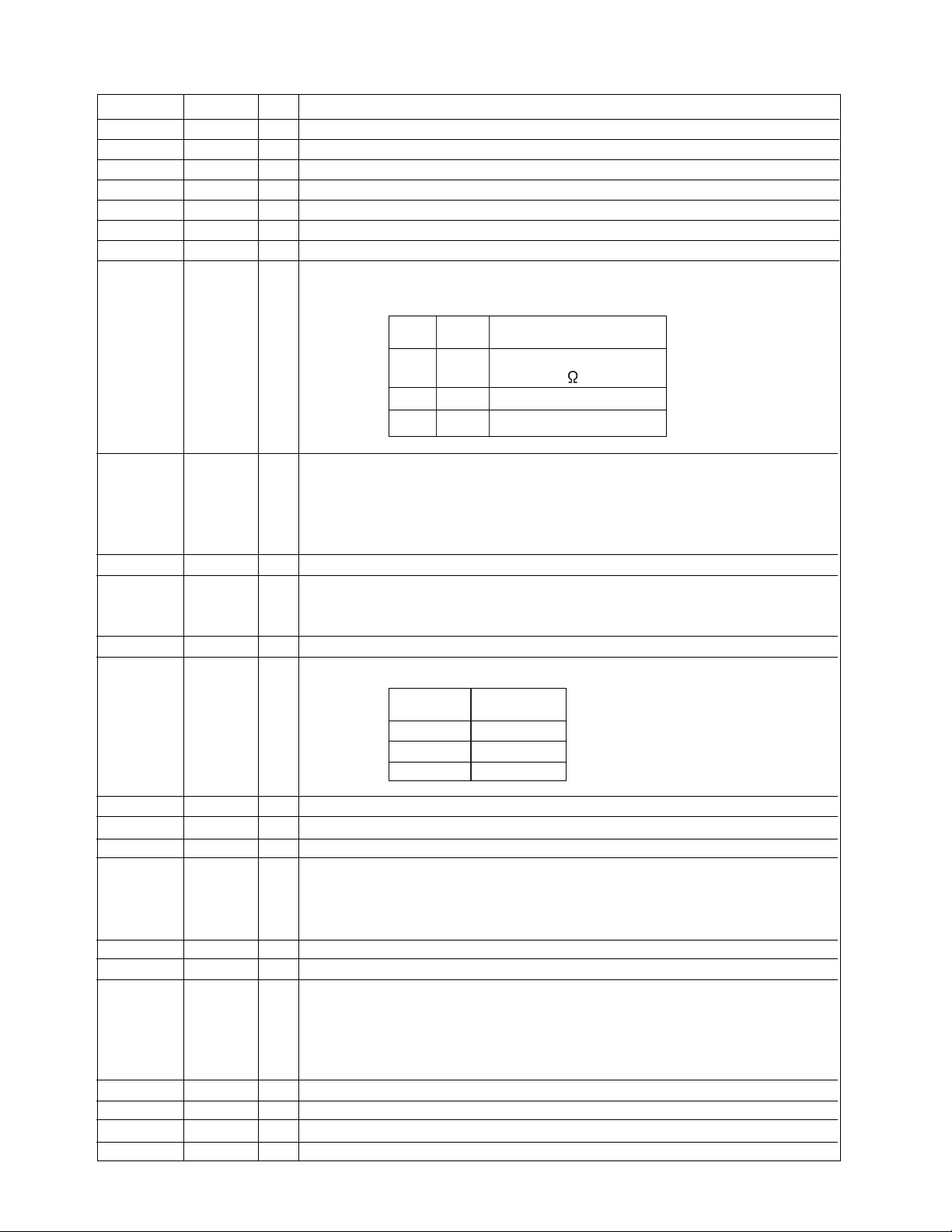

TA8273H (IC941) : Power amp

1.Block diagram

INRF

0.22 F

AC CONT1

INRR

0.22 F

+

Vcc 1/2 Vcc 3/4

2200 F 0.022

6 20

+

11

-

+

+

-

9

7

OUT RF+

OUT RF-

1

Protective

circuit

+

-

+

12

+

-

GND

8

OUTRR+

5

OUTRR-

3

GND

2

ST BY

REF

47 F

INLF

AC CONT2

PRE GND

INLR

+5V

ST ON

+

0.22 F

+

0.22 F

4

Stand by

Switch

Mute

10

+

Ripple

Filter

Mute

22

circuit

3.3 F

+

15

-

+

-

17

19

10K

+

OUTLF+

OUTLF-

Low Level

Mute ON

25

18

21

23

GND

OUTLR+

OUT LR-

13

14

Protective

circuit

-

+

+

-

1-22

ON TIME

22 F

Muting &

16

+

ON Time Control

Circuit

GND

24

Page 8

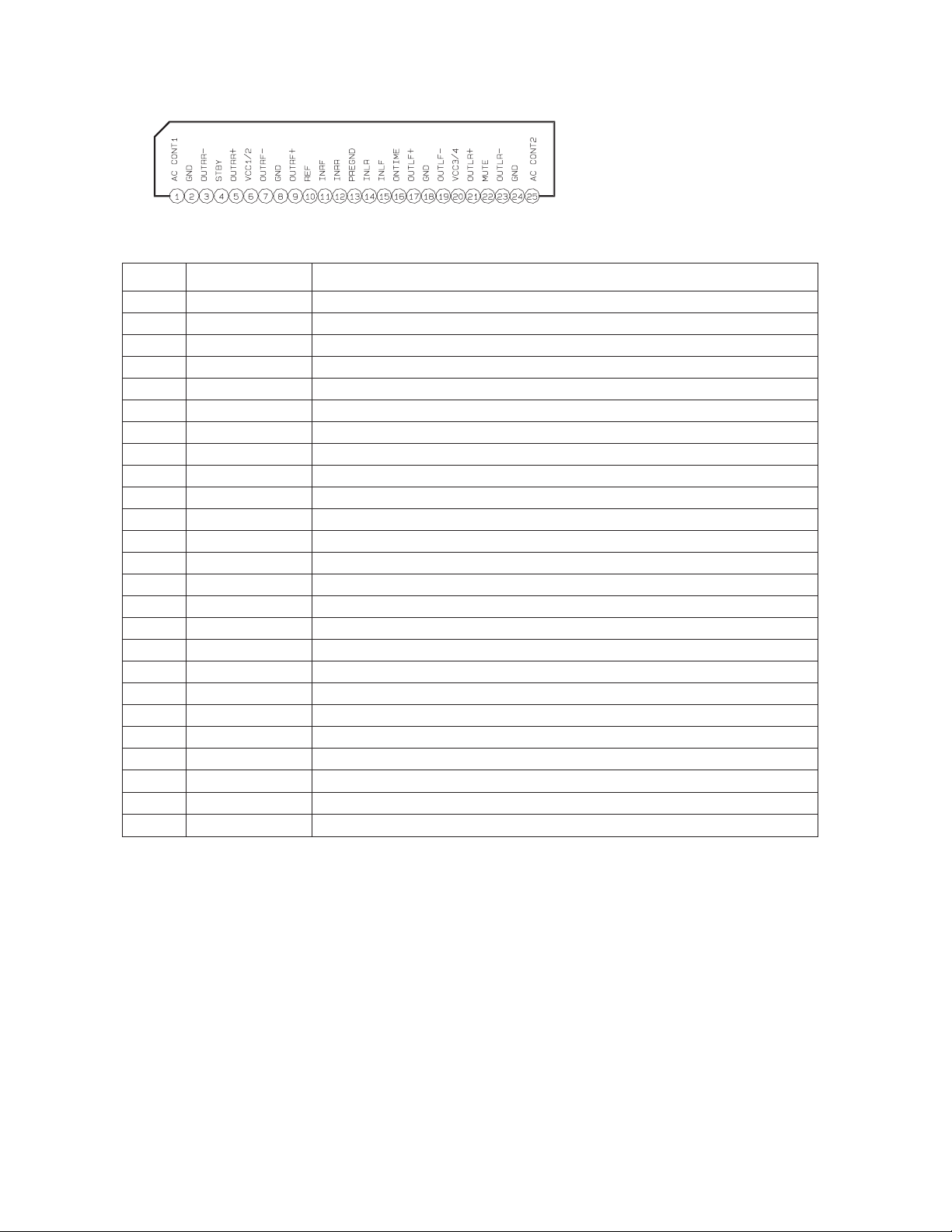

2.Terminal layout

KD-LX333R

3.Pin function

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

SymbolPin No. Function

AC CONT 1

GND

OUTRRSTBY

OUTRR+

VCC1/2

OUTRFGND

OUTRF+

REF

INRF

INRR

PREGND

INLR

INLF

ONTIME

OUTLF+

GND

OUTLFVCC3/4

OUTLR+

MUTE

OUTLRGND

AC CONT 2

Header of IC

Power GND

Outpur(-) for Rear Rch

Stand by input

Output (+) for Rear Rch

Power input

Output (-) for Front Rch

Power GND

Output (+) for Front Rch

Ripple filter

Front Rch input

Rear Rch input

Signal GND

Rear Lch input

Front Lch input

Power on time control

Output (+) for Front Lch

Power GND

Output (-) for Front Lch

Power input

Output (+) for Rear Lch

Muting control input

Output (-) for Rear Lch

Power GND

Header of IC

TA8273H

1-23

Page 9

KD-LX333R

UPD784217AGC168 (IC701) : Main micon

1.Pin layout

100 ~ 76

1

75

~

25

26 ~ 50

2.Pin functions(1/3)

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

Symbol

SW2

SW3

SW4

RST-SW

LMO

LM1

DIM-OUT

ILLUM1

VDD

X2

X1

VSS

XT2

XT1

RESET

SW1

BUS-INT

PS2

CRUISE

RDS-SCK

RDS DA

REMOCON

AVDD

AVREFO

TEM1

KEY0

KEY1

KEY2

LEVEL

MRC

SQ

SM

AVSS

W-VOL

DOT-CNT

AVREF

BUS-SI

BUS-SO

BUS-SCK

STAGE2

LCD-DA

LCD-SCK

~

51

I/O

Function

I

CD mechanical switch 2 detection signal input

I

CD mechanical switch 3 detection signal input

I

CD mechanical switch 4 detection signal input

I

Rest switch detection signal input

O

Motor signal control signal output at loading

O

Motor signal control signal output at leject

O

DIMMER pulse control output

O

POWER ON:H,FLAT PANEL:L

-

5V

-

-

-

GND

-

I

Reset detection teaminal

I

CD mechanical switch 1 detection signal input

I

J-BUS int

I

POWER SAVE2. Operating together with BACKUP.H input:STOP

I

Pulse signal for CRUISE input(only in 330R)

I

RDS clock input

I

RDS data input

I

Remocon input(111R:READY)

-

5V

-

5V

I

Temperature detection input

I

Key input 0

I

Key input 1

I

Key input 2

I

Level meter input

I

MRC output voltage detection

I

S.QUALITY level input

I

S.METER level input

-

GND

O

Subwoofer volume control analog output

O

Dot matrix contrast adjustment analog output

-

5V

I

J-BUS data input

O

J-BUS data output

I/O

J-BUS clock input and output

I

H:LX333R L:LX111R

O

Data output to LCD driver

O

Clock output to LCD driver

1-24

Page 10

2.Pin functions(2/3)

KD-LX333R

Pin No.

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

Symbol

LCD-CE1

BUZZER

12C-DAI

12C-DAO

12C-CLK

BUS-I/O

TMO

TM1

DMO

DM1

ST

NC

AFCK

C-SW1

C-SW2

C-SW3

C-SW4

C-SW5

VOL1

VOL2

SEEK/STP

NC

FM/AM

PLL-CE

PLL-DO

PLL-CLK

PLL-DI

TEL-MUTE

AMP-KILL

VSS

DIM -IN

PS1

POWER

CD-ON

MUTE

W-LPF1

W-LPF2

W-MUTE

VDD

VOL-DA

VOL-CLK

CF-SEL

GVSW

LCD RST

NC

DMK

TMK

NC

BUCK

CCE

RST

TEST

I/O

Function

O

Chip enable output 1 to LCD driver

O

Buzzer output

I

12C communication data input

O

12C communication data output

O

12C communication clock output

O

J-BUSI/O signal terminal

O

Tray motor negative signal output terminal

O

Tray motor positive signal output terminal

O

Motor control signal output in door down

O

Motor control signal output in door up

I

Stereo signal input L:Stereo

O

O

AF check output AF check:L

I

Chameleon machanical switch 1 detection signal input

I

Chameleon machanical switch 2 detection signal input

I

Chameleon machanical switch 3 detection signal input

I

Chameleon machanical switch 4 detection signal input

I

Chameleon machanical switch 5 detection signal input

I

Rotary volume signal 1 input

I

Rotary volume signal 2 input

O

Auto seek/stop selection output SEEK:L STOP:H

O

-

FM/AM selection output FM:H AM:L

O

IC control CE output

O

IC control data output

O

IC control clock output

I

IC control data input

I

Telephone mute detection input

O

POWER AMP ON/OFF selection output

-

GND

I

Dimmer detection input L:dimmer ON

I

Power save 1 Operating together with ACC.Power save :L Operating :H

O

Power ON/OFF selection output Power ON:H

O

CD power supply control signal output CD:H

O

Mute output MUTEON:L

O

Subwoofer cut off frequency control output 1

O

Subwoofer cut off frequency control output 2

O

Subwoofer mute output MUTE ON:H

-

5V

O

data output terminal

O

clock signal output terminal

O

FM band filter selection signal output

O

CD-DA/CD-RW selection control output CD-RW:L

O

Reset signal output to LCD driver

-

O

Door motor kick signal output

O

Tray motor kick signal output

-

O

Data cmmunication clock output with CDLSI

O

Data cmmunication clock CE with CDLSI

O

CDLSI reset signal output

-

GND

1-25

Page 11

KD-LX333R

+

+

-

-

+

+

-

-

-

+

+

2.Pin functions(3/3)

Pin No.

95

96

97

98

99

100

Symbol

BUSO

BUS1

BUS2

BUS3

DISCSEL

NC

I/O

Function

I/O

Data communication input and output port 0 with CDLSI

I/O

Data communication input and output port 1 with CDLSI

I/O

Data communication input and output port 2 with CDLSI

I/O

Data communication input and output port 3 with CDLSI

I

H:not for 8cm DISC L:for 8cm DISC

O

BA3220FV-X (IC301,IC401) : Line out amp

1.Pin layout

14

3220

17

8

2.Block diagram

1

CL-

14

LGND

13

REFL

2

Vcc

OUTL OUTR RGND

3

INL

1112

4

NFLCL+

10

REFR

FILTER

56

FIL

CR-

9

NFR

CR+

8

7

INR

1-26

Page 12

BD3860K (IC911) : E.Vol & Loud

1.Terminal layout

33 23

KD-LX333R

2.Block diagram

GND FIL VCC SEL1

6 5 9 40 36 35 343328323130 2919 15 14

POWER

SUPPLY

A1

41

B1

42

C1

43

D1

44

INPUT

1

2

3

4

SELECTOR

A2

B2

C2

D2

34

44

1 11

INPUT

GAIN

0 18 dB

INPUT

GAIN

0 18 dB

22

12

VIN1 LOUD1 HF1 LF1 DET1 TIN1 TNF1 BNF1

MAIN

VOLUME

0 -40 dB

LOUDNESS

MAIN

VOLUME

0 -40 dB

LOUDNESS

LOW(f=50Hz) 6dB

PROCESS CONTROL +3 to 12dB

(f=10kHz)

LOGIC

LOW(f=50Hz) 6dB

PROCESS CONTROL +3 to 12dB

(f=10kHz)

TREBLE

-14 +14dB

TREBLE

-14 +14dB

-14 +14dB

-14 +14dB

BASS

BASS

BOUT1VCA1 MIX1 BBOUT1

FADER

CH1 FRONT

0 -5 dB

FADER

CH1 REAR

0 -5 dB

FADER

CH2 REAR

0 -5 dB

FADER

CH2 FRONT

0 -5 dB

13

12

37

10

11

7

8

OUTF1

OUTR1

SI

SC

OUTR2

OUTF2

3.Pin function

Pin

Symbol Function

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

A2

B2

C2

D2

FIL

GND

SI

SC

VCC

OUTR2

OUTF2

OUTR1

OUTF1

BOUT1

BNF1

BOUT2

BNF2

TNF2

TNF1

TIN2

BBOUT2

MIX2

CH2 Input Pin A

CH2 Input Pin B

CH2 Input Pin C

CH2 Input Pin D

1/2 VCC Pin

Ground Pin

Serial Data Receiving Pin

Serial Clock Receiving Pin

Power Supply Pin

CH2 Rear Output Pin

CH2 Front Output Pin

CH1 Rear Output Pin

CH1 Front Output Pin

CH1 Bass Filter Setting Pin

CH1 Bass Filter Setting Pin

CH2 Bass Filter Setting Pin

CH2 Bass Filter Setting Pin

CH2 Treble Filter Setting Pin

CH1 Treble Filter Setting Pin

CH2 Treble Input Pin

CH2 BBE II Signal Output Pin

CH2 Output MIX Amplifier

Inverse Input Pin

39 38 37 25 24 26 23 22 21 20 18 17 16

Pin

Symbol Function

No.

23

24

25

26

27

28

29

30

BBOUT1

31

32

33

34

35

LOUD1

36

37

LOUD2

38

39

40

41

42

43

44

VCA2

LF2

HF2

DET2

DEF

DET1

TIN1

MIX1

VCA1

LF1

HF1

VIN1

VIN2

SEL2

SEL1

A1

B1

C1

D1

CH2 High Pass VCA Output Pin

CH2 Low Pass Filter Setting Pin

CH2 High Pass Filter Setting Pin

CH2 High Pass Attack/Release Time Setting Pin

BBE ON/OFF switching time constant pin

CH1 High Pass Attack/Release Time Setting Pin

CH1 treble Input Pin

CH1 BBE II Signal Output Pin

CH1 Output MIX Amplifier Inverse Input Pin

CH1 High Pass VCA Output Pin

CH1 Low Pass Filter Setting Pin

CH1 High Pass Filter Setting Pin

CH1 Loudness Filter Setting Pin

CH1 Main Volume Input Pin

CH2 Loudness Filter setting Pin

CH2 Main Volume Input Pin

CH2 Input Gain Output Pin

CH1 Input Gain output Pin

CH1 Input Pin A

CH1 Input Pin B

CH1 Input Pin C

CH1 Input Pin D

BOUT2BNF2TNF2TIN2BBOUT2MIX2VCA2DET2LF2HF2LOUD2VIN2SEL2

1-27

Page 13

KD-LX333R

BR24C32F-X (IC703) : EEPROM

1. Pin layout

Vdd WPIN SCL SDA

A0 A1 A2

3. Block diagram

A0 1

A1 2

A2 3

11bit

Address

decoder

GND

11bit

START

Control circuit

2. Pin function

Symbol

Vdd

GND

A0,A1,A2

SCL

SDA

WPIN

16kbit EEPROM allay

Slave Word

Address resister

STOP

I/O

Power supply.

GND

No use connect to GND.

I

Serial clock input.

I

Serial data I/O of slave and word address.

I/O

Write protect terminal.

I

8bit

Data

resister

Function

8 Vdd

7 WPIN

6 SCL

GND 4

High voltage osc circuit

Power supply

voltage det.

BU4066BCFV-X (IC322) : Quad analog switch

1. Pin layout & Block diagram

VDD C1 C4 I/O4 I/O3O/I4 O/I3

14 13 12 11 810 9

ACK

5 SDA

1-28

1234 756

I/O1 O/I1 O/I2 I/O2 VssC2 C3

Page 14

BU1923F (IC51) : RDS decoder

1. Pin layout

1

QUAL

RDATA

Vref

MUX

VDD1

VSS1

VSS3

CMP

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

RCLK

N.C.

XO

XI

VDD2

VSS2

T1

T2

KD-LX333R

2. Block diagram

4

MUX

3

Vref

5

VDD1

VSS1

VDD2

VSS2

12

11

Analog

Power supply

6

Digital

Power supply

100k

120k

100k

+

anti-aliasing

filter

PLL

57kHz

RDS/ARI

Reference

clock

PLL

1187.5Hz

VSS3

8th Switched

capacitor filter

Bi-phase

decoder

7

CMP

Measurement

circuit

8

comparator

Differential

decoder

16

1

2

RCLK

QUAL

RDATA

13

Xl

14

X0

RPM6938-SV4 (IC602) : Remote sensor

1.Block diagram

AMP

I/V

conversion

PD

magnetic shield

BPF

fo

trimming

circuit

AGC

Detector

10 9

T1

Vcc

Comp

T2

Vcc

22k

Rout

GND

1-29

Page 15

KD-LX333R

FAN8037 (IC581) : CD driver

1. Pin layout & Block diagram

48 47 46 45 44 43 42 41 40 39 38 37

2. Pin function

Pin

Symbol

No.

1

IN2+

2

IN2-

3

OUT2

4

IN3+

5

IN3-

6

OUT3

7

IN4+

8

IN4-

9

OUT4

10

CTL1

11

FWD1

12

REV1

13

CTL2

14

FWD2

15

REV2

16

SGND

17

FWD3

18

REV3

19

CTL3

20

SB

21

PS

22

MUTE

23

PVCC2

24

DO7-

1

2

3

4

5

6

7

8

9

10

11

12

13 14 15 16 17 18 19 20 21 22 23 24

Function

I/O

I

CH2 op-amp input(+)

I

CH2 op-amp input(-)

O

CH2 op-amp output

I

CH3 op-amp input(+)

I

Ch3 op-amp input(-)

O

CH3 op-amp output

I

CH4 op-amp input(+)

I

CH4 op-amp input(-)

O

CH4 op-amp output(+)

I

CH5 motor speed control

I

CH5 forward input

I

CH5 reverse input

I

CH6 motor speed control

I

CH6 forward input

I

CH6 reverse input

-

Signal ground

I

CH7 forward input

I

CH7 reverse input

I

CH7 motor speed control

I

Stand by

I

Power save

I

All mute

-

Power supply voltage

O

CH7 drive output(-)

M

s

S

w

C

M

s

S

w

C

M

s

S

w

C

T.S .D

D

D

D

D

D

D

STAND BY

ALL MUTE

POWER SAVE

Pin

No.

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

Symbol

DO7+

DO6-

DO6+

PGND2

DO5-

DO5+

DO4-

DO4+

DO3-

DO3+

PGND1

DO2-

DO2+

DO1-

DO1+

PVCC1

REGOX

REGX

RESX

VREF

SVCC

IN1+

IN1-

OUT1

36

35

34

33

32

31

30

29

28

27

26

25

Function

I/O

O

CH7 drive output(+)

O

CH6 drive output(-)

O

CH6 drive output(+)

-

Power ground2

O

CH5 drive output(-)

O

CH5 drive output(+)

O

CH4 drive output(-)

O

CH4 drive output(+)

O

CH3 drive output(-)

O

CH3 drive output(+)

-

Power ground1

O

CH2 drive output(-)

O

CH2 drive output(+)

O

CH1 drive output(-)

O

CH1 drive output(+)

-

Power supply voltage

I

Regulator feedback input

O

Regulator output

I

Regulator reset input

I

Bias voltage input

-

Signal supply voltage

I

CH1 op-amp input(+)

I

CH1 op-amp input(-)

O

CH1 op-amp output

1-30

Page 16

HA13164A (IC961) : Regulator

1.Terminal layout

123456789101112131415

KD-LX333R

2.Block diagram

ANT OUT

C3

0.1u

EXT OUT

C4

0.1u

ANT CTRL

CTRL

CD OUT

C5

0.1u

AUDIO OUT

C6

10u

11

12

10

BATT.DET OUT

9

COMPOUT

6

VDD OUT

4

SW5VOUT

5

14

UNIT R:

+B

ACC

ILMOUT

R1

C7

0.1u

C8

0.1u

C1

100u

VCC ACC

8

2

1

7

Surge Protector

BIAS TSD

15

3

TAB

note1) TAB (header of IC)

ILM AJGND GND

connected to GND

13

C2

0.1u

C:F

3.Pin function

Pin No. Symbol Function

1

2

EXTOUT

ANTOUT

Output voltage is VCC-1 V when M or H level applied to CTRL pin.

Output voltage is VCC-1 V when M or H level to CTRL pin and H level

to ANT-CTRL.

3

4

5

6

7

8

9

10

11

12

13

14

15

ACCIN

VDDOUT

SW5VOUT

COMPOUT

ANT CTRL

VCC

BATT DET

AUDIO OUT

CTRL

CD OUT

ILM AJ

ILM OUT

GND

Connected to ACC.

Regular 5.7V.

Output voltage is 5V when M or H level applied to CTRL pin.

Output for ACC detector.

L:ANT output OFF , H:ANT output ON

Connected to VCC.

Low battery detect.

Output voltage is 9V when M or H level applied to CTRL pin.

L:BIAS OFF, M:BIAS ON, H:CD ON

Output voltage is 8V when H level applied to CTRL pin.

Adjustment pin for ILM output voltage.

Output voltage is 10V when M or H level applied to CTRL pin.

Connected to GND.

1-31

Page 17

KD-LX333R

HD74HC126FP (IC771) : Changer control

OE1

A1

Y1

OE2

A2

Y2

Vss

1

2

3

4

5

6

7

HD74HC126

14

13

12

11

10

9

8

Vcc

OE4

A4

Y4

OE3

A3

Y3

NJM2100M (IC821) : Operational amp

A OUT

A IN+

A IN–

VEE

1

A

+–

2

B

+–

3

4

8

7

6

5

VCC

B OUT

B IN–

B IN+

M5282FP-X (IC321) : E. volume

1. Pin layout

1

2

3

4

5

3. Pin function

Pin

Symbol Function

No.

1

Vcc/2

2

Amp+IN

3

Amp-IN

4

Amp OUT

5

GND

6

7

VCA IN

8

9

VCA OUT

10

NC

Vc

Vcc

10

9

8

7

6

Vcc/2 output for microphone amp.

Microphone amp. positive input terminal.

Microphone amp. negative input terminal.

Microphone amp. output terminal.

Ground.

Non connection.

VCA input terminal.

VCA control terminal.

VCA output terminal.

Power supply.

2. Block diagram

10

1

2

3

457

9

8

1-32

Page 18

LC75878W (IC601) : LCD driver

1. Pin layout

100 ~ 76

KD-LX333R

2. Block diagram

OSC

VLCD

VLCD0

VLCD1

VLCD2

VLCD3

VLCD4

VDD

VSS

1

~

25

26 ~ 50

P1

GENERAL

PORT

CLOCK

GENERATOR

CONTRAST

ADJUSTER

P4

75

~

51

COM1

COMMON

DRIVER

COM8

S75/COM9

S74/COM10

S73

SEGMENT DRIVER & LATCH

CONTROL

REGISTER

SHIFT REGISTER

CCB

INTERFACE

S1

3. Pin function

No. Symbol

1~73

76~83

84~87

100

74

75

88

89

90

91

92

93

94

95

96

97

98

99

SEG1~SEG73

SEG74

SEG75

COM8~COM1

P1~P4

VDD

VLCD

VLCD0

VLCD1

VLCD2

VLCD3

VLCD4

VSS

OSC

LCD RESET

CE

CL

DI

DI

INH

I/O

O

Segment driver output pin.

O

Segment driver output pin.

O

Segment driver output pin.

O

Common driver output pin.

O

General-purpose output pin.

-

Logic block power supply pin.

-

LCD driver power supply pin.

O

LCD driver bias 4/4 voltage (H-level) power pin.

I

LCD driver bias 3/4 voltage (intermediate level) power pin.

I

LCD driver bias 2/4 voltage (intermediate level) power pin.

I

LCD driver bias 1/4 voltage (intermediate level) power pin.

I

LCD driver bias 0/4 voltage (L-level) power pin.

-

Power supply pin to connect to ground.

I/O

Oscillator pin.

I

Display off, general-purpose output port L fixed input pin.

I

Chip enable

I

Synchronization clock

I

Transfer data

Function

CL

CE

1-33

Page 19

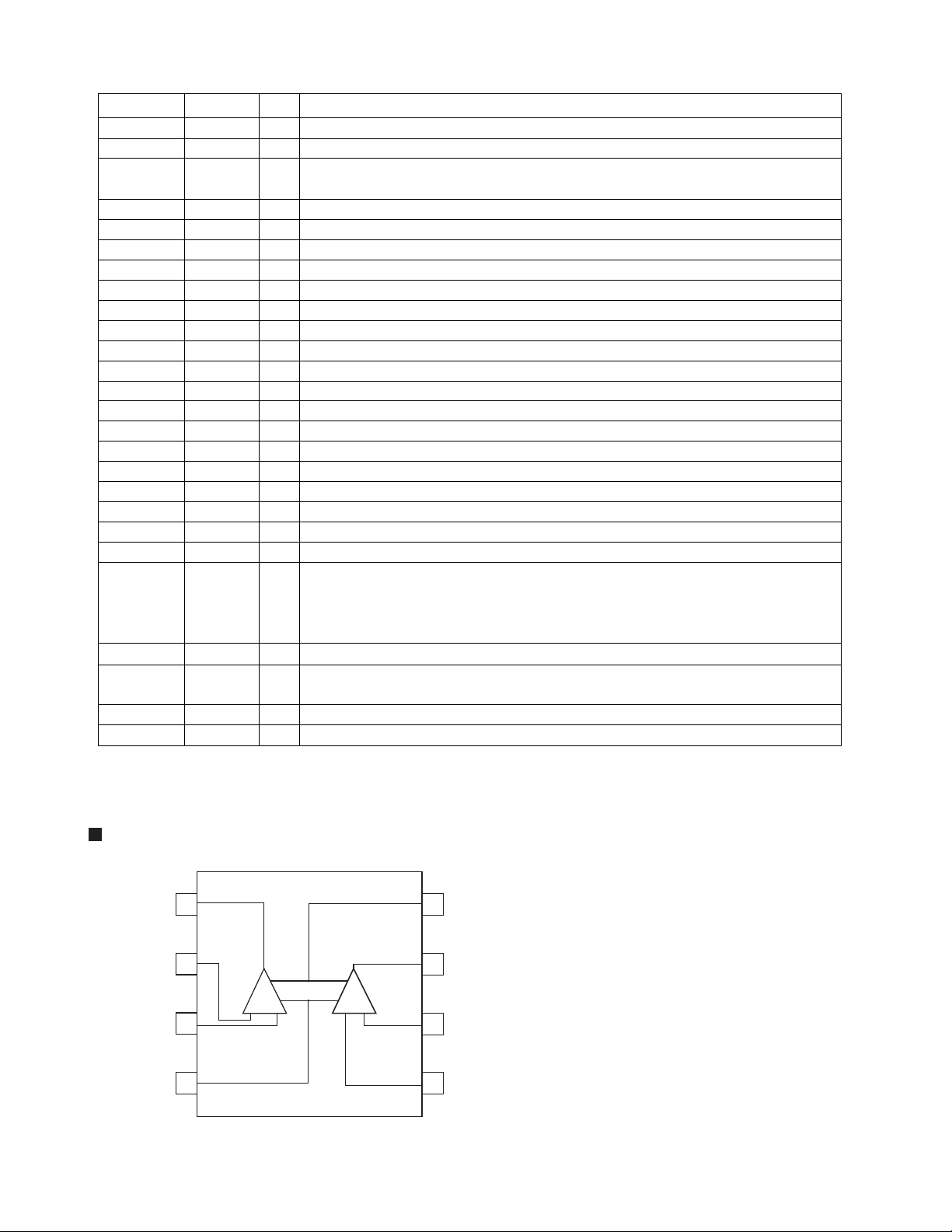

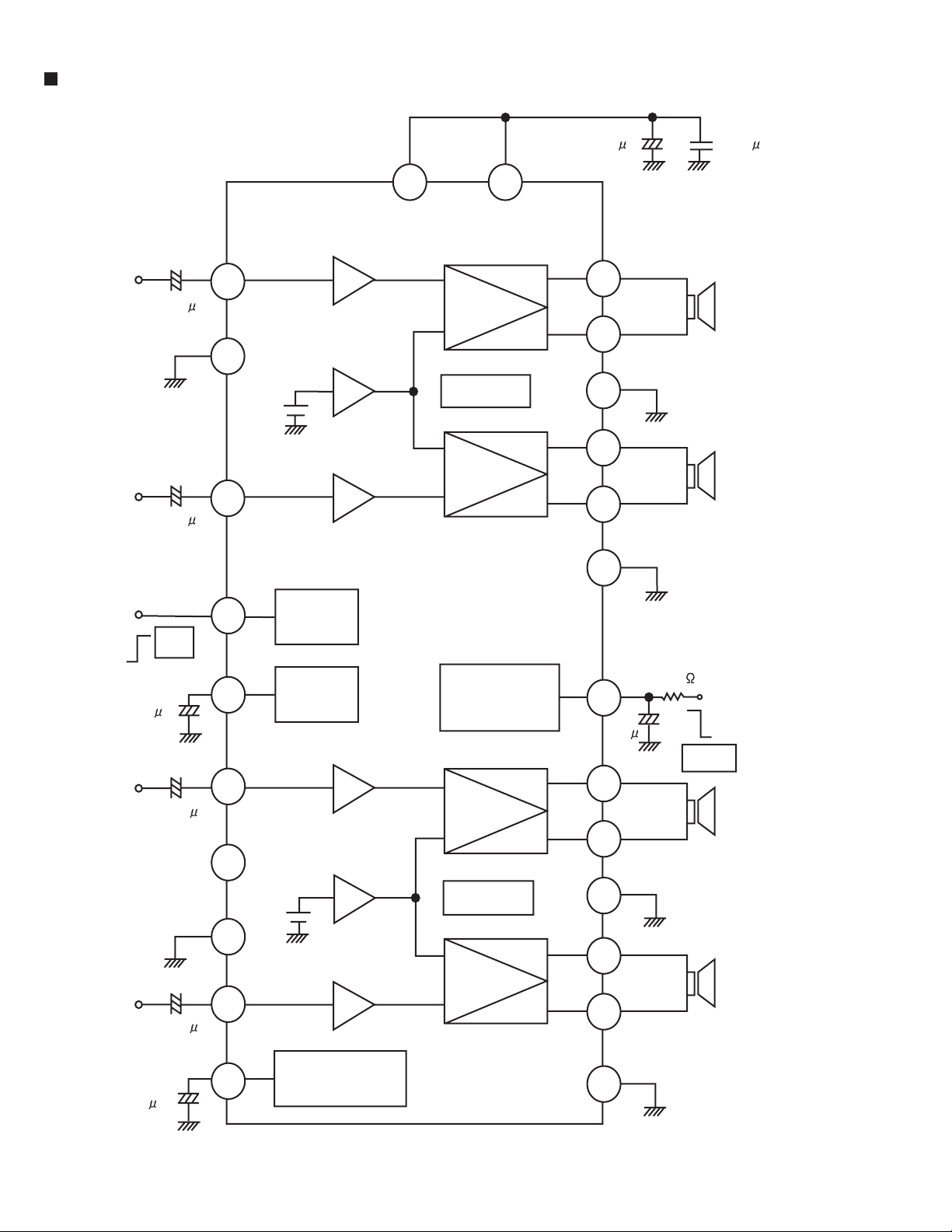

Block diagram

KD-LX333R

IC151

CD LPF

L-CH

R-CH

J1

TU1

TUNER PACK

FM/AM

S.METER

SEEK/STOP

SD/ST

PLLCE

PLLD1

PLLCL

L-CH

R-CH

FMDET.ADJ

IC51

RDS

RDSDA

RDSSCK

AMAF

IC701

CPU

IC911

CD-L

CD-R

VOL-DA

VOL-CLK

DA1

CLK

BUSSI/BUSSO BUSINT,BUSSCK

RESET

E.VOLUME

IC703

EPROM

IC951

REGULATOR

VCC

LOUTF

LOUTR

LOUTF

LOUTR

IC702

RESET

IC771

JVCBUS

IC361

Lch

IC461

Rch

INFL

INFR

INFL

INFR

IC941

POWER AMP

IC961

REGULATOR

REAR L

REAR R

OUTFL ,OUTFR

OUTFL ,OUTFR

ACC

CH-L

CHR

Front speaker

Rear speaker

CN901

BATT

Line out

CN301

CN771

BUS0

BUS1

BYS2

BUS3

BUCK

CCE

RST

IC521

DSP&DAC

FOO

FRD

DMO

FMO

DOOR TRAY

CN503 CN504

CASW1

CASW2

CASW3

CN704

SLE,TEB,RFDC,RFBC

TE,RFBO,RFRP,FEO

IC581

CD&TRAY/DOOR

LOADINGDRIVER

IC501

RF AMP

VA,VB,VC

MD,LC

TR SP FE

LO FO

LCDDA,LCDDL,LCDCF1,LCDCE2,LCDRST

RSET,REMOCON,KEY1,KEY2

CN501

CD MECHA

CN701

CN601

REMOCON

LCDRST,LCDCE1

LCDCL,LCDDA

KEY2

INV

KEY0

KEY1

CN702

CN631

KEY0

KEY1

IC603

REMOCON

KEY SWITCH

IC601

LCD DRIVER

LED

LCD

2-1

Page 20

A

Standard schematic diagram

Main amp section

KD-LX333R

KD-LX333R

Parts are safety assurance parts.

When replacing those parts make

sure to use the specified one.

TUNER SIGNAL

CD SIGNAL

CD CHANGER SIGNAL

FRONT SIGNAL

REAR SIGNAL

D

2-2

Page 21

KD-LX333R

KD-LX333R

Parts list (General assembly)

Item

A

1 DG4152010

2 DG3070010

3 DG3005030

4 DG3007010

5 DG4117000

6 YM2626001

7 XT2640BSC

8 EX0000490

12 XT2640BSC

13 DG3111000

14 FU15R0031

15 DG3089020

16 DG4090030

17 DG4091020

18 DG3092030

19 EX0000495

20 EX0000535

21 DG1002011

22 DG4114000

23 ---------------

24 XT2640BSC

25 DG4003030

26 XT2040PSB

27 DG4154010

28 DG1069001

29 DG4004000

30 XM2030PSB

32 EX0000508

33 DG3010010

37 DG3014000

38 DG4023010

39 YM2029000

40 YM2626000

41 DG4112010

44 DG3015000

51 DG3022000

52 DG3131030

79 DG4087040

80 YWP020300

81 DG3038001

82 YWP020301

83 DG4039000

84 DG4041000

86 DG3038002

88 DG4054000

89 DG4055000

90 DG3056000

93 000013660

Parts number Parts name Area

Q'ty

SHEET (WIRE)

REG.IC BRACET

REAR BRACKET

REAR HEAT SINK

POWER IC BKT 2

SCREW

SCREW

RCA CORD ASSY

SCREW

LEAD PLATE

AUTO FUSE (15A)

LCD CASE

LCD FILTER

ZEBRA CONTACT

LIGHTING CASE

6P FLAT CABLE

16P FLAT CABLE

CHASSIS TOP

INSULATOR

CD MECHA

SCREW

FFC P.MECHA 1

SCREW

SHEET (FFC)

FRONT COVER

BLIND

SCREW

WIRE ASS'Y

BOTTOM ASSY

INSULATOR

BUTTON B. GUIDE

SCREW

SCREW

PANEL COVER ASS

DOOR BASE ASSY

ROD GEAR

MOVE BKT ASS'Y

LEVER SPRING

C.WASHER

CLUTCH ASSY

C.WASHER

GEAR-4

GEAR-5

CLUTCH ASSY

GEAR-1

GEAR-2 1

GEAR-3

FEED MOTER

1

1

1

1

1

3

1

1

2

1

1

1

1

2

1

1

1

1

1

CHASSIS TOP

1

3

QYSDST2604Z

2

QYSPST2004M

1

1

1

LV40828-002A

2

QYSPSP2003M

1

1

1

1

LV41545-001A

1

3

1

1

LV31605-001A

1

LV31610-001A

1

1

7

1

LV30981-005A

2

1

LV41466-001A

1

LV41467-001A

1

LV30981-007A

1

LV41463-001A

LV41464-001A

1

LV31611-001A

1

QAR0029-001

Description

Block No. M1MM

Parts list (General assembly)

Item

A

95 KA2502011

97 000013680

99 KA2502012

100 XP2020P1C

101 DG3151000

106 DG3058000

107 DG4116010

108 DG1140013

109 DG2141011

110 DG2142020

111 DG1139000

112 DG4026030

113 YM1701004

114 DG1122002

115 DG4130000

116 DG4136000

117 DG3027010

118 DG3102010

121 DG4125000

122 DG4061010

125 DG4060000

126 DG3143010

134 DG4104000

135 DG3148000

136 DG3126020

137 YM1701001

138 DG3024000

139 DG4071020

140 YM2029000

141 DG4029010

142 XP1728P3B

143 YM2029000

144 XT2640BSC

145 YM2626002

146 YM2626000

147 DG3008000

148 XT26A0BPC

150 DG4115000

151 PLN125100

152 PLC013500

153 LV40847-002A

156 DG4155000

LCD 1 000101490

Parts number Parts name Area

Q'ty

2P CONECTOR ASSY

MOTOR

2P CONECTOR ASSY

SCREW

PUSH LEVER ASSY

FFC GUIDE

SHEET (FRONT BK

PANEL (BUTTON)

BUTTON (FUNC)

BUTTON (PRESET)

BUTTON BASE

PLATE SPRING

MINI SCREW

DISPLAY PANEL

SPACER (UP,DOWN

SPACER E

D,P, PLATE

FINDER ASSY

SPACER (P)

UP DOWN BUTTON

REMOTE LENS

KNOB VOL ASSY

ENCODER GUIDE

ENCODER PLATE 1

KNOB SPRING

MINI SCREW 4

BUTTON BASE BKT

BUTTON B SUPORT

SCREW

TENS SPRING BTM

SCREW

SCREW

SCREW

SCREW 1

SCREW

SIDE HEAT SINK

SCREW

SHEET 2

NAME LABEL 1

LASER CAUTION 1

SPACER 2

SHEET(F.CVOER)

LCD 1

1

1

QAR0188-001

1

4

1

1

1

1

1

1

1

1

LV41825-004A

6

VKZ4777-004

1

1

LV40846-005A

1

1

LV32035-001A

1

1

LV40848-009A

1

LV41469-001A

1

LV41505-001A

1

1

1

VKZ4777-001

1

1

3

2

LV41452-003A

4

4

8

1

1

1

LV41843-001A

1

Block No. M1MM

Description

3-4

Page 22

KD-LX333R

Parts list (CD mechanism)

Item

A

1 30310101T

2 30310103T

3 303101073T

4 30310108T

5 30310164T

6 30310143T

7 30310154T

8 30310112T

9 30310155T

10 30310115T

11 30310116T

12 30310134T

13 30310159T

14 30310150T

15 30310156T

16 30310138T

17 30310122T

18 30310148T

19 30310125T

20 30310149T

22 30310151T

23 30310129T

29 30300510T

32 30310544T

33 30310547T

36 30310546T

38 30310533T

39 30310577T

40 30310512T

41 30310558T

42 30310514T

43 30310552T

44 30310541T

45 30310566T

48 30310557T

49 30310524T

50 30310525T

51 30310545T

56 64180405T

57 QAL0230-001

61 30311035T

62 19501403T

63 30311045T

64 30311044T

65 30311038T

66 30311039T

67 30311040T

68 30311041T

Parts number Parts name Area

FRAME

DANPER PIN

UPPER PL(3)

SEL STOP PLATE

SEL ARM (L8)L

SEL ARM (R)L

S ARM SPRING(L8

TRIG LEVER

TRIG PL(Z)

TRIG PL SPRING

TRIG ARM

FIX ARM (L)B

FIX ARM (R)Z

FIX PL (L)Z

FIX PL (R) Z

LDG GR (6)B

LDG GEAR (6)SP

S.L ARM(N)

S.L ARM SPRING

REAR DAM BKT(Z)

HUNG UP SP (FZ)

HUNG UP SP (R)

PU GEAR(B)

F.M.BASE(Z)

FD GR BLK(Z)

PU GUIDE(Z)

THRUST SPR(M)

PU M NUT(Z-S)

NUT PUSH SPR PL

CLP ARM(Z)

CLP ARM SPRING

CLAMPER(Z)

8CM STOPPER(M)

8CM STOP SPP Z

CLAMPER PLATE(Z

DAMPER (J)

CLP ARM SPR (L)

F SCREW GUIDE(Z

DET SW

C.D PICK (SONY)

FPC HOLDER(Z)

WIRE CLAMPER

PICK UP FPC(Z-S

CONNECT.PCB(Z-S

WIRE (5P-Z)

WIRE (LD-Z)

WIRE (FD-Z)

WIRE (RS-Z)

Q'ty

1

2

1

1

1

1

2

1

1

1

1

1

1

1

1

1

1

1

1

1

2

2

1

1

1

1

1

1

1

1

1

1

1

1

1

3

1

1

1

ESE11SF4

1

1

4

1

1

1

1

1

1

Block No. MBMM

Description

3-6

Page 23

LX-333R

Parts list (CD mechanism)

Item

A

70 64180402T

71 64180403T

72 68150232T

79 30311105T

80 30311138T

81 30311109T

82 30311110T

84 30311112T

86 30311131T

88 30311118T

89 30311119T

90 30311123T

91 30311124T

92 30311129T

93 30311140T

100 9C0620503T

101 9C2020401T

102 9C4320403T

103 9C0117223T

104 9C0917703T

105 9C0320201T

106 9C4920013T

107 9C4920603T

108 9P0220031T

110 9C0420253

113 9W0330276

116 9W0725030T

117 9W0640030T

130 303105310T

131 303105311T

132 303105312T

133 303111301T

134 303111302T

135 303105502T

Parts number Parts name Area

DET SWITCH

DET SWITCH

CONNECTOR

SOPPORT PLATE

GR MT BLK(N)

LDG GEAR (2)

LDG GEAR (3)

LDG GEAR (5)

LDG ROLLER

L.P SPRING (L)

L.P SPRING (R)

SW PCB

SW ACTUATOR

LDG BELT

FRONT BRKT (J)

C B TAP SCREW

C SCREW TS.G

C B TAP SCREW

SCREW

C TAP SCREW S3

C TAP SCREW S3

C TAP SCREW S3

C TAP SCREW B3

TAMS SCREW

C TAP SCREW

NW BLUE

LUMILAR W

WASHER

FEED MO ASSY

SPINDLE MO ASSY

FEED SCREW ASSY

LDG MOTOR ASSY

RDG RLR SFT ASY

T.T.BASE ASSY

Q'ty

2

2

1

1

1

1

1

1

2

1

1

1

1

1

1

2

5

4

2

1

1

2

4

2

1

2

1

1

1

1

1

1

1

1

Block No. MBMM

Description

ESE22MH1

ESE22MH3

TKC-W26X-C1

M2X5

M2X4

M2X4

M1.7X2.2

M1.7X7

M2X2

M2X10

M2X6

M2X3

M2X2.5

2.9X5X0.3

2.3X9.8X0.25

1.4X3.2X0.4

3-7

Page 24

KD-LX333R

ea

ea

Electrical parts list (Main board)

Item

A

BZ791 000393760 BUZZER CD11PA-XZ

CN301 KN2507297 CONN.TERMINAL 7P BASE POST

CN302 KN2506297 CONN.TERMINAL 6P BASE POST

CN501 KZ042260L CONN.TERMINAL 26P CONNECTOR

CN503 KN2502091 CONN.TERMINAL 2P BASE POST

CN504 KN2502091 CONN.TERMINAL 2P BASE POST

CN701 KZ041160L CONN.TERMINAL 16P FPC CONNECT

CN702 KZ040060L CONN.TERMINAL 6P FPC CONNECTO

CN704 KN530409L CONN.TERMINAL 4P BASE POST

CN771 KX0040800 CONN.TERMINAL 8P BUS CONNECTO

CN901 KX0071600 CONN.TERMINAL DC CONNECTOR (1

C1 CY473623J C.CAPACITOR 0.047 MF

C103 CY153623J C.CAPACITOR 0.015 MF

C11 CY103623J C.CAPACITOR 0.01 MF

C112 CE1056468 E.CAPACITOR 1 MF/50V

C113 CE4754468 E.CAPACITOR 4.7 MF/25V

C116 CY222623J C.CAPACITOR 0.0022MF

C118 CY472623J C.CAPACITOR 0.0047MF

C119 CE1063468 E.CAPACITOR 10 MF/16V

C120 CZ4716D2J C.CAPACITOR 470 PF

C123 CZ2216D2J C.CAPACITOR 220 PF

C13 CY103623J C.CAPACITOR 0.01 MF

C133 CE4754468 E.CAPACITOR 4.7 MF/25V

C14 CY473623J C.CAPACITOR 0.047 MF

C141 CE1056468 E.CAPACITOR 1 MF/50V

C142 CE1056468 E.CAPACITOR 1 MF/50V

C143 CZ3316D2J C.CAPACITOR 330 PF

C144 CZ3316D2J C.CAPACITOR 330PF

C151 CE4754468 E.CAPACITOR 4.7 MF/25V

C152 CY122623J C.CAPACITOR 0.0012MF

C153 CZ1216D2J C.CAPACITOR 120PF

C154 CZ1016D2J C.CAPACITOR 100PF

C155 CE4760468 E.CAPACITOR 47 MF/6.3V

C156 CE1071468 E.CAPACITOR 100 MF/10V

C161 CE1056468 E.CAPACITOR 1 MF/50V

C162 CE2263468 E.CAPACITOR 22 MF/16V

C163 CY473623J C.CAPACITOR 0.047 MF

C164 CY224122J C.CAPACITOR 0.22MF

C172 CE1063468 E.CAPACITOR 10 MF/16V

C173 CE2260468 E.CAPACITOR 22 MF/6.3V

C174 CY223623J C.CAPACITOR 0.022 MF

C175 CE4760468 E.CAPACITOR 47 MF/6.3V

C2 CE4763468 E.CAPACITOR 47 MF/16V

C203 CY153623J C.CAPACITOR 0.015 MF

C21 CZ3316D2J C.CAPACITOR 330 PF

C212 CE1056468 E.CAPACITOR 1 MF/50V

C213 CE4754468 E.CAPACITOR 4.7 MF/25V

C216 CY222623J C.CAPACITOR 0.0022MF

C218 CY472623J C.CAPACITOR 0.0047MF

C219 CE1063468 E.CAPACITOR 10 MF/16V

C22 CY103623J C.CAPACITOR 0.01 MF

C220 CZ4716D2J C.CAPACITOR 470PF

C223 CZ2216D2J C.CAPACITOR 220 PF

C23 CY472623J C.CAPACITOR 0.0047MF

C233 CE4754468 E.CAPACITOR 4.7 MF/25V

C24 CY104423J C.CAPACITOR 0.1 MF

C241 CE1056468 E.CAPACITOR 1 MF/50V

C242 CE1056468 E.CAPACITOR 1 MF/50V

C243 CZ3316D2J C.CAPACITOR 330PF

C244 CZ3316D2J C.CAPACITOR 330 PF

C25 CY474122J C.CAPACITOR 0.47 MF

C251 CE4754468 E.CAPACITOR 4.7 MF/25V

C252 CY122623J C.CAPACITOR 0.0012MF

Parts number Parts name Ar

Block No. 01

Remarks

Item

A

C253 CZ1216D2J C.CAPACITOR 120 PF

C254 CZ1016D2J C.CAPACITOR 100PF

C272 CE1063468 E.CAPACITOR 10 MF/16V

C273 CE2260468 E.CAPACITOR 22 MF/6.3V

C3 CY103623J C.CAPACITOR 0.01 MF

C301 CE4754468 E.CAPACITOR 4.7 MF/25V

C302 CE4754468 E.CAPACITOR 4.7 MF/25V

C303 CE4763468 E.CAPACITOR 47 MF/16V

C305 CE4754468 E.CAPACITOR 4.7 MF/25V

C306 CE4754468 E.CAPACITOR 4.7 MF/25V

C307 CE1071468 E.CAPACITOR 100 MF/10V

C308 CE4754468 E.CAPACITOR 4.7 MF/25V

C309 CE4754468 E.CAPACITOR 4.7 MF/25V

C310 CE1071468 E.CAPACITOR 100 MF/10V

C321 CE1063468 E.CAPACITOR 10 MF/16V

C322 CY103623J C.CAPACITOR 0.01 MF

C323 CE4763468 E.CAPACITOR 47 MF/16V

C324 CE1063468 E.CAPACITOR 10 MF/16V

C325 CE2256468 E.CAPACITOR 2.2 MF/50V

C326 CY682623J C.CAPACITOR 0.0068MF

C327 CY823423J C.CAPACITOR 0.082 MF

C329 CE2256468 E.CAPACITOR 2.2 MF/50V

C330 CY123623J C.CAPACITOR 0.012MF

C331 CY562623J C.CAPACITOR 0.0056MF

C332 CY273623J C.CAPACITOR 0.027MF

C333 CY273623J C.CAPACITOR 0.027MF

C334 CY333623J C.CAPACITOR 0.033MF

C335 CE2256468 E.CAPACITOR 2.2 MF/50V

C336 CY473623J C.CAPACITOR 0.047 MF

C337 CY473623J C.CAPACITOR 0.047 MF

C351 CY104423J C.CAPACITOR 0.1 MF

C352 CY103623J C.CAPACITOR 0.01 MF

C353 CE4754468 E.CAPACITOR 4.7 MF/25V

C354 CY104423J C.CAPACITOR 0.1 MF

C355 CZ4716D2J C.CAPACITOR 470PF

C356 CE1063468 E.CAPACITOR 10 MF/16V

C357 CY472623J C.CAPACITOR 0.0047MF

C358 CY224122J C.CAPACITOR 0.22MF

C359 CY224122J C.CAPACITOR 0.22 MF

C4 CE2271468 E.CAPACITOR 220 MF/10V

C401 CE4754468 E.CAPACITOR 2.2 MF/50V

C402 CE4754468 E.CAPACITOR 2.2 MF/50V

C403 CE4763468 E.CAPACITOR 47 MF/16V

C405 CE4754468 E.CAPACITOR 4.7 MF/25V

C406 CE4754468 E.CAPACITOR 4.7 MF/25V

C407 CE1071468 E.CAPACITOR 100 MF/10V

C408 CE4754468 E.CAPACITOR 4.7 MF/25V

C409 CE4754468 E.CAPACITOR 4.7 MF/25V

C410 CE1071468 E.CAPACITOR 100 MF/10V

C451 CY104423J C.CAPACITOR 0.1MF

C452 CY103623J C.CAPACITOR 0.01MF

C454 CY104423J C.CAPACITOR 0.1 MF

C455 CZ4716D2J C.CAPACITOR 470 PF

C456 CE1063468 E.CAPACITOR 10 MF/16V

C457 CY472623J C.CAPACITOR 0.0047MF

C458 CY224122J C.CAPACITOR 0.22 MF

C459 CY224122J C.CAPACITOR 0.22MF

C5 CE1071468 E.CAPACITOR 100 MF/10V

C501 CE1071468 E.CAPACITOR 100 MF/10V

C502 CY103623J C.CAPACITOR 0.01 MF

C504 CY103623J C.CAPACITOR 0.01 MF

C505 CY103623J C.CAPACITOR 0.01MF

C506 CE1071468 E.CAPACITOR 100 MF/10V

Parts number Parts name Ar

Remarks

3-8

Page 25

LX-333R

ea

ea

Electrical parts list (Main board)

Item

A

C507 CY103623J C.CAPACITOR 0.01 MF

C508 CY104423J C.CAPACITOR 0.1 MF

C509 CY104423J C.CAPACITOR 0.1 MF

C51 CZ1206D2J C.CAPACITOR 12 PF

C510 CZ8206D2J C.CAPACITOR 82PF

C511 CY682623J C.CAPACITOR 0.0068MF

C512 CE1071468 E.CAPACITOR 100 MF/10V

C513 CY103623J C.CAPACITOR 0.01 MF

C515 CZ5R06A2J C.CAPACITOR 5 PF

C52 CZ1206D2J C.CAPACITOR 12 PF

C521 CE1071468 E.CAPACITOR 100 MF/10V

C522 CE1071468 E.CAPACITOR 100 MF/10V

C523 CE1056468 E.CAPACITOR 1 MF/50V

C524 CY103623J C.CAPACITOR 0.01 MF

C525 CY103623J C.CAPACITOR 0.01 MF

C529 CE1071468 E.CAPACITOR 100 MF/10V

C53 CE4760468 E.CAPACITOR 47 MF/6.3V

C533 CZ4706D2J C.CAPACITOR 47PF

C534 CY153623J C.CAPACITOR 0.015MF

C536 CY103623J C.CAPACITOR 0.01 MF

C537 CY272623J C.CAPACITOR 0.0027MF

C538 CY103623J C.CAPACITOR 0.01 MF

C539 CY333623J C.CAPACITOR 0.033 MF

C54 CY103623J C.CAPACITOR 0.01 MF

C540 CY473623J C.CAPACITOR 0.047 MF

C542 CZ4716D2J C.CAPACITOR 470 PF

C543 CZ4716D2J C.CAPACITOR 470 PF

C545 CY473623J C.CAPACITOR 0.047 MF

C546 CY473623J C.CAPACITOR 0.047 MF

C547 CY473623J C.CAPACITOR 0.047 MF

C549 CY473623J C.CAPACITOR 0.047 MF

C55 CZ5616D2J C.CAPACITOR 560 PF

C550 CY333623J C.CAPACITOR 0.033MF

C551 CE1071468 E.CAPACITOR 100 MF/10V

C552 CY103623J C.CAPACITOR 0.01MF

C553 CY103623J C.CAPACITOR 0.01MF

C554 CE1071468 E.CAPACITOR 100 MF/10V

C555 CY103623J C.CAPACITOR 0.01 MF

C556 CZ8R06B2J C.CAPACITOR 8 PF

C557 CZ8R06B2J C.CAPACITOR 8 PF

C558 CZ1016D2J C.CAPACITOR 100PF

C56 CY223623J C.CAPACITOR 0.022 MF

C57 CE2256468 E.CAPACITOR 2.2 MF/50V

C571 CE1071468 E.CAPACITOR 100 MF/10V

C573 CY103623J C.CAPACITOR 0.01MF

C574 CE1071468 E.CAPACITOR 100 MF/10V

C581 CE2271468 E.CAPACITOR 220 MF/10V

C582 CY103623J C.CAPACITOR 0.01 MF

C583 CE2263468 E.CAPACITOR 22 MF/16V

C584 CY473623J C.CAPACITOR 0.047MF

C7 CE1046468 E.CAPACITOR 0.1 MF/50V

C701 CZ2206D2J C.CAPACITOR 22PF

C702 CZ2706D2J C.CAPACITOR 27PF

C703 CZ1506D2J C.CAPACITOR 15 PF

C704 CZ1506D2J C.CAPACITOR 15 PF

C705 CZ2216D2J C.CAPACITOR 220 PF

C706 CY473623J C.CAPACITOR 0.047MF

C707 CY103623J C.CAPACITOR 0.01 MF

C708 CE1063468 E.CAPACITOR 10 MF/16V

C710 CE2271468 E.CAPACITOR 220 MF/10V

C711 CY474122J C.CAPACITOR 0.47 MF

C712 CY474122J C.CAPACITOR 0.47MF

C713 CE2271468 E.CAPACITOR 220 MF/10V

Parts number Parts name Ar

Block No. 01

Remarks

Item

A

C719 CZ2216D2J C.CAPACITOR 220PF

C720 CY473623J C.CAPACITOR 0.047 MF

C721 CY222623J C.CAPACITOR 0.0022MF

C722 CY222623J C.CAPACITOR 0.0022MF

C750 CY474122J C.CAPACITOR 0.47 MF

C755 CY473623J C.CAPACITOR 0.047 MF

C756 CY222623J C.CAPACITOR 0.0022MF

C771 CY473623J C.CAPACITOR 0.047 MF

C791 CE1046468 E.CAPACITOR 0.1 MF/50V

C821 CY183623J C.CAPACITOR 0.018 MF

C822 CY393623J C.CAPACITOR 0.039MF

C823 CY393623J C.CAPACITOR 0.039MF

C824 CY393623J C.CAPACITOR 0.039 MF

C825 CY393623J C.CAPACITOR 0.039 MF

C826 CY122623J C.CAPACITOR 0.0012MF

C827 CE1063468 E.CAPACITOR 10 MF/16V

C828 CE2263468 E.CAPACITOR 22 MF/16V

C9 CE4763468 E.CAPACITOR 47 MF/16V

C911 CE4763468 E.CAPACITOR 47 MF/16V

C912 CE1071468 E.CAPACITOR 100 MF/10V

C913 CY104423J C.CAPACITOR 0.1MF

C931 CZ1016D2J C.CAPACITOR 100PF

C932 CY473623J C.CAPACITOR 0.047 MF

C937 CY104423J C.CAPACITOR 0.1 MF

C940 CY102623J C.CAPACITOR 0.001 MF

C941 CE4746468 E.CAPACITOR 0.47 MF/50V

C942 CE4763468 E.CAPACITOR 47 MF/16V

C943 CY103603J C.CAPACITOR 0.01 MF

C944 CE2256468 E.CAPACITOR 2.2 MF/50V

C945 CY104423J C.CAPACITOR 0.1MF

C951 CY104423J C.CAPACITOR 0.1 MF

C952 CE1063468 E.CAPACITOR 10 MF/16V

C961 CE3383541 E.CAPACITOR 3300MF/16V

C962 CE2256468 E.CAPACITOR 2.2 MF/50V

C964 CE2271468 E.CAPACITOR 220 MF/10V

C965 CE2263468 E.CAPACITOR 22 MF/16V

C966 CY103623J C.CAPACITOR 0.01 MF

C967 CE2263468 E.CAPACITOR 22 MF/16V

C968 CY104423J C.CAPACITOR 0.1 MF

C969 CE2263468 E.CAPACITOR 22 MF/16V

C970 CY473623J C.CAPACITOR 0.047MF

C971 CE4763468 E.CAPACITOR 47 MF/16V

C977 CE2263468 E.CAPACITOR 22 MF/16V

C978 CE1071468 E.CAPACITOR 100 MF/10V

C982 CE2263468 E.CAPACITOR 22 MF/16V

C987 CY104423J C.CAPACITOR 0.1MF

C991 CZ2716D2J C.CAPACITOR 270PF

C992 CZ2716D2J C.CAPACITOR 270PF

C993 CZ2716D2J C.CAPACITOR 270PF

C994 CZ2716D2J C.CAPACITOR 270PF

C995 CZ2716D2J C.CAPACITOR 270PF

C996 CZ2716D2J C.CAPACITOR 270PF

C997 CZ2716D2J C.CAPACITOR 270PF

C998 CZ2716D2J C.CAPACITOR 270PF

D1 DIAN217UL SI.DIODE

D11 DIAN202UL DIODE ARRAY DAN202U-W

D111 DIAN202UL DIODE ARRAY DAN202U-W

D131 DIAP202UL DIODE ARRAY DAP202U-X

D161 DIAN217UL SI.DIODE

D231 DIAP202UL DIODE ARRAY DAP202U-X

D332 DIAN202UL DIODE ARRAY DAN202U-W

D351 DIAN202UL DIODE ARRAY DAN202U-W

D451 DIAN202UL DIODE ARRAY DAN202U-W

Parts number Parts name Ar

Remarks

3-9

Page 26

KD-LX333R

Q

)

Q

Q

Q

Q

Q

Q

Q

)

Q

Q

Q

Q

Q

Q

Q

Q

Q

Q

Q

Q

Q

)

Q

)

Q

Q

Q

Q

Q

Q

Q

Q

Q

Q

)

Q

Q

Q

Q

Q

Q

)

Q

ea

ea

Electrical parts list (Main board)

Item

A

D701 DI0CRS03L SI.DIODE CRS03-X

D711 DI1SS400L SI.DIODE

D941 DI1SS400L SI.DIODE

D961 000372050 ZENE R DIODE 1N5404TU-15

D962 DI0CRS03L SI.DIODE CRS03-X

D963 DI1SS400L SI.DIODE

D965 DIAN202UL DIODE ARRAY DAN202U-W

D967 DI0CRS03L SI.DIODE CRS03-X

D978 Z0UDZ11BL ZENER DIODE UDZ11B-X

D980 DI1SS400L SI.DIODE

D986 DIAP202UL DIODE ARRAY DAP202U-X

IC151 000474740-T IC NJM4565MD

IC171 000474740-T IC NJM4565MD

IC301 000874370-T IC BA3220FV-X

IC321 000874410-T IC M5282FP-XE

IC322 000874420-T IC BU4066BCFV

IC323 000474740-T IC NJM4565MD

IC401 000874370-T IC BA3220FV-X

IC501 000874440-T IC TA2147F-X

IC51 000874740-T IC BU1923F

IC521 000874450 IC TC9490F

IC581 000874460 IC FAN8037

IC701 000974270 IC UPD784217AGC-**

IC702 000974280-T IC PST3433UL

IC703 000874700-T IC BR24C32F

IC771 000774040-T IC HD74HC126FP

IC821 000874400-T IC NJM2100M

IC911 000874470 IC BD3860K

IC941 000874560 IC TA8273H

IC951 000574840-T IC MJM2904M

IC961 000874970 IC HA13164A

J1 EX0000487 ANTENNA JACK

L1 LC4R7J257 CHOKE COIL 4.7MH

L521 LC470J10J CHOKE COIL LC 47MH

L522 LC470J10J CHOKE COIL LC 47MH

L524 LC470J10J CHOKE COIL LC 47MH

L7 LC1R8K24J RF COIL 1.8MH

L701 LC470J10J CHOKE COIL LC 47MH

L718 LC1R8K24J RF COIL LC 1.8MH

L719 LC1R8K24J RF COIL 1.8MH

L771 LC1R8K24J RF COIL 1.8MH

L772 LC1R8K24J RF COIL 1.8MH

L961 000125560 CHOKE COIL

Parts number Parts name Ar

1 TRC4081(QRS)L TRANSISTOR 2SC4081 (QRS

11 TRB1197(QR)L TRANSISTOR 2SB1197K/QR/X

12 TRC114EUL-A DIGI.TRANSISTOR DTC114EUA-X

13 TRA1576(QRS)L-A TRANSISTOR 2SA1576A/QR/-X

131 TRD1048(678)L TRANSISTOR 2SD1048/6-7/-X

132 TRD1048(678)L TRANSISTOR 2SD1048/6-7/-X

161 TRC4081(QRS)L TRANSISTOR 2SC4081/QR/-X

2 TRC4081(QRS)L TRANSISTOR 2SC4081 (QRS

22 TRC4081(QRS)L TRANSISTOR 2SC4081/QR/-X

23 TRC4081(QRS)L TRANSISTOR 2SC4081/QR/-X

231 TRD1048(678)L TRANSISTOR 2SD1048/6-7/-X

232 TRD1048(678)L TRANSISTOR 2SD1048/6-7/-X

24 TRC114EUL-A DIGI.TRANSISTOR DTC114EUA-X

3 TRA114EUL-A DIG I.TRANSISTOR DTA114EUA-X

321 TRC114EUL-A DIGI.TRANSISTOR DTC114EUA-X

322 TRC114EUL-A DIGI.TRANSISTOR DTC114EUA-X

323 TRD1048(678)L TRANSISTOR 2SD1048/6-7/-X

34 TRA114EUL-A D IGI.TRANSISTOR DTA114EUA-X

4 TRC4081(QRS)L TRANSISTOR 2SC4081/QR/-X

5 TRA114EUL-A DIG I.TRANSISTOR DTA114EUA-X

Block No. 01

Remarks

Item

A

R1 RK393JA0J COMP.RESISTOR 1/10W 39 K

R10 RK4R7JA0J RESISTOR 1/10W 4.7

R11 RK4R7JA0J RESISTOR 1/10W 4.7

R111 RK224JA0J COMP.RESISTOR 1/10W 220K

R113 RK472JA0J C.RESISTOR 1/10W 4.7 K

R118 RK104JA0J COMP.RESISTOR 1/10W 100 K

R119 RK101JA0J UNF.C.RESISTOR 1/10W 100

R12 RK473JA0J COMP.RESISTOR 1/10W 47 K

R123 RK273JA0J COMP.RESISTOR 1/10W 27 K

R13 RK472JA0J C.RESISTOR 1/10W 4.7 K

R131 RK222JA0J C.RESISTOR 1/10W 2.2K

R132 RK222JA0J C.RESISTOR 1/10W 2.2K

R133 RK681JA0J C.RESISTOR 1/10W 680

R134 RK681JA0J C.RESISTOR 1/10W 680

R135 RK101JA0J UNF.C.RESISTOR 1/10W 100

R136 RK101JA0J UNF.C.RESISTOR 1/10W 100

R14 RK473JA0J COMP.RESISTOR 1/10W 47 K

R141 RK473JA0J COMP.RESISTOR 1/10W 47K

R142 RK473JA0J COMP.RESISTOR 1/10W 47 K

R143 RK473JA0J COMP.RESISTOR 1/10W 47K

R144 RK473JA0J COMP.RESISTOR 1/10W 47 K

R145 RK473JA0J COMP.RESISTOR 1/10W 47K

R146 RK473JA0J COMP.RESISTOR 1/10W 47K

R15 RK332JA0J C.RESISTOR 1/10W 3.3 K

R151 RK153JA0J COMP.RESISTOR 1/10W 15K

R152 RK333JA0J COMP.RESISTOR 1/10W 33 K

R153 RK123JA0J C.RESISTOR 1/10W 12 K

R155 RK472JA0J C.RESISTOR 1/10W 4.7K

R16 RK472JA0J C.RESISTOR 1/10W 4.7 K

R161 RK473JA0J COMP.RESISTOR 1/10W 47 K

R162 RK123JA0J C.RESISTOR 1/10W 12K

R163 RK184JA0J C.RESISTOR 1/10W 180 K

R164 RK223JA0J COMP.RESISTOR 1/10W 22 K

R165 RK391JA0J C.RESISTOR 1/10W 390

R166 RK102JA0J C.RESISTOR 1/10W 1 K

R167 RK274JA0J COMP.RESISTOR 1/10W 270K

R171 RK471JA0J C.RESISTOR 1/10W 470

R172 RK104JA0J COMP.RESISTOR 1/10W 100 K

R173 RK822JA0J C.RESISTOR 1/10W 8.2 K

R174 RK822JA0J C.RESISTOR 1/10W 8.2 K

R175 RK103JA0J C.RESISTOR 1/10W 10 K

R176 RK103JA0J C.RESISTOR 1/10W 10 K

R177 RK102JA0J C.RESISTOR 1/10W 1 K

R21 RK473JA0J COMP.RESISTOR 1/10W 47 K

Parts number Parts name Ar

501 TRB1241(PQR)8 TRANSISTOR 2SB1241 (PQR

581 TRB1241(PQR)8 TRANSISTOR 2SB1241 (PQR

590 TRA114EUL-A DIGI.TRANSIST OR DTA114EUA-X

591 TRC114EUL-A DIGI.TRANSISTOR DTC114EUA-X

700 TRA114EUL-A DIGI.TRANSIST OR DTA114EUA-X

701 TRC114EUL-A DIGI.TRANSISTOR DTC114EUA-X

702 TRA1576(QRS)L-A TRANSISTOR 2SA1576A/QR/-X

791 TRC114EUL-A DIGI.TRANSISTOR DTC114EUA-X

942 TRC114TUL-A DIGI.TRANSISTOR DTC114EUA-X

943 TRC114EUL-A DIGI.TRANSISTOR DTC114EUA-X

965 TRC114EUL-A DIGI.TRANSISTOR DTC114EUA-X

966 TRA1576(QRS)L-A TRANSISTOR 2SA1576A (QRS

967 TRC4081(QRS)L TRANSISTOR 2SC4081/QR/-X

977 TRA114EUL-A DIGI.TRANSIST OR DTA114EUA-X

979 TRA114EUL-A DIGI.TRANSIST OR DTA114EUA-X

981 TRA114EUL-A DIGI.TRANSIST OR DTA114EUA-X

982 TRC114EUL-A DIGI.TRANSISTOR DTC114EUA-X

983 TRC4081(QRS)L TRANSISTOR 2SC4081 (QRS

986 TRC114EUL-A DIGI.TRANSISTOR DTC114EUA-X

Remarks

3-10

Page 27

LX-333R

ea

Electrical parts list (Main board)

Item

A

R211 RK224JA0J COMP.RESISTOR 1/10W 220K

R213 RK472JA0J C.RESISTOR 1/10W 4.7 K

R218 RK104JA0J COMP.RESISTOR 1/10W 100 K

R219 RK101JA0J UNF.C.RESISTOR 1/10W 100

R22 RK393JA0J COMP.RESISTOR 1/10W 39 K

R223 RK273JA0J COMP.RESISTOR 1/10W 27 K

R23 RK103JA0J C.RESISTOR 1/10W 10 K

R231 RK222JA0J C.RESISTOR 1/10W 2.2K

R232 RK222JA0J C.RESISTOR 1/10W 2.2K

R233 RK681JA0J C.RESISTOR 1/10W 680

R234 RK681JA0J C.RESISTOR 1/10W 680

R235 RK101JA0J UNF.C.RESISTOR 1/10W 100

R236 RK101JA0J UNF.C.RESISTOR 1/10W 100

R24 RK222JA0J C.RESISTOR 1/10W 2.2 K

R241 RK473JA0J COMP.RESISTOR 1/10W 47K

R242 RK473JA0J COMP.RESISTOR 1/10W 47K

R243 RK473JA0J COMP.RESISTOR 1/10W 47K

R244 RK473JA0J COMP.RESISTOR 1/10W 47 K

R245 RK473JA0J COMP.RESISTOR 1/10W 47 K

R246 RK473JA0J COMP.RESISTOR 1/10W 47K

R25 RK103JA0J C.RESISTOR 1/10W 10 K

R251 RK153JA0J COMP.RESISTOR 1/10W 15K

R252 RK333JA0J COMP.RESISTOR 1/10W 33 K

R253 RK123JA0J C.RESISTOR 1/10W 12 K

R255 RK472JA0J C.RESISTOR 1/10W 4.7K

R26 RK103JA0J C.RESISTOR 1/10W 10 K

R27 RK471JA0J C.RESISTOR 1/10W 470

R272 RK104JA0J COMP.RESISTOR 1/10W 100 K

R273 RK822JA0J C.RESISTOR 1/10W 8.2 K

R274 RK822JA0J C.RESISTOR 1/10W 8.2 K

R275 RK103JA0J C.RESISTOR 1/10W 10K

R276 RK103JA0J C.RESISTOR 1/10W 10 K

R277 RK102JA0J C.RESISTOR 1/10W 1 K

R28 RK473JA0J COMP.RESISTOR 1/10W 47 K

R301 RK243JA0J C.RESISTOR 1/10W 24 K

R302 RK243JA0J C.RESISTOR 1/10W 24 K

R303 RK333JA0J COMP.RESISTOR 1/10W 33 K

R304 RK333JA0J COMP.RESISTOR 1/10W 33 K

R305 RK154JA0J C.RESISTOR 1/10W 150 K

R322 RK103JA0J C.RESISTOR 1/10W 10 K

R323 RK103JA0J C.RESISTOR 1/10W 10 K

R324 RK104JA0J COMP.RESISTOR 1/10W 100 K

R325 RK104JA0J COMP.RESISTOR 1/10W 100 K

R326 RK103JA0J C.RESISTOR 1/10W 10 K

R327 RK562JA0J C.RESISTOR 1/10W 5.6 K

R328 RK153JA0J COMP.RESISTOR 1/10W 15 K

R329 RK000JA0J C.RESISTOR 1/10W 0

R330 RK473JA0J COMP.RESISTOR 1/10W 47 K

R331 RK104JA0J COMP.RESISTOR 1/10W 100 K

R332 RK104JA0J COMP.RESISTOR 1/10W 100K

R333 RK473JA0J COMP.RESISTOR 1/10W 47 K

R334 RK473JA0J COMP.RESISTOR 1/10W 47 K

R335 RK821JA0J C.RESISTOR 1/10W 820

R336 RK473JA0J COMP.RESISTOR 1/10W 47 K

R337 RK472JA0J C.RESISTOR 1/10W 4.7K

R338 RK101JA0J UNF.C.RESISTOR 1/10W 100

R339 RK101JA0J UNF.C.RESISTOR 1/10W 100

R340 RK474JA0J COMP.RESISTOR 1/10W 470K

R341 RK105JA0J C.RESISTOR 1/10W 1M

R342 RK105JA0J C.RESISTOR 1/10W 1M

R343 RK105JA0J C.RESISTOR 1/10W 1 M

R344 RK105JA0J C.RESISTOR 1/10W 1 M

R351 RK224JA0J COMP.RESISTOR 1/10W 220K

Parts number Parts name Ar

Block No. 01

Remarks

Item

A

R352 RK224JA0J COMP.RESISTOR 1/10W 220K

R353 RK105JA0J C.RESISTOR 1/10W 1 M

R354 RK682JA0J C.RESISTOR 1/10W 6.8 K

R355 RK224JA0J COMP.RESISTOR 1/10W 220K

R358 RK332JA0J C.RESISTOR 1/10W 3.3 K

R401 RK243JA0J C.RESISTOR 1/10W 24 K

R402 RK243JA0J C.RESISTOR 1/10W 24K

R403 RK333JA0J COMP.RESISTOR 1/10W 33 K

R404 RK333JA0J COMP.RESISTOR 1/10W 33 K

R405 RK154JA0J C.RESISTOR 1/10W 150 K

R451 RK224JA0J COMP.RESISTOR 1/10W 220 K

R452 RK224JA0J COMP.RESISTOR 1/10W 220 K

R454 RK682JA0J C.RESISTOR 1/10W 6.8 K

R455 RK224JA0J COMP.RESISTOR 1/10W 220 K

R458 RK332JA0J C.RESISTOR 1/10W 3.3 K

R5 RK100JA0J C.RESISTOR 1/10W 10

R501 RK823JA0J COMP.RESISTOR 1/10W 82 K

R502 RK823JA0J COMP.RESISTOR 1/10W 82 K

R503 RK823JA0J COMP.RESISTOR 1/10W 82 K

R504 RK823JA0J COMP.RESISTOR 1/10W 82 K

R505 RK154JA0J C.RESISTOR 1/10W 150 K

R506 RK154JA0J C.RESISTOR 1/10W 150 K

R507 RK220JA0J C.RESISTOR 1/10W 22

R508 RK220JA0J C.RESISTOR 1/10W 22

R509 RK821JA1J C.RESISTOR 1/10W 820

R51 RK220JA0J C.RESISTOR 1/10W 22

R510 RK473JA0J COMP.RESISTOR 1/10W 47 K

R511 RK103JA0J C.RESISTOR 1/10W 10 K

R512 RK202JA0J C.RESISTOR 1/10W 2 K

R513 RK102JA0J C.RESISTOR 1/10W 1 K

R514 RK273JA0J COMP.RESISTOR 1/10W 27 K

R515 RK823JA0J COMP.RESISTOR 1/10W 82K

R516 RK101JA0J UNF.C.RESISTOR 1/10W 100

R52 RK222JA0J C.RESISTOR 1/10W 2.2 K

R520 RK222JA0J C.RESISTOR 1/10W 2.2 K

R521 RK472JA0J C.RESISTOR 1/10W 4.7 K

R522 RK472JA0J C.RESISTOR 1/10W 4.7 K

R523 RK472JA0J C.RESISTOR 1/10W 4.7 K

R524 RK472JA0J C.RESISTOR 1/10W 4.7 K

R525 RK103JA0J C.RESISTOR 1/10W 10 K

R527 RK820JA0J C.RESISTOR 1/10W 82

R53 RK103JA0J C.RESISTOR 1/10W 10 K

R530 RK225JA0J C.RESISTOR 1/10W 2.2M

R531 RK562JA0J C.RESISTOR 1/10W 5.6 K

R532 RK473JA0J COMP.RESISTOR 1/10W 47K

R533 RK474JA0J COMP.RESISTOR 1/10W 470K

R536 RK153JA0J COMP.RESISTOR 1/10W 15K

R537 RK103JA0J C.RESISTOR 1/10W 10 K

R54 RK222JA0J C.RESISTOR 1/10W 2.2 K

R540 RK000JA0J C.RESISTOR 1/10W 0

R541 RK101JA0J UNF.C.RESISTOR 1/10W 100

R542 RK101JA0J UNF.C.RESISTOR 1/10W 100

R543 RK000JA0J C.RESISTOR 1/10W 0

R544 RK000JA0J C.RESISTOR 1/10W 0

R545 RK101JA0J UNF.C.RESISTOR 1/10W 100

R547 RK101JA0J UNF.C.RESISTOR 1/10W 100

R550 RK105JA0J C.RESISTOR 1/10W 1 M

R555 RK000JA0J C.RESISTOR 1/10W 0

R556 RK106JA0J C.RESISTOR 1/10W 10 M

R581 RK332JA0J C.RESISTOR 1/10W 3.3 K

R582 RK122JA0J C.RESISTOR 1/10W 1.2 K

R583 RK332JA0J C.RESISTOR 1/10W 3.3 K

R584 RK182JA0J C.RESISTOR 1/10W 1.8 K

Parts number Parts name Ar

Remarks

3-11

Page 28

KD-LX333R

Q

ea

Electrical parts list (Main board)

Item

A

R585 RK682JA0J C.RESISTOR 1/10W 6.8 K

R586 RK682JA0J C.RESISTOR 1/10W 6.8 K

R587 RK682JA0J C.RESISTOR 1/10W 6.8 K

R588 RK682JA0J C.RESISTOR 1/10W 6.8 K

R589 RK392JA0J C.RESISTOR 1/10W 3.9 K

R590 RK472JA0J C.RESISTOR 1/10W 4.7 K

R591 RK392JA0J C.RESISTOR 1/10W 3.9 K

R592 RK472JA0J C.RESISTOR 1/10W 4.7 K

R593 RK392JA0J C.RESISTOR 1/10W 3.9 K

R594 RK472JA0J C.RESISTOR 1/10W 4.7 K

R595 RK103JA0J C.RESISTOR 1/10W 10 K

R596 RK333JA0J COMP.RESISTOR 1/10W 33 K

R700 RK103JA0J C.RESISTOR 1/10W 10 K

R701 RK473JA0J COMP.RESISTOR 1/10W 47 K

R702 RK101JA0J UNF.C.RESISTOR 1/10W 100

R703 RK473JA0J COMP.RESISTOR 1/10W 47K

R704 RK473JA0J COMP.RESISTOR 1/10W 47 K

R705 RK473JA0J COMP.RESISTOR 1/10W 47K

R706 RK103JA0J C.RESISTOR 1/10W 10K

R707 RK472JA0J C.RESISTOR 1/10W 4.7 K

R708 RK472JA0J C.RESISTOR 1/10W 4.7 K

R709 RK472JA0J C.RESISTOR 1/10W 4.7 K

R710 RK103JA0J C.RESISTOR 1/10W 10K

R711 RK103JA0J C.RESISTOR 1/10W 10K

R712 RK103JA0J C.RESISTOR 1/10W 10K

R713 RK102JA0J C.RESISTOR 1/10W 1 K

R714 RK103JA0J C.RESISTOR 1/10W 10 K

R715 RK472JA0J C.RESISTOR 1/10W 4.7 K

R716 RK472JA0J C.RESISTOR 1/10W 4.7 K

R717 RK472JA0J C.RESISTOR 1/10W 4.7 K

R718 RK104JA0J COMP.RESISTOR 1/10W 100 K

R719 RK104JA0J COMP.RESISTOR 1/10W 100 K

R720 RK331JA0J C.RESISTOR 1/10W 330

R721 RK103JA0J C.RESISTOR 1/10W 10 K

R722 RK103JA0J C.RESISTOR 1/10W 10 K

R723 RK102JA0J C.RESISTOR 1/10W 1 K

R724 RK271JA0J C.RESISTOR 1/10W 270

R725 RK271JA0J C.RESISTOR 1/10W 270

R726 RK473JA0J COMP.RESISTOR 1/10W 47 K

R727 RK103JA0J C.RESISTOR 1/10W 10 K

R728 RK222JA0J C.RESISTOR 1/10W 2.2 K

R731 RK473JA0J COMP.RESISTOR 1/10W 47 K

R732 RK473JA0J COMP.RESISTOR 1/10W 47 K

R733 RK473JA0J COMP.RESISTOR 1/10W 47 K

R734 RK472JA0J C.RESISTOR 1/10W 4.7 K

R735 RK472JA0J C.RESISTOR 1/10W 4.7 K

R736 RK102JA0J C.RESISTOR 1/10W 1 K

R737 RK103JA0J C.RESISTOR 1/10W 10K

R738 RK103JA0J C.RESISTOR 1/10W 10K

R739 RK473JA0J COMP.RESISTOR 1/10W 47K

R740 RK473JA0J COMP.RESISTOR 1/10W 47K

R742 RK103JA0J C.RESISTOR 1/10W 10 K

R743 RK473JA0J COMP.RESISTOR 1/10W 47 K

R746 RK473JA0J COMP.RESISTOR 1/10W 47 K

R747 RK473JA0J COMP.RESISTOR 1/10W 47 K

R748 RK473JA0J COMP.RESISTOR 1/10W 47 K

R749 RK473JA0J COMP.RESISTOR 1/10W 47 K

R750 RK473JA0J COMP.RESISTOR 1/10W 47 K

R751 RK106JA0J C.RESISTOR 1/10W 10 M

R757 RK103JA0J C.RESISTOR 1/10W 10K

R760 RK103JA0J C.RESISTOR 1/10W 10K

R761 RK473JA0J COMP.RESISTOR 1/10W 47 K

R762 RK222JA0J C.RESISTOR 1/10W 2.2 K

Parts number Parts name Ar

Block No. 01

Remarks

Item

A

R763 RK222JA0J C.RESISTOR 1/10W 2.2 K

R764 RK222JA0J C.RESISTOR 1/10W 2.2 K

R765 RK222JA0J C.RESISTOR 1/10W 2.2 K

R766 RK473JA0J COMP.RESISTOR 1/10W 47 K

R772 RK473JA0J COMP.RESISTOR 1/10W 47 K

R773 RK223JA0J COMP.RESISTOR 1/10W 22 K

R775 RK103JA0J C.RESISTOR 1/10W 10 K

R776 RK104JA0J COMP.RESISTOR 1/10W 100 K

R777 RK223JA0J COMP.RESISTOR 1/10W 22 K

R779 RK473JA0J COMP.RESISTOR 1/10W 47 K

R781 RK331JA0J C.RESISTOR 1/10W 330

R782 RK104JA0J COMP.RESISTOR 1/10W 100 K

R791 RK102JA0J C.RESISTOR 1/10W 1 K

R8 RK472JA0J C.RESISTOR 1/10W 4.7 K

R821 RD102J3CQ C.RESISTOR 1/4W 1K

R822 RK822JA0J C.RESISTOR 1/10W 8.2 K

R823 RK223JA0J COMP.RESISTOR 1/10W 22K

R824 RK822JA0J C.RESISTOR 1/10W 8.2 K

R825 RK223JA0J COMP.RESISTOR 1/10W 22K

R826 RK153JA0J COMP.RESISTOR 1/10W 15 K

R827 RK472JA0J C.RESISTOR 1/10W 4.7 K

R828 RK223JA0J COMP.RESISTOR 1/10W 22 K

R829 RK223JA0J COMP.RESISTOR 1/10W 22 K

R830 RK103JA0J C.RESISTOR 1/10W 10 K

R831 RK820JA0J C.RESISTOR 1/10W 82

R9 RK472JA0J C.RESISTOR 1/10W 4.7 K

R908 RK104JA1J C.RESISTOR 1/10W 100K

R911 RK222JA0J C.RESISTOR 1/10W 2.2 K

R912 RK222JA0J C.RESISTOR 1/10W 2.2 K

R941 RK273JA0J COMP.RESISTOR 1/10W 27K

R943 RK562JA0J C.RESISTOR 1/10W 5.6 K

R950 RK000JA0J C.RESISTOR 1/10W 0

R954 RK103JA0J C.RESISTOR 1/10W 10 K

R962 RK912JA0J C.RESISTOR 1/10W 9.1 K

R963 RK472JA0J C.RESISTOR 1/10W 4.7 K

R965 RK473JA0J COMP.RESISTOR 1/10W 47 K

R970 RK123JA0J C.RESISTOR 1/10W 12 K

R971 RK393JA0J COMP.RESISTOR 1/10W 39 K

R975 RK153JA0J COMP.RESISTOR 1/10W 15K

R976 RK222J41J RESISTOR 1/8W 2.2 K

R977 RK222J41J RESISTOR 1/8W 2.2 K

R979 RD102J3CQ C.RESISTOR 1/4W 1K

R981 RK183JA0J COMP.RESISTOR 1/10W 18K

R984 RK473JA0J COMP.RESISTOR 1/10W 47 K

R985 RK472JA0J C.RESISTOR 1/10W 4.7 K

R986 RK102JA0J C.RESISTOR 1/10W 1 K

R987 RK473JA0J COMP.RESISTOR 1/10W 47K

R988 RK332JA0J C.RESISTOR 1/10W 3.3 K

R989 RK472JA0J C.RESISTOR 1/10W 4.7 K

S651 000392900-T TACT SWITCH

S652 000392900-T TACT SWITCH

S653 000392900-T TACT SWITCH

TH700 TH103J05J THERMISTOR

TH981 TH103J05J THERMISTOR

TU1 000153680 TUNER PACK TUNNER FAE372-E

X51 000171200-T CRYSTAL 4.332MHZ

X521 000171590-T CRYSTAL 16.9344MHZ

X701 000171600-T CRYSTAL 12.5MHZ

X702 000171610 CRYSTAL

Parts number Parts name Ar

Remarks

AX0401-001

3-12

Page 29

LX-333R

Q

Q

Q

Q

Q

Q

Q

Q

Electrical parts list (Front board)

Item

A

CN601 KZ040160L CONN.TERMINAL 16P FPC CONNECT

CN631 KZ040060L CONN.TERMINAL 6P FPC CONNECTO

C606 CY104423J C.CAPACITOR 0.1 MF

C607 CY104423J C.CAPACITOR 0.1 MF

C608 CY104423J C.CAPACITOR 0.1 MF

C609 CZ6816D2J C.CAPACITOR 680 PF

C610 CY475316J C.CAPACITOR 4.7 MF

C611 CY475316J C.CAPACITOR 4.7 MF

C612 CQ393328J C.CAPACITOR 0.039 MF

C613 CY180J90J C.CAPACITOR 18 PF 3.15K

C614 CY104423J C.CAPACITOR 0.1 MF

C615 CY562623J C.CAPACITOR 0.0056MF

C616 CY475316J C.CAPACITOR 4.7 MF

C617 CY475316J C.CAPACITOR 4.7 MF

C623 CY475316J C.CAPACITOR 4.7 MF

C661 CY102623J C.CAPACITOR 0.001 MF

C662 CY102623J C.CAPACITOR 0.001 MF

D623 000372400-T SI.DIODE SML310LT

D624 000372400-T SI.DIODE SML310LT

D625 ZDZS5R1BL ZENER DIODE UDZS5.1B

D627 000372390-T SI.DIODE LT1F67AF