Page 1

SECTION 4

CHARTS AND DIAGRAMS

SCHEMATIC DIAGRAM NOTES

• Schematic safety precaution

! Parts are safety related parts.

When replacing them, be sure to use the specified parts.

• Unit of value

Unless otherwise specified

1) Resistance is in Ω (1/6 W)

2) Capacitance is in µF

3) Inductance is in µH

• Expression of wiring

As the following circuit diagram is divided to print on some

sheets, such an indication as the following is found in the

case the wiring extends over two or more divided sections.

1) Circuit diagram divided into two or more sections:

Board Board Name

10

20

30

33

MAIN

MIF

AUDIO

PR MDA

Number of

divided sections

1/18 to 18/18

1/7 to 7/7

1/2 to 2/2

1/3 to 3/3

2) Indication of wiring which extends to another section:

(Example)

A)

This indication that wiring extends to “3/3” of

the diagram.

NTSC(L) TO 3/3

•Others

In regard of a board assembly whose circuit is composed of

multilayered board patterns such 4- or 6-layered patterns, board

patterns of the power supply lines and grounding lines are

omitted in this section.

Note: For detail of each electrical part, refer to Section 6

“ELECTRICAL PARTS LIST” by it symbol number.

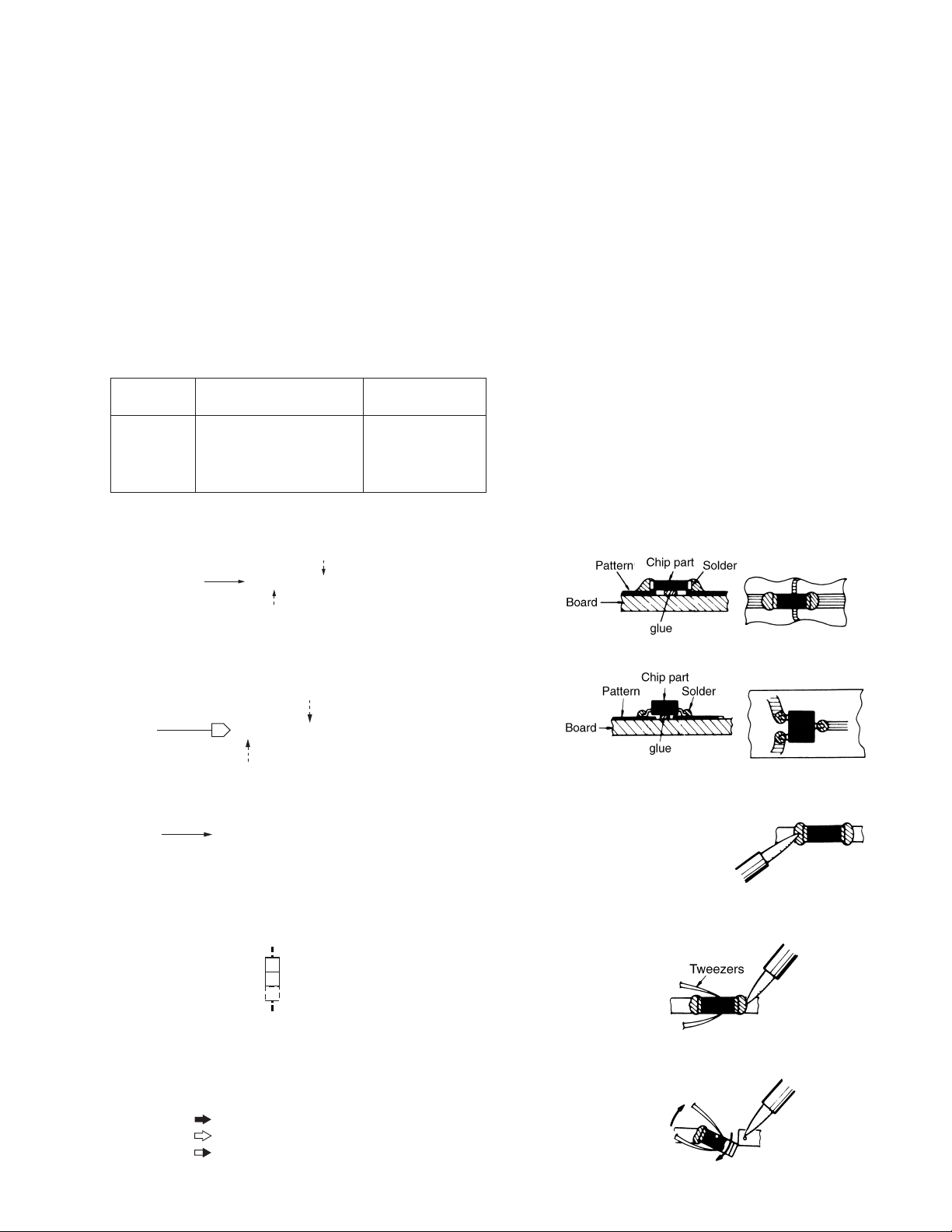

REPLACING SURFACE MOUNT “CHIP” COMPONENTS

• Some resistors, shorting jumpers (0 resistance), ceramic

capacitors, transistors, and diodes are chip parts. These chip

parts cannot be reused after they are once removed.

• Chip resistors used in some circuits are of high precision

type having little error in resistance.

To demonstrate the full capacity of this set, place an order

for proper parts referring to the diagrams and parts lists in

the section 5.

• Soldering cautions:

1) Do not apply heat for more than 3 seconds.

2) Avoid using a rubbing stroke when soldering.

3) Discard removed chips; do not reuse them.

4) Supplementary cementing is not required.

5) Use care not to scratch or otherwise damage the chips.

(1) Soldered condition of chip parts

• Resistors, capacitors, etc.

Signal name

In the above case, the end of the wiring is connected to

the “NTSC(L)” on the 3nd section of the diagram.

B)

This indication that wiring extends to

“DV I/O” section of the diagram.

FRP DV I/O

Signal name

In the above case, the end of the wiring is connected to

the “FRP” on the “DV I/O” section of the diagram.

C)

PIX _ RST

3 : E8

In the above case, the end of the wiring is connected to

the “PIX _ RST” on “E” (X-axis) and “8” (Y-axis) position

scale in page “3” of the diagram.

• Wiring of connector

(Example)

CN9

1

FROM/To

2

CN9 (Page 4-24)

06

REAR1

In the above example, CN9 is connected with CN9 on 06

REAR1 board.

• Signal flow on the diagram

The following allow marks indicate the specified signal

paths respectively.

: Recording or EE signal path

: Playback signal ptah

: Recording and Playback signal path

• Transistors, diodes, etc.

(2) Removing of chip parts

• Resistors, capacitors, etc.

i) Melt solder at a side.

ii) Holding the chip with tweezers, melt solder at the other

side.

iii) Take off the chip in twisting and sliding motion.

4-1

Page 2

• Transistors, diodes, etc.

i) Melt solder at the side of single lead.

CHIP PARTS PIN ARRANGEMENT

[1] Digital transistors

ii) Lift the unsolderd side upwards.

iii) Simultaneously melt solder at two leads of the other

side and pull up the chip.

(3) Preheating and soldering of chip parts

Except transistors, make sure to preheat all chip parts,

capacitors in particular, with a hot wind of 150°C approx.

(of a hair dryer, etc.) for 2 minutes just before soldering,

and immediately solder by a soldering iron of approx. 30 W.

(4) Attaching of chip parts

i) Heap up a proper amount of solder beforehand.

DTC 1

1 2 3

C

R1

R2

BE

DTA 1

DTB 1

1 2 3

C

R1

R2

BE

(Top view) (Top view)

Two digits show resistance of R1 in abbreviation.

1

43 : 4.7 kΩ

14 : 10 kΩ

24 : 22 kΩ

44 : 47 kΩ

Roman letter show the resistive ratio between R1 and R2

2

in abbreviation.

E:R2/R1 = 1/1

Y:R2/R1 = 5/1

W:R2/R1 = 2/1

X:R2/R1 = 1/2

T:R2 is opened.

Symbol the shape of resistor in abbreviation.

3

[2] Chip transistors and chip F.E.T.s

2SA

2SB

C

2SC

2SD

C

ii) Holding down a new chip by tweezers, solder it to the

board by a soldering iron to melt solder from its lower

part to the upper part (in the direction shown by a big

arrow).

4-2

BE

BE

(Top view) (Top view)

2SJ2SK

G

SD

G

SD

(Top view) (Top view)

[3] Chip diodes

MA143A/MA742 MA142WA MA142A

(Top view)(Top view) (Top view)

Page 3

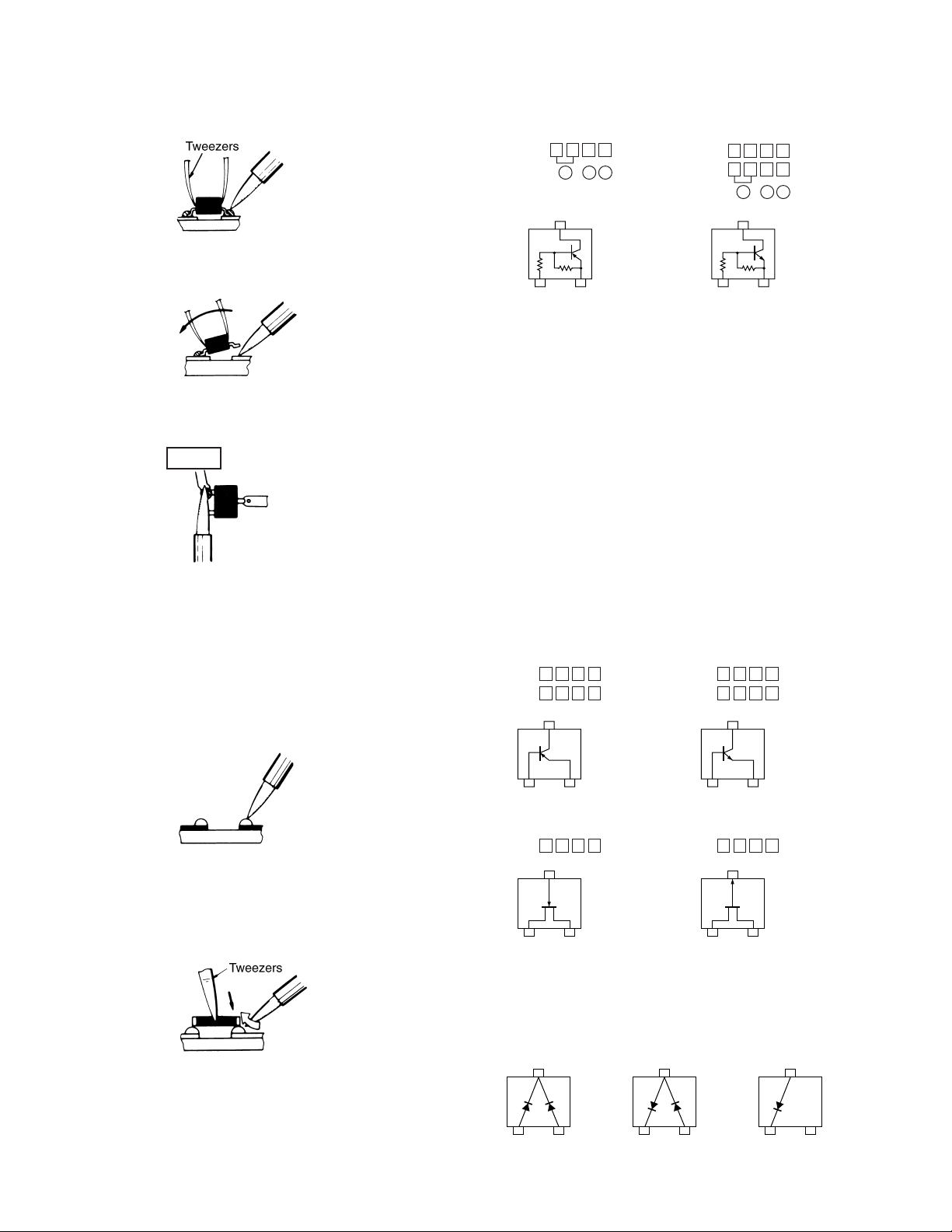

4.1 INDEX TO PAGES OF MAIN BOARDS AND CIRCUIT BOARD LOCATION

4

21

PS

TERM

4.1.1 Circuit board location

DV OUT

3

01

42

ISB

VJK

02

56

31

ISG

XLR

LINE SELECT

20

32

MIF

52

SD

OPE

57

63

USR

SWP

58

65

STA

PBM

59

51

AVR

MNU

30

35

AUDIO

MOS

64

44

FRL

EAR

53

EJT

MECHA CONNECTOR

70

ISR

03

AWB

55

Board

No.

01 ISB 4-8 4-10

02 ISG 4-7 4-10

03 ISR 4-9 4-10

10 MAIN 4-11 to 4-28 4-29

20 MIF 4-31 to 4-37 4-30

21 PS 4-38 4-30

30 AUDIO 4-44 to 4-45 4-43

31 LINE SELECT 4-46 4-47

32 SD 4-48 4-49

33 PRMDA 4-40 to 4-42 4-39

34 VF DR 4-56 4-55

Board Name

66

ZBR

Page of diagram

Schematic diagram

Circuit board

MAIN

10

Board

No.

35 MOS 4-48 4-49

41 DC IN 4-48 4-49

42 V JK 4-48 4-49

43 DV OUT 4-48 4-49

44 EAR 4-48 4-49

51 MNU 4-50 4-51

52 OPE 4-50 4-51

53 EJT 4-50 4-51

54 VF IF 4-54 4-55

55 AWB 4-50 4-51

56 XLR 4-50 4-51

Board Name

Schematic diagram

Page of diagram

Circuit board

4-3

Board

No.

57 SWP 4-50 4-51

58 STA 4-50 4-51

59 AVR 4-50 4-51

61 M BL 4-57 4-58

62 FTY 4-52 4-53

63 USR 4-52 4-53

64 FRL 4-52 4-53

65 PBM 4-52 4-53

66 ZBR 4-52 4-53

67 A JACK 4-52 4-53

70 MECHA CONNECTOR 4-52 4-53

80 FNC 4-52 4-53

4-3

Board Name

Schematic diagram

Page of diagram

Circuit board

33

PRMDA

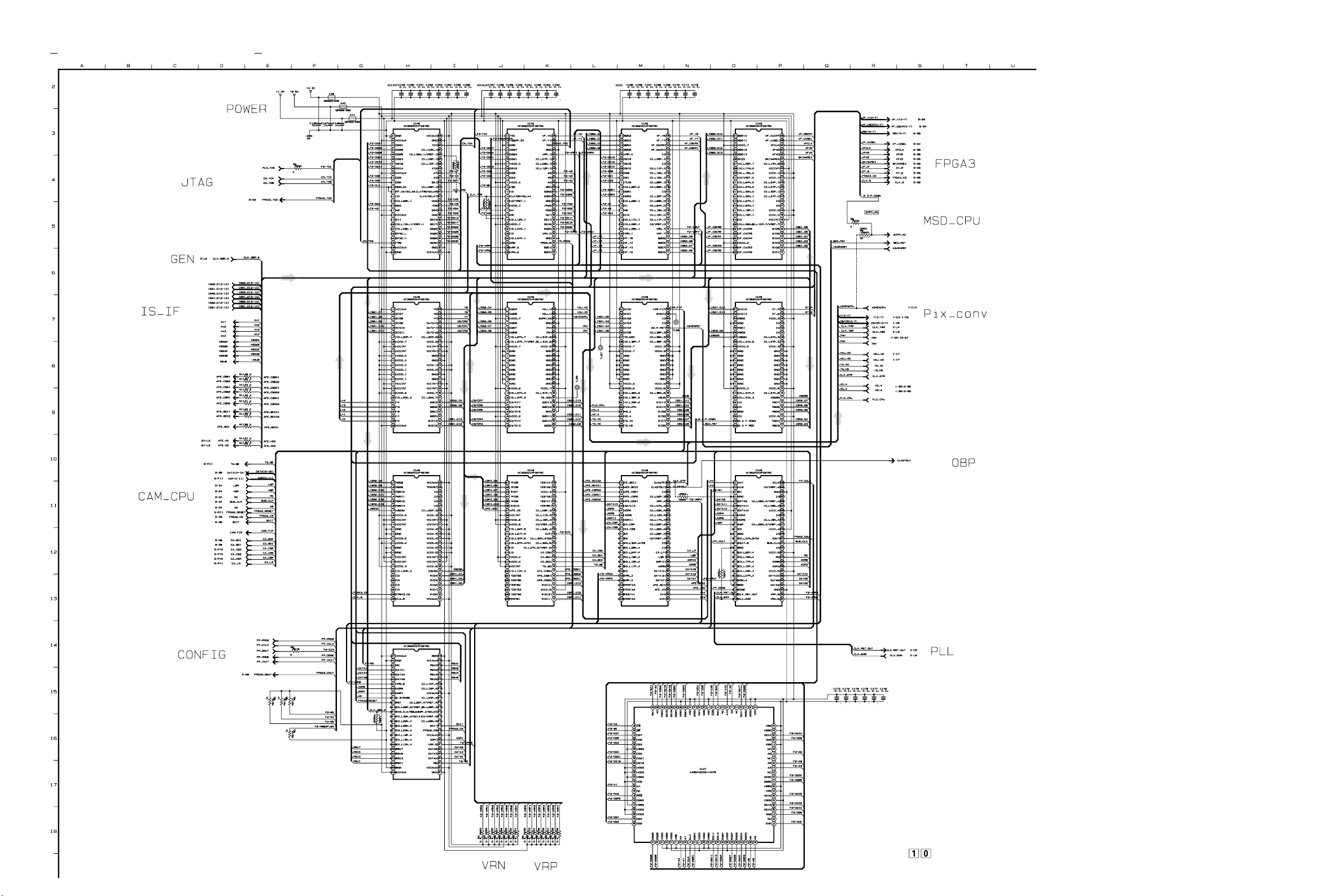

Page 4

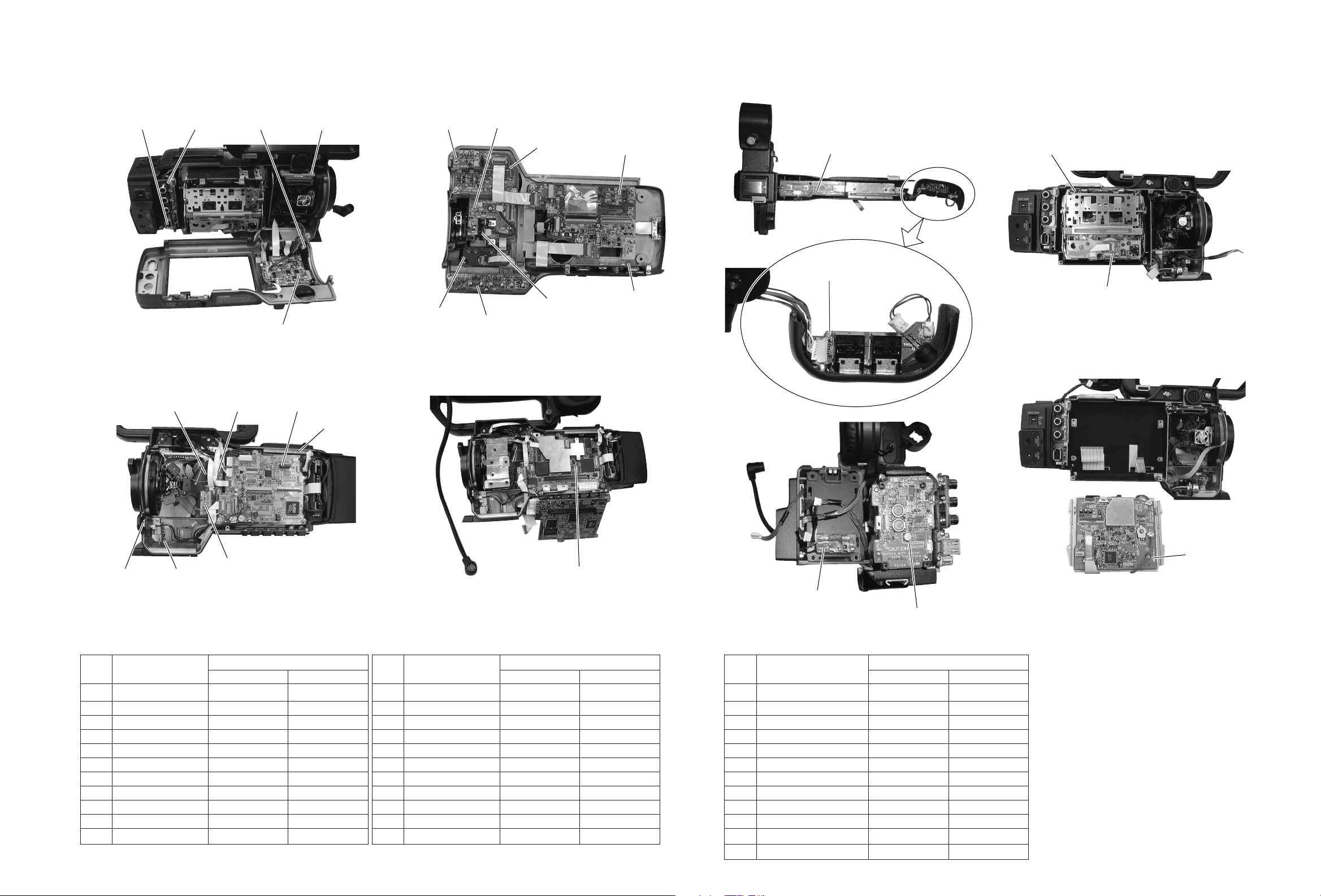

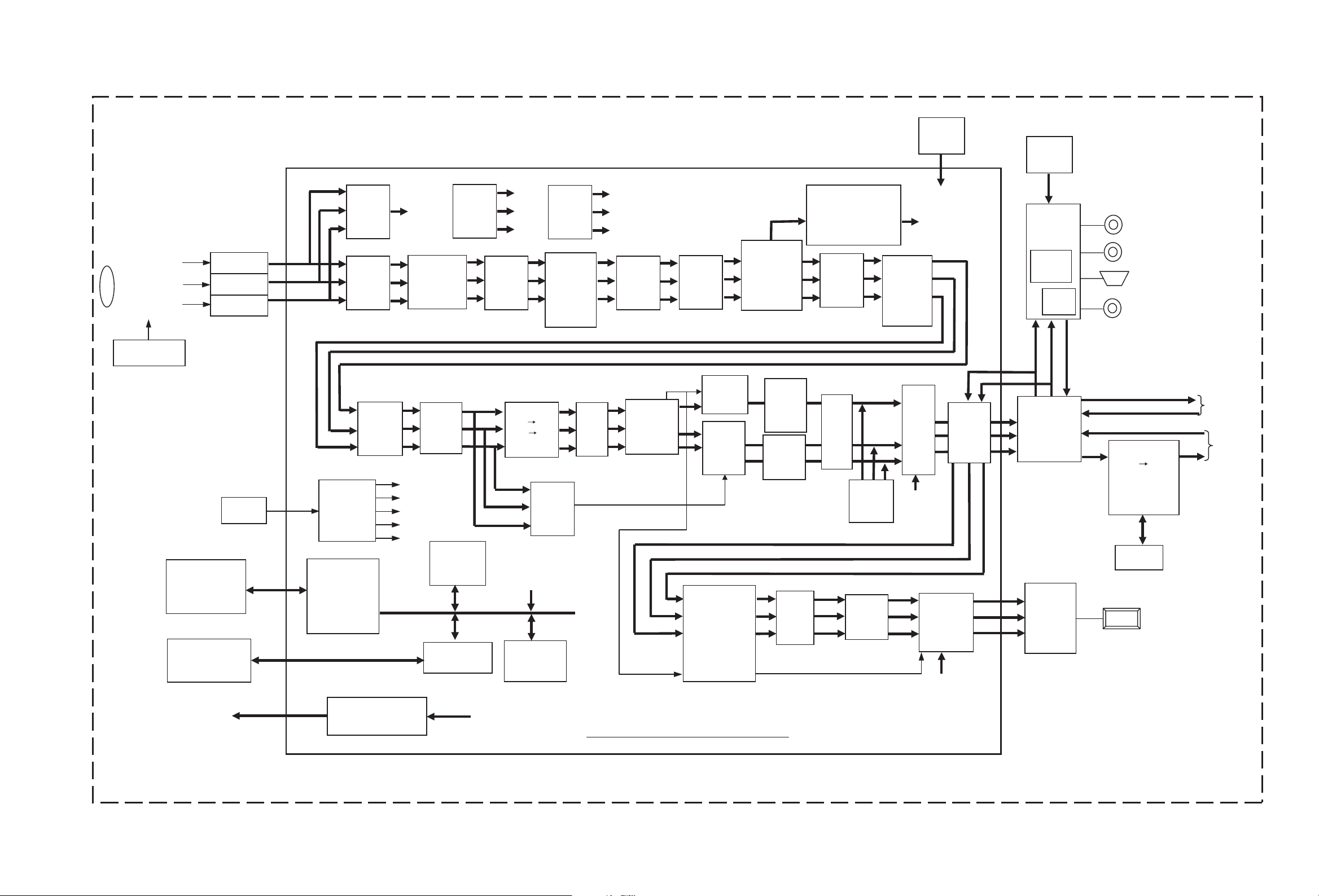

4.2 GY-HD100 BLOCK DIAGRAM

SYSCPU_SIO

ISG/ISB/ISR

PS CCD

ICX485

PS CCD

ICX485

PS CCD

ICX485

VF DR

VF Driver

CXM3005TQ

LCD OSD

IC48,IC49

VF OSD

PD6467GR

AFE:AD9949AK

SYSCPU_SIO

LENS Ctl

DC IN

+7.2V

VF

AFE

AFE

AFE

AFE

AFE

AFE

PS

MIF

IC52

Video DAC

ADV7123KST

RGB

IC53

SDRAM

K4S643233H

12

12

IC6

Multi DC-DC

BD9730KV

LCD

IC99

LCD Driver

CXM3004R

IC50

LCD/VF Process(FPGA3)

XC3S1000-4

IC46

Camera

Process(FPGA2)

XCS3S2000-4

SIO

ANTON

BATTERY

SYSCPU_SIO

RGB:9

SIO

16

IC54

CAM CPU

HD64F2368

IC57

EEPROM

M95320

MOSFET

IC51

Video DAC

ADV7123KST

RGB:9

IC47

SDRAM

K4S643233H

SIO

KeyScan

LED IC

Y:8,Cb/Cr:8

Y:8,Cb/Cr:8

IC61

EEPROM

M95320

IC58

SYS CPU

HD64F2368

IC63

RTC

RS5C314

+48V,+15V

+12V,+5V

9V, 3.3V

-8V

Composite

Component

IC5

Analog IF SD/HD

JCP8076

SIO

IC403

Pixel Conv

HD/SD

JCY0210

IC107

SDRAM

K4S643233H

IC108

60P→30P

(FPGA4)

XC3S1000-4

SIO

1kHz

MIF

TV

Y:8,Cb/Cr:8

SIO

SIO

JTAG

RGB

Y/Cb/Cr:8

Y/Cb/Cr:8

Y:8,Cb/Cr:8

Y:8,Cb/Cr:8

IC71

MSD CPU

MM103SF66R

IC70

EEPROM

M95320

SYSCPU_SIO

720P

IC3,IC4

480i/P

OSD BU3095-0CFV

32

IC88

SD

Ctl

MM5774

MAIN

SIO

MPEG TS→SB/DV

IC84

SDRAM

K4S641633H

SIO

Parallelbus

PRMDA

IC3

PLL

JCY0132

IC79

DVC DSP

JCY0152

IC86

32

IC94

Flash ROM

SA16D70BFI02A02

MPEG Bridge

JCY0173

IC91

Super ENC HD ENC/DEC

NLC0459APB

16

NTSC/PAL

27MHz

36MHz

72MHz

74MHz

FPGA2/3/4

MPEG TS/DV

32

IC93

SDRAM-1

EDS1232AABB

IC29

CLOCK GEN

MK3720

MIF

IC95

ROM CTL

XC2C2567VQ

PRMDA

IC3

Pre/Rec

JCY0132

32

IC95

SDRAM-1

EDS1232AABB

128Mbit

H or L

X1

27MHz

IC97

FPGA1/2/3/4

CONFIG FLASH

MBV160BE90PBA

IC89

1394 Phy

TSB41AB2PAP

128Mbit

MAIN

IC6

MDA

BA6865KV

IC108

DELAY

(FPGA4)

XC3S1000-4

DV TAPE

IC100

AudioADC

AK5357VT

IC101

AudioDAC

AK4384VT

EJTAG

IEEE1394

1kHz

MIF

MIC

SP

Battery

Charger

Battery

4-4 4-4

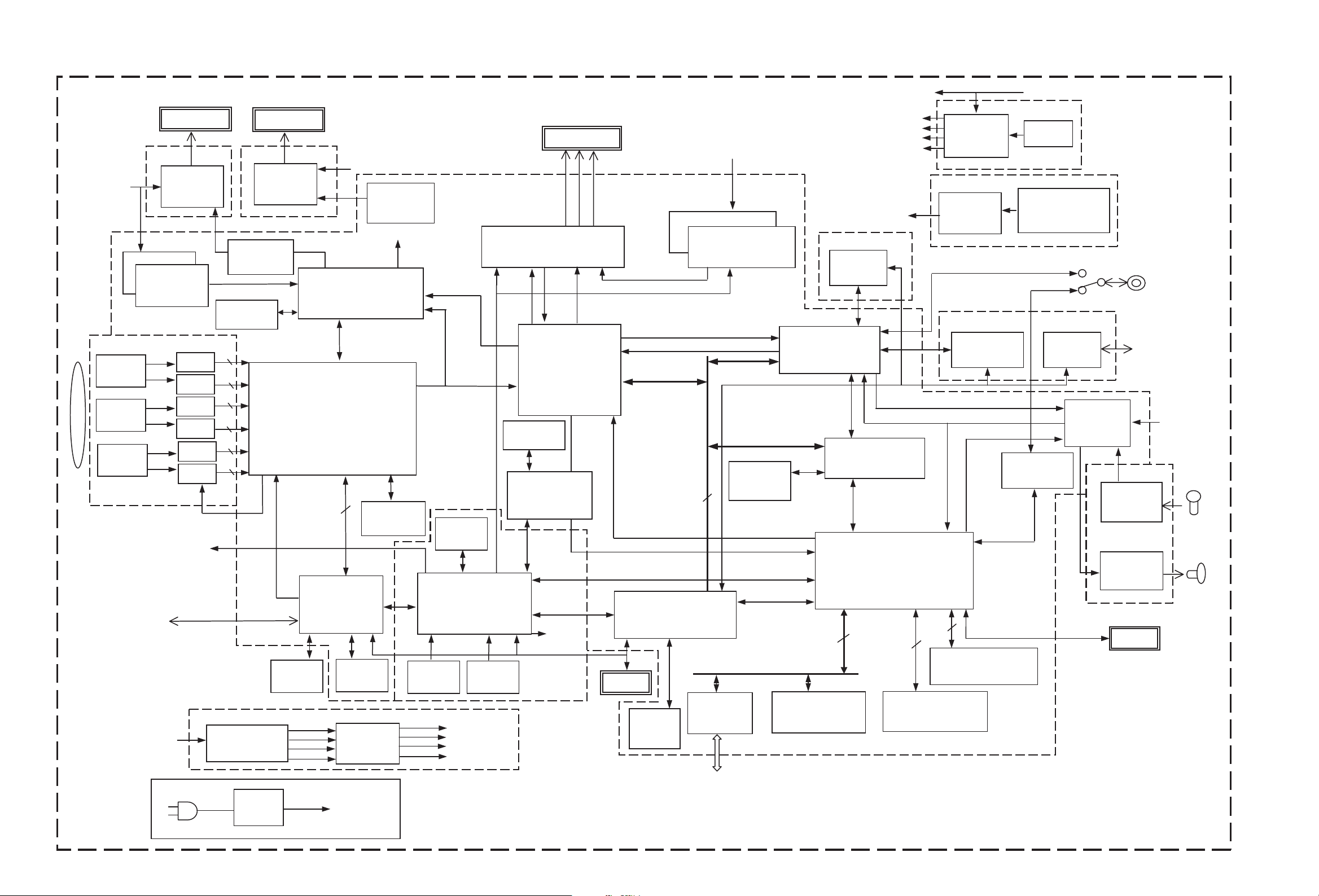

Page 5

IC46 Camera Process LSI

CAMERA PROCESS BLOCK DIAGRAM4.3

OSD

OSD

CCD ICX485

CCD ICX485

CCD ICX485

PS/HDTG

JCY0178

AFE

AFE

AFE

OSC

SSG

White

blemish

detect

Noise

Posi.

data

Pixel

compensation

Gamma

(Cinema)

TEST

Signal SG

FPN

correction

RGB YUV

444 422

GAIN

linearity

NUM

Slow

Shutter

Sepia

Line

Add

2 pixel

Add

Skin

Tone

Det

Skin_flag

Zoom

Twice

VDTL(freq)

Detail

Chroma

Sapless

GAIN

(AW,

White Balance

LOLUX,

etc.)

Y Gamma

KNEE

BLACK

Stretch

Chroma

GAIN

HUE

Peak defect

(AE,LEVEL Det.)

Skin area.

Area setting

Infrared rays mode

Master

pedestal

Feder

Color

Bar.

Color

matrix

(Cinema)

(Fluores

cense light)

OSD

MIX

Key

data

Key

SEL

JCP8076

Analog I/F

Setup

Level

3DNR

S

H

D

D

/

S

D

JCY0210

Pixel Conv

VBS OUT

Y/C OUT

CPNOUT

VBS IN(SD)

H

D

/

S

D

DV MAIN

FPGA(15k LUT)

1

60P 30P

SuperENC

2Audio Delay

3AudioTEST

TONE(1kHz)

HITACHI

H8CPU

SDRAM

128M

CPU

I/F

Internal signal OUT Port

(Auto Focus Det.)

Process

(Register,

status)

SDRAM I/F

data

DSP

Internal video signal

Rate converter

Down converter

Zoom

Over scan

16:9

IC46 Camera Process LSI

4-5 4-5

Peaking

Focus

Assist

SDRAM

128M

OSD MIX

Safty zone

WHITE area

Skin area

Zebra

Key

Encorder

VF

Page 6

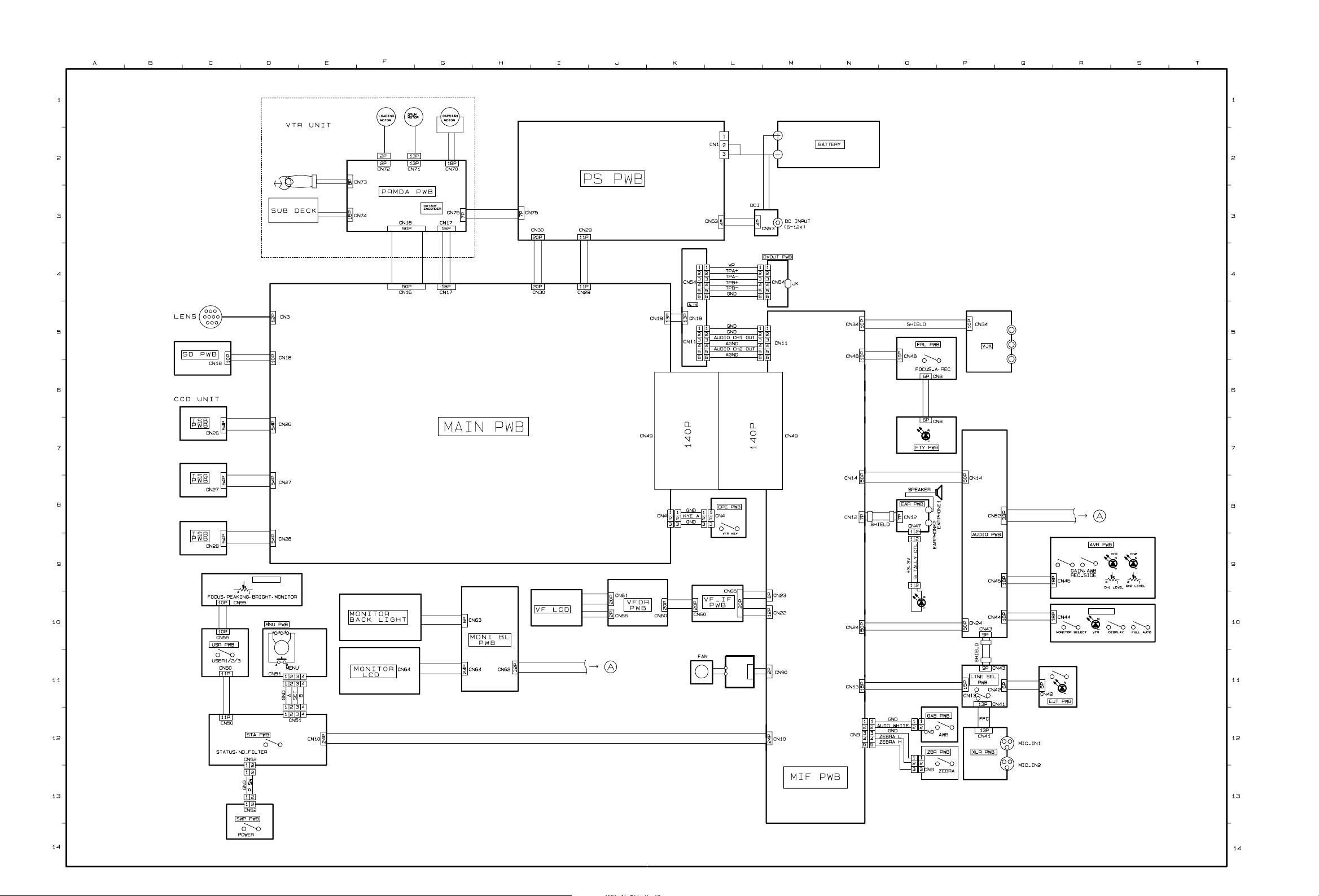

OVERALL WIRING DIAGRAM

4.4

PBM PWB

Board to Board

MOS PWB

CN90

2P

FNC

4-6 4-6

Page 7

ISG SCHEMATIC DIAGRAM

4.5

ADC

CLAMP

CDS VGA

VGA

CLAMP

ADC

CDS

FROM/TO

CN27

MAIN

ISG

4-7 4-7

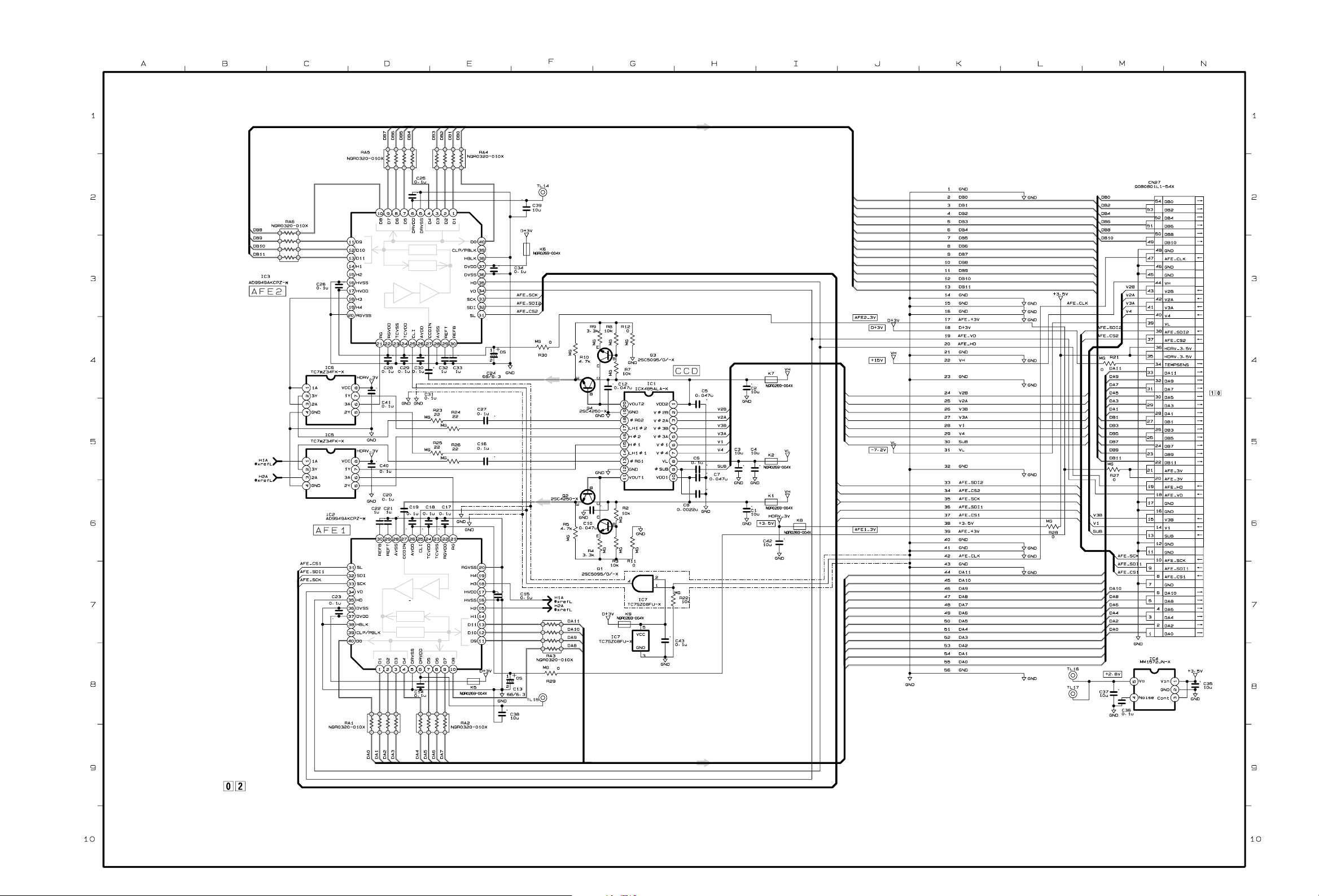

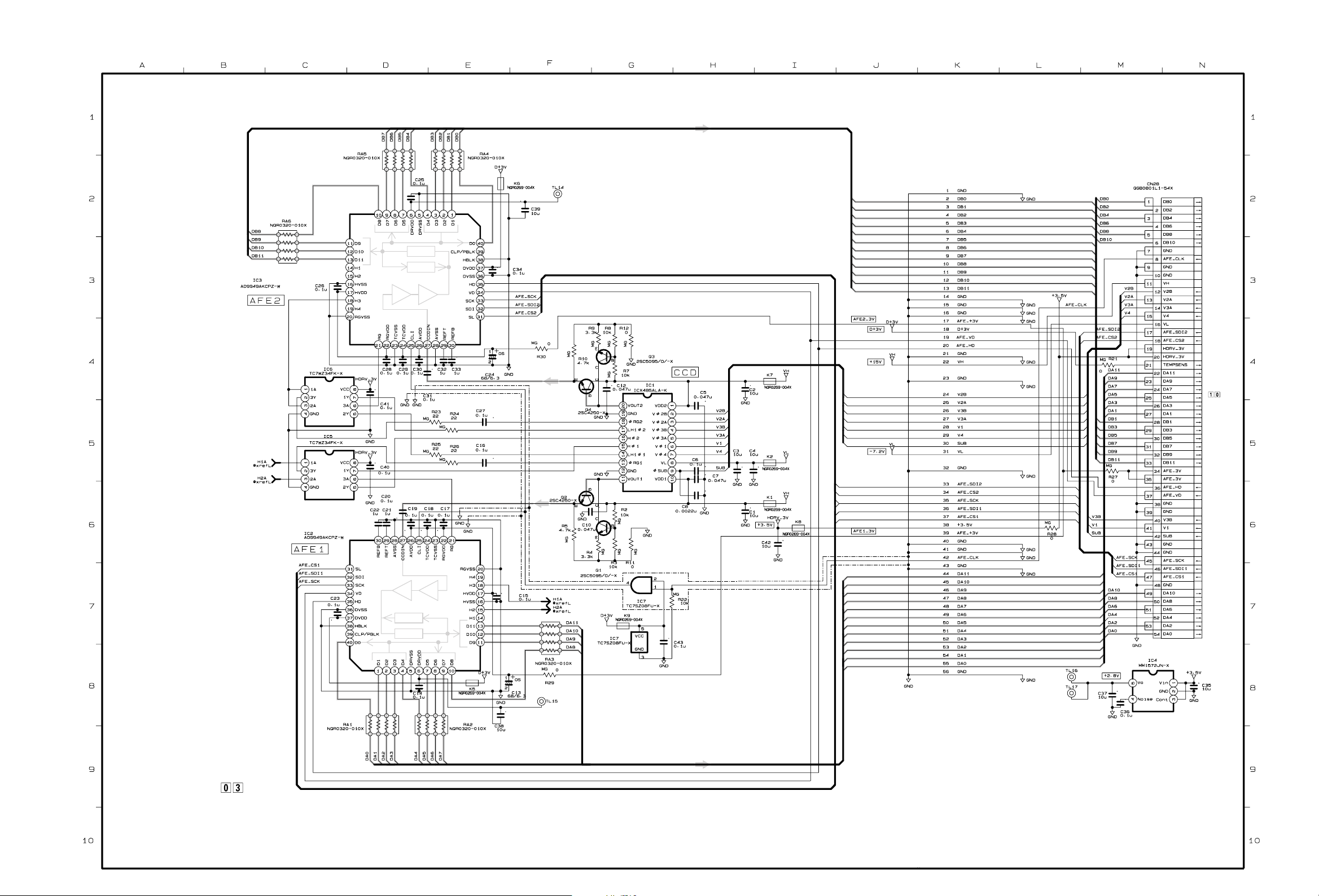

Page 8

ISB SCHEMATIC DIAGRAM

4.6

ADC

CLAMP

CDS VGA

CLAMP

ADC

FROM/TO

CN26

MAIN

CDSVGA

ISB

4-8 4-8

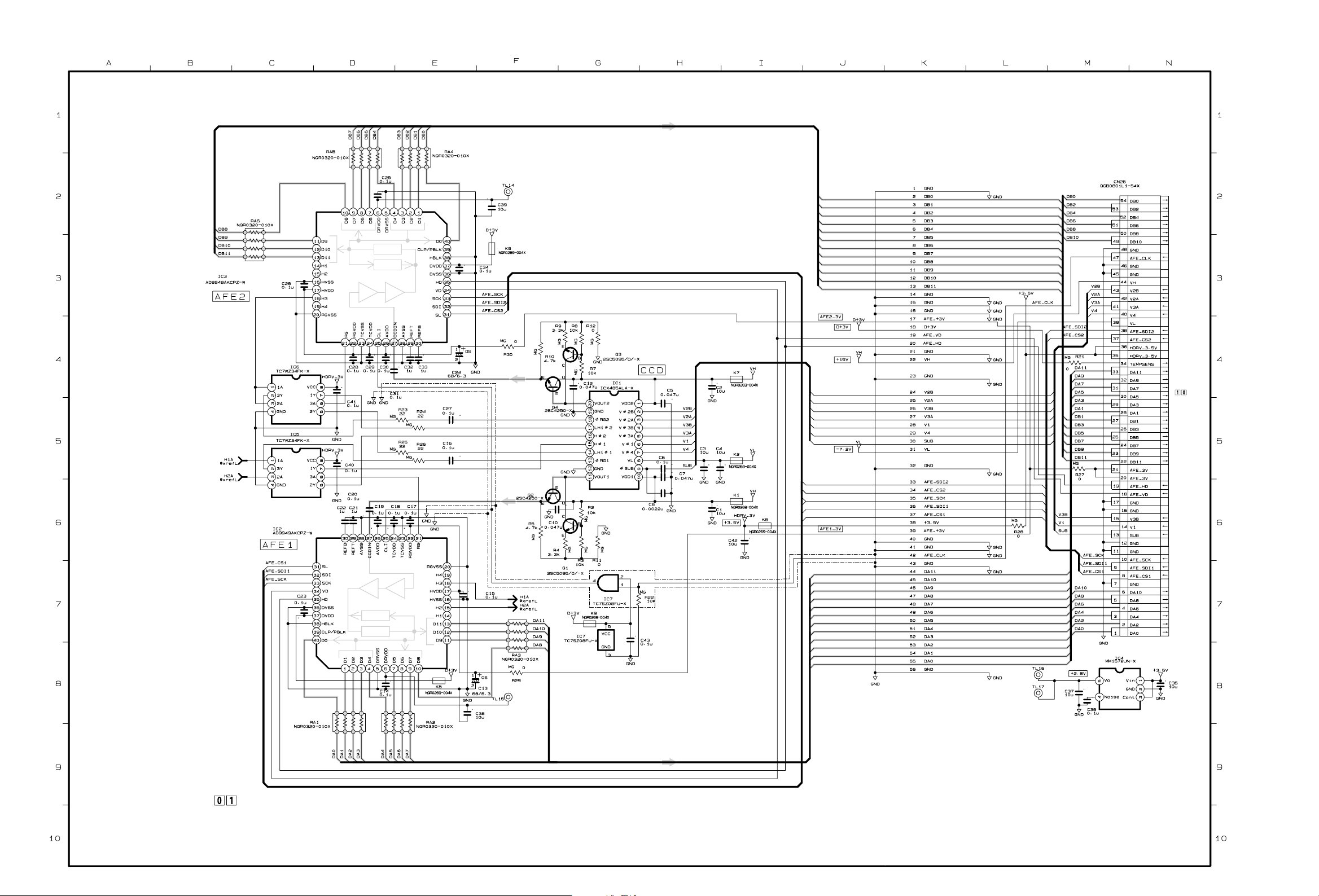

Page 9

ISR SCHEMATIC DIAGRAM

4.7

ADC

CLAMP

CDS VGA

CLAMP

ADC

FROM/TO

CN28

MAIN

CDSVGA

ISG

4-9 4-9

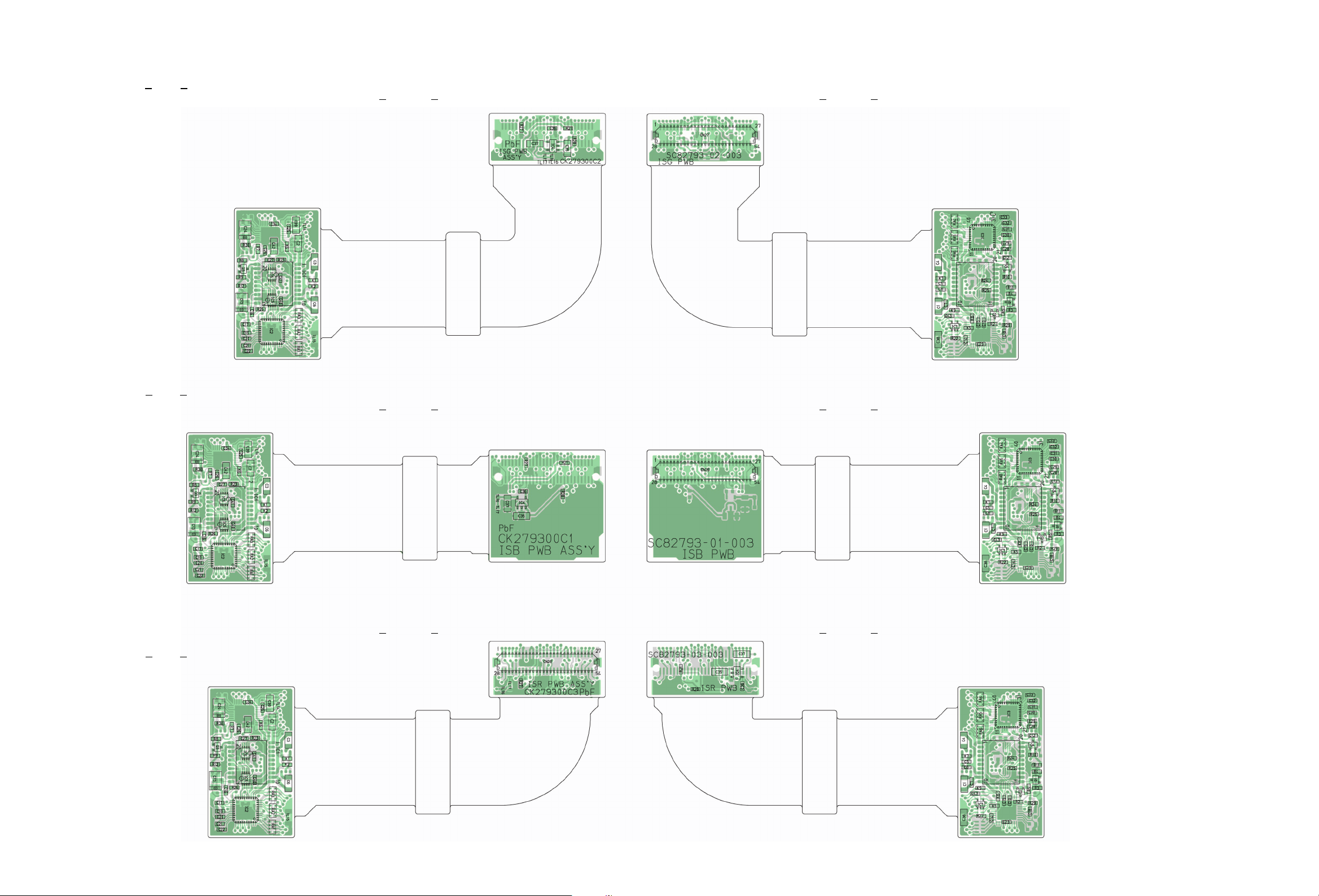

Page 10

4.8

ISG,ISB,ISR CIRCUIT BOARDS

ISG

ISB

SIDE A

SIDE A SIDE B

SIDE B

ISR

SIDE BSIDE A

4-10 4-10

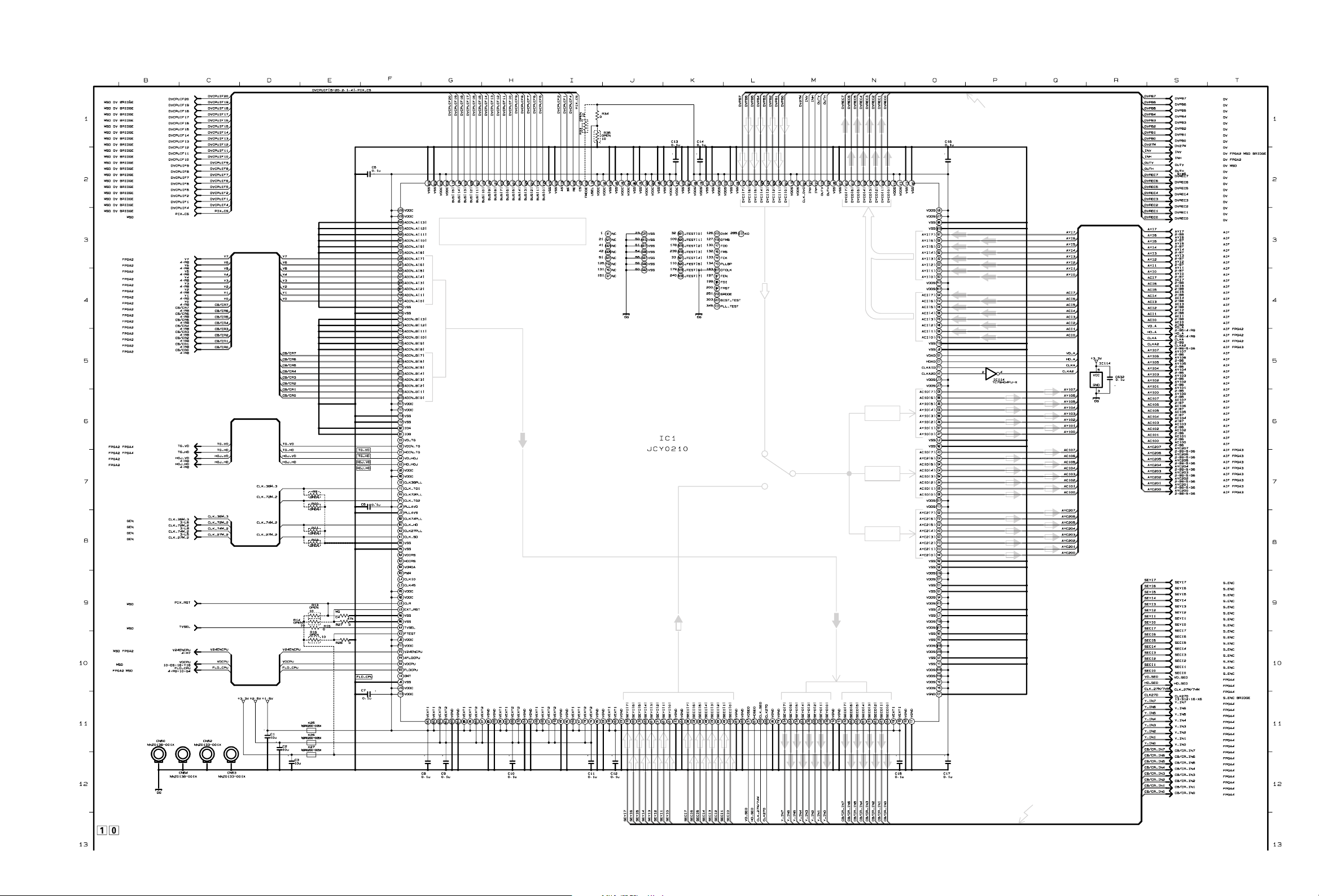

Page 11

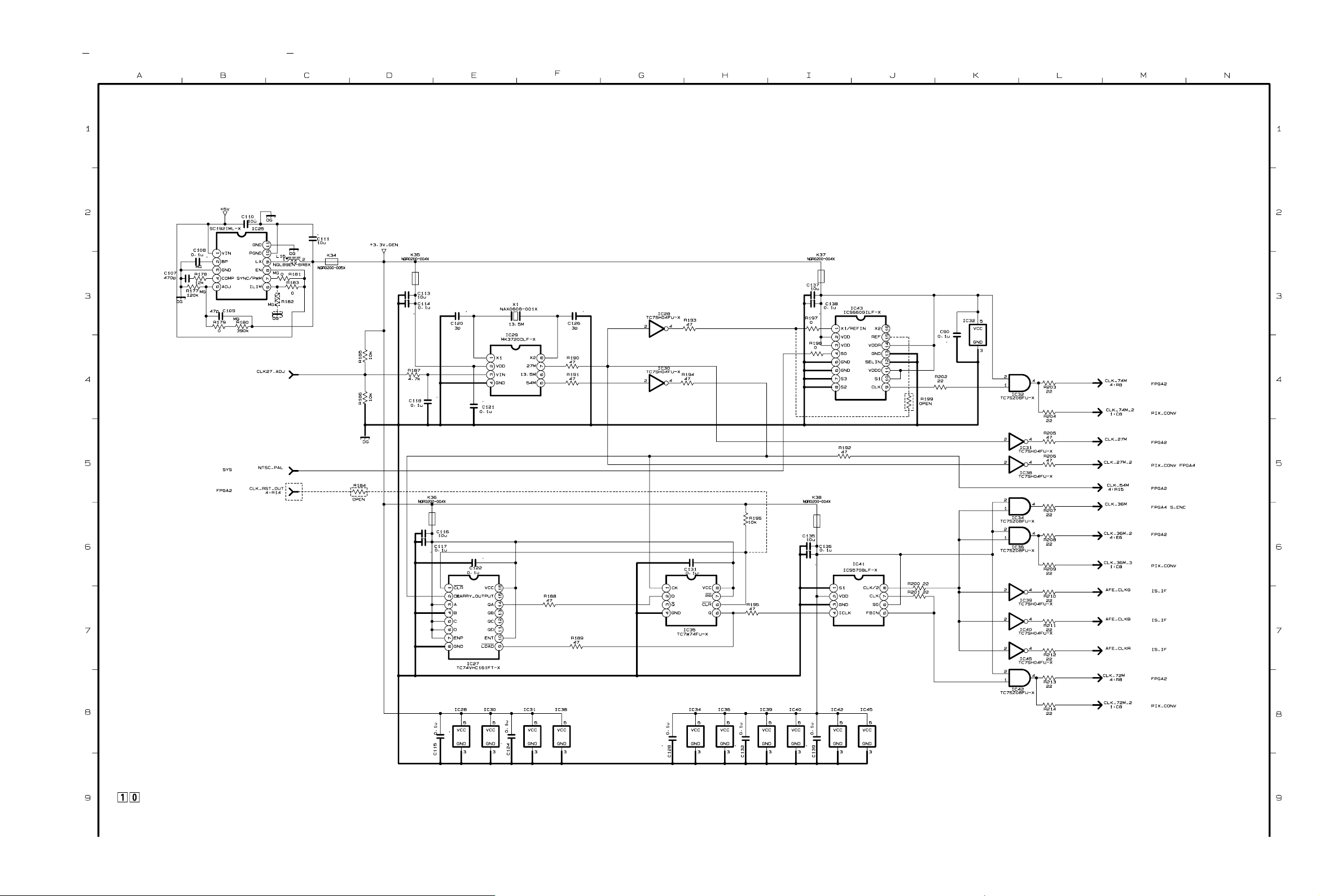

MAIN SCHEMATIC DIAGRAMS(1/18)(Pixel CONV

4.9

)

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:R3;9:S5;10:S12

7:I2

PIX CONVERTER

CONV 1

9:W8

SD

9:W8

9:W8

9:W8

9:W8

9:W7

9:W7

9:W7

9:X14

4:R8;7:E9;9:W7;10:Q13

4:R8;9:W7

10 :F12;9:W6

9:W9

9:W9

9:W9

9:W9

9:W9

9:W9

9:W9

9:W9

4:R9;16:U4

4:R9;16:U4

CONV 2

3:L5;16:X10

7:R10

7:Q8

S

_

ENC

CONV 3

HD

13 : W13

13 : W13

13 : W13

13 : W13

13 : W13

13 : W13

13 : W13

13 : W13

13 : W14

13 : W14

13 : W14

13 : W14

13 : W14

13 : W14

13 : W14

13 : W14

16:U4

16:U4

16 : S5

16:U3

16:U3

16 : U2

16 : U2

16 : U2

16 : U2

16 : U2

16 : U2

16:U3

16:U3

16:U3

16:U3

16:U3

16:U3

16:U3

16:U3

MAIN

4-11 4-11

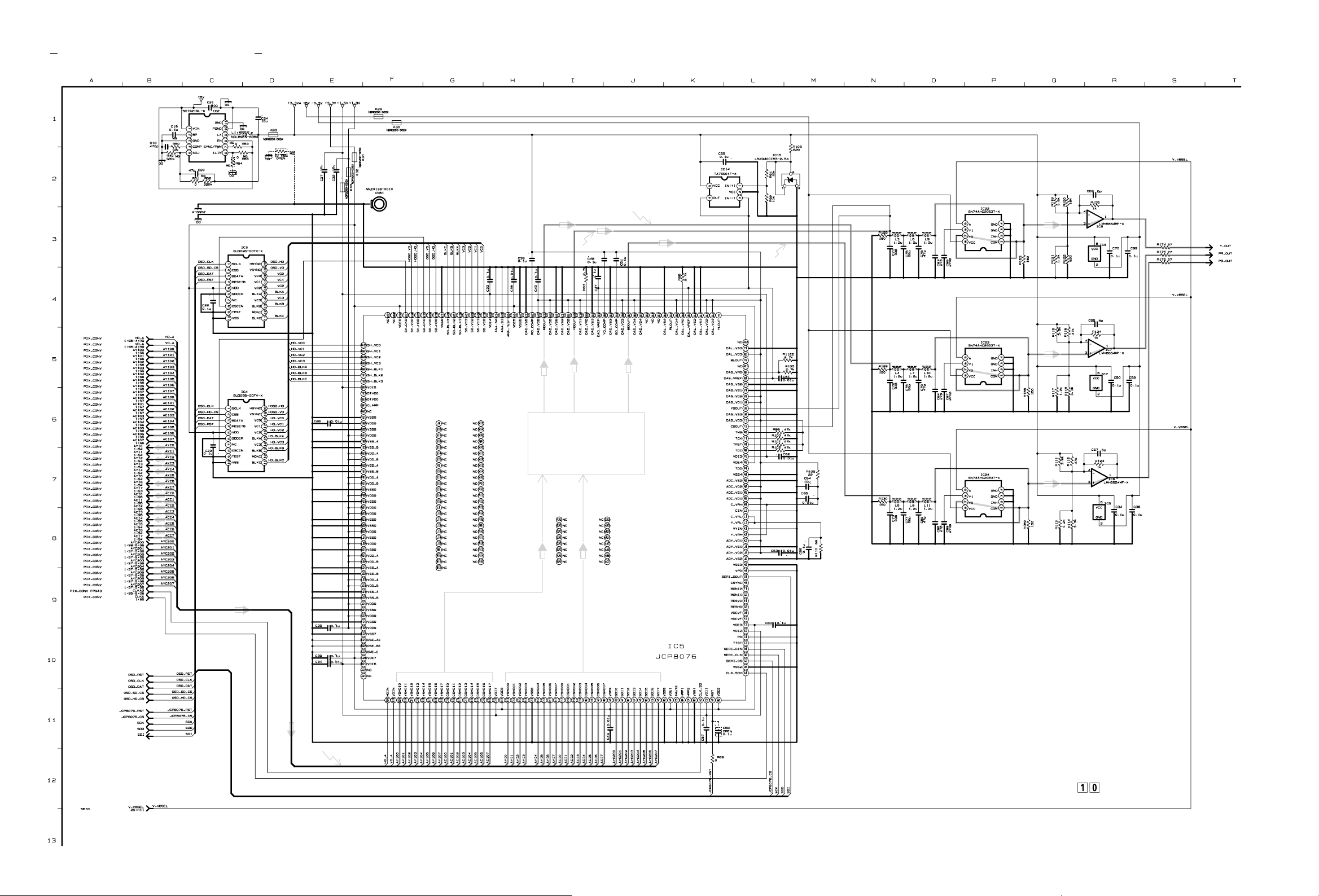

Page 12

MAIN SCHEMATIC DIAGRAMS(2/18

)

(

Analog I/F

)

P

R

FPGA2

FPGA2

FPGA3

FPGA3

FPGA3

FPGA3

FPGA3

FPGA3

FPGA3

FPGA3

Y

Analog I/F

SD/HD

18:E9MIF

_

IF

_

IF

P

B

18:E9MIF

18:E9MIF

_

IF

FPGA3 MIF

FPGA3 MIF

FPGA3 MIF

MIF

MIF

MIF

MIF

FPGA4 MIF

FPGA4 MIF

FPGA4 MIF

_

IF

_

IF

_

IF

_

IF

_

IF

_

IF

_

IF

_

IF

16 :F10;16:X11;18:N9

_

IF

16 :F10;16:X11;18:N9

_

IF

5:Q16;25:M4

5:Q16;18:Q9

5:Q16;18:Q9

18:Q9

18:Q9

18:N9

18:N9

16 :F10;18:N9

HD/SD

MAIN

4-12 4-12

Page 13

MAIN SCHEMATIC DIAGRAMS(3/18

IF

8:N9

)

(

)

GEN

6:F11;18:P9

4:R9;18:H9

1:C8;16:X10

13:E5;16:S6

15:L4

15:L2

15:L7

_

IF

MIF

MAIN

4-13 4-13

Page 14

MAIN SCHEMATIC DIAGRAMS(4/18

5:G8;16:F6;18:J9

5:G8;16:F6;18:J9

15:L5

15:L5

15:L7

15:L7

15:L3

15:L3

15:L4

15:L4

15:L4

15:L4

15:L4

15:L4

15:L4

15:L4

15:L4

15:L2

15:L2

15:L2

15:L2

15:L2

15:L2

15:L2

15:L2

15:L2

)

(

CAM FPGA-2

18:J9

)

5:G6;7:Q13;16:S8

7:E4

7:E9

1:S2;7:E9;9:W7;10:Q13

1:C7;16:U4

1:C7;16:U4

3:L5;18:H9

1:C10;7:Q4

6:D7;10:D11;18:N9

5:G9;16:F7;18:H9

5:G9;16:F7;18:H9

18:H9

5:G9;16:F8;18:H9

5:G9;16:F8;18:H9

18:G9

4-14 4-14

MAIN

Page 15

MAIN SCHEMATIC DIAGRAMS(5/18

)

(

VF FPGA-3

)

4:F5;16:F6;18:I9

4:F5;16:F6;18:I9

4:F14;16:F7;18:H9

4:F14;16:F7;18:H9

4:F15;16:F8;18:H9

4:F15;16:F8;18:H9

4:R6;7:Q13;16:S8

FPGA3

LCD/VF

PROCESS

MAIN

18:Q9

18:Q9

18:Q9

18:Q9

18:Q9

D/A

CONVERTER

D/A

CONVERTER

4-15 4-15

18 :E9

18 :E9

18 :E9

18 :E9

18 :E9

18 :E9

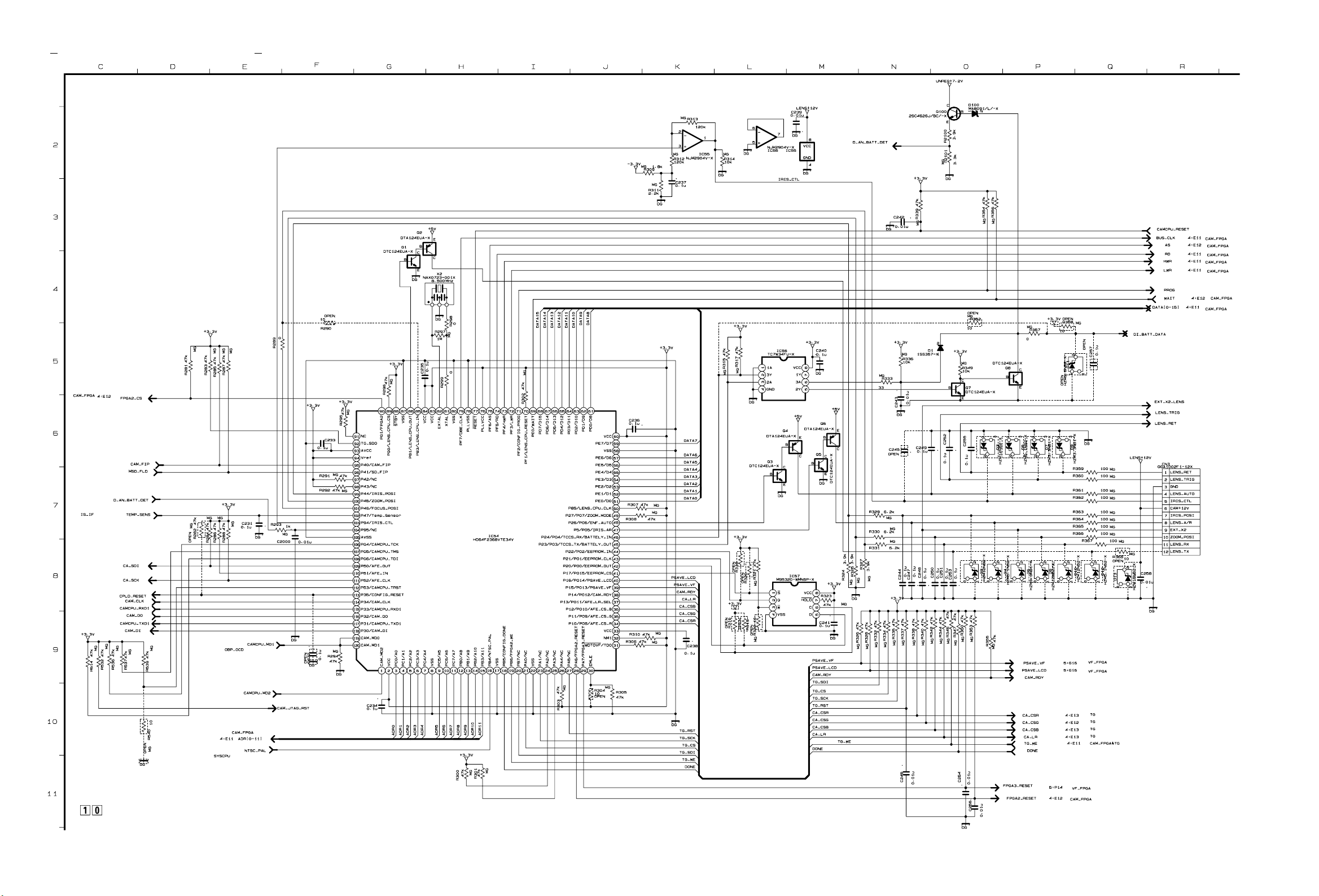

Page 16

MAIN SCHEMATIC DIAGRAMS(6/18

)

(

CAM CPU

)

18:M9

18:M9MIFIF

18 : M9 MIF IF

17 : C7 LOCAL

4:E12;7:D11;18:N9

10 :L2;13:Y15;18:N9

MIF IF18:M9

15:L3

MIF IF18:H9

MIF IF18:N9

MIF IF18:H9

MIF IF18:N9

MIF IF18:L9

MIF IF18:O9

MIF IF18:L9

MIF IF18:O9

18:L9

18:L9

18:M9

18:O9

18:P9MIFIF

18:J9MIFIF

18:J9MIFIF

MIF IF

MAIN

3:C5;18:P9

4-16 4-16

18:J9

MIF IF

Page 17

MAIN SCHEMATIC DIAGRAMS(7/18

)

(

MSD CPU

)

9:U15;9:U16;18:F9

8:L7

8:M6

10 :L13

10:S9

16:F5

6:D7;13:Y15;18:N9

16 :F5

18:P9

1:C1;1:C2;1:C3;9:S5;10:S12

10 :S9

8:M6

4:E12;6:D7;18:N9

18:L9

18:L9

9:X13

10:S9

8:R7;9:F15;18:F9

MAIN

18:L9

10:S9

10:S9

10:S9

4-17 4-17

8:J4;18:M9;18:P9;18:J9

4:R6;5:G6;16:S8

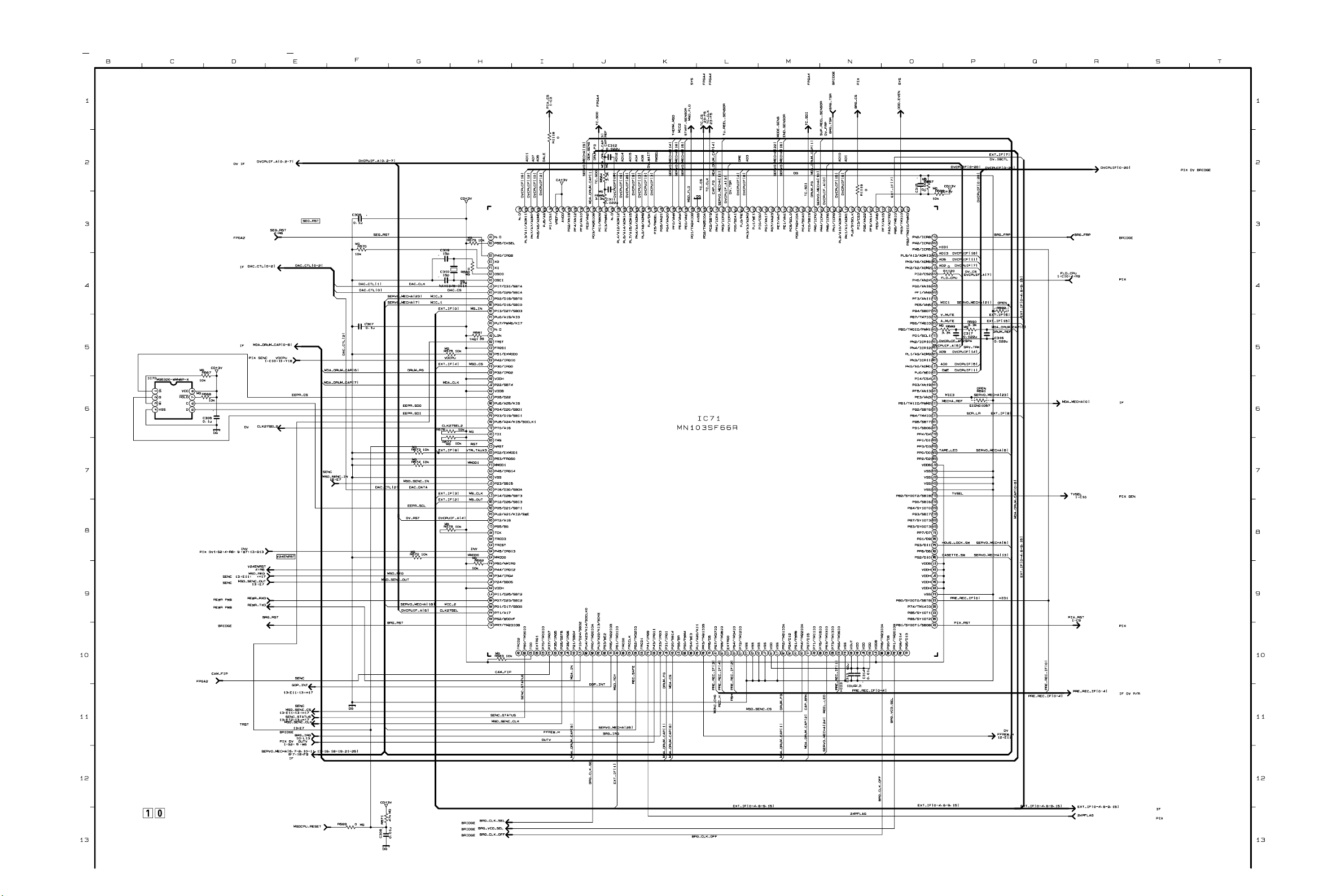

Page 18

MAIN SCHEMATIC DIAGRAMS(8/18

)

(

)

I/F

7:Q6

7:E5

7:F9;18:F9;18:N9

7:E4

9:F16

9:T13

9:F15

10:S8

7:Q11;9:F15;18:F9

MAIN

4-18 4-18

Page 19

MAIN SCHEMATIC DIAGRAMS(9/18

10 :S4 ; 10 :S5

)

(

DV MAIN

)

1:C1;1:C2;1:C3;7:R3;10:S12

7:P12

10 :S5

10 :S5

10 :S5

10 :S6

10 :S6

10 :S6

10 :S5

10 :S5

10 :S5

10 :S5

10 :S5

10 :S6

10 :S6

10 :S6

10 :S6

HD

ECC

PB

DE FORMAT

VITERBI

DV EQ

1:S2;7:F12

1:S2;4:R8;7:E9;10:Q13

ECC

COMP

DE COMP DE SHUFF

SHUFF

SD

SD

SD

16 :U10

16 :U10

16 :W10

REC

DVMAIN

16 :W10

FORMAT

16 :U10

16 :L15 ; 23 :X10

16 :U10

16 :U10

18 :F9

MAIN

18 :G9

18 :F9

7:Q11;8:R7;18:F9

8:N9

18 :F9

8:N8

10 :S6

4-19 4-19

18 :F9

9:N8

7:E3;U16;18:F9

7:E3;U15;18:F9

12 :K5

12 :K5

12 :K5

12 :K5

12 :K5

7:E7

10 :S6 ; 13 :X6 ; 16 :F14

Page 20

MAIN SHEMATIC DIAGRAMS(10/18

)

(

BRIGE

)

HD

HD

13:X6

16 :F15

16 :F15

16 :F14

16 :F14

16 :F14

16 :F14

16 :F14

16 :F14

16 :F14

16 :F13

16 :F15

13:X7;16:F14

16 :F15

16 :F15

16 :F13

16 :F15

HD

MPEGIF OUT

SDRAM

IF

TP GEN

MPEGIF IN

REC MUX

BRIDGE

DEF

HD

9:F4

9:F4

9:F4

9:F4

9:F4

9:F4

9:F4

9:F4

9:F7

9:F7

9:F7

9:F7

9:F7

9:F7

9:F7

9:F7

9:F8

9:F8

9:F8

9:F7

9:F7

9:F7

9:F8

9:X13;13:X6;16:F14

9:N7

7:I13

7:E10

7:I13

7:I13

7:Q4

7:N2

MAIN

4-20 4-20

7:F12

7:N12

1:S2;4:R8;7:E9;9:W7

1:C1;1:C2;1:C3;10:R3;9:S5

1:S11;13:X6

Page 21

MAIN SCHEMATIC DIAGRAMS(11/18

)

(

SD I/F

)

MAIN

4-21 4-21

Page 22

MAIN SCHEMATIC DIAGRAMS(12/18

)

(

1394 PHY

)

18:J9

4-22 4-22

MAIN

Page 23

Page 24

MAIN SCHEMATIC DIAGRAMS(14/18

)

(

SENC RAM

)

11:B6;13:D15

11:B6;13:D15

11:B6;13:D15

11:B6;13:D15

11:B6;13:D15

11:B6;13:D15

11:B6;13:D15

13 : J17;18:J9

MAIN

4-24 4-24

Page 25

MAIN SCHEMATIC DIAGRAMS(15/18

)

(

)

IS I/F

FROM/TO

CN26 ISB

MAIN

FROM/TO

CN27 ISG

FROM/TO

CN28 ISR

4-25 4-25

Page 26

MAIN SCHEMATIC DIAGRAMS(16/18

7:L2

7:J2

7:M2

7:L2

4:F5;5:G8;18:I9

4:F5;5:G8;18:I9

18:I9

4:F14;5:G9;18:H9

4:F14;5:G9;18:H9

4:F15;5:G9;18:I9

4:F15;5:G10;18:I9

2:B12;18:N9

2:B11;X11;18:N9

2:B11;X11;18:N9

18:M9

18:M9

18:P9

)

(

60/30 FPGA-4

)

13 :Y6

13 :X11

13 :X11

13 :X11

13 :X11

13 :X11

13 :X11

13 :X11

13 :X11

13 :W12

13 :W12

13 :W12

13 :W12

13 :W12

13 :W12

13 :W12

13 :W12

13 :Y14

13 :Y14

13 :W10

13 :Y6

13 :Y6

13:Y5

13 :Y6

13:Y5

13:X8

13:X8

13:X8

13:X8

13:X8

13:X8

13:X8

18 :G9

18 :H9

18 :G9

18 :G9

18 :G9

18 :G9

18 :G9

18 :G9

9:W10

9:W11

9:W11

9:W11

9:W10

13:X8

13 :X10

13 :X10

13 :X10

13 :X10

13 :X10

13 :X10

13 :X10

13 :X10

13:X8

13:X9

13:X7

13:X9

13:X8

13:X9

10 :W11 ; L15

18 :Q9

18 :Q9

2:B11;F10;18:N9

2:B11;F10;18:N9

10 :W10

10 :W10

60p →30p

FPGA 4

9:X13;10:S6;13:X6

MAIN

10:B4

10:B4

10:B4

10:B4

10:B4

10:B4

10:B4

10:B4

10:B6

10:B6

10:B6

10:B6

10:B6

10:B6

10:B6

10:B5

10:B6;13:X7

10:B4

10:B6

10:B4

10:B5

10:B4

10:B5

13:Y6

HD

HD

18:J9

9:W11;X10

4-26 4-26

Page 27

MAIN SCHEMATIC DIAGRAMS(17/18

)

(

LOCAL

18:P9

_

PWR

)

MAIN

18:M9

18:P9

18:P9

4-27 4-27

Page 28

MAIN SCHEMATIC DIAGRAMS(18/18

)

(

MIF I/F

)

FROM/TO CN49

MIF

MAIN

7:O2

7:Q13

9:T13

9:E14

16 : U12

16 : U11

16 : U11

16 : U11

16 : U11

16 : U11

16 : U11

9:E14

9:F16

9:D16

7:F12;8:F7

7:Q11;8:R7

7:Q11;8:R7;9:F15

7:E3;9:U15;9:U16

16 : U11

4:F14;5:G9;16:F7

4:F14;5:G9;16:F7

4:F15;5:G9;16:F8

4:F15;5:G10;16:F8

16:F6

12:K6

16:N15

13:E5;I17;14:M3

7:F13

7:E10

7:Q13

7:E9

17:C7

16 : F10

16 : F10

8:F7

8:F6

7:Q13

13:E5

7:Q13

7:Q13

7:Q13

7:Q13

17:C7

13 : C12

13 : E12; 13 : H17

7:Q13

17:C7

17:C4

16 : F10

16 : X10

16 : X10

4-28 4-28

Page 29

4.10

MAIN CIRCUIT BOARD

SIDE A SIDE B

4-29 4-29

Page 30

4.11 MIF & PS CIRCUIT BOARDS

MIF

SIDE BSIDE A

PS

SIDE A SIDE B

4-30 4-30

Page 31

MIF SCHEMATIC DIAGRAMS(1/7)(MIF-MAIN I/F

4.12

)

FROM/TO

CN49

MAIN

4:C11

4:C11

FROM/TO

CN90

FNC

4:C11

6:B2

6:B2

6:B2

MIF

4-31 4-31

Page 32

MIF SCHEMATIC DIAGRAMS(2/7

)

(

SYS CPU

)

4-32 4-32

× :Not mounted

MIF

Page 33

MIF SCHEMATIC DIAGRAMS(3/7

)

(

)

OBP

MIF

4-33 4-33

Page 34

MIF SCHEMATIC DIAGRAMS(4/7

)

(

)

SPIO

FROM/TO

CN13

LINE SEL

FROM/TO

CN9

ZBR

FROM/TO

CN9

AWB

TO

VJK

CN34

FROM/TO

CN10

STA

FROM/TO

CN11

AJK

FROM/TO

CN48

FRL

FROM/TO

CN14

AUDIO

MIF

4-34 4-34

FROM/TO

CN12

EAR

Page 35

MIF SCHEMATIC DIAGRAMS(5/7

)

(CF)

MIF

4-35 4-35

Page 36

MIF SCHEMATIC DIAGRAMS(6/7

FROM/TO

CN65

VF IF

)

(

M-VF LCD

)

FROM/TO

CN24

AUDIO

LCD

DRIVER

FROM/TO

CN65

VF IF

4-36 4-36

MIF

Page 37

MIF SCHEMATIC DIAGRAMS(7/7

)

(

AUDIO AD/DA

)

MIF

4-37 4-37

Page 38

PS SCHEMATIC DIAGRAM4.13

4-38 4-38

PS

Page 39

PRMDA CIRCUIT BOARD

4.14

SIDE A SIDE B

4-39 4-39

Page 40

4.15 PRMDA SCHEMATIC DIAGRAMS(1/3

)

AGC

BIAS

REC

GAIN

MIX

FROM/TO

DRUM

4-40 4-40

PRMDA

Page 41

PRMDA SCHEMATIC DIAGRAMS(2/3

)

FROM

DEW SENSOR

FROM/TO

MOTOR

FROM/TO

CN2

MECHA

CONN

PRMDA

FROM/TO

CAPSTAN

MOTOR

FROM/TO

CN75

PS

4-41 4-41

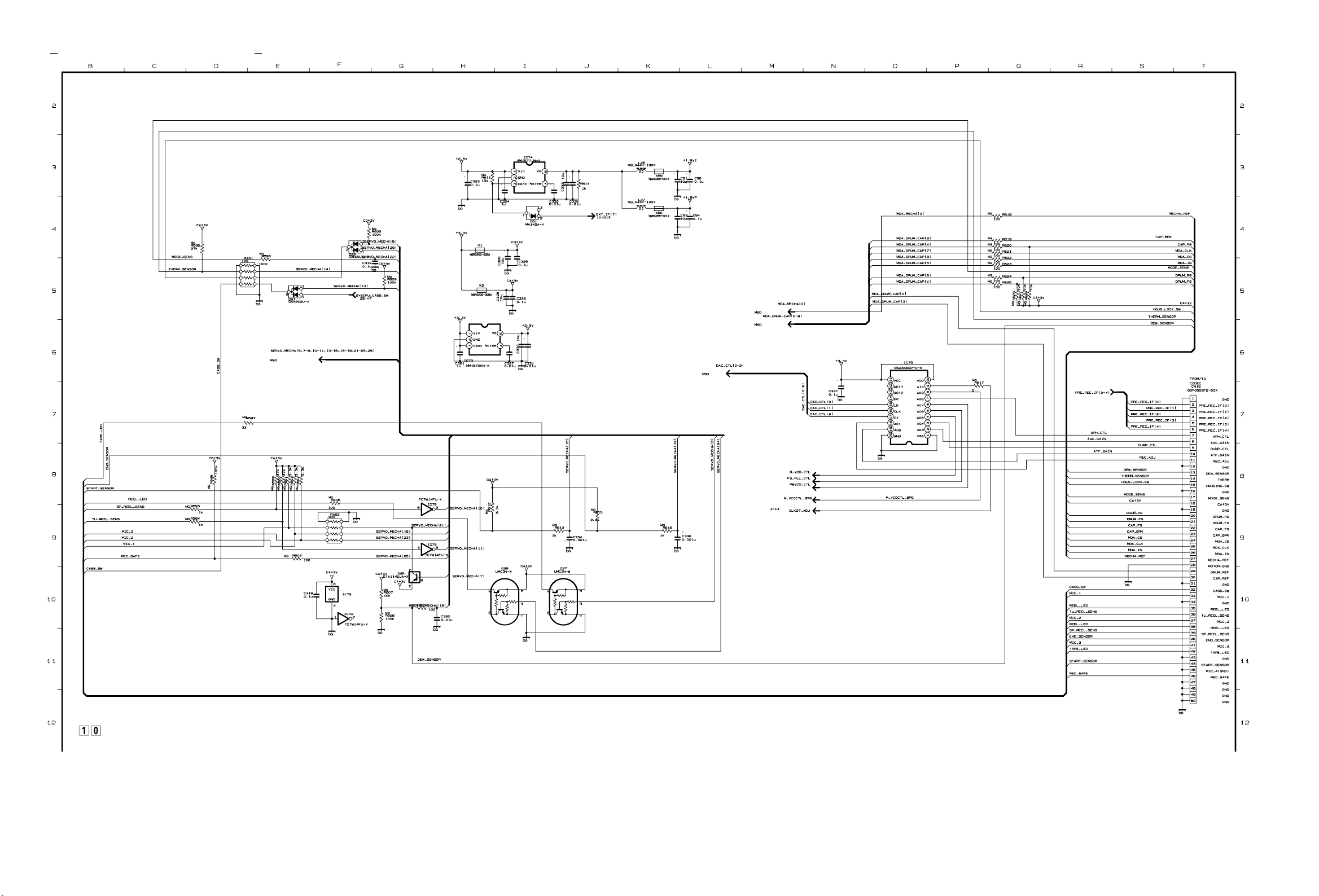

Page 42

PRMDA SCHEMATIC DIAGRAMS(3/3

)

4-42 4-42

PRMDA

Page 43

4.16 AUDIO CIRCUIT BOARD

SIDE A SIDE B

4-43 4-43

Page 44

4.17 AUDIO SCHEMATIC DIAGRAMS(1/2

FROM/TO

CN45

AVR

)

FROM/TO

CN43

LINE SEL

AUDIO

FROM/TO

CN44

MOS

2SC3326/AB/-X

2SC3326/AB/-X

4-44 4-44

Page 45

AUDIO SCHEMATIC DIAGRAMS(2/2

FROM/TO

CN14

MIF

)

FROM/TO

CN24

MIF

FROM/TO

CN62

M-BL

AUDIO

4-45 4-45

Page 46

LINE SELECT SCHEMATIC DIAGRAM

4.18

LINE SELECT

4-46 4-46

Page 47

4.19

LINE SELECT CIRCUIT BOARD

SIDE A SIDE B

4-47 4-47

Page 48

4.20

OPERATION-1 & ETC(MOS,DVOUT,VJK,EAR,DC IN & SD)SCHEMATIC DIAGRAMS

TO

PS

CN53

FROM/TO

CN54

AJK

TO

AUDIO

CN45

FROM/TO

CN34

MIF

FROM/TO

CN12

MIF

FROM/TO

CN18

MAIN

4-48 4-48

Page 49

4.21

OPERATION-1 & ETC(MOS,DVOUT,VJK,EAR,DC IN & SD)CIRCUIT DIAGRAMS

DC IN

VJK

MOS

SIDE A SIDE B

SIDE A

SIDE B

SIDE A SIDE B

SD

EAR

DV OUT

SIDE A SIDE B

SIDE A SIDE B

SIDE A SIDE B

4-49 4-49

Page 50

4.22

OPERATION-2(AVR,STA,SWP,MNU,OPE,EJT,AWB & XLR)SCHEMATIC DIAGRAMS

TO

MAIN

CN4

FROM/TO

CN51

STA

TO

MIF

CN9

TO

STA

CN52

FROM/TO

CN45

AUDIO

TO

CN11

LINE SEL

FROM/TO

CN42

LINE SEL

FROM

CN52

SWP

FROM/TO

CN50

USR

FROM/TO

MNU

CN51

FROM/TO

CN10

MIF

4-50 4-50

Page 51

4.23 OPERATION-2(AVR,STA,SWP,MNU,OPE,EJT,AWB & XLR)CIRCUIT BOARDS

MNU

SIDE A SIDE B

OPE

SWP

SIDE A SIDE B

AVR

SIDE A SIDE B

SIDE BSIDE A

EJT

XLR

SIDE A

SIDE BSIDE A

STA

SIDE A SIDE B

SIDE B

AWB

SIDE A SIDE B

4-51 4-51

Page 52

4.24 OPERATION-3(FTY,USR,FRL,PBM,AJK,FNC & ZBR)& MECHA CONNECTOR SCHEMATIC DIAGRAMS

FROM/TO

CN52

STA

FROM/TO

CN8

FRL

FROM/TO

CN55

PBM

TO

MIF

CN11

FROM/TO

CN55

USR

FROM

MIF

CN90

FROM/TO

CN9

MIF

TO

CN8

FTY

FROM/TO

CN48

MIF

FROM/TO

CN19

MAIN

FROM/TO

CN54

DV OUT

FROM/TO

CN71

PR MDA

MECHA CONN

FROM/TO

DRUM

4-52 4-52

Page 53

4.25 OPERATION-3(FTY,USR,FRL,PBM,AJK,FNC & ZBR)& MECHA CONNECTOR CIRCUIT BOARDS

FTY

SIDE A SIDE B

USR

AJK

SIDE A SIDE B

FRL

SIDE A SIDE B

SIDE A SIDE B

ZBR

SIDE A SIDE B

FNC

SIDE A

PBM

SIDE A SIDE B

MECHA CONN

SIDE A

4-53 4-53

Page 54

4.26 VF IF SCHEMATIC DIAGRAM

FROM/TO

CN22

MIF

FROM/TO

CN60

VF DR

FROM/TO

CN23

MIF

VF IF

4-54 4-54

Page 55

4.27 VF IF & VF DR CIRCUIT BOARDS

VF IF

SIDE A SIDE B

VF DR

SIDE BSIDE A

4-55 4-55

Page 56

4.28

VF DR SCHEMATIC DIAGRAM

FROM/TO

CN60

VF IF

VF DRIVER

TO VF LCD

VF DR

4-56 4-56

Page 57

4.29

MBLSCHEMATIC DIAGRAM

MBL

FROM/TO

CN62

AUDIO

4-57 4-57

FROM/TO

LCD PANEL

Page 58

4.30 M BL CIRCUIT BOARD

SIDE A

4-58 4-58

Loading...

Loading...