Page 1

VIDEO TECHNICAL GUIDE

COPYRIGHT © 2000 VICTOR COMPANY OF JAPAN, LTD.

No. 86056

September 2000

2000 Basic DVC Models

DIGITAL VIDEO CAMERA

Page 2

INDEX

INDEX-1

SECTION 1 OUTLINE OF THE PROCUCTS

1.1 COMPARSION TABLE OF DV MODELS SPECIFICATION BY PRODUCTS YEAR.............1-1

1.1.1 Comparison table of DV models specification by products year.....................................1-1

1.1.2 Specification of the DVC models....................................................................................1-3

SECTION 2 EXPLANATION OF ELECTRICAL CIRCUIT

2.1 CIRCUIT OUTLINE..............................................................................................................2-1

2.1.1 Basic block diagram.......................................................................................................2-1

2.2 CCD (ICX220AK/ICX221BK)................................................................................................2-2

2.2.2 CCD Image Sensor........................................................................................................2-3

2.2.3 Numbers of pixel for main models..................................................................................2-6

2.3 EXPLANATION OF CAMERA CIRCUIT...............................................................................2-7

2.3.1 Present AW / AE control system....................................................................................2-7

2.3.2 AF (Auto Focus) control.................................................................................................2-13

2.3.3 EIS (Electric Image Stabilizer) control............................................................................2-14

2.4 CAMERA SYSREM IC'S FUNCTION...................................................................................2-15

2.4.1 Camera DSP (IC4301: JCY0120) function.....................................................................2-15

2.5 EXPLANATION OF DECK CIRCUIT ....................................................................................2-22

2.5.1 Deck system overall structure........................................................................................2-22

2.5.2 PB equalizer and ATF....................................................................................................2-23

2.5.3 PLL operation................................................................................................................2-24

2.5.4 Basic principle of Viterbi detection .................................................................................2-25

2.5.5 Audio recording mode....................................................................................................2-26

2.5.6 Audio signal processing.................................................................................................2-27

2.5.7 Clock system for audio data...........................................................................................2-28

2.5.8 Deck DSP IC function....................................................................................................2-29

2.5.9 Audio AMP IC function...................................................................................................2-35

2.6 SYSCON CPU.....................................................................................................................2-38

2.6.1 Contents of SYSCON CPU processing..........................................................................2-38

2.6.3 System composition.......................................................................................................2-39

2.6.4 SYSCON CPU block diagram........................................................................................2-40

2.6.5 SYSCON CPU (IC1001: MN1021617HL) pin functions..................................................2-41

2.7 DECK CPU...........................................................................................................................2-44

2.7.1 Contents of DECK CPU processing...............................................................................2-44

2.7.2 DECK system composition.............................................................................................2-44

2.7.3 Tracking Error information..............................................................................................2-45

2.7.4 1394 interface control....................................................................................................2-46

2.7.5 JLIP Video Capture........................................................................................................2-46

2.7.6 DECK CPU block diagram.............................................................................................2-47

2.7.7 Deck CPU (IC1401: MN103004KRH) pin functions........................................................2-48

Page 3

INDEX-2

SECTION 3 HEAD CLOG WARNING

3.1 HEAD CLOG WARNING OF DVC........................................................................................3-1

3.1.1 Structure of Sync Blocks and Error correction................................................................3-1

3.1.2 Error Rate of DVC..........................................................................................................3-3

3.1.3 Previous method of head clog detection ........................................................................3-4

3.1.4 New method of head clog detection...............................................................................3-5

SECTION 4 DOCTOR SYSTEM

4.1 WHAT IS DOCTOR PROGRAM?.........................................................................................4-1

4.1.1 Matching of Doctor Program with Microcomputer Program............................................4-1

4.1.2 Use of Doctor Program for Camcorder...........................................................................4-2

4.1.3 Revision of Service Support System Software for Doctor Program................................4-2

4.1.4 Procedure to Rewrite Doctor Program...........................................................................4-3

4.2 DOCTOR PROGRAM SYSTEM IN THE PRESENT CIRCUMSTANCES.............................4-5

4.2.1 ON/OFF address and Program address.........................................................................4-5

4.2.2 Writing function of EEPROM data..................................................................................4-7

4.2.3 Upgrade of the service support system..........................................................................4-7

Page 4

SECTION 1

OUTLINE OF THE PROCUCTS

1-1

1.1 COMPARSION TABLE OF DV MODELS SPECIFICATION BY PRODUCTS YEAR

1.1.1 Comparison table of DV models specification by products year (1/2)

Model

Function

Battery BN-V11 Ni-Cd

(6V, 1100 mAh)

BN-V12 Ni-Cd

(6V, 1200 mAh)

BN-V20 Ni-MH

(6V, 2000 mAh)

Continuous shooting tim e:

when VF is used:

BN-V12: 1hr.10min.

BN-V20: 1hr.50min.

when LCD is used:

BN-V12: 1hr.

BN-V20: 1hr.40min.

BN-V207 Lithium-ion

(7.2V, 700 mAh)

BN-V214 Lithium-ion

(7.2V, 1400 mAh)

Continuous shooting tim e:

when VF is used:

BN-V207: 1hr.

BN-V214: 2hrs.20min.

BN-V856: 8hrs.30min.

when LCD is used:

BN-V207: 50min.

BN-V214: 1hr.55min.

BN-V856: 7hrs.

BN-V408 Lithium-ion

(7.2V, 800 mAh)

BN-V416 Lithium-ion

(7.2V, 1600 mAh)

BN-V428 Lithium-ion

(7.2V, 2800 mAh)

Continuous shooting tim e:

when VF is used:

BN-V408: 1hr.15min.

BN-V416: 2hrs.30min.

BN-V428: 4hrs.20min.

BN-V856: 8hrs.40min.

when LCD is used:

Charging the battery Charging time: AA-V15 us ed

70 min. (BN-V11)

70 min. (BN-V12)

110 min. (BN-V20)

Charging time: AA-V20 us ed

90 min. (BN-V207)

180 min. (BN-V214)

Charging time: AA-V40 us ed

90 min. (BN-V408)

120 min. (BN-V416)

200 min. (BN-V428)

Viewfinder Color LCD 0.55" 113k pixels

B/W CRT

Color LCD 0.55" 113k pixels

B/W LCD 0.24" 76k pi xels

Color LCD 0.44" 113k pixels

B/W LCD 0.24" 76k pi xels

LCD monitor Non

2.5" 480 × 234 = 112k pixels

3" 480 × 234 = 112k pixels

Horizontal resolution: 240 lines

Amorphous silicon transistor

2.5" 480 × 234 = 112k pixels

3" 480 × 234 = 112k pixels

3.5" 480 × 234 = 112k pixels

Horizontal resolution: 240 lines

Amorphous silicon transistor

←

Image device 1/4"

Total 766 × 596 = 460k pixels

(*799 × 711 = 540k pixels)

Effective aria 611 × 480 = 290k pixels

(*601 × 576 = 350k pixels)

1/4"

Total 998 × 677 = 680k pixels

(*998 × 797 = 800k pixels)

Effective aria 711 × 485 = 340k pixels

(*702 × 575 = 400k pixels)

←

Horizontal resolution 360 Lines 400 Lines

←

Electric image

stabilizer

Yes

←←

Sensitivity 10 lux (*12 lux)

50 IRE Level, Slow Shutter off

16 lux (*18 lux)

50 IRE Level, Slow Shutter off

18 lux

50 IRE Level, Slow Shutter off

Lens specification F1.6 f = 3.9 to 62.4 mm

←

F1.8 f = 3.6 to 36.0 mm

Tele macro Yes

←←

Zoom ratio

Optical zoom: 16

×

Digital zoom: 4×/10× or 8×/20

×

Max. zoom: 160× or 320

×

←

Optical zoom: 10

×

Digital zoom: 4×/10×,25× or 45

×

Max. zoom: 100× ,250× or 450

×

Snapshot 5 mode

With frame

Full

Pin-up

Pin-up 4-division

Pin-up 9-division

←←

Playback snapshot Yes

←←

Playback digital zoom

Yes 10

×

RM-V712U

Yes 4

×

RM-V711U

Yes 10× or 25

×

RM-V716U

2000 Fusion DV Model1998 Fusion DV Model 1999 Fusion DV Model

Table 1-1-1 Comparison table of DV models specification by products year (1/2)

Page 5

1-2

••••

Comparison table of DV models specification by products year (2/2)

Model

Function

Slow motion Yes

RM-V712U

Yes (Frame Advance)

RM-V711U (optional: GR-DVF11U)

Yes (Frame Advance)

RM-V716U

Video auto li

g

ht Yes Yes ( /No

)

Yes

Audio 2ch

(

48kHz,16-bit) /4ch(32kHz,12-bit

)

←←

Snapshot search No

←←

Record end search No

←←

Audio dubbing No (Yes:PAL model,32kHz only,RCU

only)

Yes (32kHz only,RCU only)

←

V.insert editin

g

No

←

Yes (SP onl

y)

Time code Yes

←←

Headphone terminal No

←←

AV output terminal RCA

(Video Audio L/R)

←

Ø3.5 mini

S output terminal Yes

←←

JLIP terminal Yes

←←

PC terminal No Yes (No: GR-DVF11U) Yes

(No: GR-DVF10,DVL100U,DVL305U,

DVL307U)

Digital still image output

terminal

No Yes (No: GR-DVF11U) Yes

(No: GR-DVF10,DVL100U,DVL305U,

DVL307U)

DV terminal No Yes (EG/EK Model Output only) Yes

(Output only: GR-DVL100EG/EK,

DVL108EG/EK,DVL200EG/EK,

DVL300EG/EK,DVL308EG/EK)

JLIP related

software

GV-CB3 JLIP video capture box (optional)

JLIP video capture Ver.2.0

JLIP video producer Ver.1.13

Provided CD-ROM or optional HS-V4KIT

(No: GR-DVF11U)

JLIP video capture Ver.3.0

JLIP video producer Ver.1.16

Provided CD-ROM or optional HS-V14KIT

(No: GR-DVF10,DVL100U,DVL305U,

DVL307U)

JLIP video capture Ver.3.1

JLIP video producer Ver.2.0

Picture Navigator (DSC model only)

JLIP ID number 06

←←

Remote control sensor Yes

←←

Button battery

(only for clock backup)

Yes: CR-2025 type Yes: CR-2032 type (built-in)

←

2000 Fusion DV Model1998 Fusion DV Model 1999 Fusion DV Model

Table 1-1-1 Comparison table of DV models specification by products year (2/2)

Page 6

1-3

1.1.2 Specification of the DVC models

MODEL

SIGNAL

FORMAT

CCD VF

LDC

MONIDVTERMINAL

DIGITAL

STILL

OUTPUT

DSC MMC

DIGITAL

ZOOM

GR-DVF10 NTSC 1/4" 680K B/W 3.0 INCH IN/OUT - - - 250 X

GR-DVA10 NTSC 1/4" 680K COLOR 3.0 INCH IN/OUT YES - - 100 X

GR-DVA11/K NTSC 1/4" 680K COLOR 3.0 INCH IN/OUT YES DSC

MMC

100 X

GR-DVL100U NTSC 1/4" 680K B/W 2.5 INCH IN/OUT - - - 250 X

GR-DVL300U NTSC 1/4" 680K B/W 2.5 INCH IN/OUT YES - - 250 X

GR-DVL305U NTSC 1/4" 680K COLOR 2.5 INCH IN/OUT - - - 250 X

GR-DVL307U NTSC 1/4" 680K B/W 3.0 INCH IN/OUT - - - 250 X

GR-DVL500U NTSC 1/4" 680K COLOR 3.0 INCH IN/OUT YES - - 250 X

GR-DVL505U NTSC 1/4" 680K B/W 3.0 INCH IN/OUT YES DSC - 250 X

GR-DVL507U NTSC 1/4" 680K B/W 3.5 INCH IN/OUT YES - - 250 X

GR-DVL805U NTSC 1/4" 680K COLOR 3.5 INCH IN/OUT YES DSC - 250 X

GR-DVL300UM NTSC 1/4" 680K B/W 2.5 INCH IN/OUT YES - - 250 X

GR-DVL505UM NTSC 1/4" 680K B/W 3.0 INCH IN/OUT YES DSC - 250 X

GR-DVL805UM NTSC 1/4" 680K COLOR 3.5 INCH IN/OUT YES DSC - 250 X

GR-DVL300KR NTSC 1/4" 680K B/W 2.5 INCH IN/OUT YES - - 250 X

GR-DVL805KR NTSC 1/4" 680K COLOR 3.5 INCH IN/OUT YES DSC - 250 X

GR-DVL100EG PAL 1/4" 800K B/W 2.5 INCH OUT

∗

OPTION

- - 100 X

GR-DVL107EG PAL 1/4" 800K B/W 2.5 INCH IN/OUT YES - - 100 X

GR-DVL108EG PAL 1/4" 800K B/W 2.5 INCH OUT YES DSC

MMC

100 X

GR-DVL109EG PAL 1/4" 800K B/W 2.5 INCH IN/OUT YES DSC

MMC

100 X

GR-DVL200EG PAL 1/4" 800K B/W 3.0 INCH OUT YES DSC - 100 X

GR-DVL300EG PAL 1/4" 800K COLOR 3.5 INCH OUT YES - - 100 X

GR-DVL307EG PAL 1/4" 800K COLOR 3.5 INCH IN/OUT YES - - 100 X

GR-DVL308EG PAL 1/4" 800K COLOR 3.5 INCH OUT YES DSC

MMC

100 X

GR-DVL309EG PAL 1/4" 800K COLOR 3.5 INCH IN/OUT YES DSC

MMC

100 X

GR-DVL100EK PAL 1/4" 800K B/W 2.5 INCH OUT

∗

OPTION

- - 100 X

GR-DVL107EK PAL 1/4" 800K B/W 2.5 INCH IN/OUT

∗

OPTION

- - 100 X

GR-DVL108EK PAL 1/4" 800K B/W 2.5 INCH OUT YES DSC

MMC

100 X

GR-DVL109EK PAL 1/4" 800K B/W 2.5 INCH IN/OUT YES DSC

MMC

100 X

GR-DVL200EK PAL 1/4" 800K B/W 2.5 INCH OUT YES DSC - 100 X

GR-DVL300EK PAL 1/4" 800K COLOR 3.5 INCH OUT YES - - 100 X

GR-DVL308EK PAL 1/4" 800K COLOR 3.5 INCH OUT YES DSC

MMC

100 X

GR-DVL105A PAL 1/4" 800K B/W 2.5 INCH IN/OUT

∗

OPTION

- - 450 X

GR-DVL300A PAL 1/4" 800K B/W 2.5 INCH IN/OUT YES - - 450 X

GR-DVL800A PAL 1/4" 800K COLOR 3.5 INCH IN/OUT YES DSC - 450 X

GR-DVL105A-S PAL 1/4" 800K B/W 2.5 INCH IN/OUT

∗

OPTION

- - 450 X

GR-DVL300A-S PAL 1/4" 800K B/W 2.5 INCH IN/OUT YES - - 450 X

GR-DVL800A-S PAL 1/4" 800K COLOR 3.5 INCH IN/OUT YES DSC - 450 X

GR-DVL100EA PAL 1/4" 800K B/W 2.5 INCH IN/OUT

∗

OPTION

- - 450 X

GR-DVL300EA PAL 1/4" 800K COLOR 3.5 INCH IN/OUT YES - - 450 X

GR-DVL300ED PAL 1/4" 800K B/W 2.5 INCH IN/OUT YES - - 450 X

GR-DVL400ED PAL 1/4" 800K B/W 3.0 INCH IN/OUT YES - - 450 X

GR-DVL500ED PAL 1/4" 800K COLOR 3.0 INCH IN/OUT YES - - 450 X

GR-DVL600ED PAL 1/4" 800K B/W 3.5 INCH IN/OUT YES - - 450 X

GR-DVL707ED PAL 1/4" 800K B/W 3.5 INCH IN/OUT YES DSC - 450 X

GR-DVL800ED PAL 1/4" 800K COLOR 3.5 INCH IN/OUT YES DSC - 450 X

CC9370 NTSC 1/4" 680K B/W 3.0 INCH IN/OUT - - - 250 X

∗

OPTION: HS-V14KITE (CD-ROM and Cables)

Table 1-1-2 Specification of the DVC models

Page 7

SECTION 2

EXPLANATION OF ELECTRICAL CIRCUIT

2-1

2.1 CIRCUIT OUTLINE

2.1.1 Basic block diagram

CCD

IC4301

CAMERA_DSP

IC4302

FIELD

MEMORY

TMY(8)

TMC(4)

TG

V.DRV

IC5501

FOCUS

DRIVER

&

ZOOM

DRIVER

IC4851

IRIS

DRIVER

&

HALL

AMP

IC4802-IC4805

SYSCON

CPU

IC1001

DYO(4),DCO(4)

BUS(16)

IRIS_O/C

DATA_OUT

IC3001

DECK_DSP

IC3002

16M

DRAM

IC3501

REC AMP

&

PB AMP

IC1401

DECK

CPU

IC3201

DVEQ

IC3301

DVANA

HSE

AUDIO

AMP

IC2201

RD(16)

RA(10)

MIC UNIT

INT_MIC / L

INT_MIC / R

A_OUT / R

A_OUT / L

MAIN

10

FMY(8)

FMC(4)

H1, H2, RG

XAVD, XAHD

IC1003

E2PROM

IC1004

RTC

32kHz

X1002

ANA_IO

S_DT_IN

AD(16)

S_DT_IN

S_DT_OUT

ON

SCREEN

IC1002

DRIVE+,-

FOCUS (4)

ZOOM (4)

IC1601

MDA

M

M

M

CAPSTAN

MOTOR

DRUM

MOTOR

LOADING

MOTOR

VIDEO

HEAD

IRIS PWM

AIDAT

DODAT

AIDAT

DODAT

MDA_IN

ATF_GAIN, M_VCOCTL, PBVCOCTL, FSPLLCTL

DV_C

LCD_R-Y

DATA_OUT

CLK27,CLK18,CLK13

OPTICAL

BLOCK

CCD_OUT

CDS/AGC

A/D

IC4201

CAM_AD(10)

54MHz

X5501

1394PHY

IC3101

TPA+,TPATPB+,TPB-

DATA_OUT

SUB

S_DT_OUT

LOAD_FWD

LOAD_REV

V1,V2,V3,V4

PD(4)

DYI(4),DCI(4)

HSE

PBDATA

ADDT(16)

ADDT(16)

ADDT(16)

ANA_IO

SPK+,SPK-

SP

PB_ENV

PB_ENV

IRIS PWM

RECC_ADJ

RECC_ADJ

H_GAIN,H_OFFSET

H_GAIN,H_OFFSET

MDA_IN

CCD

40

JUNCTION50

D_COIL_U

D_COIL_V

D_COIL_W

C_COIL_U

C_COIL_V

C_COIL_W

1F

1S

2F

2S

PBO

ATFO

IC5001

DATA_OUT

LCD

DRIVER

IC7601

MONI

LCD

R

G

B

SW

IC7604

VF

LCD

R

G

B

MONITOR20

LCD

DRIVER

IC7101

VF

LCD

EEP

ROM

RXD

TXD

SRV_TX

IF_RX

IC8001

DSC_IF

M32_R/D

CPU

IC8002

IC8003

16Mb

FLASH

DSC

01

REAR70

PC

RX

GND

J552

TX

JLIP

RX

TX

GND

EDIT

J553

IC1302

IC1014

IF_RX

IF_TX

TXD

RXD

EDIT_CTL

JLIP_L

M32_DTIN

PC_RX

PC_TX

JLIP_RX

JLIP_TX

32D(16)

32A(25) 32A(19)

JACK60

ATF_GAIN, M_VCOCTL

PBVCOCTL, FSPLLCTL

LCD_B-Y

LCD_Y

M32_DTOUT

TXD

RXD

M32_DTOUT

M32_DTIN

VIDEO

OUT

DV_Y

MY(8),MC(4)

DV_C

DV_Y

V_OUT

Y_OUT

C_OUT

S_OUT

AV

OUT

DV

AV_DET

MY(8),MC(4)

IC7603

A_OUT / R

A_OUT / L

DATA_OUT

VF_R, VF_G, VF_B, VBLK

VC1, BLK1

DRUM_REF

CAP_REF

DRUM_PG

DRUM_FG

CAP_FG

J501

J503

J502

*only for B/W VF model

DATA_OUT

JACK60

PD(4)

M14D2 Series

OSD_DATA

Fig. 2-1-1 Basic block diagram

Page 8

2-2

2.2 CCD (ICX220AK/ICX221BK)

This IC functions as an interline CCD (Charge

Coupled Device = one of solid-state pickup

devices). Since this CCD conforms to the SD

mode of the DV standard, it has an optimum

number of vertical pixels for the MPEG2 main level

and it realizes a horizontal resolution of 450 TV

lines. As same as general CCD's currently in use,

this CCD is capable of camera shaking correction

and electronic panning and tilting owing to the

extension area of 33 percent extra in both the

vertical and horizontal directions.

Moreover, this CCD provides high quality wide

picture whose aspect ratio is exactly 16:9 without

vertical interpolation.

High sensitivity and low dark current are realized

thanks to adoption of the Super HAD CCD

technology with the color filters of yellow, cyan,

magenta and complementary green mosaic filters.

This CCD has an electronic shutter function that is

able to vary charge storage time by the field period

read system.

Frame period read system is realized by joint use

of the newly developed TG IC.

HØ1

HØ2

ØRG

ØSUB

VØ1

VØ2

VØ3

VDD

Photo

Sensor

VØ4

1

Ye

G

Ye

Mg

Ye

G

Cy

Mg

Cy

G

Cy

Mg

Ye

G

Ye

Mg

Ye

G

Horizontal-Register

Vertical-Register

14131211108 9

7 6 5 4 3 2

GND

VOUT

TEST

∗

Cy

Mg

Cy

G

Cy

Mg

GND

VL

∗

Fig. 2-2-1 CCD block diagram

ELEMENT STRUCTURE Int e rline type CCD image sensor

Optical size 1/4 inch size format

Total pixels NTSC: 998 (H) × 677 (V) approx. 680,000 pixels, PAL: 998×797 approx. 800,000 pixels

Effective pixels NTSC: 962 (H) × 654 (V) approx. 630,000 pixels, PAL: 962×774 approx. 740,000 pixels

4:3 NTSC NT SC: 711 (H) × 485 (V) approx. 340,000 pixels, PAL: 702×575 approx. 400,000 pixels

16:9 18MHZ NTSC: 948 (H) × 485 (V) approx. 460,000 pixels, PAL: 936×575 approx. 540,000 pixels

16:9 5fsc NTSC: 942 (H) × 485 (V) approx. 460,000 pixels, PAL: 922×575 approx. 530,000 pixels

H direction: Front 4 pixels, Rear 32 pixels

V direction: Front 11pixels, Rear 12 pixels

Board material Silicon

OB

Table 2-2-1 CCD functions

Pin No. Label In/Out Descript ion Pin No. Label In/Out Descript ion

1

V

φ

4

In Vertical register transfer clock 8 VOUT Out Video signal output

2

V

φ

3

In Vertical register transfer clock 9 GND - Ground

3

V

φ

2

In Vertical register transfer clock 10

φ

RG

In Reset gate clock

4

V

φ

1

In Vertical register transfer clock 11

Hφ1

In Horizontal register transfer clock

5 GND - Ground 12

H

φ

2

In Horizontal register transfer clock

6 T EST - Open 13

φ

SUB

In Su bstrate clo c k

7 VDD - Power supply 14 VL - Protect transistor bias

Table 2-2-2 CCD pin function

Page 9

2-3

2.2.2 CCD Image Sensor

Main difference in CCD adopted with DVC and VHS-C.

(Pixel)

7.15µ m

5.55

µ

m

(Pixel)

3.80µ m

4.15

µ

m

33% EIS Area

962(H)

711(H)

485(V)

654(V)

Picture Area

13.5MHz

18MHz

510(H)

492(V)

9.54545MHz

(Pixel)

7.3µ m

4.7

µ

m

500(H)

582(V)

9.45833MHz

(Pixel)

4.85µ m

4.65

µ

m

752(H)

582(V)

14.1875MHz

(Pixel)

3.85µ m

3.50

µ

m

33% EIS Area

962(H)

702(H)

575(V)

774(V)

Picture Area

13.5MHz

18MHz

NTSC: effective 630,000 (Image 340,000) pixels PAL: effective 740,000 (Image 400,000) pixels

NTSC: effective250,000 pixels PAL: effective 290,000 pixels

PAL (760H-type): effective 440,000 pixels

510H-type/760H-type 1/4" CCD for VHS-C

960H-type 1/4" CCD (w/ EIS area) for DVC

(GR-DVX7, GR-DVF31/DVL40, GR-DVL300 etc.)

NTSC PAL NTSC PAL PAL (760H)

9.54545MHz

910fH × 2/3

910fH = 4 × fsc

Horizontal drive

frequency

9.45833MHz

908fH × 2/3

14.1875MHz

908fH

DVC VHS-C

18MHz: 1144fH

Picture area:13.5MHz: 858fH

13.5MHz = 18MHz × 3/4

13.5MHz: DVC format Y signal sampling frequency

f

H

= 15.734264KHz (PAL: 15.625KHz): Horizontal sync frequency

f

SC

= 3.579545MHz (PAL: 4.433618MHz): Color sub-carrier frequency

Fig. 2-2-2 Pixel number and pixel size of various CCD

Page 10

2-4

1. Feature of CCD for this model

This CCD adopts the drive frequency and the number of pixels conforming to the DVC format. The

horizontal drive frequency is 18MHz based on 13.5MHz that is Y signal sampling frequency of the DVC

format. And the number of pixels secures the horizontal resolution of 400 lines that conforms to the high

resolution DVC format. Moreover, to keep resolution even if EIS is switched on, the CCD having EIS

(Electric Image Stabilizer) area (approx. 33% in area) is adopted.

Adoption of the usual 1/4”-type CCD realizes miniaturization of the lens unit with keep the zoom ratio of 10

times, and it also realizes miniaturization of whole body.

On the other hand, a pixel size gets smaller as the evil effect of miniaturization and large numbers of pixel.

It becomes unfavorable in the point of CCD sensitivity and dynamic range. For such reason, the minimum

object illumination is determined as 18 Lux EIA standard.

2. Improvement of the CCD for DVC

It is elaborated the following idea to make up for the decline of the sensitivity of CCD at all.

1) Optimization of the on-chip microlens

Loss of incident light is minimized by reduction of ineffective area between microlenses on the pixels.

Photo

shielding AI

Light

Ineffective

Effective

Transfer

section

On-chip microlens On-chip microlens

Sensor

Transfer

section

Ineffective

Light

Photo

shielding AI

Transfer

section

Transfer

section

Effective

Fig. 2-2-3 Structural drawing of CCD image sensor

Page 11

2-5

2) Construction of internal lens

Since the internal lens is constructed between the color filter and gobo, the light condensation

efficiency is improved even for inclined incident light.

Sensor V. Register

On-chip

microlens

Color filter

Poly Si

Gobo

V. Register

Poly Si

Internal len

s

On-chip

microlens

Color filter

Gobo

Sensor

Fig. 2-2-4 Structural drawing of internal lens

Page 12

2-6

2.2.3 Numbers of pixel for main models

Models Optical size Total pixels

Effective pixels

(EIS)

practical pixels

GR-DV1

GR-DVM1

GR-DVX

1/3” approx. 570,000

908H 616V

approx. 530,000

858H 614V

approx. 350,000

704H 499V

GR-DVL /DVL9000U

GR-DVL7 /DVL9600U

1/3”

Progressive

scan

approx. 380,000

758H 504V

–

approx. 360,000

724H 494V

GR-DVY

GR-DVM5U /DV3U

GR-DVF10U /20U

1/4” approx. 460,000

766H 596V

approx. 420,000

724H 582V

approx. 290,000

611H 480V

GR-DVX7

GR-DVM70U /50U

GR-DVA1 /F1

GR-DVF11 /21 /31U

GR-DVA10 /F10 /A11

GR-DVL100 /200 /300U

1/4” approx. 680,000

998H 677V

approx. 630,000

962H 654V

approx. 340,000

711H 485V

GR-DVL700

GR-DVL9800U

1/3”

Progressive

scan

approx. 680,000

1002H 662V

approx. 630,000

962H 654V

approx. 340,000

720H 480V

DSC XGA: 630,000

962H 654V

GR-DV1E

GR-DVM1E

GR-DVXE

1/3” approx. 670,000

908H 728V

approx. 620,000

858H 726V

approx. 420,000

704H 594V

GR-DVL9000E

GR-DVL9500E /9600E

1/3”

Progressive

scan

approx. 450,000

758H 592V

–

approx. 420,000

724H 582V

GR-DVM5E /DV3E

GR-DVF1E /DVF10E

1/4” approx. 540,000

766H 711V

approx. 500,000

724H 697V

approx. 530,000

601H 576V

GR-DVX4E /DVX7E

GR-DVL20 /30 /40E

GR-DVL100 /200 /300E

GR-DVL9200E

1/4” approx. 800,000

998H 797V

approx. 740,000

962H 774V

approx. 400,000

702H 575V

GR-DVL9700E /9800E 1/3”

Progressive

scan

approx. 800,000

1002H 782V

approx. 740,000

962H 774V

approx. 420,000

720H 576V

DSC XGA: 740,000

962H 774V

GR-SXM46 /SX41E

GR-SXM26 /SX21E

1/4” approx. 470,000

795H 596V

–

approx. 440,000

752H 582V

GR-FX11 /FXM16E

GR-FX102 /FXM106S

1/4” approx. 320,000

537H 597V

–

approx. 290,000

500H 582V

VHS-C

NTSC

GR-AXM220U

GR-SXM920U

1/4” approx. 270,000

537H 505V

–

approx. 250,000

510H 492V

DVC

PAL

DVC

NTSC

VHS-C

PAL

Table 2-2-3 Numbers of pixel for main models

Page 13

2-7

2.3 EXPLANATION OF CAMERA CIRCUIT

2.3.1 Present AW / AE control system

The signal-processing block of the present camera system is composed as shown below ( Fig. 2-3-1)

CCD A/D

COLOR

SEPARATION

LPF

MATRIX

ENCODER

PROCESS

AGC

GCA

GCA

Y

R

G

B

Y

C

TG

DRIVE

IRIS DRIVE

CAMERA CPU

IR SENSOR

∗

1

∗

2

∗

3

∗

4

∗

5

∗

1 Iris control

∗

2 Shutter speed setting

∗

3 Analog amp gain (AGC gain)

∗

4 WB setting (RED gain, BLUE gain)

∗

5 Parameter for picture compensation (color reproducibility, S/N ratio…)

Fig. 2-3-1 Camera block configuration

Page 14

2-8

1. AE (Auto Exposure) control

The luminance level of camera output picture is controlled to always be proper exposure regardless of the

brightness and illumination of the object.

1) AE input information

•

Average of luminance level divided a frame picture into 48 blocks passed through the LPF.

•

The area ratio of the sections having luminance components higher than a certain level to the

whole sections.

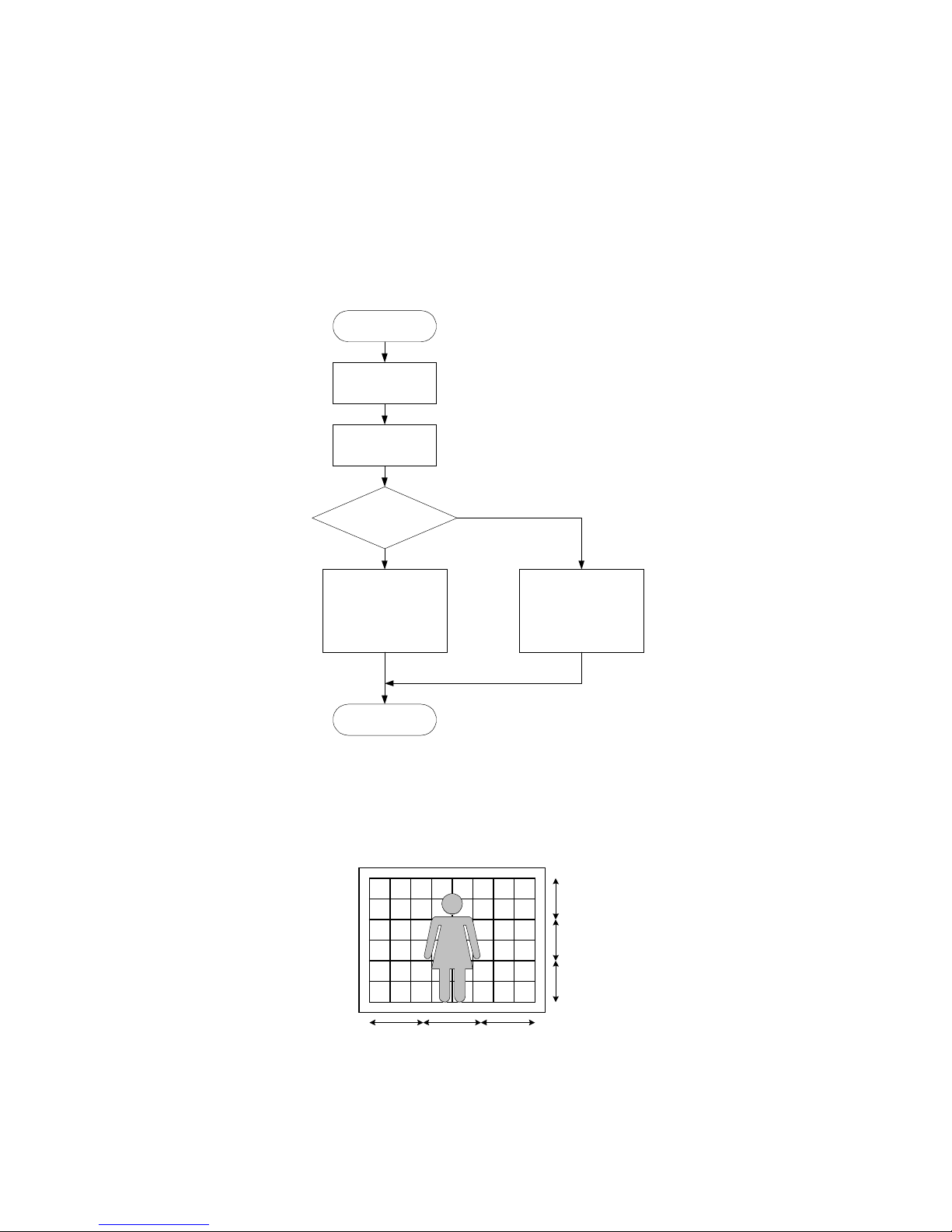

AE control

Weighting of

sectioned data

Caluculation of

evaluation value

Target > Evaluation?

AGC gain down

↓

Slow shutter OFF

↓

Iris close

Iris open

↓

AGC gain up

↓

Slow shutter ON

RET

Fig. 2-3-2 AE control flow chart

2) Weighting of data on sections

Though the respective data on 48 sections are weighted, the basic settin g is to weight the center part

high.

Low

Low

High

High LowLow

Fig. 2-3-3 Weighting of data on sections

Page 15

2-9

3) AE control and output luminance signal level

Gain-up mode: AUTO (OFF and AGC modes are the same as the VHS-C camcorder)

100 IRE

Open

0 IRE

5000 lux 300 lux 40-50 lux 10 lux

Close

MAX

MIN

1/30

1/60

1/240

ON

OFF

50 IRE

LUMINANCE

IRIS

APERTURE

AGC

GAIN

SHUTTER

SPEED

AUTO

LIGHT

ILLUMINATIONBRIGHT DARK

(2)

(1)

(3)

(4)

(5)

(6)

Fig. 2-3-4 AE control and output luminance signal level

Page 16

2-10

(1) When the intensity of illumination is high and iris aperture is stopped down, the iris is opened for

compensating drop of the signal level by changing the shutter speed to high (1/250 sec).

(2) Since raising the AGC gain deteriorates the S/N ratio, the E-E level is slightly lowered in the

exposure compensation by controlling the AGC as compared with the iris control mode.

(3) As the intensity of illumination becomes low and AGC gain rises to maximum, the camera enters

the slow shutter mode (1/30 sec).

(4) When the camera enters the slow shutter mode, the signal level r ises by 6 dB and the AGC gain

drops in inverse proportion to the signal level.

(5) The auto-light is turned on when the illumination turns down a little more after the camera entered

the slow shutter mode and AGC gain rose to the maximum. There is a hysteresis to prevent

hunting as the auto-light is switched on/off.

(6) The intensity of illumination shown in the f igure is just an example and it varies depending on the

object, angle of view, etc.

Page 17

2-11

2. AW (Auto White balance) control

AW control compensates the Red component gain and Blue component gain shown in the camera block

diagram to keep the white balance in the camera picture under every kind of light source.

Basic input data for AW control are three of the following.

(1) R, G, B levels of sections divided a picture into 48 sections.

(2) Data on existence/absence of infrared rays in the light source. This data is used for judging the

sort of the light so urce.

(3) Illumination judged with the exposure compensation parameters (iris/ AGC gain/ shutter speed).

The white balance is controlled by the following setting referring to the R, G, B data on the section that is

judged as a white (uncolored) part of the picture according to the three kinds of data mentioned above.

Red component gain = Green level / Red level

Blue component gain = Green level / Blue level

Besides the white balance control, balance among color phases is controlled by the parameter control in

the color signal processing from RGB to C signal depending on the light source.

1) Light source judging process

IR FLICKER BRIGHT LIGHT

DC component AC component (Over 4000 Lx)

SOURCE

Yes Yes Yes HAROGEN

Yes Yes No

∗

Yes No Yes OUT DOOR

Yes No No OUT DOOR

No Yes Yes FL LIGHT

No Yes No FL LIGHT

No No Yes FL LIGHT

No No No FL LIGHT

∗

: OUT DOOR or HAROGEN (not FL LIGHT)

Table 2-3-1 Light source judging process

Page 18

2-12

2) AWB cont rol algorithm

AWB control

Light source judgment

(Gain limiter setting)

Sunlight?

Gain calculation from white block data

(Calculation value = Target gain)

Gain setting (adjustment) for the sunlight

(Adjustment value = Target value)

Optimum time constant setting for gain

control

Is the WB deviating to

blue?

R-gain up / B-gain down

Is the WB deviating to

red?

R-gain down / B-gain up

RET

YES

NO

NO

NO

YES

YES

The upper and lower limits of each gain are set according to

the ratio between R and B components and judgment of the

light source by the infrared sensor.

Setting of the control time constant to avoid unnatural color

variation.

Fig. 2-3-5 AW control flow chart

The light source of the natural light (sunlight), halogen lamp (indoor) or fluorescent lamp is judged

according to data of the infrared sensor and data on the illumination.

Since the gain to be compensated by the white balance control greatly varies depending on the

device used (CCD, IR cut filter, lens, etc.) and parameter for color separation, settings of limiter,

control time constant and color reproducing parameters differ from model to model.

Page 19

2-13

2.3.2 AF (Auto Focus) control

1. Auto Focus operation during slow shutter mode

Though the basic Auto Focus operation is the sam e as usual, the interval of Auto Focus operation varies

conforming to the timing of the picture data renewal when the camera is in the slow shutter mode. For

example, in case the Gain-up mode is set to Auto, the shutter speed is changed to 1/30(2V) according to

the illumination of the object. Therefore, the Auto Focus operation also works every 2V. The Auto focus

operation works every 4V in Slow-4X mode and every 10V in Slow-10X in the same way.

1/60

Data

Renewal/processing

1/30

VD

Focus

operation

2V

Fig. 2-3-6 AF operation timing in slow shutter mode

2. Improvement of the Low-contrast performance

To improve the AF performance in the low contrast subject (such as the man's face), a route that has low

stage filter (HPF1) is added newly. The low contrast subject contains the frequency element that is not

comparatively high.

BPF HPF2 Rectifier

Peak

Addition

HPF1 Rectifier

Peak

Addition

HPF2 Rectifier

Peak

Addition

AFE

HPE

HPF1

HPF2

BPF

HPF1 Rectifier

Peak

Addition

HPF1 Rectifier

Peak

Addition

HPF2 Rectifier

Peak

Addition

AFE1

HPE1

HPF1

HPF2

HPF2 Rectifier

Peak

Addition

AFE2

HPE2

HPF1: 500KHz

HPF2: 1.7MHz

Previous

New

Fig. 2-3-7 Addition of AFE low stage filter

Page 20

2-14

2.3.3 EIS (Electric Image Stabilizer) control

The accurate compensation without picture quality deterioration is possible by using CCD with expansion

area and correcting it two times.

CCD

CDS / AGC /

ADC

IWD FMC

VRAM

TG/

V_DRIVER

CPU

13.5 MHz18 MHz

Vector

(1) (2)

(3)

(4)

DSP

Fig. 2-3-8 EIS system block diagram

962

654(*774)

800

240(*288)

720

245(*292)

(1) Cutting out at TG (2) Cutting out at IWD

(3) Cutting out at Field Memory (4) Camera output

2 lines mixing transfer

Fig. 2-3-9 EIS operation

Page 21

2-15

2.4 CAMERA SYSTEM IC'S FUNCTION

2.4.1 Camera DSP (IC4301: JCY0120) function

1. Camera DSP (IC4301: JCY0120) internal block diagram

CLK45

ADIN [9:0]

YO

CLR

SSG1

EIS/FMC

VRAM Contol

Vector Detect

ID

CLKYCA

CLK13

CLK13X

YOUT

SSG for TG/YCA

SSG2

CLK13

Main SSG

AUTO

CLKYCA

Auto operation

process

CLK18I

CLK13I

CLK27I

CLKGEN

Clock generate

TVSEL0

Y/C

CLKYCA

Y/C signal

process

IWD

CLK14

Frequency

converter

KIZU

White noise

compensation

SELECT

CLK13

ANA I/F

CLK13

Analog input

interface

NTSC/PAL

Color Encoder

CLKENC2

ENC

CLKENC1

CVF

CLK13

Interface for Color

Viewfer

KASHA

CLK13

Shutter sound

occurrence

D/A Converter

CLKENC1

YDAC

CO

D/A Converter

CLKENC2

CDAC

D/A Converter

CLK13

Y2DAC

Y2O

D/A Converter

CLK13

RYDAC

D/A Converter

CLK13

BYDAC

D/A Converter

KDAC

RYO

RYO

KO

BEND

PWM

AFBEND

AYO [3:0]

ACO [3:0]

COUT

Y2OUT

RYOUT

BYOUT

KOUT

CLKYCA

IRSI

HDYCA

VDYCA

FLDYCA

VBDAT

VBSTART

Test signal generator / Wipe / OSD mix

Hadamard NR / Mix / Signal select

CSYNC

HDANA

VDANA

CSYNC1

DYI [3:0]

DCI [3:0]

EOUT1 EOUT5 EOUT9

EOUT2 EOUT6 EOUT10

EOUT3 EOUT7 EOUT11

EOUT4 EOUT8 EOUT12

CLK27

INHA

INVA

ANACNT

FMY [7:0]

FMC [3:0]

TMY [7:0]

TMC [3:0]

IE1 FMRE1 FMWE1

IE2 FMRE2 FMWE2

OMT

MCLK RAD

FMWR WAD

RAE1 WAE1

RAE2 WAE2

DSC I/F

CLK13

DSC interface

FLDDSC

CLKDSC

HDDSC

VDDSC

CLKYCA

DSYO [7:0]

DSCO [7:0]

DSYI [7:0]

DSCI [7:0]

EDAC

12ch EVR DAC

ESSG

CLK13

SSG for Encoder

CBLK

CSYNC

BF

LSW

HRST4T

VRST4T

VBGEN

CLK13

VBID/WSS

Generator

YCIN

LHFO

ADYC

CLKYCA

ADKZ

HDTG

VDTG

SLEN

OSD I/F

CLK13

CLK13X

OSD Interface

DVC I/F

CLK13

DVC Interface

CLK27

DVSL SLDV

SLCV

FMSLSLFMDSSLSLDS

VBLK0

BLK10

BLK20

OSY_V OSY_1

OSR_V OSY_2

OSB_V

DYO [3:0]

DCO [3:0]

INH

INV

OUTH

OUTV

VR VBLK

VG BLK1

VB BLK2

VC1

VC2

HDOSD

VDOSD

CLKOSD

HDANA13

VDANA13

HDFMC

VDFMC

FLDFMC

OUTH13

OUTV13

CLKYCA

CLK13

CLK13X

CLKENC1

CLKENC2

RE DSTB

LWE HWE

CS RWSEL

ALE USEL0

USEL1

BUS [15:0]

CPU I/F

CPU Interface

CONTROL SINGNAL

DBI[15:0]

VDMDA

HDCPU VDCPU

FRP FLDCPU

Fig. 2-4-1 Camera DSP (IC4301: JCY0120) internal block diagram

Page 22

2-16

2. Camera DSP (IC4301: JCY0120) pin functions (1/6)

Pin No. Label In/Out Description

100 VDMDA Out Vertical reference signal output for MDA

158 PWM Out PWM output

20 CLK45 Out 4.5MHz output

1 VSS - Ground for Digital

251 VDDE - Power supply for Digital (I/O)

255 CSYNCI

191 HDANA

117 VDANA

36 ANACNT

33 AY00

113 AY01

186 AY02

32 AY03

35 AC00

34 AC01

187 AC02

114 AC03

188 INHA

115 INVA

138 ADDVSS - Ground for add Digital

256 VDDE - Power supply for Digital (I/O)

64 VSS - Ground for Digital

69 ADDVDDE - Power supply for add Digital (I/O)

137 DSYO0

208 DSYO1

270 DSYO2

61 DSYO3

136 DSYO4

207 DSYO5

60 DSYO6

59 DSYO7

140 DSCO0

210 DSCO1

272 DSCO2

142 DSCO3

139 DSCO4

209 DSCO5

63 DSCO6

62 DSCO7

211 CLKDSC Out Clock for DSC

141 HDDSC Out Horizontal reference pulse output for DSC

212 VDDSC

143 FLDDSC

70 ADDVSS - Ground for add Digital

271 VDDE - Power supply for Digital (I/O)

146 DSYI0

215 DSYI1

145 DSYI2

Not used-

Not used-

Out Vertical reference pulse output for DSC

In Digital luminance signal input for DSC

Table 2-4-1 Camera DSP (IC4301: JCY0120) pin functions (1/6)

Page 23

2-17

••••

Camera DSP (IC4301: JCY0120) pin functions (2/6)

Pin No. Label In/Out Description

65 DSYI3

276 DSYI4

214 DSYI5

144 DSYI6

213 DSYI7

217 DSCI0

148 DSCI1

68 DSCI2

278 DSCI3

216 DSCI4

67 DSCI5

147 DSCI6

66 DSCI7

30 TVSEL In TV system select (L: NTSC, H: PAL)

112 CPUSEL0 In CPU select (L: n, H: M)

185 CPUSEL1 In CPU select 1 (L: MN2_H: MN3)

273 VDDI - Power supply for Digital (I/O, internal)

275 ADDVDDE - Power supply for add Digital (I/O)

106 TCK

178 TMS

245 TRST In Test terminal (for JTAG with pull-up)

179 TDIN

105 TDOUT

31 ADDVSS - Ground for add Digital

252 VDDI - Power supply for Digital (I/O, internal)

21 ADDVSS - Ground for add Digital

22 VSS - Ground for Digital

125 DACTEST In Test terminal for DAC

184 AVDDA - Power supply for Analog sound

250 DVDDM - Power supply for DAC

248 AVDDV2 - Power supply Analog video

249 AVSSA - Ground for Analog sound

26 AVSSV2 - Ground for Analog video

28 VREFHK In Reference voltage input, top side (for shutter sound)

111 VREFLK In Reference voltage input, bottom side (for shutter sound)

29 K_OUT Out Shutter sound output

25 IREFVF In/Out Reference register terminal for current adjustment, (for VF signal)

110 VREFVF In Reference voltage input terminal for adjustment, (for VF signal)

27 B-Y_OUT Out B−Y signal output for VF

182 R-Y_OUT Out R−Y signal output for VF

24 IREFC In/Out Reference register terminal for current adjustment,(for chromatic signal)

247 VREFC In Reference voltage input terminal for adjustment,(for chromatic signal)

109 C_OUT Out Modulation color signal output

23 IREFY In/Out Reference register terminal for current adjustment,(for luminance signal)

107 VREFY In Reference voltage input terminal for adjustment,(for luminance signal)

181 Y_OUT Out Luminance signal output

183 Y2_OUT Out Luminance signal output for VF

108 AVSSV1 - Ground for Analog video

Not used-

In Digital luminance signal input for DSC

In Digital color difference signal input for DSC

Not used-

Not used-

Table 2-4-1 Camera DSP (IC4301: JCY0120) pin functions (2/6)

Page 24

2-18

••••

Camera DSP (IC4301: JCY0120) pin functions (3/6)

Pin No. Label In/Out Description

246 AVDDV1 - Power supply for Analog video

180 NC - Not used

222 AVSSE3 - Ground for EVR

79 VREFL3 In Reference voltage input for bottom side

75 VREFH3 - Power supply for EVR

78 AVDDE3 - Power supply for EVR

223 DVDDM - Power supply for DAC

220 AVSSE2 - Ground for EVR

221 VREFL2 In Reference voltage input for bottom side

74 VREFH2 In Reference voltage input for top side

75 AVDDE2 - Power supply for EVR

279 NC - Not used

71 AVSSE1 - Ground for EVR

150 VREFL1 In Reference voltage input for bottom side

218 VREFH1 In Reference voltage input for top side

72 AVDDE1 - Power supply for EVR

149 EOUT1 Out EVR output 1

280 EOUT2 Out EVR output 2

219 EOUT3 Out EVR output 3

73 EOUT4 Out EVR output 4

281 EOUT5 Out EVR output 5

151 EOUT6 Out EVR output 6

152 EOUT7 Out EVR output 7

282 EOUT8 Out EVR output 8

77 EOUT9 Out EVR output 9

153 EOUT10 Out EVR output 10

283 EOUT11 Out EVR output 11

154 EOUT12 Out EVR output 12

162 ADDVDDE - Power supply for add Digital (I/O)

126 ADDVSS - Ground for add Digital

167 ADDVDDE - Power supply for add Digital (I/O)

284 VSS - Ground for Digital

286 VDDE - Power supply for Digital (I/O)

269 VSS - Ground for Digital

266 VDDE - Power supply for Digital (I/O)

254 VSS - Ground for Digital

263 ADDVDDE - Power supply for add Digital (I/O)

192 ADDVSS - Ground for add Digital

177 ADDVDDE - Power supply for add Digital (I/O)

101 NAND2_O Out NAND 2 output

102 NAND2_B In NAND 2 input B

176 NAND2_A In NAND 2 input A

175 NAND1_O Out NAND 1 output

242 NAND1_B In NAND 1 input B

103 NAND1_A In NAND 1 input A

15 ADDVDDE - Power supply for add Digital (I/O)

274 VSS - Ground for Digital

267 VDDI - Power supply for Digital (I/O, internal)

Table 2-4-1 Camera DSP (IC4301: JCY0120) pin functions (3/6)

Page 25

2-19

••••

Camera DSP (IC4301: JCY0120) pin functions (4/6)

Pin No. Label In/Out Description

99 CSYNC Out Internal composite sync. Signal output

238 ADDVSS - Ground for add Digital

174 DYO0

18 DYO1

19 DYO2

240 DYO3

239 VSS - Ground for Digital

243 VDDI - Power supply for Digital (I/O, internal)

16 DCO0

17 DCO1

97 DCO2

98 DCO3

173 INH Out Horizontal reference pulse output for DVC REC

172 INV Out Vertical reference pulse output for DVC REC

13 DYI0

14 DYI1

169 DYI2

12 DYI3

277 VDDI - Power supply for Digital (I/O, internal)

244 VSS - Ground for Digital

95 DCI0

170 DCI1

94 DCI2

11 DCI3

171 OUTH In Horizontal reference pulse input for DVC PB

96 OUTV In Vertical reference pulse input for DVC PB

241 VDDE - Power supply for Digital (I/O)

203 MCLK Out Clock output for field memory

49 IE1 Out Input enable

130 FMWE1 Out Memory write enable

48 WAD Out Write address

200 RAD Out Read address

201 FMRE1 Out Memory read enable

50 RAE1 Out R ead address enable

129 FMWR Out Memory write transfer

265 WAE1 Out Write address enable

258 VDDI - Power supply for Digital (I/O, internal)

259 VSS - Ground for Digital

206 ADDVDDE - Power supply for add Digital (I/O)

51 IE2

131 FMWE2

202 FMRE2

52 RAE2

53 WAE2

134 TMY0

205 TMY1

56 TMY2

55 TMY3

Not used-

In Digital luminance signal input for DVC

In Digital colon difference signal input for DVC

Out D igital luminance signal output for DVC

Out D igital luminance signal output for field memory

Out D igital colon difference signal output for DVC

Table 2-4-1 Camera DSP (IC4301: JCY0120) pin functions (4/6)

Page 26

2-20

••••

Camera DSP (IC4301: JCY0120) pin functions (5/6)

Pin No. Label In/Out Description

204 TMY4

133 TMY5

54 TMY6

132 TMY7

135 TMC0

58 TMC1

268 TMC2

57 TMC3

47 ADDVDDE - Power supply for add Digital (I/O)

128 ADDVSS - Ground for add Digital

261 FMY0

197 FMY1

260 FMY2

196 FMY3

195 FMY4

194 FMY5

193 FMY6

257 FMY7

199 FMC0

46 FMC1

127 FMC2

198 FMC3

262 VDDI - Power supply for Digital (I/O, internal)

236 VDDE - Power supply for Digital (I/O)

237 VDDI - Power supply for Digital (I/O, internal)

43 VSS - Ground for Digital

190 ADDVDDE - Power supply for add Digital (I/O)

44 CLK27

42 CLK18

45 CLK13

123 ID In Line discriminate pulse input

189 VDTG Out Vertical reference pulse output for TG

116 HDTG Out Horizontal reference pulse output for TG

253 LHFO Out LHF signal output

86 ADDVDDE - Power supply for add Digital (I/O)

264 VSS - Ground for Digital

118 ADIN9

37 ADIN8

119 ADIN7

38 ADIN6

120 ADIN5

39 ADIN4

121 ADIN3

40 ADIN2

122 ADIN1

41 ADIN0

232 VDDI - Power supply for Digital (I/O, internal)

7 ADDVSS - Ground for add Digital

Digital colon difference signal input form field memory

Digital luminance signal intput form field memory

In

In Clock input

Out Digital colon difference signal output for field memory

In

In Digital signal input from A/D

Out Digital luminance signal output for field memory

Table 2-4-1 Camera DSP (IC4301: JCY0120) pin functions (5/6)

Page 27

2-21

••••

Camera DSP (IC4301: JCY0120) pin functions (6/6)

Pin No. Label In/Out Description

6 ADDVDDE - Power supply for add Digital (I/O)

9 RE In Read enable

235 HWE In High address write enable

8 LWE In Low address write enable

168 ALE In Address latch enable

230 BUS15

87 BUS14

163 BUS13

231 BUS12

2BUS11

88 BUS10

164 BUS9

89 BUS8

3BUS7

90 BUS6

4BUS5

165 BUS4

233 BUS3

5BUS2

91 BUS1

166 BUS0

234 VSS - Ground for Digital

124 CLR In Clear input

160 VDCPU Out Vertical reference pulse output for CPU

228 HDCPU Out Horizontal reference pulse output for CPU

159 FRP Out Frame detect pulse output

227 OMT Out EIS read-out data enable flag output

85 AFBEND Out CPU interrupt pulse output

161 FLDCPU Out Field discriminate pulse output for CPU

287 BEND Out Block average data interrupt pulse output

229 VSS - Ground for Digital

92 DSTB In Data strobe

104 VPD In Test pin for pull-up

10 CS In Chip select

93 RWSEL In Read write select

288 VDDI - Power supply for Digital (I/O, internal)

157 CLKOSD Out Clock output for OSD

84 HDOSD Out Horizontal reference signal for OSD

226 VDOSD Out Vertical reference signal for OSD

225 BLK1 In Blank signal 1

156 BLK2 In Blank signal 2

81 VC1 In Character signal 1

224 VC2 In Character signal 2

155 VR In Character signal 3R

82 VG In Character signal 3G

285 VB In Character signal 3B

80 VBLK In Blank signal 3

83 ADDVSS - Ground for add Digital

In/Out CPU bus I/O

Table 2-4-1 Camera DSP (IC4301: JCY0120) pin functions (6/6)

Page 28

2-22

2.5 EXPLANATION OF DECK CIRCUIT

2.5.1 Deck system overall structure

The DVC deck system has such the IC construction as shown in Fig. 2-5-1. The DV-MAIN IC (IC3001)

serves as the center IC of the deck system IC construction, and this system has been incorporated in the

models of the GR-DVX7 and after.

In recording, the deck system processes image data input from the camera section by shuffling and DV

compression and adds parity codes to it as well as the audio data and sub code data input to the deck

system, and saves those data as sync blocks.

The formatter inside the DV-MAIN IC serves as the 24-25 converter for generating A TF pilot signal and the

data column converter for adapting the data to the digital magnetic recording/playback system (scrambled

interleaved NRZI), and it outputs the processed data to the PRE/REC IC as recording data.

In playback the playback signal transmitted from the PRE/REC IC is input to the DV-ANA (IC3301) and

DV-EQ (IC3201) for waveform equalization, and then supplied to the DV-MAIN IC as playback data. The

DV-EQ IC takes charge of various functions such as playback clock generation, VITERBI decoding, ATF

detection, and so on. For details of its functions, refer to the next page.

The DV-MAIN IC processes playback data by the reverse p rocedure of recording and it transmits playback

data to the camera section and audio section. Since the DV-MAIN IC has the 1394 LINK function, it inputs

and outputs DV data from/to the camera through the 1394 PHY IC (IC3101).

The 16-Mbits DRAM (IC3002) is used as the memory for shuffling/de-shuffling and ECC error correction.

IC3001

DV_MAIN

Shuffling / De-shuffling

Compress / De-compress

ECC Encode / Decode

Formatter / Deformatter

1394 LINK

IC3201

DV_EQ

Auto EQ

Viterbi

PLL det

IC3301

DV_ANA

AGC

PB VCO

IC3501

PRE/REC

HEAD

CAMERA

AUDIO

IC3002

16M DRAM

IC3101

1394 PHY

DV

IN/OUT

Fig. 2-5-1 DVC deck IC structure

Page 29

2-23

2.5.2 PB equalizer and ATF

LPFAGC

BPFGCA

AD1

AUTO

EQ

1+D

VITERBI

PLL

DET

2CH

DAC

PWM

AD2ATF

CPU

I/F

JIG CONN

PB_VCO

IC3202

PB_ENV

DISCRI

RECCLK

PB_DATA

PB_CLK

RECCTL

ADDT

0:15

To:

DECK

CPU

IC3301IC3201 DV_ANADV_EQ

41.85MHz

41.85MHz

+

-

PBO

ATFO

PLLO

CLK

VOA

VOB REFV

PLLE

AINAD2

AINAD1

ATF_GAIN

DISCR

CTL1

DTR

REC:H

SW

VCO

PB:H

VCOC

CLKO

To:

DV

MAIN

Fig. 2-5-2 PB equalizer and ATF block diagram

In the playback mode the PB ENV signal output from the PB amplif ier is branched into two in t he IC3301

DV ANA; one is the signal for playback data and the other is that for ATF. The PBO signal output through

the LPF and AGC is sent to the IC3201 DV EQ as that for playback data, while the ATFO signal output

through the BPF and GCA is also sent to the IC3201 DV EQ as that for ATF.

In the IC3201 DV EQ, the playback signal undergoes digitalization (AD1), waveform equalization (AUTO

EQ), SI-NRZI channel decoding (1+D), and Viterbi-decoding (VITERBI). The resultant signal processed as

mentioned above is output from the IC3201 as the playback data signal. At the same time, the PLL circuit

constructed in this circuitry controls phase correction in order to generate the PB clock synchronizing with

the playback signal. The 41.85MHz signal oscillated by the internal VCO of the IC3301 is outp ut as the PB

clock (PB CLK). Since the internal switch of the IC3301 varies the capacitance of the capacitor, the switch

is turned off to minimize the capacitance of the capacitor when the level of the REC CTL is H, namely, in

the Audio-Dubbing mode. As a result, the response time is shortened in that mode. The discriminator

(DISCRI) compares the 41.85MHz signal oscillated from the VCO with the other 41.85MHz signal

produced from the 81MHz of the main clock in order to detect a difference between the two frequencies. In

the general playback mode, the discriminator outputs a Low-level signal when the frequency difference is

+1%

or more or a High-level signal when the difference is −1% or more. In the other modes, a Low-level

signal is output when the frequency difference is +3% or more or a High-level signal is output when the

difference is −3% or more. When the frequency difference is within ±1% in the general playback mode or

within ±3% in the other modes, the output signal has high impedance. Therefore, a frequency difference, if

there is, is roughly corrected.

Regarding the signal for the ATF, the frequency component of the ATF pilot signal is extracted from t he

playback signal by the BPF and the ATF gain is adjusted by the GCA. Then, the ATF circuit in the IC3201

DV EQ detects a tracking difference using the pilot signals of F0, F1 and F2, and data on the detection

result is transmitted to the servo CPU.

Page 30

2-24

2.5.3 PLL operation

X5501

54MHz

TG

V.DRV

IC5501

VCXO

VCO

X3301

81MHz

PHYCLK

PWM405

IC3001

CLK27

VCO

VCOAUDPWMAUD

VCOAUD

ANA_PD

X3001

24.576MHz

MAIN_VCO

MAIN_VCO

ADJ

FS_PLLADJ

JIG CONN

IC3301

FS_PLL

JIG CONN

CLK

OSC

PC

FRP

GEN

81MHz

41.85MHz

Serial I/F

From

DECK_CPU

12.288MHz

11.289MHz

8.192MHz

DVDSP

DVANA

FRP

GEN

MAIN CLK

1394

LINK

REF

1394

PHY

PC

REF

27MHz FRP

FRP

DOMCK

40.5MHz

Not used

REC CLK

IC3101

ANA_DATA

VCO405I

VCO405

IC3007

Fig. 2-5-3 PLL operation block diagram

The main clock for the deck section operates at a frequency of 40.5MHz, which is equivalent to 18MHz for

the previous models. Since two memories of the SHUFFLE memory and the ECC memory that are

needed for the previous models are integrated into one DRAM, the clock frequency is raised in order to

increase the processing speed. For setting the clock duty ratio exactly at 50%, 40.5MHz clock is produced

from the 81MHz clock. The PLL circuit of the main clock system produces 81MHz clock by the X'TAL

X3301 and VCXO, and sends the 81 MHz clock to the IC3001 DV DSP. Using the frame pulse produced

from the 81MHz pulse as the comparison signal of the PLL, the frame pulse (29.97Hz in NTSC or 25Hz in

PAL) is produced from the 27MHz pulse output from the camera and this frame pulse is used as the

reference signal of the PLL in the general recording and playback modes. However, the frame pulse

produced by decoding the input DV signal is used as the PLL reference signal for phase compa rison in the

1394 input mode. A phase error is output as the PWM405 sig nal, which passes through the filter circuit

and controls the VCXO. For PLL adjustment, the filter output voltage is set nearly at the center (1.2V

±

0.1V) of the tolerance in the condition that the PLL is locked.

There are three audio sampling frequencies (32kHz, 44.1kHz and 48kHz) provided, therefore, master

clocks (8.192MHz, 11.289MHz and 12.288MHz) are produced by the VCO in the IC3301 for the

respective sampling frequencies, and those master clocks are output to the IC3001 DV DSP. For adjusting

the FS-PLL, the respective frequencies are adjusted in the free-run status.

Page 31

2-25

2.5.4 Basic principle of Viterbi detection

Recording

signal

1V

-1V

0V

Threshold level

"1"

"0"

"-1"

PB

signal

"1" "0" "0" "1" "0"

Usual detection

(Hard decision)

Viterbi decoder

0.01.0 -0.4 0.8 0.0 (V)

ERROR !!

A/D converter

"1" "0" "0" "1" "0"

"1" "0" "-1" "1" "0"

Select the most

reliable line

point A

Threshold level

Fig. 2-5-4 Basic principle of Viterbi detection

Fig. 2-5-4 is a conceptual chart showing the basic principle of Viterbi decoding method. Decoding means a

ternary decision that judges differential waveform at the identification point by the ternary criteria when

NRZI-recorded signal is played back.

The previous detection method is based on the ternary criteria of the preset identification level, and this

method is called the hard decision because of the fixed identification level. By this method, for example,

the identification value at the point "A" (in Fig.2-5-4) is "0", which represents an error occurrence.

On the other hand, the Viterbi decoding adopts the soft decision method. In the Viterbi decoding, playback

signal is converted from analog to digital data and then the signal level is read. If the signal level is 0.4V at

the point "A" by ways of example, the previous method judges it as "0", but the Viterbi decoding met hod

detects a possibility that it may be "0" or "1" and i t assu mes two kinds of bit strings of "10010" and "10110".

Next, the Viterbi method introduces another criterion in decision. In the NRZI recording, there is a

regularity in the recording signal and playback waveform. That is to say, there is a fall point between two

rise points in the recording signal. This means that there must be "−1" between "1" and "1". According to

this principle, the bit string of "10010" is theoretically non-existent, and "10110" is consequently selected.

As mentioned above, the Viterbi decoding method utilizes the regularity between bits or the redundancy of

NRZI-recorded signal for error correction. T he above explanation of the Viter bi decoding m ethod is just a

conceptual description, and a high degree of data processing system such as to select the most possible

bit string from a great deal of probabilities is introduced in the actual Viterbi decoding.

Page 32

2-26

2.5.5 Audio recording mode

There are four basic modes in the DVC audio mode as shown in Table 2-5-1, and it is recommended that

the DVC can cover all of the four basic modes by the specifications.

Mode Channel Sampling frequency Quantiazation

48K mode 48kHz

44.1K mode 44.1kHz

32K mode 32kHz

32K-4ch mode 4 32kHz 12-bit non- linear

2 16-bit linear

Table 2-5-1 Audio basic modes

CH 1 CH 2

VIDEO

AUDIO

1 Frame (10 Tracks)

Tape travel

Head motion

CH 1 CH 2

VIDEO

AUDIO

1 Frame (12 Tracks)

Tape travel

Head motion

NTSC 525/60 system

PAL 625/50 system

Fig. 2-5-5 Audio track pattern

Page 33

2-27

The audio recording system of this model is as follows. In the 2-channel mode, quantiazation is linearly

processed in a data unit of 16-bits and the sampling frequency is 48kHz. In regard to the recording pattern,

the first 5 tracks (6 tracks in PAL) of 10 tracks (12 tracks in PAL) in a frame is used for CH1 recording and

the second 5 tracks in a frame is used for CH2 recording. Since audio data for one channel is interleaved

extending over 5 tracks (6 tracks in PAL), it is possible to interpolate audio data by 1/5 (or 1/6 in PAL) if

there is a data error in a track.

In the 4-channel mode, quantiazation is non-linearly processed to convert 16-bits input data into 12-bit

data and the sampling frequency is 32kHz. In regard to the recording pattern, the CH1 is used for

recording sound-1 while the CH2 is used for recording sound-2 which is used for audio dubbing. The

previous models show the audio mode by the sa mpling frequency o f 48 kHz or 32 kHz, how ev er, the recent

models show it by 16-BIT or 12-BIT to meet the market trend.

Sound mode Sam p ling

(MENU) frequency

L ch

R ch

L ch Audio

R ch dubbing

L ch

R ch

Channel

16 BIT 48kH z

CH 1

CH 2

SOUND 1

SOUND 2

12 BIT 32kH z

CH1

CH2

Table 2-5-2 Channel format

2.5.6 Audio signal processing

This model adopts a new audio signal processing IC, which comes equipped with AD and DA converter.

Rch

Lch

PHASE

EQ

EQ

HPF

HPF

ALC

ALC

PHASE

ADC

AUDIO

I/F

DAC

MUTE

MUTE

VOL

VOL

MIX

MIX

MIX

AD

I/F

DA

I/F

CLK

MIX

MIX

16 → 12bits

CONVERT

12 → 16bits

CONVERT

FADER

DRAM

I/F

SP

SHUTTER

IC2201 Audio & A/D_D/A

IC3001 DECK DSP

MIC

CH1

CH2

CH1

CH2

AIDAT

DODAT

DOMCK

DOBCK

DOLRCK

OFF

ON

OFF

ON

EE/REC

PB

PB

EE/REC

A/V OUT

Fig. 2-5-6 Audio block diagram

Page 34

2-28

2.5.7 Clock system for audio data

DOMCK (Master Clock)

Sampling frequency DOMCK

48kHz 256fs: 12.288MHz

32kHz 384fs: 12.288MHz

48kHz 256fs: 12.288MHz

44.1kHz 256fs: 11.2896MHz

32kHz 256fs: 8.192MHz

A. Dubbing 32kHz 256fs: 8.192MHz

REC

PLAY

DOBCK (Serial Clock)

Sampling frequency DOB C K

48kHz 36fs: 1.536MHz

32kHz 36fs: 1.024MHz

48kHz 36fs: 1.536MHz

44.1kHz 36fs: 1.4112MHz

32kHz 36fs: 1.024MHz

A. Dubbing 32k H z 36fs: 1.024MHz

REC

PLAY

DOLRCK (LR Clock)

Sampling frequency DOLRCK

48kHz 48kHz

32kHz 32kHz

48kHz 48kHz

44.1kHz 44.1kHz

32kHz 32kHz

A. Dubbing 32kHz 32kHz

REC

PLAY

Table 2-5-3 Clock frequencies

15 14 13 012 15 14 13 012

120131415120131415

L ch DATA R ch DATA

DOLRCK

DOBCK

DODAT

AIDAT

MSB LSB

Fig. 2-5-7 Timing chart

Page 35

2-29

2.5.8 Deck DSP IC function

1. Deck DSP (IC3001: JCY0106-2) pin functions (1/6)

Pin No. Label In/Out Description

69 VDD - Power supply

1 GND - Ground

134 PWMAUDO Out Audio PLL control signal, (To DVANA: IC3301)

70 VDDS

2VDD

71 VCOAUDI In PB audio b PLL input, (From DVANA: IC3301)

3 VCOAUDO Out PB audio b PLL adjustment voltage output

135 GND - Ground

189 VDD - Power supply

226 OSC32I - L: Fixed (Not used)

72 - - Not used

4 OSC32O - Open (Not used)

136 OSC44I - L: Fixed (Not used)

73 OSC44O - Open (Not used)

190 OSC48I In 24.5MHz clock input

5 OSC48O Out 24.5MHz clock output

227 GND - Ground

137 AUDIOTESTI - L: Fixed

74 AUDIOTESTIO - H: Fixed

6 VDDS - Power supply

191 DILRCK

138 DIBCK

75 DIMCK

7DIDAT

8 AILRCK Out Serial I/O interface channel clock for ADC, (To ADC: IC2101)

76 AIBCK Out Audio serial data clock, (To ADC: IC2101)

139 AIMCK Out Audio master clock, (To ADC: IC2101)

192 PHYCLK Out IEEE 1394 crystal oscillator output (27MHz), (To 1394 PHY: IC3101)

228 GND - Ground

9 AIDAT [0]

77 AIDAT [1]

140 DOLRCK

193 DOBCK

229 DOMCK

10 DODAT

78 VDD - Power supply

141 AOLRCK

230 AOBCK

194 AOMCK

11 AODAT [0] Out Audio serial data output, (To ADC: IC2101)

79 AODAT [1] - Open (Not used)

142 VDDS - Power supply

231 GND - Ground

Open (Not used)-

L: Fixed (Not used)-

Audio serial data input, (From ADC: IC2101)In

- Power supply

Open (Not used)-

Table 2-5-4 Deck DSP (IC3001: JCY0106-2) pin functions (1/6)

Page 36

2-30

••••

Deck DSP (IC3001: JCY0106-2) pin functions (2/6)

Pin No. Label In/Out Description

195 - - Not used

12 YSO [0]

80 YSO [1]

143 YSO [2]

232 YSO [3]

13 BRSO [0]

81 BRSO [1]

196 BRSO [2]

144 BRSO [3]

14 - - Not used

233 VDDS - Power supply

82 YSI [0]

197 YSI [1]

145 YSI [2]

15 YSI [3]

83 BRSI [0]

16 BRSI [1]

146 BRSI [2]

84 BRSI [3]

17 VDD - Power supply

147 OUTH Out Horizontal reference pulse output for DVC PB, (To CAMERA DSP: IC4301)

85 OUTV Out Vertical reference pulse output for DVC PB, (To CAMERA DSP: IC4301)

18 INH In Horizontal reference pulse input for DVC REC, (From CAMERA DSP: IC4301, )

148 INV In Vertical reference pulse input for DVC REC, (From CAMERA DSP: IC4301)

86 GND - Ground

19 VDD - Power supply

87 OSC27I In 27MHz clock input, (From CAMERA DSP: IC4301)

20 OSC27O - Open (Not used)

149 GND - Ground

196 VDD - Power supply

234 - - Not used

88 RAMADRS [0]

21 RAMADRS [1]

150 RAMADRS [2]

89 RAMADRS [3]

199 VDDS - Power supply

22 RAMADRS [4]

235 RAMADRS [5]

151 RAMADRS [6]

90 RAMADRS [7]

23 GND - Ground

200 RAMADRS [8]

152 RAMADRS [9]

Out DRAM address output, (To 16M_DRAM: IC3002)

Out DRAM address output, (To 16M_DRAM: IC3002)

Out DRAM address output, (To 16M_DRAM: IC3002)

Out DVC playback digital luminance signal output, (To CAMERA_DSP: IC4301)

DVC playback digital color difference signal output, (To CAMERA_DSP: IC4301)Out

DVC record digital luminance signal input

(From CAMERA_DSP: IC4301, ANALOG VIDEO I/O: IC3801)

DVC record digital color difference signal input

(From CAMERA_DSP: IC4301, ANALOG VIDEO I/O: IC3801)

In

In

Table 2-5-4 Deck DSP (IC3001: JCY0106-2) pin functions (2/6)

Page 37

2-31

••••

Deck DSP (IC3001: JCY0106-2) pin functions (3/6)

Pin No. Label In/Out Description

91 - - Not used

24 VDD - Power supply

25 RAMWE Out Write enable output, (To 16M_DRAM: IC3002)

92 RAMRAS Out Lower address strobe, (To 16M_DRAM: IC3002)

153 RAMCAS [0] Out Address strobe (Lower bit), (To 16M_DRAM: IC3002)

201 RAMCAS [1] Out Address strobe (Upper bit), (To 16M_DRAM: IC3002)

235 RAMOE Out Output enable (L: active), (To 16M_DRAM: IC3002)

26 VDDS - Power supply

93 RAMDATA [0]

154 RAMDATA [1]

202 RAMDATA [2]

237 RAMDATA [3]

27 RAMDATA [4]

94 RAMDATA [5]

155 RAMDATA [6]

238 RAMDATA [7]

203 VDD - Power supply

28 - - Not used

95 RAMDATA [8]

156 RAMDATA [9]

239 RAMDATA [10]

204 RAMDATA [11]

29 RAMDATA [12]

96 RAMDATA [13]

157 RAMDATA [14]

240 RAMDATA [15]

30 GND - Ground

97 XRESET In Reset pulse input, (From DECK CPU: IC1401)

205 GND - Ground

158 CPUALE In Bus address strobe signal input, (From DECK CPU: IC1401)

31 XCPUDSTB [0] In Bus memory write enable signal input, (From DECK CPU: IC1401)

241 XCPUDSTB [1] In Bus memory read enable signal input, (From DECK CPU: IC1401)

98 XCPURW In Bus read/write select signal input, (From DECK CPU: IC1401)

206 XCPUCS In Chip select input, (From DECK CPU: IC1401)

159 - - Not used

32 XINT - Open (Not used)

99 CPUWAIT In Wait command, (From DECK_CPU: IC1401)

33 CPUAD [0]

160 CPUAD [1]

100 CPUAD [2]

34 CPUAD [3]

161 VDD - Power supply

101 CPUAD [4] In/Out Data (16bits)/Address (15bits) I/O, (From/To DECK CPU: IC1401)

In/Out Audio/Shuffle/ECC memory data I/O, (From/To 16M_DRAM: IC3002)

In/Out Data (16bits)/Address (15bits) I/O, (From/To DECK CPU: IC1401)

In/Out Audio/Shuffle/ECC memory data I/O, (From/To 16M_DRAM: IC3002)

Table 2-5-4 Deck DSP (IC3001: JCY0106-2) pin functions (3/6)

Page 38

2-32

••••

Deck DSP (IC3001: JCY0106-2) pin functions (4/6)

Pin No. Label In/Out Description

35 CPUAD [5]

162 CPUAD [6]

102 CPUAD [7]

36 GND - Ground

103 - - Not used

37 CPUAD [8]

163 CPUAD [9]

207 CPUAD [10]

242 CPUAD [11]

104 VDDS - Power supply

38 CPUAD [12]

164 CPUAD [13]

105 CPUAD [14]

208 CPUAD [15]

39 VDD - Power supply

243 CPUWAITH - H: Fixed (Not used)

165 VDD - Power supply

106 TESTIO [0]

40 TESTIO [1]

209 TESTIO [2]

166 TESTIO [3]

107 TESTIO [4]

41 TESTIO [5]

42 TESTIO [6]

108 TESTIO [7]

167 - - Not used

210 VDDS - Power supply

244 TESTIO [8]

43 TESTIO [9]

109 TESTIO [10]

168 TESTIO [11]

211 TESTIO [12]

245 TESTIO [13]

44 TESTIO [14]

110 TESTIO [15]

169 GND

246 GND

212 TESTIO [16]

45 TESTIO [17]

111 TESTIO [18]

170 TESTIO [19]

247 TESTIO [20]

213 TESTIO [21]

In/Out Data (16bits)/Address (15bits) I/O, (From/To DECK CPU: IC1401)

Open (Not used)-

In/Out Data (16bits)/Address (15bits) I/O, (From/To DECK CPU: IC1401)

In/Out Data (16bits)/Address (15bits) I/O, (From/To DECK CPU: IC1401)

Ground -

Open (Not used)-

Open (Not used)-

Table 2-5-4 Deck DSP (IC3001: JCY0106-2) pin functions (4/6)

Page 39

2-33

••••

Deck DSP (IC3001: JCY0106-2) pin functions (5/6)

Pin No. Label In/Out Description

46 TESTIO [22]

112 TESTIO [23]

171 VDD - Power supply

248 - - Not used

47 SCANENABLE

113 SCANMODE

214 TRST In Reset signal input for boundary scan

172 TDI - H: Fixed (Not used)

48 TCK - L: Fixed (Not used)

249 TMS - H: Fixed (Not used)

114 TDO - Open (Not used)

215 TEST - L: Fixed (Not used)

173 VDD - Power supply

49 PHYDATA [3]

115 PHYDATA [2]

50 PHYDATA [1]

174 PHYDATA [0]

116 VDDS - Power supply

51 SCLK Out IEEE1394 system clock (49.152MHz), (To 1394PHY:IC3101)

175 LOCONT - H: Fixed

117 XPHYISO Out Link interface isolation status (H: Enable), (To 1394PHY: IC3101)

52 PHYCTL [1]

176 PHYCTL [0]

118 PHYLREQ - IEEE1394 link request signal output, (To 1394PHY:IC3101)

53 GND - Ground

119 VDD - Power supply

54 EXTCLKIN

177 EXREQ

216 EXRW - H: Fixed (Not used)

250 EXREADEMPTY

120 EXWRITEFULL

55 VDDS - Power supply

178 - - Not used

121 EXTDATA [0]

217 EXTDATA [1]

56 EXTDATA [2]

251 EXTDATA [3]

179 EXTDATA [4]

122 EXTDATA [5]

57 EXTDATA [6]

218 EXTDATA [7]

180 VDD - Power supply

123 GND - Ground

In/Out Link interface data input/output, (From/To 1394PHY: IC3101)

Open (Not used)-

L: Fixed (Not used)-

L: Fixed (Not used)-

Link interface control (H: output), (From/To 1394PHY: IC3101)In/Out

Open (Not used)-

Open (Not used)-

Table 2-5-4 Deck DSP (IC3001: JCY0106-2) pin functions (5/6)

Page 40

2-34

••••

Deck DSP (IC3001: JCY0106-2) pin functions (6/6)

Pin No. Label In/Out Description

58 PWM405O Out 40.5MHz (PLL control output) 1/2 frequency of VCO405I, (To DVANA: IC3301)

59 VDDS

124 VDD

181 VCO405I In 81MHz VCO reference clock input, (From DVANA: IC3301)

219 VCO405O - Open (Not used)

252 GND - Ground

60 VDD - Power supply

125 CLK81SEL In H: Fixed (Not used)

182 FRRES - L: Fixed

220 FRREF In Frame reference signal input, (From DECK CPU: IC1401)

253 SERVOFRREF - Open (Not used)

61 TRKREF In Drum servo reference signal input (150Hz), (From DECK CPU: IC1401)

126 SERVOTRKREF - Open (Not used)

183 GND - Ground

254 - - Not used

221 PF [0]

62 PF [1]

127 SBE Out Sync block error (Error pulse output)

184 HID

255 HSP

222 - - Not used

63 PBDATA In VITERBI processing termination playback data input, (From DVEQ: IC3201)

128 PBCLK In VITERBI processing termination playback clock input, (From DVEQ: IC3201)

185 VDDS - Power supply

256 TPNO [0]

64 TPNO [1]

129 TPNO [2]

223 RECDATA Out HSE (record data) output, (To PRE/REC: IC3501)

186 RECCTL Out Recording current control (H: ON), (To DVANA: IC3301)

65 SPA Out Pulse output for ATF sample, (To DVEQ: IC3201)

225 RECCLK Out Recording reference clock 41.85MHz