ISSI IS6MC256K-66, IS6MC256K-60, IS6MC256K-50 Datasheet

|

|

|

|

|

|

|

|

|

|

® |

|

|

|

IS6MC256K |

|

|

|

|

|

|

ISSI |

|

|

|

|

|

|

|

|

|

|

|

|

® |

|

|

||

|

IS6MC256K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

256KB CMOS 3.1 COASt CACHE MODULE |

PRELIMINARY |

||||||||||

|

FOR THE INTEL PENTIUM™ CPU |

FEBRUARY 1997 |

|

|

|

|||||||

FEATURES

•Low-cost, card-edge low-profile (CELP) module with 160 leads

•For Intel Pentium CPU-based systems

•Operates with Pentium CPU clock speeds up to 66 MHz

•Separate 5V and 3.3V power supplies

•Multiple GND pins and decoupling capacitors for maximum noise immunity

•CMOS SRAMs for low power

•Conforms to Intel COASt specification

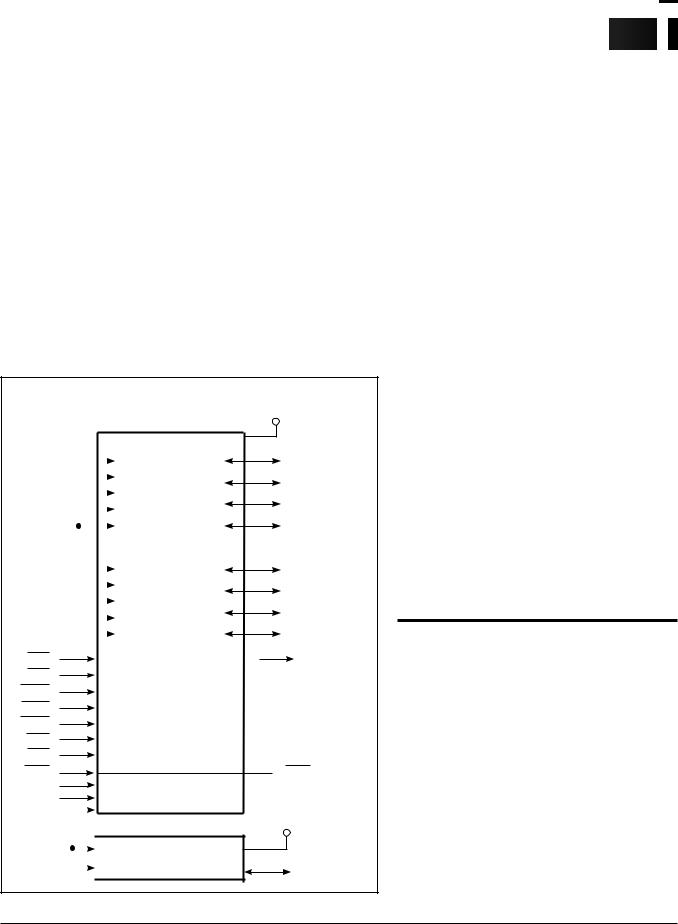

IS6MC256K FUNCTIONAL BLOCK DIAGRAM

256KB PIPELINED BURST MODULE

|

|

|

|

|

|

|

CWE0 |

|

|

32K x 32 |

|||

|

||||||

|

|

|

|

|||

|

CWE1 |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

Pipelined |

CWE2 |

|

|

|

|||

|

|

Burst |

||||

|

|

|

|

|

|

|

CWE3 |

|

|

|

|||

|

|

SRAM |

||||

|

CLK0 |

|

|

|

||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

32K x 32 |

|

|

|

|

|

|

|

CWE4 |

|

|

|

|||

|

|

Pipelined |

||||

|

|

|

|

|

|

|

CWE5 |

|

|

|

|||

|

|

Burst |

||||

|

|

|

|

|

|

|

CWE6 |

|

|

|

|||

|

|

SRAM |

||||

|

|

|

|

|

|

|

|

CWE7 |

|

|

|

|

|

|

|

|||||

CCS

COE

ADSP

CADS

CADV

GWE

BWE

ECS1

A3

A4

A17-A5 |

|

|

|

|

8K x 8 |

||

|

|

|

|

||||

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TAG SRAM |

|

TWE |

|

|

|

|

||

|

|

||||||

|

|

|

|

|

|

|

|

+3.3V

D7-D0

D15-D8

D23-D16

D31-D24

D39-D32

D47-D40

D55-D48

D63-D56

PD0

PD1

PD1

PD2

PD2

PD3

PD3

PD4

PD4

ECS2

ECS2

+5V

TIO7-TIO0

DESCRIPTION

The ISSI IS6MC256K is a secondary cache module designed for use with Intel Pentium CPUbased systems. This ISSI synchronous cache module uses IS61C632 32K x 32 pipelined synchronous burst static RAMs which are mounted on a multilayer board. In addition, this module uses a single 5V 8-bit wide CMOS SRAM for the tag.

On-board logic, 3.3V data RAM, and a 5V tag RAM provide an exact interface between the module and the PC chipset. Five PD (presence detect) input pins allow the system to determine the particular cache configuration.

ISSI's CELP 160-lead module provides space savings that allows the customer to design additional functions into the system or to shrink the size of the motherboard.

All inputs and outputs are TTL-compatible. Multiple GND pins and on-board decoupling capacitors provide maximum protection from noise.

PRESENCE DETECT TABLE

PD4 |

PD3 |

PD2 |

PD1 |

PD0 |

MODULE |

NC |

NC |

NC |

NC |

NC |

No Cache Present |

|

|

|

|

|

|

GND |

NC |

GND |

NC |

NC |

IS6MC256K |

This document contains PRELIMINARY data. ISSI reserves the right to make changes to its products at any time without notice in order to improve design and supply the best possible product. We assume no responsibility for any errors which may appear in this publication. © Copyright 1997, Integrated Silicon Solution, Inc.

Integrated Silicon Solution, Inc.

SR004-1B-297

IS6MC256K

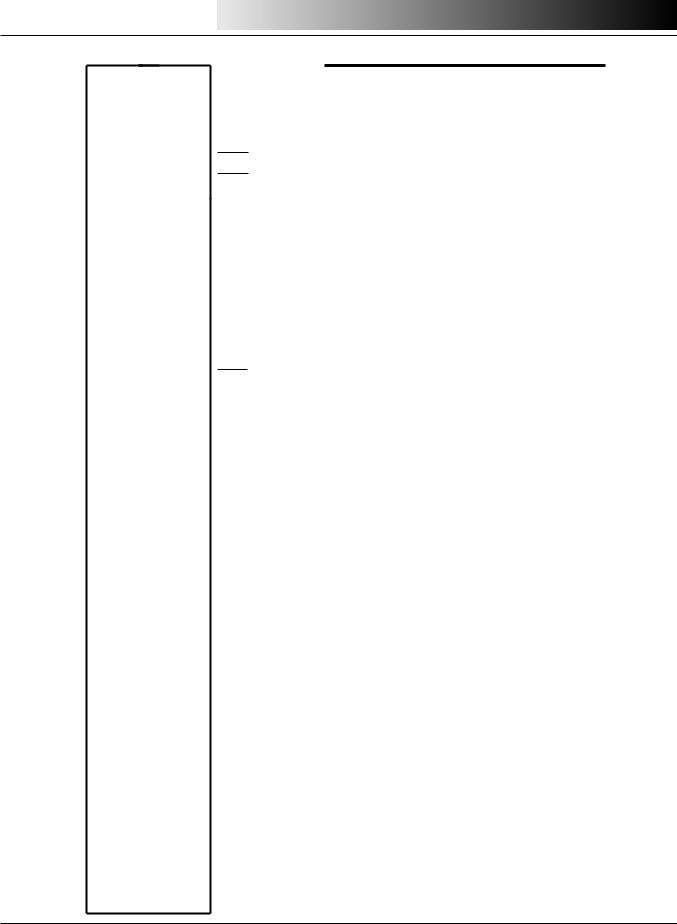

PIN CONFIGURATION

|

|

GND |

81 |

|

|

|

|

TIO1 |

82 |

|

|

|

|

TIO7 |

83 |

|

|

|

|

TIO5 |

84 |

|

|

|

|

TIO3 |

85 |

|

|

|

|

NC |

86 |

|

|

|

VCC5 |

87 |

|

||

|

|

NC |

88 |

|

|

|

CADV |

|

89 |

|

|

|

|

GND |

90 |

|

|

|

|

COE |

91 |

|

|

|

CWE5 |

|

92 |

|

|

CWE7 |

93 |

|

|||

CWE1 |

94 |

|

|||

|

VCC5 |

95 |

|

||

CWE3 |

96 |

|

|||

|

|

NC |

97 |

|

|

|

|

NC |

98 |

|

|

|

|

GND |

99 |

|

|

|

|

NC |

100 |

|

|

|

|

A4 |

101 |

|

|

|

|

A6 |

102 |

|

|

|

|

A8 |

103 |

|

|

|

|

A10 |

104 |

|

|

|

VCC5 |

105 |

|

||

|

|

A17 |

106 |

2X80SC) |

|

|

|

GND |

107 |

||

|

|

A9 |

108 |

|

|

|

|

A14 |

109 |

|

|

|

|

A15 |

110 |

|

|

|

|

NC |

111 |

CELP |

|

|

|

PD0 |

112 |

||

|

|

PD2 |

113 |

|

|

|

|

PD4 |

114 |

(BURNDY |

|

|

VCC5 |

119 |

|||

|

|

GND |

115 |

|

|

|

|

CLK0 |

116 |

|

|

|

|

GND |

117 |

|

|

|

|

D63 |

118 |

|

|

|

|

D61 |

120 |

CONNECTOR |

|

|

|

D59 |

121 |

||

|

|

D57 |

122 |

|

|

|

|

GND |

123 |

|

|

|

|

D55 |

124 |

|

|

|

|

D53 |

125 |

|

|

|

|

D51 |

126 |

OF |

|

|

|

D49 |

127 |

||

|

|

GND |

128 |

VIEW |

|

|

|

D47 |

129 |

||

|

|

D45 |

130 |

|

|

|

|

D43 |

131 |

TOP |

|

|

VCC5 |

132 |

|||

|

|

D41 |

133 |

|

|

|

|

D39 |

134 |

|

|

|

|

D37 |

135 |

|

|

|

|

GND |

136 |

|

|

|

|

D35 |

137 |

|

|

|

|

D33 |

138 |

|

|

|

|

D31 |

138 |

|

|

|

VCC5 |

140 |

|

||

|

|

D29 |

141 |

|

|

|

|

D27 |

142 |

|

|

|

|

D25 |

143 |

|

|

|

|

GND |

144 |

|

|

|

|

D23 |

145 |

|

|

|

|

D21 |

146 |

|

|

|

|

D19 |

147 |

|

|

|

VCC5 |

148 |

|

||

|

|

D17 |

149 |

|

|

|

|

D15 |

150 |

|

|

|

|

D13 |

151 |

|

|

|

|

GND |

152 |

|

|

|

|

D11 |

153 |

|

|

|

|

D9 |

154 |

|

|

|

|

D7 |

155 |

|

|

|

VCC5 |

156 |

|

||

|

|

D5 |

157 |

|

|

|

|

D3 |

158 |

|

|

|

|

D1 |

159 |

|

|

|

|

GND |

160 |

|

|

2

®

1GND

2TIO0

3TIO2

4TIO6

5TIO4

6NC

7VCC3

8TWE

9CADS

10GND

11CWE4

12CWE6

13CWE0

14CWE2

15VCC3

16CCS

17GWE

18BWE

19GND

20A3

21A7

22A5

23A11

24A16

25VCC3

26NC

27GND

28A12

29A13

30ADSP

31ESC1

32ESC2

33PD1

34PD3

35GND

36NC

37GND

38D62

39VCC3

40D60

41D58

42D56

43GND

44D54

45D52

46D50

47D48

48GND

49D46

50D44

51D42

52VCC3

53D40

54D38

55D36

56GND

57D34

58D32

59D30

60VCC3

61D28

62D26

63D24

64GND

65D22

66D20

67D18

68VCC3

69D16

70D14

71D12

72GND

73D10

74D8

75D6

76VCC3

77D4

78D2

79D0

80GND

PIN DESCRIPTIONS

A17-A3 |

Address Inputs |

A17-A5 |

Tag Address Inputs |

|

|

CLK0 |

Clock Input |

|

|

D63-D0 |

Cache Data Inputs/Outputs |

|

|

TIO7-TIO0 |

Tag Inputs/Outputs |

|

|

PD0-PD4 |

Presence Detect Pins |

|

|

COE |

Cache Data Output Enable Input |

|

|

TWE |

Tag Write Enable Input |

|

|

CWE7-CWE0 Cache Data Write Enable Input |

|

|

|

CCS |

Cache Data Chip Enable Input |

|

|

CADS |

Cache Address Status Input |

|

|

ADSP |

Processor Address Status Input |

|

|

CADV |

Burst Address Advance |

|

|

GWE |

Global Write Input |

|

|

BWE |

Byte Write Enable Input |

|

|

ECS1 |

Expansion Chip Select Input |

|

|

ECS2 |

Expansion Chip Select Output |

|

|

Integrated Silicon Solution, Inc.

SR004-1B-297

Loading...

Loading...