Page 1

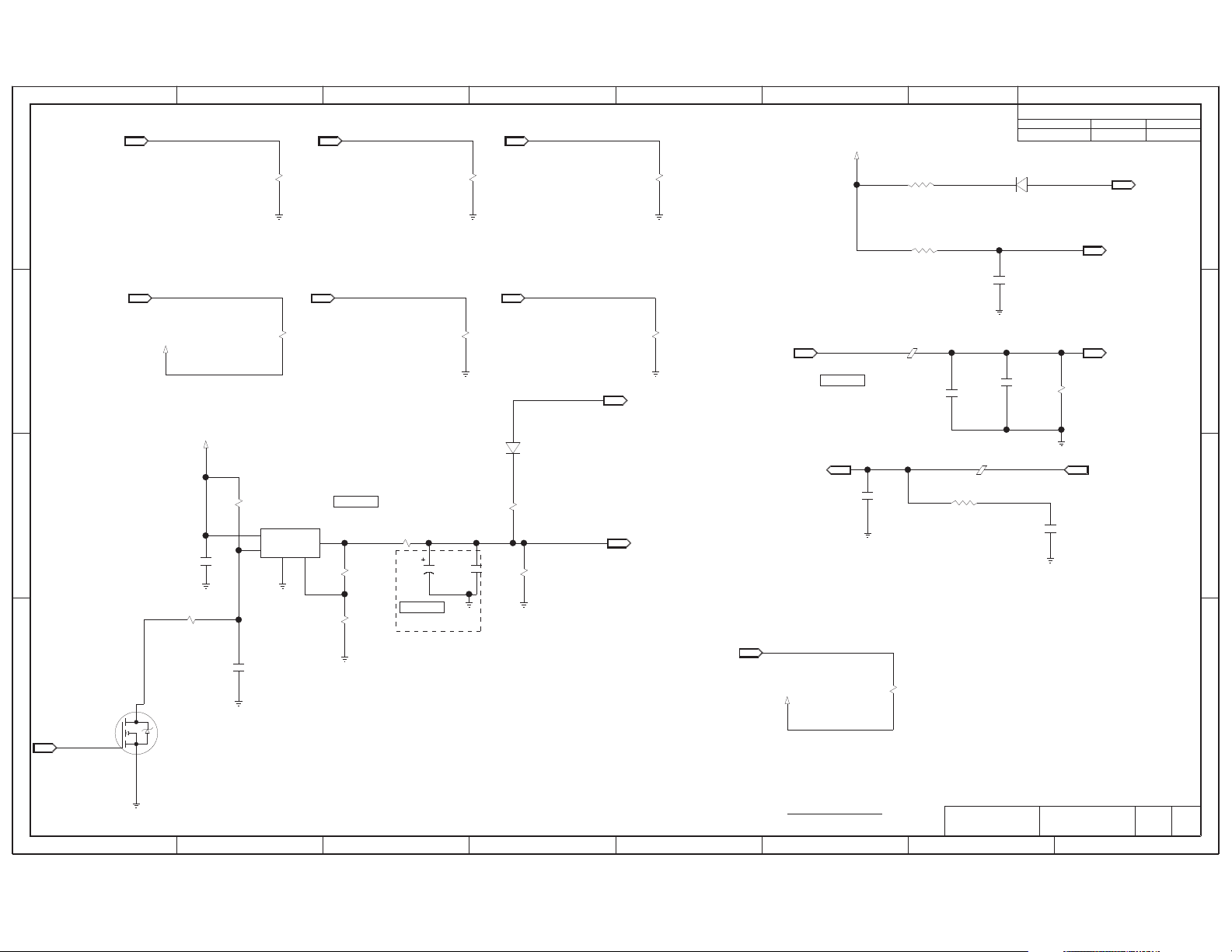

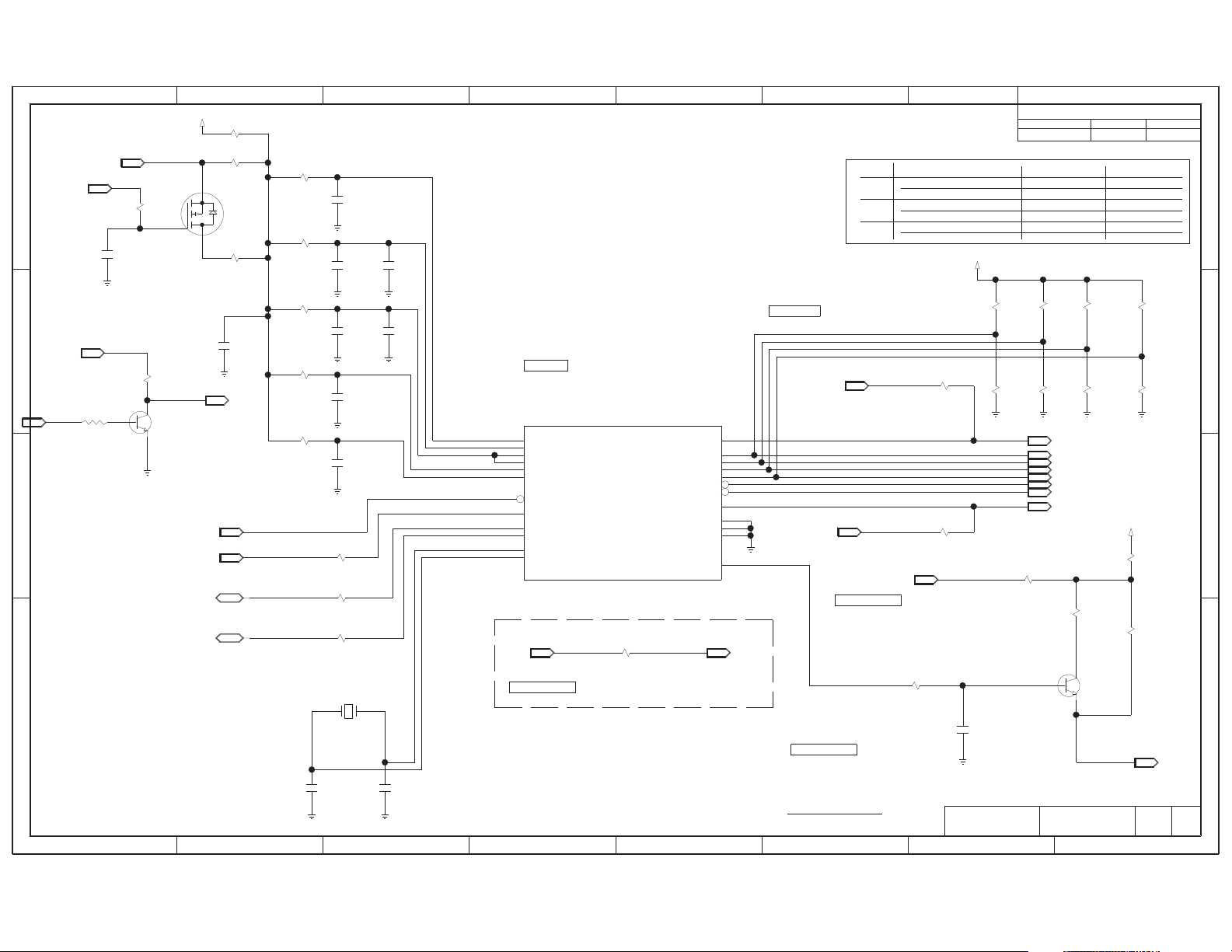

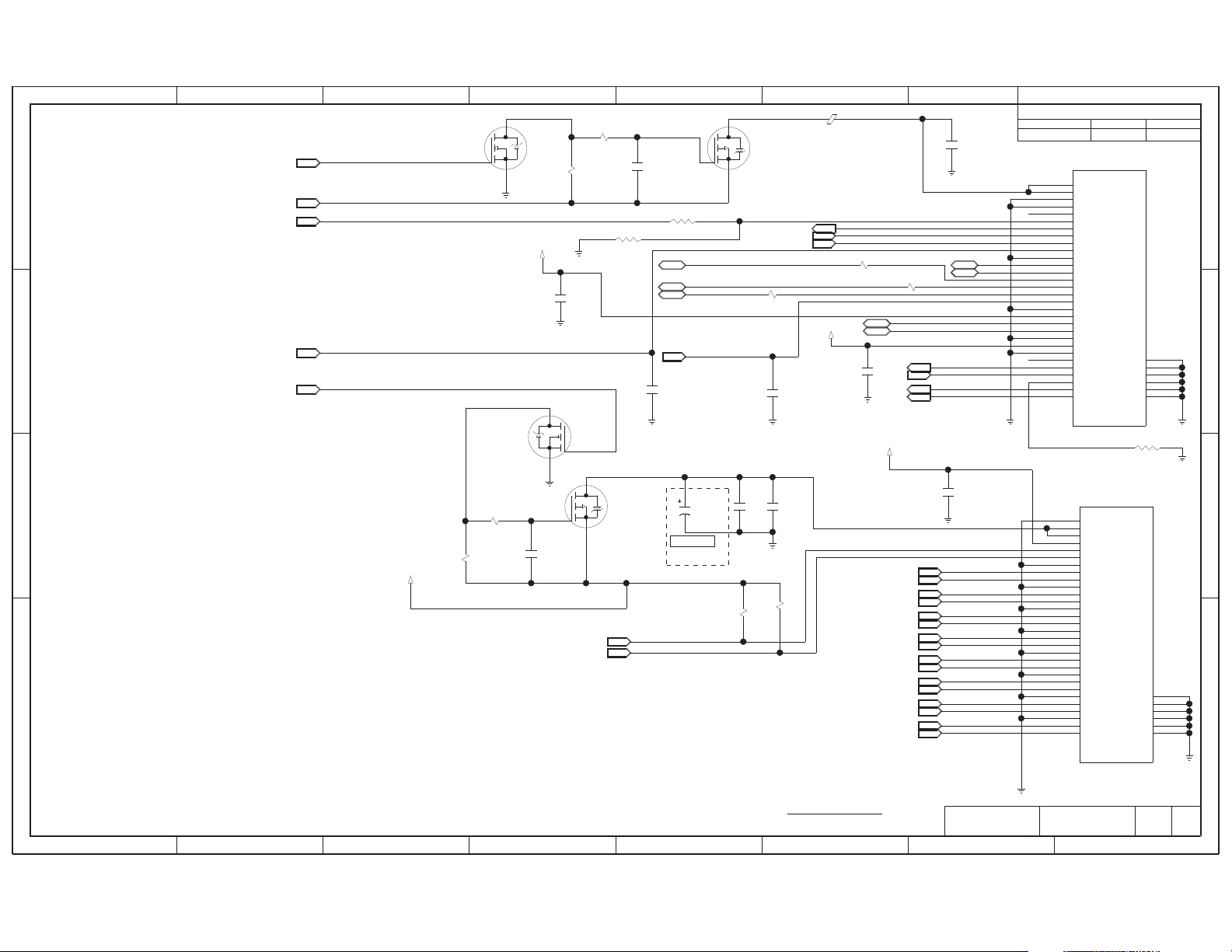

CR-1 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAG E1

8 2

[

1. COVER]

7

[2. BLOCK DIAGRAM]

[3. SCH ANNOTATION & BRD INF]

D

[4. GPIO MAP]

[5. USB TABLE]

[6. CPU (1 OF 3)]

[7. CPU (2 OF 3)]

[8. CPU (3 OF 3)]

[9. CPU THERMAL MONITORS AND FAN]

[10. GMCH (1 OF 8)]

[11. GMCH (2 OF 8)]

[12. GMCH (3 OF 8)]

[13. GMCH (4 OF 8)]

[14. GMCH (5 OF 8)]

[15. GMCH (6 OF 8)]

C

[16. GMCH (7 OF 8)]

[17. GMCH (8 OF 8)]

[18. CRESTLINE STRAPPINGS]

[19. DDR DIMM 0]

[20. DDR DIMM 1]

[21. DDR TERMINATION AND THERMAL]

[22. CK505 PAGE [ 1 OF 3 ]]]]]

[23. CK505 PAGE [ 2 OF 3 ]]]]]

[24. CK505 PAGE [ 3 OF 3 ]]]]]

[25. CRT/VGA]

[26. LVDS\LCD PANEL]

B

[27. S-VIDEO]

[28. VGA SWTICH]

[29. ICH8M (1 OF 5)]

[30. ICH8M (2 OF 5)]

[31. ICH8M (3 OF 5)]

[32. ICH8M (4 OF 5)]

[33. ICH8M STRAPS/ISOLATION]

[34. ICH8M (5 OF 5)]

[35. X1 MINI-PCIE 1]

[36. X1 MINI-PCIE 2]

[37. EXPRESS CARD CONN]

[38. ICH8M DUAL SPI]

[39. HDD CONNECTOR]

[40.

ICH8M IDE - ODD CONNECTOR]

[41. AUDIO CODEC]

[42. AUDIO DECOUPLING & JACK SENSE & DMIC]

[43. AUDIO SPEAKER & SUBWOOFER AMP]

[44. AUDIO ANTI-POP,ANTI-THEFT CIRCUITRY]

[45. AUDIO VREG]

[46. LAN INTEL/NINEVEH]

[47. LAN SWITCH/CONNECTORS]

8

7

6

45

[48. LAN POWER]

[49. MODEM/MDC]

[50. XDP]

[51. KBD CONN]

. BLUETOOTH/LPC/TOUCHPAD/HOT KEY CONN]

[52

[53. CHASSIS UP SIGNAL CONN]

[54. LOWER RIGHT CONN]

[55. KEYBOARD CONTROLLER]

[56. EC SIGNAL STUFFING OPTIONS]

[57. KBC SPI/SEQUENCING]

[58. MASTER SMBUS]

.TPM]

[59

[60. CORE_VR_POWER_MAP]

[61. VREG: V_SM/SMVTT]

[62. VREG: 1.5/1.05 CONTROLLER]

[63. VREG: 1.05V OUTPUT]

[64. VREG: 1.5V OUTPUT]

[65. VREG: 5V/3.3V CONTROLLER]

[66. VREG: 5V STANDBY OUTPUT]

[67. VREG: 3.3V STANDBY OUTPUT]

[68. VREG: RAIL SWITCHES 1 OF 2]

[69. VREG: RAIL SWITCHES 2 OF 2]

[70. VREG: V_1P25_M\V_1P05_M]

[71. VREG: DISCHARGE CIRCUITRY]

[72. VREG: POWER GOOD FOR CLPWRO]

[73. VREG: BATTERY CHARGER PAGE 1OF 2]

[74. VREG: BATTERY CHARGER PAGE 2 OF 2]

[75. VREG: V_GFX CONTROLLER]

[76. VREG: V_GFX OUTPUT]

[77. VREG: VCCP ADP3207 CONTROLER]

[78. VREG: VCCP PHASE 1 & 2]

[79. VREG: VCCP DECOUPLING / 2X2 CONN]

[80. MEDIA READE R CONTROLLER]

[81. MEDIA READER SOCKET]

[82. USB LEFT JACK]

[83. PORT REP HDR]

[84. MTG HOLES/JUMPERS]

[85. EC GPIO MAP]

BPAGE DRAWING

[PAGE_TITLE=COVER]

65

tawas_b.sch_1.1

Fri Feb 09 14:58:59 2007

4 2

3

REVDE

SCRIPTION

REVISIONS

DF

DATECHK

T

TAWAS

FAB B

REV

TAPED OUT: 2-08-07

PBA D73802-200

IMERSION SILVER BUILD

NOTES:

1. THIS SCHEMATIC DOCUMENTS THE GENERIC PRODUCT WITH

2. RESISTORS ARE IN OHMS UNLESS OTHERWISE SPECIFIED.

3. VCC = +5V UNLESS OTHERWISE SPECIFIED.

4. * SUFFIX INDICATES ACTIVE LOW SIGNAL.

5. \I SUFFIX INDICATES SIGNAL EXITS HIERARCHICAL BLOCK.

BOM_RELEASE_DATE

DRN_BY

CHK_BY

ENGR_APVD

CUSTOM TEXT B-PAGE

6. THIS DOCUMENT ALSO EXISTS ON E LECTRONIC MEDIA.

SIGNATURE

?

?

3

2.0

ALL POSSIBLE CONFIGURATIONS.

PLEASE REFER TO SPECIFIC PRODUCT PBA EPL FOR

ITEMS S HOWN AS OPTIONAL IN THE SCHEMATIC.

INTEL

D77960-002

DOCUMENT_NUMBER

?

DATE

?

??

?

PB_NUMBER

inte

TITLE

TAWAS_FAB_B

CONFIDENTIAL

D89092

1

APVDDA

TE DATE

S

3065 BOWERS AVE

SANTA CLARA, CA

95051

PAGE

REV

2.0

1/85

1

D

C

B

AA

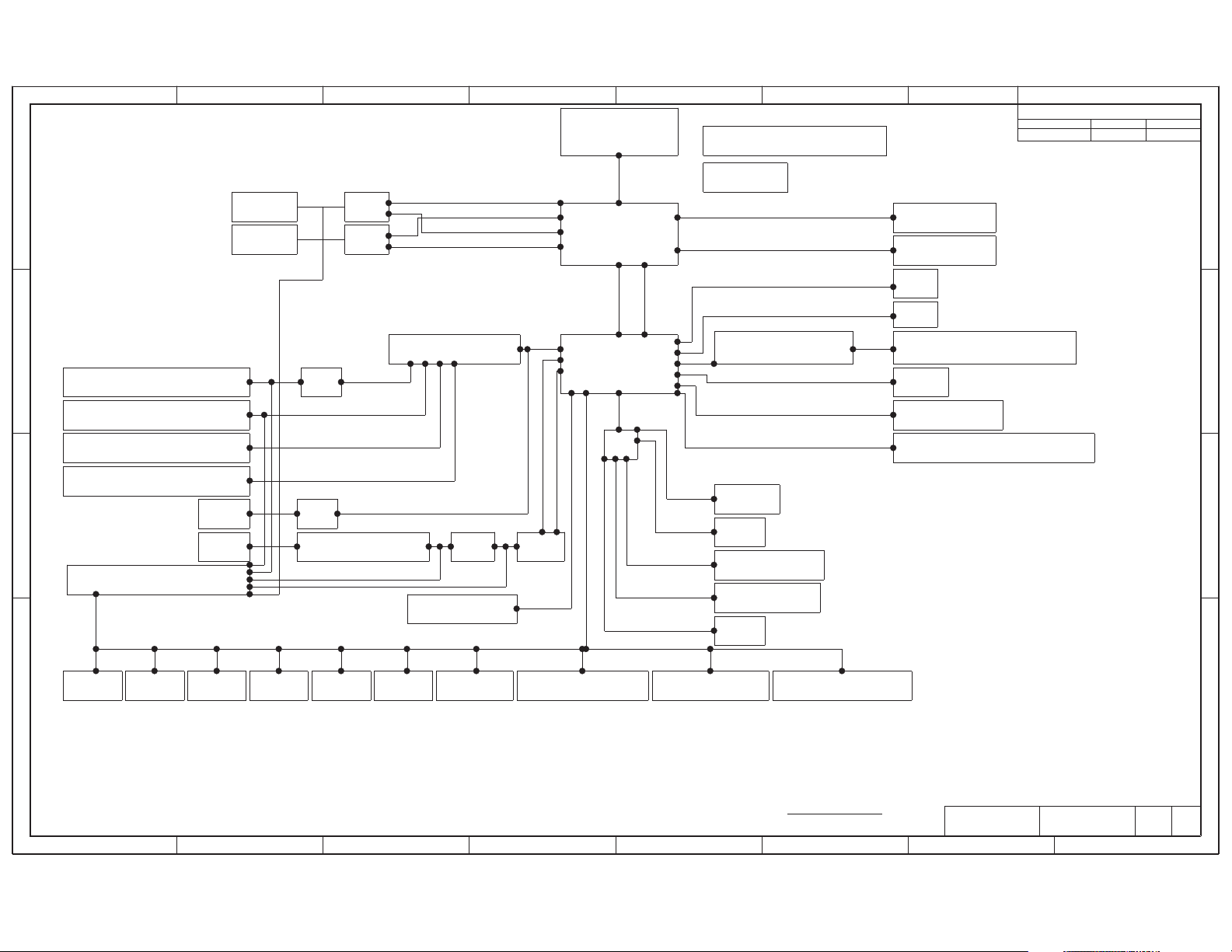

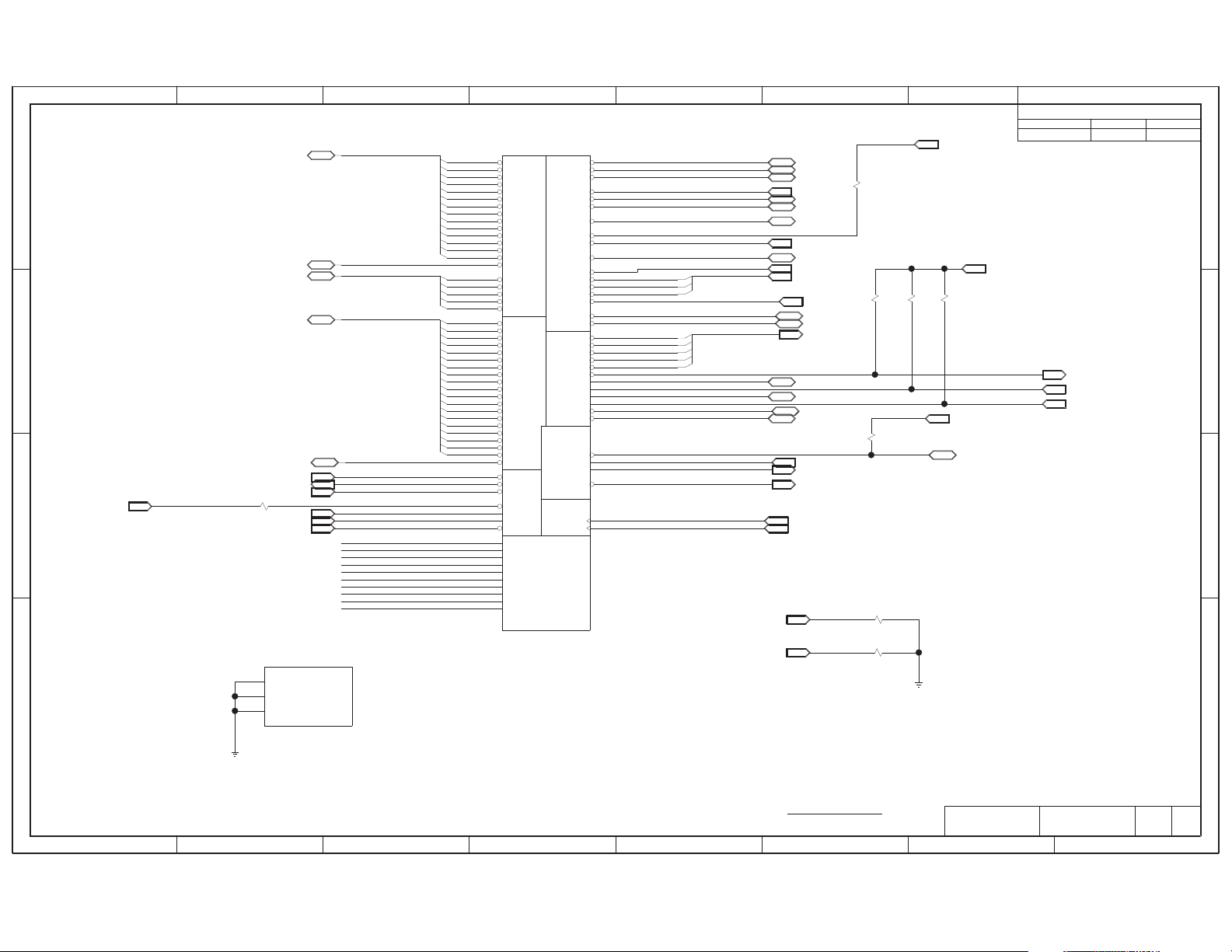

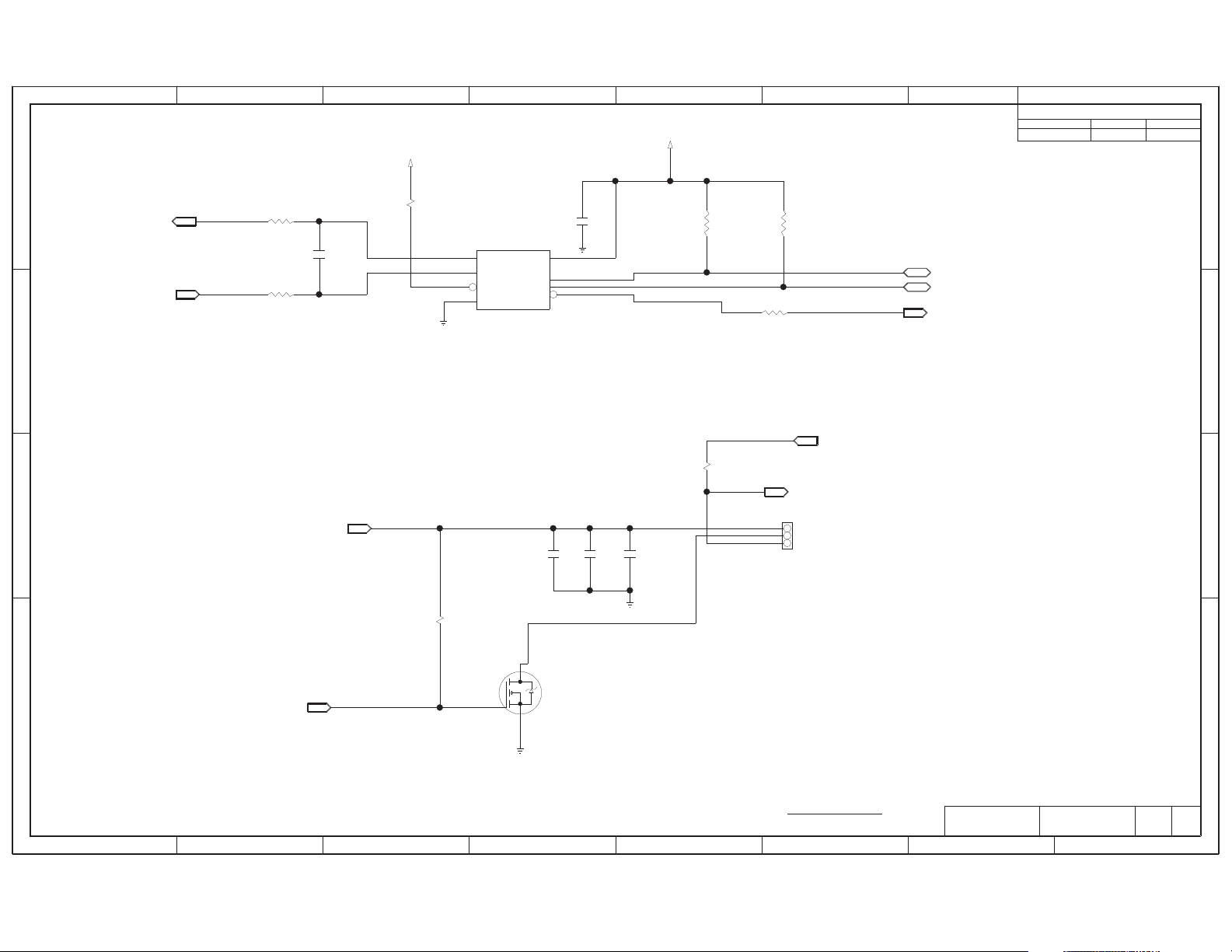

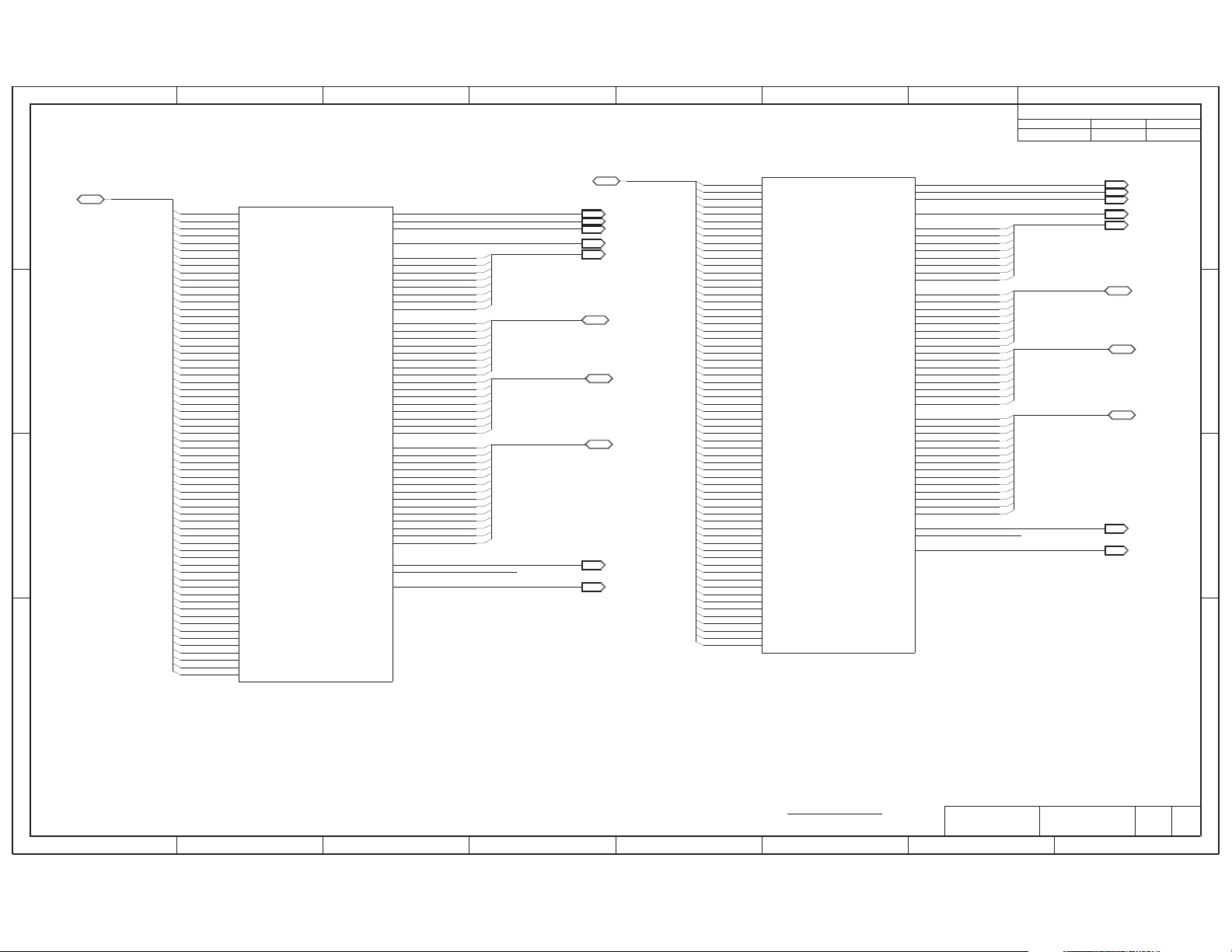

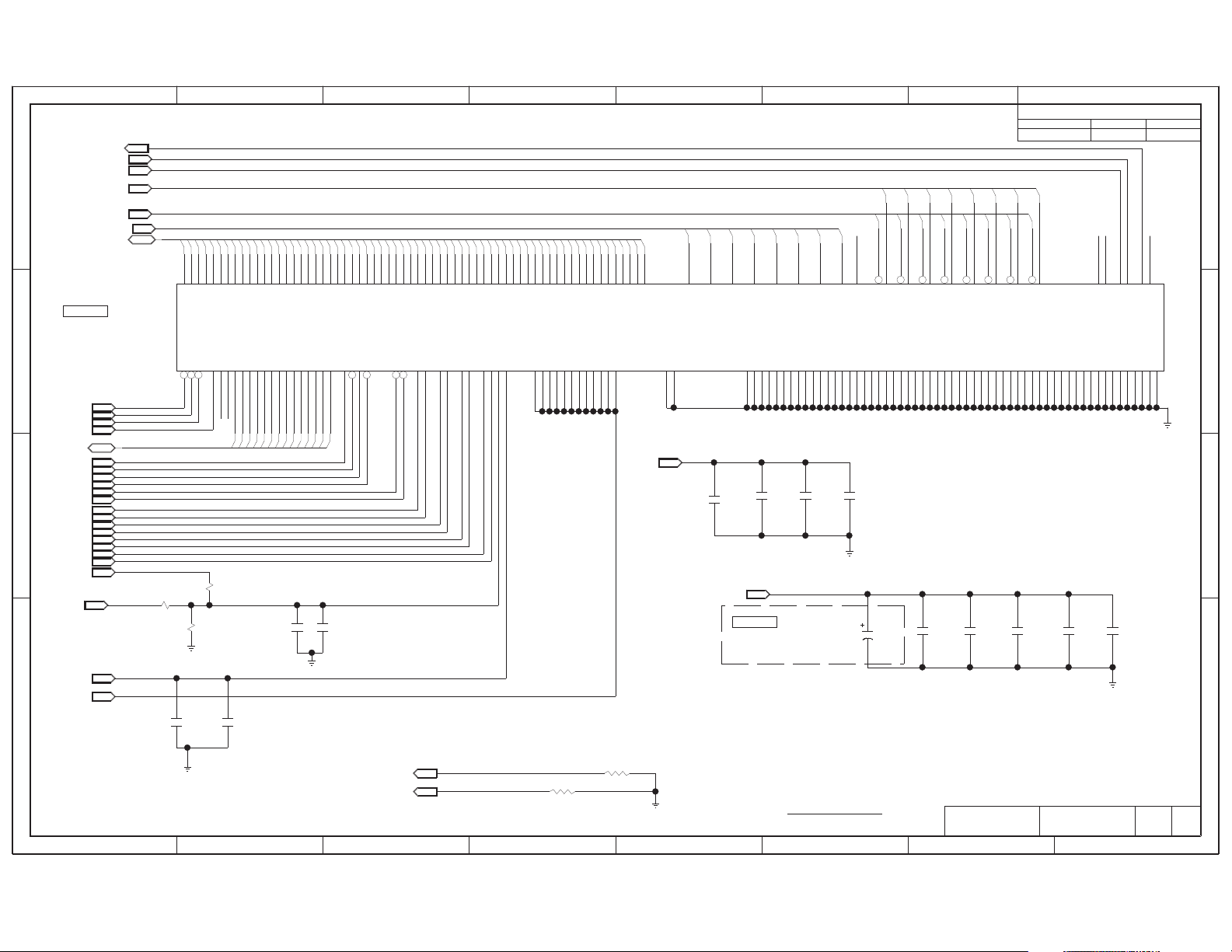

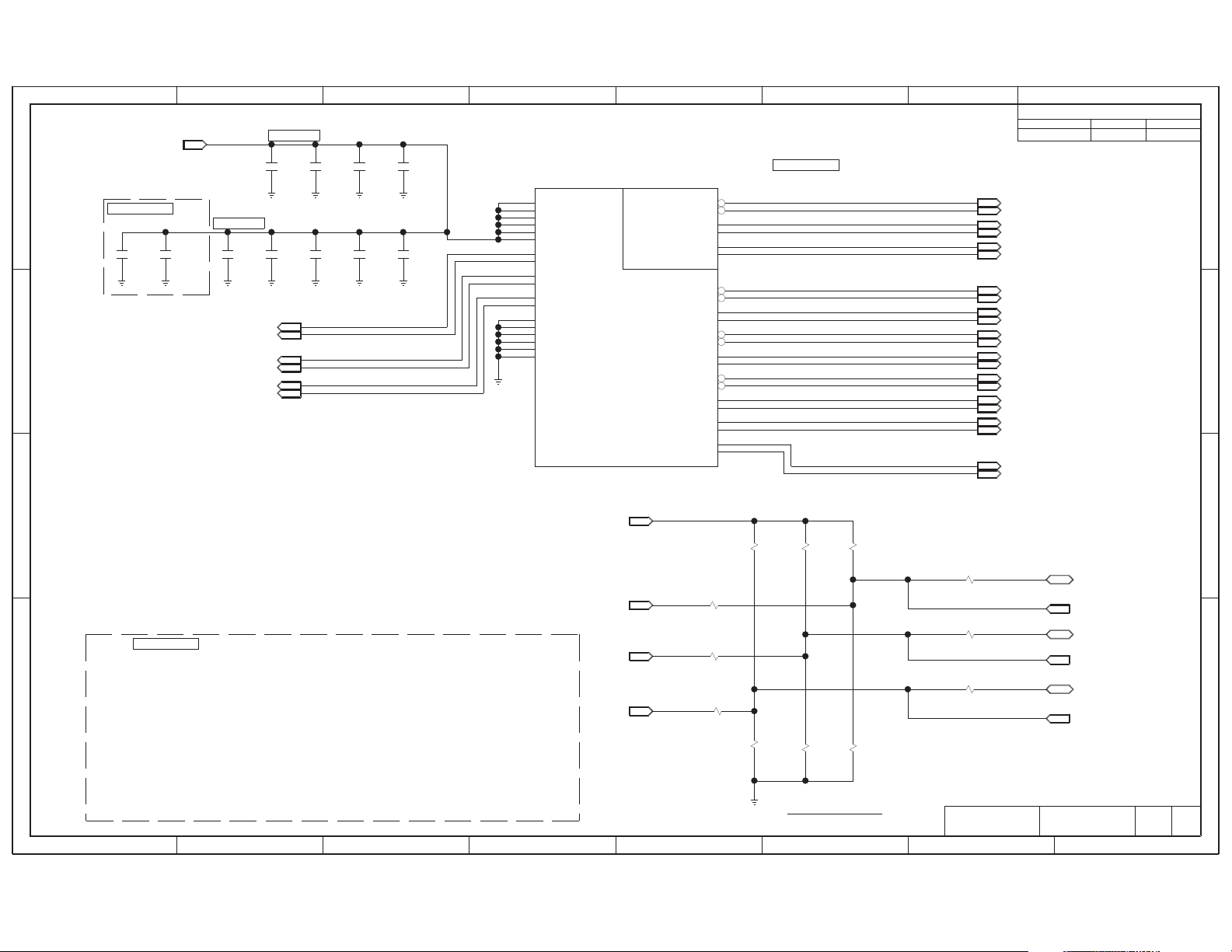

Page 2

CR-2 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAG E2

8

7

6

MEROM

45

ON_BOARD BATTERY

3

2

MODULE REV DETAILS

MODULE NAME

1

REV

DATE

ICH8M

USB

SPI

DMI X4

EC

FSB

667/

LPC

800MHZ

CONTROLER

LINK

CK 505

CARD READER

CONTROLLER

PCI

533/667MHZ

533/667MHZ

SO_DIMM0

SO_DIMM1

SATA

HDD

PATA

ODD

CARD READER SLOT

PCIE

WLAN

PCIE

ROBSON/TV

PCIE

EXPRESS CARD SLOT

D

2GB

2GB

C

D

SVIDEO

SVIDEO

VGA

VGA

CRESTLINE

HD AUDIO

VGA

TV

C

SPEAKER

AMP

MUX

MU

X

AUDIO CODEC

HEADPHONE JACK

LCI

GLCI

MICROPHONE JACK

ARRAY MICROPHONE

FLASH

B

RJ11

MDC

B

CIR

RJ45

PORT REPLICATOR

USB 1

TRANSFORMER

SIGNAL

PHY

LED

SPI FLASH

32MBIT

LAN

USB BUS

TOUCH PAD

KEYBOARD

TPM

A

USB

USB USB USB

LRCLRC URCURC

PCIE

PCIE

CAMERA

XPRESS CARD

BLUE TOOTH

FINGER PRINT

A

[PAGE_TITLE=BLOCK DIAGRAM]

BPAGE DRAWING

tawas_b.sch_1.2

Wed Feb 07 17:18:03 2007

8

7

6

5

4 2

3

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

D89092

PAGE

REV

2

2.0

1

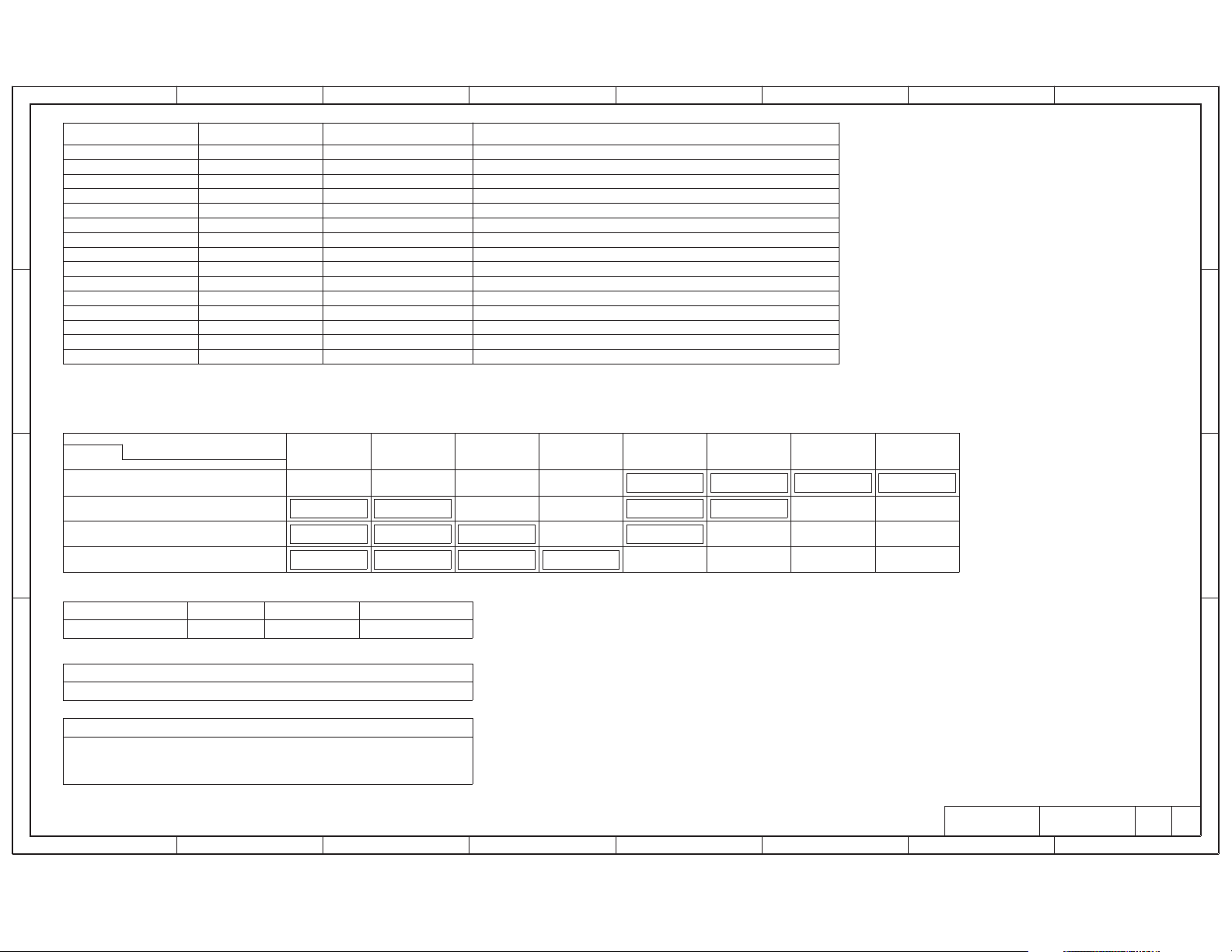

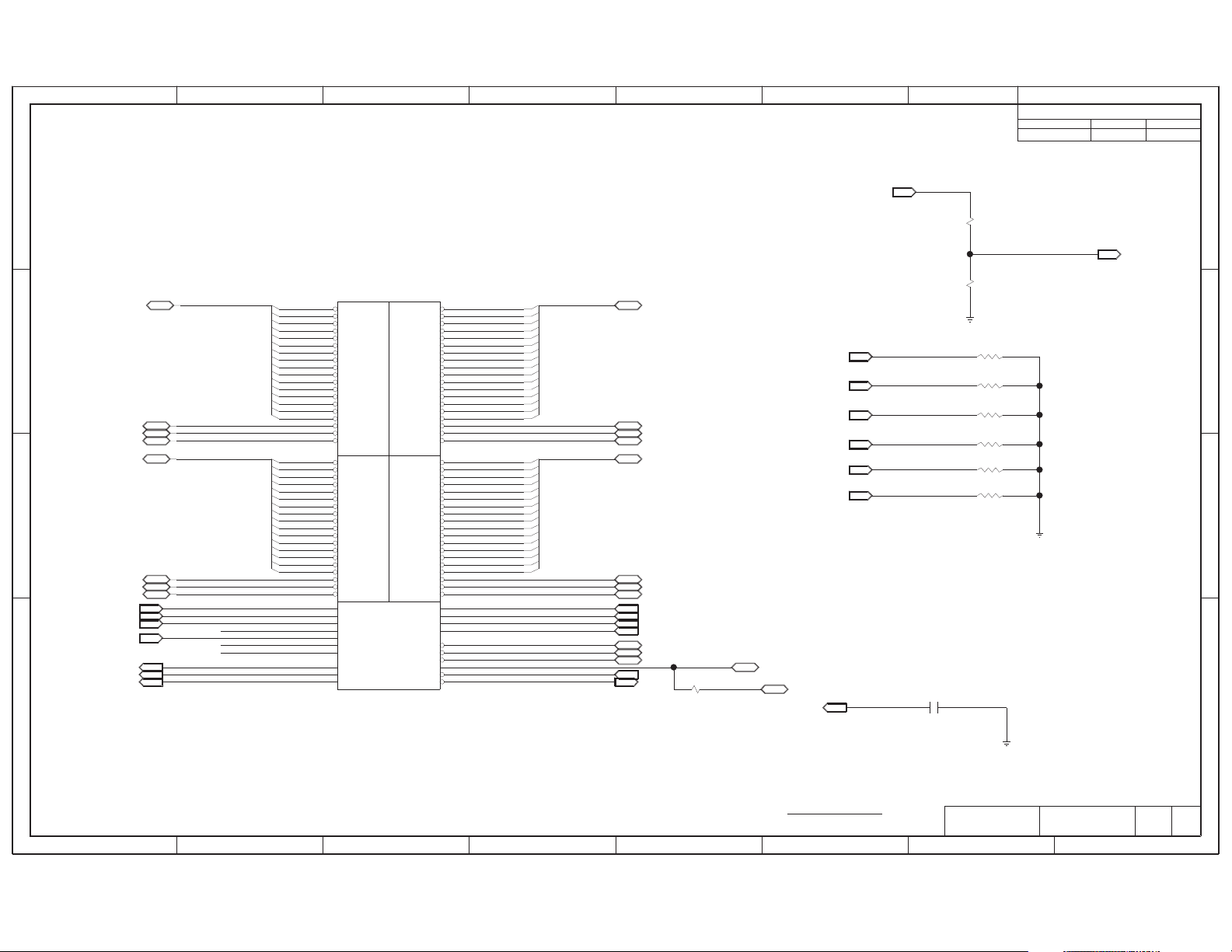

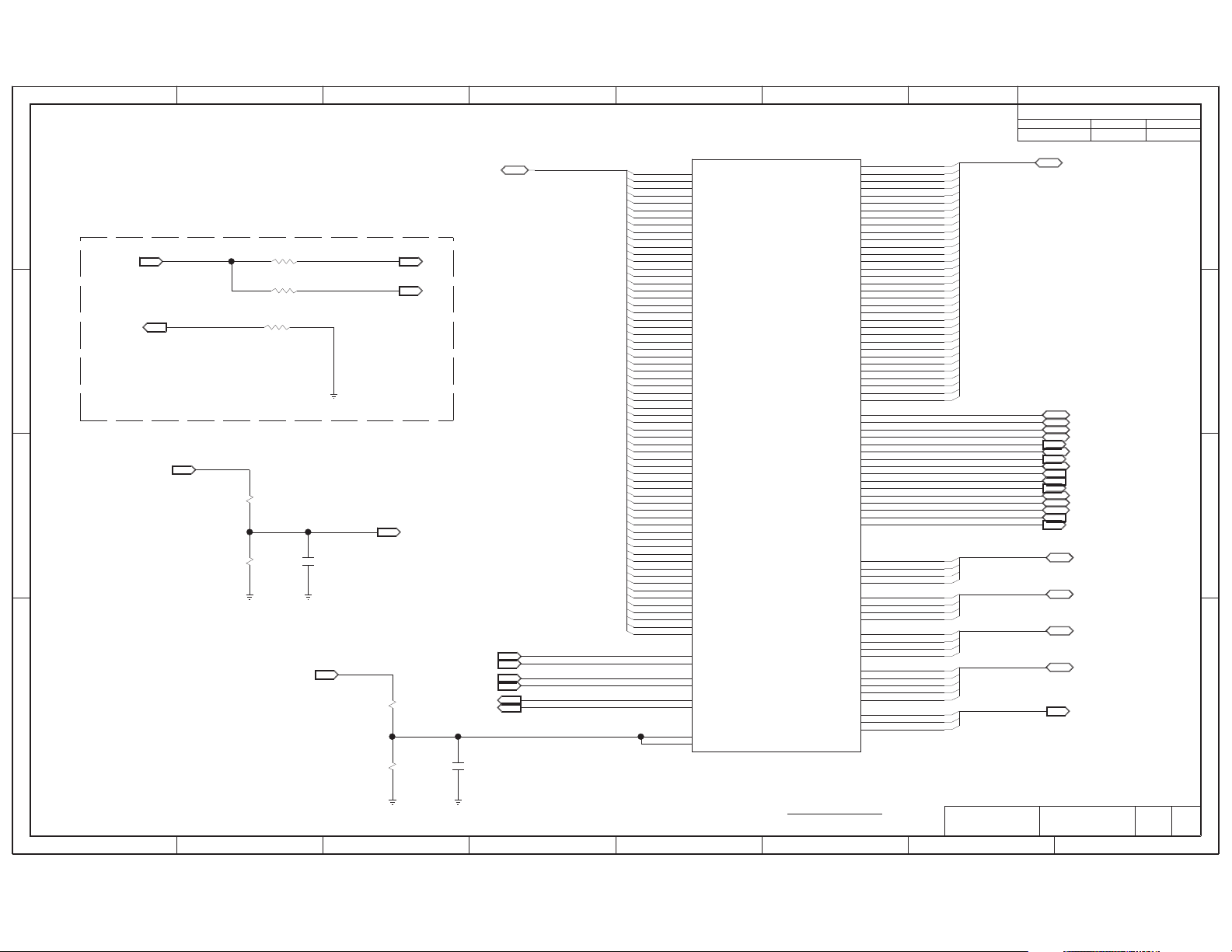

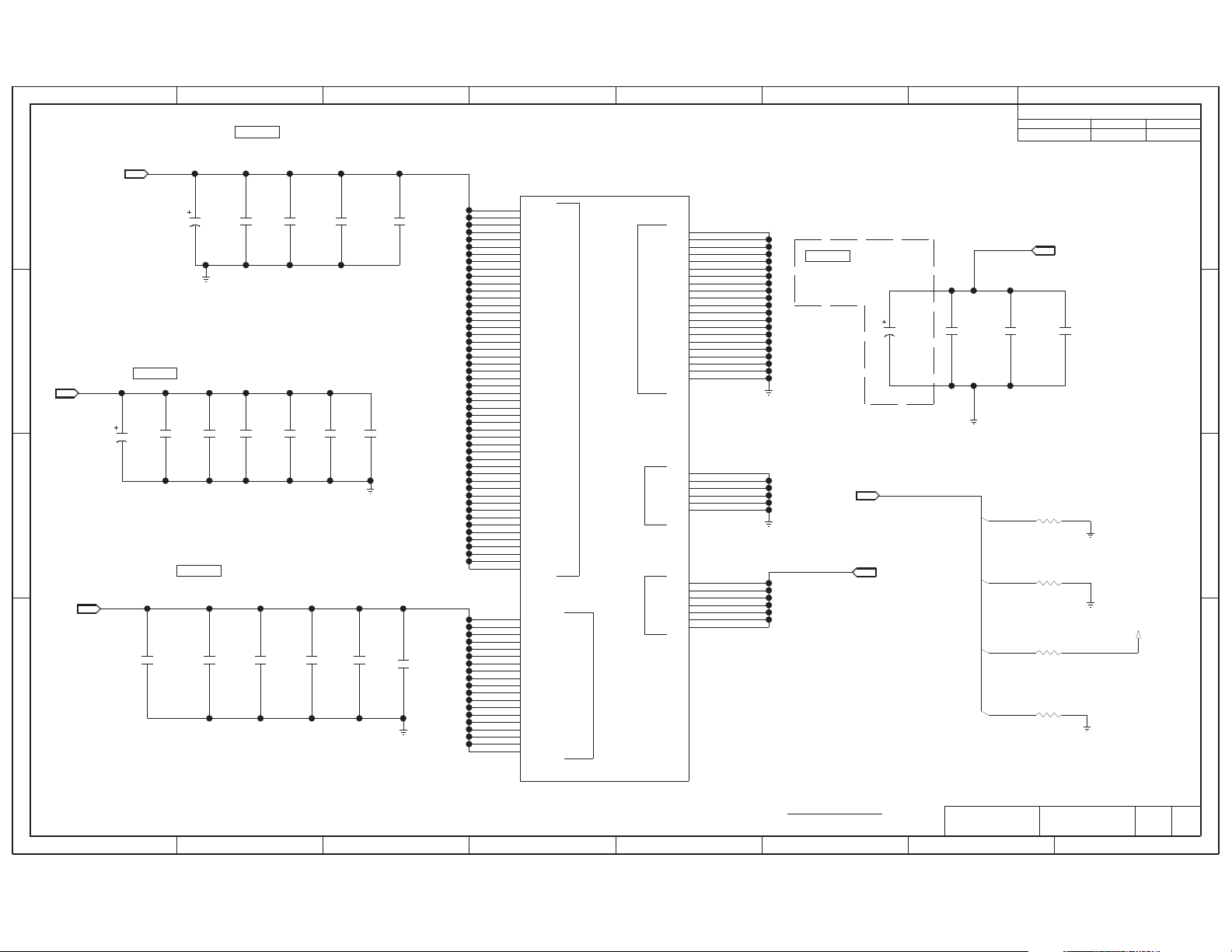

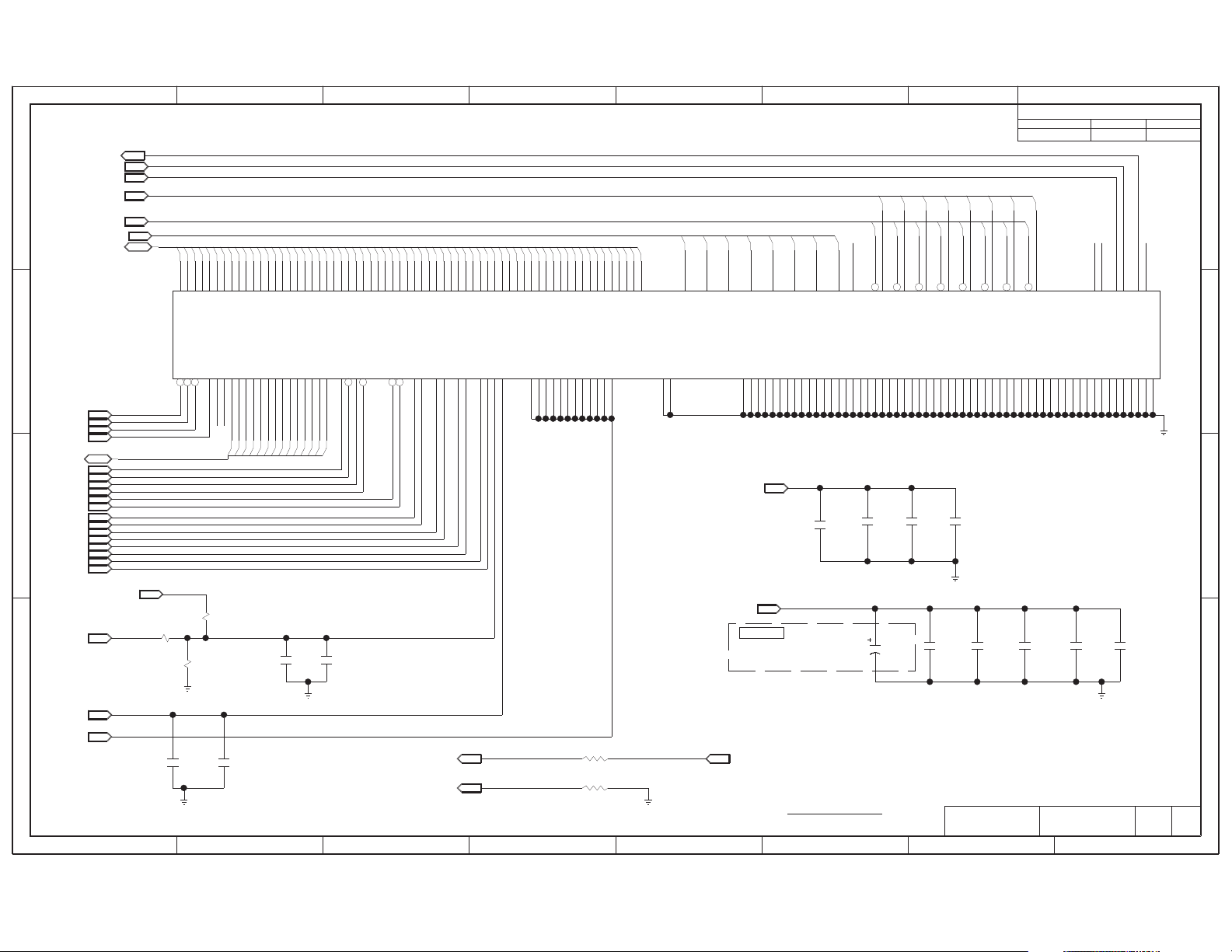

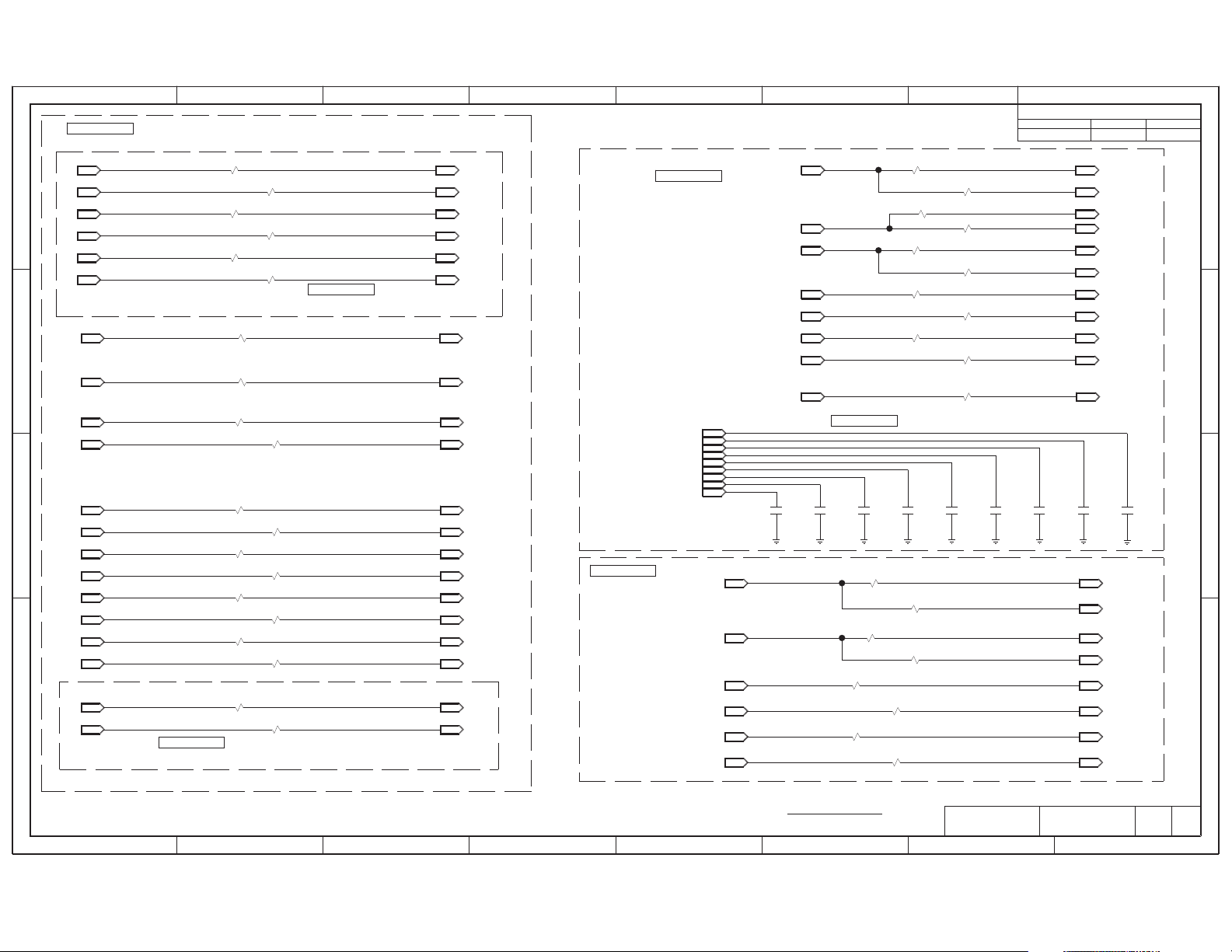

Page 3

CR-3 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAG E3

VOLTAGE RAILS

POWER PLANE DESCRIPTION

+VBAT

=>

D

V_5P0_STBY\G

VCC

V_3P3_STBY\G

AGE

VOLT

9V-12.5V

5V

5V

3.3V

7

654

3

28

1

S3COLD ACTIVE

S0,S3,S4,S5

S0,S3,S4

S0

S0,S3,S4,S5

BATTERY RAIL IN MOVILE POWER MODE

VR

PERIPHERAL

EC & PERIPHERAL

D

VCC3

V_SM

V1.8S

=>

V_SM_VTT

V_1P5_CORE

V_1P25_CORE

V_1P05_CORE

C

V_GFX

VCC_CORE

=>

THOSE W\ ARROWS ARE NOT CONFIRMED

POWER STATES

STATE

FULL ON

B

S3 (SUSPEND TO RAM)

S4 (SUSPEND TO DISK)

S5 / SOFT OFF

PCI D EVICES

DEVICE

CARD READER

NET NAMING CONVENTIONS

SUFFIX

A

N =ACTIVE LOW SIGNAL

3.3V

1.8V

1.8V

0.9V

1.5V

1.25V

1.05V

0.5V-1.325V

0.5V-1.325V

SIGNAL

IDSEL#

AD18

S0

S0,S3

S0

,S3

S0

S0

S0

S0

S0

S0

SLP_M#

HIGH HIGH

LOW

LOW

SLP_S3#

HIGH

LOW

LOW

LOWLOW

REQ/GNT#

00

REQ/GNT#

A

PERIPHERAL

DDR CORE

CARD READER

DDR PULL UP

CHIPSET POWER RAIL

CHIPSET POWER RAIL

CHIPSET POWER RAIL

CPU CORE RAIL

GFX CORE RAIL

SLP_S4#

HIGH

HIGH

LOW

LOW

SLP_S5#

HIGH

HIGH

LOW

+V*A

ON

ON

OFF

+V*

ONON

ON

OFF

OFF

+V*S

ON

OFF

OFF

OFF

CLOCKS

ON

OFF

OFF

OFF

C

B

A

PREFIX

H=HOST

M =DDR MEMORY

TP=TEST POINT

[PAGE_TITLE=SCH ANNOTATION & BRD INFO

8

7

6

INTEL

CONFIDENTIAL

45

3

2

DOCUMENT NUMBER

PAGE

REV

1

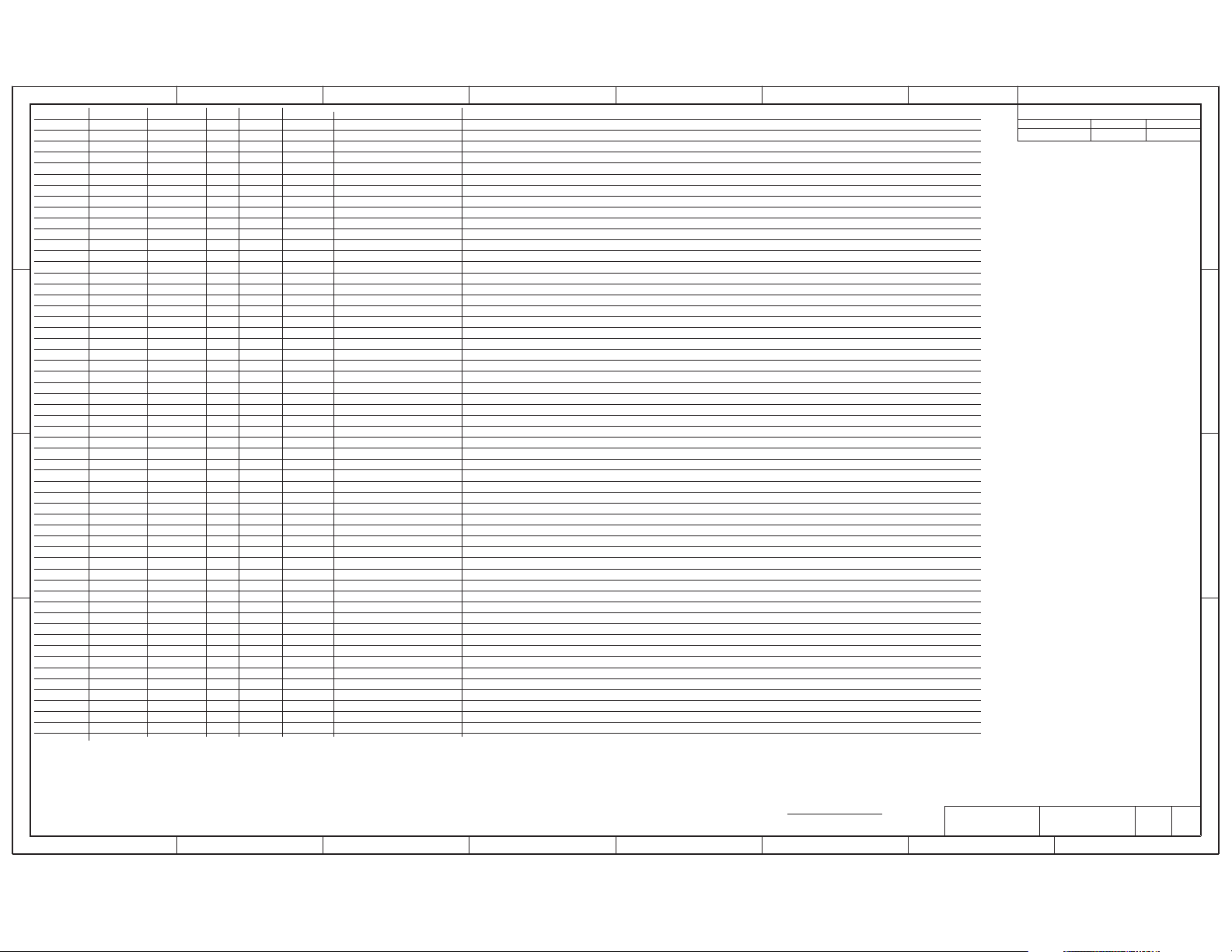

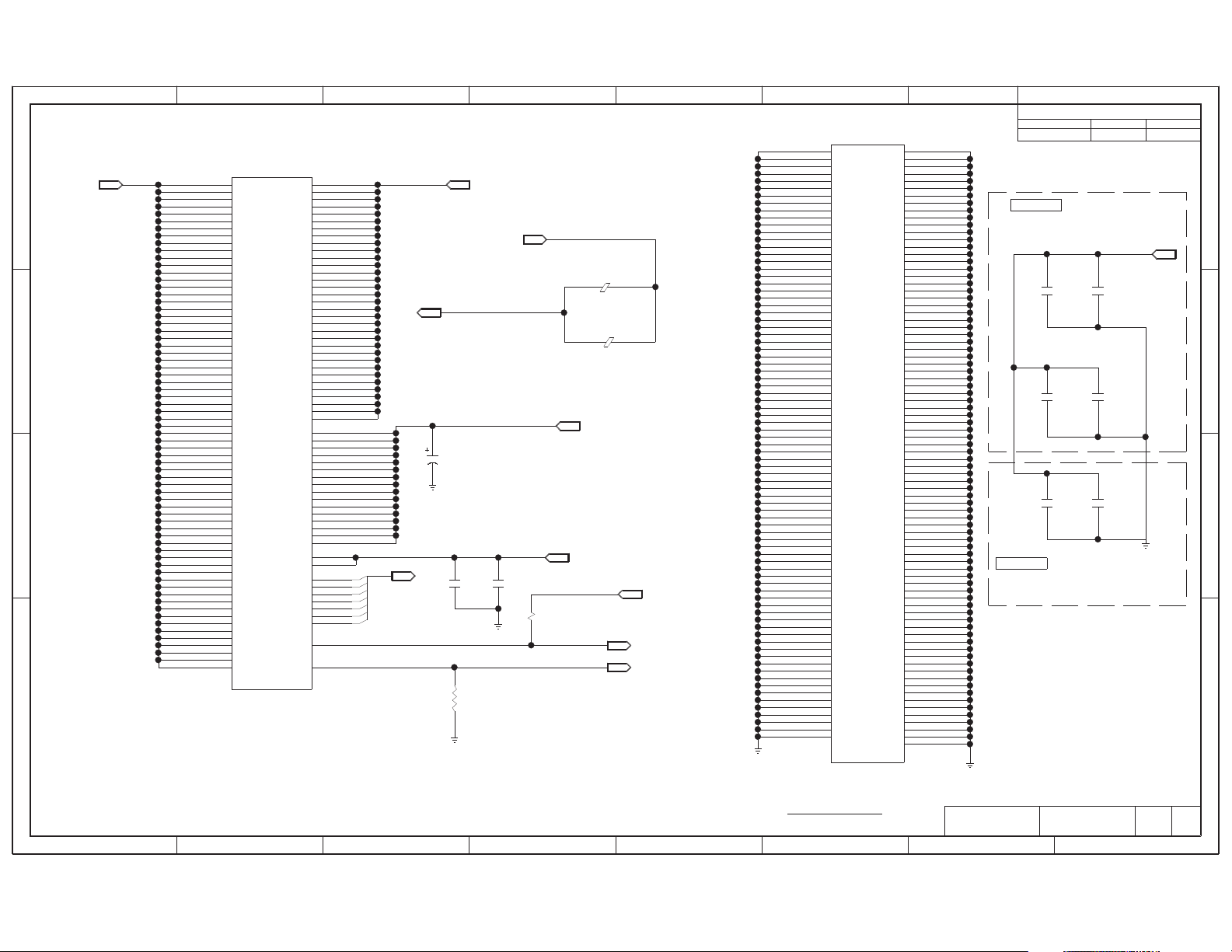

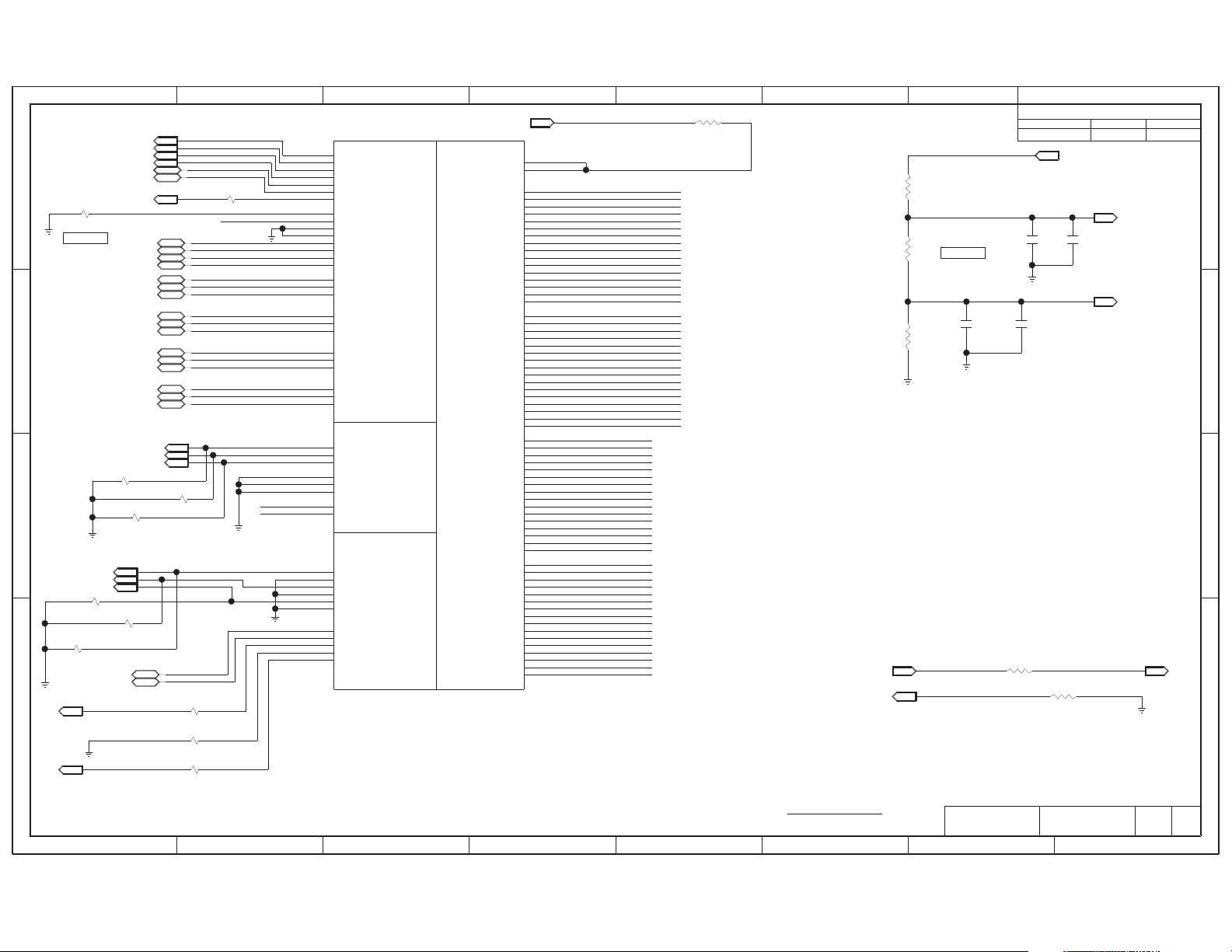

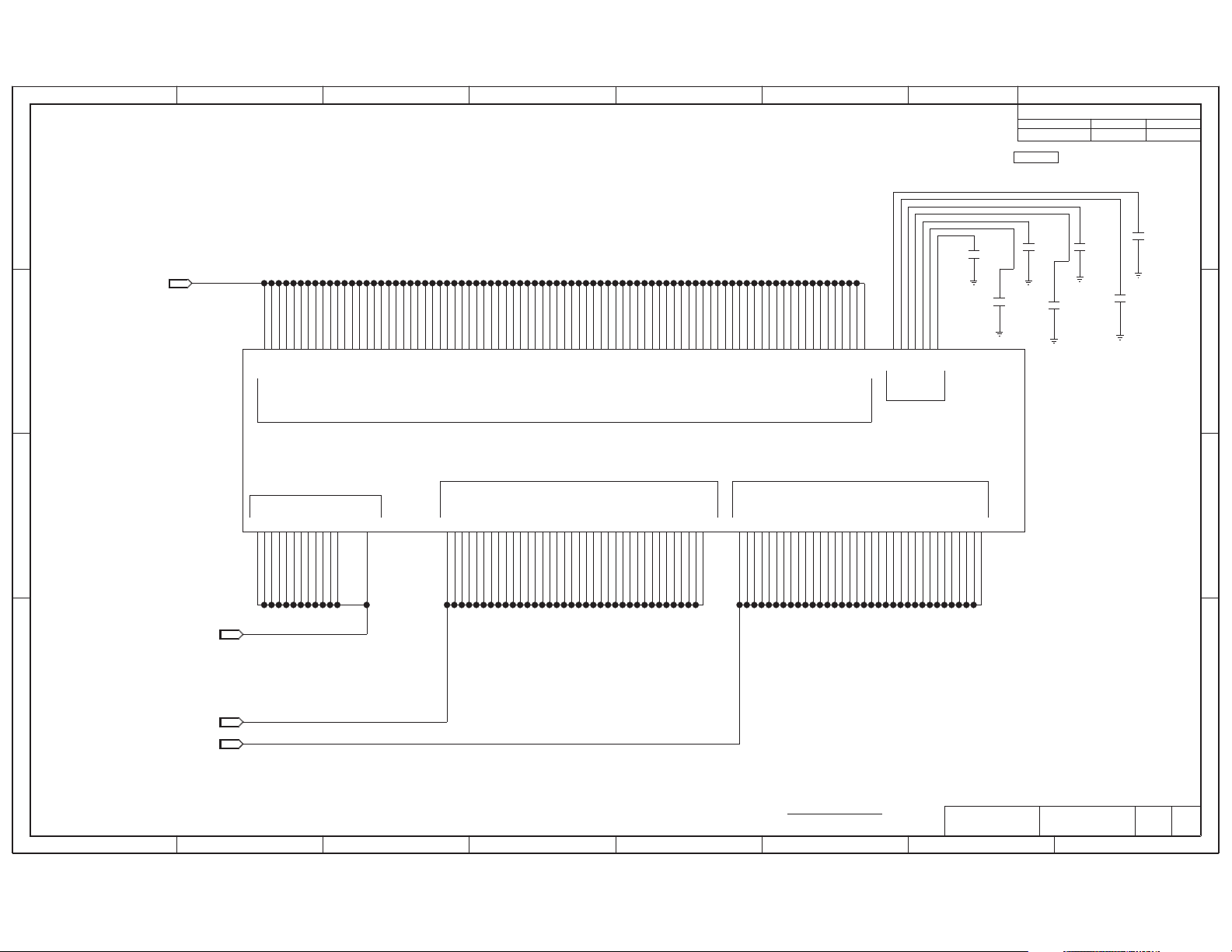

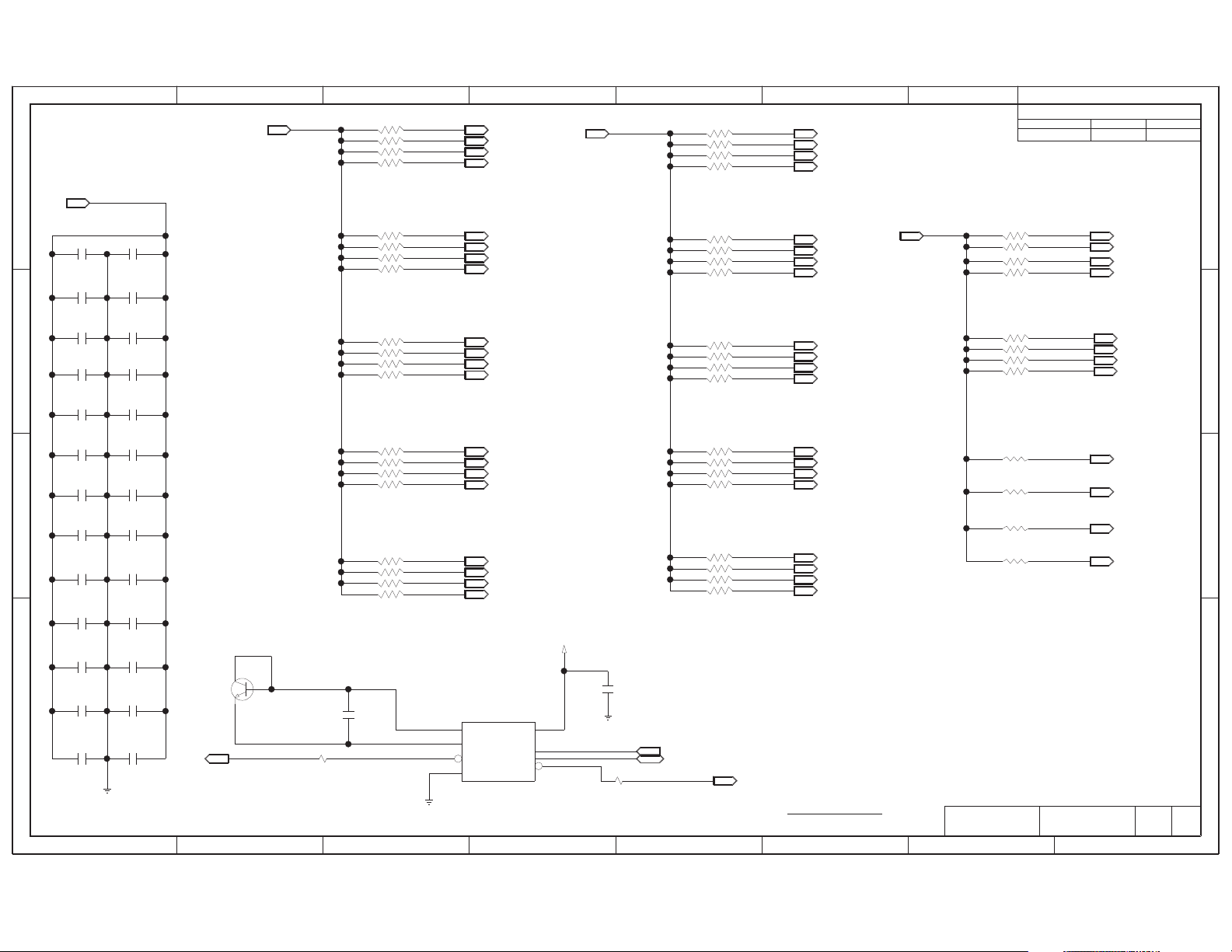

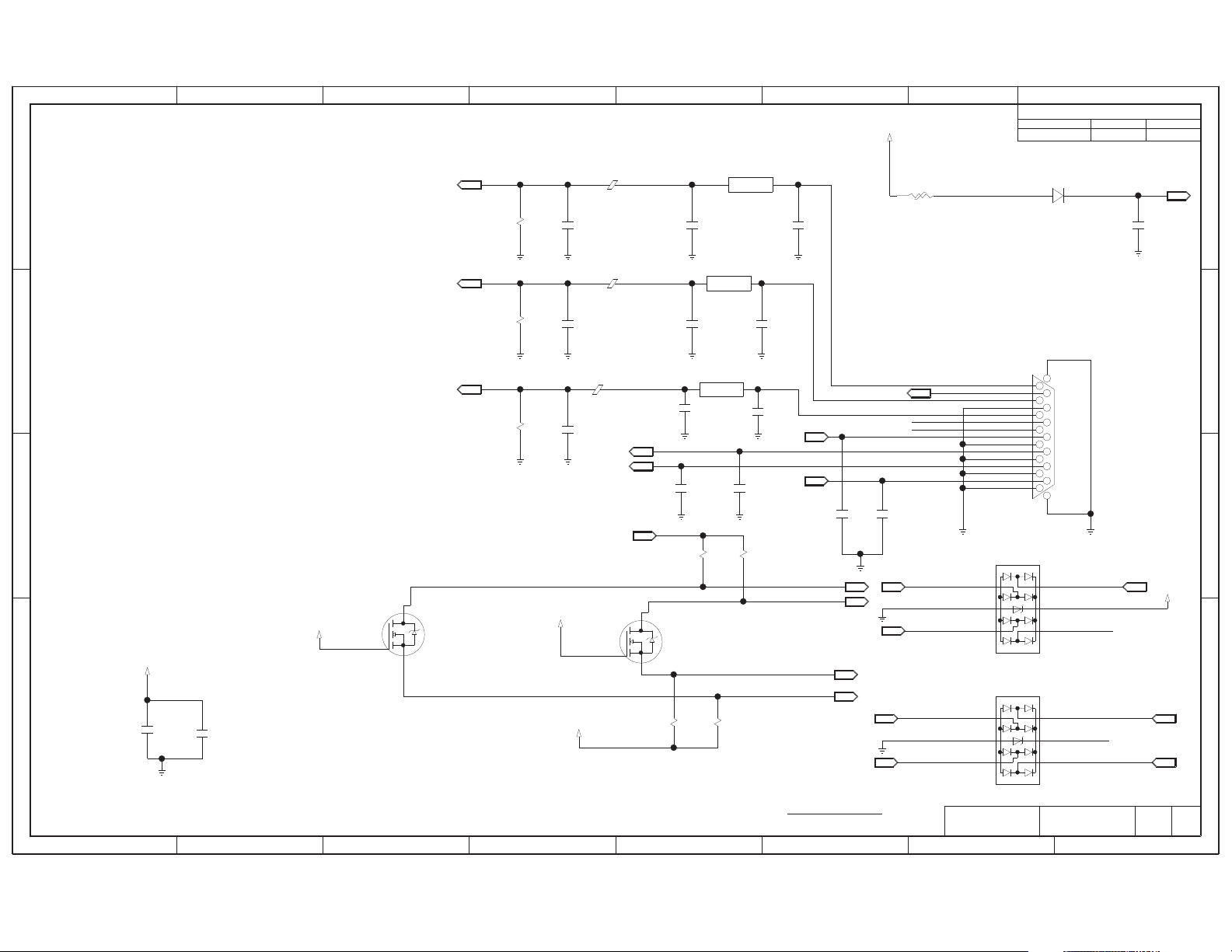

Page 4

PIN NAME

GP[0]

GP[1]

GP[2]

GP[3]

GP[4]

D

GP[5]

GP[6]

GP[7]

GP[8]

GP[9]

GP[10]

GP[11]

GP[12]

GP[13]

GP[14]

GP[15]

GP[16]

GP[17]

GP[18]

GP[19]

GP[20]

C

GP[21]

GP[22]

GP[23]

GP[24]

GP[25]

GP[26]

GP[27]

GP[28]

GP[29]

GP[30]

GP[31]

GP[32]

GP[33]

GP[34]

GP[35]

B

GP[36]

GP[38]

GP[39]

GP[40]

GP[41]

GP[42]

GP[43]

GP[44]

GP[45]

GP[46]

GP[47]

GP[48]

GP[49]

GP

GP[51]

A

GP[52]

GP[53]

GP[54]

GP[55]

CR-4 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAG E4

8

[50]

WELL

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

MAIN

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAI

MAIN

MAIN

MAINGP[37]

MAIN

MAIN

RESUM

RESUME

RESUME

RESUME

N/A

N/A

N/A

N/A

MAIN

V_CPU_IO

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

8

TOL.

3.3V

3.3V

5V

5V

5V

5V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

3.3V

N

3.3V

3.3V

3.3V

3.3V

E

3.3V

3.3V

3.3V

3.3V

N/A

N/A

N/A

N/A

3.3V

V_CPU_IO

5V

3.3V

5V

3.3V

5V

3.3V

PIN#

AG12

AJ8

F8

G11

2

F1

B3

AJ9

AH9

AE16

AG19

AJ24

AG22

AC19

AH21

AF22

AE20

AJ14

AG83.3V

AH12

AJ10

AE1

AJ12

AG10

E6

AJ27

AG18

AH27

AH25

AD16

AG17

AD12

AJ18

AH11

AE10

AG14

AG

AF113.3V

AG11

AF9

AJ11

AG

AG15

AE15

AF15

N/A

N/A

N/A

N/A

AD10

AG29

E18

C18

B19

F18

A11

C10

13

16

1

7

PLTRST

7

DEFAULT

IN

OUT

I/O

I/O

IN

NATIVE

OU

NATIVE

IN

IN

IN

I/O

OUT

IN

IN

IN

IN

OUT

IN

NATIVE

IN

NATIVE

IN

OUT

RIGHT SIDE

FROM DATASHEET

LEFT SID E

FROM SCHEMATIC

USAGE (NETNAME)

IN

BM_BUSY_N

IN

EC_EXTSMI_N

P_INTE_N

IN

P_INTF_N

IN

IN

P_INTG_N

IN

P_INTH_N

IN

HP_AMP_EN

IN

EC_RUNTIME_SCI_N

IN

EC_WAKE_SCI_N

IN

TP

IN

TP

SMB_ALERT_N

IN

GP12_MFG_MODE_N

ENERGY_DET_GPIO13

IN

TP

IN

PM_STPPCI_ICH_N

PM_DPRSLPVR_R

OUT

RF_KILL_N

FWH_TBL_N

IN

BOARD_ID0

PORT_REP_DETECT

OUT

IN

SATA0GP

FWH_WP_N

TP

OUT

TP

PM_STPCPU_ICH_N

T

TP

OUT

TP

OUT

TP

USB_OC5_N

USB_OC6_N

USB_OC7_N

PM_CLKRUN_N

OUT

TP

TP

OUT

OUT

CK_O

BOARD_ID1

IN

BOARD_ID4

TP

IN

IN

BOARD_ID2

USB_O

USB_OC2_N

USB_OC3_N

USB_OC4_N

N/A

N/A

N/A

N/A

IN

BOARD_ID3

H_PWRGD

P_REQ_N<1>

TP

P_REQ_N<2>

TP

P_REQ_N<3>

P_GNT_N<3>

6

E_SATA_N

C1_N

6

45

NOTES

FUNCTIONALITY NUXED WITH GPIO MY NOT BE USED FOR DESKTOP

DETECTS WHETHER PORT REPLICATOR IS CONNECTED

FUNCTIO

NALITY NUXED WITH GPIO MY NOT BE USED FOR DESKTOP

TRISTATED,UNABLE TO ACTIVELY DRIVING HIGH,NEED PULL UP

BPAGE DRAWING

tawas_b.sch_1.4

Wed Feb 07 17:18:04 2007

5

4 2

3

2

MODULE REV DETAILS

MODULE NAME

1

REV

DATE

D

C

B

A

[PAGE_TITLE=GPIO MAP]

PAGE

INTEL

CONFIDENTIAL

3

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

D89092

REV

4

2.0

1

Page 5

CR-5 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAGE5

8

7

6

45

3

2

MODULE REV DETAILS

MODULE NAME

1

REV

DATE

D

USB PORT

USB_0

USB_1

C

B

USB_2

USB_3

USB_4

USB_5

USB_6

USB_7

SIGNAL NAME

USB_0_DN/DP

USB_1_DN/DP

USB_2_DN/DP

USB_3_DN/DP

USB_4_DN/DP

USB_5_DN/DP

USB_6_DN/DP

USB_7_DN/DP

GOING TO

USB JACK (CHASSIS DN SIG)

USB

USB JACK (CHASSIS UP SIG)

FINGER P (CHASSIS DN SIG)

REPLICATOR PORT

MINIPCIE FOR ROBSON

MINIPCIE FOR WLAN

EXPRESS CARD

JACK (CHASSIS UP SIG)

D

C

B

USB_8

A

8

USB_9

7

6

USB_8_DN/DP

USB_9_DN/DP

5

4 2

BLUETOOTH

CAMERA (INV CONN)

[

BPAGE DRAWING

tawas_b.sch_1.5

Wed Feb 07 17:18:04 2007

3

PAGE_TITLE=USB TABLE]

CONN

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

D89092

A

PAGE

REV

5

2.0

1

Page 6

CR-6 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAG E6

8

D

C

H_STPCLK_N

29

B

IN

A

7

H_A_N<16..3>

10

BI

H_ADSTB0_N

10

BI

H_REQ_N<4..0>

10

BI

H_A_N<35..17>

10

BI

H_ADSTB1_N

10

BI

H_A20M_N

29

IN

H_FERR_N

29

OUT

H_IGNNE_N

29

R

2

R_STPCLK_N

HS_TAWAS

GND_1

GND_2

GND_3

IN

29

IN

29

IN

29

IN

HS20

1OF1

EMPTY

H_INTR

H_NMI

H_SMI_N

TP_CPU_RSVD01

TP_CPU_RSVD02

TP_CPU_RSVD03

TP_CPU_RSVD04

TP_CPU_RSVD05

TP_CPU_RSVD06

TP_CPU_RSVD07

TP_CPU_RSVD08

TP_CPU_RSVD09

TP_CPU_RSVD10

R14P

1

5%

0

CH

402

1

2

3

REV=1

6

U1PR

3

4

5

6

7

8

9

10

11

12

13

14

15

16

0

1

2

3

4

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

AA4

AB2

AA3

D22

A[3]#

L5

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L2

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U1

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W2

A[27]#

W5

A[28]#

Y4

A[29]#

U2

A[30]#

V4

A[31]#

W3

A[32]#

A[33]#

A[34]#

A[35]#

V1

ADSTB[1]#

A6

A20M#

A5

F

ERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD[01]

N5

RSVD[02]

T2

RSVD[03]

V3

RSVD[04]

B2

RSVD[05]

C3

RSVD[06]

D2

RSVD[07]

RSVD[08]

D3

RSVD[09]

F6

RSVD[10]

ADDR GROUP 0

ADDR GROUP 1

PROCHOT#

THERMAL

TH

ERMTRIP#

ICH

HCLK

RESERVED

F4

1O

DEFER#

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

XDP/ITP SIGNA LS

THERMDA

THERMDC

BCLK[0]

BCLK[1]

MEROM_SKT_NOHS

J4

REV=1

ADS#

BNR#

BPRI#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

TRDY#

HIT#

HITM#

PRDY#

PREQ#

TRST#

DBR#

TCK

TDI

TDO

TMS

IC

H1

E2

G5

H5

F21

E1

F1

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C2

D21

A24

B25

C7

A22

A21

0

45

H_ADS_N

H_BNR_N

H_BPRI_N

H_DEFER_N

H_DRDY_N

H_DBSY_N

H_BREQ_N

H_IERR_N

H_INIT_N

H_LOCK_N

H_CPURST_N

H_RS_N<2..0>

0

1

2

H_TRDY_N

H_HIT_N

H_HITM_N

XDP_BPM_N<4..0>

0

1

2

3

4

XDP_BPM_N<5>

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST_N

XDP_DBRESET_N

H_PROCHOT_N

H_THERMDA

H_THERMDC

PM_THRMTRIP_N

CK_H_CPU_DP

CK_H_CPU_DN

BI

BI

BI

IN

BI

BI

BI

IN

BI

IN

IN

BI

BI

OUT

BI

BI

BI

BI

IN

OUT

OUT

IN

IN

6

50

6

50

IN

24

24

IN

IN

10

10

10

10

10

10

10

29

33

10

10

50

10

10

10

10

50

6

50

50

6

50

31

9

9

12

29

3

1

2

50

XDP_TCK

XDP_TRST_N

V_1P05_CPU

R1PR

56

5%

CH

402

R5PR

1

54.9

1%

CH

2

603

V_1P05_CPU

R11PR

1

68

5%

CH

2

603

R9PR

1

2

54.9

1%

CH

603

R10PR

2

1

649

1%

CH

603

IN

V_1P05_CPU

R4PR

1

54.9

1%

CH

603

678

50 79

2

MODULE REV DETAILS

NAME

MODULE

TAWAS_CORE

1

V

RE

1.02.01 2-05-07

E

DAT

D

678

50 79

IN

R2PR

1

54.9

1%

CH

22

603

C

50

OUT

50

IN

50

678

50 79

IN

77

BI

IN

B

A

BPAGE DRAWING

tawas_b.sch_1.6

Wed Feb 07 17:18:05 2007

8

7

6

5

4 2

3

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

D89092

PAGE

REV

6

2.0

1

[PAGE_TITLE=CPU (1 OF 3)]

Page 7

CR-7 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAG E7

8

7

6

45

3

2

MODULE REV DETAILS

MODULE NAME

TAWAS_CORE

1

REV

DATE

2-05-071. 02.01

D

U1PR

ROM_SKT_NOHS

BI

C

H_DSTBN_N<0>

10

BI

H_DSTBP_N<0>

10

BI

H_DINV_N<0>

10

BI

10

BI

B

H_DSTBN_N<1> H_DSTBN_N<3>

10

BI

H_DSTBP_N<1>

10

BI

H_DINV_N<1>

10

BI

H_GTLREF

7

IN

CPU_TEST1

7

IN

CPU_TEST2

7

IN

CPU_TEST4

7

IN

CPU_BSEL0

23

OUT

CPU_BSEL1

23

OUT

CPU_BSEL2

23

A

OUT

TP_CPU_TEST3

TP_CPU_TEST5

TP_CPU_TEST6

E22

0

F24

1

E26

2

G22

3

F23

4

G25

5

E25

6

E23

7

K24

8

G24

9

J24

10

J23

11

H22

12

F26

13

K22

14

H23

15

J26

H26

H25

N22

16

K25

17

P26

18

R23

19

L23

20

M24

21

L22

22

M23

23

P25

24

P23

25

P22

26

T24

27

R24

28

L25

29

T25

30

N25

31

L26

M26

N24

AD26

C23

D25

C24

AF26

AF1

A26

B22

B23

C21

ME

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

BSEL[0]

BSEL[1]

BSEL[2]

REV=1

DATA GRP 0

DATA GRP 2DATA GRP 3

DSTBN[2]#

DSTBP[2]#

DATA GRP 1

DSTBN[3]#

DSTBP[3]#

MISC

2OF4

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

IC

SLP#

PSI#

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

H_D_N<47..32>H_D_N<15..0>

H_DSTBN_N<2>

H_DSTBP_N<2>

H_DINV_N<2>

H_D_N<63..48>H_D_N<31..16>

H_DSTBP_N<3>

H_DINV_N<3>

COMP0

COMP1

COMP2

COMP3

H_DPRSTP_N

H_DPSLP_N

H_DPWR_N

H_PWRGD

H_CPUSLP_N

H_PSI_N

OUT

1010

BI

10

BI

10

BI

10

BI

10

BI

10

BI

10

BI

10

BI

7

IN

7

IN

7

IN

7

IN

12

29

BI

BI

BI

IN

77

29

10

10

R8PR

77

1

1KCH5%

402

H_PWRGD_XDP

2

29

BI

50

BI

7

OUT

5079

7

IN

7

IN

7

IN

7

IN

7

IN

7

IN

CPU_TEST4

68

IN

COMP0

COMP1

COMP2

COMP3

CPU_TEST1

CPU_TEST2

V_1P05_CPU

C1PR

1

10%

.1UF

16V

EMPTY

603

2

1

R15PR

1K

1%

CH

2

603

R16PR

1

2K

1%

CH

2

603

R17PR

1

27.41%

603

R18PR

1

54.9CH1%

603

R19PR

1

27.4

603

R3PR

1

54.9

603

R6PR

1

1K

6031%EMPTY

1

R7PR

1K

EMPTY603

H_GTLREF

OUT

7

2

CH

2

2

1%

CH

2

1%

CH

2

2

1%

D

C

B

A

BPAGE DRAWING

tawas_b.sch_1.7

Wed Feb 07 17:18:07 2007

8

7

6

5

4 2

3

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

D89092

PAGE

REV

7

2.0

1

[PAGE_TITLE=CPU (2 OF 3)]

Page 8

CR-8 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAG E8

8

D

C

B

VCCP

8717879

IN IN

A10

A12

A13

A15

A17

A18

A20

B10

B12

B14

B15

B17

B18

B20

C10

C12

C13

C15

C17

C18

D10

D12

D14

D15

D17

D18

E10

E12

E13

E15

E17

E18

E20

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

A7

A9

B7

B9

C9

D9

E7

E9

F7

F9

A

7

U1PR

MEROM_SKT_NOHS

VCC[001]

VCC[068]

VCC[002]

VCC[069]

VCC[070]

VCC[003]

VCC[071]

VCC[004]

VCC[072]

VCC[005]

VCC[073]

VCC[006]

VCC[074]

VCC[007]

VCC[075]

VCC[008]

VCC[076]

VCC[009]

VCC[077]

VCC[010]

VCC[078]

VCC[011]

VCC[079]

VCC[012]

VCC[080]

VCC[013]

VCC[081]

VCC[014]

VCC[082]

VCC[015]

VCC[016]

VCC[083]

VCC[017]

VCC[084]

VCC[018]

VCC[085]

VCC[019]

VCC[086]

VCC[020]

VCC[087]

VCC[021]

VCC[088]

VCC[089]

VCC[022]

VCC[090]

VCC[023]

VCC[091]

VCC[024]

VCC[092]

VCC[025]

VCC[093]

VCC[026]

VCC[094]

VCC[027]

VCC[095]

VCC[028]

VCC[096]

VCC[029]

VCC[097]

VCC[030]

VCC[098]

VCC[031]

VCC[099]

VCC[032]

VCC[100]

VCC[033]

VCC[034]

VCC[035]

VCCP[01]

VCCP[02]

VCC[036]

VCCP[03]

VCC[037]

VCCP[04]

VCC[038]

VCCP[05]

VCC[039]

VCCP[06]

VCC[040]

VCCP[07]

VCC[041]

VCCP[08]

VCC[042]

VCCP[09]

VCC[043]

VCCP[10]

VCC[044]

VCCP[11]

VCC[045]

VCCP[12]

VCC[046]

VCCP[13]

VCC[047]

VCCP[14]

VCC[048]

VCCP[15]

VCC[049]

VCCP[16]

VCC[050]

VCC[051]

VCCA[01]

VCC[052]

VCCA[02]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

REV=1

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

3OF4

6

62

H_

VID<6..0>

VCCP

2329

32

678

OUT

5079

1

C2PR

220U

20%

2.5V

TANT

2

SM

1

77 79

OU

T

2

1

2

8

16

1718

V_1P05_CPU

V_1P05_CPU

F

C3PR

.01UF

10%

25V

R

X7

402

R13PR

100

1%

EMPTY

402

78

71

79

1415

10

63

71

77

V_1P5_CORE

1

C4PR

10.0UF

20%

6.3V

2

X5R

1206

1

2

IN

R12PR

100

1%

EMPTY

402

V_1P05_CORE

68

IN

1832373940

16

IN

VCCP

VCC_SENSE

VSS_SENSE

FB1PR

1

1

7

FB2PR

N

UNK

330

1.5A

BROAD

2

FB

UNK

330

1.5A

BROAD

2

FB

50 79

IN

OUT

OUT

N

77

77

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

0

AF5

1

AE5

2

AF4

3

AE3

4

AF3

5

AE2

6

AF7

AE7

IC

62 64

87178 79

45

71

3

U1

ME

ROM_SKT_NOHS

VSS[001]

VSS[082]

VSS[083]

VSS[002]

VSS[084]

VSS[003]

VSS[085]

VSS[004]

VSS[005]

VSS[086]

VSS[006]

VSS[087]

VSS[088]

VSS[007]

VSS[008]

VSS[089]

VSS[009]

VSS[090]

VSS[010]

VSS[091]

VSS[011]

VSS[092]

VSS[093]

VSS[012]

VSS[013]

VSS[094]

VSS[014]

VSS[095]

VSS[015]

VSS[096]

VSS[097]

VSS[016]

VSS[098]

VSS[017]

VSS[099]

VSS[018]

VSS[019]

VSS[100]

VSS[101]

VSS[020]

VSS[102]

VSS[021]

VSS[103]

VSS[022]

VSS[104]

VSS[023]

VSS[105]

VSS[024]

VSS[106]

VSS[025]

VSS[107]

VSS[026]

VSS[108]

VSS[027]

VSS[109]

VSS[028]

VSS[110]

VSS[029]

VSS[111]

VSS[030]

VSS[112]

VSS[031]

VSS[

VSS[032]

VSS[114]

VSS[033]

VSS[115]

VSS[034]

VSS[116]

VSS[035]

VSS[117]

VSS[036]

VSS[118]

VSS[037]

VSS[119]

VSS[038]

VSS[120]

VSS[039]

VSS[121]

VSS[040]

VSS[122]

VSS[041]

VSS[042]

VSS[123]

VSS[043]

VSS[124]

VSS[125]

VSS[044]

VSS[126]

VSS[045]

VSS[127]

VSS[046]

VSS[128]

VSS[047]

VSS[129]

VSS[048]

VSS[130]

VSS[049]

VSS[131]

VSS[050]

VSS[132]

VSS[051]

VSS[133]

VSS[052]

VSS[134]

VSS[053]

VSS[135]

VSS[054]

VSS[136]

VSS[055]

VSS[137]

VSS[056]

VSS[138]

VSS[057]

VSS[139]

VSS[058]

VSS[140]

VSS[059]

VSS[141]

VSS[060]

VSS[142]

VSS[061]

VSS[143]

VSS[062]

VSS[144]

VSS[063]

VSS[145]

VSS[064]

VSS[146]

VSS[065]

VSS[147]

VSS[066]

VSS[067]

VSS[148]

VSS[149]

VSS[068]

VSS[150]

VSS[069]

VSS[151]

VSS[070]

VSS[152]

VSS[071]

VSS[153]

VSS[072]

VSS[154]

VSS[073]

VSS[074]

VSS[155]

VSS[075]

VSS[156]

VSS[076]

VSS[157]

VSS[077]

VSS[158]

VSS[078]

VSS[159]

VSS[079]

VSS[160]

VSS[080]

VSS[161]

VSS[081] VSS[162]

VSS[163]

PR

113]

2

MODULE REV DETAILS

MODULE NAME

TAWAS_CORE

REV

CAD NOTE:

PLACE ON TOP SIDE IN

CPU CAVITY

V_1P05_CPU

C5PR

.1

UF

10%

16V

X7R

603

C7PR

.1UF

10%

16V

X7R

603

C9PR

.1UF

10%

16V

EMPTY

603

1

C6PR

.1UF

10%

16V

2

X7R

603

1

C8PR

.1UF

10%

16V

2

R

X7

603

1

C10PR

.1UF

10%

16V

2

EMPTY

603

1

2

1

2

1

2

CAD NOTE:

PLACE ON TOP SIDE SOUTH OF

CPU

1

DATE

2-05-071. 02.01

D

6

7

IN

8

50 79

C

B

A

4OF4

REV=1

IC

[PAGE_TITLE=CPU (3 OF 3)]

8

7

6

5

4 2

BPAGE DRAWING

tawas_b.sch_1.8

Thu Feb 08 10:56:06 2007

3

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

D89092

PAGE

REV

8

2.0

1

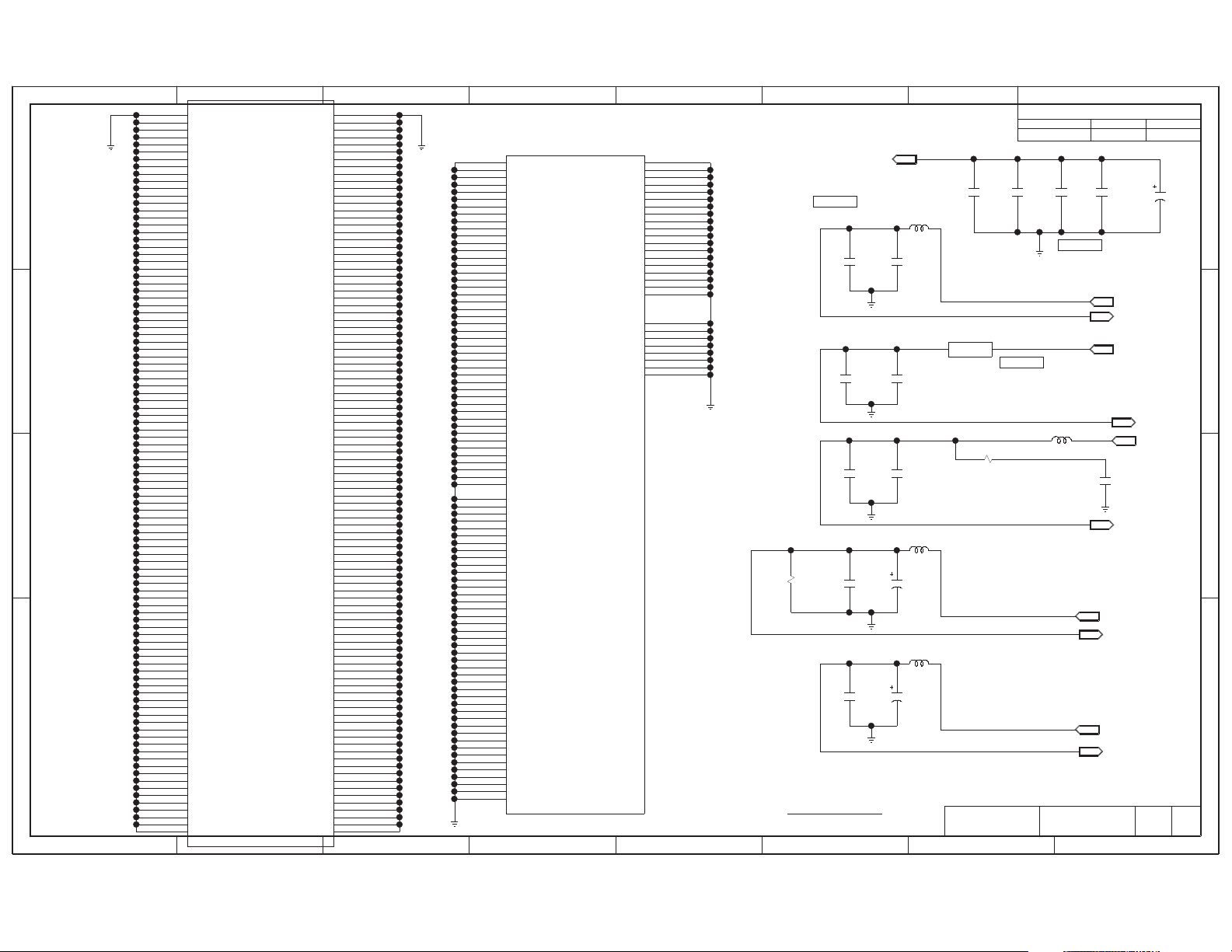

Page 9

CR-9 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAG E9

8

7

6

45

3

VCC3

2

MODULE REV DETAILS

MODULE NAME

1

REV

DATE

VCC3

D

R25

10K

5%

R27

1

H_THERMDA

6

OUT

H_THERMDC

6

IN

499

603

R28

1

499CH1%

603

2

1%

CH

1

C6

1000P

F

10%

50V

2

X7R

603

2

CH

402

ADT_THERM_DXP

ADT_THERM_DXN

ADT_THM_N

U2

ADM1032

2

D+

3

D-

4

THERM*

5

GN

SCLK

SDATA

ALERT*

D

VDD

IC

1

8

7

THRM_ALERT_N

6

1

C5

0.

1UF

20%

16V

2

Y5V

402

1

R26

10K

5%

CH

402

2

1

R24

10K

5%

CH

402

2

SMB_THRM_CLK

SMB_THRM_DATA

1

2

R29

1A

0

EM

603

PTY

PM

_THRM_N

OUT

55

BI

55

BI

33

31

C

D

C

V_3P3_STBY\G

1

R45

10K

5%

2

CH

402

CPU_FAN_TACH

B

26

3233

45616265666869

707576777883

IN

V_5P0_STBY\G

R460BU

10K

5%

CH

402

1

1

C93

.1

UF

10%

10V

2

2

X5R

402

CPU_FAN_PWM_N

C94

4.7UF

10%

6.3V

EMPTY

603

1

C943

1UF

20%

16V

2

Y5V

805

OUT

A36295-007

J39

1X3HDR

1

2

3

HDR

IN

55

31

32 333740 44 50 52

22 26

54 55 56 65 67 68 69 72 75 77

B

3

Q100

D

A

CPU_FAN_PWM

55

IN

1

BSS138N

FET

S

G

2

A

[PAGE_TITLE=CPU THERMAL MONITORS AND FAN]

BPAGE DRAWING

tawas_b.sch_1.9

Thu Feb 08 17:24:51 2007

8

7

6

5

4 2

3

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

D89092

PAGE

REV

9

2.0

1

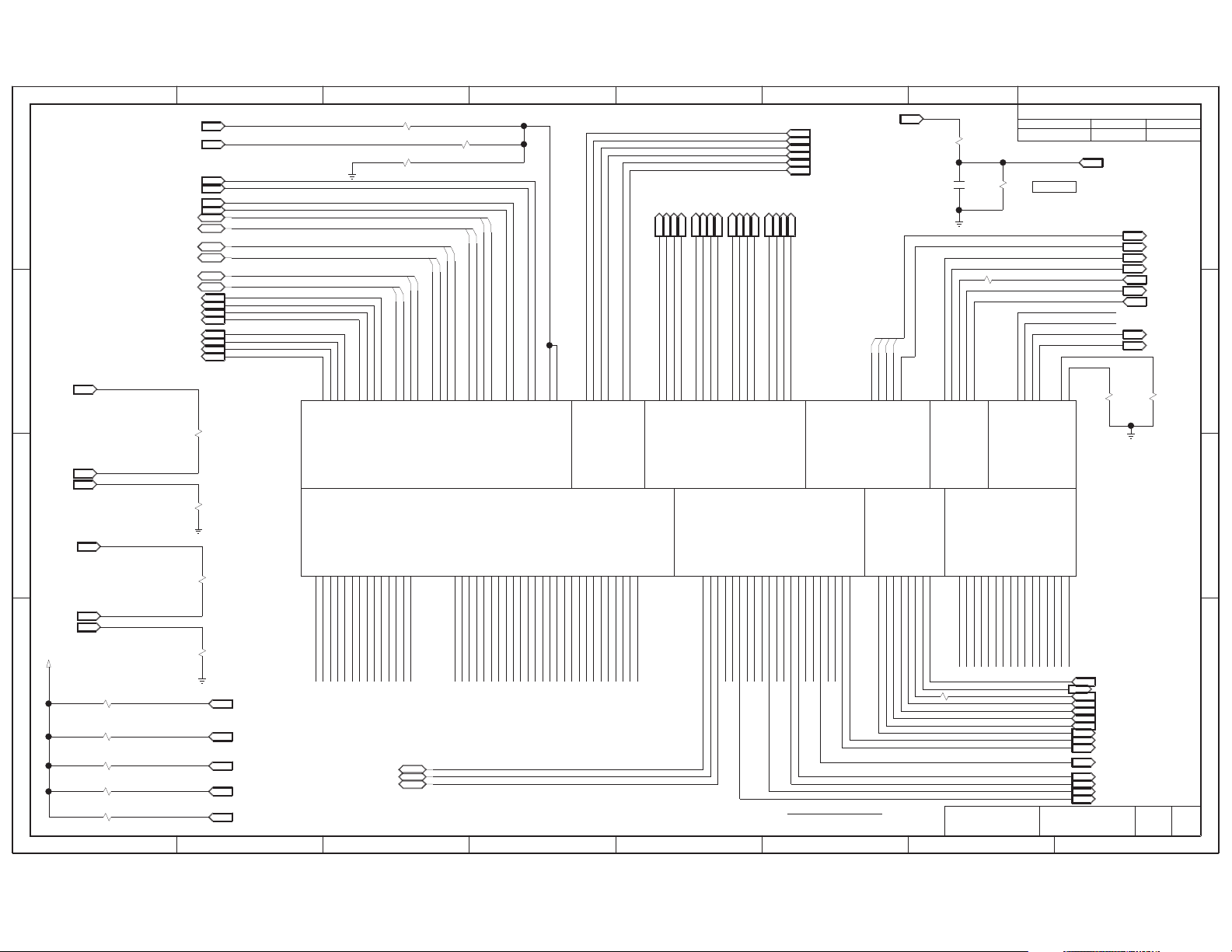

Page 10

CR-10 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAGE10

8

7

6

45

3

U1UB

H_D_N<63..0>

7

D

77

32

2329

15

16

17

18

6263

71

V_1P05_CORE

81014

IN

H_RCOMP

10

OUT

C

1

24.9

603

1

54.

402

1

54.

402

R34UB

R35UB

9

R36UB

9

2

1%

CH

1%

CH

2

1%

CH

H_SCOMP

2

H_SCOMP_N

OUT

OUT

10

10

BI

COMPS

V_1P05_CORE

161718

2329

32

B

A

8101415

IN

6263

7177

32

1

R32UB

221

1%

CH

2

603

1

R33UB

100

1%

2

CH

603

15

16

17

182329

71

77

H_SWING

1

C49UB

0.1UF

20%

16V

2

Y5V

402

V_1P05_CORE

8

1014

IN

6263

OUT

1

2

10

R37UB

1K

1%

CH

603

10

10

10

10

50

H_SWING

IN

H_RCOMP

IN

H_SCOMP

IN

H_SCOMP_N

IN

H_CPURST_N

6

OUT

H_CPUSLP_N

7

OUT

H_VREF

1

2

R38UB

2K

1%

CH

603

1

C53UB

.1UF

10%

10V

2

X5R

402

E2

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

AD12

32

33

34

35

36

AC14

37

AD11

38

AC11

39

40

41

42

43

44

45

46

47

48

49

AJ14

50

51

AE11

52

AH12

53

54

55

56

57

58

59

60

61

62

AH13

63

M10

N12

P13

W10

AE3

AD9

AC9

AC7

AB2

AD7

AB1

AC6

AE2

AC5

AG3

AJ9

AH8

AE9

AJ5

AH5

AJ6

AE7

AJ7

AJ2

AE5

AJ3

AH2

H_D#_0

G2

H_D#_1

G7

H_D#_2

M6

H_D#_3

H7

H_D#_4

H3

H_D#_5

G4

H_D#_6

F3

H_D#_7

N8

H_D#_8

H2

H_D#_9

H_D#_10

H_D#_11

N9

H_D#_12

H5

H_D#_13

H_D#_14

K9

H_D#_15

M2

H_D#_16

H_D#_17

Y8

H_D#_18

V4

H_D#_19

M3

H_D#_20

J1

H_D#_21

N5

H_D#_22

N3

H_D#_23

W6

H_D#_24

W9

H_D#_25

N2

H_D#_26

Y7

H_D#_27

Y9

H_D#_28

P4

H_D#_29

W3

H_D#_30

N1

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

Y3

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

B3

H_SWING

C2

H_RCOMP

W1

H_SCOMP

W2

H_SCOMP#

B6

H_CPURST#

E5

H_CPUSLP#

B9

H_AVREF

A9

H_DVREF

HOST

BPAGE DRAWING

Wed Feb 07 17:18:09 2007

CRESTLINE 1.0

8

7

6

5

4 2

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DS

TBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

1OF10

tawas_b.sch_1.10

3

J13

B11

C11

M11

C15

F16

L13

G17

#_10

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D1

7

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

G12

H17

G20

C8

E8

F12

D6

C10

AM5

AM7

H8

K7

E4

C6

G10

B7

K5

L2

AD13

AE13

M7

K3

AD2

AH11

L7

K2

AC2

AJ10

M14

E13

A11

H13

B12

E12

D7

D8

IC

[PAGE_TITLE=GMCH (1 OF 8)]

2

H_A_N<35..3>

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

H_ADS_N

H_ADSTB0_N

H_ADSTB1_N

H_BNR_N

H_BPRI_N

H_BREQ_N

H_DEFER_N

H_DBSY_N

CK_H_MCH_DP

CK_H_MCH_DN

H_DPWR_N

H_DRDY_N

H_HIT_N

H_HITM_N

H_LOCK_N

H_TRDY_N

H_DINV_N<3..0>

0

1

2

3

H_DSTBN_N<3..0>

0

1

2

3

H_DSTBP_N<3..0>

0

1

2

3

H_REQ_N<4..0>

0

1

2

3

4

H_RS_N<2..0>

0

1

2

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

1

MODULE REV DETAILS

MODULE NAME

TAWAS_CORE

BI

BI

BI

BI

BI

OU

T

BI

OUT

BI

IN

IN

OUT

BI

BI

BI

IN

OUT

BI

BI

BI

BI

OUT

DOCUMENT_NUMBER

1.02.01 2-05-07

6

6

6

6

6

6

6

6

6

24

24

7

6

6

6

6

6

7

7

7

6

6

D89092

REV

PAGE

10

1

DATE

REV

2.0

D

C

B

A

Page 11

D

C

B

A

28

28

CR-11 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAGE11

8

_BKLTCTL

L

26

OUT

L_BKLTEN

26

OUT

L_CTRL_CLK

1226

OUT

L_CTRL_DATA

1226

OUT

L_DDC_CLK

26

BI

L_DDC_DATA

26

BI

26

R41UB

1

R43UB

1

150

402

OUT

OUT

OUT

46UB

R

1

25

25

1%

CH

2

1%

CH

26

26

26

26

26

26

26

26

26

26

26

26

26

26

26

26

2

1%

CH

2

BI

BI

OUT

LVDS_IBG

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

27

OUT

27

OUT

27

OUT

R42UB

1

150

402

CRT_DDC_CLK

CRT_DDC_DATA

402

1.3KCH1%

603

402

CRT_BLUE

CRT_GREEN

CRT_RED

R48UB

1

39

R47UB

1

R49UB

1

39

R63UB

2

1

2.

1%

43K

CH

402

BOM NOTE:

MOD TO 2.37K OHM 1%

IPN A93548-283

150

402

28

28

28

R44UB

2

1

1%

150

CH

402

150

402

R45UB

2

1

1%

150

CH

402

CRT_HSYNC

OUT

CRT_VSYNC

OUT

8

R40UB

L_VDDEN

1

0

603

TP_LVDS_VBG

LA_CLK_DN

LA_CLK_DP

LB_CLK_DN

LB_CLK_DP

LA_DATA0_DN

LA_DATA1_DN

LA_DATA2_DN

LA_DATA0_DP

LA_DATA1_DP

LA_DATA2_DP

LB_DATA0_DN

LB_DATA1_DN

LB_DATA2_DN

LB_DATA0_DP

LB_DATA1_DP

LB_DATA2_DP

TVA_DAC

TVB_DAC

TVC_DAC

2

1%

CH

HSYNC

2

5%

CH

CRTIREF

2

VSYNC

2

5%

CH

2

1A

CH

7

L_VDD_EN_R

7

6

U1UB

CRESTLINE 1.0

J40

L_BKLT_CTRL

H39

L_BKLT_EN

E39

L_CTRL_CLK

E40

L_CTRL_DATA

C37

L_DDC_CLK

D35

L_DDC_DATA

K40

L_VDD_EN

L41

LVDS_IBG

L43

LVDS_VBG

N41

LVDS_VREFH

N40

LVDS_VREFL

D46

LVDSA_CLK#

C45

LVDSA_CLK

D44

LVDSB_CLK#

E42

LVDSB_CLK

G51

LVDSA_DATA#_0

E51

LVDSA_DATA#_1

F49

LVDSA_DATA#_2

G50

LVDSA_DATA_0

E50 L50

LVDSA_DATA_1

F48

LVDSA_DATA_2

G44

LVDSB_DATA#_0

7

B4

LVDSB_DATA#_1

B45

LVDSB_DATA#_2

E44

LVDSB_DATA_0

A47

LVDSB_DATA_1

A45

LV

DSB_DATA_2

E27

TVA_DAC

G27

TVB_DAC

K27

TVC_DAC

F27

TVA_RTN

J27

TVB_RTN

L27

TVC_RTN

M35

TP_TV_DCONSEL_0

TP_TV_DCONSEL_1

P33

H32

G32

K29

J29

F29

E29

K33

G3

F33

C32

E33

5

TV_DCONSEL_0

TV_DCONSEL_1

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_TVO_IREF

CRT_VSYNC

LVDS

TV

VGA

PEG_COMPI

PEG_COMPO

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

PEG_RX#_7

PEG_RX#_8

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PCI-EXPRESS GRAPHICS

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PEG_TX#_11

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

3OF10

6

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

45

R39UB

2

VCC_PEG

16

17

IN

N43

PEG_COMP

M43

TP_PEG_RX_N<0>

J51

TP_PEG_RX_N<1>

L51

TP_PEG_RX_N<2>

N47

TP_PEG_RX_N<3>

T45

TP_PEG_RX_N<4>

T50

TP_PEG_RX_N<5>

U40

TP_PEG_RX_N<6>

Y44

TP_PEG_RX_N<7>

Y40

TP_PEG_RX_N<8>

AB51

TP_PEG_RX_N<9>

W49

TP_PEG_RX_N<10>

AD44

TP_PEG_RX_N<11>

AD40

TP_PEG_RX_N<12>

AG46

TP_PEG_RX_N<13>

AH49

TP_PEG_RX_N<14>

AG45

TP_PEG_RX_N<15>

AG41

TP_PEG_RX<0>

J50

TP_PEG_RX<1>

TP_PEG_RX<2>

M47

TP_PEG_RX<3>

U44

TP_PEG_RX<4>

T49

TP_PEG_RX<5>

T41

TP_PEG_RX<6>

W45

TP_PEG_RX<7>

W41

TP_PEG_RX<8>

AB50

TP_PEG_RX<9>

Y48

TP_PEG_RX<10>

AC45

TP_PEG_RX<11>

AC41

TP_PEG_RX<12>

AH47

TP_PEG_RX<13>

AG49

TP_PEG_RX<14>

AH45

TP_PEG_RX<15>

AG42

TP_P_TXN0

N45

U39

TP_P_TXN1

TP_P_TXN2

U47

N51

TP_P_TXN3

R50

TP_P_TXN4

T42

TP_P_TXN5

Y43

TP_P_TXN6

W46

TP_P_TXN7

TP_P_TXN8

W38

TP_P_TXN9

AD39

AC46

TP_P_TXN10

TP_P_TXN11

AC49

TP_P_TXN12

AC42

TP_P_TXN

AH39

AE49

AH44

M45

T38

T46

N50

R51

U43

W42

Y47

Y39

AC38

AD47

AC50

AD43

AG39

AE50

AH43

TP_P_TXN14

TP_P_TXN15

TP_P_TXP0

TP_P_TXP1

TP_P_TXP2

TP_P_TXP3

TP_P_TXP4

TP_P_TXP5

TP_P_TXP6

TP_P_TXP7

TP_P_TXP8

TP_P_TXP9

TP_P_TXP10

TP_P_TXP11

TP_P_TXP12

TP_P_TXP13

TP_P_TXP14

TP_P_TXP15

13

1

9

1%

24.

CH

603

61

71

IC

3

1

R52UB

1K

1%

CH

603

2

1

R54UB

3.

24K

1%

CH

603

2

1

R55UB

1K

1%

CH

603

2

V_SM SM_RCOMP

11

12

14

15

1617

1920

IN

SM_RCOMP_N

12

OUT

2

V_SM

BOM NOTE:

MOD TO 3.01K OHM 1%

IPN A93550-095

1

C57UB

.01UF

10%

25V

2

X7R

402

MODULE REV DETAILS

MODULE NAME

TAWAS_CORE

111214 151617

IN

SM_RCOMP_VOH

1

1

2

C54UB

.01UF

10%

25V

X7R

402

2

C55UB

2.2UF

10%

6.

X5R

603

SM_RCOMP_VOL

1

C58UB

2.2UF

10%

6.3V

2

X5R

603

1

2

R61UB

1%

20

CH

402

R62UB

1

2021%

402

CH

1

REV

1.02.01 2-05-07

12

OUT

3V

12

OUT

DATE

19 206171

12

OUT

D

C

B

A

[PAGE_TITLE=GMCH (2 OF 8)]

BPAGE DRAWING

tawas_b.sch_1.11

Wed Feb 07 17:18:10 2007

5

4 2

3

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

D89092

PAGE

REV

11

2.0

1

Page 12

CR-12 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAGE12

8

11

14

ORE

ORE

15161719

19

20

61

11

11

11

11

20

21

19

21

20

21

19

21

20

21

19

21

20

20

19

19

20

20

19

19

1

R3UB

4.7K

5%

EMPTY

2

402

1

R4UB

4.

5%

2

EM

402

20

6171

D

C

71

V_1P25_C

12

1617

IN

18

32

68

CK_96M_DREF_DN

1224

IN

CK_96M_DREF_DP

1224

IN

B

71

V_1P25_C

12

16

17

IN

68

1832

1

2

CK_DREF_100M_SS_DN

12

24

IN

CK_DREF_100M_SS_DP

12

24

IN

1

VCC3

A

R67UB

10K

402

R68UB

10K

402

R69UB

10K

402

R70UB

10K

402

R71UB

10K

402

1

1

1

1

1

2

CK_

5%

CH

PM_EXTTS0_N

2

5%

CH

PM_EXTTS1_N

2

5%

CH

L_CTRL_CLK

2

5%

CH

2

L_CTRL_DATA

5%

CH

2

OE_MCH_N

8

V_SM

IN

DDR_REF

IN

IN

IN

IN

IN

BI

BI

BI

BI

BI

BI

M_CLK_DDR_DN<4>

OUT

M_CLK_DDR_DN<3>

OUT

M_CLK_DDR_DN<1>

OUT

M_CLK_DDR_DN<0>

OUT

M_CLK_DDR_DP<4>

OUT

M_CLK_DDR_DP<3>

OUT

M_CLK_DDR_DP<1>

OUT

M_CLK_DDR_DP<0>

OUT

7K

PTY

R6

UB

4.

7K

5%

EMPTY

402

R7UB

4.7K

5%

EMPTY

402

12

IN

121921

IN

12

IN

11

IN

11

IN

7

SM_RCOMP_VOL

SM_RCOMP_VOH

SM_RCOMP_N

SM_RCOMP

M_ODT<3..2>

M_ODT<1..0>

M_CS_N<3..2>

M_CS_N<1..0>

M_CKE<4..3>

M_CKE<1..0>

U1UB

24

20

21

26

26

7

CRESTLINE 1.0

6

R73UB

1

2

1K

1%

EMPTY

402

R74UB

1

2

1K1%

EMPTY

402

2

1

0

3

4

1

0

BD39

BG37

BG20

BK16

BG16

AV23

BA25

BB23

AV29

SM_CK_0

SM_CK_4

SM_CK_1

SM_CK_3

AY32

AW30

AW25

BA23

BE29

AW23

SM_CK#_4

SM_CK#_0

SM_CK#_1

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_3

SM_CKE_4

SM_CS#_0

SM_CS#_1

DDR

MUXING

R27UB

2

5%CH0

3

BE13

SM_CS#_2

SM_CS#_3

1

402

2

1

0

BJ14

BJ15

BH18

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_MCH_VREF

3

BK31

BL15

BE16

BK14

SM_ODT_3

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

L31

B

SM_RCOMP_VOL

H48

K44

H47

C42

AW4

B42

AR49

PEG_CLK

SM_VREF_0

SM_VREF_1

PEG_CLK#

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

CLK

RSVD

RSVD1

RSVD2

RSVD3

RSVD4

P37

R35

N35

P36

TP_MCH_RSVD_1

TP_MCH_RSVD_2

TP_MCH_RSVD_4

TP_MCH_RSVD_3

RSVD11

RSVD10

RSVD12

RSVD5

RSVD6

AR13

AR12

TP_MCH_RSVD_6

TP_MCH_RSVD_5

RSVD13

RSVD7

RSVD8

RSVD9

RSVD14

37

J12

D20

AN13

AM12

AR37

AL36

AM36

AM

TP_MCH_RSVD_14

TP_MCH_RSVD_11

TP_MCH_RSVD_10

TP_MCH_RSVD_9

TP_MCH_RSVD_8

TP_MCH_RSVD_7

TP_MCH_RSVD_12

TP_MCH_RSVD_13

23

BI

23

BI

23

BI

RSVD21

RSVD20

H10

B51

TP_MCH_RSVD_21

TP_MCH_RSVD_20

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

BF23

BJ20

BF19

BJ18

BK18

BH20BK22

P_MCH_RSVD_26

P_MCH_RSVD_23

T

TP_MCH_RSVD_25

T

TP_MCH_RSVD_28

TP_MCH_RSVD_27

TP_MCH_RSVD_24

TP_MCH_RSVD_22

SVD35

RSVD31

RSVD30

RSVD32

RSVD33

RSVD29

RSVD34

BH39

BE24

BJ29

BG23

BC23

BD24

TP_MCH_RSVD_33

TP_MCH_RSVD_32

TP_MCH_RSVD_34

TP_MCH_RSVD_29

TP_MCH_RSVD_30

TP_MCH_RSVD_31

RSVD41

R

RSVD36

RSVD42

RSVD43

RSVD44

RSVD37

RSVD38

D47

C48

BK20

AW20

TP_MCH_RSVD_38

TP_MCH_RSVD_35

TP_MCH_RSVD_36

TP_MCH_RSVD_37

RSVD45

RSVD39

RSVD40

A35

B37

B34 K45

C44

B36

C34

B44

TP_MCH_RSVD_42

TP_MCH_RSVD_41

TP_MCH_RSVD_40

TP_MCH_RSVD_39

TP_MCH_RSVD_45

TP_MCH_RSVD_44

TP_MCH_RSVD_43

[PAGE_TITLE=GMCH (3 OF 8)]

6

5

45

CK_96M_DREF_DP

_96M_DREF_DN

CK

CK_DREF_100M_SS_DP

CK_DREF_100M_SS_DN

CK_PE_100M_3GPLL_DP

CK_PE_100M_3GPLL_DN

303030

30

OUT

OUT

OUT

OUT

DMI_IT_MR_0_DN

DMI_IT_MR_3_DN

DMI_IT_MR_2_DN

DMI_IT_MR_1_DN

AN47

AN46

AN42

AJ38

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

303030

30

OUT

OUT

OUT

OUT

DMI_IT_MR_3_DP

DMI_IT_MR_2_DP

DMI_IT_MR_1_DP

DMI_IT_MR_0_DP

AN41

AJ39

AN45

AM47

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

30

303030

OUT

OUT

OUT

OUT

DMI_MT_IR_1_DN

DMI_MT_IR_3_DN

DMI_MT_IR_2_DN

DMI_MT_IR_0_DN

AM40

AJ41

AM44

AJ46

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

303030

30

OUT

OUT

DMI_MT_IR_1_DP

DMI_MT_IR_2_DP

DMI_MT_IR_0_DP

AM39

AJ42

AJ47

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI

CFG

CFG_1

CFG_3

CFG_4

CFG_2

CFG_0

C23

N27

P27

C21

N24

TP_MCH_CFG_4

TP_MCH_CFG_3

4 2

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

L23

C20

G23

F23

R24

J20

N23

TP_MCH_CFG_7

TP_MCH_CFG_6

TP_MCH_CFG_10

TP_MCH_CFG_11

TP_MCH_CFG_8

Wed Feb 07 17:18:11 2007

CFG_11

3

6870

12

24

IN

12

24

IN

12

24

IN

12

24

IN

24

IN

24

IN

OUT

OUT

DMI_MT_IR_3_DP

AM43

DMI_TXP_3

G

RAPHICS VID

CFG_12

CFG_13

E23

J23

BPAGE DRAWING

tawas_b.sch_1.12

CFG_20

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

K23

L35

L32

M20

M24

N33

E20

TP_MCH_CFG_14

TP_MCH_CFG_15

TP_MCH_CFG_17

TP_MCH_CFG_18

3

V_1P25_M

1617

IN

3

210

B39

A39

E36

C38

E35

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VR_EN

PM NC

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

PM_DPRSTP#

THERMTRIP#

L39

L36

J36

DPRSLPVR

N20

G36

AV20

AW49

RST_IN_MCH+_N

100

402

PM_BM_BUSY#

G41

2

R51UB

1

1K

1%

CH

2

402

1

C56UB

.1UF

10%

16V

2

X7R

603

R9UB

1

0

402

CLPWROK_MCH_R

AM50

AM49

AN49

AK50

AT43

CL_CLK

CL_DATA

CL_RST#

CL_VREF

CL_PWROK

ME

NC_1

NC_2

NC_4

NC_5

NC_3

BL50

BK50

BL49

BJ51

BK51

TP_MCH_NC3

TP_MCH_NC5

TP_MCH_NC2

TP_MCH_NC1

TP_MCH_NC4

H_DPRSLPVR

PM_THRMTRIP_N

R50UB

PLTRST_N

2

1

DELAY_VR_PWRGOOD

5%

PM_EXTTS1_N

CH

PM_EXTTS0_N

H_DPRSTP_N

PM_BMBUSY_N

MCH_CFG_20

MCH_CFG_19

MCH_CFG_16

MCH_CFG_13

MCH_CFG_12

MCH_CFG_9

MCH_CFG_5

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

MODULE REV DETAILS

NAME

MODULE

TAWAS_CORE

MCH_CLVREF

1

R53UB

390

5%

BOM NOTE:

2

CH

REPLACE R53UB WIT H 392 OHM A93550-408

603

G_VID<3..0>

INT_GFX_ENABLE

CL_CLK0

CL_DATA0

CLPWROK

2

5%

CL_RST0_N

CH

MCH_CLVREF

H35K36

G39

G40

CLK_REQ#

ICH_SYNC#

SDVO_CTRL_CLK

SDVO_CTRL_DATA

MI

SC

NC_6

NC_7

NC_8

NC_9

NC_11

NC_10

NC_12

E1

BJ1A5C51

BK1

BL3

BL2

TP_MCH_NC11

TP_MCH_NC10

TP_MCH_NC8

TP_MCH_NC12

TP_MCH_NC6

TP_MCH_NC7

TP_MCH_NC9

IN

TP_SDVO_CTRLCLK

TP_SDVO_CTRLDATA

CK_OE_MCH_N

MCH_ICH_SYNC_N

MCH_TEST1_R

MCH_TEST2_R

A37

R32

1

2

IC

TEST_1

2OF10

NC_13

NC_14

NC_15

NC_16 TEST_2

BK2

B50

A50

A49

TP_MCH_NC13

TP_MCH_NC15

TP_MCH_NC14

TP_MCH_NC16

31

IN

6

OUT

34 37

IN

31

IN

122021

IN

121921

IN

7

IN

31

OUT

18

OUT

18

OUT

18

OUT

18

OUT

18

OUT

18

OUT

18

OUT

DOCUMENT_NUMBER

D89092

12

29

29 77

V

RE

OUT

OUT

OUT

OUT

OUT

OUT

OUT

R57UB

20K

5%

CH

402

77

52 59

55

1

E

DAT

2-05-071. 02.01

D

75

14

75

31

31

31

72

IN

31

12

IN

12

24

1

2

31

R56UB

0

5%

CH

402

C

B

A

PAGE

REV

12

2.0

1

Page 13

CR-13 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAGE13

8

D

M_A_DQ<63..0>

19

BI

C

B

AR43

0

AW44

1

BA45

2

AY46

3

AR41

4

AR45

5

AT42

6

AW47

7

BB45

8

BF48

9

BG47

10

BJ45

11

BB47

12

BG50

13

BH49

14

BE45

15

AW43

16

BE44

17

BG42

18

BE40

19

BF44

20

BH45

21

BG40

22

BF40

23

AR40

24

AW40

25

AT39

26

AW36

27

AW41

28

AY41

29

AV38

30

AT38

31

AV13

32

AT13

33

AW11

34

AV11

35

AU15

36

AT11

37

BA13

38

BA11

39

BE10

40

BD10

41

BD8

42

AY9

43

BG10

44

AW9

45

BD7

46

BB9

47

BB5

48

AY7

49

AT5

50

AT7

51

AY6

52

BB7

53

AR5

54

AR8

55

AR9

56

AN3

57

AM8

58

AN10

59

AT9

60

AN9

61

AM9

62

AN11

63

A

7

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

U1UB

CRESTLINE 1.0

DDR SYSTEM MEMORY A

4OF10

SA_BS_0

SA_BS_1

SA_BS_2

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVEN#

SA_WE#

6

M_B_DQ<63..0>

20

BI

M_A_DM<7..0>

0

1

2

3

4

5

6

7

M_A_DQS_DP<7..0>

0

1

2

3

4

5

6

7

M_A_DQS_DN<7..0>

0

1

2

3

4

5

6

7

M_A_A<13..0>

0

1

2

3

4

5

6

7

8

9

10

11

12

13

M_A_BS<0>

M_A_BS<1>

M_A_BS<2>

M_A_CAS_N

M_A_RAS_N

M_A_WE_N

OUT

OUT

OUT

OUT

OUT

OUT

OUT

19 21

19 21

19 21

19 21

19

19

BI

19

BI

21

19

BI

19 21

19 21

BB19

BK19

BF29

BL17

AT45

BD44

BD42

AW38

AW13

BG8

AY5

AN6

AT46

BE48

BB43

BC37

BB16

BH6

BB2

AP3

AT47

BD47

BC41

BA37

BA16

BH7

BC1

AP2

BJ19

BD20

BK27

BH28

BL24

BK28

BJ27

BJ25

BL28

BA28

BC19

BE28

BG30

BJ16

BE18

AY20

BA19

TP_SA_RCVEN_N

IC

45

AP49

0

AR51

1

AW50

2

AW51

3

AN51

4

AN50

5

AV50

6

AV49

7

BA50

8

BB50

9

BA49

10

BE50

11

BA51

12

AY49

13

BF50

14

BF49

15

BJ50

16

BJ44

17

BJ43

18

BL43

19

BK47

20

BK49

21

BK43

22

BK42

23

BJ41

24

BL41

25

BJ37

26

BJ36

27

BK41

28

BJ40

29

BL35

30

BK37

31

BK13

32

BE11

33

BK11

34

BC11

35

BC13

36

BE12

37

BC12

38

BG12

39

BJ10

40

41

42

43

44

BK10

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

BL9

BK5

BL

BK9

BJ8

BJ6

BF4

BH5

BG1

BC2

BK3

BE4

BD3

BJ2

BA3

BB3

AR1

AT3

AY2

AY3

AU2

AT2

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

5

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

3

U1UB

CRESTLINE 1.0

SYSTEM MEMORY B

DDR

5OF10

SB_BS_0

SB_BS_1

SB_BS_2

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVEN#

SB_WE#

IC

AY17

BG18

BG36

BE17

AR50

BD49

BK45

BL39

BH12

BJ7

BF3

AW2

AT50

BD50

BK46

BK39

BJ12

BL

BE2

AV2

AU50

BC50

BL45

BK38

BK12

BK7

BF2

AV3

BC18

BG28

BG25

AW17

BF25

BE25

BA29

BC28

AY28

BD37

BG17

BE37

BA39

BG13

AV16

AY18

BC17

7

2

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

8

9

10

11

12

13

TP_MB_RCVEN_N

1

MODULE REV DETAILS

MODULE NAME

TAWAS_CORE

M_B_BS<0>

M_B_BS<1>

M_B_BS<2>

M_B_CAS_N

M_B_DM<7..0>

M_B_DQS_DP<7..0>

M_B_DQS_DN<7..0>

M_B_A<13..0>

M_B_RAS_N

M_B_WE_N

REV

1.02.01 2-05-07

20

21

OUT

20

21

OUT

20

21

OUT

20

21

OUT

20

OUT

20

BI

20

BI

20

BI

20

21

OUT

20

21

OUT

DATE

D

C

21

B

A

BPAGE DRAWING

tawas_b.sch_1.13

Wed Feb 07 17:18:12 2007

8

7

6

5

4 2

3

INTEL

CONFIDENTIAL

CUSTOM TEXT BPAGE

DOCUMENT_NUMBER

D89092

PAGE

REV

13

2.0

1

[PAGE_TITLE=GMCH (4 OF 8)]

Page 14

CR-14 : @TAWAS_B_LIB.TAWAS_B(SCH_1):PAGE14

8

7

6

45

3

BOM NOTE:

REPLACE C63UB AND C64UB WITH

1823

D

62637177

IN

29

32

V_1P05_CORE

81015

16

17

C

BOM NOTE:

75

V_GFX

15

IN

71

76

REPLACE C68UB WITH 0.47UF IPN 602433-015

1

1

C67UB

C68UB

220UF

4700PF

20%

20%

2.5V

50V

2

PTY

EM

X7

2

7343

R

603

B

BOM NOTE:

REPLACE C73UB AND C74UB WITH

V_1P05_M

14

70

IN

A

0.22UF IPN 602433-021

1

72UB

C

22UF

20%

6.3V

2

X5R

805

0.22UF IPN 602433-021

1

C62UB

1

C59UB

220UF

22U

T

1U

F

3V

73UB

2

1

2

F

20%

6.3V

X5R

805

C70UB

10UF

20%

6.3V

X5R

805

1

2

C

2200PF

5%

25V

COG

603

20%

2.5V

TAN

2

SM

1

C69UB

20%

6.

2

X5R

603

1

C

2200PF

5%

25V

2

COG

603

74UB

U1UB

CRESTLINE 1.0

C63UB

2200P

5%

25V

COG

603

C60UB

22U

F

20%

6.3V

X5R

805

1

2

1

F

2

1

C71UB

.1

UF

10%

10V

2

X5R

402

5UB

C7

.1UF

10%

10V

X5R

402

1

2

1

2

C64UB

2200P

5%

25V

COG

603

1

2

1

2

F

C

.1UF

10%

10V

X5R

402

C61UB

.1

10%

10V

X5R

402

76UB

1

C65UB

.1

UF

10%

10V

2

X5R

402

UF

1

C77UB

.1UF

10%

10V

2

X5R

402

AB33

AB36

AB37

AC33

AC35

AC36

AD35

AD36

AF33

AF36

AH33

AH35

AH36

AH37

AJ33

AJ35

AK33

AK35

AK36

AK37

AD33

AJ36

AM35

AL33

AL35

AA33

AA35

AA36

AP35

AP36

AR35

AR36

AL24

AL26

AL28

AM26

AM28

AM29

AM31

AM32

AM33

AP29

AP31

AP32

AP33

AL29

AL31

AL32

AR31

AR32

AR33

Y32

Y33

Y35

Y36

Y37

T30

T34

T35

U29

U31

U32

U33

U35

U36

V32

V33

V36

V37

VCC_NCTF_1

VCC_NCTF_2

VCC_NCTF_3

VCC_NCTF_4

VCC_NCTF_5

VCC_NCTF_6

VCC_NCTF_7

VCC_NCTF_8

VCC_NCTF_9

VCC_NCTF_10

VCC_NCTF_11

VCC_NCTF_12

VCC_NCTF_13

VCC_NCTF_14

VCC_NCTF_15

VCC_NCTF_16

VCC_NCTF_17

VCC_NCTF_18

VCC_NCTF_19

VCC_NCTF_20

VCC_NCTF_21

VCC_NCTF_22

VCC_NCTF_23

VCC_NCTF_24

VCC_NCTF_25

VCC_NCTF_26

VCC_NCTF_27

VCC_NCTF_28

VCC_NCTF_29

VCC_NCTF_30

VCC_NCTF_31

VCC_NCTF_32

VCC_NCTF_33

VCC_NCTF_34

VCC_NCTF_35

VCC_NCTF_36

VCC_NCTF_37

VCC_NCTF_38

VCC_NCTF_39

VCC_NCTF_40

CC_NCTF_41

V

VCC_NCTF_42

VCC_NCTF_43

VCC_NCTF_44

VCC_NCTF_45

VCC_NCTF_46

VCC_NCTF_47

VCC_NCTF_48

VCC_NCTF_49

VCC_NCTF_50

VCC_AXM_NCTF_1

VCC_AXM_NCTF_2

VCC_AXM_NCTF_3

VCC_AXM_NCTF_4

VCC_AXM_NCTF_5

VCC_AXM_NCTF_6

VCC_AXM_NCTF_7

VCC_AXM_NCTF_8

VCC_AXM_NCTF_9

VCC_AXM_NCTF_10

VCC_AXM_NCTF_11

VCC_AXM_NCTF_12

VCC_AXM_NCTF_13