Page 1

Intel® Stratix® 10 SX SoC

Development Kit User Guide

Subscribe

Send Feedback

UG-20081 | 2020.09.08

Latest document on the web: PDF | HTML

Page 2

Contents

Contents

1. Overview........................................................................................................................ 4

1.1. General Development Kit Description........................................................................4

1.2. Recommended Operating Conditions........................................................................ 5

1.3. Handling the Development Kit................................................................................. 5

2. Getting Started............................................................................................................... 6

2.1. Installing Quartus Prime Software............................................................................6

2.2. Installing the Intel FPGA Download Cable..................................................................7

2.3. Installing the Intel SoC Embedded Development Suite (EDS).......................................7

2.4. Installing the Intel Stratix 10 SX SoC Development Kit Package................................... 7

3. Development Kit Setup................................................................................................... 9

3.1. Inspect the Development Kit................................................................................... 9

3.2. Default Setup of the Development Kit.......................................................................9

3.3. Intel MAX 10 System Controller Updates................................................................. 10

4. Development Kit Components....................................................................................... 12

4.1. Development Kit Feature Summary........................................................................ 12

4.2. Board Components...............................................................................................14

4.3. Intel Stratix 10 SoC Device Overview..................................................................... 17

4.4. Intel MAX 10 System Controller Overview............................................................... 22

4.5. FPGA Configuration.............................................................................................. 24

4.6. General User Input/Output....................................................................................24

4.7. Connectors and Interfaces.................................................................................... 25

4.7.1. PCIe Slot................................................................................................ 25

4.7.2. ZQSFP+..................................................................................................28

4.7.3. SFP+......................................................................................................29

4.7.4. HDMI..................................................................................................... 29

4.7.5. SDI Port................................................................................................. 30

4.7.6. MXP....................................................................................................... 30

4.7.7. Intel FPGA Download Cable Direct Port (Debug Port).....................................31

4.7.8. FMC+ A/B Slot.........................................................................................32

4.7.9. FMC+ A/B LVDS Interfaces (LPC Pins).........................................................38

4.7.10. LMK05028 Jitter Attenuator..................................................................... 45

4.7.11. FPGA-IOMAX10 Interface........................................................................ 46

4.8. Daughter Cards................................................................................................... 49

4.8.1. HPS IO-48 OOBE Daughter Card................................................................ 49

4.8.2. HPS IO-48 NAND Flash Daughter Card........................................................ 59

4.8.3. HPS Boot Flash Card.................................................................................67

4.9. System Memory...................................................................................................72

4.9.1. FPGA Memory (DDR4 SO-DIMM)................................................................ 72

4.9.2. HPS Memory (External 4 GB HILO x72 DDR4 )............................................. 76

4.9.3. HPS I2C Interface.....................................................................................81

4.10. System Power....................................................................................................82

4.10.1. Power Supply Options............................................................................. 82

4.10.2. Power Sequence.....................................................................................83

4.10.3. Power Distribution Network..................................................................... 84

Intel® Stratix® 10 SX SoC Development Kit User Guide

2

Send Feedback

Page 3

Contents

5. Board Test System........................................................................................................ 86

5.1. Preparing the Board............................................................................................. 87

5.2. Running the BTS..................................................................................................87

5.3. Using the BTS..................................................................................................... 87

5.3.1. The Configure Menu................................................................................. 87

5.3.2. The GPIO Tab.......................................................................................... 89

5.3.3. The QSFP/SFP Tab....................................................................................90

5.3.4. The PCIE Tab...........................................................................................93

5.3.5. The MXP Tab........................................................................................... 96

5.3.6. The FMCA Tab..........................................................................................99

5.3.7. The FMCB Tab........................................................................................105

5.3.8. The DDR4 Tab........................................................................................110

5.3.9. Power Monitor........................................................................................111

5.3.10. The Clock Control................................................................................. 113

A. Additional Information............................................................................................... 115

A.1. Modify the Intel Stratix 10 SX SoC Development Kit to use a battery for the BBRAM... 115

A.2. Modify the Intel Stratix 10 SX SoC Development Kit HPS DDR4 memory width and

ECC configuration using the Golden Hardware Reference Design project..................116

A.3. Safety and Regulatory Information....................................................................... 117

A.3.1. Safety Warnings.....................................................................................117

A.3.2. Safety Cautions..................................................................................... 119

A.4. Compliance Information......................................................................................121

A.4.1. Compliance and Conformity Statements.................................................... 121

B. Revision History..........................................................................................................122

B.1. Revision History ................................................................................................122

Send Feedback

Intel® Stratix® 10 SX SoC Development Kit User Guide

3

Page 4

UG-20081 | 2020.09.08

Send Feedback

1. Overview

This document describes the features of the Intel® Stratix® 10 SoC development kit,

including detailed pin-out and component reference information required to create

custom FPGA designs that interface with all components of the board.

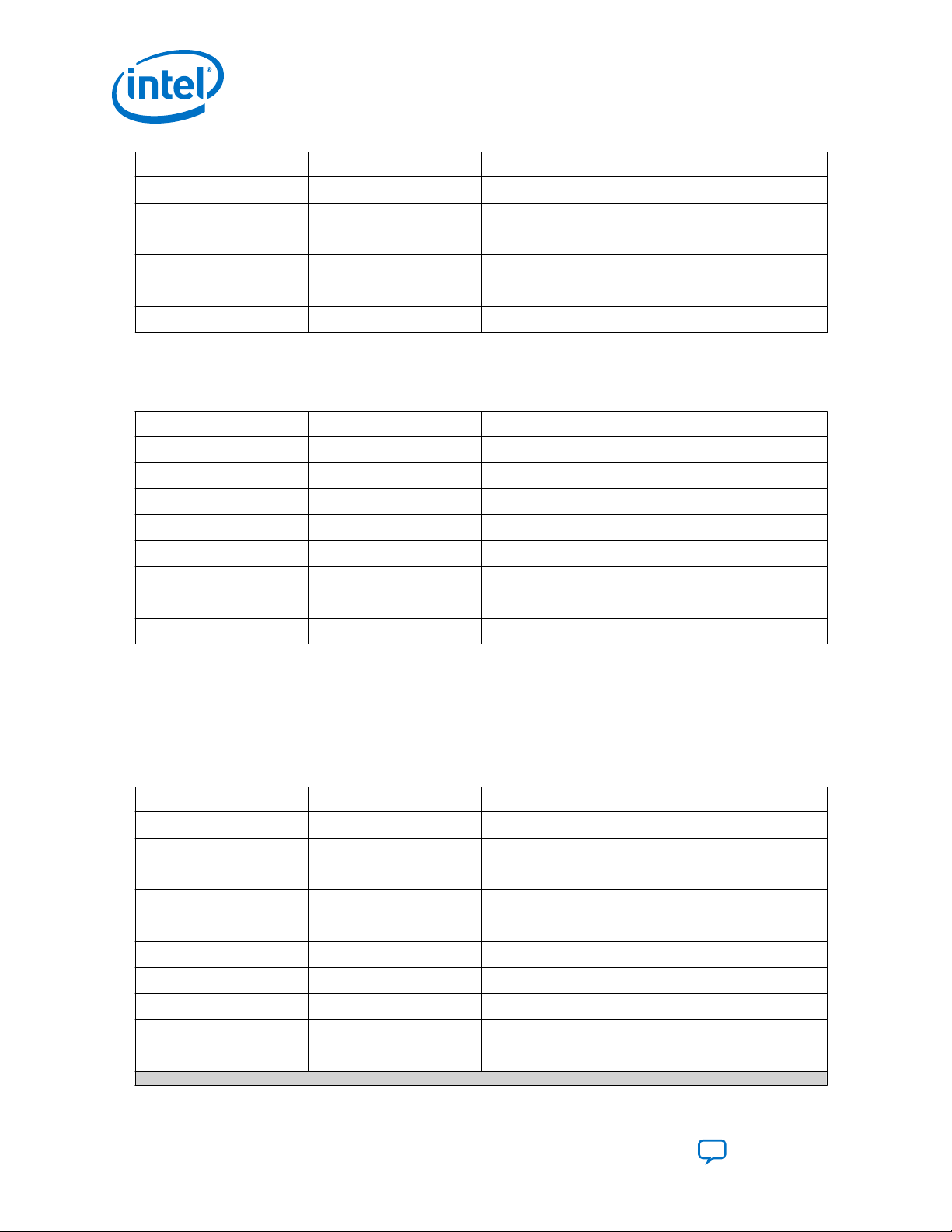

This development board comes in two different versions as shown in the table below.

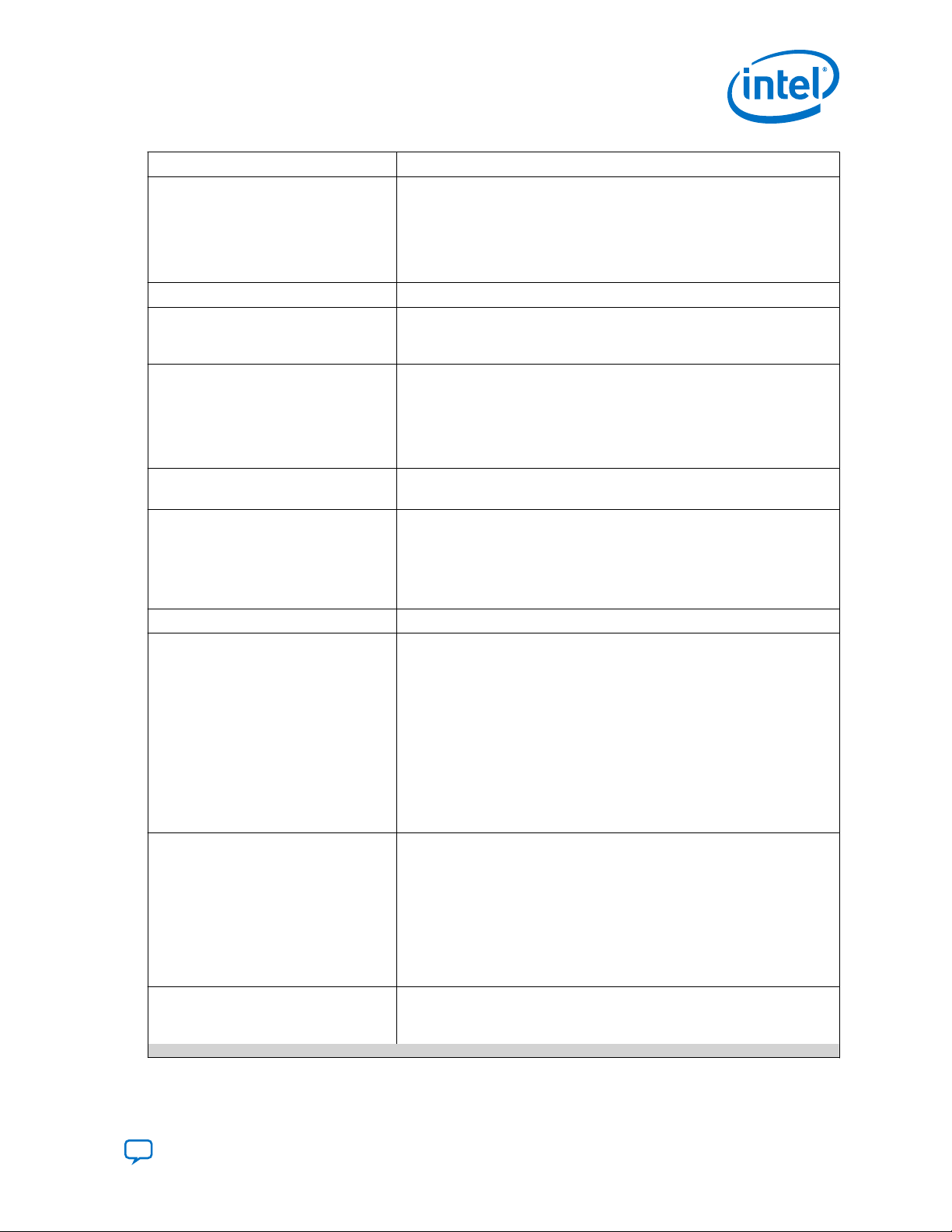

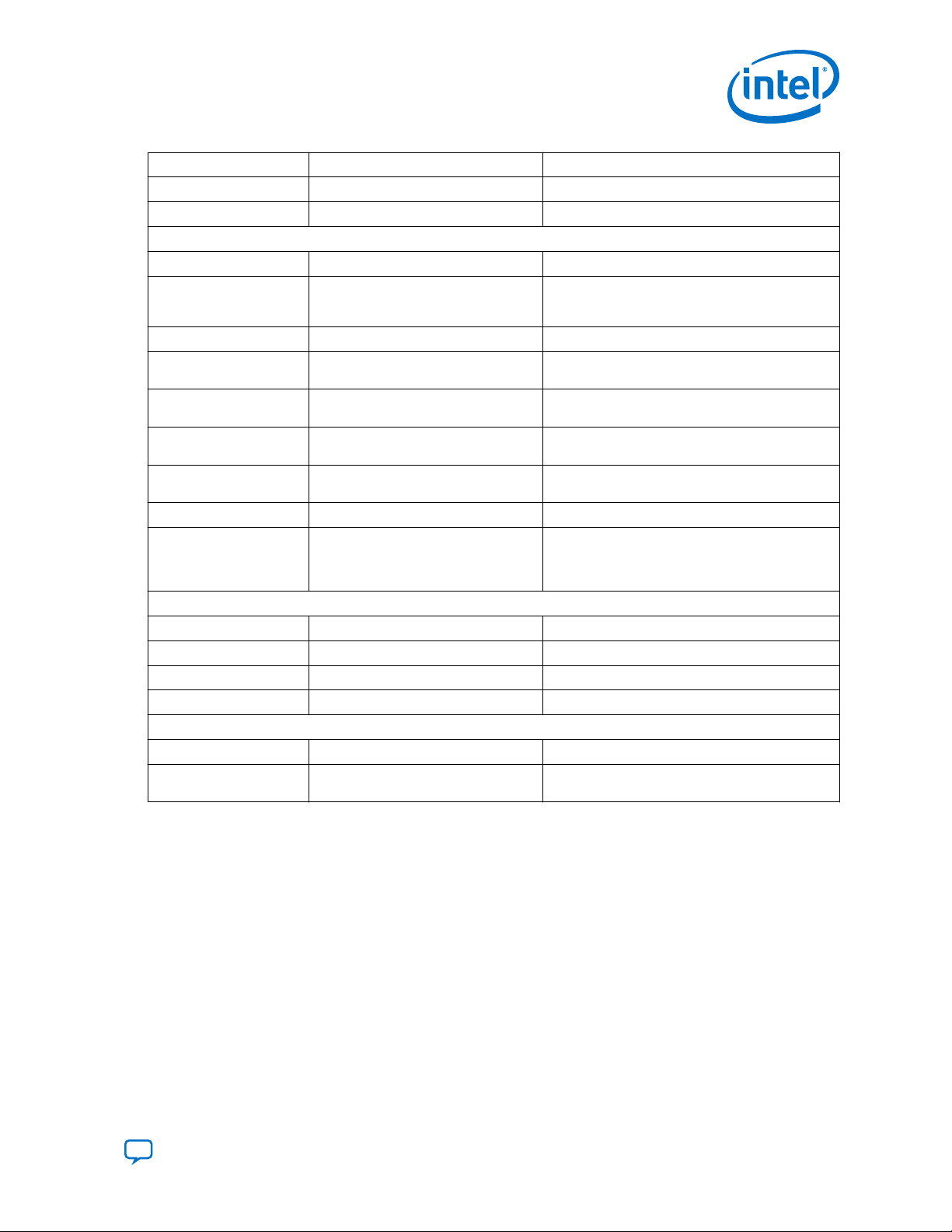

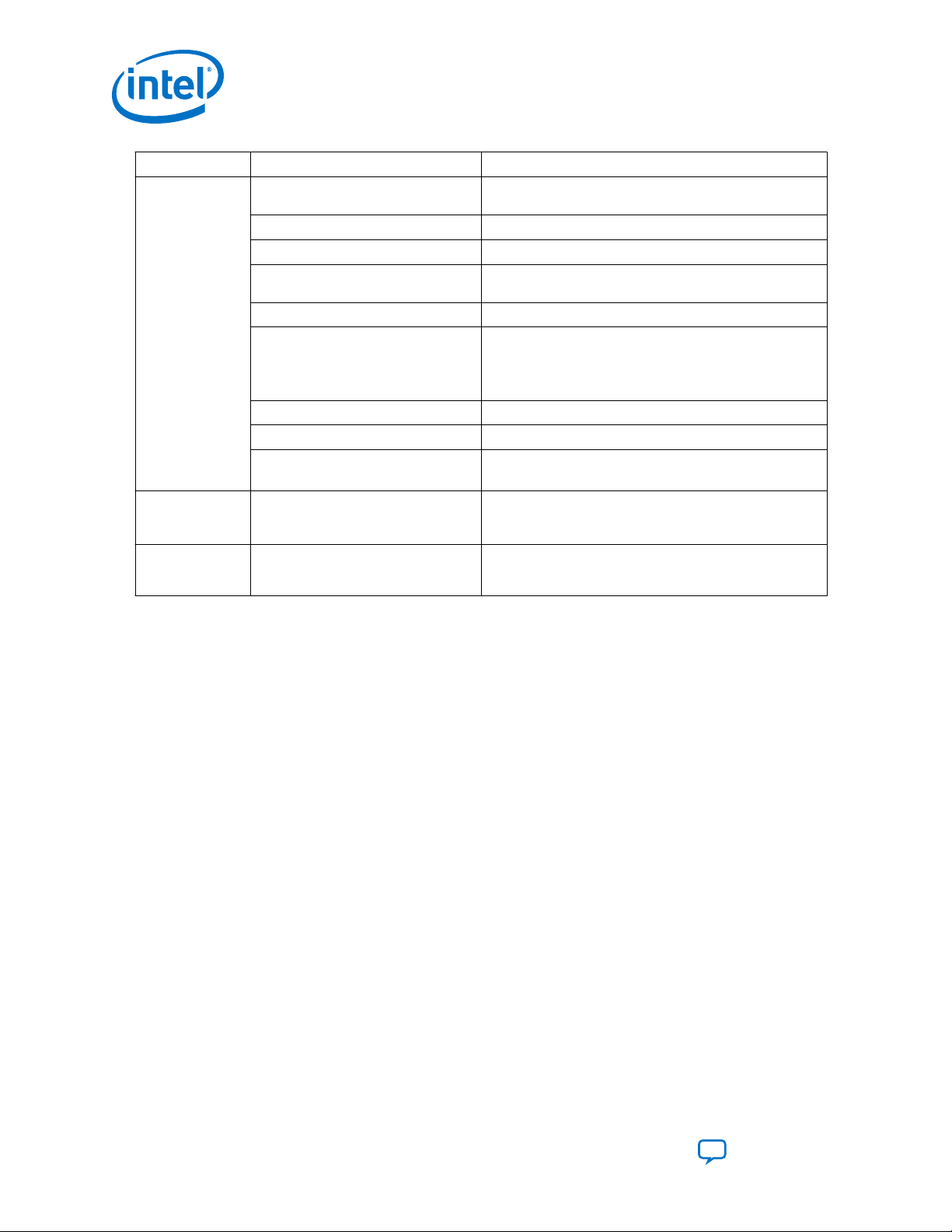

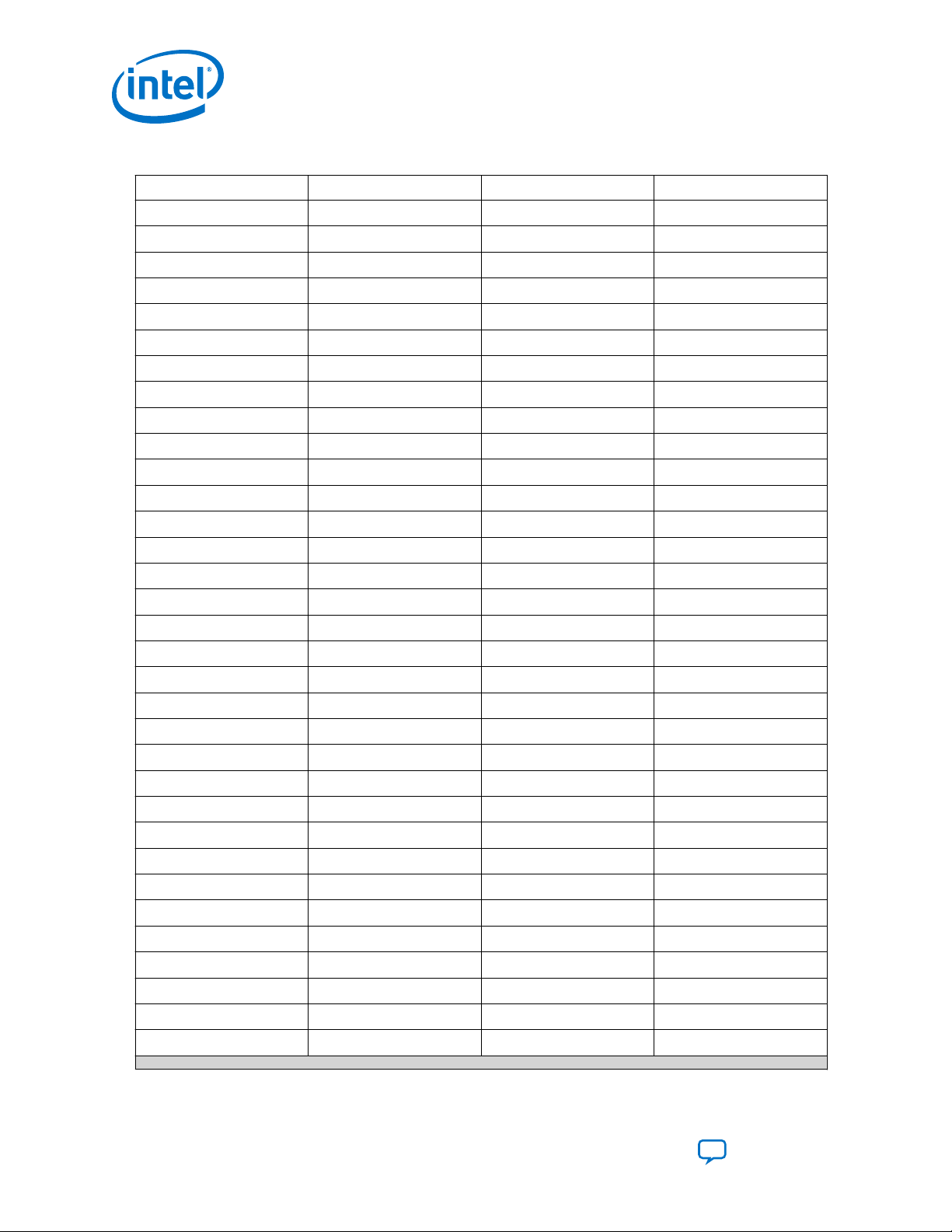

Table 1. Development Kit Version Information

Development Kit Version Ordering Code Device Part Number

Intel Stratix 10 SX SoC L-Tile DK-SOC-1SSX-L-A

DK-SOC-1SSX-L-D

Intel Stratix 10 SX SoC H-Tile DK-SOC-1SSX-H-A 1SX280HU2F50E1VGAS

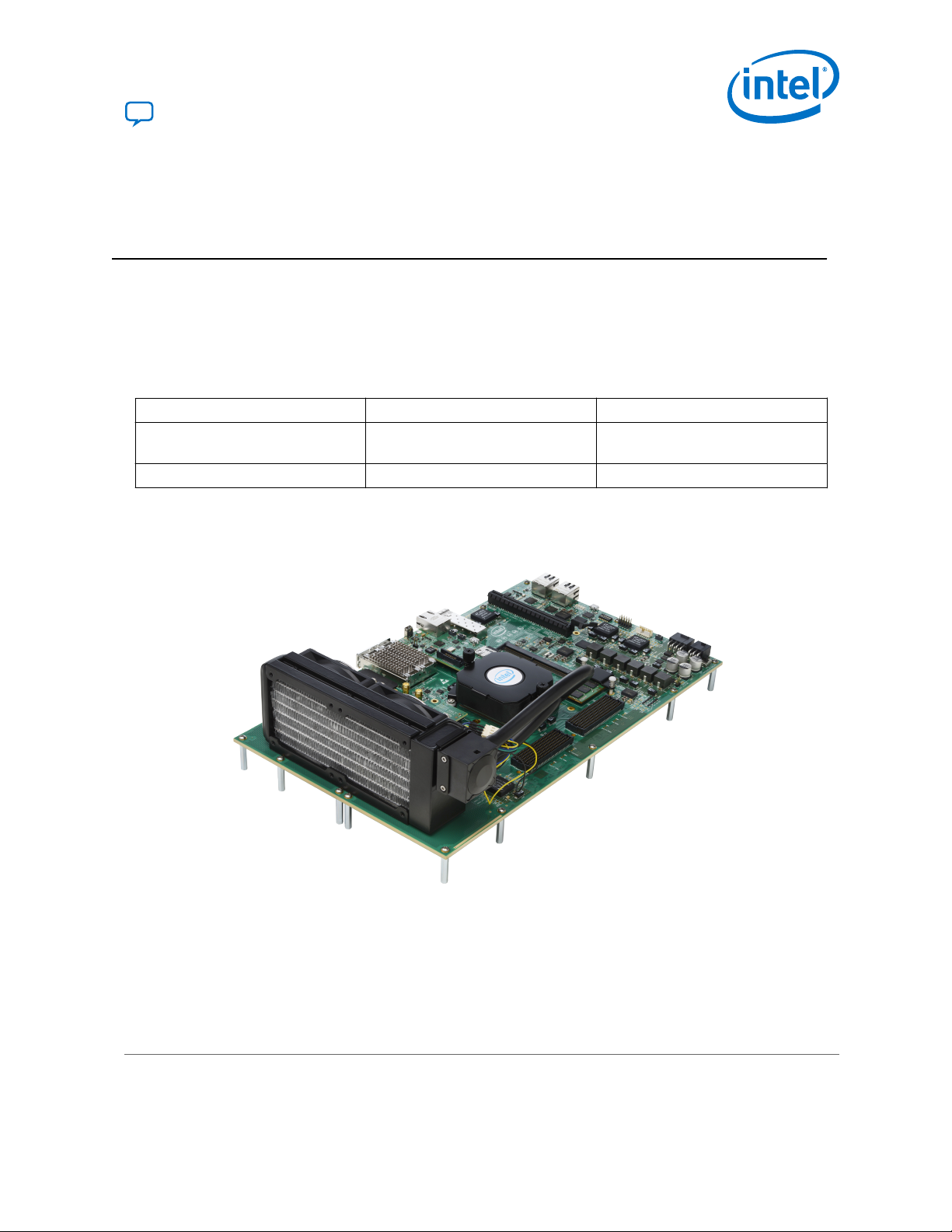

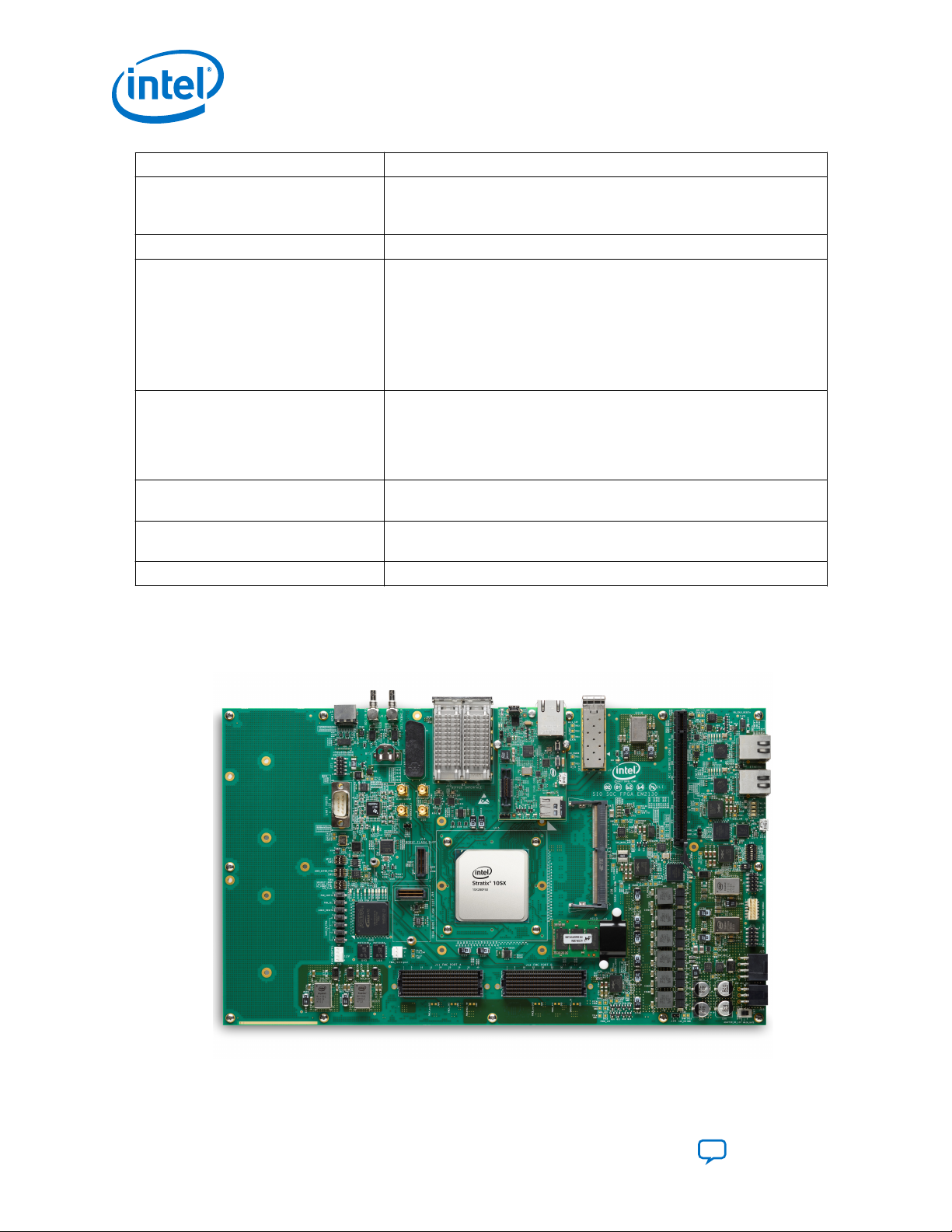

Figure 1. Development Kit Picture

1SX280LU2F50E1VG

1.1. General Development Kit Description

The Intel Stratix 10 SoC development board provides a hardware platform for

developing and prototyping low-power, high-performance and logic-intensive designs

using Intel Stratix 10 SoC. The board provides a wide range of peripherals and

memory interfaces to facilitate the development of Intel Stratix 10 SoC designs.

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios,

Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or

other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2015

Registered

Page 5

PCle® Gen3 x 16

Hardcore CxP

PCle® Gen3 x 16

Hardcore

100G / 50G

Hardcore

DDR3/DDR4

Hardcore

1C

24 Channels

DDR4 Dual

Rank

Clock

Block

DDR4

Signal Rank

HILO x72

FPGA Boot

Flash DC

(optional)

SODIMM x72

SDMI Bus

LVDS Bus

1D 1E 1F 1K 1L 1M 1N 4C 4D 4E 4F 4N

ZQSFP

x2

PCle

Gen3/Gen2/Gen1

x16 RC

FMCA

V57.4

PCle EP

Trace 16/32

(optional)

68-Bit Bus

24 Channels

16 Channels

FMCA

V57.4

PCle EP

FPGA_I/O

HBA, HBB

FPP

Flash

Intel

MAX 10

FPGA

Avalon-ST

Intel MAX 10

FPGA_I/O

DPIO

SDI_I/O

2F

SDM + JTAG + 05Cdk1 HPS_I/O

HPS

3A

FPGA

SGMII

MAC CORE

2M

2M

2L

3I

3J

3K

3L

2A

/

2B

3C

/

3B

3A

/

3L

FPGA

I/O

2C

/

2B

4E

MXP

SEEPROM/

RTC/TEMP

ClockI2C

PMBUS_VID

Ext I2C 1

Ext I2C 2

I2C 1

HPS Daughtercard

USB 2.0

PHY

USB3320

10/100/1000

RGMII PHY

KSZ9031RNX

UART

to USB

Boot Flash

DC

SDMI Bus

RGMII

USB2.0

UART1 TX/RX

Micro

SD Port

LT_12C

SFP+

HDMI

SDI/Ox1

x1

x4

x2

Intel® MAX 10

FPGA

JTAG Switch

and Power

Sequencer

Controller

Intel FPGA

Download

Cable II

2X

SGMII

PHY

88E1111

4 Channels

4L

4K

4M

Avalon®-ST

16/32 Bus

Intel® Enpirion® Power Solutions

1. Overview

UG-20081 | 2020.09.08

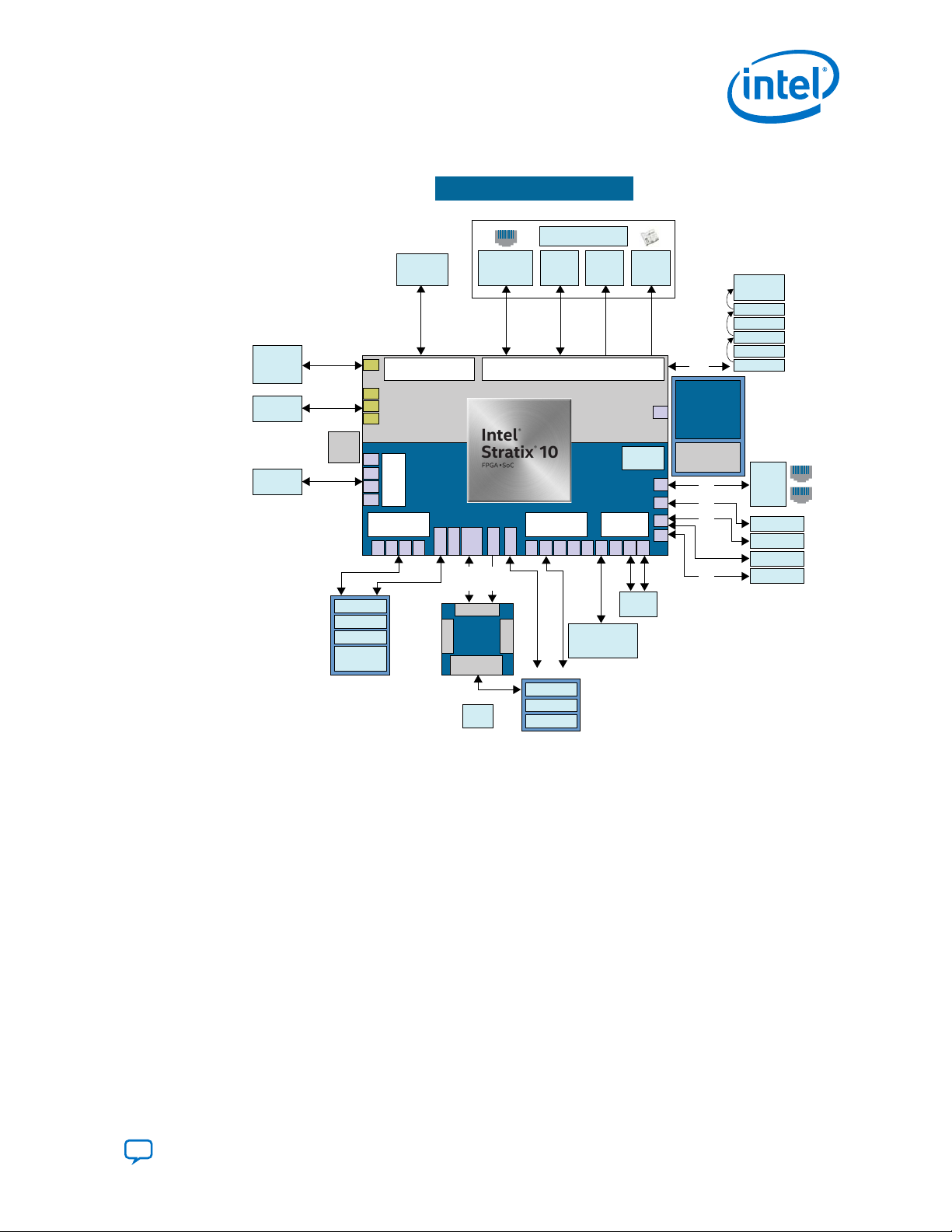

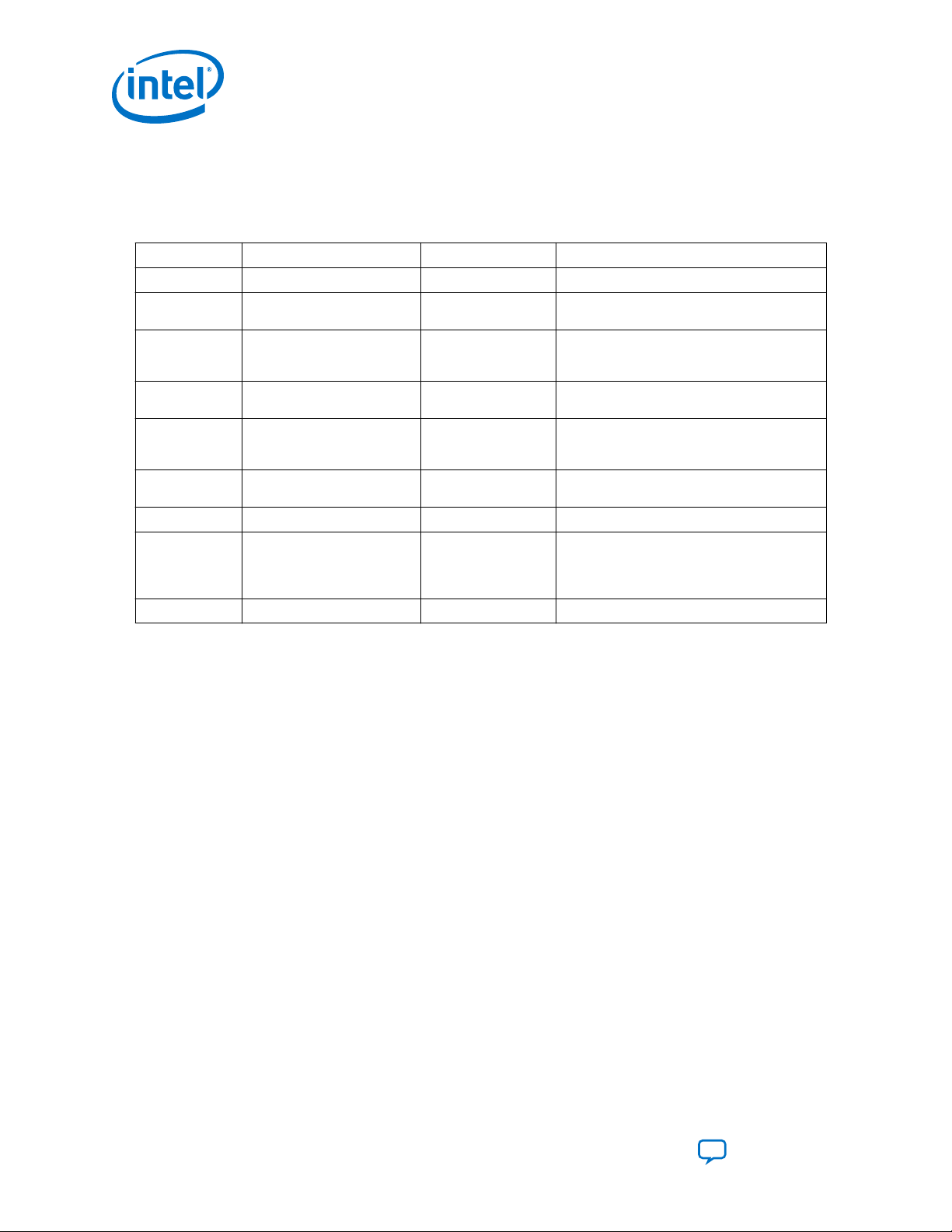

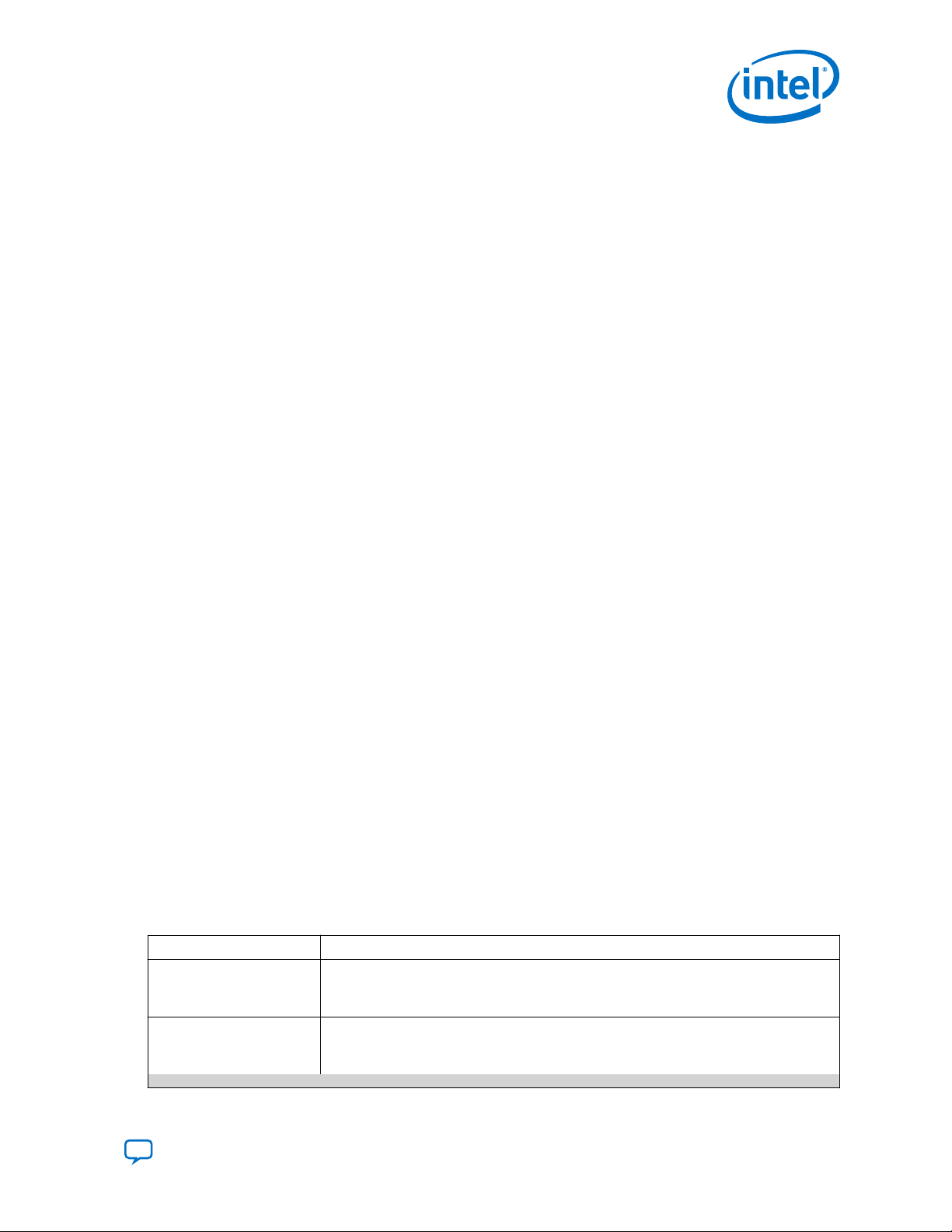

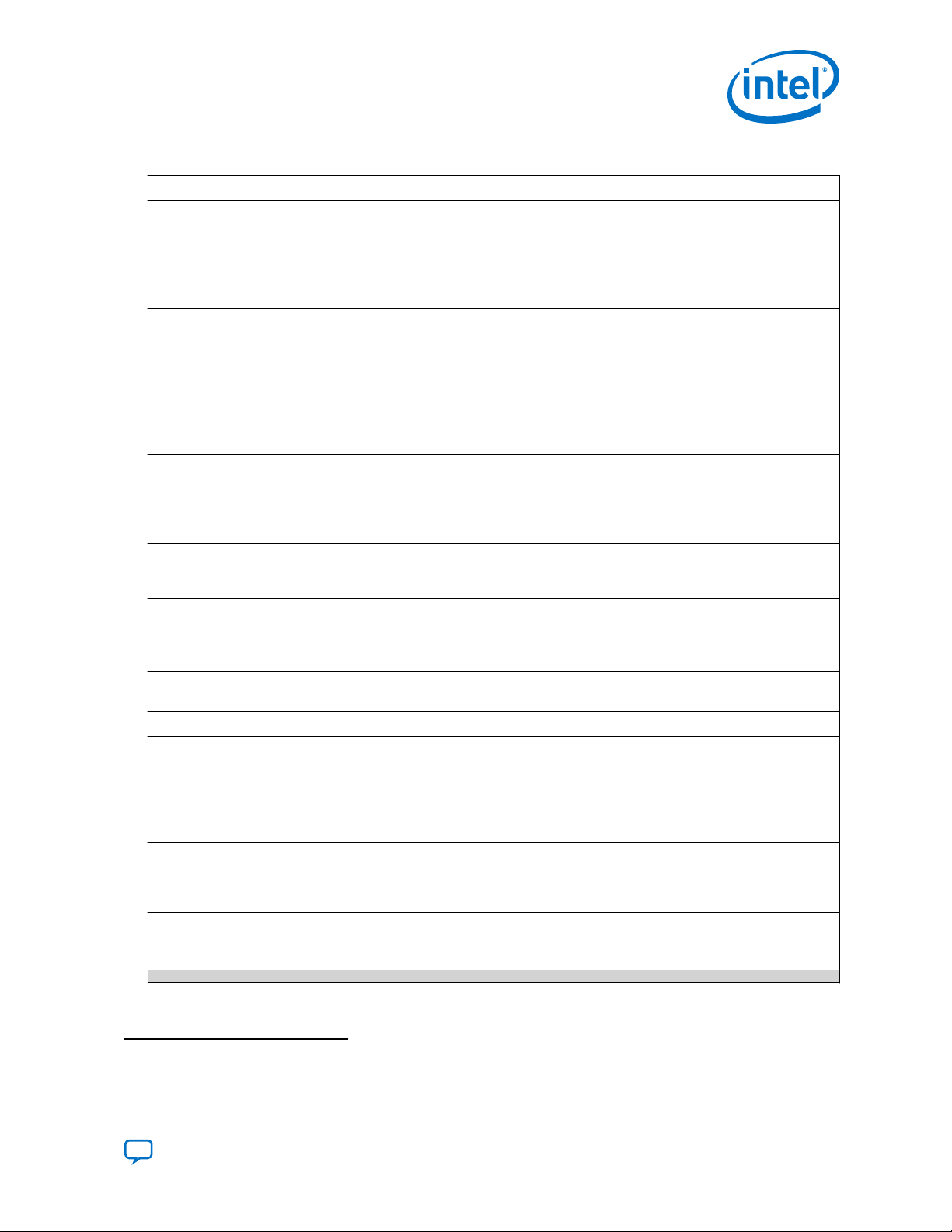

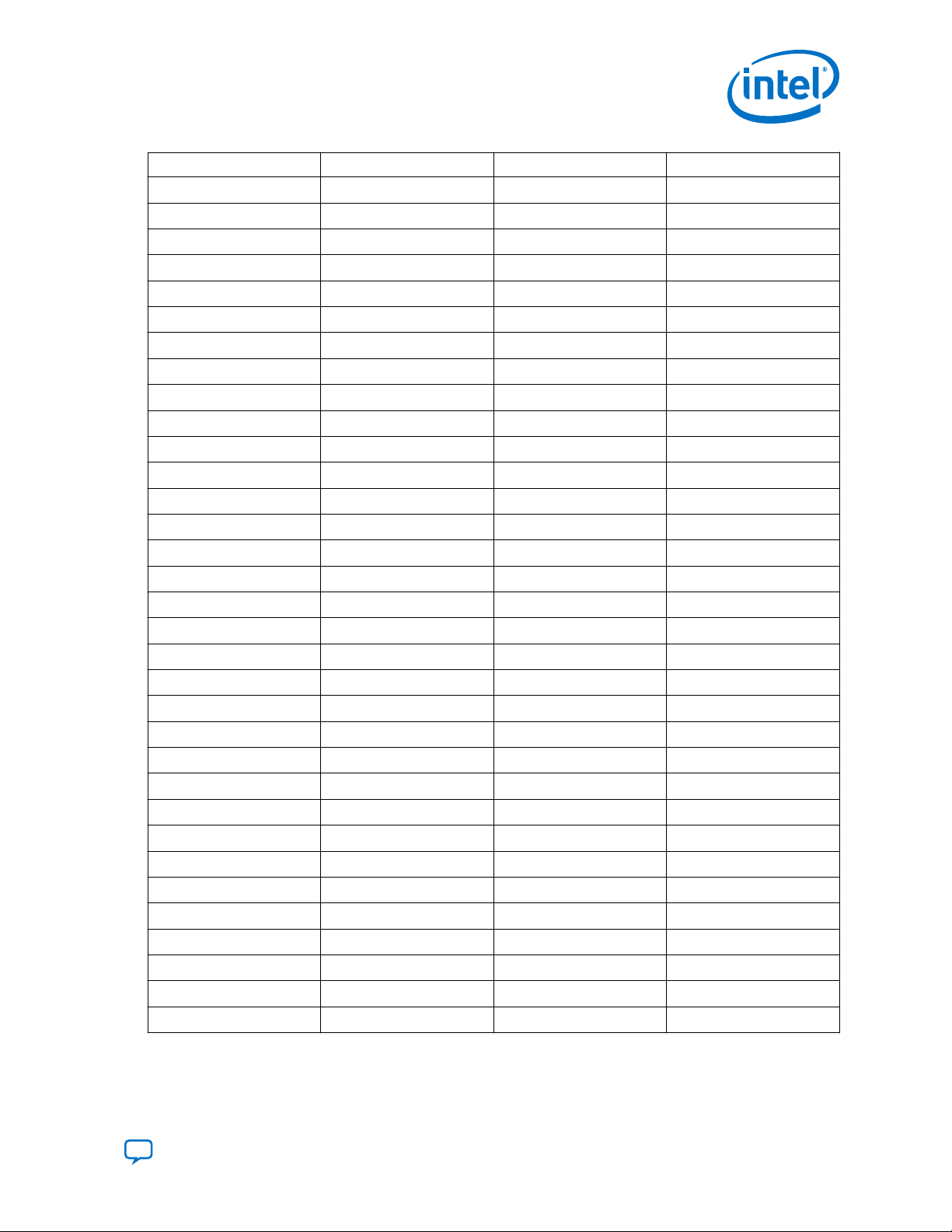

Figure 2. Intel Stratix 10 SoC Development Kit Block Diagram

Intel® Stratix® 10 SX SoC Development Kit User Guide

1.2. Recommended Operating Conditions

• Recommended ambient operating temperature range: 0 °C to 45 °C

1.3. Handling the Development Kit

Caution: Without proper anti-static handling, the board can be damaged. Therefore, use anti-

Caution: You must not operate this development kit in a vibration environment.

Send Feedback

• Maximum ICC load current: 190 A

• Maximum ICC load transient percentage: 30%

• FPGA maximum power supported by the supplied heatsink/fan: 300 W

When handling the board, it is important to observe static discharge precautions.

static handling precautions when touching the board.

5

Page 6

UG-20081 | 2020.09.08

Send Feedback

2. Getting Started

2.1. Installing Quartus Prime Software

The Intel Quartus® Prime design software is a multiplatform design environment that

easily adapts to your specific needs in all phases of FPGA, CPLD, and SoC designs. The

Intel Quartus Prime software delivers the highest performance and productivity for

Intel FPGAs, CPLDs, and SoCs.

Design software must enable dramatically increased design productivity in order to

take advantage of devices with multi-million logic elements with increased capabilities

that provide designers with an ideal platform to meet next-generation design

opportunities.

The new Intel Quartus Prime Design Suite design software includes everything needed

to design for Intel FPGAs, SoCs and CPLDs from design entry and synthesis to

optimization, verification and simulation. The Intel Quartus Prime Design Suite

software includes an additional Spectra-Q® engine that is optimized for Intel Stratix

10 and future devices. The Spectra-Q engine enables new levels of design productivity

for next generation programmable devices with a set of faster and more scalable

algorithms, a hierarchical database infrastructure and a unified compiler technology.

Intel Quartus Prime

The Intel Quartus Prime Design Suite software is available in three editions based on

specific design requirements: Pro, Standard, and Lite Edition.

The Intel Quartus Prime Pro Edition is optimized to support the advanced features in

Intel's next generation FPGAs and SoCs and requires a paid license.

Intel Quartus Prime Standard Edition includes the most extensive support for Altera's

latest device families and requires paid license.

Intel Quartus Prime Lite Edition provides an ideal entry point to Intel's high-volume

device families and is available as a free download with no license file required.

Included in the Intel Quartus Prime Pro Edition are the Intel Quartus Prime software,

Nios® II EDS and the MegaCore IP Library.

To install Intel's development tools, download the Intel Quartus Prime Pro Edition

software from the Quartus Prime Pro Edition page in the Download Center of Intel's

website.

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios,

Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or

other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2015

Registered

Page 7

2. Getting Started

UG-20081 | 2020.09.08

2.2. Installing the Intel FPGA Download Cable

The Intel Stratix 10 SoC Development Kit includes embedded Intel FPGA Download

Cable circuits for FPGA and Intel MAX® 10 programming. However, for the host

computer and board to communicate, you must install the Intel FPGA Download Cable

driver on the host computer.

Installation instructions for the Intel FPGA Download Cable driver for your operating

system are available on the Intel website.

On the Intel website, navigate to the Cable and Adapter Drivers Information link to

locate the table entry for your configuration and click the link to access the

instructions.

2.3. Installing the Intel SoC Embedded Development Suite (EDS)

The Intel SoC EDS is a comprehensive software tool suite for embedded software

development on Intel SoC devices. It contains development tools, utility programs,

run-time software, and application examples to expedite firmware and application

software of SoC embedded systems.

As a part of the Intel SoC EDS, the Arm* Development Studio (DS) Intel SoC FPGA

Edition Toolkit provides a comprehensive set of embedded development tools for

Intel's SoC FPGAs.

For more information and steps to install the SoC EDS Tool Suite refer to the links

below.

Related Information

• Arm Development Studio (DS) Intel SoC FPGA Edition

• Intel SoC FPGA Embedded Development Suite User Guide

2.4. Installing the Intel Stratix 10 SX SoC Development Kit Package

The Intel Stratix 10 SX SoC Development Kit offers a quick and simple approach for

developing custom Arm processor-based SoC designs. The Intel Stratix 10 SX SoCs

offer full software compatibility with previous generation SoCs, a broad ecosystem of

Arm software and tools, and the enhanced FPGA and digital signal processing (DSP)

hardware design flow.

Intel Stratix 10 SX SoC Development Kit Package Installer is a single installation file

contains that Intel Stratix 10 SX SoC Development Kit board design files, documents,

and examples including the Board Test System (BTS) installation files.

Download and unzip Intel Stratix 10 SX SoC Development Kit Package Installer first.

Install the Intel Stratix 10 SX SoC Board Test System.

Note:

To view the the layout *.brd files in the board package, you can download the

Cadence® Allegro®/OrCAD® Free Viewer from Cadence's website.

For additional information, refer to the Intel Stratix 10 SX SoC Development Kit

webpage on Intel's website using the link provided at the end of this section.

Send Feedback

Intel® Stratix® 10 SX SoC Development Kit User Guide

7

Page 8

Related Information

• Intel Stratix 10 SX SoC Development Kit

• Cadence Allegro

2. Getting Started

UG-20081 | 2020.09.08

Intel® Stratix® 10 SX SoC Development Kit User Guide

8

Send Feedback

Page 9

UG-20081 | 2020.09.08

Send Feedback

3. Development Kit Setup

The instructions in this chapter explain how to setup the Intel Stratix 10 SoC

Development Board.

3.1. Inspect the Development Kit

To inspect the board, perform the following steps:

1. Place the board on an anti-static surface and inspect it to ensure that it has not

been damaged during shipment.

2. Verify that all components on the board appear in place and intact.

Caution: Without proper anti-static handling, you could damage the board.

Table 2. Stratix 10 SoC Development Kit Contents

Item Quantity

Intel Stratix 10 SoC Development Board 1

USB Cable 2

USB Cable Micro 1

Ethernet Cable 1

HPS IO48 OOBE Daughter Card 1

HPS IO48 NAND Daughter Card 1

SODIMM Memory Card 1

QSPI Flash 1

SD Micro Flash 1

Related Information

• Thermal Management for FPGAs

• Intel Intel Enpirion® Digital Power Configurator Graphical User Interface (GUI)

3.2. Default Setup of the Development Kit

This development kit ships with its board switches preconfigured to support the design

examples in the kit.

1. Power up the development board by using the included power supply.

2. When configuration is complete, the configuration done green LED (D22)

illuminates, signaling that the Intel Stratix 10 device is configured successfully.

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios,

Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or

other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2015

Registered

Page 10

3. Development Kit Setup

UG-20081 | 2020.09.08

Caution: Use only the provided power supply. Power regulation circuits on the board can be

damaged by power supplies with greater voltage and a lower-rated power supply may

not be able to provide enough power for the board.

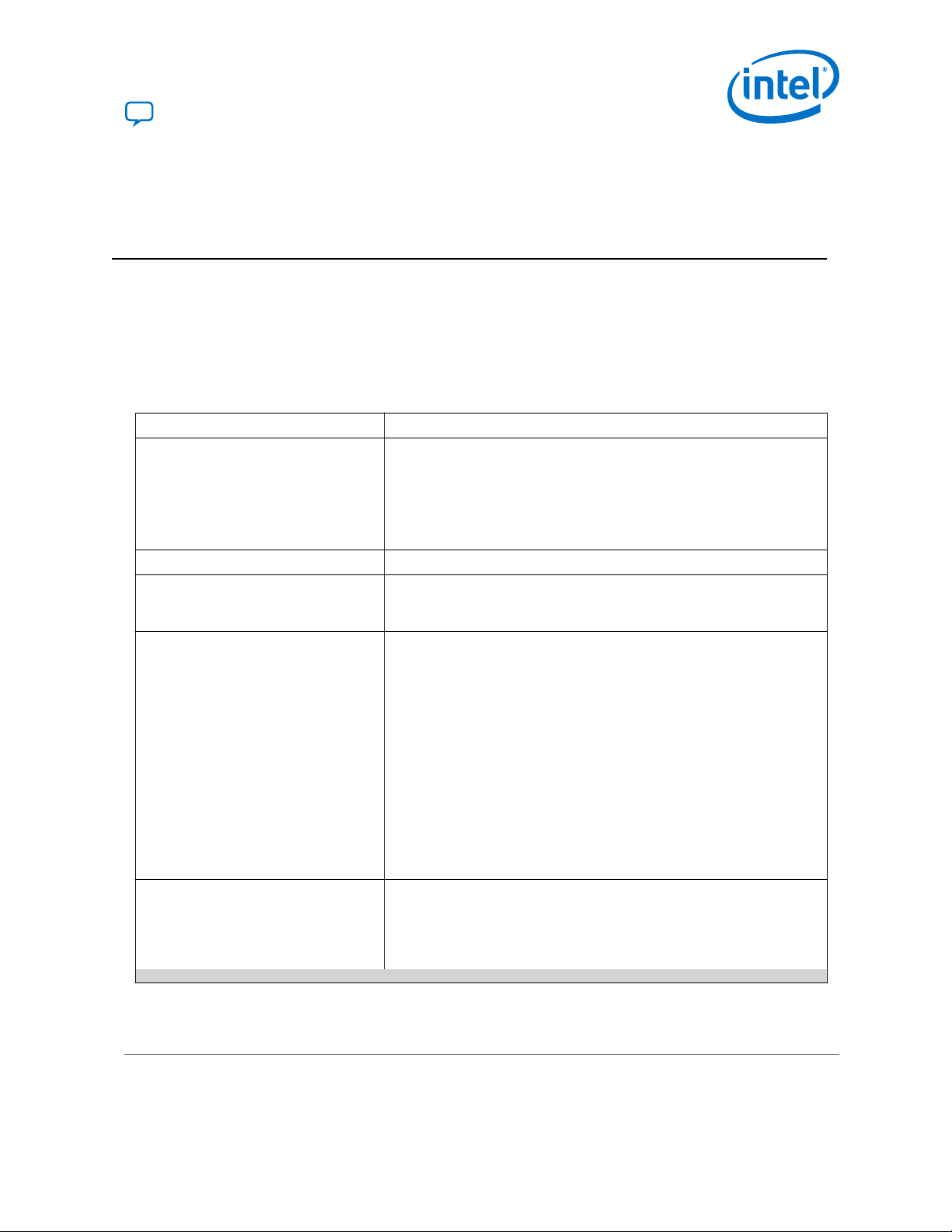

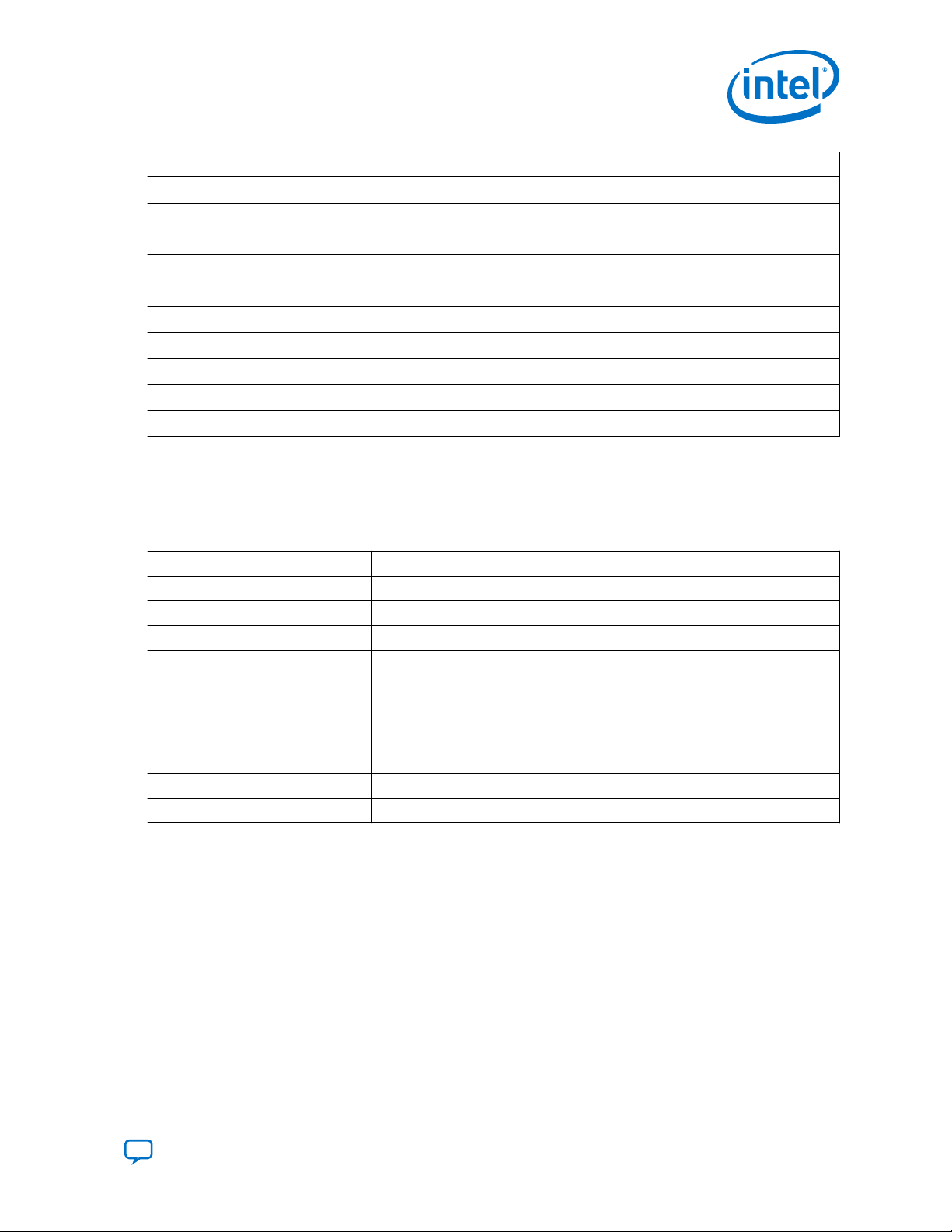

Table 3. Default Setup

Checkpoint Name Reference Description

1 Power Switch SW7 Power is turn off at left position

2 Power Adapter connector J25, J55 Both connectors can be used to connect the

3 Intel Intel Enpirion

4 JTAG Dongle connector J1 You can install Intel JTAG dongle to access

5 JTAG Switch SW1 Default Setup from bit 1 to bit 8 is “off, off,

6 USB JTAG Port J57 You need connect Micro USB cable to access

7 12V Fan Connector J16 You need use it to connect thermal Fan

8 Boot Switch SW4 Default set up from bit 1 to Bit 4 is “on, off,

9 MSEL Switch SW2 Default Setup is “on on on on”: JTAG mode

®

J29 You can install Intel Enpirion dongle to

power adapter

monitor the board power rails. Switch 8 is at

off position.

FPGA

on, on, on, on, on, on”: Intel Stratix 10 SoC

and Intel MAX 10 are on the JTAG chain

Intel Stratix 10 SoC

on, off”

FPGA/HPS I2C is enabled. Daughter card

power is on

3.3. Intel MAX 10 System Controller Updates

The Intel MAX 10 System Controller manages several features on the Intel Stratix 10

SX SoC Development kit, including clocks, I2C, and some configuration signals. In

certain situations, it may be necessary to ensure the Intel MAX 10 System Controller

internal flash contains the latest available design. This may include the Intel Stratix 10

device failing to configure from OSC_CLK_1, or when other unexpected issues arise.

The latest System Controller design is included in the Intel Stratix 10 SX Soc

Development Kit Installer Package, in the “system_max10” folder inside the

“examples” folder.

To update the internal flash, follow the steps outlined in the procedure below:

1. Power off the Intel Stratix 10 SX SoC Development Kit.

2. Ensure SW1 and SW2 are set to the default settings so the System Intel MAX 10

is on the JTAG chain and the Intel Stratix 10 device does not automatically

configure itself.

3. Connect a micro USB cable to J57 for JTAG access and power on the board.

4. Open the Intel Quartus Prime Programmer and scan the device chain.

5. Right click on the Intel MAX 10 and select “Change File”. Navigate to the

“system_max10” folder and select the .pof file, for example,

“max10_system_rev13.pof”.

Intel® Stratix® 10 SX SoC Development Kit User Guide

10

Send Feedback

Page 11

3. Development Kit Setup

UG-20081 | 2020.09.08

6.

Check the Program/Verify box in the row with the .pof and the Intel MAX 10

Device. The Program/Verify boxes in the immediately following rows, CFM0 and

UFM, will auto-check as well. Refer to the following screenshot:

7. Click Start and wait for the programming cycle to finish.

8. Power off the board and reset SW1 and SW2 to prior settings, if any.

Send Feedback

Intel® Stratix® 10 SX SoC Development Kit User Guide

11

Page 12

UG-20081 | 2020.09.08

Send Feedback

4. Development Kit Components

This chapter introduces the major components on the Intel Stratix 10 Development

Board. The board overview figure illustrates the component locations and the board

components table provides a brief description of all component features of the board.

4.1. Development Kit Feature Summary

Table 4. Intel Stratix 10 SoC Development Kit Feature Summary

Feature Description

Programmable Logic • Intel Stratix 10 SoC FPGA

• 10M04SCU169C8G Intel MAX 10 CPLD as the Intel FPGA Download Cable

and JTAG switch device

• 10M16SAU169C8G Intel MAX 10 CPLD as the Power manager and

sequencer device

• 10M50DAF484I7G Intel MAX 10 CPLD as the IO level translator, IO MUX

and Passive AVST-16 FPGA controller device

HPS memory 1066 MHz 4 GB 72-bit HILO memory card

HPS Boot Flash (Flash Card) • Boot Codes for QSPI, SD Micro

• QSPI Flash: 256 MB (MT25QU02GCBB8E12-0SIT)

• SD Micro Flash Card: 16 GB (Kingston)

HPS IO48 OOBE Daughter Card • One HPS IO48 60-pin Samtec Connector

• One RGMII 10/100/1000 Mbps Ethernet port: Standard RJ-45

• One UART port: Standard USB Mini-B Receptacle

• One Micro SD Card Connector: Standard Micro SD Card Socket

• One USB 2.0 port: Standard USB Micro-AB Receptacle

• One Mictor 38-pin connector (JTAG only without Trace signals)

— Two JTAG targets selected by the resistors MUX: FPGA JTAG chain

(optional) and HPS JTAG Port (default)

• I2C: HPS I2C port

• GPIO

— 2 Push buttons

— 3 LEDs

— 1 Ethernet Interrupt from Ethernet PHY

— 1 USB over-current indicator

• HPS Clock: 25 MHz oscillator

HPS IO48 NAND Flash Daughter Card • One HPS IO48 60-pin Samtec connector

• One RGMII 10/100/1000 Mbps Ethernet port: Standard RJ-45

• One UART port: Standard USB Mini-B Receptacle

• NAND Flash (x16): 8 Gb

• eMMC (x8): 8 GB 5.0 compliant eMMC

continued...

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios,

Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or

other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2015

Registered

Page 13

4. Development Kit Components

UG-20081 | 2020.09.08

Feature Description

• I2C: HPS I2C port

• GPIO

— 2 Push Buttons

— 3 LEDs

— 1 Ethernet Interrupt from Ethernet PHY

• HPS Clock: 25 MHz oscillator

FPGA memory 1200 MHz 16 GB DDR4 SO-DIMM MTA18ASF2G72HZ – 2G6

FPGA File Flash (Flash Card) • NAND Flash (x8): 1 GB

• QSPI Flash: 256 MB

• SD Micro Flash Card: 16 GB (Kingston)

Two V57.4 High Pin Count FMC+ Slots • 28 Gbps signals: Insertion loss less than 5 dB, return loss less than 10 dB

• FMC+ PCIe* Gen3 x16 cable (not included)

• FMC to PCIe Gen3 x8 cable (not included)

• 16/32 bit trace

Note: FMC to PCIe cables are sold separately by Samtec. Please contact

them directly regarding P/N HDR-201768-01-PCIEC

FPGA PCIe Gen 1/2/3 x16 RC Slot • 75 W Power

• Meets PCIe specifications

FPGA Communication Ports • Two 28 Gbps ZQSFP+ Ports: 100/50 Gbps IP, Insertion loss less than 5

FPGA Debug Ports Intel FPGA Download Cable Direct Port & JTAG

FPGA Reference Clocks • Clock Cleaner

I2C Devices • 4 KB SEEPROM

Intel MAX 10 Controller I/O CPLD Features • System Reset Controller

dB, return loass less than 10 dB

• One 10 Gbps SFP+ Port: 10 Gbps Ethernet IP

• SMA Test Port: Up to four 28 Gbps channels, inseertion loss less than 5

dB, return loss less than 10 dB, one external reference clock

• One DB-9 RS-232 Port (MAX3221)

— 122.88 MHz (Network)

— 644.5312 MHz (Network)

— 297 MHz (SDI)

— 245 MHz (SDI)

• Clock Generators

— LMH1983 (27 MHz, 148.5 MHz)

— Si5388 (133.33 MHz)

— PCIe (100 MHz)

— Si5338 (148 MHz, 100 MHz, 27 MHz, 100 MHz)

— Si5341 (155.52 MHz, 644.53125 MHz, 135 MHz, 156.25 MHz, 625

MHz, 100 MHz, 125 MHz, 125 MHz)

• Real Time Clock

• Silicon Labs™ Clock Generators

• FMC+ Slots

• PCIe Slots

• SFP+

• ZQSFP

• Clock Cleaner

• Power Supplies

• FPGA PS AVST Configuration Controller

• I2C Master Controller

continued...

Send Feedback

Intel® Stratix® 10 SX SoC Development Kit User Guide

13

Page 14

4. Development Kit Components

Feature Description

• UART Level Shifter

• FPGA I/O MUX

• SDI/HDMI/QSFP/SFP+ I/O level shift

Intel MAX 10 Power CPLD Sequencer FPGA, PCIe, FMC+ slots power sequencer, Reset.

Intel MAX 10 CPLD Features • Intel FPGA Download Cable II

• JTAG Switch

— Input JTAG Sources (Intel FPGA Download Cable II, 10-pin Program

Header, FMCA+, FMCB+, Mictor JTAG)

— Output JTAG Sources (Intel MAX 10 A JTAG, MAX10B JTAG, Intel

Stratix 10 JTAG, FMCA+, FMCB+, PCIe)

— JTAG Program

— User I/O

User I/O • 4 Push Buttons

• 4-bit Dipswitch

• 4 User LEDs

• 2-pin I/O Header

• System Intel MAX 10 LEDs and 4-bit switch

Power • Volgen KTPS200-12160, 12V, 24A

• ATX-Power

Mechanical • 8.5" x 14.5" Rectangular Form Factor

• Liquid cool thermal heat sink (300W @ 35C)

System Monitor Power, Voltage, Current

UG-20081 | 2020.09.08

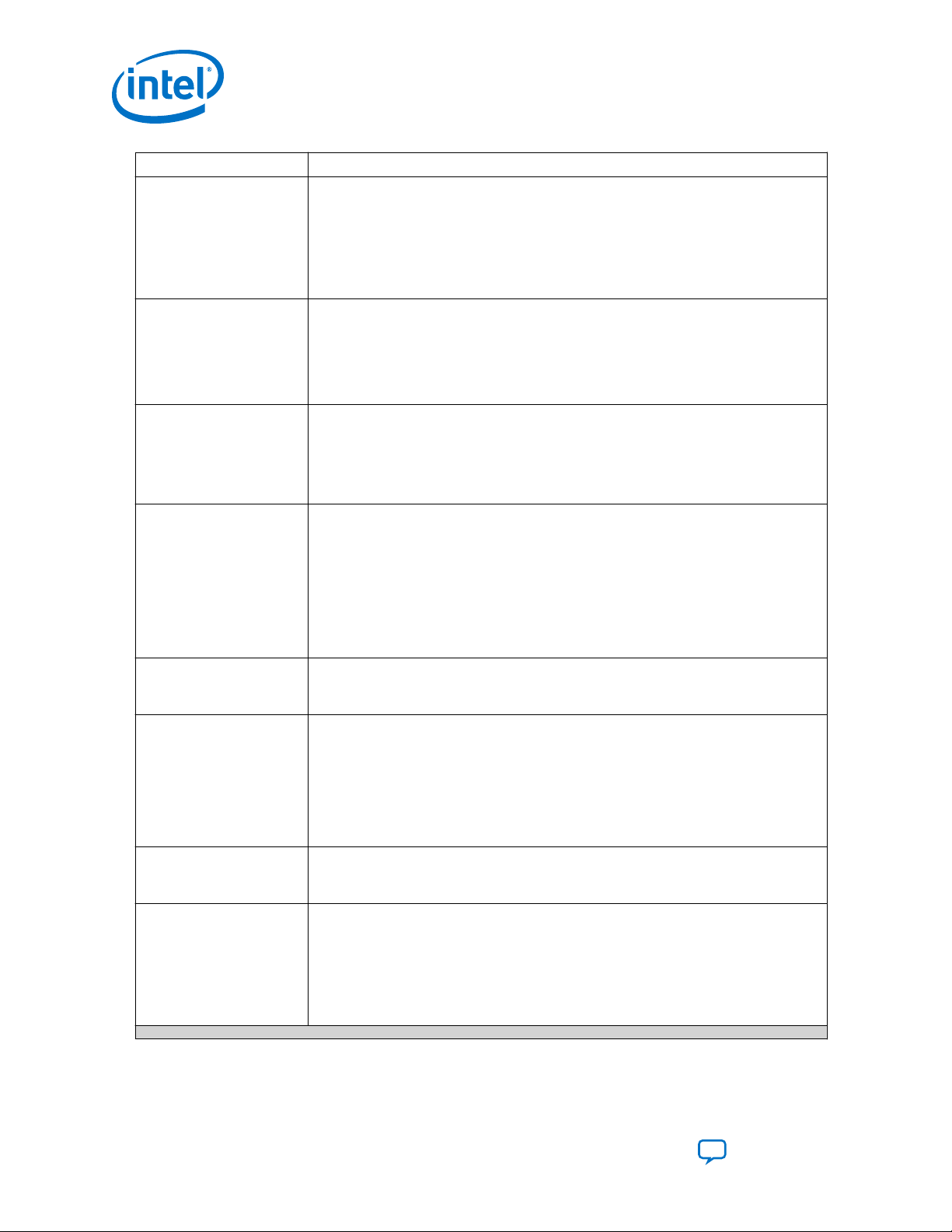

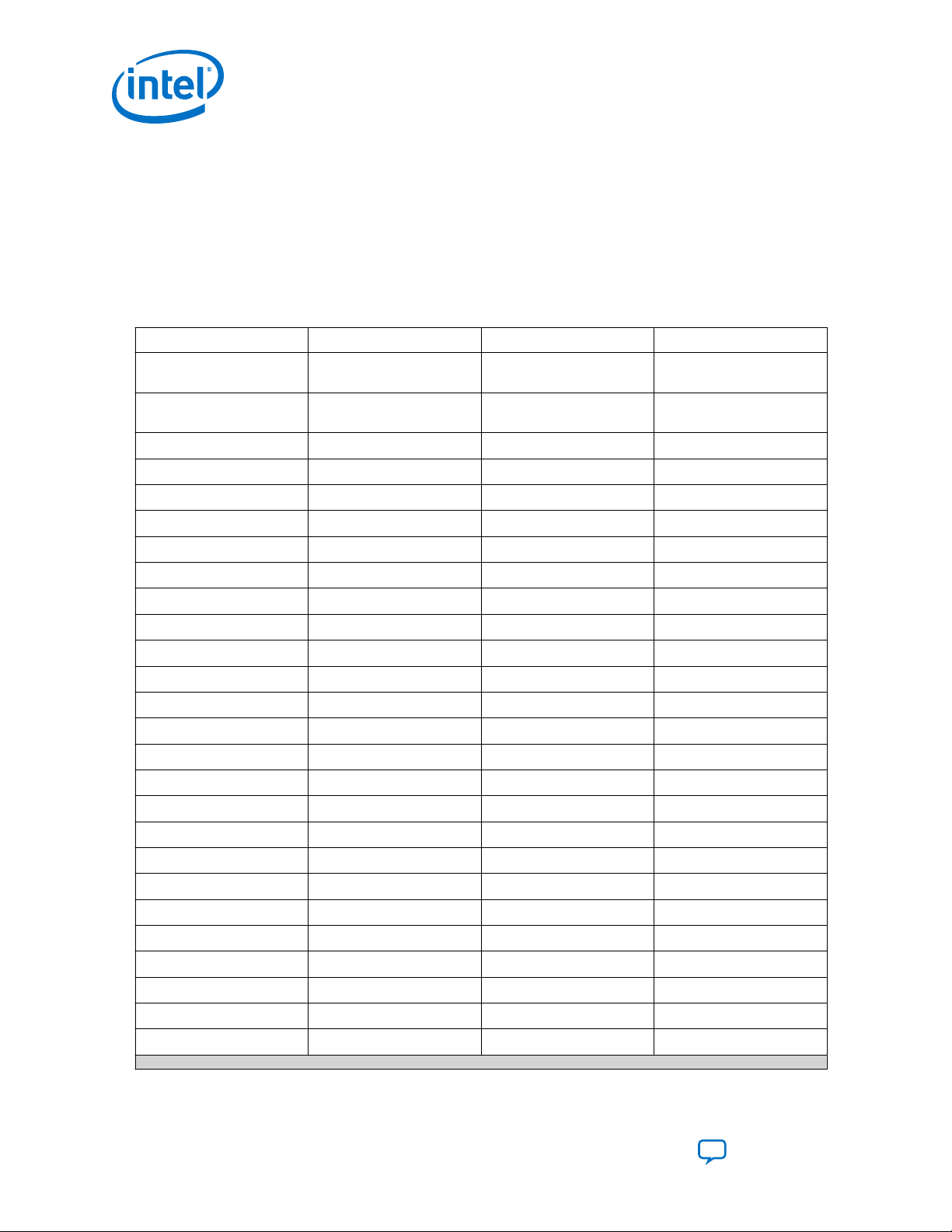

4.2. Board Components

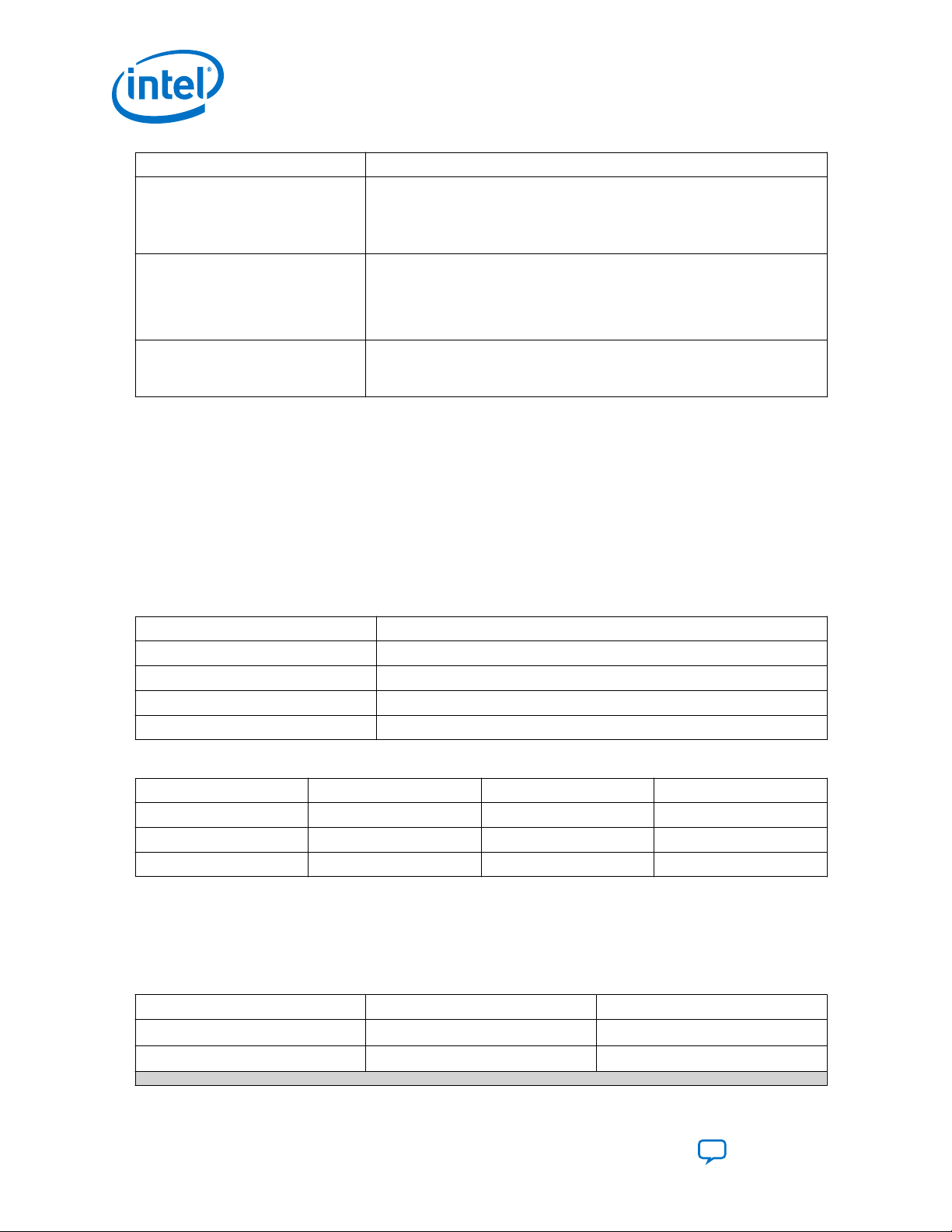

Figure 3. Board Picture (Top View)

Intel® Stratix® 10 SX SoC Development Kit User Guide

14

Send Feedback

Page 15

4. Development Kit Components

UG-20081 | 2020.09.08

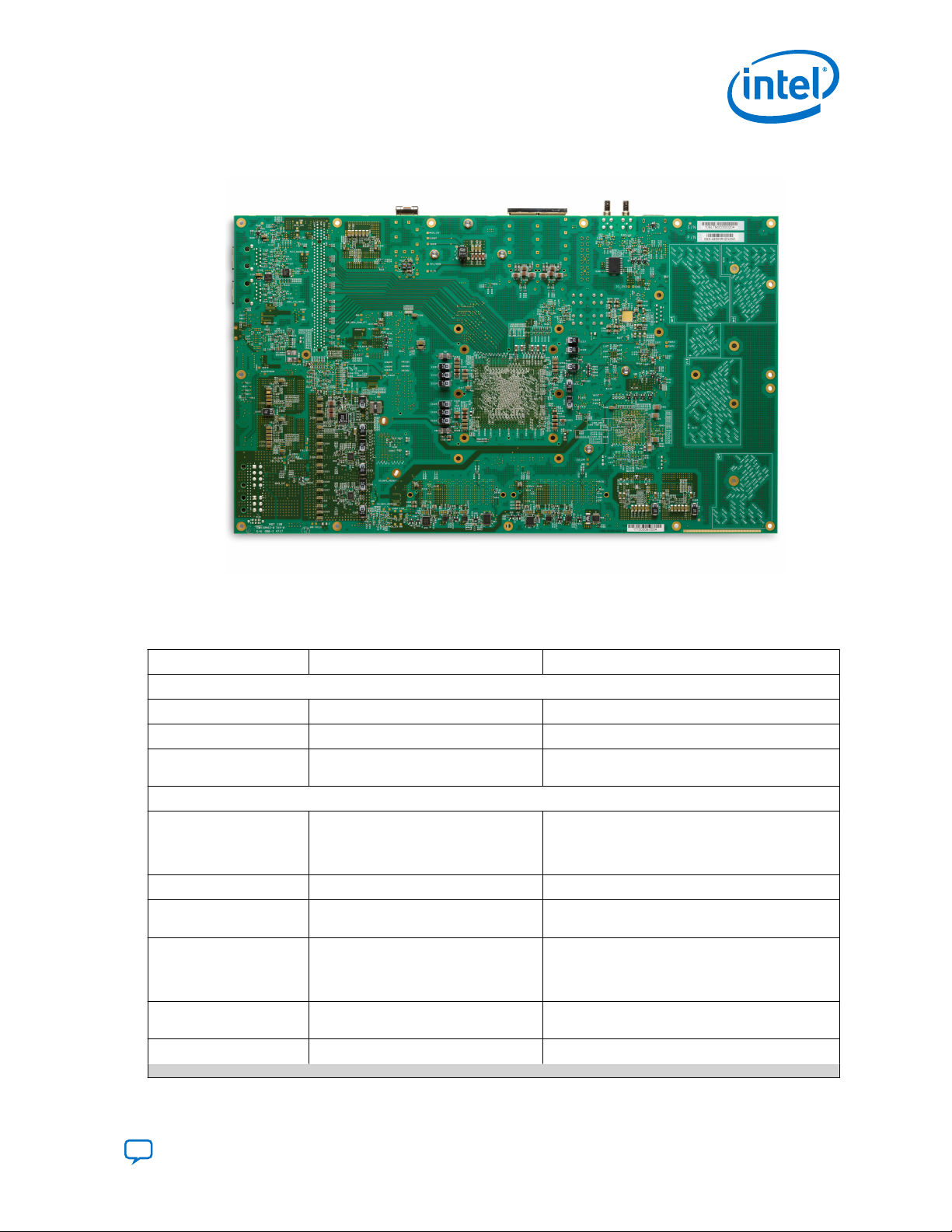

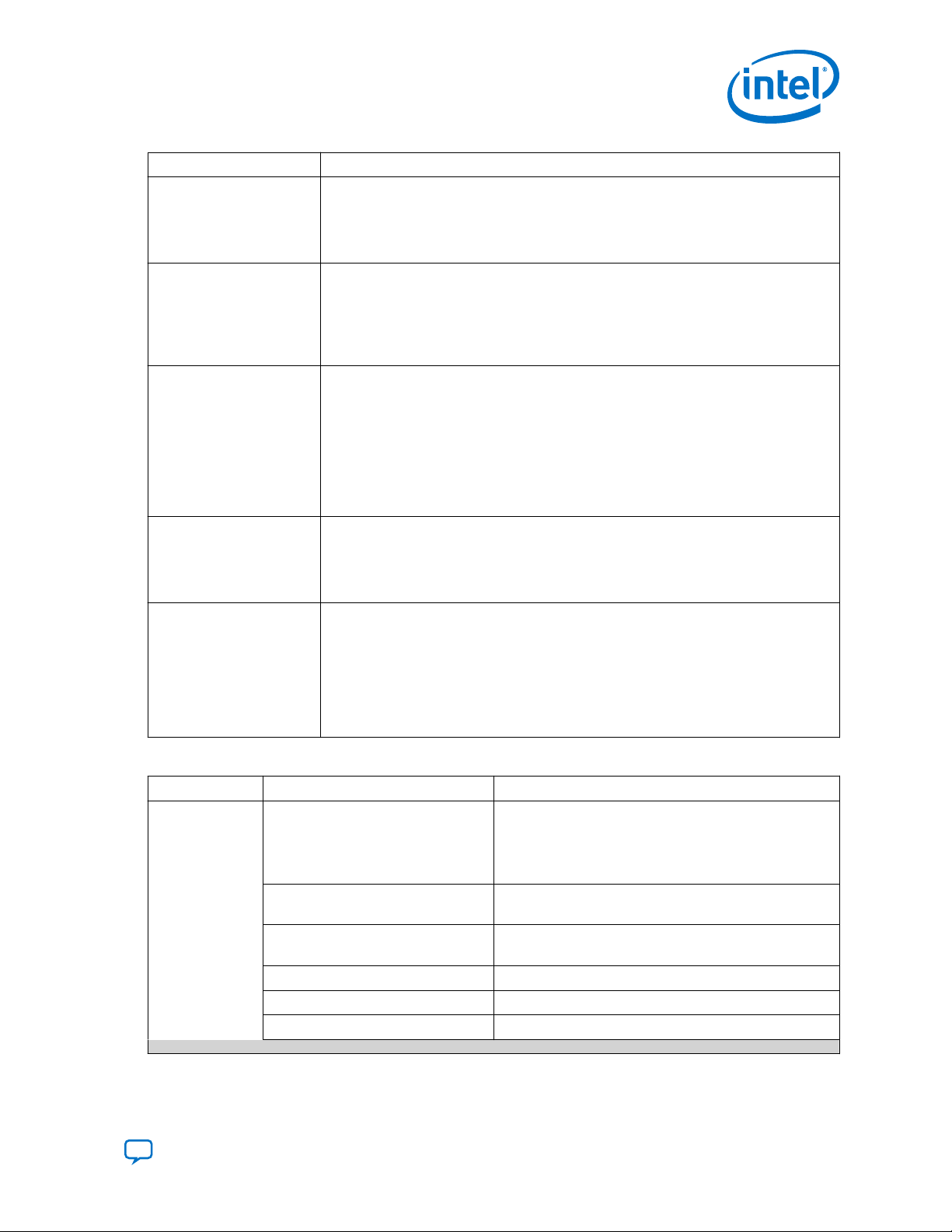

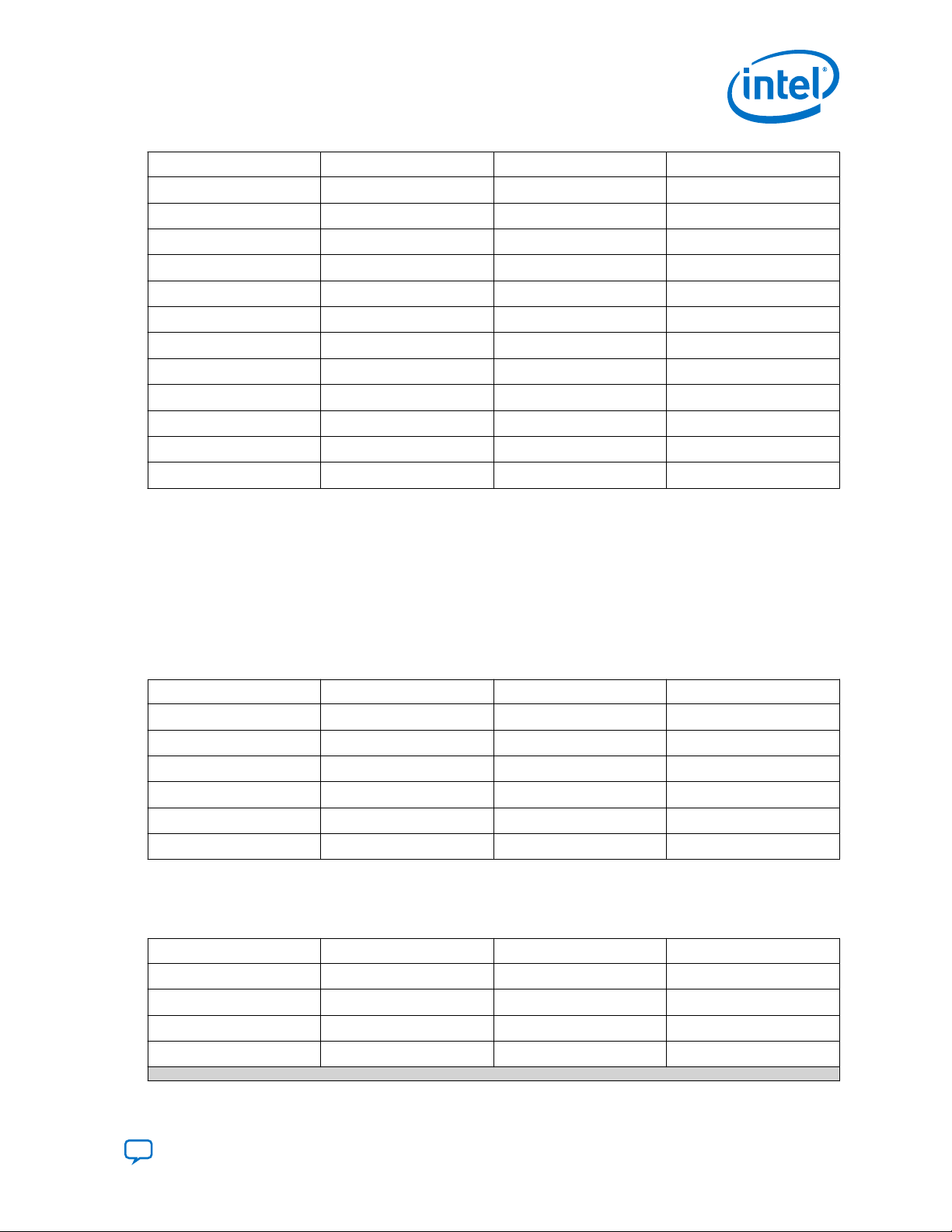

Figure 4. Board Picture (Bottom View)

Board Components Table

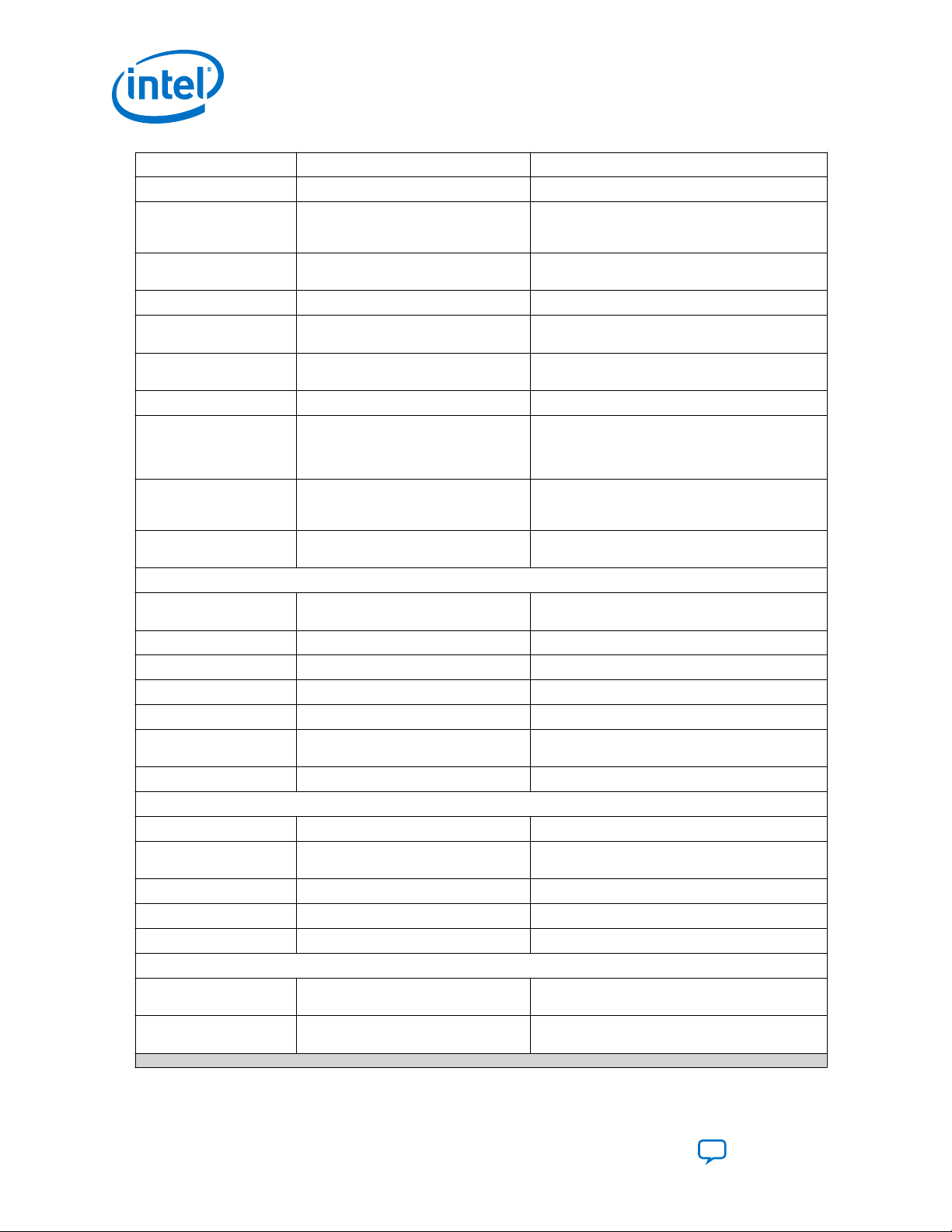

Table 5. Intel Stratix 10 SoC Board Components Table

Board Reference Type Description

Featured Device

U15 FPGA Intel Stratix 10 SoC FPGA

U43 CPLD Intel MAX 10 10M50DAF484I7G System Controller

U46 CPLD Intel MAX 10 10M16SAU169C8G Power Manager

Configuration, Status and Setup Elements

J1 JTAG chain header Provides access to the JTAG chain and disables the

SW1 JTAG chain control DIP switch Remove or include devices in the active JTAG chain

SW2 MSEL DIP Switch Controls the configuration scheme on the board.

J57 Micro-USB Header USB interface to on-board Intel FPGA Download

SW4 Function DIP Switch Selects I2C master, controls PCIe slot power and

SW8 Power Switch ON position: Power GUI

CPLD

on-board Intel FPGA Download Cable II when using

an external JTAG debugger such as an Intel FPGA

Download Cable II

MSEL pin 0,1,2 connect to the DIP Switch

Cable II JTAG for programming and debugging

HPS, FPGA orIntel MAX 10 CPLD through a type-B

Micro-USB cable.

selects FPGA image source

continued...

Send Feedback

Intel® Stratix® 10 SX SoC Development Kit User Guide

15

Page 16

4. Development Kit Components

UG-20081 | 2020.09.08

Board Reference Type Description

OFF position: Intel Enpirion dongle

S2 Program select push button Toggles the program select LEDs which selects the

S1 Configure push button Load image from flash memory to the FPGA based

D22 Configuration done LED Illuminates when the FPGA is configured

D20 Load LED Illuminates when the Intel MAX 10 CPLD System

D19 Error LED Illuminates when the FPGA configuration from flash

D31 Power LED Illuminates when 3.3V power is present

D1, D2 JTAG TX/RX LEDs Indicates the transmit or receive activity of the

D24, D26, D28 Program select LEDs Illuminates to show which flash memory image

D29, D30 FMC port present LEDs Illuminates when a daughtercard is plugged into

Clock Circuits

U26 Multi-output oscillator Si5338A quad-output fixed oscillator with 148.5

U29 50-MHz oscillator 50 MHz crystal oscillator for general purpose logic

U25 Multi-output oscillator Two 100 MHz outputs for PCIe application

J19, J20 Clock input SMA connector External clock inputs for the transceiver test port

U33 Multi-output oscillator Si5341 ten-output fixed oscillator

U31 Multi-output oscillator Si5338A quad-output fixed oscillator with four

U34 Multi-output clock cleaner LMK05028 Clock Cleaner

General User Input/Output

D21, D23, D25, D27 User LEDs Four user LEDs. Illuminate when driven high.

SW3 User DIP Switch User DIP switch. When the switch is ON, a logic 0

S3 FPGA Reset Push Button Reset the FPGA logic

S4, S5, S6, S7 General user push buttons Four user push buttons. Driven low when pressed

S20 HPS Reset Push Buttons HPS cold/warm reset push buttons

Memory Connectors

J134 HPS HILO Memory Connector HPS memory card include DDR3 HILO memory

J14 Boot Flash Connector Boot flash card options include QSPI flash card, SD

program image that loads from flash memory to

the FPGA

on the settings of the program select LEDs

Controller

memory fails

JTAG chain. The TX and RX LEDs flicker if the link

is in use and active. The LEDs are either off when

not in use or on when in use but idle

loads to the FPGA when you press the program

select push button

the FMC port

MHz, 100 MHz, 27 MHz and 100 MHz outputs

133.33 MHz outputs

is selected

card and DDR4 HILO memory card

micro flash card

continued...

Intel® Stratix® 10 SX SoC Development Kit User Guide

16

Send Feedback

Page 17

4. Development Kit Components

UG-20081 | 2020.09.08

Board Reference Type Description

J28 SO-DIMM 16 GB SO-DIMM DDR4 Memory Card

U41 I2C EEPROM 32 Kb I2C serial EEPROM

Communication Ports

J53 PCIe socket Gen3 x16 Socket

J11, J12 FMC Port J29 is a V57.4 compatible FMC connector. J19 is a

J7 SFP+ Port One SFP+ Ports

J3 Gigabit Ethernet Port SGMII Gigabit Ethernet port through FPGA

J4 Gigabit Ethernet Port SGMII Gigabit Ethernet Port through FPGA

J9-J10 QSFP28 Optical Transceiver Interface 17 Gbps/28 Gbps, 8 channels connected to QSFP28

J57, U2 USB-UART Port Mini-B USB interface to USB-to-UART bridge for

J22 DB9 UART Port DB9 RS-232 UART Port

U42 Real-time clock DS1339 device with built-in power sense circuit

Video and Display Ports

J8 HDMI Port Display Port interface

J5, U13 SDI Video Output Port HDBNC 75-Ohm SDI video TX interface

J6, U14 SDI Video Input Port HDBNC 75-Ohm SDI video RX interface

J29 Power GUI Connector Intel Enpirion Power GUI Connector

Power Supply

J25, J55 DC input jack Accepts 12 V DC power supply

SW7 Power Switch Switch to power on or off the board when power is

FMC connector defined by Intel 16 transceivers

specification

transceiver

transciever

modules

serial UART interface

that detects power failures and automatically

switches to backup battery supply, maintaining

time keeping even when the board is not powered

supplied from the DC input jack

4.3. Intel Stratix 10 SoC Device Overview

Intel's 14-nm Intel Stratix 10 SX SoCs deliver 2x core performance and up to 70%

lower power over previous generation high-performance SoCs. Featuring several

groundbreaking innovations, including the all new Intel Hyperflex™ core architecture,

this device family enables you to meet the demand for ever-increasing bandwidth and

processing performance in you most advanced applications, while meeting your power

budget.

Featuring several groundbreaking innovations, including the all new HyperFlex™ core

architecture, this device family enables you to meet the demand for ever-increasing

bandwidth and processing performance in your most advanced applications, while

meeting your power budget.

Send Feedback

Intel® Stratix® 10 SX SoC Development Kit User Guide

17

Page 18

4. Development Kit Components

UG-20081 | 2020.09.08

With an embedded hard processor system (HPS) based on a quad-core 64-bit Arm

Cortex*-A53, the Stratix 10 SoC devices deliver power efficient, application-class

processing and allow designers to extend hardware virtualization into the FPGA fabric.

Stratix 10 SoC devices demonstrate Intel's commitment to high-performance SoCs

and extend Intel's leadership in programmable devices featuring an Arm-based

processor system.

Important innovations in Stratix 10 FPGAs and SoCs include:

• All new HyperFlex core architecture delivering 2X the core performance compared

to previous generation high-performance FPGAs

• Industry leading Intel 14-nm Tri-Gate (FinFET) technology

• Heterogeneous 3D System-in-Package (SiP) technology

• Monolithic core fabric with up to 5.5 million logic elements (LEs)

• Up to 96 full duplex transceiver channels on heterogeneous 3D SiP transceiver

tiles

• Transceiver data rates up to 28.3 Gbps chip-to-chip/module and backplane

performance

• Embedded eSRAM (45 Mbit) and M20K (20 kbit) internal SRAM memory blocks

• Fractional synthesis and ultra-low jitter LC tank based transmit phase locked loops

(PLLs)

• Hard PCI Express® Gen3 x16 intellectual property (IP) blocks

• Hard 10GBASE-KR/40GBASE-KR4 Forward Error Correction (FEC) in every

transceiver channel

• Hard memory controllers and PHY supporting DDR4 rates up to 2666 Mbps per pin

• Hard fixed-point and IEEE 754 compliant hard floating-point variable precision

digital signal processing (DSP) blocks with up to 10 TFLOPS compute performance

with a power efficiency of 80 GFLOPS per Watt

• Quad-core 64-bit Arm Cortex-A53 embedded processor running up to 1.5 GHz in

SoC family variants

• Programmable clock tree synthesis for flexible, low power, low skew clock trees

• Dedicated secure device manager (SDM) for:

— Enhanced device configuration and security

— AES-256, SHA-256/384 and ECDSA-256/384 encrypt/decrypt accelerators and

authentication

— Multi-factor authentication

— Physically Unclonable Function (PUF) service and software programmable

device configuration capability

• Comprehensive set of advanced power saving features delivering up to 70% lower

power compared to previous generation high-performance FPGAs

• Non-destructive register state readback and writeback, to support ASIC

prototyping and other applications

Intel® Stratix® 10 SX SoC Development Kit User Guide

18

Send Feedback

Page 19

4. Development Kit Components

UG-20081 | 2020.09.08

With these capabilities, Stratix 10 FPGAs and SoCs are ideally suited for the most

demanding applications in diverse markets such as:

• Compute and Storage—for custom servers, cloud computing and data center

acceleration

• Networking—for Terabit, 400G and multi-100G bridging, aggregation, packet

processing and traffic management

• Optical Transport Networks—for OTU4, 2xOTU4, 4xOTU4

• Broadcast—for high-end studio distribution, headend encoding/decoding, edge

quadrature amplitude modulation (QAM)

• Military—for radar, electronic warfare, and secure communications

• Medical—for diagnostic scanners and diagnostic imaging

• Test and Measurement—for protocol and application testers

• Wireless—for next-generation 5G networks

• ASIC Prototyping—for designs that require the largest monolithic FPGA fabric

with the highest I/O count

Intel Stratix 10 SX SoC devices have a feature set that is identical to the Intel Stratix

10 FPGA devices, with the addition of an embedded quad-core 64-bit Arm Cortex A53

Hard Processor System.

Common to all Stratix 10 family variants is a high-performance fabric based on the

new HyperFlex core architecture that includes additional Hyper-Registers throughout

the interconnect routing and at the inputs of all functional blocks. The core fabric also

contains an enhanced logic array utilizing Intel’s adaptive logic module (ALM) and a

rich set of high performance building blocks including:

To clock these building blocks, Stratix 10 devices use programmable clock tree

synthesis, which uses dedicated clock tree routing to synthesize only those branches

of the clock trees required for the application. All devices support in-system, finegrained partial reconfiguration of the logic array, allowing logic to be added and

subtracted from the system while it is operating.

All family variants also contain high speed serial transceivers, containing both the

physical medium attachment (PMA) and the physical coding sublayer (PCS), which can

be used to implement a variety of industry standard and proprietary protocols. In

addition to the hard PCS, Stratix 10 devices contain multiple instantiations of PCI

Express hard IP that supports Gen1/Gen2/Gen3 rates in x1/x2/x4/x8/x16 lane

configurations, and hard 10GBASE-KR/40GBASE-KR4 FEC for every transceiver. The

hard PCS, FEC, and PCI Express IP free up valuable core logic resources, save power,

and increase your productivity.

Table 6. Stratix 10 FPGA and SoC Common Device Features

Feature Description

Technology • 14-nm Intel Tri-Gate (FinFET) process technology

• SmartVoltage ID (VID) controlled standard VCC option

• 0.8 V and 0.85 V optional VCC core voltage

Low power serial

transceivers

• Up to 96 total transceivers available

• Continuous operating range of 1 Gbps to 28.3 Gbps for Stratix 10 GX/SX devices

• Backplane support up to 28.3 Gbps for Stratix 10 GX/SX devices

continued...

Send Feedback

Intel® Stratix® 10 SX SoC Development Kit User Guide

19

Page 20

4. Development Kit Components

UG-20081 | 2020.09.08

Feature Description

• Extended range down to 125 Mbps with oversampling

• ATX transmit PLLs with user-configurable fractional synthesis capability

• XFP, SFP+, QSFP/QSFP28, CFP/CFP2/CFP4 optical module support

• Adaptive linear and decision feedback equalization

• Transmit pre-emphasis and de-emphasis

• Dynamic partial reconfiguration of individual transceiver channels

• On-chip instrumentation (EyeQ non-intrusive data eye monitoring)

General purpose I/Os • Up to 1640 total GPIO available

• 1.6 Gbps LVDS—every pair can be configured as an input or output

• 1333 MHz/2666 Mbps DDR4 external memory interface

• 1067 MHz/2133 Mbps DDR3 external memory interface

• 1.2 V to 3.0 V single-ended LVCMOS/LVTTL interfacing

• On-chip termination (OCT)

Embedded hard IP • PCIe Gen1/Gen2/Gen3 complete protocol stack, x1/x2/x4/x8/x16 end point and root

Transceiver hard IP • 10GBASE-KR/40GBASE-KR4 Forward Error Correction (FEC)

Power management • SmartVoltage ID controlled standard VCC option

High performance monolithic

core fabric

Internal memory blocks • eSRAM - 45-Mbit with hard ECC support

Variable precision DSP

blocks

port

• DDR4/DDR3/LPDDR3 hard memory controller (RLDRAM3/QDR II+/QDR IV using soft

memory controller)

• Multiple hard IP instantiations in each device

• Single Root I/O Virtualization (SR-IOV)

• 10G Ethernet PCS

• PCI Express PIPE interface

• Interlaken PCS

• Gigabit Ethernet PCS

• Deterministic latency support for Common Public Radio Interface (CPRI) PCS

• Fast lock-time support for Gigabit Passive Optical Networking (GPON) PCS

• 8B/10B, 64B/66B, 64B/67B encoders and decoders

• Custom mode support for proprietary protocols

• Low static power device options

• Intel Quartus Prime Pro Edition integrated power analysis

• HyperFlex core architecture with Hyper-Registers throughout the interconnect routing

and at the inputs of all functional blocks

• Monolithic fabric minimizes compile times and increases logic utilization

• Enhanced adaptive logic module (ALM)

• Improved multi-track routing architecture reduces congestion and improves compile

times

• Hierarchical core clocking architecture with programmable clock tree synthesis

• Fine-grained partial reconfiguration

• M20K—20-Kbit with hard ECC support

• MLAB—640-bit distributed LUTRAM

• IEEE 754-compliant hard single-precision floating point capability

• Supports signal processing with precision ranging from 18x19 up to 54x54

• Native 27x27 and 18x19 multiply modes

• 64-bit accumulator and cascade for systolic FIRs

• Internal coefficient memory banks

• Pre-adder/subtractor improves efficiency

• Additional pipeline register increases performance and reduces power

continued...

Intel® Stratix® 10 SX SoC Development Kit User Guide

20

Send Feedback

Page 21

4. Development Kit Components

UG-20081 | 2020.09.08

Feature Description

Phase locked loops (PLL) • Fractional synthesis PLLs (fPLL) support both fractional and integer modes

• Fractional mode with third-order delta-sigma modulation

• Precision frequency synthesis

• Integer PLLs adjacent to general purpose I/Os, support external memory, and LVDS

interfaces, clock delay compensation, zero delay buffering

Core clock networks • 1 GHz fabric clocking

• 667 MHz external memory interface clocking, supports 2666 Mbps DDR4 interface

• 800 MHz LVDS interface clocking, supports 1600 Mbps LVDS interface

• Programmable clock tree synthesis, backwards compatible with global, regional and

peripheral clock networks

• Clocks only synthesized where needed, to minimize dynamic power

Configuration • Dedicated Secure Device Manager

• Software programmable device configuration

• Serial and parallel flash interface

• Configuration via protocol (CvP) using PCI Express Gen1/Gen2/Gen3

• Fine-grained partial reconfiguration of core fabric

• Dynamic reconfiguration of transceivers and PLLs

• Comprehensive set of security features including AES-256, SHA-256/384, and

ECDSA-256/384 accelerators, and multi-factor authentication

• Physically Unclonable Function (PUF) service

Packaging • Intel Embedded Multi-die Interconnect Bridge (EMIB) packaging technology

• Multiple devices with identical package footprints allows seamless migration across

different device densities

• 1.0 mm ball-pitch FBGA packaging

• Lead and lead-free package options

Software and tools • Intel Quartus Prime Pro Edition design suite with new Spectra-Q engine and Hyper-

Aware design flow

• Fast Forward compiler to allow HyperFlex architecture performance exploration

• Transceiver toolkit

• Qsys system integration tool

• DSP Builder advanced blockset

• OpenCL™ support

• SoC Embedded Design Suite (EDS)

Table 7. Stratix 10 SoC Specific Device Features

SoC Subsystem Feature Description

Hard Processor

System

Send Feedback

Multi-processor unit (MPU) core • Quad-core Arm Cortex-A53 MPCore processor with Arm

CoreSight debug and trace technology

• Scalar floating-point unit supporting single and double

precision

• Arm NEON media processing engine for each processor

System Controllers • System Memory Management Unit (SMMU)

• Cache Coherency Unit (CCU)

Layer 1 Cache • 32 KB L1 instruction cache with parity

• 32 KB L1 data cache with ECC

Layer 2 Cache • 1 MB Shared L2 Cache with ECC

On-Chip Memory • 256 KB On-Chip RAM

Direct memory access (DMA) controller • 8-Channel DMA

Intel® Stratix® 10 SX SoC Development Kit User Guide

continued...

21

Page 22

4. Development Kit Components

SoC Subsystem Feature Description

Secure Device

Manager

External

Memory

Interface

Ethernet media access controller

(EMAC)

USB On-The-Go controller (OTG) • 2 USB OTG with integrated DMA

UART controller • 2 UART 16550 compatible

Serial Peripheral Interface (SPI)

controller

I2C controller • 5 I2C controllers

SD/SDIO/MMC controller • 1 eMMC version 4.5 with DMA and CE-ATA support

NAND flash controller • 1 ONFI 1.0, 8- and 16-bit support

General-purpose I/O (GPIO) • Maximum of 48 software programmable GPIO

Timers • 4 general-purpose timers

Security • Secure boot

External Memory Interface • Hard Memory Controller with DDR4 and DDR3, and

• Three 10/100/1000 EMAC with integrated DMA

• 4 SPI

• SD, including eSD, version 3.0

• SDIO, including eSDIO, verion 3.0

• CE-ATA - version 1.1

• 4 watchdog timers

• Advanced Encryption Standard (AES) and authentication

(SHA/ECDSA)

LPDDR3

UG-20081 | 2020.09.08

For further information , please refer to the Intel Stratix 10 GX/SX Device Overview

available on the Intel website.

Related Information

Stratix 10 GX/SX Device Overview

4.4. Intel MAX 10 System Controller Overview

Intel MAX 10 devices are single-chip, non-volatile low-cost programmable logic devices

(PLDs) to integrate the optimal set of system components.

Intel MAX 10 devices are the ideal solution for system management, I/O expansion,

communication control planes, industrial, automotive, and consumer applications.

The highlights of the Intel MAX 10 devices include:

• Internally stored dual configuration flash

• User flash memory

• Instant on support

• Integrated analog-to-digital converters (ADCs)

• Single-chip Nios II soft core processor support

Intel® Stratix® 10 SX SoC Development Kit User Guide

22

Send Feedback

Page 23

4. Development Kit Components

UG-20081 | 2020.09.08

Table 8. Summary of Features for Intel MAX 10 Devices

Feature Description

Technology 55 nm TSMC Embedded Flash (Flash + SRAM) process technology

Packaging • Low cost, small form factor packages—support multiple packaging

Core architecture • 4-input look-up table (LUT) and single register logic element (LE)

Internal memory blocks • M9K—9 kilobits (Kb) memory blocks

User flash memory (UFM) • User accessible non-volatile storage

Embedded multiplier blocks • One 18 × 18 or two 9 × 9 multiplier modes

ADC • 12-bit successive approximation register (SAR) type

Clock networks • Global clocks support

Internal oscillator Built-in internal ring oscillator

PLLs • Analog-based

General-purpose I/Os (GPIOs) • Multiple I/O standards support

External memory interface (EMIF)

(1)

technologies and pin pitches

• Multiple device densities with compatible package footprints for seamless

migration between different device densities

• RoHS6-compliant

• LEs arranged in logic array block (LAB)

• Embedded RAM and user flash memory

• Clocks and PLLs

• Embedded multiplier blocks

• General purpose I/Os

• Cascadable blocks to create RAM, dual port, and FIFO functions

• High speed operating frequency

• Large memory size

• High data retention

• Multiple interface option

• Cascadable blocks enabling creation of filters, arithmetic functions, and image

processing pipelines

• Up to 17 analog inputs

• Cumulative speed up to 1 million samples per second ( MSPS)

• Integrated temperature sensing capability

• High speed frequency in clock network

• Low jitter

• High precision clock synthesis

• Clock delay compensation

• Zero delay buffering

• Multiple output taps

• On-chip termination (OCT)

• Up to 830 megabits per second (Mbps) LVDS receiver, 800 Mbps LVDS

transmitter

Supports up to 600 Mbps external memory interfaces:

• DDR3, DDR3L, DDR2, LPDDR2 (on 10M16, 10M25, 10M40 and 10M50)

• SRAM (Hardware support only)

continued...

(1)

EMIF is only supported in selected MAX 10 device density and package combinations. Refer to

the External Memory Interface User Guide for more information.

Send Feedback

Intel® Stratix® 10 SX SoC Development Kit User Guide

23

Page 24

Feature Description

Note: For 600 Mbps performance, –6 device speed grade is required.

Performance varies according to device grade (commercial, industrial, or

automotive) and device speed grade (–6 or –7). Refer to the MAX 10

Device Data Sheet or External Memory Interface Spec Estimator for more

details.

Configuration • Internal configuration

• JTAG

• Advanced Encryption Standard (AES) 128-bit encryption and compression

options

• Flash memory data retention of 20 years at 85 °C

Flexible power supply schemes • Single- and dual-supply device options

• Dynamically controlled input buffer power down

• Sleep mode for dynamic power reduction

4.5. FPGA Configuration

This development kit supports the following FPGA configurations:

• QSPI Configuration

• SDMMC x4 Configuration

• JTAG Only

4. Development Kit Components

UG-20081 | 2020.09.08

A 4-bit DIP Switch (SW2) is used to select the FPGA configuration mode.

Table 9. DIP Switch Bits

Switch Bit Name

1 MSEL0

2 MSEL1

3 MSEL2

4 Not Used

Table 10. DIP Switch Bit Description

MSEL2 MSEL1 MSEL0 Mode

OFF OFF ON QSPI

ON OFF OFF SDMMC x4, SDMMC x8

ON ON ON JTAG

Note: The default setting is JTAG mode. The default bit position is "ON, ON, ON, ON"

4.6. General User Input/Output

Table 11. User I/O Pin Map

Pin Name Schematic Signal Name Description

PIN_A24

PIN_B24

USER_LED_FPGA0

USER_LED_FPGA2

USER_LED0

USER_LED1

continued...

Intel® Stratix® 10 SX SoC Development Kit User Guide

24

Send Feedback

Page 25

4. Development Kit Components

UG-20081 | 2020.09.08

Pin Name Schematic Signal Name Description

PIN_F22

PIN_E22

PIN_A26

PIN_A25

PIN_D23

PIN_D24

PIN_B23

PIN_C23

PIN_E23

PIN_E24

USER_LED_FPGA1

USER_LED_FPGA3

USER_PB_FPGA0

USER_PB_FPGA1

USER_PB_FPGA2

USER_PB_FPGA3

USER_DIPSW_FPGA0

USER_DIPSW_FPGA1

USER_DIPSW_FPGA2

USER_DIPSW_FPGA3

4.7. Connectors and Interfaces

The FPGA portion of this development kit includes 96 transceivers.

Table 12. Channel Assignment for Transceiver Applications

USER_LED2

USER_LED3

USER_PB0

USER_PB1

USER_PB2

USER_PB3

USER_DPSW0

USER_DPSW1

USER_DPSW2

USER_DPSW3

Applications Channel (Bank, Number)

FMC+ A 1C (1C, 0-5), 1D (1D, 0-5), 1E (1E, 0-3), 1F (PCIE EP x16)

SFP+ Port (4C, 0)

PCIE RC x16 (4K, 0-5), (4L, 0-5), (4M, 0-3)

SGMII Port 1 and Port 2 (4M, 4), (4M, 5)

FMC+ B 1K (1K, 0-5), 1L (1L, 0-5), 1M (1M, 0-3), 1N (PCIE EPx16)

MXP Test Ports (4D, 0, 1, 3, 4)

SDI Port TX (4E,1), RX (4F, 0)

HDMI (4C, 2-5)

ZQSFP+ B (4F, (0,1,3,4))

ZQSFP+ A (4N, (0,1,3,4))

4.7.1. PCIe Slot

The PCIe root port is a PCIe Gen3 x16 port. This port is assigned to 4K, 4L and 4M

Banks. The transceiver I/O bank power is connected to 1.8 V.

PCIE_PRSNT2n, PCIE_PERSTn and PCIE_WAKE_N 3V3 signals are mapped to the

dedicated trasnceiver I/O bank (IO4) in the Intel MAX 10. The system performance of

the PCIe root port should meet the PCIe 3.0 specifications.

Send Feedback

Intel® Stratix® 10 SX SoC Development Kit User Guide

25

Page 26

Table 13. PCIE Root Port FPGA Pin Map

Pin Name Schematic Signal Name Direction Description

PIN_V12

PIN_V13

PIN_L4

PIN_L3

PIN_H6

PIN_H5

PIN_K2

PIN_K1

PIN_L8

PIN_L7

PIN_N4

PIN_N3

PIN_K6

PIN_K5

PIN_M2

PIN_M1

PIN_N8

PIN_N7

PIN_R4

PIN_R3

PIN_M6

PIN_M5

PIN_P2

PIN_P1

PIN_R8

PIN_R7

PIN_T2

PIN_T1

PIN_P6

PIN_P5

PIN_U4

PIN_U3

PIN_T6

PCIE_REFCLK_QR0_P

PCIE_REFCLK_QR0_N

PCIE_TX_N15

PCIE_TX_P15

PCIE_RX_N15

PCIE_RX_P15

PCIE_TX_N14

PCIE_TX_P14

PCIE_RX_N14

PCIE_RX_P14

PCIE_TX_N13

PCIE_TX_P13

PCIE_RX_N13

PCIE_RX_P13

PCIE_TX_N12

PCIE_TX_P12

PCIE_RX_N12

PCIE_RX_P12

PCIE_TX_N11

PCIE_TX_P11

PCIE_RX_N11

PCIE_RX_P11

PCIE_TX_N10

PCIE_TX_P10

PCIE_RX_N10

PCIE_RX_P10

PCIE_TX_N9

PCIE_TX_P9

PCIE_RX_N9

PCIE_RX_P9

PCIE_TX_N8

PCIE_TX_P8

PCIE_RX_N8

4. Development Kit Components

UG-20081 | 2020.09.08

Input REFCLK_GXBR4K_CHTP

Input REFCLK_GXBR4K_CHTN

Output GXBR4M_TX_CH3N

Output GXBR4M_TX_CH3P

Input GXBR4M_RX_CH3N

Input GXBR4M_RX_CH3P

Output GXBR4M_TX_CH2N

Output GXBR4M_TX_CH2P

Input GXBR4M_RX_CH2N

Input GXBR4M_RX_CH2P

Output GXBR4M_TX_CH1N

Output GXBR4M_TX_CH1P

Input GXBR4M_RX_CH1N

Input GXBR4M_RX_CH1P

Output GXBR4M_TX_CH0N

Output GXBR4M_TX_CH0P

Input GXBR4M_RX_CH0N

Input GXBR4M_RX_CH0P

Output GXBR4L_TX_CH5N

Output GXBR4L_TX_CH5P

Input GXBR4L_RX_CH5N

Input GXBR4L_RX_CH5P

Output GXBR4L_TX_CH4N

Output GXBR4L_TX_CH4P

Input GXBR4L_RX_CH4N

Input GXBR4L_RX_CH4P

Output GXBR4L_TX_CH3N

Output GXBR4L_TX_CH3P

Input GXBR4L_RX_CH3N

Input GXBR4L_RX_CH3P

Output GXBR4L_TX_CH2N

Output GXBR4L_TX_CH2P

Input GXBR4L_RX_CH2N

continued...

Intel® Stratix® 10 SX SoC Development Kit User Guide

26

Send Feedback

Page 27

4. Development Kit Components

UG-20081 | 2020.09.08

Pin Name Schematic Signal Name Direction Description

PIN_T5

PIN_V2

PIN_V1

PIN_U8

PIN_U7

PIN_Y2

PIN_Y1

PIN_V6

PIN_V5

PIN_W4

PIN_W3

PIN_Y6

PIN_Y5

PIN_AB2

PIN_AB1

PIN_W8

PIN_W7

PIN_AA4

PIN_AA3

PIN_AB6

PIN_AB5

PIN_AD2

PIN_AD1

PIN_AA8

PIN_AA7

PIN_AC4

PIN_AC3

PIN_AD6

PIN_AD5

PIN_AE4

PIN_AE3

PIN_AC8

PIN_AC7

PCIE_RX_P8

PCIE_TX_N7

PCIE_TX_P7

PCIE_RX_N7

PCIE_RX_P7

PCIE_TX_N6

PCIE_TX_P6

PCIE_RX_N6

PCIE_RX_P6

PCIE_TX_N5

PCIE_TX_P5

PCIE_RX_N5

PCIE_RX_P5

PCIE_TX_N4

PCIE_TX_P4

PCIE_RX_N4

PCIE_RX_P4

PCIE_TX_N3

PCIE_TX_P3

PCIE_RX_N3

PCIE_RX_P3

PCIE_TX_N2

PCIE_TX_P2

PCIE_RX_N2

PCIE_RX_P2

PCIE_TX_N1

PCIE_TX_P1

PCIE_RX_N1

PCIE_RX_P1

PCIE_TX_N0

PCIE_TX_P0

PCIE_RX_N0

PCIE_RX_P0

Input GXBR4L_RX_CH2P

Output GXBR4L_TX_CH1N

Output GXBR4L_TX_CH1P

Input GXBR4L_RX_CH1N

Input GXBR4L_RX_CH1P

Output GXBR4L_TX_CH0N

Output GXBR4L_TX_CH0P

Input GXBR4L_RX_CH0N

Input GXBR4L_RX_CH0P

Output GXBR4K_TX_CH5N

Output GXBR4K_TX_CH5P

Input GXBR4K_RX_CH5N

Input GXBR4K_RX_CH5P

Output GXBR4K_TX_CH4N

Output GXBR4K_TX_CH4P

Input GXBR4K_RX_CH4N

Input GXBR4K_RX_CH4P

Output GXBR4K_TX_CH3N

Output GXBR4K_TX_CH3P

Input GXBR4K_RX_CH3N

Input GXBR4K_RX_CH3P

Output GXBR4K_TX_CH2N

Output GXBR4K_TX_CH2P

Input GXBR4K_RX_CH2N

Input GXBR4K_RX_CH2P

Output GXBR4K_TX_CH1N

Output GXBR4K_TX_CH1P

Input GXBR4K_RX_CH1N

Input GXBR4K_RX_CH1P

Output GXBR4K_TX_CH0N

Output GXBR4K_TX_CH0P

Input GXBR4K_RX_CH0N

Input GXBR4K_RX_CH0P

Send Feedback

Intel® Stratix® 10 SX SoC Development Kit User Guide

27

Page 28

4.7.2. ZQSFP+

The ZQSFP+ 0/1 ports meet SFF8665 and QSFP28 industrial standards. The connector

part number is Molex 170432-001. The cage part number is TE 2227103-2. The PCB

trace insertion loss is less than -5 dB and return loss is less than -10 dB. The ZQSFP+

signals (Modesl, RESETL, MOdPrsl, LPmode, int) are mapped to the dedicated I/O

in System Intel MAX 10. The BC25, BC26 pins in 2F bank are I2C interface. The user

needs this interface to access ZQSFP.

Table 14. ZQSFP+ 0/1 Ports FPGA Pin Map

Pin Name Schematic Signal Name Direction Description

PIN_P9

PIN_P10

PIN_C4

PIN_C3

PIN_A8

PIN_A7

PIN_E4

PIN_E3

PIN_C8

PIN_C7

PIN_G4

PIN_G3

PIN_D6

PIN_D5

PIN_F2

PIN_F1

PIN_G8

PIN_G7

PIN_T9

PIN_T10

PIN_AF2

PIN_AF1

PIN_AG8

PIN_AG7

PIN_AJ4

PIN_AJ3

CLEARNER_XVR_644.53125

MHZ_P

CLEARNER_XVR_644.53125

MHZ_N

ZQSFP0_TXN3

ZQSFP0_TXP3

ZQSFP0_RXN3

ZQSFP0_RXP3

ZQSFP0_TXN2

ZQSFP0_TXP2

ZQSFP0_RXN2

ZQSFP0_RXP2

ZQSFP0_TXN1

ZQSFP0_TXP1

ZQSFP0_RXN1

ZQSFP0_RXP1

ZQSFP0_TXN0

ZQSFP0_TXP0

ZQSFP0_RXN0

ZQSFP0_RXP0

REFCLK0_P

REFCLK0_N

ZQSFP1_TXN3

ZQSFP1_TXP3

ZQSFP1_RXN3

ZQSFP1_RXP3

ZQSFP1_TXN2

ZQSFP1_TXP2

4. Development Kit Components

UG-20081 | 2020.09.08

Input REFCLK_GXBR4N_CHTP

Input REFCLK_GXBR4N_CHTN

Output GXBR4N_TX_CH3N

Output GXBR4N_TX_CH3P

Input GXBR4N_RX_CH3N

Input GXBR4N_RX_CH3P

Output GXBR4N_TX_CH2N

Output GXBR4N_TX_CH2P

Input GXBR4N_RX_CH2N

Input GXBR4N_RX_CH2P

Output GXBR4N_TX_CH1N

Output GXBR4N_TX_CH1P

Input GXBR4N_RX_CH1N

Input GXBR4N_RX_CH1P

Output GXBR4N_TX_CH0N

Output GXBR4N_TX_CH0P

Input GXBR4N_RX_CH0N

Input GXBR4N_RX_CH0P

Input REFCLK_GXBR4N_CHBP

Input REFCLK_GXBR4N_CHBN

Output GXBR4F_TX_CH3N

Output GXBR4F_TX_CH3P

Input GXBR4F_RX_CH3N

Input GXBR4F_RX_CH3P

Output GXBR4F_TX_CH2N

Output GXBR4F_TX_CH2P

continued...

Intel® Stratix® 10 SX SoC Development Kit User Guide

28

Send Feedback

Page 29

4. Development Kit Components

UG-20081 | 2020.09.08

Pin Name Schematic Signal Name Direction Description

PIN_AF6

PIN_AF5

PIN_AL4

PIN_AL3

PIN_AH6

PIN_AH5

PIN_AK2

PIN_AK1

PIN_AL8

PIN_AL7

PIN_AM12

PIN_AM13

4.7.3. SFP+

ZQSFP1_RXN2

ZQSFP1_RXP2

ZQSFP1_TXN1

ZQSFP1_TXP1

ZQSFP1_RXN1

ZQSFP1_RXP1

ZQSFP1_TXN0

ZQSFP1_TXP0

ZQSFP1_RXN0

ZQSFP1_RXP0

REFCLK_QSFP1_P

REFCLK_QSFP1_N

Input GXBR4F_RX_CH2N

Input GXBR4F_RX_CH2P

Output GXBR4F_TX_CH1N

Output GXBR4F_TX_CH1P

Input GXBR4F_RX_CH1N

Input GXBR4F_RX_CH1P

Output GXBR4F_TX_CH0N

Output GXBR4F_TX_CH0P

Input GXBR4F_RX_CH0N

Input GXBR4F_RX_CH0P

Input REFCLK_GXBR4F_CHBP

Input REFCLK_GXBR4F_CHBN

The SFP+ Port meets SFF-8431 Industrial Standard. The connector part number is

Samtec MECT-110-01-M-D-RA1. The cage part number is Molex 74754-0101. The PCB

trace insertion loss is less than -5 dB and return loss less than -10 dB.

SFP+ signals (TX_disable, RS0/1, MOD_ABS, LOS, Fault) are mapped to the dedicated

transceiver I/O in Intel MAX 10.

Table 15. SFP+ Port FPGA Pin Map

Pin Name Schematic Signal Name Direction Description

PIN_BJ5

PIN_BJ4

PIN_BH10

PIN_BH9

PIN_AT9

PIN_AT10

SFPA_TX_N

SFPA_TX_P

SFPA_RX_N

SFPA_RX_P

REFCLK_SFPA_P

REFCLK_SFPA_N

4.7.4. HDMI

Table 16. HDMI Port FPGA Pin Map

Pin Name Schematic Signal Name Direction Description

PIN_AP9

PIN_AP10

PIN_BC4

PIN_BC3

HDMIREFCLK_P

HDMIREFCLK_N

HDMI_LANE_CLKN

HDMI_LANE_CLKP

Output GXBR4C_TX_CH0N

Output GXBR4C_TX_CH0P

Input GXBR4C_RX_CH0N

Input GXBR4C_RX_CH0P

Input REFCLK_GXBR4C_CHBP

Input REFCLK_GXBR4C_CHBN

Input REFCLK_GXBR4C_CHTP

Input REFCLK_GXBR4C_CHTN

Output GXBR4C_TX_CH5N

Output GXBR4C_TX_CH5P

continued...

Send Feedback

Intel® Stratix® 10 SX SoC Development Kit User Guide

29

Page 30

Pin Name Schematic Signal Name Direction Description

PIN_BF2

PIN_BF1

PIN_BE4

PIN_BE3

PIN_BG4

PIN_BG3

HDMI_LANE_N2

HDMI_LANE_P2

HDMI_LANE_N1

HDMI_LANE_P1

HDMI_LANE_N0

HDMI_LANE_P0

4.7.5. SDI Port

Table 17. SDI Port FPGA Pin Map

Pin Name Schematic Signal Name Direction Description

PIN_AF9

PIN_AF10

PIN_AR4

PIN_AR3

PIN_AR8

PIN_AR7

PIN_AK12

PIN_AK13

CLEARNER_SDI_245MHZ_P

CLEARNER_SDI_245MHZ_N

SDI_TX_N

SDI_TX_P

SDI_RX_N

SDI_RX_P

CLEARNER_SDI_297MHZ_P

CLEARNER_SDI_297MHZ_N

4. Development Kit Components

UG-20081 | 2020.09.08

Output GXBR4C_TX_CH4N

Output GXBR4C_TX_CH4P

Output GXBR4C_TX_CH3N

Output GXBR4C_TX_CH3P

Output GXBR4C_TX_CH2N

Output GXBR4C_TX_CH2P

Input REFCLK_GXBL4E_CHTP

Input REFCLK_GXBL4E_CHTN

Output GXBR4E_TX_CH1N

Output GXBR4E_TX_CH1P

Input GXBR4E_RX_CH0N

Input GXBR4E_RX_CH0P

Input REFCLK_GXBL4F_CHTP

Input REFCLK_GXBL4F_CHTN

4.7.6. MXP

The MXP Test Port is a MXP Coaxial Print Connectors. The PCB trace insertion loss is

less than -5 dB and return loss is less than -10 dB. You can use it for 100 Gbps

applications.

Table 18. MXP Port FPGA Pin Map

Pin Name Schematic Signal Name Direction Description

PIN_AK9

PIN_AK10

PIN_AY2

PIN_AY1

PIN_AU8

PIN_AU7

PIN_AW4

PIN_AW3

PIN_AY6

PIN_AY5

REFCLK_SMA_P

REFCLK_SMA_N

MXP_TXN3

MXP_TXP3

MXP_RXN3

MXP_RXP3

MXP_TXN2

MXP_TXP2

MXP_RXN2

MXP_RXP2

Input REFCLK_GXBR4D_CHTP

Input REFCLK_GXBR4D_CHTN

Output GXBR4D_TX_CH3N

Output GXBR4D_TX_CH3P

Input GXBR4D_RX_CH3N

Input GXBR4D_RX_CH3P

Output GXBR4D_TX_CH2N

Output GXBR4D_TX_CH2P

Input GXBR4D_RX_CH2N

Input GXBR4D_RX_CH2P

continued...

Intel® Stratix® 10 SX SoC Development Kit User Guide

30

Send Feedback

Page 31

4. Development Kit Components

UG-20081 | 2020.09.08

Pin Name Schematic Signal Name Direction Description

PIN_BA4

PIN_BA3

PIN_BB6

PIN_BB5

PIN_BD2

PIN_BD1

PIN_BA8

PIN_BA7

MXP_TXN1

MXP_TXP1

MXP_RXN1

MXP_RXP1

MXP_TXN0

MXP_TXP0

MXP_RXN0

MXP_RXP0

Output GXBR4D_TX_CH1N

Output GXBR4D_TX_CH1P

Input GXBR4D_RX_CH1N

Input GXBR4D_RX_CH1P

Output GXBR4D_TX_CH0N

Output GXBR4D_TX_CH0P

Input GXBR4D_RX_CH0N

Input GXBR4D_RX_CH0P

4.7.7. Intel FPGA Download Cable Direct Port (Debug Port)

The Direct Port is connected to the 3B bank.

Table 19. Debug Port FPGA Pin Map

Pin Name Schematic Signal Name Description

PIN_AP16

PIN_AP15

PIN_AU13

PIN_AV13

PIN_AU12

PIN_AT12

PIN_AR13

PIN_AP12

PIN_AP14

PIN_AP13

PIN_AT14

PIN_AR14

PIN_AR18

PIN_AP18

PIN_AU14

PIN_AU15

USB0

USB1

USB2

USB3

USB4

USB5

USB6

USB7

USB_RDN

USB_WRN

USB_OEN

USB_RESETN

USB_EMPTY

USB_FULL

USB_SDA

USB_SCL

USB Debug Data

USB Debug Data

USB Debug Data

USB Debug Data

USB Debug Data

USB Debug Data

USB Debug Data

USB Debug Data

USB Debug Control Signal

USB Debug Control Signal

USB Debug Control Signal

USB Debug Control Signal

USB Debug Control Signal

USB Debug Control Signal

USB Debug I2C

USB Debug I2C

Send Feedback

Intel® Stratix® 10 SX SoC Development Kit User Guide

31

Page 32

4.7.8. FMC+ A/B Slot

Table 20. FMC+ A Slot FPGA Pin Map

Pin Name Schematic Signal Name Direction Description

PIN_AP41

PIN_AP40

PIN_BC46

PIN_BC47

PIN_BD44

PIN_BD45

PIN_BF48

PIN_BF49

PIN_BC42

PIN_BC43

PIN_BE46

PIN_BE47

PIN_BE42

PIN_BE43

PIN_BG46

PIN_BG47

PIN_BG42

PIN_BG43

PIN_BF44

PIN_BF45

PIN_BJ42

PIN_BJ43

PIN_BJ45

PIN_BJ46

PIN_BH40

PIN_BH41

PIN_AT41

PIN_AT40

PIN_AK41

PIN_AK40

PIN_AU46

FAGBTCLK0M2CP

FAGBTCLK0M2CN

FAD5C2MN

FAD5C2MP

FAD5M2CN

FAD5M2CP

FAD4C2MN

FAD4C2MP

FAD4M2CN

FAD4M2CP

FAD3C2MN

FAD3C2MP

FAD3M2CN

FAD3M2CP

FAD2C2MN

FAD2C2MP

FAD2M2CN

FAD2M2CP

FAD1C2MN

FAD1C2MP

FAD1M2CN

FAD1M2CP

FAD0C2MN

FAD0C2MP

FAD0M2CN

FAD0M2CP

CLEARNER_XVRR_122.88MH

Z_P

CLEARNER_XVRR_122.88MH

Z_N

FAGBTCLK1M2CP

FAGBTCLK1M2CN

FAD11C2MN

4. Development Kit Components

UG-20081 | 2020.09.08

Input REFCLK_GXBL1C_CHTP

Input REFCLK_GXBL1C_CHTN

Output GXBR1C_TX_CH5N

Output GXBR1C_TX_CH5P

Input GXBR1C_RX_CH5N

Input GXBR1C_RX_CH5P

Output GXBR1C_TX_CH4N

Output GXBR1C_TX_CH4P

Input GXBR1C_RX_CH4N

Input GXBR1C_RX_CH4P

Output GXBR1C_TX_CH3N

Output GXBR1C_TX_CH3P

Input GXBR1C_RX_CH3N

Input GXBR1C_RX_CH3P

Output GXBR1C_TX_CH2N

Output GXBR1C_TX_CH2P

Input GXBR1C_RX_CH2N

Input GXBR1C_RX_CH2P

Output GXBR1C_TX_CH1N

Output GXBR1C_TX_CH1P

Input GXBR1C_RX_CH1N

Input GXBR1C_RX_CH1P

Output GXBR1C_TX_CH0N

Output GXBR1C_TX_CH0P

Input GXBR1C_RX_CH0N

Input GXBR1C_RX_CH0P

Input REFCLK_GXBL1C_CHBP

Input REFCLK_GXBL1C_CHBN

Input REFCLK_GXB1D_CHTP

Input REFCLK_GXB1D_CHTN

Output GXBR1D_TX_CH5N

continued...

Intel® Stratix® 10 SX SoC Development Kit User Guide

32

Send Feedback

Page 33

4. Development Kit Components

UG-20081 | 2020.09.08

Pin Name Schematic Signal Name Direction Description

PIN_AU47

PIN_AV44

PIN_AV45

PIN_AY48

PIN_AY49

PIN_AU42

PIN_AU43

PIN_AW46

PIN_AW47

PIN_AY44

PIN_AY45

PIN_BB48

PIN_BB49

PIN_AW42

PIN_AW43

PIN_BA46

PIN_BA47

PIN_BB44

PIN_BB45

PIN_BD48

PIN_BD49

PIN_BA42

PIN_BA43

PIN_AM41

PIN_AM40

PIN_AF41

PIN_AF40

PIN_AM48

PIN_AM49

PIN_AK44

PIN_AK45

PIN_AN46

PIN_AN47

PIN_AM44

FAD11C2MP

FAD11M2CN

FAD11M2CP

FAD10C2MN

FAD10C2MP

FAD10M2CN

FAD10M2CP

FAD9C2MN

FAD9C2MP

FAD9M2CN

FAD9M2CP

FAD8C2MN

FAD8C2MP

FAD8M2CN

FAD8M2CP

FAD7C2MN

FAD7C2MP

FAD7M2CN

FAD7M2CP

FAD6C2MN

FAD6C2MP

FAD6M2CN

FAD6M2CP

FAGBTCLK3M2CP

FAGBTCLK3M2CN

FAGBTCLK2M2CP

FAGBTCLK2M2CN

FAD17C2MN

FAD17C2MP

FAD17M2CN

FAD17M2CP

FAD16C2MN

FAD16C2MP

FAD16M2CN

Output GXBR1D_TX_CH5P

Input GXBR1D_RX_CH5N

Input GXBR1D_RX_CH5P

Output GXBR1D_TX_CH4N

Output GXBR1D_TX_CH4P

Input GXBR1D_RX_CH4N

Input GXBR1D_RX_CH4P

Output GXBR1D_TX_CH3N

Output GXBR1D_TX_CH3P

Input GXBR1D_RX_CH3N

Input GXBR1D_RX_CH3P

Output GXBR1D_TX_CH2N

Output GXBR1D_TX_CH2P

Input GXBR1D_RX_CH2N

Input GXBR1D_RX_CH2P

Output GXBR1D_TX_CH1N

Output GXBR1D_TX_CH1P

Input GXBR1D_RX_CH1N

Input GXBR1D_RX_CH1P

Output GXBR1D_TX_CH0N

Output GXBR1D_TX_CH0P

Input GXBR1D_RX_CH0N

Input GXBR1D_RX_CH0P

Input REFCLK_GXBL1D_CHBP

Input REFCLK_GXBL1D_CHBN

Input REFCLK_GXBL1E_CHBP

Input REFCLK_GXBL1E_CHBN

Output GXBR1E_TX_CH5N

Output GXBR1E_TX_CH5P

Input GXBR1E_RX_CH5N

Input GXBR1E_RX_CH5P

Output GXBR1E_TX_CH4N

Output GXBR1E_TX_CH4P

Input GXBR1E_RX_CH4N

continued...

Send Feedback

Intel® Stratix® 10 SX SoC Development Kit User Guide

33

Page 34

PIN_AM45

PIN_AP48

PIN_AP49

PIN_AN42

PIN_AN43

PIN_AT48

PIN_AT49

PIN_AP44

PIN_AP45

PIN_AR46

PIN_AR47

PIN_AT44

PIN_AT45

PIN_AV48

PIN_AV49

PIN_AR42

PIN_AR43

PIN_AH41

PIN_AH40

PIN_AK38

PIN_AK37

PIN_AG46

PIN_AG47

PIN_AE42

PIN_AE43

PIN_AF48

PIN_AF49

PIN_AG42

PIN_AG43

PIN_AJ46

PIN_AJ47

PIN_AF44

PIN_AF45

PIN_AH48

4. Development Kit Components

UG-20081 | 2020.09.08

Pin Name Schematic Signal Name Direction Description

FAD16M2CP

FAD15C2MN

FAD15C2MP

FAD15M2CN

FAD15M2CP

FAD14C2MN

FAD14C2MP

FAD14M2CN

FAD14M2CP

FAD13C2MN

FAD13C2MP

FAD13M2CN

FAD13M2CP

FAD12C2MN

FAD12C2MP

FAD12M2CN

FAD12M2CP

FAGBTCLK4M2CP

FAGBTCLK4M2CN

FAGBTCLK5M2CP

FAGBTCLK5M2CN

FAD23C2MN

FAD23C2MP

FAD23M2CN

FAD23M2CP

FAD22C2MN

FAD22C2MP

FAD22M2CN

FAD22M2CP

FAD21C2MN

FAD21C2MP

FAD21M2CN

FAD21M2CP

FAD20C2MN

Input GXBR1E_RX_CH4P

Output GXBR1E_TX_CH3N

Output GXBR1E_TX_CH3P

Input GXBR1E_RX_CH3N

Input GXBR1E_RX_CH3P

Output GXBR1E_TX_CH2N

Output GXBR1E_TX_CH2P

Input GXBR1E_RX_CH2N

Input GXBR1E_RX_CH2P

Output GXBR1E_TX_CH1N

Output GXBR1E_TX_CH1P

Input GXBR1E_RX_CH1N

Input GXBR1E_RX_CH1P

Output GXBR1E_TX_CH0N

Output GXBR1E_TX_CH0P

Input GXBR1E_RX_CH0N

Input GXBR1E_RX_CH0P

Input REFCLK_GXBL1E_CHBP

Input REFCLK_GXBL1E_CHBN

Input REFCLK_GXBL1F_CHTP

Input REFCLK_GXBL1F_CHTN

Output GXBR1F_TX_CH5N

Output GXBR1F_TX_CH5P

Input GXBR1F_RX_CH5N

Input GXBR1F_RX_CH5P

Output GXBR1F_TX_CH4N

Output GXBR1F_TX_CH4P

Input GXBR1F_RX_CH4N

Input GXBR1F_RX_CH4P

Output GXBR1F_TX_CH3N

Output GXBR1F_TX_CH3P

Input GXBR1F_RX_CH3N

Input GXBR1F_RX_CH3P

Output GXBR1F_TX_CH2N

continued...

Intel® Stratix® 10 SX SoC Development Kit User Guide

34

Send Feedback

Page 35

4. Development Kit Components

UG-20081 | 2020.09.08

Pin Name Schematic Signal Name Direction Description

PIN_AH49

PIN_AJ42

PIN_AJ43

PIN_AL46

PIN_AL47

PIN_AH44

PIN_AH45

PIN_AK48

PIN_AK49

PIN_AL42

PIN_AL43

PIN_AM38

PIN_AM37

FAD20C2MP

FAD20M2CN

FAD20M2CP

FAD19C2MN