Page 1

Intel® Server Board S5000PAL /

S5000XAL

Technical Product Specification

Intel order number: D31979-007

Revision 1.4

May 2007

Enterprise Platforms and Services Division - Marketing

Revision 1.4

ii

Intel order number: D31979-007

Page 2

Intel® Server Board S5000PAL / S5000XAL TPS Revision History

Revision History

Date Revision

Number

April 2006 1.0 First external release.

June 2006 1.1 Updated theoretical memory bandwidth performance numbers.

Added Platform Control sections.

August 2006 1.2 Memory RAS is now available.

Updated Snoop Filter Section.

Updated Figures #16 and #25.

January 2007 1.3 Updated Table 44 BMC sensor.

Updated CMOS clear and password reset usage procedures.

Updated regulatory tables.

May 2007 1.4 Removed platform control information that can be found in the Intel® S5000

Server Board Family Datasheet.

Modifications

Revision 1.4

iii

Intel order number: D31979-007

Page 3

Disclaimers Intel® Server Board S5000PAL / S5000XAL TPS

Disclaimers

Information in this document is provided in connection with Intel® products. No license, express or implied,

by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as

provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever,

and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including

liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any

patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life

saving, or life sustaining applications. Intel may make changes to specifications and product descriptions

at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked

"reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility

whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel

errors known as errata which may cause the product to deviate from published specifications. Current

characterized errata are available on request.

Intel Corporation server baseboards support peripheral components and contain a number of highdensity VLSI and power delivery components that need adequate airflow to cool. Intel’s own chassis are

designed and tested to meet the intended thermal requirements of these components when the fully

integrated system is used together. It is the responsibility of the system integrator that chooses not to use

Intel developed server building blocks to consult vendor datasheets and operating parameters to

determine the amount of air flow required for their specific application and environmental conditions. Intel

Corporation can not be held responsible if components fail or the server board does not operate correctly

when used outside any of their published operating or non-operating limits.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2007.

®

Server Board S5000PAL and the Intel® Server Board S5000XAL may contain design defects or

Revision 1.4

iv

Intel order number: D31979-007

Page 4

Intel® Server Board S5000PAL / S5000XAL TPS Table of Contents

Table of Contents

1. Introduction ........................................................................................................................12

1.1 Chapter Outline...................................................................................................... 12

1.2 Server Board Use Disclaimer ................................................................................ 12

2. Product Overview...............................................................................................................13

2.1 Intel® Server Board S5000PAL / S5000XAL Feature Set ...................................... 13

2.2 Server Board Layout.............................................................................................. 14

2.2.1 Connector and Component Locations ................................................................... 15

2.2.2 Light Guided Diagnostic LED Locations ................................................................ 17

2.2.3 External I/O Connector Locations.......................................................................... 18

2.2.4 Server Board Mechanical Drawings ...................................................................... 19

3. Functional Architecture.....................................................................................................24

3.1 Intel® 5000P and 5000X Memory Controller Hubs (MCH) ..................................... 25

3.1.1 System Bus Interface............................................................................................. 25

3.1.2 Processor Support ................................................................................................. 25

3.1.3 Memory Sub-system.............................................................................................. 27

3.1.4 Snoop Filter (5000X MCH only)............................................................................. 33

3.2 ESB-2 IO Controller ............................................................................................... 33

3.2.1 PCI Sub-system..................................................................................................... 34

3.2.2 Serial ATA Support ................................................................................................ 36

3.2.3 Parallel ATA (PATA) Support ................................................................................ 37

3.2.4 USB 2.0 Support.................................................................................................... 37

3.3 Video Support ........................................................................................................ 37

3.4 Network Interface Controller (NIC) ........................................................................ 39

3.4.1 Intel® I/O Acceleration Technology ........................................................................ 39

3.4.2 MAC Address Definition......................................................................................... 39

3.5 Super I/O ...............................................................................................................40

4. Platform Management........................................................................................................43

5. Connector / Header Locations and Pin-outs....................................................................44

5.1 Board Connector Information................................................................................. 44

5.2 Power Connectors ................................................................................................. 45

5.3 System Management Headers ..............................................................................46

5.3.1 Intel® Remote Management Module (RMM) Connector ........................................ 46

5.3.2 Intel® RMM NIC Connector .................................................................................... 47

5.3.3 LCP/AUX IPMB Header......................................................................................... 48

5.3.4 IPMB Header ......................................................................................................... 48

Revision 1.4

Intel order number: D31979-007

v

Page 5

Table of Contents Intel® Server Board S5000PAL / S5000XAL TPS

5.4 Riser Card Slots..................................................................................................... 48

5.5 SSI Control Panel Connector................................................................................. 53

5.6 Bridge Board Connector ........................................................................................ 53

5.7 I/O Connector Pin-out Definition ............................................................................ 55

5.7.1 VGA Connector...................................................................................................... 55

5.7.2 NIC Connectors ..................................................................................................... 55

5.7.3 IDE Connector ....................................................................................................... 56

5.7.4 Intel® I/O Expansion Module Connector ................................................................56

5.7.5 SATA Connectors .................................................................................................. 57

5.7.6 Serial Port Connectors........................................................................................... 58

5.7.7 Keyboard and Mouse Connector ........................................................................... 58

5.7.8 USB 2.0 Connectors .............................................................................................. 59

5.8 Fan Headers .......................................................................................................... 60

6. Jumper Block Settings ......................................................................................................61

6.1 Recovery Jumper Blocks ....................................................................................... 61

6.1.1 CMOS Clear and Password Reset Usage Procedure ...........................................62

6.1.2 BMC Force Update Procedure .............................................................................. 62

6.2 BIOS Select Jumper .............................................................................................. 63

6.3 External RJ45 Serial Port Jumper Block................................................................ 64

7. Light Guided Diagnostics..................................................................................................65

7.1 5-Volt Standby LED ............................................................................................... 65

7.2 System ID LED and System Status LED ............................................................... 66

7.2.1 System Status LED – BMC Initialization................................................................ 67

7.3 DIMM Fault LEDs .................................................................................................. 68

7.4 Processor Fault LED.............................................................................................. 68

7.5 Post Code Diagnostic LEDs ..................................................................................69

8. Power and Environmental Specifications........................................................................70

8.1 Intel® Server Board S5000PAL / S5000XAL Design Specifications ......................70

8.2 Server Board Power Requirements ....................................................................... 71

8.2.1 Processor Power Support...................................................................................... 71

8.2.2 Power Supply Output Requirements ..................................................................... 72

8.2.3 Turn On No Load Operation .................................................................................. 72

8.2.4 Grounding .............................................................................................................. 73

8.2.5 Standby Outputs .................................................................................................... 73

8.2.6 Remote Sense ....................................................................................................... 73

8.2.7 Voltage Regulation ................................................................................................73

8.2.8 Dynamic Loading ................................................................................................... 74

8.2.9 Capacitive Loading ................................................................................................ 74

Revision 1.4

vi

Intel order number: D31979-007

Page 6

Intel® Server Board S5000PAL / S5000XAL TPS Table of Contents

8.2.10 Closed-Loop Stability.............................................................................................74

8.2.11 Common Mode Noise ............................................................................................ 74

8.2.12 Ripple / Noise ........................................................................................................75

8.2.13 Soft Starting ........................................................................................................... 75

8.2.14 Timing Requirements............................................................................................. 75

8.2.15 Residual Voltage Immunity in Standby Mode ........................................................ 78

9. Regulatory and Certification Information.........................................................................79

9.1 Product Regulatory Compliance ............................................................................ 79

9.1.1 Product Safety & Electromagnetic (EMC) Compliance.......................................... 79

9.2 Electromagnetic Compatibility Notices ..................................................................80

9.2.1 FCC Verification Statement (USA) ........................................................................ 80

9.2.2 ICES-003 (Canada) ............................................................................................... 80

9.2.3 Europe (CE Declaration of Conformity) ................................................................. 80

9.2.4 BSMI (Taiwan) ....................................................................................................... 81

9.2.5 RRL (Korea)........................................................................................................... 81

9.3 Product Ecology Compliance................................................................................. 82

9.4 Other Markings ...................................................................................................... 83

Appendix A: Integration and Usage Tips................................................................................84

Appendix B: BMC Sensor Tables............................................................................................85

Appendix C: POST Code Diagnostic LED Decoder.............................................................101

Appendix D: POST Error Messages and Handling ..............................................................105

Appendix E: Supported Intel® Server Chassis.....................................................................108

Glossary...................................................................................................................................111

Reference Documents............................................................................................................114

Revision 1.4

Intel order number: D31979-007

vii

Page 7

List of Figures Intel® Server Board S5000PAL / S5000XAL TPS

List of Figures

Figure 1. Components & Connector Location Diagram .............................................................. 16

Figure 2. Light Guided Diagnostic LED Location Diagram .........................................................17

Figure 3. Intel

Figure 4. Intel

Figure 5. Intel

Figure 6. Intel

Figure 7. Intel

Figure 8. Intel

Figure 9. Server Board Functional Block Diagram...................................................................... 24

Figure 10. CEK Processor Mounting ..........................................................................................27

Figure 11. Memory Layout .......................................................................................................... 27

Figure 12. Recommended Minimum Two DIMM Memory Configuration .................................... 30

®

Server Board S5000PAL / S5000XAL ATX I/O Layout ...................................... 18

®

Server Board S5000PAL / S5000XAL – Hole and Component Positions (1 of 2)19

®

Server Board S5000PAL / S5000XAL – Hole and Component Positions (2 of 2)20

®

Server Board S5000PAL / S5000XAL – Restricted Areas on Side 1 ................. 21

®

Server Board S5000PAL / S5000XAL – Restricted Areas on Side 2 ................. 22

®

Server Board S5000PAL / S5000XAL - Primary Side Duct and VR Restrictions23

Figure 13. Recommended Four DIMM Configuration ................................................................. 31

Figure 14. Single Branch Mode Sparing DIMM Configuration .................................................... 32

Figure 15. Serial Port Configuration Jumper Location ................................................................ 41

Figure 16. SMBUS Block Diagram.............................................................................................. 43

Figure 17. Recovery Jumper Blocks (J1D1, J1D2, J1D3) ......................................................... 61

Figure 18. BIOS Select Jumper (J3H1) ......................................................................................63

Figure 19. External RJ45 Serial Port Configuration Jumper ....................................................... 64

Figure 20. 5V Standby Status LED Location ..............................................................................65

Figure 21. System ID LED and System Status LED Locations................................................... 66

Figure 22. DIMM Fault LED Locations........................................................................................ 68

Figure 23. Processor Fault LED Location ................................................................................... 68

Figure 24. POST Code Diagnostic LED Location ....................................................................... 69

Figure 25. Power Distribution Block Diagram ............................................................................. 71

Figure 26. Output Voltage Timing ............................................................................................... 76

Figure 27. Turn On/Off Timing (Power Supply Signals).............................................................. 77

Figure 28. Diagnostic LED Placement Diagram .......................................................................101

Figure 29. 1U – Intel

Figure 30. 1U – Intel

Figure 31. 2U – Intel

®

Server Chassis SR1500 Overview ........................................................108

®

Server Chassis SR1550 Overview ........................................................109

®

Server Chassis SR2500 Overview ........................................................110

Revision 1.4

viii

Intel order number: D31979-007

Page 8

Intel® Server Board S5000PAL / S5000XAL TPS List of Tables

List of Tables

Table 1. Processor Support Matrix .............................................................................................26

Table 2. I

Table 3. Maximum 8 DIMM System Memory Configuration – x8 Single Rank ...........................28

Table 4. Maximum 8 DIMM System Memory Configuration – x4 Dual Rank .............................. 28

Table 5. PCI Bus Segment Characteristics................................................................................. 34

Table 6. Video Modes ................................................................................................................. 38

Table 7. NIC2 Status LED........................................................................................................... 39

Table 8. Serial A Header Pin-out ................................................................................................40

Table 9. Rear Serial B Port Adapter Pin-out ............................................................................... 41

Table 10. Board Connector Matrix .............................................................................................. 44

Table 11. Power Connector Pin-out (J3K3) ................................................................................ 45

Table 12. 12V Power Connector Pin-out (J3K4)......................................................................... 45

2

C Addresses for Memory Module SMB .....................................................................28

Table 13. Power Supply Signal Connector Pin-out (J1K1) ......................................................... 45

Table 14. Intel

Table 15. 30-pin Intel

®

RMM Connector Pin-out (J1C5) ........................................................................ 46

®

RMM NIC Module Connector Pin-out (J1B2) .........................................47

Table 16. LPC/AUX IPMB Header Pin-out (J1C2)...................................................................... 48

Table 17. IPMB Header Pin-out (J1C3) ...................................................................................... 48

Table 18. Low-profile Riser Slot Pin-out (J5B1)..........................................................................48

Table 19. Full-height Riser Slot Pin-out (J4F1)...........................................................................49

Table 20. Front Panel SSI Standard 24-pin Connector Pin-out (J3H2) ...................................... 53

Table 21. 120-pin Bridgeboard Connector Pin-out (J4G1) .........................................................53

Table 22. VGA Connector Pin-out (J6A1)................................................................................... 55

Table 23. RJ-45 10/100/1000 NIC Connector Pin-out (JA8A1, JA8A2)...................................... 55

Table 24. 44-pin IDE Connector Pin-out (J3G1) ......................................................................... 56

Table 25. 50-pin Intel

®

I/O Expansion Module Connector Pin-out (J3B1)................................... 57

Table 26. SATA Connector Pin-out (J1H1, J1G2, J1G1, J1F2, J1E3) ....................................... 57

Table 27. External RJ-45 Serial ‘B’ Port Pin-out (J9A2) .............................................................58

Table 28. Internal 9-pin Serial ‘A’ Header Pin-out (J1B1) ........................................................... 58

Table 29. Stacked PS/2 Keyboard and Mouse Port Pin-out (J9A1) ........................................... 58

Table 30. External USB Connector Pin-out (J5A1, J6A2)........................................................... 59

Table 31. Internal USB Connector Pin-out (J1J1)....................................................................... 59

Table 32. SSI Fan Connector Pin-out (J9K1,J5K1,J3K1,J3K2,J7A2,J7A1) ...............................60

Table 33. Recovery Jumpers (J1D1, J1D2, J1D3) ..................................................................... 61

Table 34: Server Board Design Specifications ...........................................................................70

Table 35. Dual-Core Intel® Xeon

Revision 1.4

®

Processor 5000 Sequence TDP Guidelines per processor .. 71

Intel order number: D31979-007

ix

Page 9

List of Tables Intel® Server Board S5000PAL / S5000XAL TPS

Table 36. 600W Load Ratings ....................................................................................................72

Table 37: No load operating range ...........................................................................................72

Table 38. Voltage Regulation Limits ........................................................................................... 73

Table 39. Transient Load Requirements..................................................................................... 74

Table 40. Capacitive Loading Conditions ...................................................................................74

Table 41. Ripple and Noise......................................................................................................... 75

Table 42. Output Voltage Timing ................................................................................................ 76

Table 43. Turn On/Off Timing ..................................................................................................... 77

Table 44. BMC Sensors..............................................................................................................87

Table 45: POST Progress Code LED Example ........................................................................101

Table 46. Diagnostic LED POST Code Decoder ...................................................................... 102

Table 47. POST Error Messages and Handling........................................................................ 105

Table 48. POST Error Beep Codes ..........................................................................................107

Table 49. BMC Beep Codes ..................................................................................................... 107

Revision 1.4

x

Intel order number: D31979-007

Page 10

Intel® Server Board S5000PAL / S5000XAL TPS List of Tables

< This page intentionally left blank. >

Revision 1.4

Intel order number: D31979-007

xi

Page 11

Introduction Intel® Server Board S5000PAL / S5000XAL TPS

1. Introduction

This Technical Product Specification (TPS) provides board specific information detailing the features,

functionality, and high level architecture of the Intel

S5000XAL. The Intel

for more in depth detail of various board sub-systems including chipset, BIOS, System Management, and

System Management software.

In addition, design level information for specific sub-systems can be obtained by ordering the External

Product Specifications (EPS) or External Design Specifications (EDS) for a given sub-system. EPS and

EDS documents are not publicly available. They are only made available under NDA with Intel and must

be ordered through your local Intel representative.

The Intel

cause the product to deviate from published specifications. Refer to the Intel® Server Board

S5000PAL/XAL Specification Update for published errata.

®

Server Board S5000PAL/XAL may contain design defects or errors known as errata which may

®

S5000 Series Chipsets Server Board Family Datasheet should also be referenced

®

Server Board S5000PAL and Intel® Server Board

1.1 Chapter Outline

This document is divided into the following chapters

• Chapter 1 – Introduction

• Chapter 2 – Server Board Overview

• Chapter 3 – Functional Architecture

• Chapter 4 – Platform Management

• Chapter 5 – Connector & Header Location and Pin-out

• Chapter 6 – Configuration Jumpers

• Chapter 7 – Light Guided Diagnostics

• Chapter 8 – Power and Environmental Specifications

• Chapter 9 – Regulatory and Certification Information

• Appendix A – Integration and Usage Tips

• Appendix B – BMC Sensor Tables

• Appendix C – POST Code Diagnostic LED Decoder

• Appendix D – Post Code Errors

• Appendix E – Supported Intel

®

Server Chassis

1.2 Server Board Use Disclaimer

Intel Corporation server boards support add-in peripherals and contain a number of high-density VLSI

and power delivery components that need adequate airflow to cool. Intel ensures through its own chassis

development and testing that when Intel server building blocks are used together, the fully integrated

system will meet the intended thermal requirements of these components. It is the responsibility of the

system integrator who chooses not to use Intel developed server building blocks to consult vendor

datasheets and operating parameters to determine the amount of air flow required for their specific

application and environmental conditions. Intel Corporation cannot be held responsible if components fail

or the server board does not operate correctly when used outside any of their published operating or nonoperating limits.

Revision 1.4

12

Intel order number: D31979-007

Page 12

Intel® Server Board S5000PAL / S5000XAL TPS Product Overview

2. Product Overview

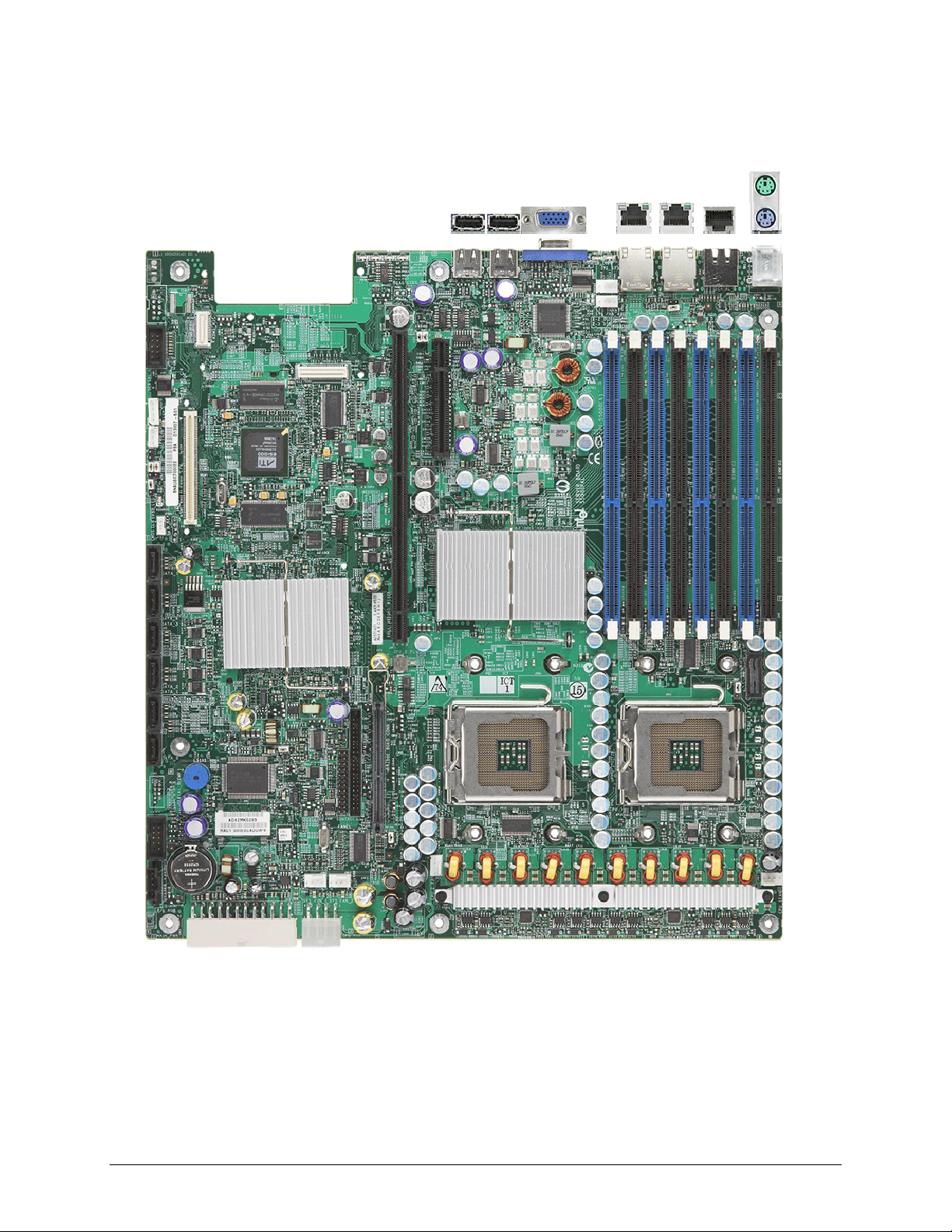

The Intel® Server Board S5000PAL and Intel® Server Board S5000XAL are monolithic printed circuit

boards with features that were designed to support the high-density 1U and 2U server markets.

2.1 Intel® Server Board S5000PAL / S5000XAL Feature Set

Feature Description

Processors 771-pin LGA sockets supporting 1 or 2 Dual-Core Intel® Xeon® processors 5000 sequence,

Memory 8 Keyed DIMM slots supporting fully buffered DIMM technology (FBDIMM) memory. 240-pin

Chipset Intel® 5000 Chipset Family which includes the following components:

On-board

Connectors/Headers

Add-in PCI, PCI-X*, PCI

Express* Cards

On-board Video ATI* ES1000 video controller with 16MB DDR SDRAM

On-board Hard Drive

Controller

LAN Two 10/100/1000 Intel® 82563EB PHYs supporting Intel® I/O Acceleration Technology

System Fans Six 4-pin Fan Headers supporting two processor fans, and four system fans

System Management Support for Intel® System Management Software

with system bus speeds of 667 MHz, 1066 MHz, or 1333 MHz

DDR2-533 and DDR2-677 FBDIMMs must be used.

®

Intel

5000P Memory Controller Hub or Intel® 5000X Memory Controller Hub

®

Intel

6321ESB I/O Controller Hub1

Note: Intel will only make available an OEM SKU of this server board using the Intel® 5000X

Memory Controller Hub.

External connections:

Stacked PS/2* ports for keyboard and mouse

RJ45 Serial B port

Two RJ45 NIC connectors for 10/100/1000 Mb connections

Two USB 2.0 ports

Video Connector

Internal connectors/headers:

One USB port header, capable of providing two USB 2.0 ports

One DH10 Serial A header

Six SATA ports via the ESB-2 supporting 3Gb/s and integrated SW RAID 0/1/10 support

One 44pin (power + I/O) ATA/100 connector for optical drive support

One Intel® Remote Management Module (Intel® RMM) connector (Intel® RMM use is

optional)

One Intel

SSI-compliant 24-pin control panel header

SSI-compliant 24-pin main power connector, supporting the ATX-12V standard on the first

20 pins

8-Pin +12V Processor Power Connector

®

I/O Expansion Module Connector supporting:

Dual GB NIC Intel® I/O Expansion Module (Optional)

External SAS Intel® I/O Expansion Module (Optional)

Infiniband* I/O Expansion Module (Optional)

One low profile riser slot supporting 1U or 2U PCIe* riser cards

One full height riser slot supporting 1U or 2U PCI-X* and PCIe* riser cards

Six ESB-2 3Gb/s SATA ports.

Intel® Embedded Server RAID Technology II with SW RAID levels 0/1/10.

Optional support for SW RAID 5 with activation key.2

1

For the remainder of this document, the Intel® 6321ESB I/O Controller Hub will be refferred to as ESB-2.

2

Onboard SATA SW RAID 5 support provided as a post-launch product feature.

Revision 1.4

Intel order number: D31979-007

13

Page 13

Product Overview Intel® Server Board S5000PAL / S5000XAL TPS

2.2 Server Board Layout

Revision 1.4

14

Intel order number: D31979-007

Page 14

Intel® Server Board S5000PAL / S5000XAL TPS Product Overview

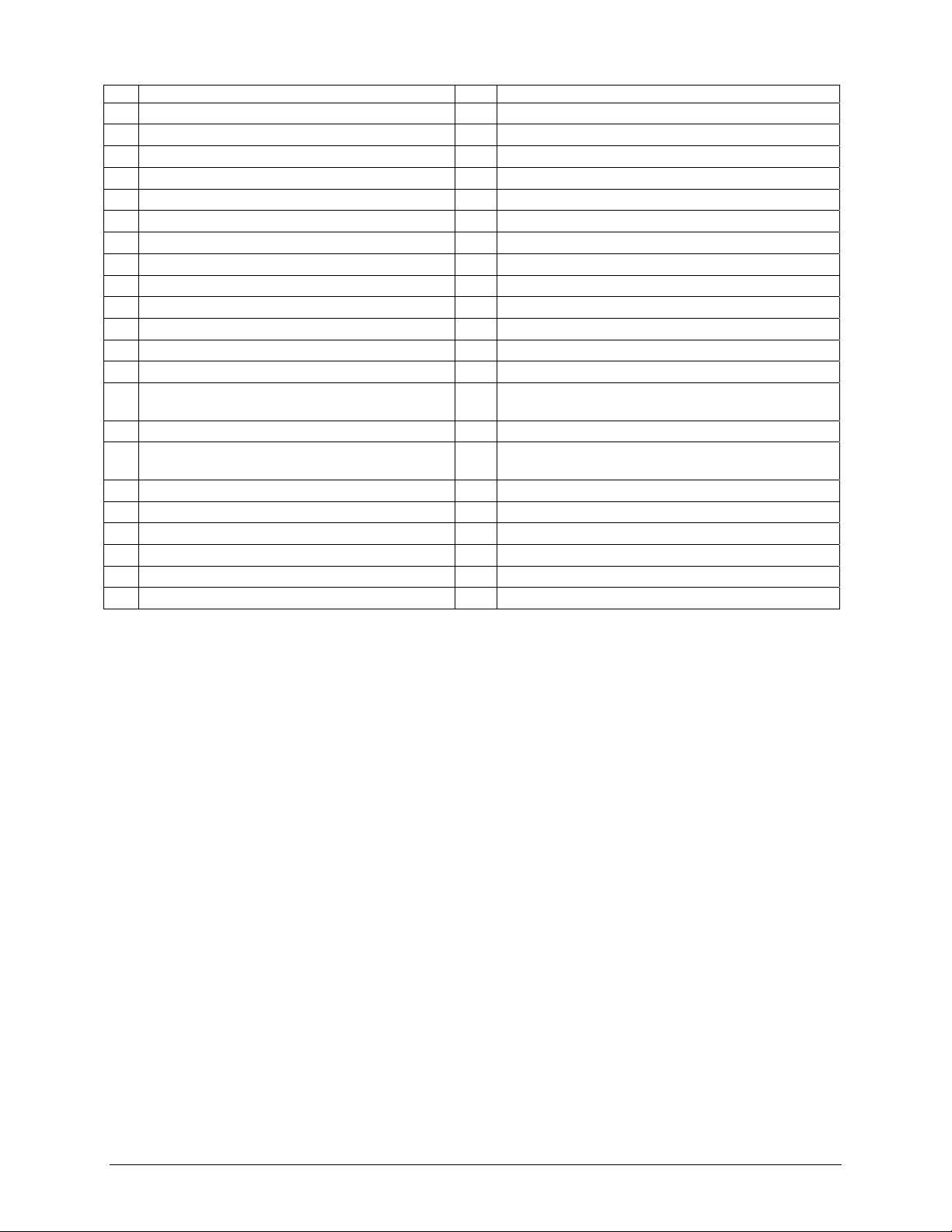

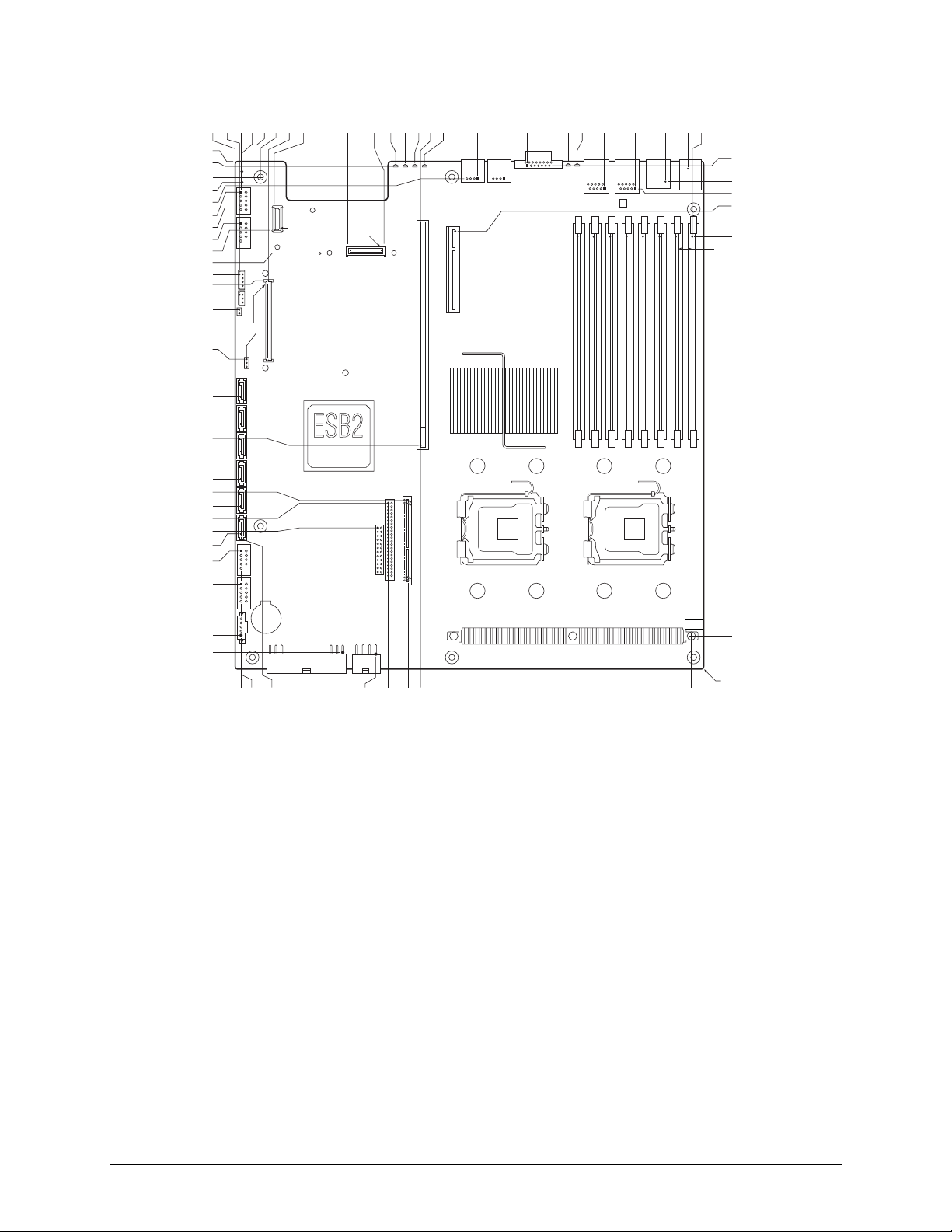

2.2.1 Connector and Component Locations

The following figure shows the board layout of the server board. Each connector and major component is

identified by a number or letter, and a description is given below the figure.

QQ

PP

OO

NN

LL

KK

JJ

HH

GG

FF

EE

DD

CC

BB

AA

II

Z

MM

B

A

C

F

ED

G

I

H

J

K

L

M

N

O

P

Q

Y

X

W

V UST

R

TP02071

Revision 1.4

15

Intel order number: D31979-007

Page 15

Product Overview Intel® Server Board S5000PAL / S5000XAL TPS

Description Description

A BIOS Bank Select Jumper V System Fan #2 Header

B Intel® ESB-2 IO Controller Hub W CPU Power Connector

C IO Module Option Connector X Main Power Connector

D POST Code Diagnostic LEDs Y Battery

E Intel® Adaptive Slot – Full Height Z Power Supply Management Connector

F PCI Express* Riser Slot – Low Profile AA Dual Port USB 2.0 Header

G System Identification LED - Blue BB System Fan #1 Header

H External IO Connectors CC SSI 24-pin Control Panel Header

I Status LED – Green / Amber DD SATA 0

J Serial ‘B’ Port Configuration Jumper EE SATA 1

K System Fan #4 Header FF SATA 2

L System Fan #3 Header GG SATA 3

M FBDIMM Slots HH SATA 4

N Intel® 5000P Memory Controller Hub (MCH) or

O CPU #1 Connector JJ SATA SW RAID 5 Activation Key Connector

P CPU #2 Connector KK Intel® Remote Management Module (RMM)

Q CPU #1 Fan Header LL System Recovery Jumper Block

R Voltage Regulator Heat Sink MM Chassis Intrusion Switch Header

S CPU #2 Fan Header NN 3-pin IPMB Header

T Bridge Board Connector OO Intel® Local Control Panel Header

U ATA-100 Optical Drive Connector (Power+IO) PP Serial ‘A’ Header

QQ Intel® RMM NIC Connector

®

Intel

5000X Memory Controller Hub (MCH)

II SATA 5

Connector

Figure 1. Components & Connector Location Diagram

Revision 1.4

16

Intel order number: D31979-007

Page 16

Intel® Server Board S5000PAL / S5000XAL TPS Product Overview

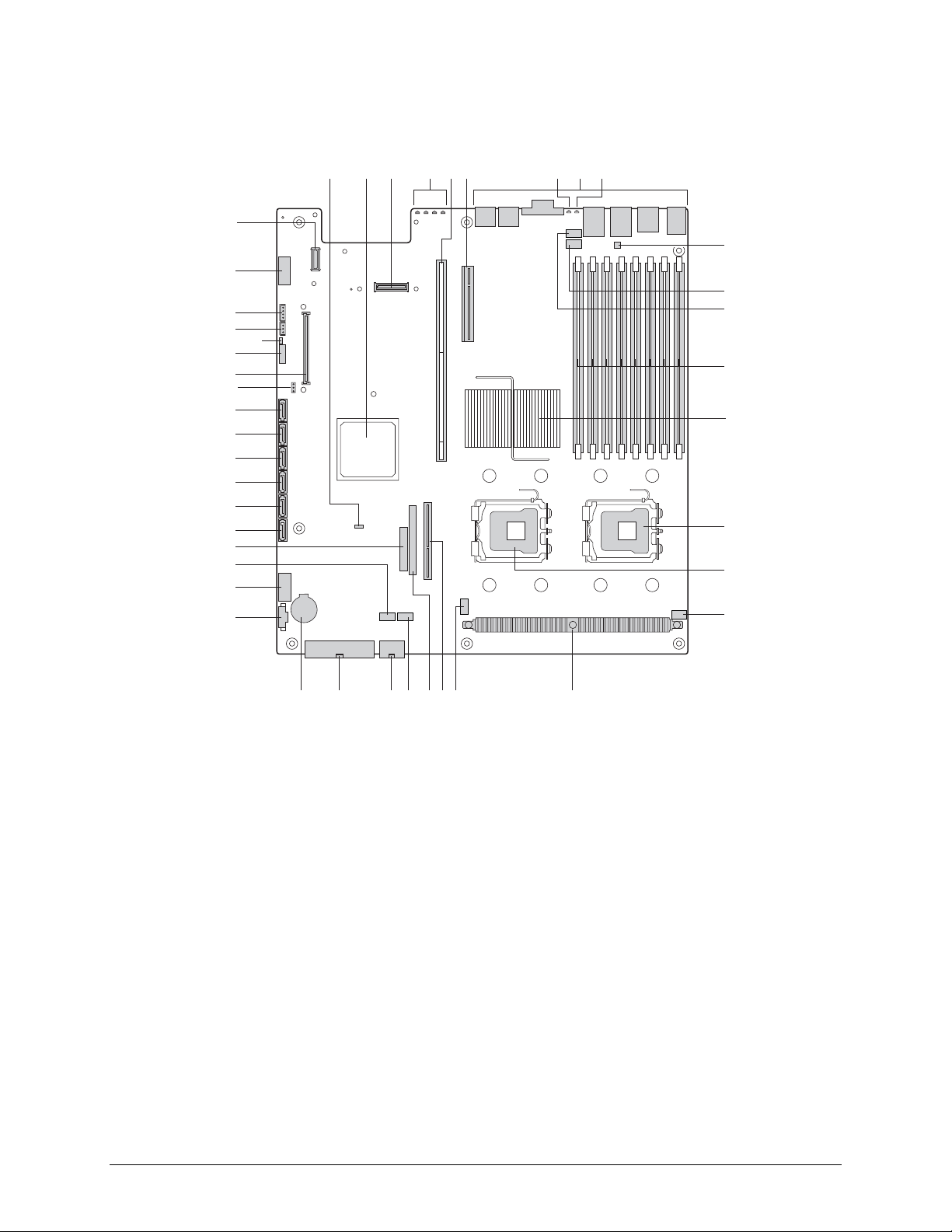

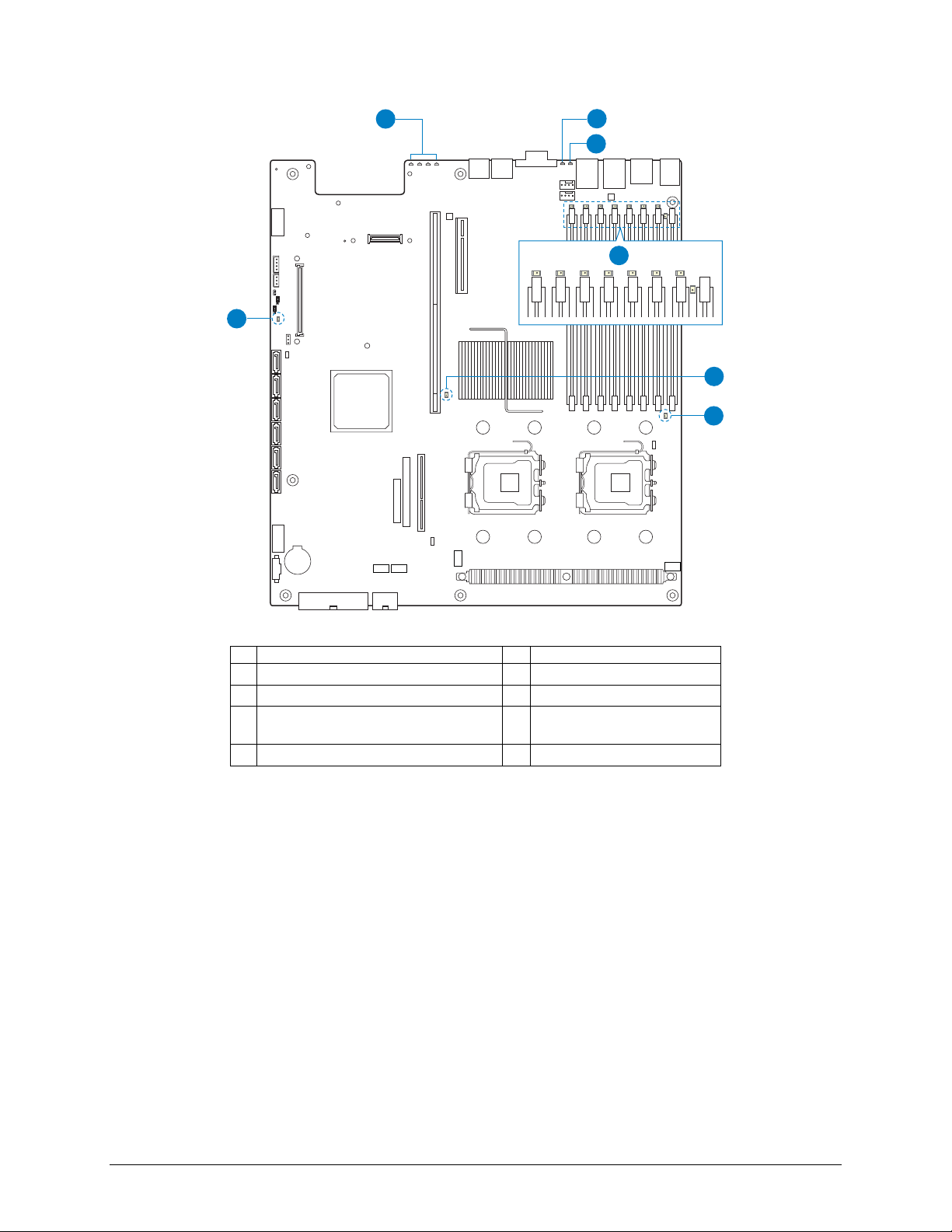

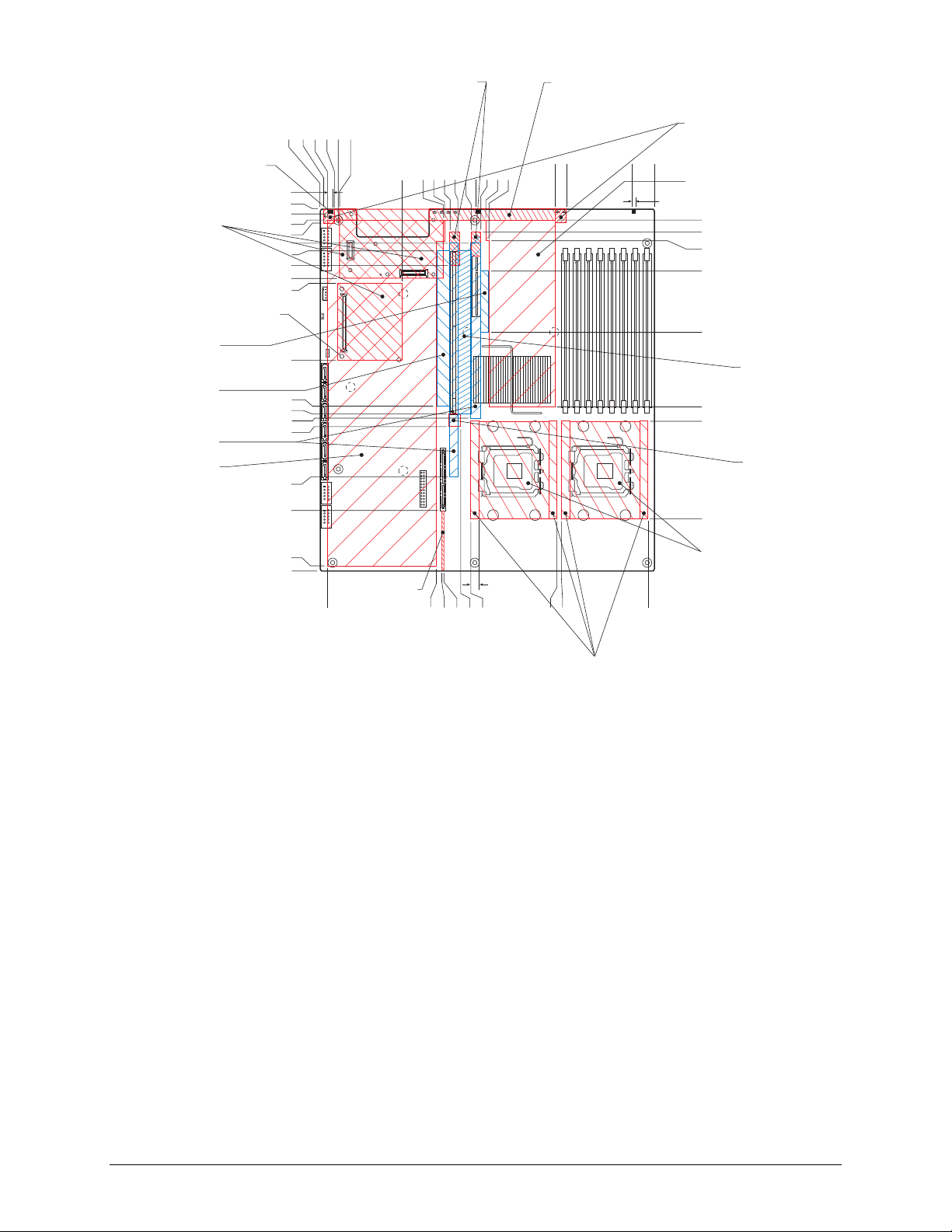

2.2.2 Light Guided Diagnostic LED Locations

A

B

C

D

LIJK NOMP

S

G

Q

E

R

F

TP02317

Description Description

A Post Code Diagnostic LEDs E CPU Fault LED

B System Identification LED – Blue F CPU Fault LED

C System Status LED – Green / Amber G 5-Volt Stand-by Present

LED

D DIMM Fault LEDs

Figure 2. Light Guided Diagnostic LED Location Diagram

Revision 1.4

Intel order number: D31979-007

17

Page 17

Product Overview Intel® Server Board S5000PAL / S5000XAL TPS

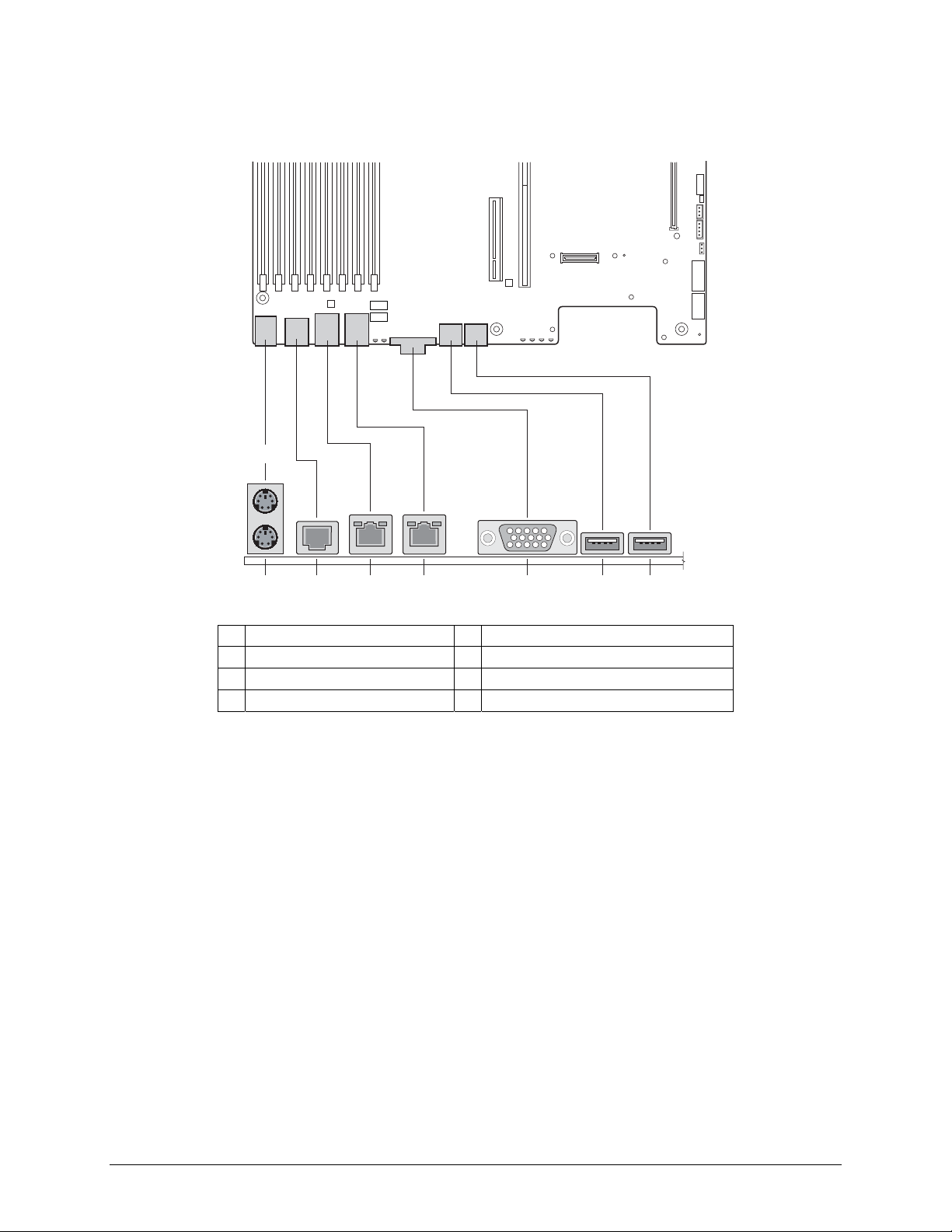

2.2.3 External I/O Connector Locations

The drawing below shows the layout of the rear I/O components for the server board.

A

FC D E G HB

TP02296

A PS/2 Mouse E NIC port 2 (1 Gb)

B PS/2 Keyboard F Video

C Serial Port B G USB port 1

D NIC port 1 (1 Gb) H USB port 2

Figure 3. Intel® Server Board S5000PAL / S5000XAL ATX I/O Layout

Revision 1.4

18

Intel order number: D31979-007

Page 18

Intel® Server Board S5000PAL / S5000XAL TPS Product Overview

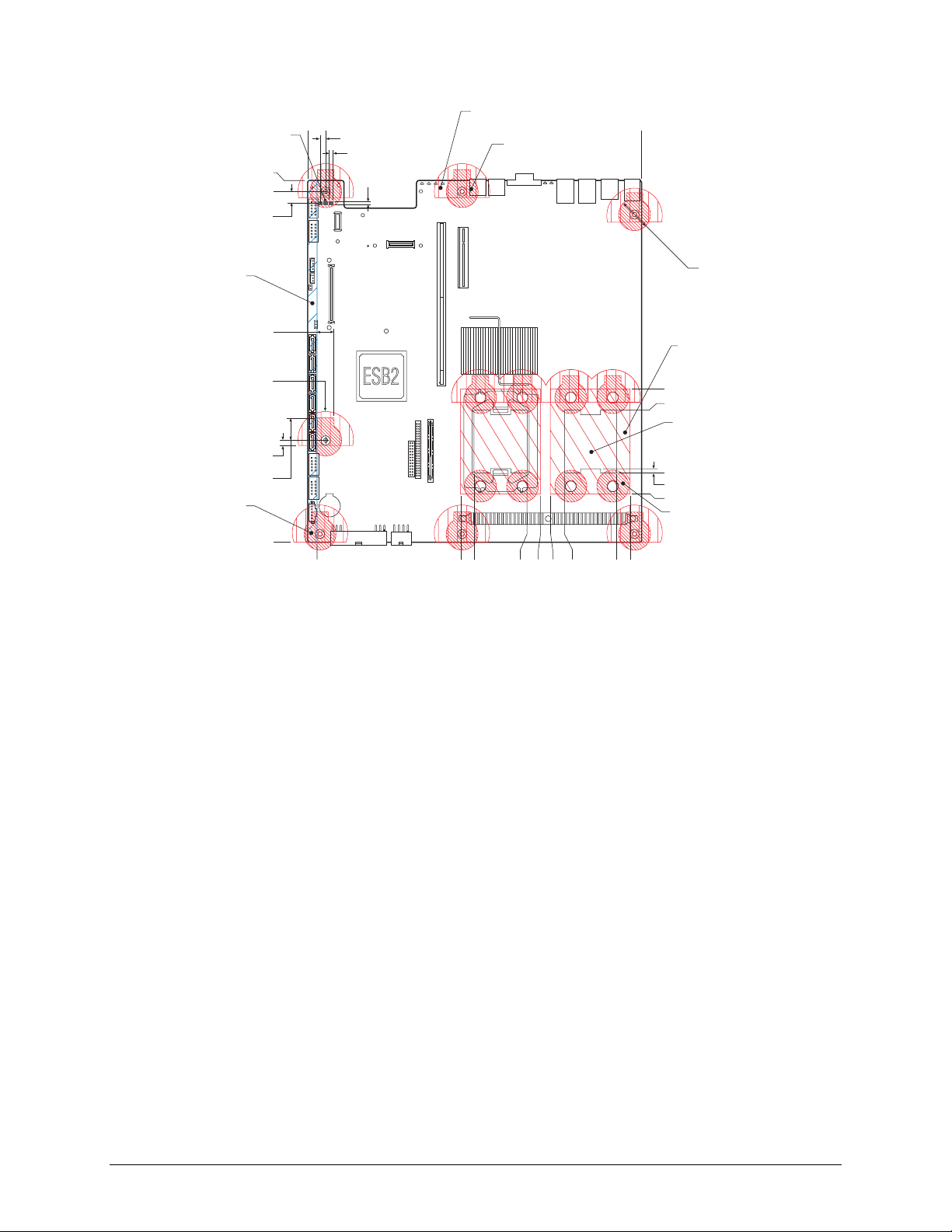

2.2.4 Server Board Mechanical Drawings

2 x 0.00 [0.000]

11.02 [0.434]

11.91 [0.469]

16.76 [0.660]

33.91 [1.335]

10.16 [0.400]

2 x 0.00 [0.000]

0.91 [0.036]

15.24 [0.600]

21.59 [0.850]

Lotes B2515BB2M

6012A0019603

45.59 [1.795]

2 x 49.35 [1.943]

62.66 [2.467]

67.31 [2.650]

Molex 22-44-7031

6012A0099701-HDR4P

Molex 22-44-7031

6012A0099701

9 x Ø 0.125 [3.18] Typ.

124.26 [4.892]

127.43 [5.017]

152.40 [6.000]

6 x Betterment

BTM-PP02.2F1611.007X

6012B0018302

227.33 [8.950]

228.60 [9.000]

Lotes B2515BB2M

6012A0019603

16.51 [0.650]

[0.129]

2 x 3.28

44.89 [1.767]

AMP 177983-5

6012A0103201

FCI 10027747-114101

0.16 [0.006]

6012A0105001

55.35

[2.179]

82.80 [3.260]

2 x 86.89 [3.421]

2 x 124.46 [4.900]

118.11 [4.650]

Molex 877715-3205

6012A0100101

Lotes AAA-PCI-033-K02

6012B0051002

196.85 [7.750]

5 x Ø 8.00 [0.315]

Silkscreen on secondary

side for spacer

Molex 43202-8927

288.29 [11.350]

6026A0027801

22.86 [0.900]

7 x Ø 3.96 [0.156]

2 x 101.60 [4.000]

4 x 187.93 [7.399]

81.28

[3.200] Typ.

3 x 312.42 [12.300]

320.04 [12.600]

Figure 4. Intel

Lotes B4L60BB2L

6012A0105401

8 x Ø 10.16 [0.400]

38.10

[1.500] Typ.

5.08 [0.200]

9.65 [0.380]

AMP 794108-1

6012A0022801

®

Server Board S5000PAL / S5000XAL – Hole and Component Positions (1 of 2)

6012A0022801

2 x 59.69 [2.350]

Molex 3930-0080

124.46 [4.900]

2 x 141.25 [5.561]

2 x 223.80 [8.811]

2 x 281.94 [11.100]

TP02316

Revision 1.4

19

Intel order number: D31979-007

Page 19

Product Overview Intel® Server Board S5000PAL / S5000XAL TPS

10.16 [0.400]

5 x 6.99 [0.275]

0.00 [0.000]

3.45 [0.136]

2 x 1.83 [0.072]

11.96 [0.471]

19.76 [0.778]

30.91 [1.217]

35.05 [1.380]

49.68 [1.956]

62.99 [2.480]

67.39 [2.653]

76.45 [3.010]

86.11 [3.390]

119.16 [4.692]

119.59 [4.708]

143.00 [5.630]

160.77 [6.330]

174.17 [6.857]

178.56 [7.030]

196.33 [7.730]

211.02 [8.308]

214.12 [8.430]

214.63 [8.450]

230.38 [9.070]

231.89 [9.130]

243.83 [9.600]

265.41 [10.449]

16.51 [0.650]

1st Pin

3 x 13.59 [0.535]

0.00 [0.000]

2 x 12.33 [0.485]

12.27 [0.483]

9.07 [0.357]

9.32 [0.367]

5.21 [0.205]

1st Pin

56.84 [2.238]

80.14 [3.155]

1st Pin

87.88 [3.460]

94.23 [3.710]

100.58 [3.960]

127.20 [5.008]

106.93 [4.210]

104.39 [4.110]

158.80 [6.252]

141.78 [5.582]

175.03 [6.891]

200.13 [7.879]

224.21 [8.827]

205.97 [8.109]

244.27 [9.617]

263.14 [10.360]

278.38 [10.960]

280.71 [11.052]

6.27 [0.247]

2.67 [0.105]

3.35 [0.132]

8.64 [0.340]

35.28 [1.389]

8 x 40.39 [1.590]

7 x 10.67 [0.420]

297.84 [11.726]

308.74 [12.155]

Figure 5. Intel

298.51 [11.752]

309.042 [12.167]

R1.52 [0.060]

12.66 [0.498]

2 x 11.93 [0.470]

6 x 12.83 [0.505]

®

Server Board S5000PAL / S5000XAL – Hole and Component Positions (2 of 2)

52.98 [2.086]

74.78 [2.944]

76.96 [3.030]

83.31 [3.280]

96.25 [3.789]

104.39 [4.110]

280.21 [11.032]

TP02292

Revision 1.4

20

Intel order number: D31979-007

Page 20

Intel® Server Board S5000PAL / S5000XAL TPS Product Overview

No Components Allowed

for Retention Pins

H < 3.5 mm [0.138"]

for Three Boards

9 x No Components 5.0 dia. on Top

No Components 3.5 dia. on Bottom

H < 12.4 mm [0.488"]

Under Riser PCIe Conn.

H < 26 mm [1.023"]

Under Riser PCI-X Conn.

H < 11.8 mm [0.465"]

Under Riser Card

H < 15.2 mm [0.600"]

Under FH PCI Option Card

2 x 5.08 [0.200]

10.16 [0.400]

3 x 5.08 [0.200]

0.00 [0.000]

2 x 3.07 [0.121]

21.23 [0.836]

28.17 [1.109]

41.96 [1.652]

53.34 [2.100]

60.15 [2.368]

130.00 [5.118]

169.98 [6.692]

177.47 [6.987]

180.92 [7.123]

188.72 [7.430]

234.75 [9.242]

264.97 [10.432]

13.18 [0.519]

9.27 [0.365]

3.28 [0.129]

16.51 [0.650]

0.00 [0.000]

0.76 [0.030]

H < 30 mm [1.181"]

PCI BKT Drop Down

96.98 [3.818]

98.88 [3.893]

101.90 [4.012]

57.89 [2.279]

109.40 [4.307]

120.85 [4.758]

125.27 [4.932]

129.69 [5.106]

134.62 [5.300]

137.72 [5.422]

H < 11.65 mm [0.459"]

Under Rear Panel Tab

198.02 [7.796]

207.98 [8.188]

267.51 [10.532]

288.29 [11.350]

3.81 [0.150]

H < 5 mm [0.196"]

PCI BKT Drop Down

H < 12.7 mm [0.499"]

Under LP PCI Option Card

0.18 [0.007]

10.80 [0.425]

18.97 [0.747]

46.76 [1.841]

102.77 [4.046]

H < 10mm [0.394"]

PCI BKT DROP DOWN

170.64 [6.718]

184.12 [7.249]

H < 3mm [0.118"]

PCI BKT DROP DOWN

273.02 [10.749]

316.00 [12.441]

320.04 [12.600]

Figure 6. Intel

94.41 [3.717]

96.57 [3.802]

111.84 [4.403]

4 x 7.62 [0.300]

120.93 [4.761]

203.48 [8.011]

199.67 [7.861]

REF ONLY

H < 11 mm [0.433"]

Under Heat Sink

282.22 [11.111]

H < 9.5 mm [0.374"]

Under Bridge Board

9.70 [0.382]

®

Server Board S5000PAL / S5000XAL – Restricted Areas on Side 1

89.36 [3.518]

REF ONLY

H < 7 mm [0.275"]

Under Heat Sink

TP02293

Revision 1.4

21

Intel order number: D31979-007

Page 21

Product Overview Intel® Server Board S5000PAL / S5000XAL TPS

3 Ground Pad

10.16 [0.400]

0.00 [0.000]

10.13 [0.399]

H < 2 mm

[0.078]

15.24 [0.600] Typ.

Ø 2.000 [50.8 mm] Typ.

5.08 [0.200] Typ.

20.32 [0.800] Typ.

Limited Height 1.27 mm

[0.05"] on Side 2

320.04 [12.600]

on Side 2

0.00 [0.000]

16.51 [0.650]

2 X 5.00 [0.197]

3 X 3.99 [0.157]

3.00 [0.118]

H < 1.47 mm [0.058"] Typ.

No Components or

Surface Layer Traces

in this Zone.

288.29 [11.350]

Ø 29.46 [1.160] Typ.

Backside Spring Area.

No Motherboard Component

Placement Allowed.

180.34 [7.100]

200.03 [7.875]

0.200" [5.08 mm Max] Keep IN

for 2U and above Platforms.

0.100" [2.54 mm Max] Keep IN

for 1U Platforms on Side 2.

257.73 [10.147]

4 x 4.45 [0.175]

276.86 [10.900]

Limited Height 1.27 mm [0.05"]

on Side 2, Dia. 29.5 mm [1.160"]

Figure 7. Intel

7.52 [0.296]

®

Server Board S5000PAL / S5000XAL – Restricted Areas on Side 2

123.47 [4.861]

136.14 [5.360]

184.40 [7.260]

218.72 [8.611]

205.99 [8.110]

197.10 [7.760]

279.68 [11.011]

266.95 [10.510]

TP02294

Revision 1.4

22

Intel order number: D31979-007

Page 22

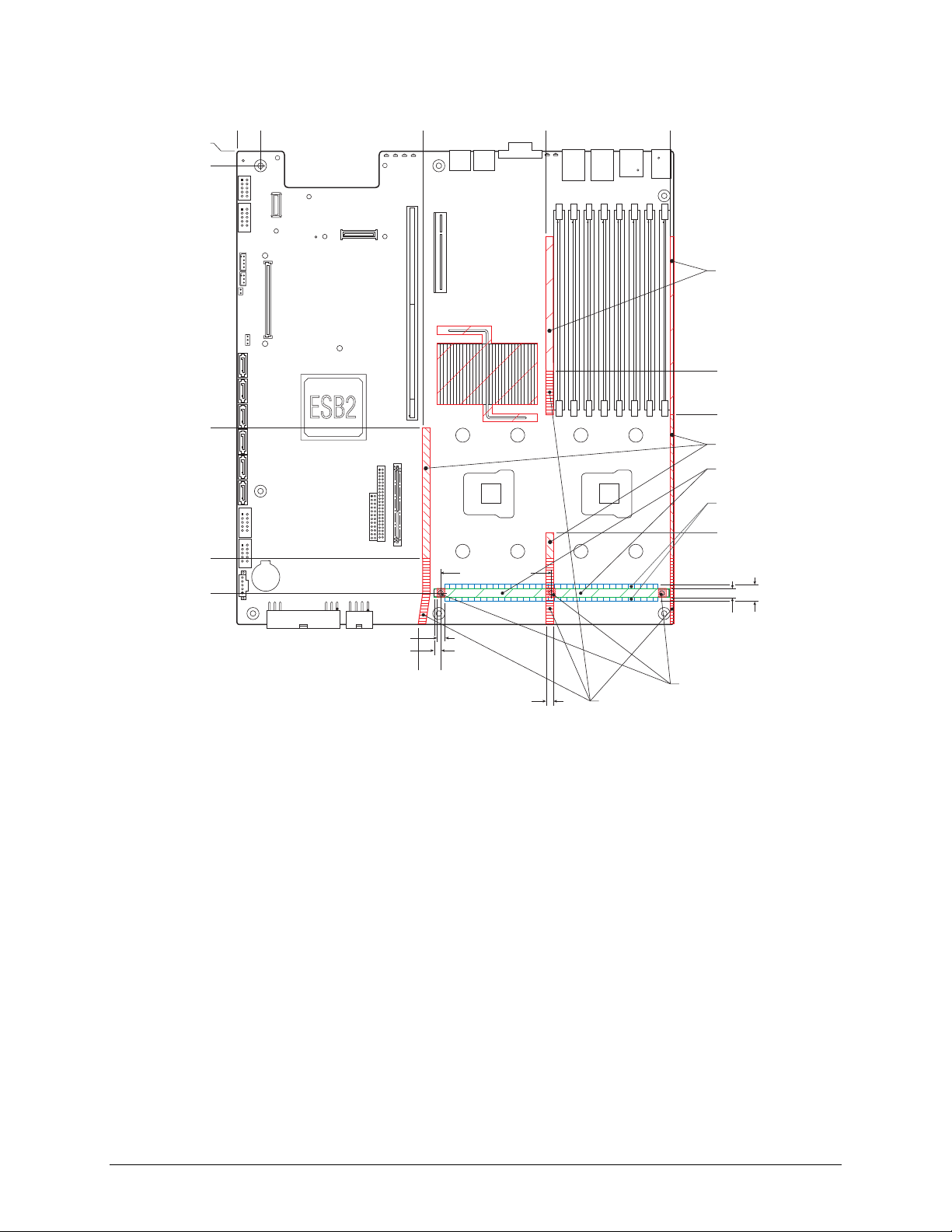

Intel® Server Board S5000PAL / S5000XAL TPS Product Overview

0.00 [0.000]

16.51 [0.650]

10.16 [0.400]

0.00 [0.000]

113.13 [4.454]

199.21 [7.843]

285.75 [11.250]

NO Components Allowed

for Duct

143.51 [5.650]

182.83 [7.198]

3 x 274.32 [10.800]

298.51 [11.753]

Figure 8. Intel

2 x 173.99 [6.850]

H < 10.0 mm [0.394"]

Under Duct

H < 0.8 mm [0.310"]

Under VR

H < 1.5 mm [0.059"]

Under VR

256.54 [10.100]

2 x 77.22 [3.040]

5.52 [0.217]

4.83 [0.190]

NO Components Allowed

5.08 [0.200]

109.86 [4.325]

125.78 [4.952]

®

Server Board S5000PAL / S5000XAL - Primary Side Duct and VR Restrictions

H < 27 mm [1.063"]

Under Duct

6.35 [0.250]

11.69 [0.460]

TP02295

Revision 1.4

23

Intel order number: D31979-007

Page 23

Functional Architecture Intel® Server Board S5000PAL / S5000XAL TPS

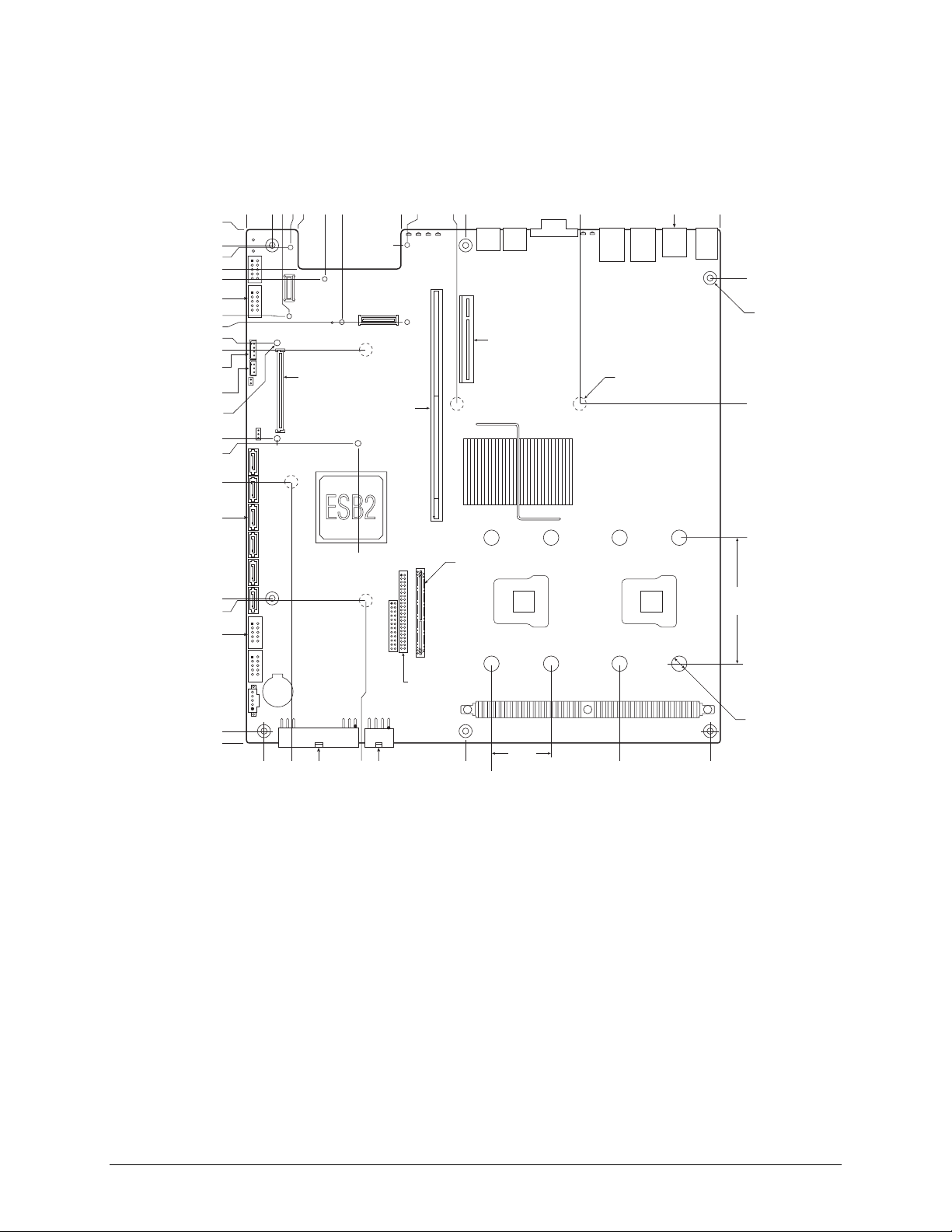

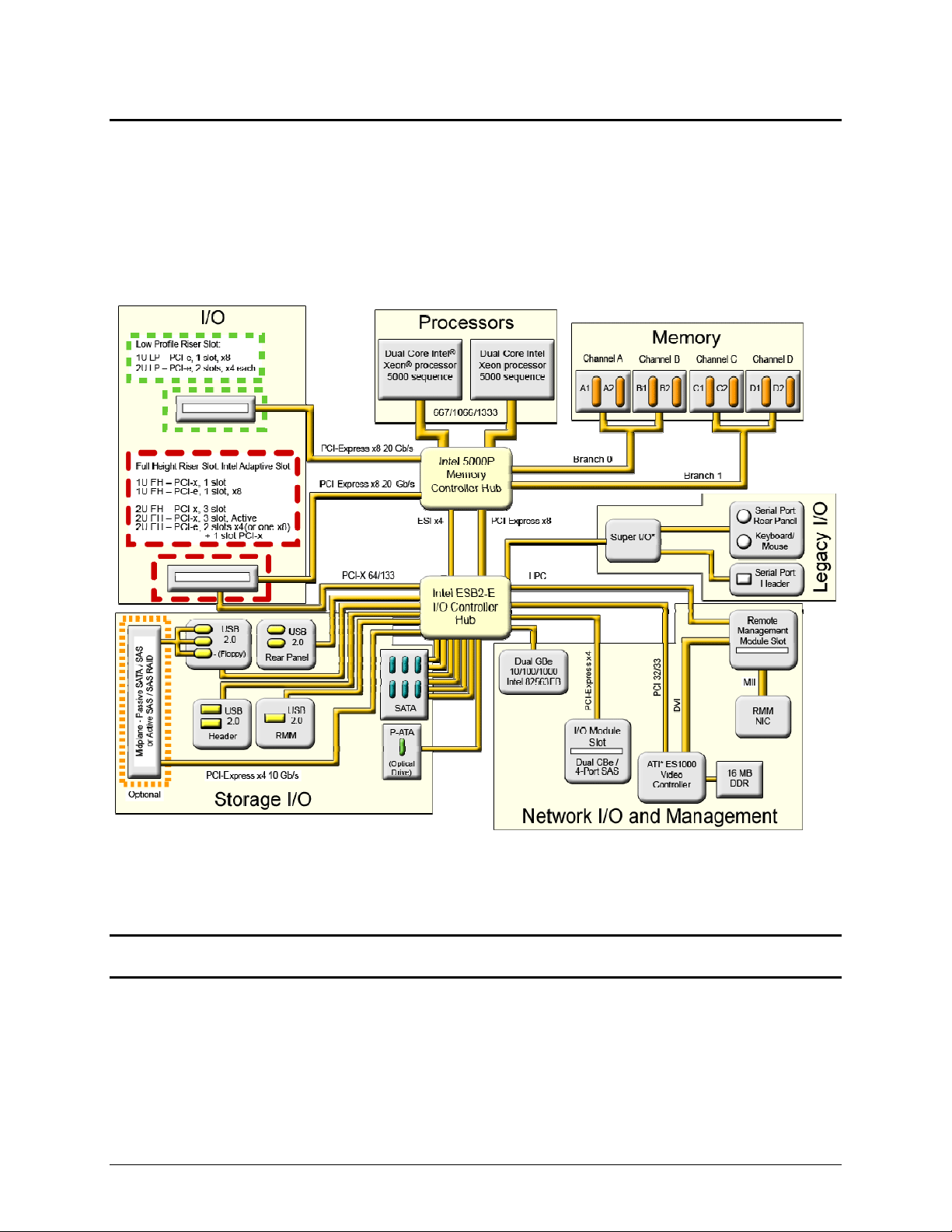

3. Functional Architecture

The architecture and design of the Intel® Server Board S5000PAL / S5000XAL is based on the Intel®

5000 Chipset Family. The chipset is designed for systems based on the Dual-Core Intel

®

Xeon®

processor 5000 sequence with system bus speeds of 667 MHz, 1066 MHz, and 1333 MHz. The chipset

is made up of two main components: the Memory Controller Hub (MCH) for the host bridge and the ESB2 I/O controller hub for the I/O subsystem. This chapter provides a high-level description of the

functionality associated with each chipset component and the architectural blocks that make up this

server board. For more in depth detail of the functionality for each of the chipset components and each of

the functional architecture blocks, see the Intel

®

S5000 Server Board Family Datasheet.

Figure 9. Server Board Functional Block Diagram

®

Note: The diagram above uses the Intel

5000P MCH as a general reference designator for both MCH

components supported on this server board.

Revision 1.4

24

Intel order number: D31979-007

Page 24

Intel® Server Board S5000PAL / S5000XAL TPS Functional Architecture

3.1 Intel® 5000P and 5000X Memory Controller Hubs (MCH)

This section will describe the general functionality of the memory controller hub as it is implemented on

this server board. Depending on the version of the server board in use, it may support either the Intel

5000P MCH or the Intel

®

5000X MCH. Features that are unique to a particular MCH will be so referenced.

®

The Memory Controller Hub (MCH) is a single 1432 pin FCBGA package which includes the following

core platform functions:

• System Bus Interface for the processor sub-system

• Memory Controller

• PCI Express* Ports including the Enterprise South Bridge Interface (ESI)

• FBD Thermal Management

• SMBUS Interface

Additional information about MCH functionality can be obtained from the Intel

Server Board Family Datasheet, the Intel

(Yellow Cover), or the Intel

®

5000X Memory Controller Hub External Design Specification (Yellow Cover).

®

5000P Memory Controller Hub External Design Specification

®

S5000 Series Chipsets

Note: Yellow Cover documents can only be obtained under NDA with Intel and ordered through an Intel

representative.

3.1.1 System Bus Interface

The MCH is configured for symmetric multi-processing across two independent front side bus interfaces

that connect to the Dual-Core Intel

uses a 64-bit wide 1066 or 1333 MHz data bus. The 1333 MHz data bus is capable of transferring data at

up to 10.66 GB/s. The MCH supports a 36-bit wide address bus, capable of addressing up to 64 GB of

memory. The MCH is the priority agent for both front side bus interfaces, and is optimized for one

processor on each bus.

®

Xeon® processors 5000 sequence. Each front side bus on the MCH

3.1.2 Processor Support

The server board supports one or two Dual-Core Intel® Xeon® processors 5000 sequence, with system

bus speeds of 667 MHz, 1066 MHz, and1333 MHz, and core frequencies starting at 2.67 GHz. Previous

generations of the Intel

Note: Only Dual-Core Intel

MHz, 1066 MHz, and1333 MHz are supported on this server board. See the following table for a list of

supported processors.

®

Xeon® processor are not supported on this server board.

®

Xeon® processors 5000 sequence, that support system bus speeds of 667

Revision 1.4

25

Intel order number: D31979-007

Page 25

Functional Architecture Intel® Server Board S5000PAL / S5000XAL TPS

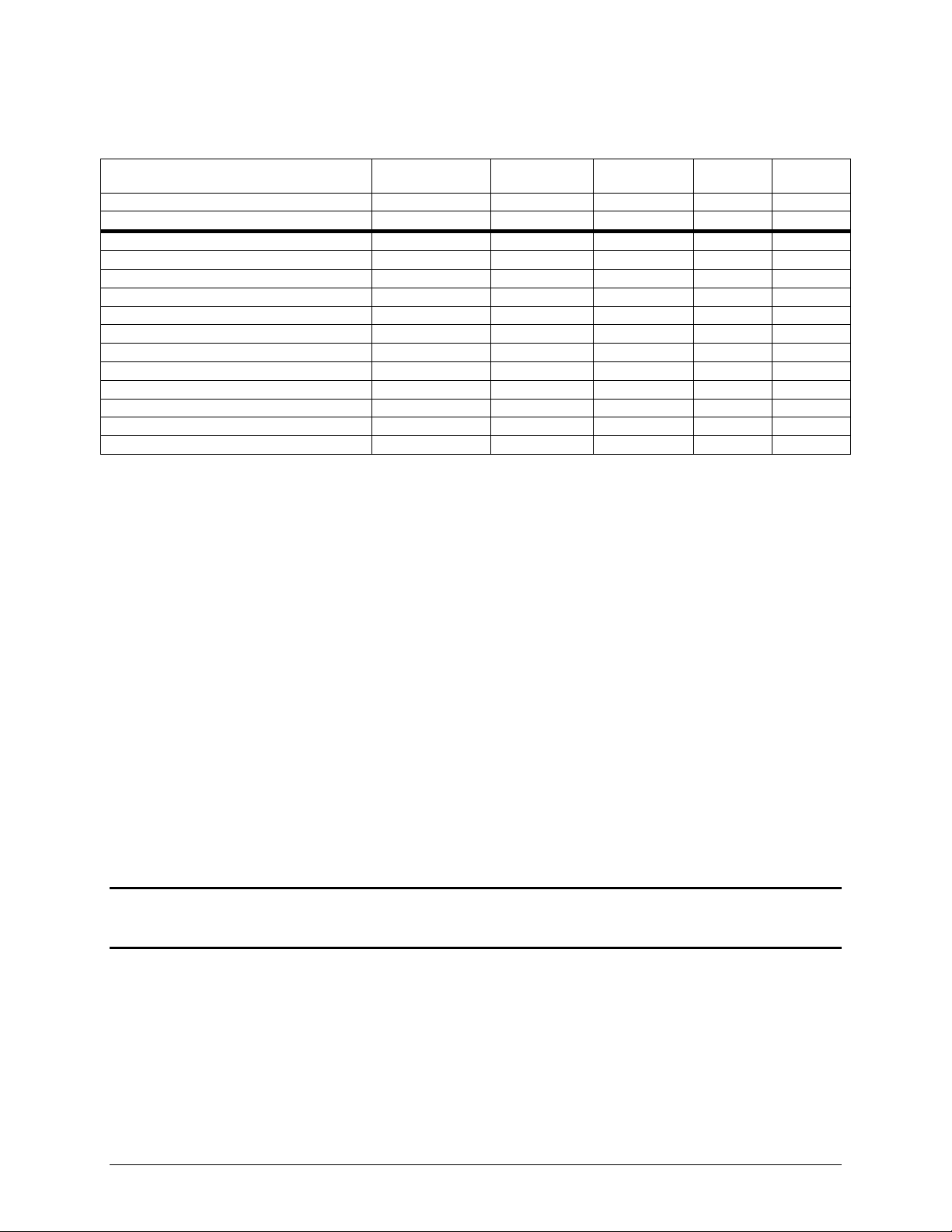

Dual-Core Intel® Xeon® processors 5000 sequence will encompass the following:

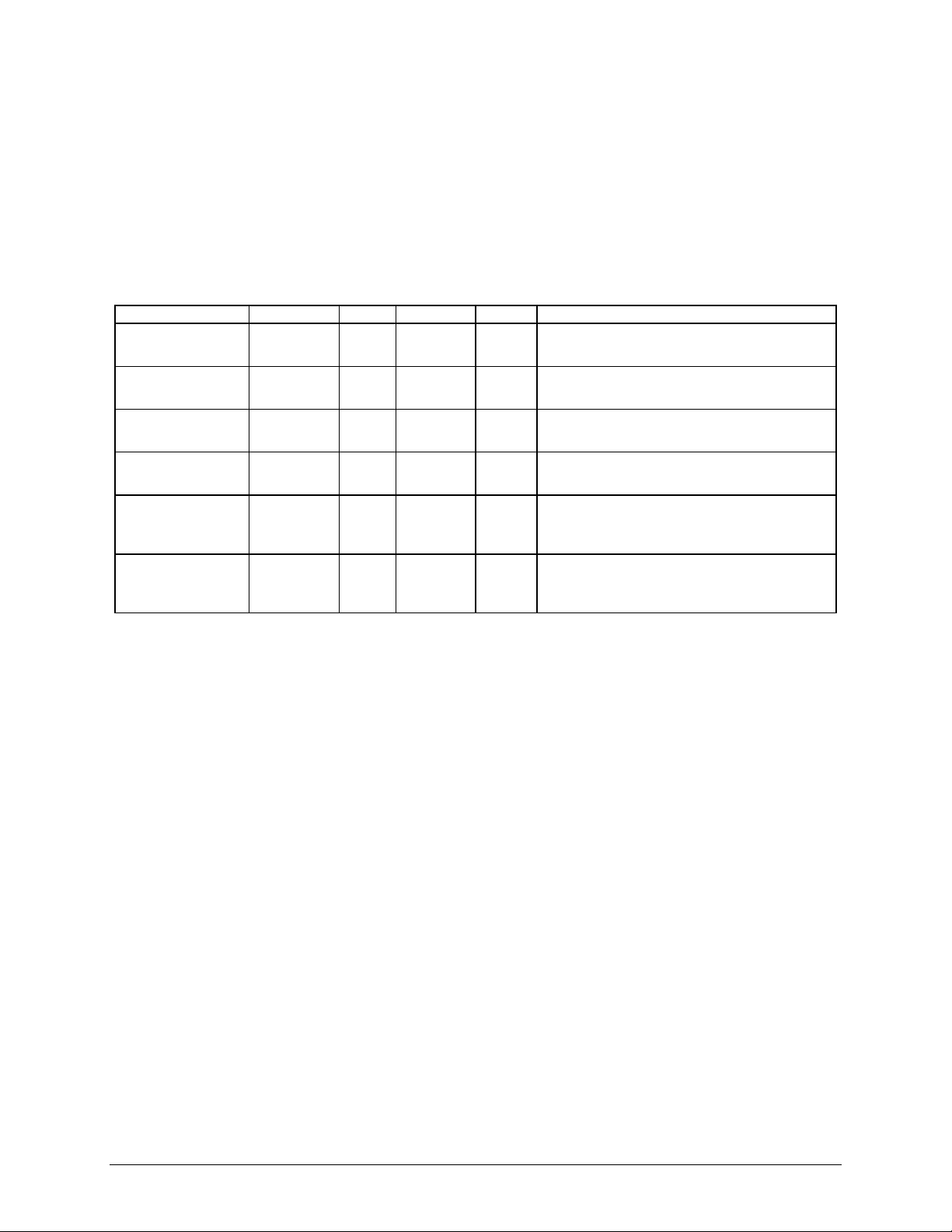

Table 1. Processor Support Matrix

Processor Family System Bus

Speed

Intel® Xeon® processor 533 MHz All No

Intel® Xeon® processor 800 MHz All No

Dual-Core Intel® Xeon® processor 5030 667 MHz 2.67 GHz 2x 2 MB 95 Yes

Dual-Core Intel® Xeon® processor 5050 667 MHz 3.0 GHz 2x 2 MB 95 Yes

Dual-Core Intel® Xeon® processor 5060 1066 MHz 3.2 GHz 2x 2 MB 130 Yes

Dual-Core Intel® Xeon® processor 5063 1066 MHz 3.2 GHz 2x 2 MB 95 Yes

Dual-Core Intel® Xeon® processor 5080 1066 MHz 3.73 GHz 2x 2 MB 130 Yes

Dual-Core Intel® Xeon® processor 5110 1066 MHz 1.60 GHz 4MB shared 65 Yes

Dual-Core Intel® Xeon® processor 5120 1066 MHz 1.87 GHz 4MB shared 65 Yes

Dual-Core Intel® Xeon® processor 5130 1333 MHz 2 GHz 4MB shared 65 Yes

Dual-Core Intel® Xeon® processor 5140 1333 MHz 2.33 GHz 4MB shared 65 Yes

Dual-Core Intel® Xeon® processor 5150 1333 MHz 2.67 GHz 4MB shared 65 Yes

Dual-Core Intel® Xeon® processor 5160 1333 MHz 3 GHz 4MB shared 80 Yes

Core

Frequency

Cache Watts Support

3.1.2.1 Processor Population Rules

When two processors are installed, both must be of identical revision, core voltage, and bus/core speed.

Mixed processor steppings is supported. However, the stepping of one processor cannot be greater than

one stepping back of the other. When only one processor is installed, it must be in the socket labeled

CPU1. The other socket must be empty.

The board is designed to provide up to 130A of current per processor. Processors with higher current

requirements are not supported.

No terminator is required in the second processor socket when using a single processor configuration.

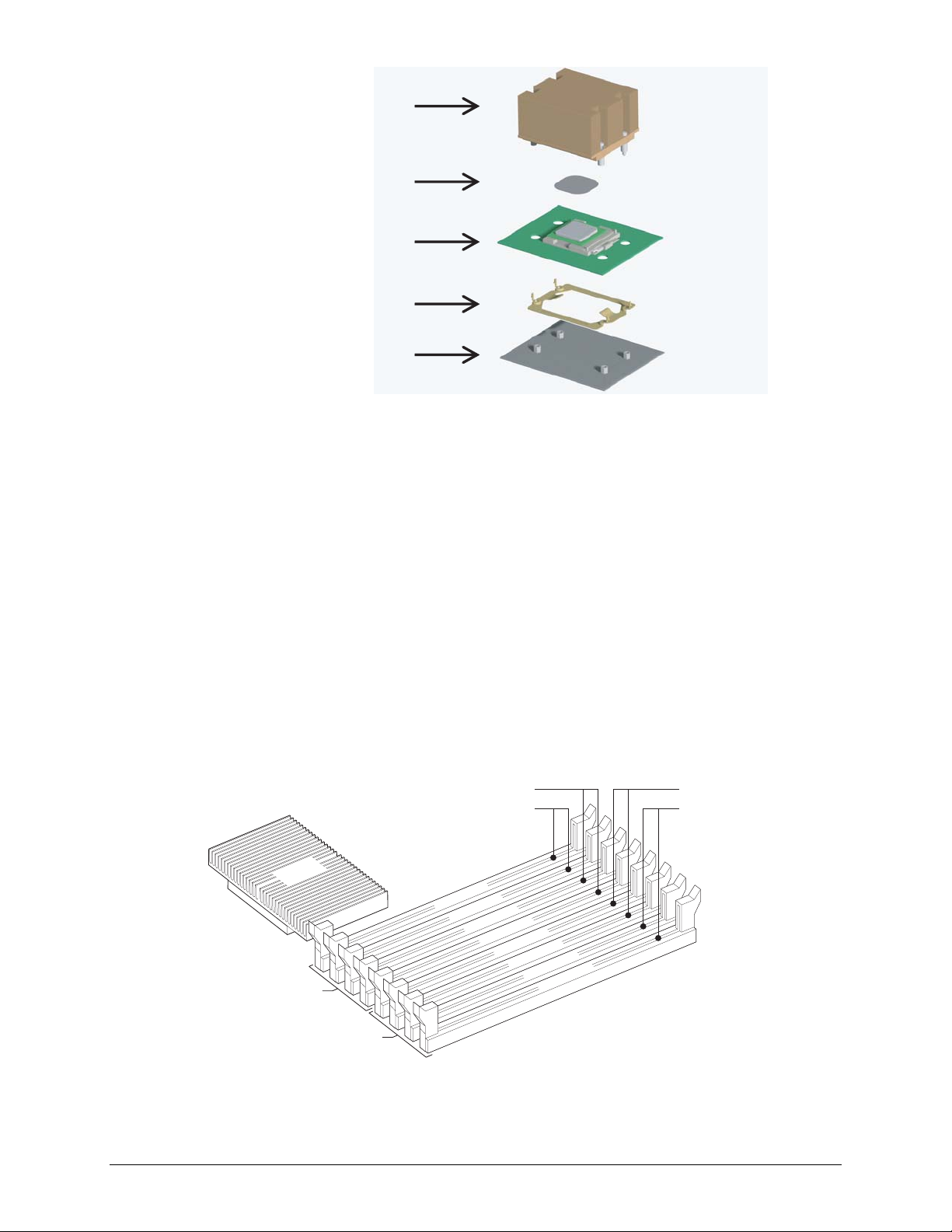

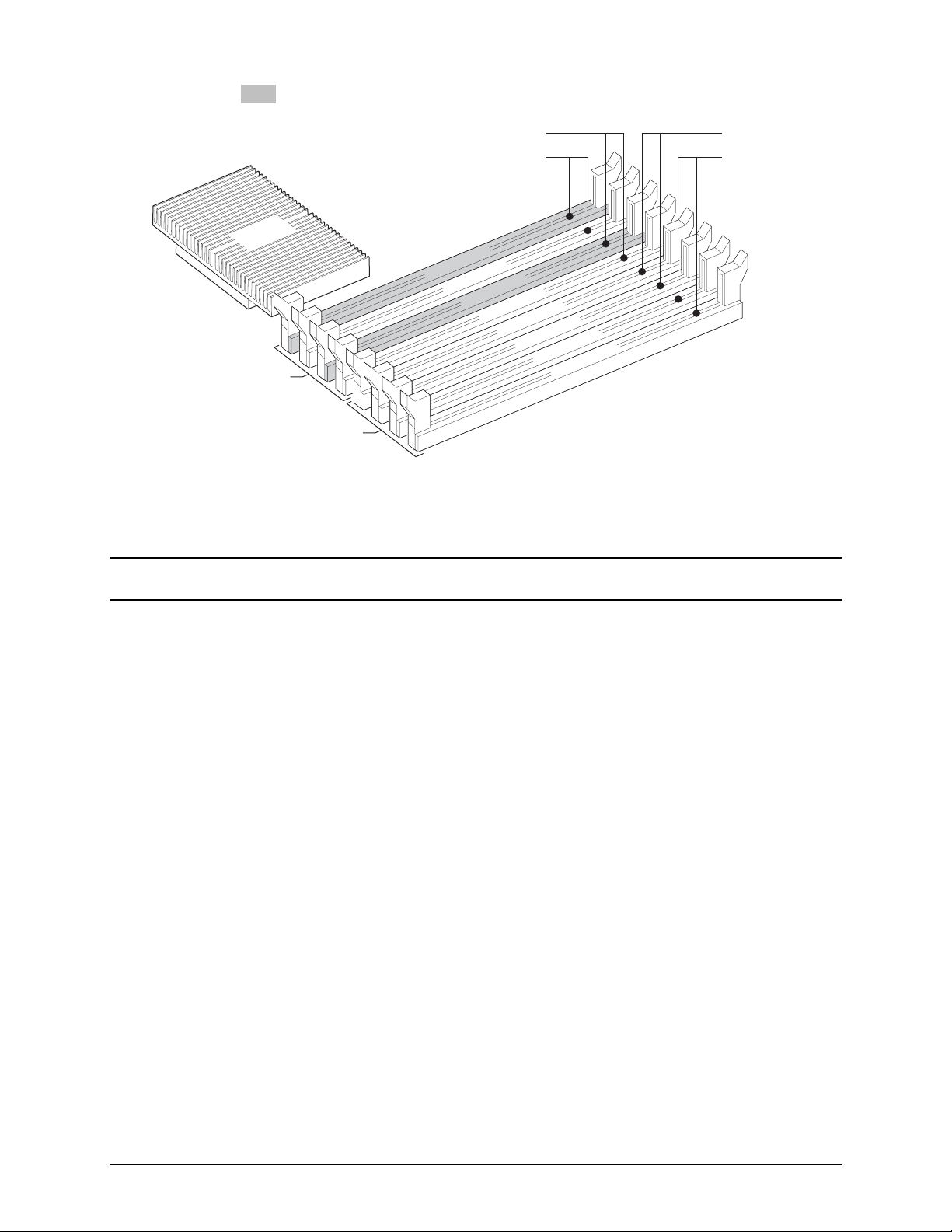

3.1.2.2 Common Enabling Kit (CEK) Design Support

The server board complies with Intel’s Common Enabling Kit (CEK) processor mounting and heat sink

retention solution. The server board ships with a CEK spring snapped onto the underside of the server

board, beneath each processor socket. The heat sink attaches to the CEK, over the top of the processor

and the thermal interface material (TIM). See the figure below for the stacking order of the chassis, CEK

spring, server board, TIM, and heat sink.

The CEK spring is removable, allowing for the use of non-Intel heat sink retention solutions.

Note: The processor heat sink and CEK spring shown in the following diagram are for reference

purposes only. The actual processor heat sink and CEK solutions compatible with this generation server

board may be of a different design.

Revision 1.4

26

Intel order number: D31979-007

Page 26

Intel® Server Board S5000PAL / S5000XAL TPS Functional Architecture

Heatsink assembly

Thermal interface material (TIM)

Server board

CEK spring

Chassis

Figure 10. CEK Processor Mounting

3.1.3 Memory Sub-system

On the Intel® Server Board S5000PAL / S5000XAL, the MCH provides four channels of Fully Buffered

DIMM (FB-DIMM) memory. Each channel can support up to 2 Dual Ranked FB-DIMM DDR2 DIMMs. FBDIMM memory channels are organized in to two branches for support of RAID 1 (mirroring). The MCH

can support up to 8 DIMMs or a maximum memory size of 32 GB physical memory in non-mirrored mode

and 16 GB physical memory in a mirrored configuration. The read bandwidth for each FB-DIMM channel

is 4.25 GB/s for DDR2 533 FB-DIMM memory which gives a total read bandwidth of 17 GB/s for four FBDIMM channels. Thus, this provides 8.5 GB/s of write memory bandwidth for four FB-DIMM channels.

The read bandwidth for each FB-DIMM channel is 5.3GB/s for DDR2 667 FB-DIMM memory which gives

a total read bandwidth of 21GB/s for four FB-DIMM channels. Thus, this provides 10.7 GB/s of write

memory bandwidth for four FB-DIMM channels. The total bandwidth is based on read bandwidth thus the

total bandwidth is 17 GB/s for 533 and 21.0 GB/s for 667.

On the Intel

®

Server Board S5000PAL / S5000XAL, a pair of channels becomes a branch where Branch

0 consists of channels A and B, and Branch 1 consists of channels C and D. FBD memory channels are

organized into two branches for support of RAID 1(mirroring).

MCH

Branch 0

Channel B

Channel A

DIMM A1

DIMM A2

DIMM B1

DIMM B2

DIMM C1

DIMM C2

DIMM D1

DIMM D2

Channel C

Channel D

Branch 1

TP02299

Figure 11. Memory Layout

Revision 1.4

27

Intel order number: D31979-007

Page 27

Functional Architecture Intel® Server Board S5000PAL / S5000XAL TPS

To boot the system, the system BIOS on the server board uses a dedicated I2C bus to retrieve DIMM

information needed to program the MCH memory registers. The following table provides the I

addresses for each DIMM slot.

2

Table 2. I

C Addresses for Memory Module SMB

Device Address

DIMM A1 0xA0

DIMM A2 0xA2

DIMM B1 0xA0

DIMM B2 0xA2

DIMM C1 0xA0

DIMM C2 0xA2

DIMM D1 0xA0

DIMM D2 0xA2

2

C

3.1.3.1 Memory RASUM Featuresi

The MCH supports several memory RASUM (Reliability, Availability, Serviceability, Usability, and

Manageability) features. These features include the Intel

SDDC) for memory error detection and correction, Memory Scrubbing, Retry on Correctable Errors,

Memory Built In Self Test, DIMM Sparing, and Memory Mirroring. See the Intel

®

x4 Single Device Data Correction (Intel® x4

®

S5000 Series Chipsets

Server Board Family Datasheet for more information describing these features.

3.1.3.2 Supported Memory

The server board supports up to eight DDR2-533 or DDR2-667 Fully Buffered DIMMs (FBD memory).

The following tables show the maximum memory configurations supported using the specified memory

technology.

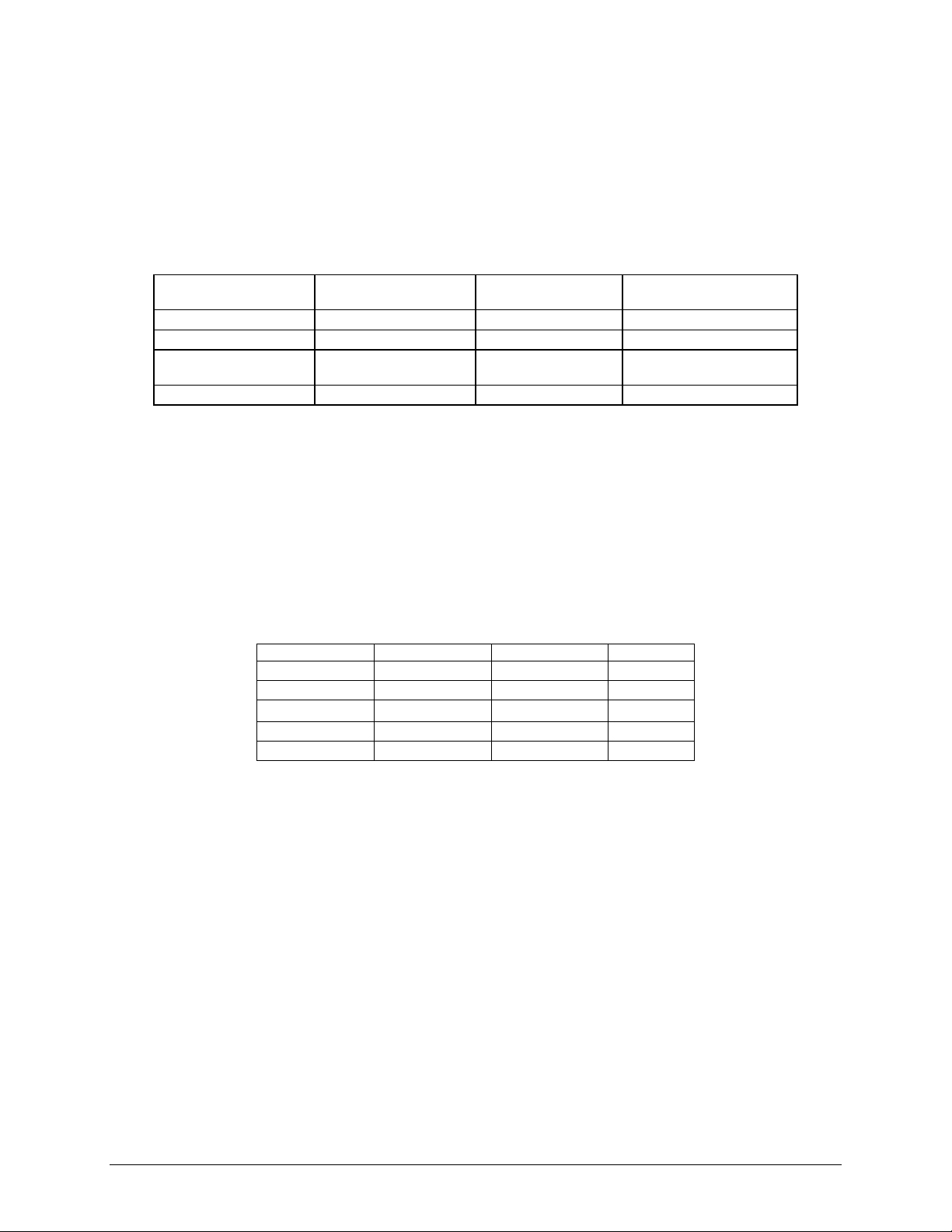

Table 3. Maximum 8 DIMM System Memory Configuration – x8 Single Rank

DRAM Technology x8

Single Rank

256 Mb 1 GB 2 GB

512 Mb 2 GB 4 GB

1024 Mb 4 GB 8 GB

2048 Mb 8 GB 16 GB

Table 4. Maximum 8 DIMM System Memory Configuration – x4 Dual Rank

DRAM Technology x4

Dual Rank

256 Mb 4 GB 8 GB

512 Mb 8 GB 16 GB

1024 Mb 16 GB 32 GB

2048 Mb 16 GB 32 GB

Maximum Capacity

Mirrored Mode

Maximum Capacity

Mirrored Mode

Maximum Capacity

Non-Mirrored Mode

Maximum Capacity

Non-Mirrored Mode

®

Note: DDR2 DIMMs that are not fully buffered are NOT supported on this server board. See the Intel

Server Board S5000PAL / S5000XAL Tested Memory List for a complete list of supported memory for

this server board.

Revision 1.4

28

Intel order number: D31979-007

Page 28

Intel® Server Board S5000PAL / S5000XAL TPS Functional Architecture

3.1.3.3 DIMM Population Rules and Supported DIMM Configurations

DIMM population rules depend on the operating mode of the memory controller, which is determined by

the number of DIMMs installed. DIMMs must be populated in pairs. DIMM pairs are populated in the

following DIMM slot order: A1 & B1, C1 & D1, A2 & B2, C2 & D2. DIMMs within a given pair must be

identical with respect to size, speed, and organization. However, DIMM capacities can be different

between different DIMM pairs.

For example, a valid mixed DIMM configuration may have 512MB DIMMs installed in DIMM Slots A1 &

B1, and 1GB DIMMs installed in DIMM slots C1 & D1.

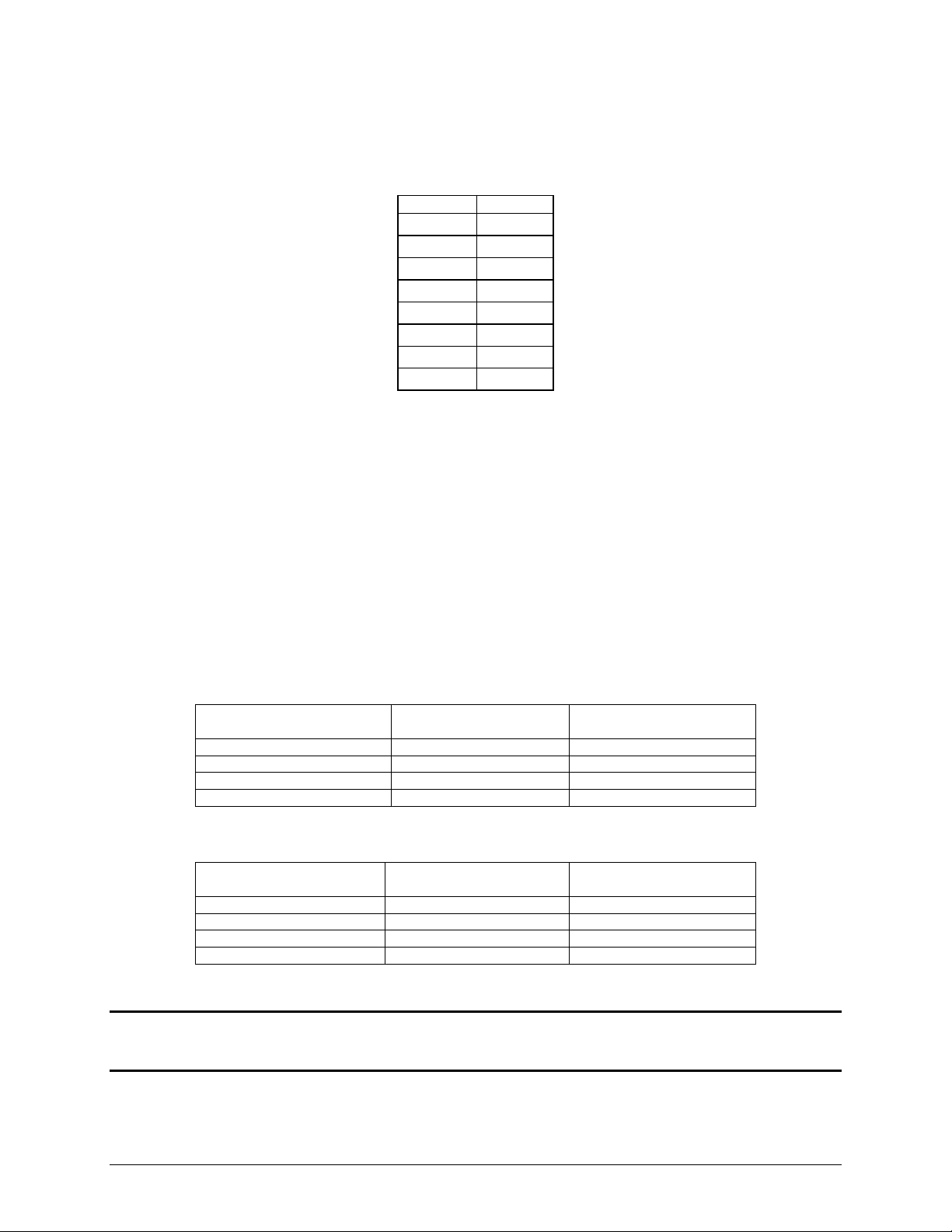

Intel supported DIMM configurations for this server board are shown in the following table.

Supported and Validated configuration : Slot is populated

Supported but not validated configuration : Slot is

populated

Slot is not populated

Mirroring: Y = Yes. Indicates that configuration supports Memory Mirroring.

Sparing: Y(x) = Yes. Indicates that configuration supports Memory Sparing.

Where x = 0 : Sparing supported on Branch0 only

1 : Sparing supported on Branch1 only

0,1 : Sparing supported on both branches

Branch 0 Branch 1

Mirroring

Channel A Channel B Channel C Channel D

DIMM_A1 DIMM_A2 DIMM_B1 DIMM B2 DIMM C1 DIMM C2 DIMM D1 DIMM D2

Y (0)

Y

Y (0)

Y Y (0, 1)

Possible

Possible

Notes:

- Single channel mode is only tested and supported with a 512MB x8 FBDIMM installed in DIMM

Slot A1.

- The supported memory configurations must meet population rules defined above.

- For best performance, the number of DIMMs installed should be balanced across both

memory branches. For Example: a four DIMM configuration will perform better than a two

DIMM configuration and should be installed in DIMM Slots A1, B1, C1, and D1. An eight

DIMM configuration will perform better then a six DIMM configuration.

- Although mixed DIMM capacities between channels is supported, Intel does not validate DIMMs

in mixed DIMM configurations.

Sparing

3.1.3.3.1 Minimum Non-Mirrored Mode Configuration

The server board is capable of supporting a minimum of one DIMM installed. However, for system

performance reasons, Intel’s recommendation is that at least 2 DIMMs be installed.

Revision 1.4

Intel order number: D31979-007

29

Page 29

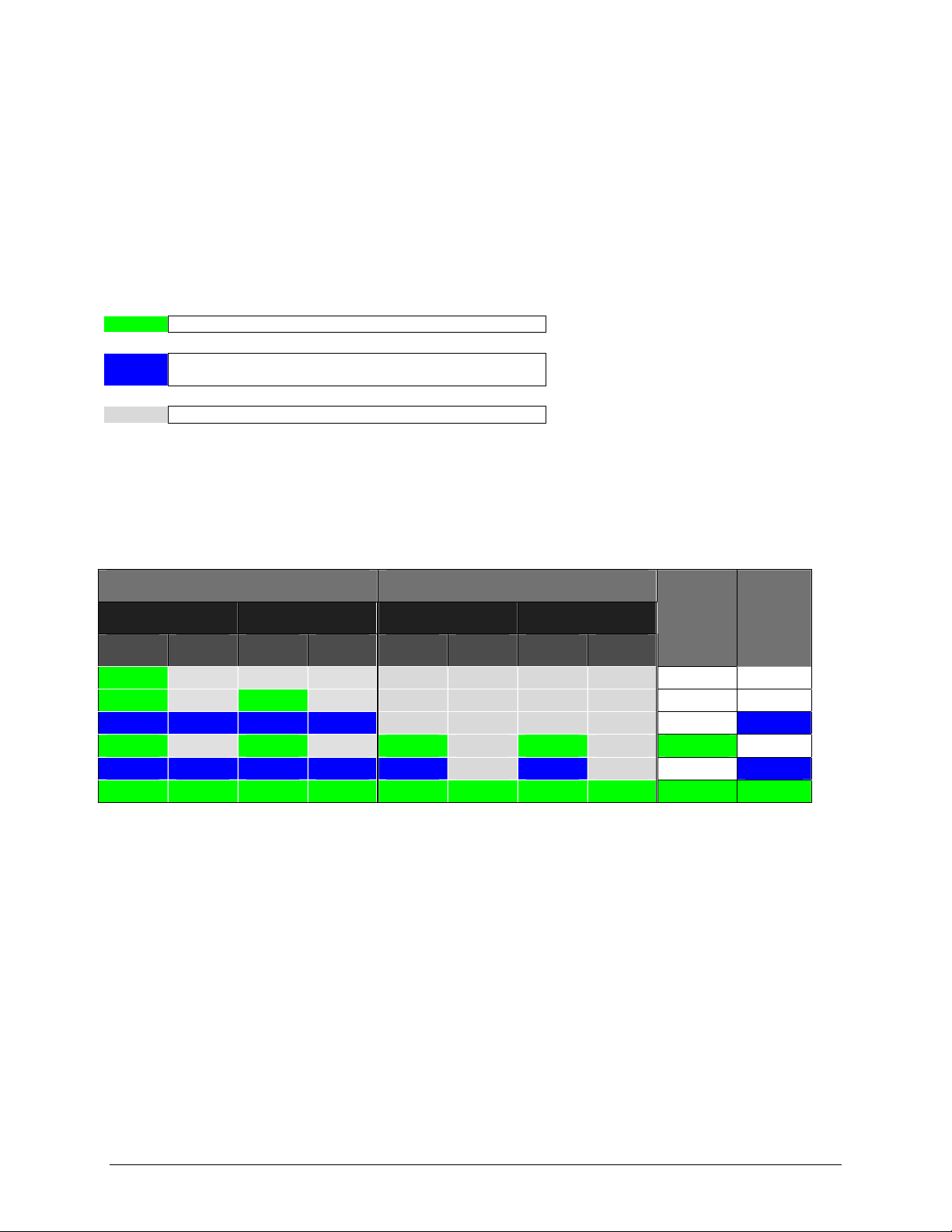

Functional Architecture Intel® Server Board S5000PAL / S5000XAL TPS

The following diagram shows the recommended minimum DIMM memory configuration. Populated DIMM

slots are shown in Grey.

Channel B

Channel A

Channel C

Channel D

MCH

DIMM A1

DIMM A2

DIMM B1

DIMM B2

DIMM C1

DIMM C2

DIMM D1

Branch 0

DIMM D2

Branch 1

TP02300

Figure 12. Recommended Minimum Two DIMM Memory Configuration

Note: The server board supports single DIMM mode operation. Intel will only validate and support this

configuration with a single 512MB x8 FBDIMM installed in DIMM slot A1.

Revision 1.4

30

Intel order number: D31979-007

Page 30

Intel® Server Board S5000PAL / S5000XAL TPS Functional Architecture

3.1.3.4 Non-mirrored mode memory upgrades

The minimum memory upgrade increment is two DIMMs per branch. The DIMMs must cover the same

slot position on both channels. DIMMs pairs must be identical with respect to size, speed, and

organization. DIMMs that cover adjacent slot positions do not need to be identical.

When adding two DIMMs to the configuration shown in Figure 12, the DIMMs should be populated in

DIMM slots C1 and D1 as shown in the following diagram. Populated DIMM slots are shown in Grey.

Channel B

Channel A

Channel C

Channel D

MCH

DIMM A1

DIMM A2

DIMM B1

DIMM B2

DIMM C1

DIMM C2

DIMM D1

Branch 0

DIMM D2

Branch 1

TP02301

Figure 13. Recommended Four DIMM Configuration

Functionally, DIMM slots A2 and B2 could also have been populated instead of DIMM slots C1 and D1.

However, your system will not achieve equivalent performance. Figure 13 shows the supported DIMM

configuration that is recommended because it allows both memory branches from the MCH to operate

independently and simultaneously. FBD bandwidth is doubled when both branches operate in parallel.

3.1.3.4.1 Mirrored Mode Memory Configuration

When operating in mirrored mode, both branches operate in lock step. In mirrored mode, branch 1

contains a replicate copy of the data in branch 0. The minimum DIMM configuration to support memory

mirroring is four DIMMs, populated as shown in Figure 13 above. All four DIMMs must be identical with

respect to size, speed, and organization.

To upgrade a four DIMM mirrored memory configuration, four additional DIMMs must be added to the

system. All four DIMMs in the second set must be identical to the first with the exception of speed. The

MCH will adjust to the lowest speed DIMM.

Revision 1.4

Intel order number: D31979-007

31

Page 31

Functional Architecture Intel® Server Board S5000PAL / S5000XAL TPS

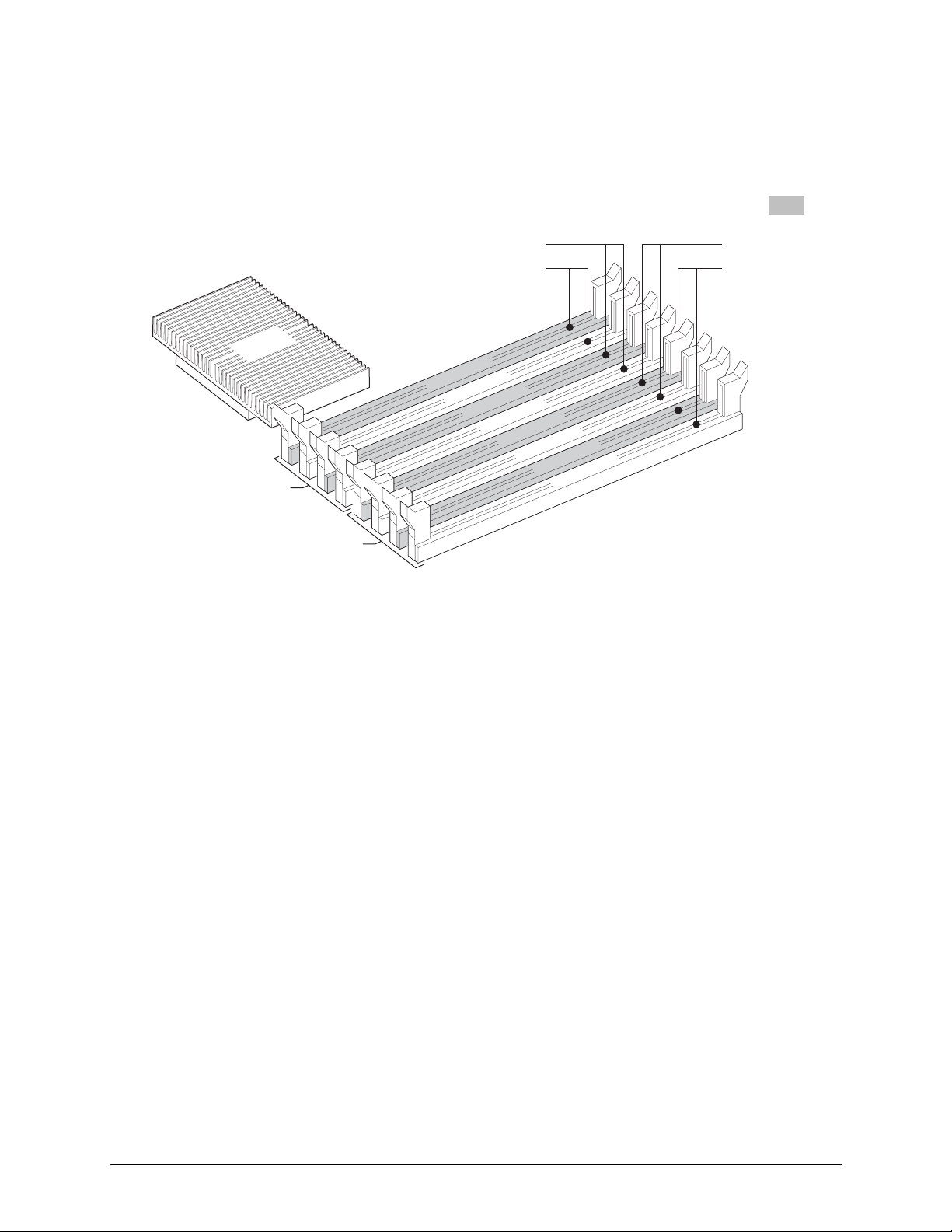

3.1.3.4.2 DIMM Sparing Mode Memory Configuration

The MCH provides DIMM sparing capabilities. Sparing is a RAS feature that involves configuring a DIMM

to be placed in reserve so it can be use to replace a DIMM that fails. DIMM sparing occurs within a given

bank of memory and is not supported across branches.

There are two supported Memory Sparing configurations.

3.1.3.4.2.1 Single Branch Mode Sparing

Slot 2

Slot 1

DIMM_A2

DIMM_A1

Channel A Channel B Channel C Channel D

DIMM_B2

DIMM_B1

DIMM_C2

DIMM_C1

DIMM_D2

DIMM_D1

Bran ch 0 Bra n ch 1

Intel® 5000P/5000X Memory Control ler Hu b

Figure 14. Single Branch Mode Sparing DIMM Configuration

• DIMM_A1 and DIMM_B1 must be identical in organization, size and speed.

• DIMM_A2 and DIMM_B2 must be identical in organization, size and speed.

• DIMM_A1 and DIMM_A2 need not be identical in organization, size and speed.

• DIMM_B1 and DIMM_B2 need not be identical in organization, size and speed.

• Sparing should be enabled in BIOS setup.

• BIOS will configure Rank Sparing Mode.

• The larger of the pairs {DIMM_A1, DIMM_B1} and {DIMM_A2, DIMM_B2} will be selected as the

spare pair unit.

Revision 1.4

32

Intel order number: D31979-007

Page 32

Intel® Server Board S5000PAL / S5000XAL TPS Functional Architecture

3.1.3.4.2.2 Dual Branch Mode Sparing

Dual branch mode sparing requires that all eight DIMM slots be populated and must comply with the

following population rules.

• DIMM_A1 and DIMM_B1 must be identical in organization, size and speed.

• DIMM_A2 and DIMM_B2 must be identical in organization, size and speed.

• DIMM_C1 and DIMM_D1 must be identical in organization, size and speed.

• DIMM_C2 and DIMM_D2 must be identical in organization, size and speed.

• DIMM_A1 and DIMM_A2 need not be identical in organization, size and speed.

• DIMM_B1 and DIMM_B2 need not be identical in organization, size and speed.

• DIMM_C1 and DIMM_C2 need not be identical in organization, size and speed.

• DIMM_D1 and DIMM_D2 need not be identical in organization, size and speed.

• Sparing should be enabled in BIOS setup.

• BIOS will configure Rank Sparing Mode.

• The larger of the pairs {DIMM_A1, DIMM_B1} and {DIMM_A2, DIMM_B2} and {DIMM_C1,

DIMM_D1} and {DIMM_C2, DIMM_D2} will be selected as the spare pair units.

3.1.4 Snoop Filter (5000X MCH only)

The 5000X version of the MCH includes a snoop filter. Depending on the application of the server, this

feature can be used to enhance the performance of the server by eliminating unnecessary traffic on the

system bus. By removing the excess traffic from the snooped bus, the full bandwidth is available for

other operations.

3.2 ESB-2 IO Controller

The ESB-2 is a multi-function device that provides four distinct functions: an IO Controller, a PCI-X*

Bridge, a Gigabit Ethernet Controller, and a Baseboard Management Controller (BMC). Each function

within the ESB-2 has its own set of configuration registers. Once configured, each appears to the system

as a distinct hardware controller.

A primary role of the ESB-2 is to provide the gateway to all PC-compatible I/O devices and features. The

server board uses the following ESB-2 features:

• PCI-X* bus interface

• Six Channel SATA interface w/SATA Busy LED Control

• Dual GbE MAC

• Baseboard Management Controller (BMC)

• Single ATA interface, with Ultra DMA 100 capability

• Universal Serial Bus 2.0 (USB) interface

• Removable Media Drives

• LPC bus interface

• PC-compatible timer/counter and DMA controllers

• APIC and 8259 interrupt controller

• Power management

• System RTC

• General purpose I/O

Revision 1.4

Intel order number: D31979-007

33

Page 33

Functional Architecture Intel® Server Board S5000PAL / S5000XAL TPS

This section describes the function of most of the listed features as they pertain to this server board. For

more detail information, see the Intel

®

Intel

Enterprise South Bridge-2 External Design Specification (Yellow Cover)

®

S5000 Series Chipsets Server Board Family Datasheet or the

3.2.1 PCI Sub-system

The primary I/O buses for the server board are PCI, PCI Express*, and PCI-X*, with six independent PCI

bus segments. The PCI buses comply with the PCI Local Bus Specification, Revision 2.3. The table

below lists the characteristics of the PCI bus segments. Details about each bus segment follow the table.

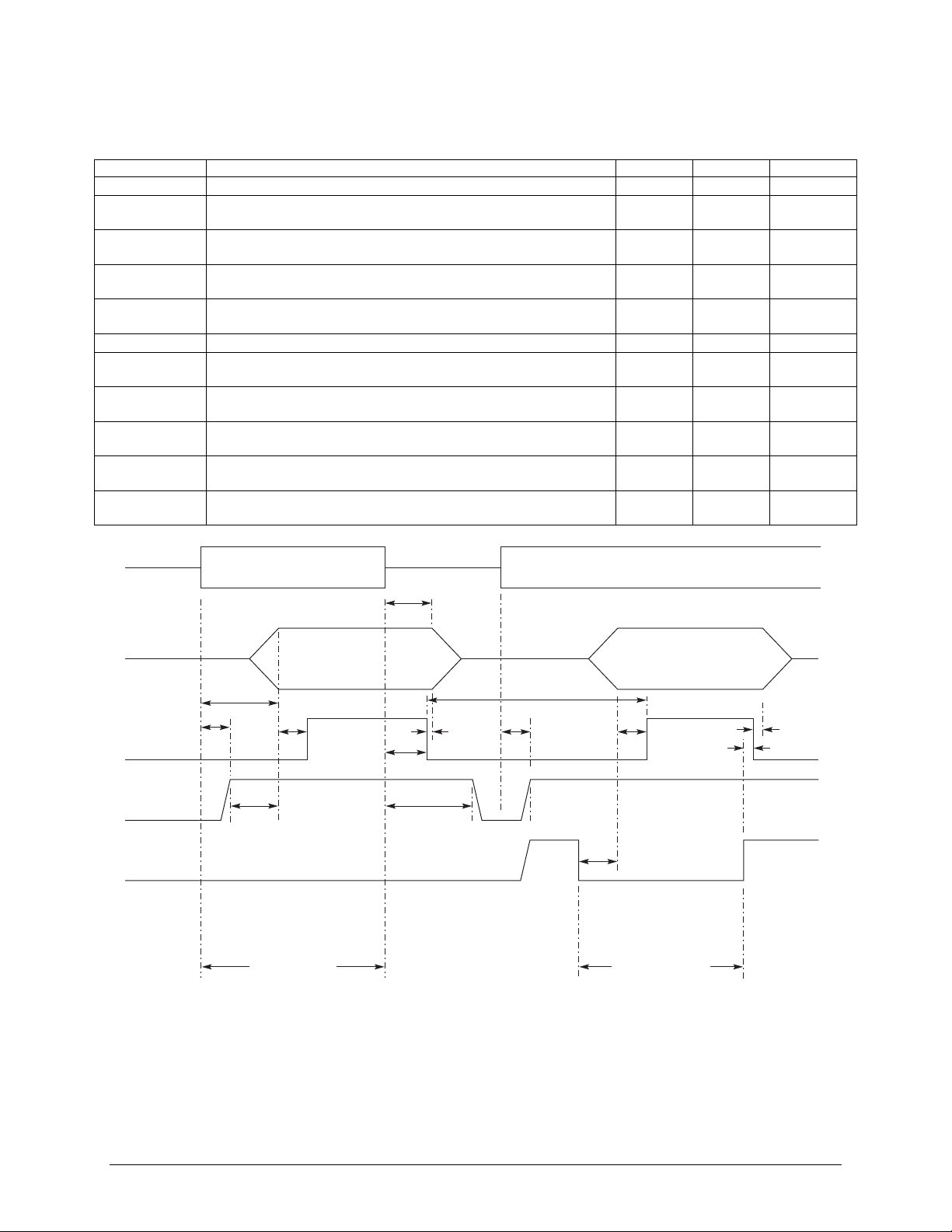

Table 5. PCI Bus Segment Characteristics

PCI Bus Segment Voltage Width Speed Type On-board Device Support

PCI32

ESB-2

PXA

ESB-2

PE1

ESB-2 PCIe* Port2

PE2

ESB-2 PCIe Port3

PE4, PE5

BNB PCIe Ports

4,5

PE6, PE7

BNB PCIe Ports

6,7

3.3V 32 bit 33MHz PCI Used internally for video controller

3.3V/5.0V 64 bit 133MHz PCI-X*

3.3V x4 10Gb/S PCIe* Used for Intel chassis for mid-plane IOP

3.3V x4 10Gb/S PCIe

3.3V x8 20Gb/S PCIe

3.3V x8 20Gb/S PCIe

Full height riser slot, up to three slots on riser

card

®

Mezzanine connector for Intel

Module

Low profile riser slot, up to two x4 slots on 2U

riser, or one x8 slot on 1U riser.

Full height riser slot, up to two x4 slots on

riser or one x8

I/O Expansion

3.2.1.1 PCI32: 32-bit, 33-MHz PCI Bus Segment

All 32-bit, 33-MHz PCI I/O is directed through the ESB-2 ICH6. The 32-bit, 33-MHz PCI segment created

by the ESB-2-ICH6 is known as the PCI32 segment. The PCI32 segment supports the following

embedded devices:

• 2D Graphics Accelerator: ATI* ES1000 Video Controller

3.2.1.2 PXA: 64-bit, 133MHz PCI-X* Bus Segment

One 64-bit PCI-X* bus segment is directed through the ESB-2 ICH6. This PCI-X segment, PXA, can

support up to three add-in cards on a riser card plugged into the full height riser card slot (J4F1).

3.2.1.3 PE1: One x4 PCI Express* Bus Segment

One x4 PCI Express* bus segment is directed through the ESB-2. This PCI Express segment, PE1,

supports the optional Active SAS Midplane IOP as used in supported Intel chassis for this server board.

3.2.1.4 PE2: One x4 PCI Express* Bus Segment

One x4 PCI Express* bus segment is directed through the ESB-2. This PCI Express segment, PE2,

supports one x4 PCI Express segment to the proprietary Intel

connector (J3B1).

®

I/O Expansion Module mezzanine

Revision 1.4

34

Intel order number: D31979-007

Page 34

Intel® Server Board S5000PAL / S5000XAL TPS Functional Architecture

3.2.1.5 PE4, PE5: Two x4 PCI Express* Bus Segments

Two x4 PCI Express* bus segments are directed through the MCH. These PCI Express segments, PE4

and PE5, support one x8 or two x4 PCI Express segments to the low profile riser slot (J5B1).

3.2.1.6 PE6, PE7: Two x4 PCI Express* Bus Segments

Two x4 PCI Express* bus segments are directed through the MCH. These PCI Express segments, PE6

and PE7, support one x8 or two x4 PCI Express segments to the full height riser slot (J4F1).

3.2.1.7 PCI Riser Slots

The server board has two riser slots capable of supporting riser cards for both 1U and 2U system

configurations. Because of board placement resulting in different pin orientations, and expanded

technology support associated with the full-height riser, the riser slots are not the same and require

different riser cards.

The low profile riser slot (J5B1) utilizes a 98-pin connector. It is capable of supporting one x8 (1U) or two

x4 (2U) low profile PCI Express* add-in cards. The x8 PCI Express* bus can support bus speeds of up to

20 Gb/S. The following table provides the supported bus throughput for the given riser card used and the

number of add-in cards installed.

Low Profile Riser 1 add-in card populated 2 add-in cards populated

1U – 1 add-in card slot x8 or x4 NA

2U – 2 add-in card slots x4 x4

Note: There are no population rules for installing a single low profile add-in card in the 2U LP riser card; a

single add in card can be installed in either PCI Express* slot. While each slot can accommodate a x8

card, each slot will only support x4 bus speeds.

The full height riser slot (J4F1) implements Intel® Adaptive Slot Technology. This 280-pin connector is

capable of supporting riser cards that meet either the PCI-X* or PCI Express* technology specifications.

The following tables show the maximum bus speed supported with different add-in card populations for

each supported riser card.

Full Height PCI-X*

(Passive) Riser

1U – 1 add-in card slot Up to 133MHz NA NA

2U – 3 add-in card slots Up to 100MHz in top PCI

1 add-in card populated 2 add-in cards populated 3 add-in cards populated

slot

Up to 100MHz using top

and middle slots

66MHz

Note: For the 2U PCI-X* (passive) riser card, add-in cards should be installed starting with the top slot

first, followed by the middle, and then the bottom. Any add-in card populated in the bottom PCI slot will

cause the bus to operate at 66MHz.

Full Height PCI-X*

(Active) Riser

2U – 3 add-in card slots Up to 133MHz Up to 133MHz Up to 133MHz

1 add-in card populated 2 add-in cards populated 3 add-in cards populated

Note: Each PCI slot on the 2U PCI-X* (active) riser card operates on an independent PCI bus. Therefore,

using an add-in card that operates below 133MHz will not affect the bus speed of the other PCI slots.

Revision 1.4

35

Intel order number: D31979-007

Page 35

Functional Architecture Intel® Server Board S5000PAL / S5000XAL TPS

Full Height PCI Express*

Riser

1U – 1 add-in card slot x4 or x8 NA NA

2U – 3 add-in card slots Single PCIe* x4 in either

1 add-in card populated 2 add-in cards populated 3 add-in cards populated

Dual PCIe* – x4

And

PCI-X* – Up to 133MHz

slot or x8 in middle slot

Or

PCI-X* – Up to 133MHz in

bottom slot

Single PCIe* – x4 in either

slot or x8 in middle slot and

PCI-X* – Up to 133MHz

Or

Dual PCIe – x4

3.2.2 Serial ATA Support

The ESB-2 has an integrated Serial ATA (SATA) controller that supports independent DMA operation on

six ports and supports data transfer rates of up to 3.0 Gb/s. The six SATA ports on the server board are

numbered SATA-0 thru SATA-5. The SATA ports can be enabled/disabled and/or configured by

accessing the BIOS Setup Utility during POST.

3.2.2.1 Intel® Embedded Server RAID Technology II Support

The onboard storage capability of this server board includes support for Intel® Embedded Server RAID

Technology which provides three standard software RAID levels: data stripping (RAID Level 0), data

mirroring (RAID Level 1), and data stripping with mirroring (RAID Level 10). For higher performance,

data stripping can be used to alleviate disk bottlenecks by taking advantage of the dual independent DMA

engines that each SATA port offers. Data mirroring is used for data security. Should a disk fail, a mirrored

copy of the failed disk is brought on-line. There is no loss of either PCI resources (request/grant pair) or

add-in card slots.

With the addition of an optional Intel RAID Activation Key, Intel

®

Embedded Server RAID Technology is

also capable of providing fault tolerant data stripping (software RAID Level 5), such that if a SATA hard

drive should fail, the lost data can be restored on a replacement drive from the other drives that make up

the RAID 5 pack.

See Figure 1. Components & Connector Location Diagram for the location of Intel RAID Activation Key

connector location.

Note: Availability of the Intel RAID Activation Key to support software RAID 5 will be deferred until after

product launch of this server board.

Intel® Embedded Server RAID Technology functionality requires the following items:

• Intel

• Intel

• Intel

®

ESB-2 IO Controller Hub

®

Embedded Server RAID Technology Option ROM

®

Application Accelerator RAID Edition drivers, most recent revision

• At least two SATA hard disk drives

®

Intel

Embedded Server RAID Technology is not available in the following configurations:

• The SATA controller in compatible mode

• Intel

®

Embedded Server RAID Technology has been disabled

Revision 1.4

36

Intel order number: D31979-007

Page 36

Intel® Server Board S5000PAL / S5000XAL TPS Functional Architecture

3.2.2.2 Intel® Embedded Server RAID Technology Option ROM

The Intel® Embedded Server RAID Technology for SATA Option ROM provides a pre-OS user interface

for the Intel

Embedded Server RAID Technology volume to be used as a boot disk as well as to detect any faults in

the Intel

®

Embedded Server RAID Technology implementation and provides the ability for an Intel®

®

Embedded Server RAID Technology volume(s) attached to the Intel® RAID controller.

3.2.3 Parallel ATA (PATA) Support

The integrated IDE controller of the ESB-2 ICH6 provides one IDE channel. It redefines signals on the

IDE cable to allow both host and target throttling of data and transfer rates of up to 100MB/s. For this

server board, the IDE channel was designed to provide Slim-line Optical Drive support to the platform.

The BIOS initializes and supports ATAPI devices such as CDROM, CD-RW and DVD. The IDE channel

is accessed through a single high density 44-pin connector ((J3G1) which provides both power and IO

signals. The ATA channel can be configured and enabled or disabled by accessing the BIOS Setup Utility

during POST.

Note: The IDE connector on this server board is NOT a standard 40 IDE connector. Instead, this

connector has an additional 4 power pins over and above the standard 40 I/O pins. The design intent of

this connector is to provide support for a slim-line optical drive only.

3.2.4 USB 2.0 Support

The USB controller functionality integrated into ESB-2 provides the server board with the interface for up

to eight USB 2.0 ports. Two external connectors are located on the back edge of the server board. One

internal 2x5 header is provided, capable of supporting two optional USB 2.0 ports. Three USB ports are

routed through the bridge board connector providing optional USB support for a system Control Panel or

other USB requirements. An additional USB port is dedicated to the Intel

®

(Intel

RMM) connector.

®

Remote Management Module

3.3 Video Support

The server board provides an ATI* ES1000 PCI graphics accelerator, along with 16MB of video DDR

SDRAM and support circuitry for an embedded SVGA video sub-system. The ATI ES1000 chip contains

an SVGA video controller, clock generator, 2D engine, and RAMDAC in a 359-pin BGA. One 4Mx16x4

bank DDR SDRAM chip provides 16MB of video memory.

The SVGA sub-system supports a variety of modes, up to 1024 x 768 resolution in 8 / 16 / 32bpp modes

under 2D. It also supports both CRT and LCD monitors up to a 100 Hz vertical refresh rate.

Video is accessed using a standard 15-pin VGA connector found on the back edge of the server board.

Video signals are also made available through the 120-pin bridgeboard connector which provides signals

for an optional video connector to be present on the platform’s control panel. Video is routed to both the

rear video connector and a control panel video connector. Video is present at both connectors

simultaneously and cannot be disabled at either connector individually. Hot plugging the video while the

system is still running is supported.

On-board video can be disabled using the BIOS Setup Utility or when an add-in video card is installed.

System BIOS also provides the option for dual video operation when an add-in video card is configured in

the system.

Revision 1.4

37

Intel order number: D31979-007

Page 37

Functional Architecture Intel® Server Board S5000PAL / S5000XAL TPS

3.3.1.1 Video Modes

The ATI ES1000 chip supports all standard IBM* VGA modes. The following table shows the 2D modes

supported for both CRT and LCD.

Table 6. Video Modes

2D Video Mode Support 2D Mode Refresh Rate (Hz)

8 bpp 16 bpp 32 bpp

640x480 60, 72, 75, 85, 90,

100, 120, 160, 200

800x600 60, 70, 72, 75, 85,

90, 100, 120,160

1024x768 60, 70, 72,

75,85,90,100