Page 1

Intel Server Board S3420®GP

Technical Product Specification

Intel order numbe

Enterprise Platforms and Services Division

r E65697-003

Revision 1.0

August 2009

Page 2

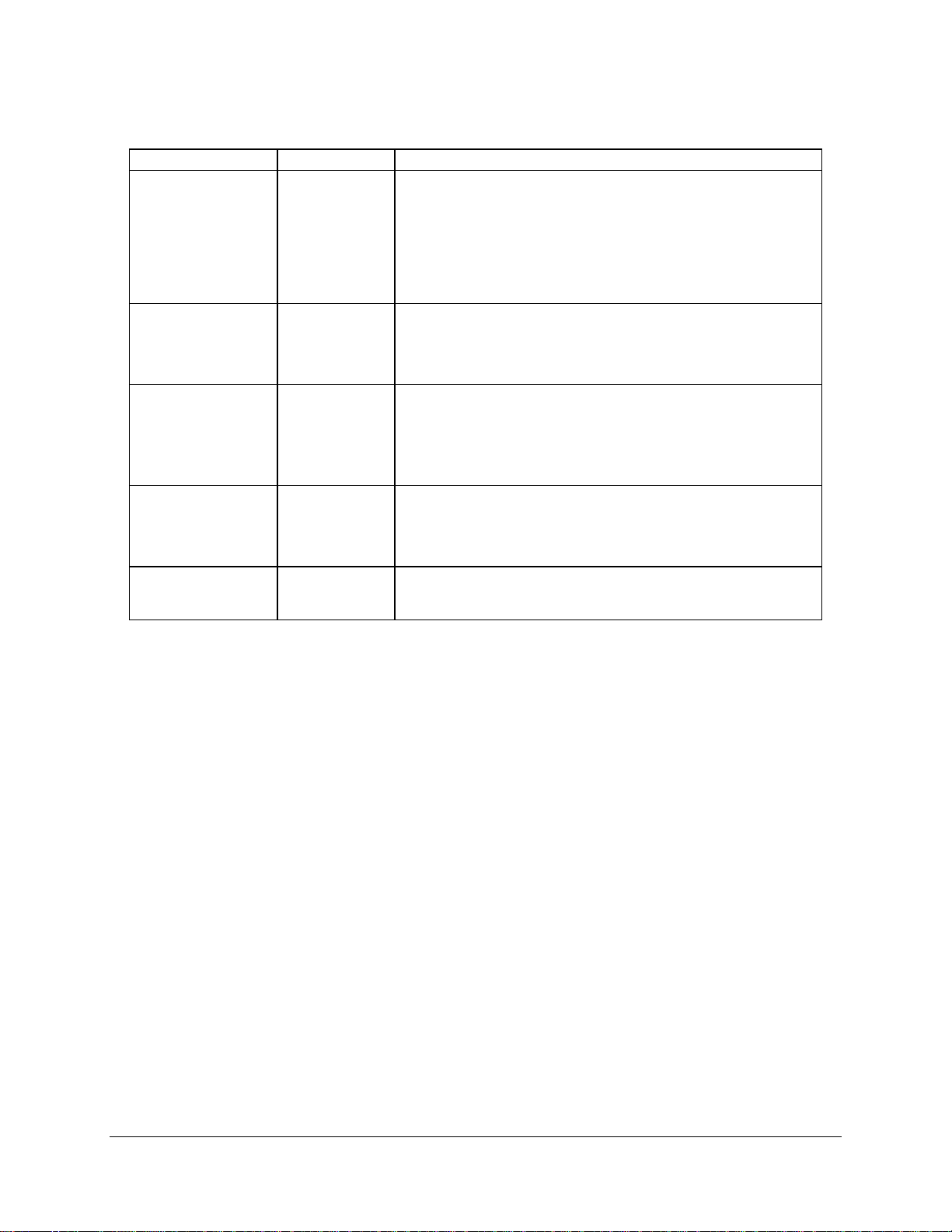

Revision History IntelP®P Server Board S3420GP TPS

Revision History

Date Revision

Number

Feb. 2009 0.3 Initial version

May 2009 0.5 Update

July. 2009 0.9 Update POST error code and diagram

Aug. 2009 1.0 Update MTBF

Modifications

Revision 1.0

ii

Intel order number E65697-003

Page 3

IntelP®P Server Board S3420GP TPS Disclaimers

Disclaimers

Information in this document is provided in connection with Intel® products. No license, express

or implied, by estoppel or otherwise, to any intellectual property rights is granted by this

document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel

assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to

sale and/or use of Intel products including liability or warranties relating to fitness for a particular

purpose, merchantability, or infringement of any patent, copyright or other intellectual property

right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked

"reserved" or "undefined." Intel reserves these for future definition and shall have no

responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information for a product that is still in development. Do not

finalize a design with this information. Information provided in this preliminary document may be

incomplete (as denoted by TBD) or may change. Revised information will be published in a later

release of this document and when the product is made available. Verify with your local sales

office that you have the latest datasheet before finalizing a design.

The Intel

®

Server Board S3420GP may contain design defects or errors known as errata which

may cause the product to deviate from published specifications. Current characterized errata

are available on request.

Intel Corporation server boards contain a number of high-density VLSI and power delivery

components that need adequate airflow to cool. Intel’s own chassis are designed and tested to

meet the intended thermal requirements of these components when the fully integrated system

is used together. It is the responsibility of the system integrator that chooses not to use Intel

developed server building blocks to consult vendor datasheets and operating parameters to

determine the amount of airflow required for their specific application and environmental

conditions. Intel Corporation cannot be held responsible if components fail or the server board

does not operate correctly when used outside any of their published operating or non-operating

limits.

Intel, Pentium, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2009.

Revision 1.0

iii

Intel order number E65697-003

Page 4

Table of Contents IntelP®P Server Board S3420GP TPS

Table of Contents

1. Introduction ..........................................................................................................................2

1.1 Chapter Outline........................................................................................................2

1.2 Server Board Use Disclaimer .................................................................................. 2

2. Overview ...............................................................................................................................1

2.1 Intel® Server Board S3420GP Feature Set.............................................................. 1

2.2 Server Board Layout................................................................................................ 3

2.2.1 Server Board Connector and Component Layout.................................................... 4

2.2.2 Intel® Server Board S3420GP Mechanical Drawings ..............................................6

2.2.3 Server Board Rear I/O Layout ...............................................................................12

3. Functional Architecture .....................................................................................................13

3.1 Processor Sub-System.......................................................................................... 14

3.1.1 Intel

®

Xeon

®

3400 Processor ................................................................................. 14

3.1.2 Intel® Turbo Boost Technology .............................................................................. 15

3.1.3 Simultaneous Multithreading (SMT) ...................................................................... 15

3.1.4 Enhanced Intel SpeedStep® Technology...............................................................15

3.2 Memory Subsystem............................................................................................... 15

3.2.1 Memory Sizing and Configuration.......................................................................... 16

3.2.2 Post Error Codes ................................................................................................... 16

3.2.3 Publishing System Memory ................................................................................... 17

3.2.4 Support for Mixed-speed Memory Modules........................................................... 18

3.2.5 Memory Map and Population Rules....................................................................... 18

3.3 Intel® 3420 Chipset PCH........................................................................................ 21

3.4 I/O Sub-system...................................................................................................... 21

3.4.1 PCI Express Interface............................................................................................ 21

3.4.2 Serial ATA Support ................................................................................................ 22

3.4.3 USB 2.0 Support.................................................................................................... 22

3.5 Optional Intel® SAS Entry RAID Module AXX4SASMOD ......................................23

3.6 Integrated Baseboard Management Controller...................................................... 23

3.6.1 Integrated BMC Embedded LAN Channel............................................................. 25

3.6.2 Optional RMM3 Advanced Management Board ....................................................25

3.6.3 Serial Ports ............................................................................................................ 26

3.6.4 Floppy Disk Controller ...........................................................................................26

Revision 1.0

iv

Intel order number E65697-003

Page 5

IntelP®P Server Board S3420GP TPS Table of Contents

3.6.5 Keyboard and Mouse Support ............................................................................... 26

3.6.6 Wake-up Control.................................................................................................... 27

3.7 Video Support........................................................................................................ 27

3.7.1 Video Modes.......................................................................................................... 27

3.7.2 Dual Video ............................................................................................................. 27

3.8 Network Interface Controller (NIC) ........................................................................ 28

3.8.1 GigE Controller 82574L ......................................................................................... 28

3.8.2 GigE PHY 82578DM.............................................................................................. 28

3.8.3 MAC Address Definition......................................................................................... 28

3.9 Intel

®

I/O Acceleration Technolgy 2 (Intel

®

I/OAT2)............................................... 29

3.9.1 Direct Cache Access (DCA) ..................................................................................29

3.10 Intel

®

Virtualization Technology for Directed I/O (Intel

®

VT-d) ...............................29

4. Platform Management........................................................................................................ 30

4.1 Feature Support..................................................................................................... 30

4.1.1 IPMI 2.0 Features .................................................................................................. 30

4.1.2 Non-IPMI Features ................................................................................................31

4.2 Optional Advanced Management Feature Support ...............................................32

4.2.1 Enabling Advanced Management Features........................................................... 32

4.2.2 Keyboard, Video, Mouse (KVM) Redirection ......................................................... 32

4.2.3 Media Redirection.................................................................................................. 33

4.2.4 Web Services for Management (WS-MAN) ........................................................... 34

4.2.5 Local Directory Authentication Protocol (LDAP) .................................................... 34

4.2.6 Embedded Webserver ........................................................................................... 34

4.3 Management Engine (ME)..................................................................................... 34

5. BIOS User Interface............................................................................................................ 35

5.1 Logo / Diagnostic Screen.......................................................................................35

5.2 BIOS Boot Popup Menu ........................................................................................ 35

5.3 BIOS Setup utility...................................................................................................35

5.3.1 Operation ............................................................................................................... 35

5.3.2 Server Platform Setup Utility Screens ................................................................... 38

5.4 Loading BIOS Defaults .......................................................................................... 63

6. Connector / Header Locations and Pin-outs.................................................................... 65

6.1 Board Connector Information.................................................................................65

6.2 Power Connectors ................................................................................................. 65

6.3 System Management Headers .............................................................................. 66

Revision 1.0

Intel order number E65697-003

v

Page 6

Table of Contents IntelP®P Server Board S3420GP TPS

6.3.1 Intel

®

Remote Management Module 3 (Intel

®

RMM3) Connector .......................... 66

6.3.2 LCP / IPMB Header ............................................................................................... 67

6.3.3 HSBP Header ........................................................................................................ 67

6.3.4 SGPIO Header....................................................................................................... 67

6.4 Front Control Panel Connector.............................................................................. 68

6.4.1 Power Button ......................................................................................................... 68

6.4.2 Reset Button .......................................................................................................... 69

6.4.3 NMI Button............................................................................................................. 69

6.4.4 System Status Indicator LED................................................................................. 69

6.5 I/O Connectors.......................................................................................................71

6.5.1 VGA Connector...................................................................................................... 71

6.5.2 Rear NIC and USB connector................................................................................ 71

6.5.3 SATA .....................................................................................................................72

6.5.4 SAS Connectors .................................................................................................... 72

6.5.5 Serial Port Connectors........................................................................................... 72

6.5.6 USB Connector...................................................................................................... 73

6.6 PCI Express* Slot / PCI Slot / Riser Card Slot /..................................................... 75

6.7 Fan Headers.......................................................................................................... 79

7. Jumper Blocks.................................................................................................................... 80

7.1 CMOS Clear and Password Reset Usage Procedure ........................................... 81

7.1.1 Clearing the CMOS................................................................................................ 81

7.1.2 Clearing the Password........................................................................................... 81

7.2 Integrated BMC Force Update Procedure ............................................................. 82

7.3 ME Force Update Jumper...................................................................................... 82

7.4 BIOS Recovery Jumper......................................................................................... 83

8. Intel® Light Guided Diagnostics........................................................................................ 84

8.1 System Status LED................................................................................................ 84

8.2 Post Code Diagnostic LEDs .................................................................................. 85

9. Design and Environmental Specifications....................................................................... 86

9.1 Intel® Server Board S3420GP Design Specifications ............................................ 86

9.2 Board-level Calculated MTBF................................................................................ 86

9.3 Server Board Power Requirements....................................................................... 87

9.3.1 Processor Power Support...................................................................................... 88

9.4 Power Supply Output Requirements .....................................................................88

9.4.1 Grounding .............................................................................................................. 89

Revision 1.0

vi

Intel order number E65697-003

Page 7

IntelP®P Server Board S3420GP TPS Table of Contents

9.4.2 Standby Outputs .................................................................................................... 89

9.4.3 Remote Sense ....................................................................................................... 89

9.4.4 Voltage Regulation ................................................................................................89

9.4.5 Dynamic Loading ................................................................................................... 89

9.4.6 Capacitive Loading ................................................................................................ 90

9.4.7 Closed-loop Stability .............................................................................................. 90

9.4.8 Common Mode Noise ............................................................................................ 90

9.4.9 Ripple / Noise ........................................................................................................90

9.4.10 Timing Requirements............................................................................................. 90

9.4.11 Residual Voltage Immunity in Standby Mode ........................................................ 93

9.4.12 Protection Circuits.................................................................................................. 93

10. Regulatory and Certification Information......................................................................... 95

10.1 Product Regulatory Compliance ............................................................................ 95

10.1.1 Product Safety Compliance ................................................................................... 95

10.1.2 Product EMC Compliance – Class A Compliance ................................................. 95

10.1.3 Certifications / Registrations / Declarations ........................................................... 95

10.1.4 Product Ecology Requirements ............................................................................. 96

10.2 Product Regulatory Compliance Markings ............................................................ 97

10.3 Electromagnetic Compatibility Notices ..................................................................99

10.3.1 FCC Verification Statement (USA) ........................................................................ 99

10.3.2 ICES-003 (Canada) ............................................................................................. 100

10.3.3 Europe (CE Declaration of Conformity) ...............................................................100

10.3.4 VCCI (Japan) ....................................................................................................... 100

10.3.5 BSMI (Taiwan) ..................................................................................................... 101

10.3.6 RRL (Korea)......................................................................................................... 101

10.3.7 CNCA (CCC-China)............................................................................................. 101

Appendix A: Integration and Usage Tips.............................................................................. 102

Appendix B: Integrated BMC Sensor Tables........................................................................ 103

Appendix C: POST Code Diagnostic LED Decoder ............................................................. 109

Appendix D: POST Code Errors ............................................................................................113

Appendix E: Supported Intel

®

Server Chassis ..................................................................... 118

Glossary................................................................................................................................... 119

Reference Documents ............................................................................................................122

Revision 1.0

Intel order number E65697-003

vii

Page 8

List of Figures IntelP®P Server Board S3420GP TPS

List of Figures

Figure 1. Intel

Figure 2. Intel

Figure 3. Intel

Figure 4. Intel

Figure 5. Intel

Figure 6. Intel

Figure 7. Intel

Figure 8. Intel

Figure 9. Intel

Figure 10. Intel

Figure 11. Intel

Figure 12. Intel

®

Server Board S3420GPLX Picture ....................................................................... 3

®

Server Board S3420GP Layout............................................................................ 4

®

Server Board S3420GP – Key Connector and LED Indicator IDENTIFICATION. 6

®

Server Board S3420GP – Hole and Component Positions .................................. 7

®

Server Board S3420GP – Major Connector Pin Location (1 of 2)........................ 8

®

Server Board S3420GP –Major Connector Pin Location (2 of 2)......................... 9

®

Server Board S3420GP – Primary Side Keepout Zone .....................................10

®

Server Board S3420GP – Secondary Side Keepout Zone................................. 11

®

Server Board S3420GP Rear I/O Layout ........................................................... 12

®

Server Board S3420GP Functional Block Diagram For S3420GPLX .............. 13

®

Server Board S3420GP Functional Block Diagram From S3420GPLC ........... 14

®

Server Board S3420GP Functional Block Diagram From S3420GPV ............. 14

Figure 13. Integrated BMC Hardware ......................................................................................... 25

Figure 14. Server Management Bus (SMBUS) Block Diagram................................................... 30

Figure 15. Setup Utility – Main Screen Display........................................................................... 39

Figure 16. Setup Utility – Advanced Screen Display ..................................................................41

Figure 17. Setup Utility – Processor Configuration Screen Display............................................ 42

Figure 18. Setup Utility – Memory Configuration Screen Display ............................................... 45

Figure 19. Setup Utility – Mass Storage Controller Configuration Screen Display ..................... 46

Figure 20. Setup Utility – Serial Port Configuration Screen Display ........................................... 48

Figure 21. Setup Utility – USB Controller Configuration Screen Display .................................... 49

Figure 22. Setup Utility – PCI Configuration Screen Display ...................................................... 50

Figure 23. Setup Utility – System Acoustic and Performance Configuration Screen Display..... 52

Figure 24. Setup Utility – Security Configuration Screen Display ............................................... 53

Figure 25. Setup Utility – Server Management Configuraiton Screen Display............................ 55

Figure 26. Setup Utility – Console Redirection Screen Display .................................................. 56

Figure 27. Setup Utility – Server Management System Information Screen Display .................. 58

Figure 28. Setup Utility – Boot Options Screen Display.............................................................. 59

Figure 29. Setup Utility – Delete Boot Option Screen Display .................................................... 60

Figure 30. Setup Utility — Hard Disk Order Screen Display....................................................... 61

Figure 31. Setup Utility – CDROM Order Screen Display........................................................... 61

Figure 32. Setup Utility — Floppy Order Screen Display............................................................ 62

Revision 1.0

viii

Intel order number E65697-003

Page 9

IntelP®P Server Board S3420GP TPS List of Figures

Figure 33. Setup Utility – Network Device Order Screen Display ............................................... 62

Figure 34. Setup Utility – Boot Manager Screen Display............................................................ 63

Figure 35. Jumper Blocks (J1A2, J1F1, J1F3, J1F2 and J1F5).................................................. 80

Figure 36. Power Distribution Block Diagram ............................................................................. 87

Figure 37. Output Voltage Timing ............................................................................................... 91

Figure 38. Turn On/Off Timing (Power Supply Signals).............................................................. 92

Figure 39. Diagnostic LED Placement Diagram .......................................................................109

Revision 1.0

ix

Intel order number E65697-003

Page 10

List of Tables IntelP®P Server Board S3420GP TPS

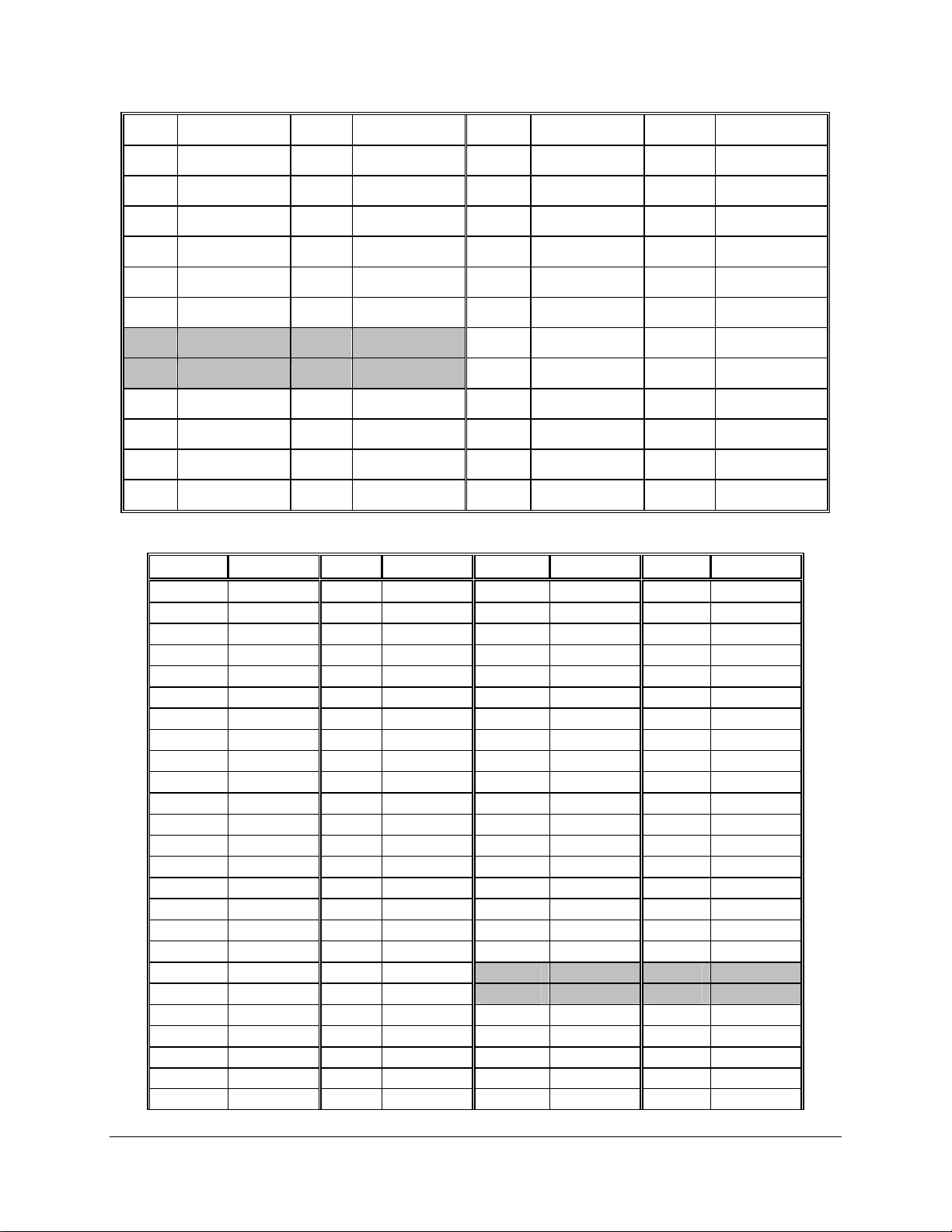

List of Tables

Table 1. Intel

Table 2. Major Board Components ............................................................................................... 5

Table 3. Standard Platform DIMM Nomenclature ....................................................................... 18

Table 4. Memory Configuration Table......................................................................................... 20

Table 5. Optional RMM3 Advanced Management Board Features ............................................26

Table 6. Serial B Header (J1B1) Pin-out..................................................................................... 26

Table 7. Video Modes ................................................................................................................. 27

Table 8. Dual Video Modes......................................................................................................... 27

Table 9. BIOS Setup Page Layout.............................................................................................. 36

Table 10. BIOS Setup: Keyboard Command Bar........................................................................ 37

Table 11. Setup Utility – Main Screen Fields .............................................................................. 39

Table 12. Setup Utility – Advanced Screen Display Fields ......................................................... 41

Table 13. Setup Utility – Processor Configuration Screen Fields ............................................... 42

Table 14. Setup Utility – Memory Configuration Screen Fields .................................................. 45

Table 15. Setup Utility – Mass Storage Controller Configuration Screen Fields......................... 46

Table 16. Setup Utility – Serial Ports Configuration Screen Fields............................................. 48

®

Server Board S3420GP Feature Set ..................................................................... 1

Table 17. Setup Utility – USB Controller Configuration Screen Fields .......................................49

Table 18. Setup Utility – PCI Configuration Screen Fields .........................................................51

Table 19. Setup Utility – System Acoustic and Performance Configuration Screen Fields ........ 52

Table 20. Setup Utility – Security Configuration Screen Fields ..................................................53

Table 21. Setup Utility – Server Management Configuration Screen Fields............................... 55

Table 22. Setup Utility – Console Redirection Configuration Fields ...........................................57

Table 23. Setup Utility – Server Management System Information Fields.................................. 58

Table 24. Setup Utility – Boot Options Screen Fields ................................................................. 59

Table 25. Setup Utility – Delete Boot Option Fields.................................................................... 60

Table 26. Setup Utility — Hard Disk Order Fields....................................................................... 61

Table 27. Setup Utility – CDROM Order Fields .......................................................................... 61

Table 28. Setup Utility — Floppy Order Fields............................................................................ 62

Table 29. Setup Utility – Network Device Order Fields............................................................... 63

Table 30. Setup Utility – Boot Manager Screen Fields ............................................................... 63

Table 31. Board Connector Matrix .............................................................................................. 65

Table 32. Baseboard Power Connector Pin-out (J9A1).............................................................. 66

Revision 1.0

x

Intel order number E65697-003

Page 11

IntelP®P Server Board S3420GP TPS List of Tables

Table 33. SSI Processor Power Connector Pin-out (J9C1) ........................................................ 66

Table 34. Intel

®

RMM3 Connector Pin-out (J2C1) ...................................................................... 66

Table 35. LPC / IPMB Header Pin-out (J1H2) ............................................................................ 67

Table 36. HSBP Header Pin-out (J1J1) ...................................................................................... 67

Table 37. SGPIO Header Pin-out (J1J3) ....................................................................................67

Table 38. Front Panel SSI Standard 24-pin Connector Pin-out (J1C1) ...................................... 68

Table 39. System Status LED Indicator States........................................................................... 70

Table 40. VGA Connector Pin-out (J7A1)................................................................................... 71

Table 41. RJ-45 10/100/1000 NIC Connector Pin-out (J5A1)..................................................... 71

Table 42. RJ-45 10/100/1000 NIC Connector Pin-out (J6A1)..................................................... 71

Table 43. SATA Connector Pin-out (J1H4, J1H1, J1G1, J1H3, J1G3, J1F4)............................. 72

Table 44. SAS Connector Pin-out (J2H1) ................................................................................... 72

Table 45. External Serial A Port Pin-out (J8A1).......................................................................... 73

Table 46. Internal 9-pin Serial B Header Pin-out (J1B2)............................................................. 73

Table 47. Internal USB Connector Pin-out ( J1E1, J1D1)........................................................... 74

Table 48. Pin-out of Internal USB Connector for Floppy ( J1J2)................................................. 74

Table 49. Pin-out of Internal USB Connector for low-profile Intel® Z-U130 Value Solid State

Drive (J3F2).......................................................................................................................... 74

Table 50. Pin-out of adaptive riser slot / PCI Express slot 6....................................................... 75

Table 51. SSI 4-pin Fan Header Pin-out (J6E1, J1J4, J6J2, J7J1, J6B1) .................................. 79

Table 52. Server Board Jumpers (J1F1, J1F2, J1F3, J1F5, J1A2) ............................................80

Table 53. Front Panel Status LED Behavior Summary............................................................... 84

Table 54. POST Code Diagnostic LED Location ........................................................................ 85

Table 55. Server Board Design Specifications ...........................................................................86

Table 56. Intel® Xeon

®

Processor TDP Guidelines ..................................................................... 88

Table 57. 350-W Load Ratings ................................................................................................... 88

Table 58. Voltage Regulation Limits ........................................................................................... 89

Table 59. Transient Load Requirements..................................................................................... 89

Table 60. Capacitve Loading Conditions .................................................................................... 90

Table 61. Ripple and Noise......................................................................................................... 90

Table 62. Output Voltage Timing ................................................................................................ 91

Table 63. Turn On/Off Timing ..................................................................................................... 92

Table 64. Over-Current Protection (OCP)................................................................................... 93

Table 65. Over-voltage Protection (OVP) Limits......................................................................... 93

Table 66. Integrated BMC Core Sensors.................................................................................. 105

Revision 1.0

Intel order number E65697-003

xi

Page 12

List of Tables IntelP®P Server Board S3420GP TPS

Table 67. POST Progress Code LED Example ........................................................................109

Table 68. Diagnostic LED POST Code Decoder ...................................................................... 109

Table 69. POST Error Messages and Handling........................................................................ 113

Table 70. POST Error Beep Codes ..........................................................................................117

Revision 1.0

xii

Intel order number E65697-003

Page 13

IntelP®P Server Board S3420GP TPS List of Tables

<This page intentionally left blank.>

Revision 1.0

xiii

Intel order number E65697-003

Page 14

Introduction IntelP®P Server Board S3420GP TPS

1. Introduction

This Technical Product Specification (TPS) provides board specific information detailing the

features, functionality, and high-level architecture of the Intel

®

Server Board S3420GP.

In addition, you can obtain design-level information for specific subsystems by ordering the

External Product Specifications (EPS) or External Design Specifications (EDS) for a given

subsystem. EPS and EDS documents are not publicly available and must be ordered through

your local Intel representative.

1.1 Chapter Outline

This document is divided into the following chapters:

Chapter 1 – Introduction

Chapter 2 – Server Board Overview

Chapter 3 – Functional Architecture

Chapter 4 – Platform Management

Chapter 5 – BIOS User Interface

Chapter 6 – Connector / Header Locations and Pin-outs

Chapter 7 –Jumpers Blocks

Chapter 8 – Intel

Chapter 9 – Design and Environmental Specifications

Chapter 10 – Regulatory and Certification Information

Appendix A – Integration and Usage Tips

Appendix B – Integrated BMC Sensor Tables

Appendix C – POST Code Diagnostic LED Decoder

Appendix D – POST Code Errors

Appendix E – Supported Intel

®

Light-Guided Diagnostics

®

Server Chassis

1.2 Server Board Use Disclaimer

Intel Corporation server boards contain a number of high-density VLSI and power delivery

components that need adequate airflow to cool. Intel ensures through its own chassis

development and testing that when Intel server building blocks are used together, the fully

integrated system meets the intended thermal requirements of these components. It is the

responsibility of the system integrator who chooses not to use Intel developed server building

blocks to consult vendor datasheets and operating parameters to determine the amount of

airflow required for their specific application and environmental conditions. Intel Corporation

cannot be held responsible if components fail or the server board does not operate correctly

when used outside any of their published operating or non-operating limits.

Revision 1.0

2

Intel order number E65697-003

Page 15

IntelP®P Server Board S3420GP TPS Overview

2. Overview

The Intel® Server Board S3420GP is a monolithic printed circuit board (PCB) with features

designed to support entry-level severs. It has three board SKUs: S3420GPLX, S3420GPLC,

and S3420GPV.

2.1 Intel® Server Board S3420GP Feature Set

Table 1. Intel® Server Board S3420GP Feature Set

Feature Description

Processor Support for one Xeon® 3400 Series Processor in FC-LGA 1156 socket package.

2.5 GT/s point-to-point DMI interface to PCH

LGA 1156 pin socket

Memory Two memory channels with support for 1066/1333 MHz ECC Unbuffered (UDIMM) or

Chipset

ECC Registered (RDIMM) (Intel® Xeon® 3400 Series only) DDR3.

• Intel

• Intel® Server Board S3420GPV

• Intel® Server board S3420GPLX

• Intel® Server board S3420GPLC

®

Server Board S3420GPLX and S3420GPLC

Up to 2 UDIMMs or 3 RDIMM (Intel® Xeon® 3400 Series only) per channel

32 GB max with x8 ECC RDIMM (2 Gb DRAM) and 16 GB max with x8

ECC UDIMM (2 Gb DRAM)

Up to 2 UDIMMs per channel

16 GB max with x8 ECC UDIMM (2 Gb DRAM)

Support for Intel® 3420 Chipset Plaftorm Controller Hub (PCH)

ServerEngines* LLC Pilot II BMC controller (Integrated BMC)

PCI Express* switch

Support for Intel® 3420 Chipset Platform Controller Hub (PCH)

ServerEngines* LLC Pilot II BMC controller (Integrated BMC)

I/O

Revision 1.0

External connections:

DB-15 video connectors

DB-9 serial Port A connector

Four ports on two USB/LAN combo connectors at rear of board.

Internal connections:

Two USB 2x5 pin headers, each supporting two USB 2.0 ports

One 2x5 Serial Port B header

Six SATA II connectors

One Intel® SAS Entry RAID Module AXX4SASMOD connector

One SAS mezzanine slot supports for optional Intel® Remote Management

Module 3

1

Intel order number E65697-003

Page 16

Overview IntelP®P Server Board S3420GP TPS

Feature Description

Add-in PCI Card, PCI

Express* Card

System Fan Support Five 4-pin fan headers supporting four system fans and one processor.

Video Onboard ServerEngines* LLC Pilot II BMC Controller

Onboard Hard Drive Support for six Serial ATA II hard drives through six onboard SATA II connectors with

LAN One Gigabit Ethernet device 82574L connect to PCI-E x1 interfaces on the PCH.

Server Management Onboard LLC Pilot II Controller (iBMC)

• Intel® Server Board S3420GPLX

Slot1: One 5V PCI 32 bit / 33 MHz connector.

Slot2: One PCI Express* Gen1 x4 (x1 throughput) connector.

Slot3: One PCI Express* Gen1 x8 (x4 throughput) connector.

Slot4: One PCI Express* Gen2 x8 (x4 throughput) connector.

Slot5: One PCI Express* Gen2 x8 (x8 throughput) connector.

Slot6: One PCI Express* Gen2 x16 (x8 throughput) connector.

• Intel® Server Board S3420GPLC/ S3420GPV

Slot1: One 5V PCI 32 bit / 33 MHz connector.

Slot3: One PCI Express* Gen1 x8 (x4 throughput) connector.

Slot5: One PCI Express* Gen2 x8 (x8 throughput) connector.

Slot6: One PCI Express* Gen2 x16 (x8 throughput) connector.

Integrated 2D Video Controller

64-MB DDR2 667 MHz Memory

SW RAID 0, 1, 5, and 10.

• Intel® Server Board S3420GPLX:

Up to four SAS hard drives through option Intel® SAS Entry RAID Module

AXX4SASMOD card

Intel® Server Board S3420GPLX/S3420GPLC:

One Gigabit Ethernet PHY 82578DM connected to PCH through PCI-E x1

interface

Integrated Baseboard Management Controller (Integrated BMC), IPMI 2.0

compliant

Integrated 2D video controller on PCI-E x1

• Intel® Server Board S3420GPLX

Intel® Remote Management Module III (RMM3)

Revision 1.0

2

Intel order number E65697-003

Page 17

IntelP®P Server Board S3420GP TPS Overview

2.2 Server Board Layout

Revision 1.0

Figure 1. Intel® Server Board S3420GPLX Picture

3

Intel order number E65697-003

Page 18

Overview IntelP®P Server Board S3420GP TPS

A

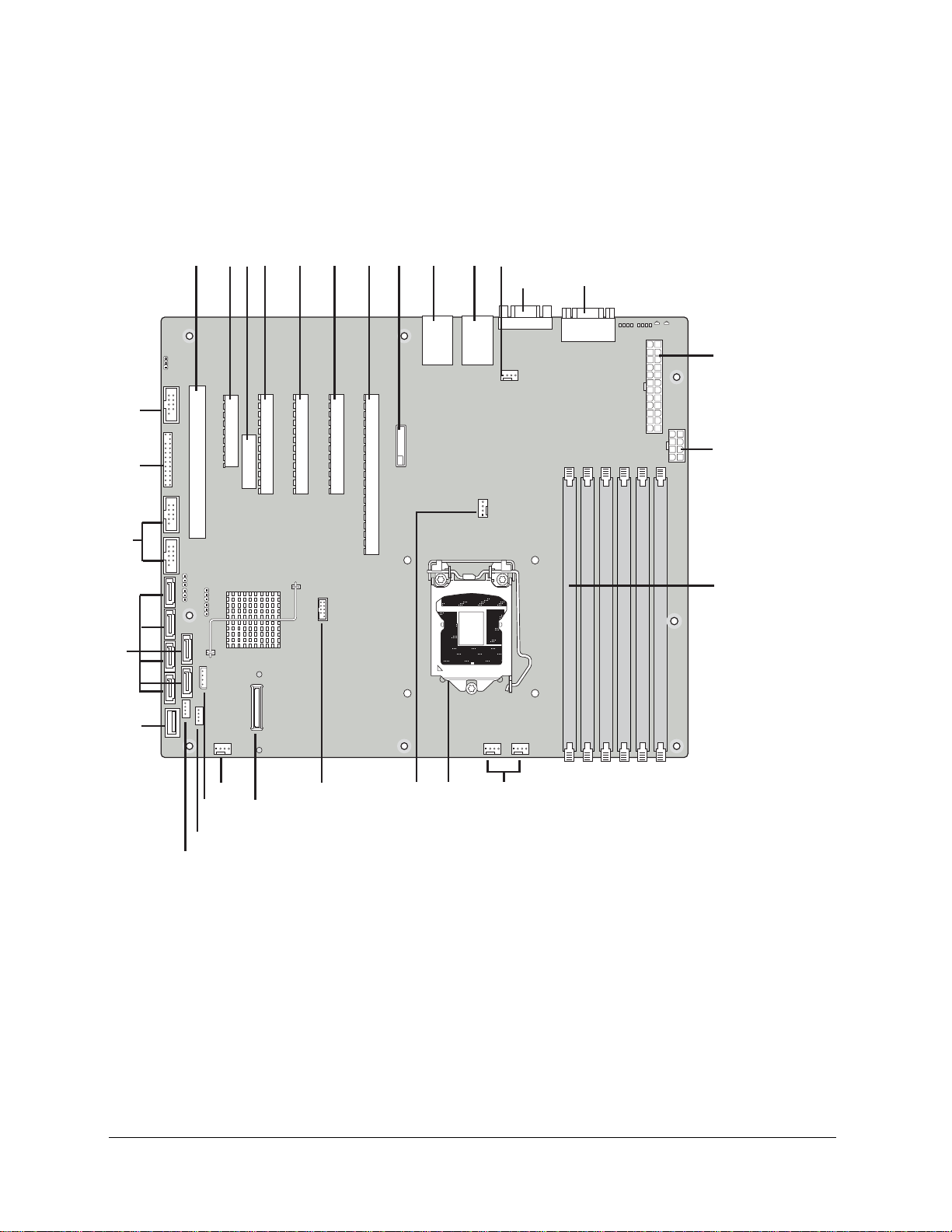

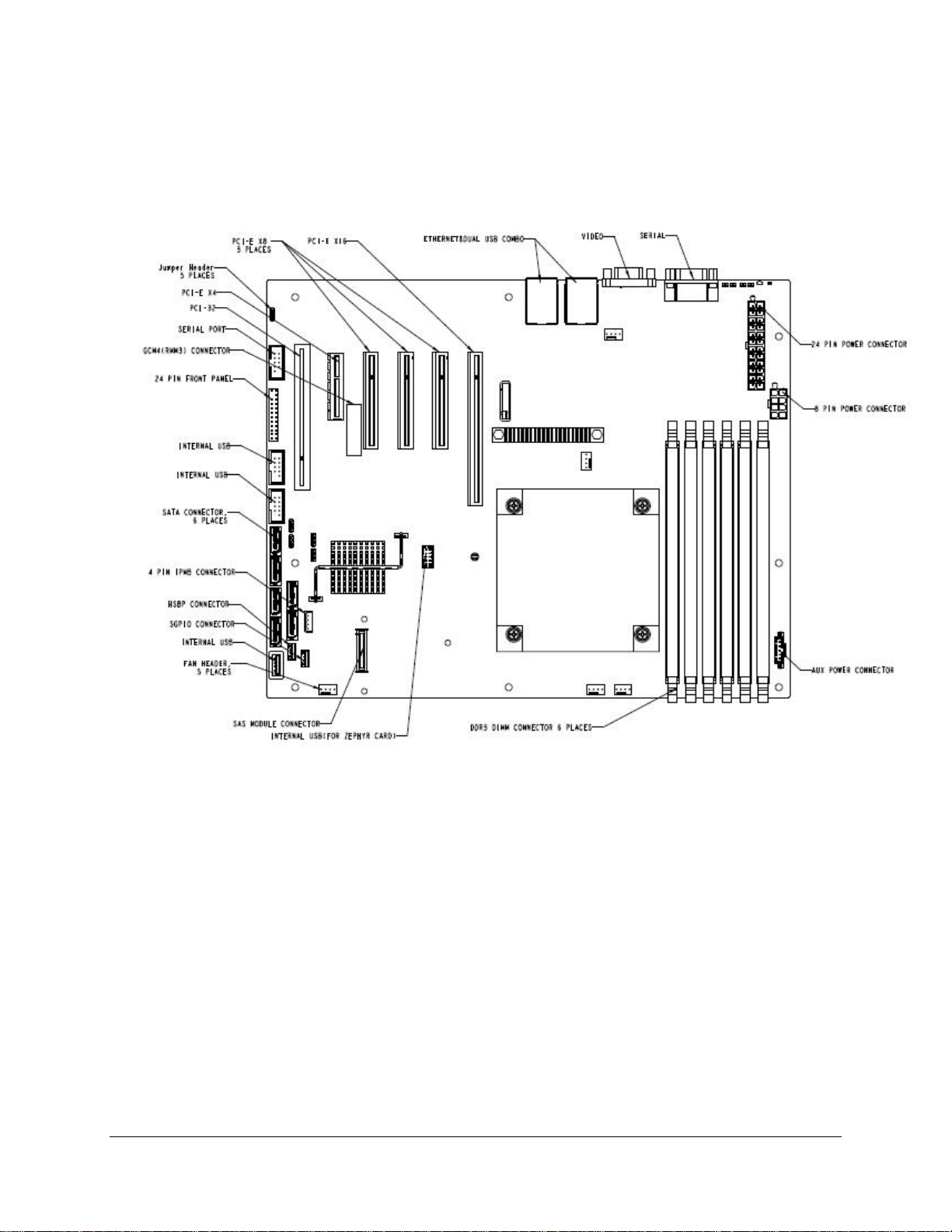

2.2.1 Server Board Connector and Component Layout

The following figure shows the board layout of the server board. Each connector and major

component is identified by a number or letter, and 2 provides the description.

DD

CC

BB

A

ABCDEFGH

J

I

K

LM

N

O

P

Z

V

W

X

Y

U

T

R

S

Q

AF003290

®

Figure 2. Intel

Server Board S3420GP Layout

Revision 1.0

4

Intel order number E65697-003

Page 19

IntelP®P Server Board S3420GP TPS Overview

Table 2. Major Board Components

A Slot 1, 32 Mbit/33 MHz PCI Q System FAN2 and System FAN 3

B Slot 2, PCI Express* Gen1 x1 (x4 connector)

(Intel Server Board S3420GPLX only)

C Intel RMM3 Connector(Intel Server Board S CPU Fan connector

S3420GPLX only)

D

Slot 3, PCI Express* Gen1 x4 (PCI Express* T USB SSD connector

Gen2 compliant)

E Slot 4, PCI Express* Gen2 x4 (x8 connector)

(x8 connector)( Intel

only)

F Slot 5. PCI Express* Gen2 x8 (x8 connector) V System FAN 1

G Slot 6, PCI Express* Gen2 x8 (x16 connector) W IPMB

H CMOS battery X SATA_SGPIO

I Ethernet and Dual USB COMBO Y HSBP

J Ethernet and Dual USB COMBO Z USB Floppy

K System FAN 4 AA Six SATA ports

L Video port BB Internal USB Connector

M External Serial port CC Front Panel Connector

N Main Power Connector DD Internal Serial Port

O CPU Power connector

P DIMM slots

Description Description

R CPU connector

®

Server Board

®

Server Board S3420GPLX

U SAS Module connector ( Intel

S3420GPLX only)

Revision 1.0

5

Intel order number E65697-003

Page 20

Overview IntelP®P Server Board S3420GP TPS

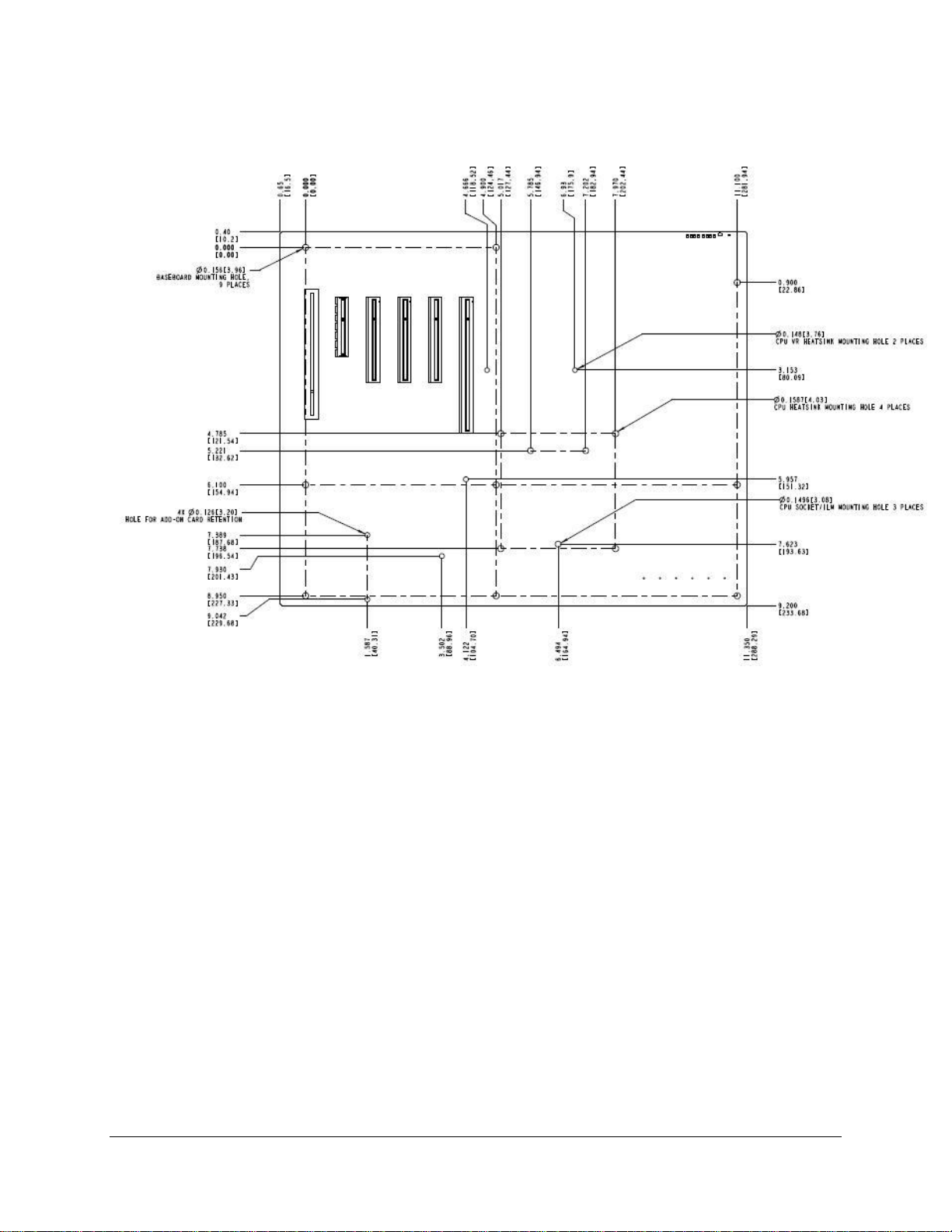

2.2.2 Intel® Server Board S3420GP Mechanical Drawings

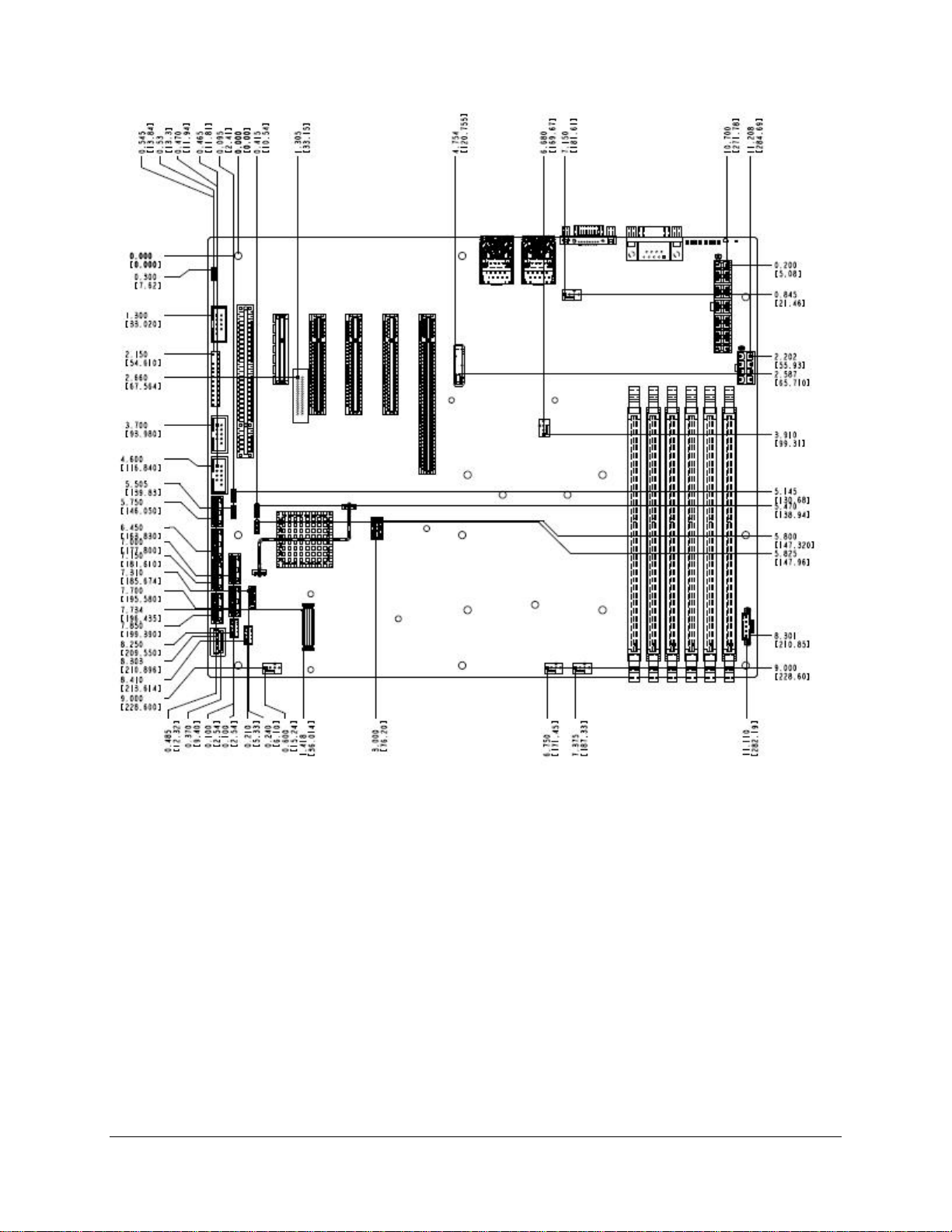

Figure 3. Intel® Server Board S3420GP – Key Connector and LED Indicator IDENTIFICATION

Revision 1.0

6

Intel order number E65697-003

Page 21

IntelP®P Server Board S3420GP TPS Overview

Figure 4. Intel® Server Board S3420GP – Hole and Component Positions

Revision 1.0

7

Intel order number E65697-003

Page 22

Overview IntelP®P Server Board S3420GP TPS

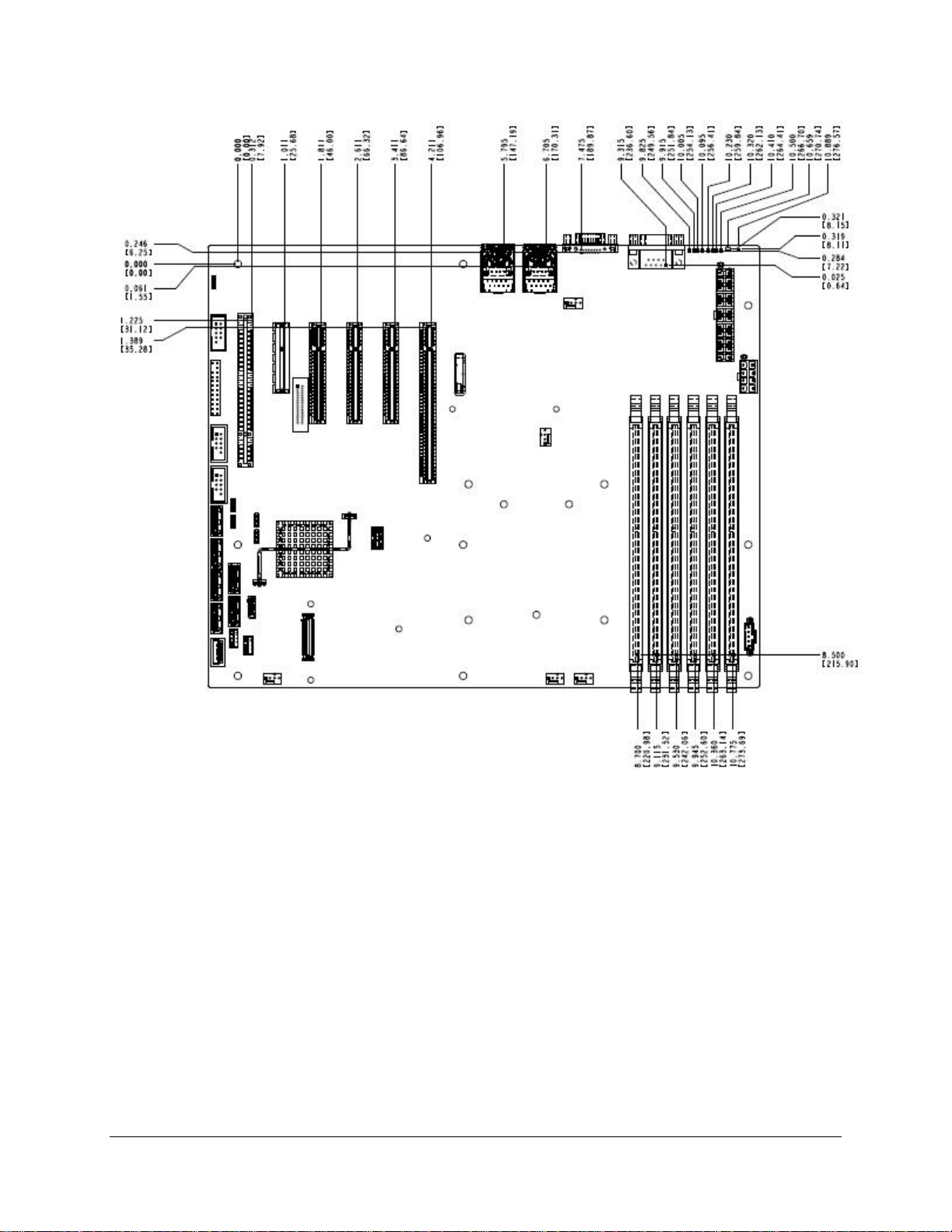

Figure 5. Intel

Revision 1.0

8

®

Server Board S3420GP – Major Connector Pin Location (1 of 2)

Intel order number E65697-003

Page 23

IntelP®P Server Board S3420GP TPS Overview

Figure 6. Intel® Server Board S3420GP –Major Connector Pin Location (2 of 2)

Revision 1.0

9

Intel order number E65697-003

Page 24

Overview IntelP®P Server Board S3420GP TPS

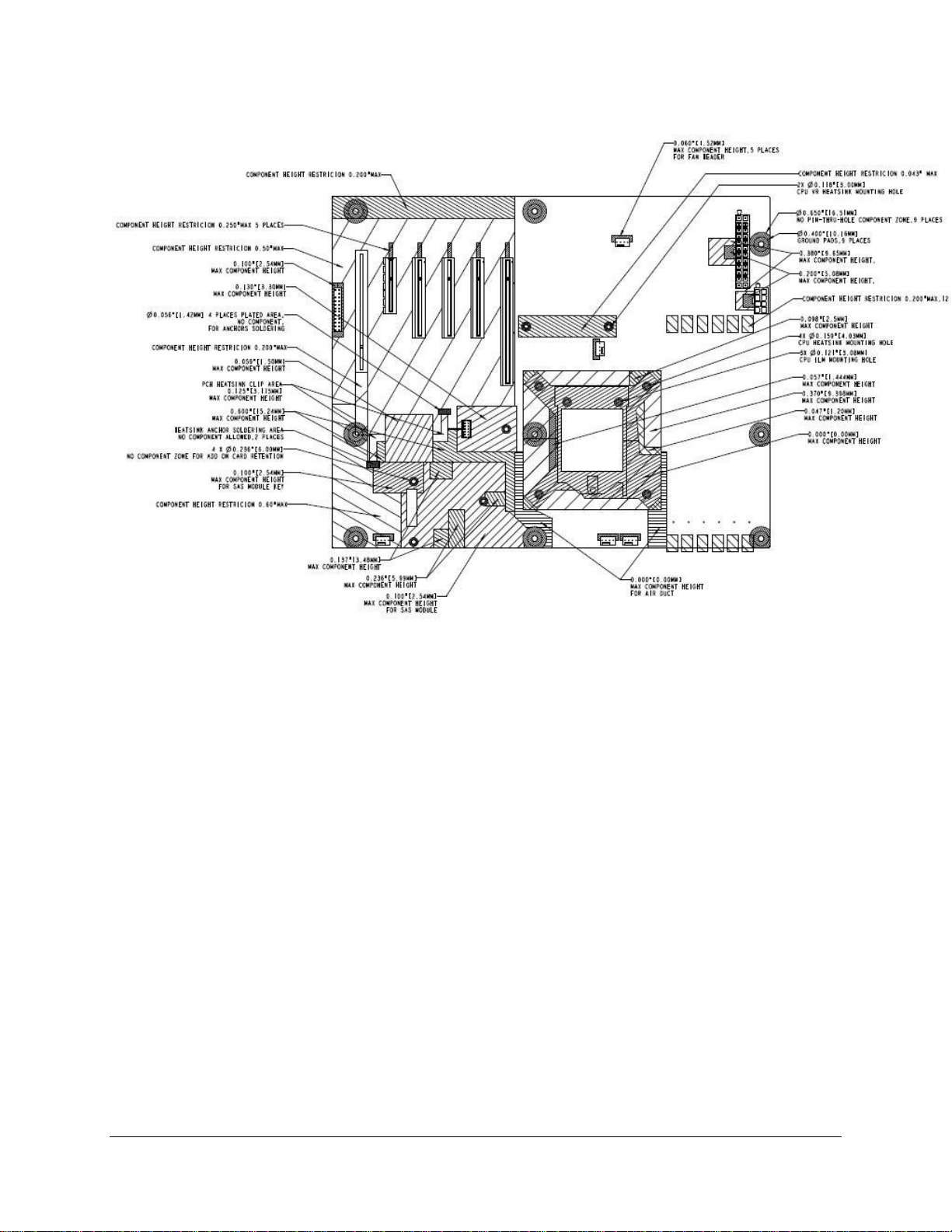

Figure 7. Intel® Server Board S3420GP – Primary Side Keepout Zone

Revision 1.0

10

Intel order number E65697-003

Page 25

IntelP®P Server Board S3420GP TPS Overview

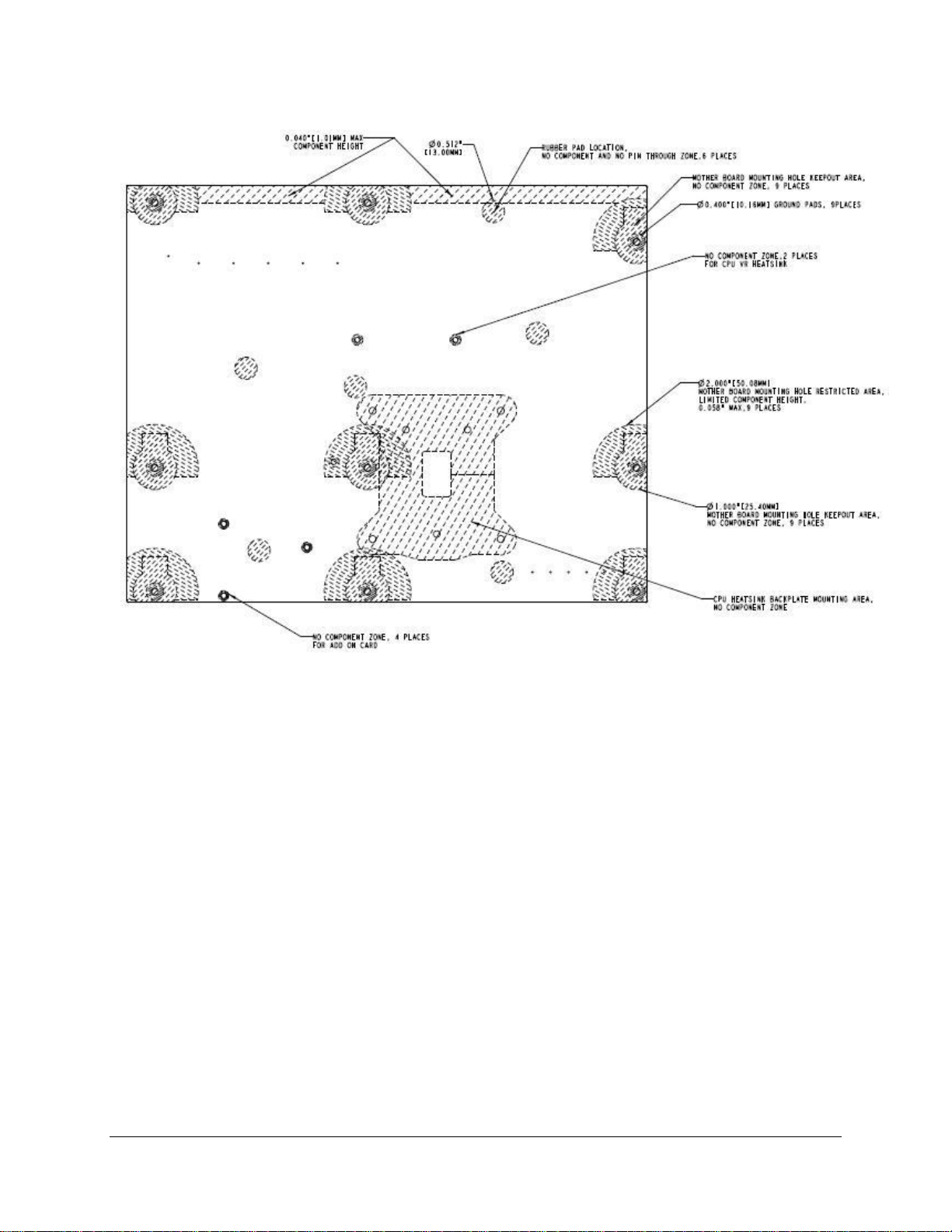

Figure 8. Intel® Server Board S3420GP – Secondary Side Keepout Zone

Revision 1.0

11

Intel order number E65697-003

Page 26

Overview IntelP®P Server Board S3420GP TPS

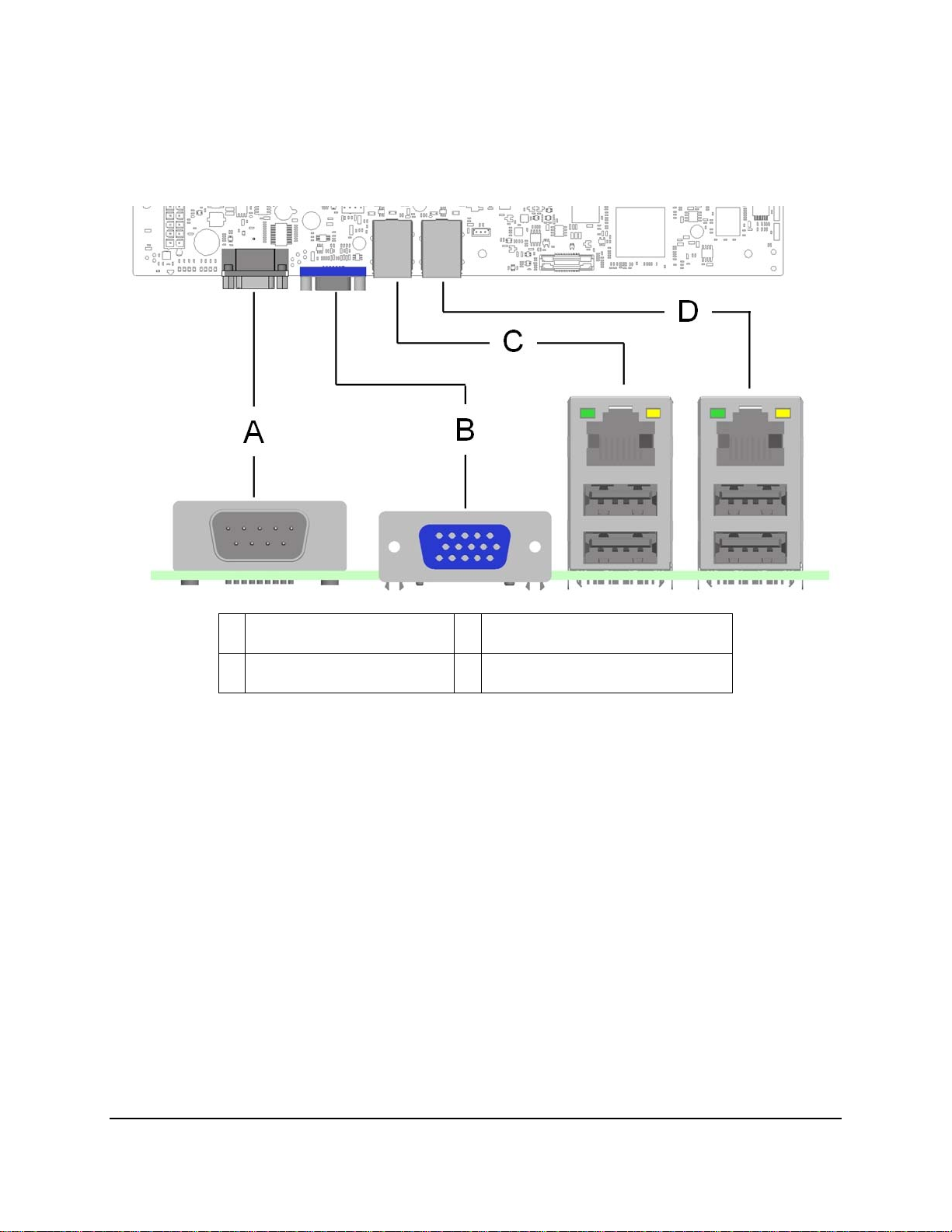

2.2.3

The fol igure shows the layou

lowing f t of the rear I/O components for the server board.

Server Board Rear I/O Layout

A Serial Port A C NIC Port 1 (1 Gb) and Dual USB Port

Connector

B Video D NIC port 2 (1 Gb) and Dual USB Port

Connector

Figure 9. Intel® Server Board S3420GP Rear I/O Layout

12

Revision 1.0

Intel order number E65697-003

Page 27

IntelP®P Server Board S3420GP TPS Functional Architecture

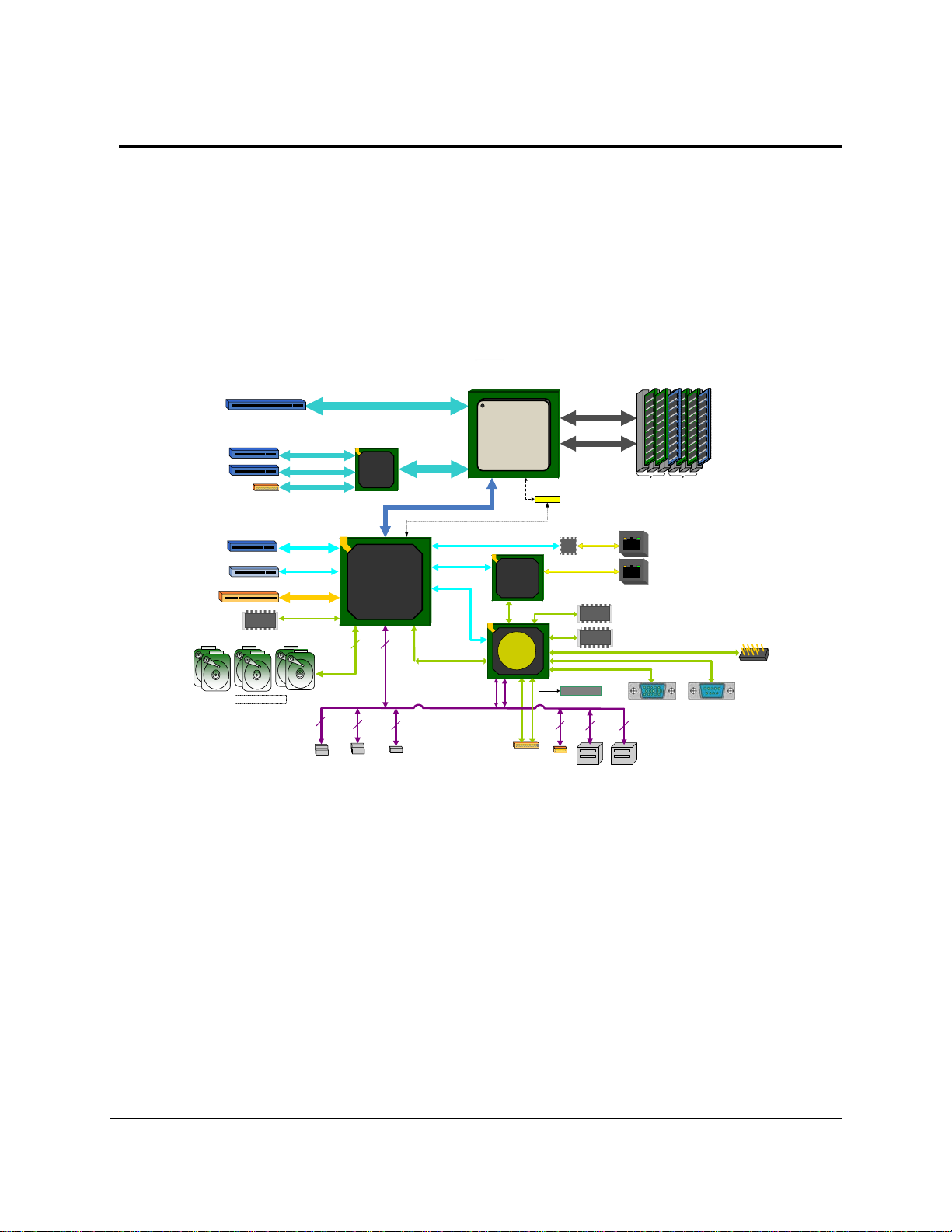

3 nct. Fu ional Architecture

The architecture and design of the Intel® Server Board S3420GP is based on the Intel

Chipset. The chipset is designed for systems based on the Intel

®

Xeon® processor in the FC-

®

3420

LGA 1156 socket package. The chipset contains two main components:

Intel 3420 Chipset

PCI Express* switch (Intel

®

®

Server Board S3420GPLX only).

This chapter provides a high-level description of the functionality associated with each chipset

component and the architectural blocks that make up the server board.

ATX - 12" x 9.6"

4 unbuffered

or

6 registered

DIMMs

SERIAL 2

SERIAL 1

(x16 connector)

(x8 connector)

(x8 connector)

(x8 connector)

(x4 connector)

Slot 6

Slot 5

Slot 4

Slot 3

Slot 2

Slot 1

SAS

PCI

FLASHFLASH

SATA-II

6 onboard

S3420GPLX Block Diagram

PCIe Gen2 x8

Intel® Xeon

PCIe Gen2 x8

PCIe Gen2 x4

PCIe Gen2 x4

PCIe

Gen1

PCIe

N/C

Gen1

PCI32

SPI

2

(FP

headers)

x4

x1

SATA

612

(User Bay

headers)

ICH

G2PS

ICH1

9/

0

Intel® 3420

PCH

1

2

USB

Floppy

Header

PCIe Gen2 x8

x4 DMI Gen1

PCIe

Gen1

PCIe

Gen1

LPC

USB

3400

Gen1 x1 )

( PCIe

x1

82574L

x1

IBMC

USB

1.1

RMII

Zoar

USB

2.0

RMII

RMM3

DDR3 (Ch B)

®

DDR3 (Ch A)

Ch A Ch B

XDP0

82578DM

GbE

PHY

SPI

PORT 80

1

SPI

2

Z-U130

FLASHFLASH

DDR2

FLASH

USB2USB

GbE

GbE

BMC Boot

Flash

VIDEO

Notes:

1. Video integrated into BMC.

Figure agram For S3420GPLX 10. Intel® Server Board S3420GP Functional Block Di

Revision 1.0

Intel order number E65697-003

ejd

13

Page 28

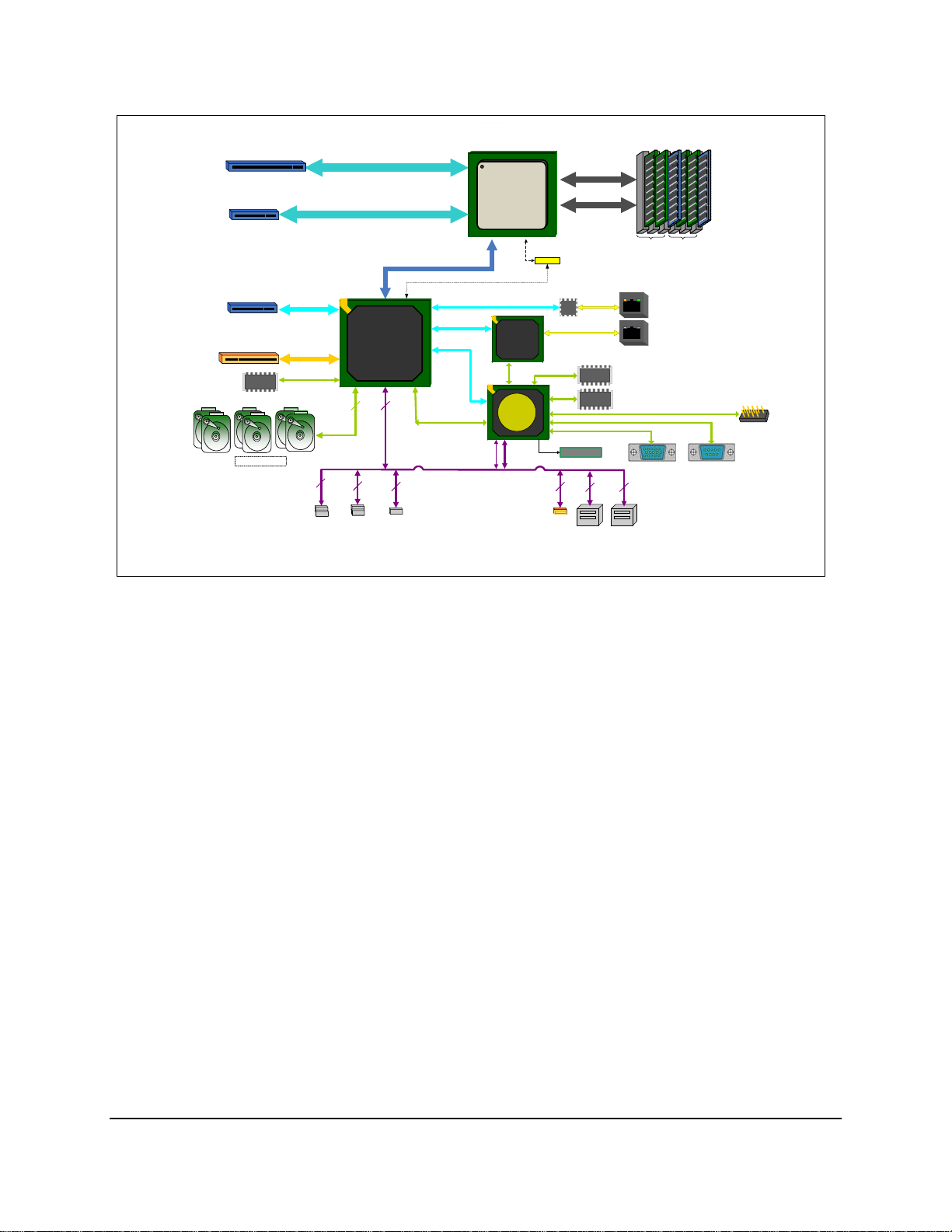

Functional Architecture IntelP®P Server Board S3420GP TPS

(x16 ectoconn r)

(x8 to

(x8 connector)

Slot 6

Slot 5

Slot 3

Slot 1

PCI

FLASHFLASH

SATA-II

6 onboard

S3420GPLC Block Diagram

PCIe

Gen1

PCI32

SPI

headers)

x4

2

(FP

PCIe Gen2 x8connec r)

Intel® 3420

Chipset

612

SATA

2

(User Bay

headers)

PCIe Gen2 x8

Intel

3420

Chipset

1

USB

Floppy

Header

®

x4 DMI Gen1

PCIe

Gen1

PCIe

Gen1

LPC

USB

® ®

Intel Xeon

3400

Processor

( PCIe Gen1 x1 )

x1

82574

x1

IBMC

Zoar

USB

USB

1.1

2.0

RMII

XDP0

RMII

SPI

Z-U130

82578DM

1

GbE

PHY

PORT 80

DDR3 (Ch B)

DDR3 (Ch A)

FLASHFLASH

DDR2

FLASH

2

USB2USB

Ch A Ch B

GbE

GbE

BMC Boot SPI

Flash

VIDEO

Not

1. Video integrated into BMC.

SERIAL 1

es:

ATX - 12" x

4 unbuffered

or

6 registered

DIMMs

SERIAL 2

9.6"

ejd

®

Figure 11. I

ntel Server Board S3420GP Functional Block Diagram From S3420GPLC

<TBD>

Figure 12. Intel Server Board S3420GP Functional Block Diagram From S3420GPV

3.1

Processor Sub-System

The t

In el® Server Board S3420GP supports the following processor:

®

Intel

The Intel

based

3.1.1

The Intel

Nehale

FC-

Xeon

®

X rocessors processors are made up of multi-core processors

eon® 3400 Series p

on the 45 nm process technology.

Intel® Xeon® 3400 Processor

®

m-based processor cores.

®

Xeon 3400 Series processors highly integrated solution variant is composed of four

LGA 1156 socket package with 2.5 GT/s.

Up to 95 W Thermal Design Power (TDP); processors with higher TDP are not

®

®

3400 Processor series

supported.

14

Revision 1.0

Intel order number E65697-003

Page 29

IntelP®P Server Board S3420GP TPS Functional Architecture

The server

3.1.2 Intel Turbo Boost Technology

Inte Boost certain processors in the Intel® Xeon® Processor

l® Turbo Technology is featured on

3400 Series. Intel

processor to run fa

board does not support previous generations of the Intel

®

®

Turbo Boost Technology opportunistically and automatically allows the

ster than the marked frequency if the processor is operating below power,

®

Xeon® processors.

temperature, and current limits. This results in increased performance for both multi-threaded

and n

si gle-threaded workloads.

®

Intel

Turbo Boost Technology operation:

t operates under Operating System control – It is only entered when the

Turbo Boos

operating system requests the highest (P0) performance state.

Turbo Boost operation can be enabled or disabled by BIOS.

Turbo Boost converts any available power and thermal headroom into higher frequency

on active cores. At nominal marked processor frequency, many applications consume

less than the rated processor power draw.

Turbo Boost availability

Maximum Turbo Boost frequency depends on the number of active cores and varies by

is independent of the number of active cores.

processor configuration.

The amount of time the system spends in Turbo Boost operation depends on workload,

o

perating environment, and platform design.

®

If th o

e pr cessor supports the Intel

an o

ption to enable or disable this feature. The default state is enabled.

Turbo Boost Technology feature, the BIO

S Setup provides

3.1. (SMT)

3 Simultaneous Multithreading

Mos t ts

t In el® Xeon® processors support Simultaneous Multithreading (SMT). The BIOS detec

processors that support this feature and enables the feature during POST.

If the processor supports this feature, the BIOS Setup provides an option to enab

this The d

feature. efault is enabled.

3.1.4 Enhanced In

®

Xeon® processors support the Geyserville3 feature of the Enhanced Intel SpeedStep®

Intel

chnology. This feature changes the processor operating ratio and voltage similar to the

te

tel SpeedStep® Technology

le or disable

Thermal Monitor 1 (TM1) feature. The BIOS implements the Geyserville3 feature in conjunction

with the TM1 feature.

The BIOS enables a combination of TM1 and TM2 according to the

processor BIOS writer's guide.

3.2 Memory Subsystem

The Intel® Xeon® 3400 series processor has an Integrated Memory Controller (IMC) in its

package. Each Intel

memory. Each DDR3 channel in the IMC supports up to three DDR3 RDIMM slots or up to two

UDIMM slots. The DDR3 RDIMM frequency can be 800/1066/1333 MHz. DDR3 UDIMM

®

Xeon® 3400 series processor produces up to two DDR3 channels of

Revision 1.0

Intel order number E65697-003

15

Page 30

Functional Architecture IntelP®P Server Board S3420GP TPS

frequency can be 1066/1333 MHz. All RDIMMs and UDIMMs include ECC (Error Correction

Code) operation. Various speeds and memory technologies are supported.

RAS (Reliability, Availability, and Serviceability) is not supported on the Intel

®

Server Board

S3420GP.

3.2.1 Memory Sizing and Configuration

The Intel® Server Board S3420GP supports various memory module sizes and configurations.

These combinations of sizes and configurations are valid only for DDR3 DIMMs approved by

Intel Corporation.

S3420GP BIOS supports:

z DIMM sizes of 1 GB, 2 GB, 4 GB, and 8 GB.

z DIMMs composed of DRAM using 2 Gb technology.

z DRAMs organized as single rank, dual rank, or quad rank DIMMS.

z DIMM speeds of 800, 1066, or 1333 MT/s.

z Registered or Unregistered (unbuffered) DIMMs (RDIMMs or UDIMMs).

Note: UDIMMs should be ECC, and ma or may not have thermal sensors; RDIMMs must have y

ECC and must have thermal sensors.

S3420GP BIOS has the below limitations:

256 Mb technology, x4 DRAM on UDIMM, and quad rank UDIMM are NOT supported

x16 DRAM on UDIMM is not supported on combo routing

Memory suppliers not productizing native 800 ECC UDIMMs

Intel

256 Mb/512 Mb technology, x4 an

All channels in a system will run at

No mixing of registered and unbuffered DIMMs

®

Xeon® 3400 Series support all timings

d x16 DRAMs on RDIMM are NOT supported

the fastest common frequency

defined by JEDEC.

3.2.2 Post Error Codes

The range {0xE0 - 0xEF} of POST codes is used for memory errors in early POST. In late POST,

this range is used for reporting other system errors.

z 0xE8 - No Us

Diagnostic LED

z 0xE8 - Configuratio

the DIMM slot as if no

DIMM installed in the s

usable memo

z 0xEB - Memory Test E

memory channe

the BIOS emits a beep code and displays POST Diagnostic LED code 0xEB

momentarily d

able Memory Error: If no memory is available, the system emits POST

code 0xE8 and halts the system.

n Error: If a DDR3 DIMM has no SPD information, the BIOS treats

DDR3 DIMM is present on it. Therefore, if this is the only DDR3

ystem, the BIOS halts with POST Diagnostic LED code 0xE8 (no

ry) and halts the system.

rror: If a DDR3 DIMM or a set of DDR3 DIMMs on the same

l (row) fails HW Memory BIST but usable memory remains available,

uring the beeping and then continues POST. If all of the memory fails HW

16

Revision 1.0

Intel order number E65697-003

Page 31

IntelP®P Server Board S3420GP TPS Functional Architecture

Memory BIST, the system acts as if no memory is available, beeping and halting with

the POST Diagnostic LED code 0xE8 (No Usable Memory) displayed.

itialization process is unable to

z 0xEA - Channel Training Error: If the memory in

properly perform the DQ/DQS training on a memory channel, the BIOS emits a beep

code and displays POST Diagnostic LED code 0xEA momentarily during the beeping. If

there is usable memory in the system on other channels, POST memory initialization

continues. Otherwise, the system halts with POST Diagnostic LED code 0xEA staying

displayed.

z 0xED - Population Error: If the installed memory contains a mix of RDIMMs and

UDIMMs, the system halts with POST Diagnostic LED code 0xED.

z 0xEE - Mismatch Error: If more th

an two quad-ranked DIMMs are installed on any

channel in the system, the system halts with POST Diagnostic LED code 0xEE.

3.2.

3 Publishing System Memory

• The BIOS displays the Total M

disabled in the BIOS setup. This is

during POST, and is the sum of the

emory of the system during POST if Quiet Boot is

the total size of memory discovered by the BIOS

individual sizes of installed DDR3 DIMMs in the

system.

• The BIOS displays the Eff

ective Memory of the system in the BIOS Setup. The term

Effective Memory refers to the total size of all active DDR3 DIMMs (not disabled) and not

used as redundant units.

• The BIOS provides the total memory of the system in the main page of the BIOS setup.

This total is the same as the amount described by the first bullet in this section.

• If Quiet Boot is disabled, the BIOS displays the total system memory on the diagnos

tic

screen at the end of POST. This total is the same as the amount described by the first

bullet in this section.

• The BIOS provides the total amount of memory in the system.

3.2.3.1 Memory Reservation for Memory-mapped Functions

A region of size 40 MB of memory below 4 GB is always reserved for mapping chipset,

proces BIOS (flash) spaces as

sor, and memory-mapped I/O regions. This region appears as a

loss of memory to the operating system. In addition to this loss, the BIOS creates another

reserved region for memory-mapped PCIe functions, including a standard 64 MB or 256 MB of

standard PCI Express* MMIO configuration space.

If PAE is turned on in the operating

system, the operating system reclaims all these reserved

regions.

In addition to this memory reservation, the BIOS creates another reserved region for memorymapped PCI Express* functions, including a standard 64 MB or 256 MB of standard PCI

Express* Memory Mapped I/O (MMIO) configura

tion space. This is based on the selection of

Maximize Memory below 4 GB in the BIOS Setup.

If this is set to Enabled, the BIOS maximizes u

sage of memory below 4 GB for an operating

system without PAE capability by limiting PCI Express* Extended Configuration Space to 64

buses rather than the standard 256 buses. This is done using the MAX_BUS_NUMBER featur

Revision 1.0

Intel order number E65697-003

e

17

Page 32

Functional Architecture IntelP®P Server Board S3420GP TPS

offered by the Intel® S3420 I/O Hub and a variably-sized Memory Mapped I/O region for the PCI

Express* functions.

3.2.3.2 High-Memory Reclaim

When 4 GB or more o f physical memory is installed (physical memory is the memory installed

as DDR s), the reserved me

feature high-memory reclaim

3 DIMM mory is lost. However, the Intel

called , which allows the BIOS and operating system to remap the

lost physical memory into system memory above 4 GB (the system memory is the memor

®

3420 chipset provides a

y the

processor can see).

The BIOS always enables high-memory reclaim if it discovers installed physical memory equal

to or greater than 4 GB. For the operating system, the reclaimed memory is recoverable only if

the

PAE feature in the processor is supported and enabled. Most operating systems support

this feature. For details, see the relevant operating system manuals.

3.2.3.3 ECC Support

Onl C

y E C memory is supported on this platform.

3.2.4 Support for Mi

xed-speed Memory Modules

The BIOS supports memory modules of mixed speed by automatic selection of the lowest

common frequency of all memory modules (DDR3 DIMM). Each DDR3 DIMM adv

ertises its

lowest supported clock speed through the TCKMIN parameter in its Serial-presence Data (SPD).

The BIOS uses this information to arrive at the common lowest frequency that satisfies all

inst e

all d DDR3 DIMMs.

Thi e

s s ction describes the expected outcome on the installation of DDR3 DIMMs of different

equencies in the system for a given user-selected frequency. The following rules apply:

fr

If all three single-rank/dual-rank RDIMM slots are populated on a channel, the BIOS

forces a global common frequency of 800 MHz.

If two quad-rank RDIMM are popu

lated on one channel, the BIOS forces a global

common frequency of 800 MHz.

If one quad-rank RDIMM are populated on one channel, the BIOS forces a global

common frequency of 1066 MHz.

If a maximum of only two DIMM slots are populated in the system among all channels

and one or more DIMMs support DDR3 frequency greater than 1333 MH

z, the BIOS

forces a global common frequency of 1333 MHz.

3.2.5 Memory Map and Population Rules

The following nomenclature is followed for DIMM sockets:

®

Note: Intel

18

Server Board S3420GP may support up to three DIMM sockets per channel.

Table 3. Standard Platform DIMM Nomenclature

Channel A Channel B

A1 A2 A3 B1 B2 B3

Revision 1.0

Intel order number E65697-003

Page 33

IntelP®P Server Board S3420GP TPS Functional Architecture

3.2.5.1 TableMemory Subsystem Operating Frequency Determinat

ion

The rules for determining the operating frequency of the memory channels are simple, but not

necessarily straightforward. There are several limitin

on a channel and organization of the DIMM - that is, either single-rank (SR), dual-rank (D

g factors, including the number of DIMMs

R), or

quad-rank (QR):

The speed of the processor’s IMC is the maximum speed possible.

The speed of the slowest com

ponent – the slowest DIMM or the IMC – determines the

maximum frequency, subject to further limitations.

A single 1333-MHz DIMM (SR or DR) on a channel may run at full 1333-MHz speed.

If two SR/DR D

A single QR RDIMM on a channel is limited to 1066 MHz.

Two QR RDIMMs or a mix of QR + SR/DR on a channel is limite

IMMs are installed on a channel, the speed is limited to 1066 MHZ.

d to 800 MHz.

3.2.5.2 Memory Subsystem Nomenclature

1. DIMMs are organized into physical slots on DDR3 memo

ry channels that belong to

processor sockets.

2. The memory channels are identified as channels A, B.

®

3. For Intel

sockets (three DIMM sockets p

Xeon® 3400 Series, each socket can support a maximum of six DIMM

er channel), which can support a maximum of six

DIMM sockets.

4. The Intel

populated on the processor socket. It has an Integ

The IMC provides two DDR3

autonomous

5. The DIMM id

channel and the proc

the first sl

® ®

Xeon 3400 Series processor on the In

tel® Server Board S3420GP is

rated Memory Controller (IMC).

channels and groups DIMMs on the board into an

memory.

entifiers on the silkscreen on the board provide information about the

essor socket to which they belong. For example, DIMM_A1 is

ot on channel A.

3.2.5.3 Memory Upgrade Rules

Upgrading the system memory requires careful positioning of the DDR3 DIMMs based on the

follo in

w g factors:

Existing DDR3 DIMM population

DDR3 DIMM characteristics

Op

timization techniques used by the Intel® Nehalem processor to maximize memory

bandwidth

In the Independent Channel mode, all DDR3 channels operate independently. Slot-to-slot DIMM

matching is not required across channels (for example, A1 and B1 do not have to match each

other in terms of size, organization, and timing). DIMMs within a channel do not have to match

in terms of size and organization, but they operate in the minimal common frequency. Also,

Independent Channel mode can be used to support single DIMM configuration in channel A and

in the Single Channel mode.

Revision 1.0

Intel order number E65697-003

19

Page 34

Functional Architecture IntelP®P Server Board S3420GP TPS

Channel A Channel B

RDIMM

UDIMM

A1 A2 A3 B1 B2 B3

X

X X

X X X

X

X X

X X X X

X X

X X X X X

X X X X X X

X

X X

X

X X

X X

X

X

X X

X

X

X X

You must observe the following general rules when selecting and configuring memory to obtain

the best performance from the system.

1. DDR3 RDIMMs must always be populated using a fill-farthest method.

2. DDR3 UDIMMs must always be populated on DIMM A1/A2/B1/B2.

®

3. Intel

Xeon® 3400 Series Processors support either RDIMMs or UDIMMs.

4. RDIMM and UDIMM CANNOT be mixed.

5. The minimal memory set is {DIMMA1}.

6. DDR3 DIMMs on adjacent slots on the same channel do not need to be identical.

Each socket supports a maxim

use the Intel

®

3420 chipset support three slots per DDR3 channel, two DDR3 channels per

um of six slots. Standard Intel

socket, and only one socket is supported on the Intel

®

®

Server Bo

r boards and systems that

serve

ard S3420GP.

3.2.5.4 Memory Configuration Table

Table 4. Memory Configuration Table

This table defines half of the valid memory configurations. You can exchange Channel A DIMMs

with the DIMMs on Channel B to get another half.

20

Intel order number E65697-003

Revision 1.0

Page 35

IntelP®P Server Board S3420GP TPS Functional Architecture

3.3 Intel® 3420 Chipset PCH

The Intel® 3420 Chipset component is the Platform Controller Hub (PCH). The PCH is designed

for use with Intel

®

processor in a UP server platform. The role of the PCH in Intel® Server Board

S3420GP is to manage the flow of information between its eleven interfaces:

DMI interface to Processor

PCI Express* Int

PCI Interface

SATA I

nterface

USB Host Interface

SMBus Host Interface

SPI Interface

LPC interface to IBMC

JTAG interface

LAN interface

ACPI interface

3.4 I/O Sub

-system

erface

Intel® 3420 Chipset PCH provides extensive I/O support.

3.4.1 PCI Express Interface

Two diffe nfigurations on single board are depende

z

z Intel

z Intel

There is one 32-bit, 33-MHz 5-V PCI slot.

Compatibility with the PCI addressing model is maintained to ensure all existing applications

and drivers operate unchanged.

The PCI Express* configuration uses standard mechanisms as defined in the PCI Plug-andPlay specification. The initial recovered clock speed of 1.25 GHz results in 2.5 Gb/s/direction,

which provides a 250-MB/s communications channel in each direction (500 MB/s total). This is

close to twice the data rate of classic PCI. The fact that 8b/10b encoding is used accounts for

the 250 MB/s where quick calculations would imply 300 MB/s. The external graphics ports

support 5.0 GT/s speed as well. Operating at 5.0 GT/s results in twice as much bandwidth per

lane as compared to 2.5 GT/s operation.

rent PCI-E co nt on different board SKUs:

Intel® Server Board S3420GPLX

One PCI-E X16 slot connected to the PCI-E ports of CPU. Two PCI-E x8 slots and one SAS

module connected to PCI-E ports

connected to the PCI-E ports of PCH.

®

Server Board S3420GPLC

One PCI-E X16 slot and o

E x8 slot connected to the PCI-E ports of PCH.

®

Server Board S3420GPV

>

<TBD

ne PCI-E X8 slot connected to the PCI-E ports of CPU. One PCI-

of PCIe switch. One PCI-E X8 slot and one PCI-E x4 slot

Revision 1.0

Intel order number E65697-003

21

Page 36

Functional Architecture IntelP®P Server Board S3420GP TPS

When operating with two PCI Express* controllers, each controller can operate at either 2.5

GT/s or 5.0 GT/s. The PCI Express* architecture is specified in three layers: Transaction Layer,

Data Link Layer, and Physical Layer. The partitioning in the component is not necessarily along

these same boundarie

s.

3.4.2 Serial ATA Support

The Int 0 Chipset has two integrated

DMA operation on up to six ports and supports data transfer rates of up to 3.0 GB/s (300 MB/s).

The SATA controller contains two

AHCI mode using memory space.

el® 342 SATA host controllers that support independent

modes of operation – a legacy mode using I/O space and an

Softwa ses legacy mode does not have AH

re that u CI capabilities. The Intel

®

3420 Chipset

supports the Serial ATA Specification, Revision 1.0a. The Ibex Peak also supports several

optional sections of the Serial ATA II: Extensions to Serial ATA 1.0 Specification, Revision 1.0

(AHCI support is required for some elements).

3.4.2.1 Intel

The Intel

AHCI (see above for details on

RAID capability provides high-p

ports of PCH. Matrix RAID support is provided to allow multiple RAID levels to be combin

®

Matrix Storage Technology

® ®

3420 Chipset provides support for Intel Matrix Storage Technology, providing both

AHCI) and integrated RAID functionality. The industry leading

erformance RAID 0, 1, 5, and 10 functionality on up to six SATA

ed on

a single set of hard drives, such as RAID 0 and RAID 1 on two disks. Other RAID features

include hot spare support, SMART alerting, and RAID 0 autos replace. Software components

include an Option ROM for pre-boot configuration and boot functionality, a Microsoft Windows*

compatible driver, and a user interface to configure and manage the RAID capability of the

®

Intel

3420 Chipset.

3.4.3 USB 2.0 Support

On the Intel® 3420 Chipset, the USB controller functionality is provided by the dual EHCI

controllers with an interface for up to ten USB 2.0 ports. All ports a

and low-speed capable.

Four external connectors are located on the back edge of the server board.

Two internal 2x5 header (J1E2 and J1D1) are pro

vided, each supporting two optional

USB 2.0 ports.

One port on internal vertical connector to support NIC.

One port on 1x4pin (J1J2) on-board header to support floppy.

re high-speed, full-speed,

3.4.3.1

Native USB Support

During the power-on self test (POST), the BIOS initializes and configures the USB subsystem.

The BIO ble low o ice

S is capa of initializing and using the fol ing types f USB dev s.

USB Specification-compliant keyboards

USB Specification-compliant mouse

USB Specification-compliant storage devices that utilize bulk-only transport mechanism

USB devices are scanned to determine if they are required for booting.

22

Intel order number E65697-003

Revision 1.0

Page 37

IntelP®P Server Board S3420GP TPS Functional Architecture

The BIOS supports USB 2.0 mode of operation, and as such supports USB 1.1 and USB 2.0

compliant devices and host controllers.

During the p

US e

B d vices and a short beep is emitted to indicate such an action. For example, if a USB

re-boot phase, the BIOS automatically supports the hot addition and hot removal of

device is hot plugged, the BIOS detects the device insertion, initializes the device, and makes it

available to the user. During POST, when the USB controller is initialized, it emits a short beep

for c

ea h USB device plugged into the system as they were all just “hot added”.

Onl n

y o -board USB controllers are initialized by BIOS. This does not prevent the operating

system

3.4.3.2

from supporting any available USB controllers including add-in cards.

Legacy USB Support

The BIOS supports PS/2 emulation of USB keyboards and mouse. During POST, the BIOS

initializes and configures the root hub ports and searches for a keyboard and/or a mouse on the

USB hub and then enables the devices that are recognized.

3.5 Optional

The Intel® Server Board S3420G vides a llation

of an op

tional Intel

Entry RAID Module AX SASMOD is detected, I

switches to the SAS Mezzanine slot. The option

SASMOD includes a SAS1064e controller that supports x4 PCI Express* link widths and

AXX4

®

SAS

®

Intel D Module AXX4SASMOD

SAS Entry RAI

PLX pro SAS Mezzanine slot (J2H1) for the insta

Entry R ule AX S

AID Mod

X4

X4SASMOD. Once the optional Intel

the x4 PCI Express* links from the PC

al Intel

®

SAS Entry RA

ID Module

®

SA

is a single-function PCI Express* end-point device.

The SAS controller supports the SAS protocol as described in the Serial Attached SCSI

Standard, version 1.0, and also supports SAS 1.1 features. A 32-bit external memory bus off th

SAS1064e controller provides an interface for Fla

sh ROM and NVSRAM (Non-volatile Static

Random Access Memory) devices.

The optional Intel

®

SAS Entry RAID Module AXX4SASMOD provid

es four SAS connectors that

support up to four hard drives with a non-expander backplane or up to eight hard drives with an

expander backplane.

e

3.6 Integrated Baseboard Management Controller

The ServerEngines* LLC Pilot II Integrated BMC is provided by an embedded ARM9 controller

and associated peripheral functionality that is required for IPMI-based server managem

Firmware usage of these hardware features

The following is a summary of the Integrated

Serv E

er ngines* LLC Pilot II Integrated BMC:

250 MHz 32-bit ARM9 Processor

Memory Management Unit (MMU)

Two 10/100 Ethernet Controllers with NC-SI support

16-bit DDR2 667 MHz interface

Dedicated RTC

Revision 1.0

Intel order number E65697-003

is platform-dependant.

BMC management hardware features used by the

ent.

23

Page 38

Functional Architecture IntelP®P Server Board S3420GP TPS

12 10-bit ADCs

Eight Fan Tachometers

Four PWMs

Battery-backed Chassis Intrusion I/O Register

JTAG Master

Six I

General-purpose I/O Ports (16 direct, 64 serial)

2

C interfaces

Additionally, the ServerEngines* Pilot II part integrates a super I/O module with the following

features:

KCS/BT Interface

Two 16C5

50 Serial Ports

Serial IRQ Support

12 GPIO Ports (shared with BMC)

LPC to SPI Bridge

SMI and PME Support

The Pilot II contains an integrated KVMS subsystem and graphics controller with the following

features:

USB 2.0 f

USB 1.1 interface for legacy PS/2 to USB bridging

or keyboard, mouse, and storage devices

Hardware Video Compression for text and graphics

Hardware encryption

2D Graphics Acceleration

DDR2 g

raphics memory interface

Up to 1600x1200 pixel resolution

PCI Express* x

1 support

24

Revision 1.0

Intel order number E65697-003

Page 39

IntelP®P Server Board S3420GP TPS Functional Architecture

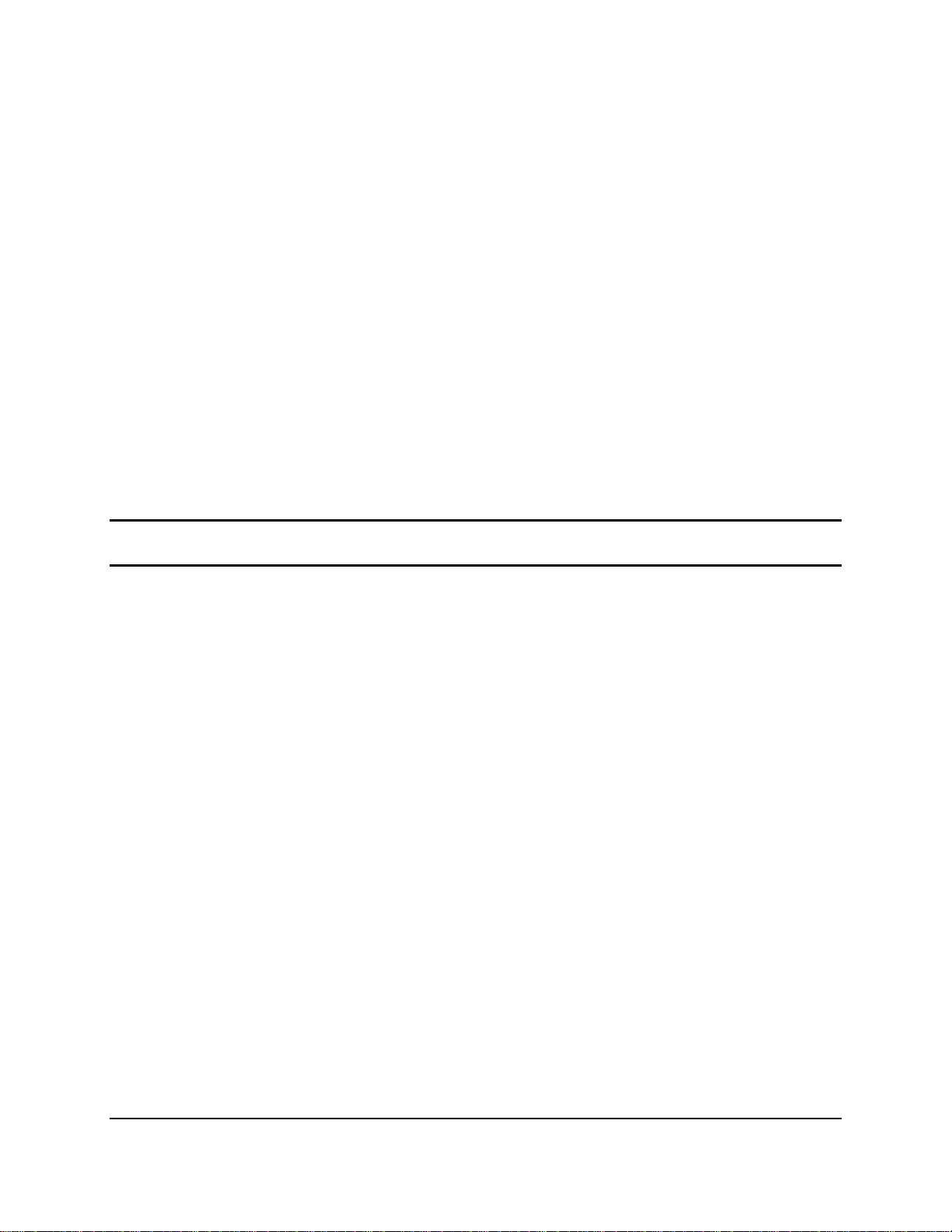

Integrated BMC Block Diagram

Interrupt

Controller

ARM926EJ-S

16K D & I

Cache

RTC &

General Purpose

TImers (3)

BMC & KVMS Subsystem

UART (3) GPIO

LPC

Interface

To Host

LPC

Interface

LPC to SPI

Flash Bridge

BMC & KVMS Subsystem Graphics Subsystem

Fan Tach (12)

PWM (4)

UART

(3)

Watchdog

Timer

I2C

(6)

KCS

BT &

Mailboxes

ADC

Thermal

Ethernet

MAC with

RMII (2)

System

Wakeup

Control

Real Time Clock

Interface

(external RTC)

USB

to Host

USB 1.1

&

USB 2.0

Crypto

Accelerator

Code

Memory

LPC Master,

JTAG Master,

& SPI FLash

DDR-II

16-bit

Memory

Controller

Graphics

Controller

JTAG

er

Mast

DDR-II

(up to

667MHz)

Video

Output

PCIe x1

Interface

Figure 13. Integrated BMC Hardware

3.6.1 Integrated BMC Embedded LAN Channel

The Integrated BMC hardware includes two dedicated 10/100 network interfaces.

Interface 1:

be shared with the host. Only one NIC may be enabled for management traffic at any time. To

change the NIC enabled for management traffic, please use the “Write LAN Channel Port” OEM

IPMI command. The default active interface is port 1 (NIC1).

Interface 2: This interface is available from the optional RMM3 which is a dedicated

management NIC that is not shared with the host.

For these channels, support can be enabled for IPMI-over-LAN and DHCP.

For security reasons, embedded LAN channels have the following default settings:

IP Address: Static

All users disabled

This interface is available from either of the available NIC ports in system that can

3.6.2 Optional RMM3 Advanced Management Board

On the Intel

management board serves two purposes:

Revision 1.0

®

Server Board S3420GPLX provides RMM3 module. RMM3 advanced

Intel order number E65697-003

25

Page 40