Page 1

Intel® Server Boards

S3200SH/S3210SH

Technical Product Specification

Intel Order Number: E14960-004

Enterprise Platforms and Services Division

Revision 1.3

April 2008

Page 2

Revision History Intel® Server Boards S3200SH/S3210SH TPS

Revision History

Date Revision

Number

Sept. 2007 1.0 Initial release.

Oct. 2007 1.1 Added new updates.

Jan. 2008 1.2 Corrected some document errors.

Apr. 2008 1.3 Added Intel® Embedded Server RAID Technology.

Modifications

Revision 1.3

ii

Page 3

Intel® Server Boards S3200SH/S3210SH TPS Disclaimers

Disclaimers

Information in this document is provided in connection with Intel® products. No license, express

or implied, by estoppel or otherwise, to any intellectual property rights is granted by this

document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel

assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to

sale and/or use of Intel products including liability or warranties relating to fitness for a particular

purpose, merchantability, or infringement of any patent, copyright or other intellectual property

right. Intel products are not intended for use in medical, life saving, or life sustaining

applications. Intel may make changes to specifications and product descriptions at any time,

without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked

"reserved" or "undefined." Intel reserves these for future definition and shall have no

responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

This document contains information on products in the design phase of development. Do not

finalize a design with this information. Revised information will be published when the product is

available. Verify with your local sales office that you have the latest datasheet before finalizing a

design.

The Intel Server boards Snow Hill family may contain design defects or errors known as errata

which may cause the product to deviate from published specifications. Current characterized

errata are available on request.

This document and the software described in it is furnished under license and may only be used

or copied in accordance with the terms of the license. The information in this manual is

furnished for informational use only, is subject to change without notice, and should not be

construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or

liability for any errors or inaccuracies that may appear in this document or any software that may

be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a

retrieval system, or transmitted in any form or by any means without the express written consent

of Intel Corporation.

Intel, Pentium

®

, Itanium, and Xeon are trademarks or registered trademarks of Intel Corporation.

*Other brands and names may be claimed as the property of others.

Copyright © Intel Corporation 2008.

Revision 1.3

iii

Page 4

Table of Contents Intel® Server Boards S3200SH/S3210SH TPS

Table of Contents

1. Introduction ..........................................................................................................................1

1.1 Chapter Outline........................................................................................................ 1

1.2 Server Board Use Disclaimer .................................................................................. 1

2. Server Board Overview........................................................................................................2

2.1 Server Board Feature Set........................................................................................ 2

2.2 Server Board Layout.............................................................................................. 10

2.2.1 Server Board Mechanical Drawings ...................................................................... 11

3. Functional Architecture.....................................................................................................13

3.1 Processor Sub-System .......................................................................................... 16

3.1.1 Processor Voltage Regulator Down (VRD)............................................................ 16

3.1.2 Reset Configuration Logic .....................................................................................16

3.2 Intel® 3200/3210 Chipset ....................................................................................... 17

3.2.1 Intel® 3200/3210 Chipset MCH: Memory Control Hub........................................... 17

3.2.2 PCI-X* Hub (PXH)..................................................................................................20

3.2.3 Intel® ICH9R: I/O Controller Hub 9R ...................................................................... 21

3.3 Memory Sub-System .............................................................................................27

3.3.1 Memory Configuration ........................................................................................... 27

3.3.2 Memory DIMM Support.......................................................................................... 30

3.4 I/O Sub-System .....................................................................................................30

3.4.1 PCI Subsystem ...................................................................................................... 30

3.4.2 Interrupt Routing .................................................................................................... 32

3.5 BMC Controller ...................................................................................................... 37

3.6 PCIe* to PCI-X* Bridge 6702PXH (PXH-V) (LX Board SKU Only) ........................ 38

3.7 Clock Generator..................................................................................................... 39

3.8 Super I/O ...............................................................................................................39

3.9 GigE Controller 82541PI........................................................................................ 39

3.10 GigE PHY ..............................................................................................................40

3.11 On Board Components .......................................................................................... 40

3.11.1 Video Support ........................................................................................................ 40

3.12 Replacing the Back-Up Battery.............................................................................. 42

4. System BIOS.......................................................................................................................43

4.1 BIOS Identification String....................................................................................... 43

Revision 1.3

iv

Page 5

Intel® Server Boards S3200SH/S3210SH TPS Table of Contents

4.2 Logo / Diagnostic Window ..................................................................................... 44

4.3 BIOS Setup Utility .................................................................................................. 44

4.3.1 Operation ............................................................................................................... 44

4.3.2 Server Platform Setup Screens ............................................................................. 47

4.4 Loading BIOS Defaults .......................................................................................... 74

4.5 Multiple Boot Blocks ..............................................................................................74

4.6 Recovery Mode...................................................................................................... 74

4.7 Intel® Matrix Storage Manager...............................................................................75

4.8 Intel® Embedded Server RAID Technology II Support........................................... 75

5. Error Reporting and Handling...........................................................................................76

5.1 Error Handling and Logging...................................................................................76

5.1.1 Error Sources and Types....................................................................................... 76

5.1.2 Error Logging via SMI Handler .............................................................................. 77

5.1.3 SMBIOS Type 15................................................................................................... 77

5.1.4 Logging Format Conventions................................................................................. 77

5.2 Error Messages and Error Codes .......................................................................... 79

5.2.1 Diagnostic LEDs .................................................................................................... 79

5.2.2 POST Code Checkpoints....................................................................................... 80

5.2.3 POST Error Messages and Handling .................................................................... 83

5.2.4 POST Error Beep Codes ....................................................................................... 84

5.2.5 POST Error Pause Option ..................................................................................... 84

6. Connectors and Jumper Blocks .......................................................................................85

6.1 Power Connectors ................................................................................................. 85

6.1.1 Main Power Connector .......................................................................................... 85

6.2 Intel® Riser Card for L SKU.................................................................................... 86

6.3 SMBus Connector.................................................................................................. 86

6.4 Front Panel Connector........................................................................................... 86

6.5 I/O Connectors....................................................................................................... 87

6.5.1 VGA Connector...................................................................................................... 87

6.5.2 NIC Connectors ..................................................................................................... 87

6.5.3 SATA Connectors .................................................................................................. 88

6.5.4 Floppy Controller Connector.................................................................................. 88

6.5.5 Serial Port Connectors........................................................................................... 89

6.5.6 Keyboard and Mouse Connector ........................................................................... 90

6.5.7 USB Connector...................................................................................................... 90

Revision 1.3

v

Page 6

Table of Contents Intel® Server Boards S3200SH/S3210SH TPS

6.6 Fan Headers .......................................................................................................... 91

6.7 Miscellaneous Headers and Connectors ............................................................... 91

6.7.1 Back Panel I/O Connectors ...................................................................................91

6.7.2 Chassis Intrusion Header ......................................................................................92

6.7.3 HDD Active LED Header ....................................................................................... 92

6.7.4 IPMB ...................................................................................................................... 92

6.7.5 HSBP ..................................................................................................................... 92

6.7.6 SATA SGPIO ......................................................................................................... 92

6.8 Jumper Blocks ....................................................................................................... 93

7. Absolute Maximum Ratings ..............................................................................................94

7.1 Mean Time Between Failures (MTBF) Test Results.............................................. 94

7.2 Calculated Mean Time Between Failures (MTBF)................................................. 94

8. Design and Environmental Specifications.......................................................................95

8.1 Power Budget ........................................................................................................ 95

8.2 Power Supply Specifications .................................................................................96

8.2.1 Power Timing Requirements ................................................................................. 96

8.2.2 Dynamic Loading ................................................................................................... 99

8.2.3 AC Line Transient Specification............................................................................. 99

8.2.4 AC Line Fast Transient (EFT) Specification ........................................................100

8.3 Product Regulatory Compliance .......................................................................... 100

8.3.1 Product Safety Compliance ................................................................................. 100

8.3.2 Product EMC Compliance – Class A Compliance ............................................... 101

8.3.3 Certifications / Registrations / Declarations ......................................................... 101

8.3.4 RoHS ................................................................................................................... 102

8.3.5 Product Regulatory Compliance Markings .......................................................... 103

8.4 Electromagnetic Compatibility Notices ................................................................104

8.4.1 FCC (USA)........................................................................................................... 104

8.4.2 ICES-003 (Canada) ............................................................................................. 105

8.4.3 Europe (CE Declaration of Conformity) ............................................................... 105

8.4.4 VCCI (Japan) ....................................................................................................... 105

8.4.5 Taiwan Declaration of Conformity (BSMI)............................................................ 105

8.4.6 Korean Compliance (RRL)................................................................................... 106

8.4.7 CNCA (CCC-China)............................................................................................. 106

8.5 Mechanical Specifications ...................................................................................107

9. Hardware Monitoring .......................................................................................................110

Revision 1.3

vi

Page 7

Intel® Server Boards S3200SH/S3210SH TPS Table of Contents

9.1 Chassis Intrusion ................................................................................................. 110

Glossary...................................................................................................................................111

Reference Documents............................................................................................................114

Revision 1.3

vii

Page 8

List of Figures Intel® Server Boards S3200SH/S3210SH TPS

List of Figures

Figure 1. Intel

Figure 2. Intel

Figure 3. Intel

Figure 4. Intel

Figure 5. Intel

®

Server Board S3210SHLX Diagram.....................................................................7

®

Server Board S3210SHLC Diagram..................................................................... 8

®

Server Board S3200SH-L/S3200SH-V SKU Diagram.......................................... 9

®

Server Board S3210SHLC ................................................................................. 10

®

Server Board S3210SHLX – Hole and Component Positions............................11

Figure 6. Intel® Server Boards S3210SHLC/S3200SHL/S3200SHV – Hole and Component

Positions...............................................................................................................................12

Figure 7. Memory Bank Label Definition..................................................................................... 29

Figure 8. Interrupt Routing Diagram ...........................................................................................34

Figure 9. Intel

®

ICH9R Interrupt Routing Diagram ...................................................................... 35

Figure 10. PXH-V Interrupt Routing Diagram .............................................................................36

Figure 11. Setup Utility — Main Screen Display ......................................................................... 48

Figure 12. Setup Utility — Advanced Screen Display................................................................. 50

Figure 13. Setup Utility — Processor Configuration Screen Display .......................................... 52

Figure 14. Setup Utility — Memory Configuration Screen Display.............................................. 54

Figure 15. Setup Utility — ATA Controller Configuration Screen Display................................... 55

Figure 16. Setup Utility — Serial Port Configuration Screen Display.......................................... 57

Figure 17. Setup Utility — USB Controller Configuration Screen Display .................................. 58

Figure 18. Setup Utility — PCI Configuration Screen Display ....................................................60

Figure 19. Setup Utility — Security Configuration Screen Display .............................................61

Figure 20. Setup Utility — Server Management Configuration Screen Display.......................... 62

Figure 21. Setup Utility — Console Redirection Screen Display ................................................64

Figure 22. Setup Utility — Server Management System Information Screen Display ................65

Figure 23. Setup Utility — Boot Options Screen Display ............................................................ 66

Figure 24. Setup Utility — Hard Disk Order Screen Display....................................................... 67

Figure 25. Setup Utility — CDROM Order Screen Display ......................................................... 68

Figure 26. Setup Utility — Floppy Order Screen Display............................................................ 68

Figure 27. Setup Utility — Network Device Order Screen Display.............................................. 69

Figure 28. Setup Utility — BEV Device Order Screen Display.................................................... 70

Figure 29. Setup Utility — Boot Manager Screen Display .......................................................... 71

Figure 30. Setup Utility — Error Manager Screen Display.......................................................... 71

Figure 31. Setup Utility — Exit Screen Display........................................................................... 72

Revision 1.3

viii

Page 9

Intel® Server Boards S3200SH/S3210SH TPS List of Figures

Figure 32. Intel

Figure 33. Intel

Figure 34. Intel

®

Server Board S3210SH-LX Back Panel I/O Connectors..................................91

®

Server Board S3210SH-LC / S3200SH-L Back Panel I/O Connectors ............ 91

®

Server Board S3200SH-V Back Panel I/O Connectors....................................92

Figure 35. Output Voltage Timing ............................................................................................... 97

Figure 36. Turn On/Off Timing (Power Supply Signals).............................................................. 98

Figure 37. Intel

®

Server Board S3200SH Mechanical Drawing (TBD)......................................107

Figure 38. Pedestal Mount I/O Shield Mechanical Drawing for the Intel® Server Board S3200SH-

V ......................................................................................................................................... 108

Figure 39. Pedestal Mount I/O Shield Mechanical Drawing for Intel® Server Boards S3200SH-L /

S3210SH-LX ......................................................................................................................109

Revision 1.3

ix

Page 10

List of Tables Intel® Server Boards S3200SH/S3210SH TPS

List of Tables

Table 1. Intel

Table 2. Intel

®

Server Board S3210SHLX Board SKU Layout Reference .................................... 7

®

Server Board S3210SHLC Layout Reference ....................................................... 8

Table 3. Processor Support Matrix .............................................................................................17

Table 4. Segment F Connections ...............................................................................................19

Table 5. Supported DDR2 Modules ............................................................................................ 19

Table 6. Segment E Configuration IDs .......................................................................................21

Table 7. Segment D Arbitration Connections.............................................................................. 21

Table 8 Boot BIOS Destination Selection .................................................................................. 24

Table 9: SPI Required Command Codes................................................................................... 25

Table 10. Memory Bank Labels and DIMM Population Order..................................................... 28

Table 11. Characteristics of Dual/Single Channel Configuration with or without Dynamic Mode29

Table 12. PCI Bus Segment Characteristics............................................................................... 30

Table 13. Segment A Configuration IDs .....................................................................................31

Table 14. Segment A Arbitration Connections............................................................................31

Table 15. PCI AND PCI-X* Interrupt Routing/Sharing ................................................................ 32

Table 16. Interrupt Definitions.....................................................................................................33

Table 17. Video Modes ............................................................................................................... 41

Table 18. BIOS Setup Page Layout............................................................................................ 45

Table 19. BIOS Setup: Keyboard Command Bar........................................................................ 46

Table 20. Setup Utility — Main Screen Fields ............................................................................49

Table 21. Setup Utility — Advanced Screen Display Fields .......................................................51

Table 22. Setup Utility — Processor Configuration Screen Fields.............................................. 52

Table 23. Setup Utility — Memory Configuration Screen Fields................................................. 54

Table 24. Setup Utility — ATA Controller Configuration Screen Fields ...................................... 56

Table 25. Setup Utility — Serial Ports Configuration Screen Fields ........................................... 57

Table 26. Setup Utility — USB Controller Configuration Screen Fields...................................... 59

Table 27. Setup Utility — PCI Configuration Screen Fields........................................................ 60

Table 28. Setup Utility — Security Configuration Screen Fields................................................. 61

Table 29. Setup Utility — Server Management Configuration Screen Fields .............................62

Table 30. Setup Utility — Console Redirection Configuration Fields..........................................64

Table 31. Setup Utility — Server Management System Information Fields ................................ 65

Table 32. Setup Utility — Boot Options Screen Fields ...............................................................66

Revision 1.3

x

Page 11

Intel® Server Boards S3200SH/S3210SH TPS List of Tables

Table 33. Setup Utility — Hard Disk Order Fields....................................................................... 67

Table 34. Setup Utility — CDROM Order Fields......................................................................... 68

Table 35. Setup Utility — Floppy Order Fields............................................................................ 69

Table 36. Setup Utility — Network Device Order Fields ............................................................. 69

Table 37. Setup Utility — BEV Device Order Fields ................................................................... 70

Table 38. Setup Utility — Boot Manager Screen Fields.............................................................. 71

Table 39. Setup Utility — Error Manager Screen Fields ............................................................. 72

Table 40. Setup Utility — Exit Screen Fields .............................................................................. 72

Table 41. Event List .................................................................................................................... 76

Table 42. SMBIOS Type 15 Event Log record format................................................................. 78

Table 43. Event Type Definition Table........................................................................................78

Table 44.: POST Progress Code LED Example .........................................................................80

Table 45. POST Code Checkpoints............................................................................................80

Table 46. POST Error Messages and Handling.......................................................................... 84

Table 47. POST Error Beep Codes ............................................................................................84

Table 48. Power Connector Pin-out (J4G1)................................................................................ 85

Table 49. Auxiliary CPU Power Connector Pin-out (J9B2) ......................................................... 85

Table 50. SMBus Connector Pin-out (J1E1)............................................................................... 86

Table 51. Front Panel 24-Pin Header Pin-out (J1K2) ................................................................. 86

Table 52. VGA Connector Pin-out (J8B1)................................................................................... 87

Table 53. NIC2-Intel

Table 54. NIC1- Intel

®

82541PI (10/100/1000) Connector Pin-out (J5B1)...................................87

®

82566E (10/100/1000) Connector Pin-out (J6B1)...................................88

Table 55. SATA Connector Pin-out (J2K1, J1K1, J1J3, J1H3, J1H2, J1H1) .............................. 88

Table 56. Legacy 34-pin Floppy Connector Pin-out (J3K1) ........................................................ 88

Table 57. External DB9 Serial A Port Pin-out (J8B1).................................................................. 89

Table 58. Keyboard and Mouse PS/2 Connectors Pin-out (J9A1).............................................. 90

Table 59. USB Connectors Pin-out (J5B1) ................................................................................. 90

Table 60. Optional USB Connection Header Pin-out (J1G1)...................................................... 91

Table 61. Four-pin Fan Headers Pin-out (J4D1, J1K2,J7K1,J4K1J6B2).................................... 91

Table 62. Chassis Intrusion Header (J1B2) Pin-out.................................................................... 92

Table 63. HDD LED Header (J1J1) Pin-out ................................................................................ 92

Table 64. Absolute Maximum Ratings ........................................................................................ 94

Table 65. MTBF Data.................................................................................................................. 94

Table 66. Power Budget ............................................................................................................95

Table 67. Server Board Power Supply Voltage Specification ..................................................... 96

Revision 1.3

xi

Page 12

List of Tables Intel® Server Boards S3200SH/S3210SH TPS

Table 68. Output Voltage Timing ................................................................................................ 96

Table 69. Turn On/Off Timing ..................................................................................................... 98

Table 70. Transient Load Requirements..................................................................................... 99

Table 71. AC Line Sag Transient Performance .......................................................................... 99

Table 72. AC Line Surge Transient Performance ..................................................................... 100

Table 73. Product Certification Markings .................................................................................. 103

Revision 1.3

xii

Page 13

Intel® Server Boards S3200SH/S3210SH TPS List of Tables

< This page intentionally left blank. >

Revision 1.3

xiii

Page 14

Page 15

Intel® Server Boards S3200SH/S3210SH TPS Introduction

1. Introduction

This Technical Product Specification (TPS) provides a high-level technical description for the

®

Intel

Server Boards S3200SH/S3210SH. It details the architecture and feature set for all

functional sub-systems that make up the server boards.

Note: The term “server board” is used throughout the document and applies to all four board

SKUs. When exceptions occur, the specific board is called out by name.

1.1 Chapter Outline

This document is divided into the following chapters:

Chapter 1 – Introduction

Chapter 2 – Server Board Overview

Chapter 3 – Functional Architecture

Chapter 4 – System BIOS

Chapter 5 – Platform Management Architecture

Chapter 6 – Error Reporting and Handling

Chapter 7 – Connectors and Jumper Blocks

Chapter 8 – Absolute Maximum Ratings

Chapter 9 – Design and Environmental Specifications

Chapter 10 – Hardware Monitoring

Appendix A – Integration and Usage Tips

Glossary

Reference Documents

1.2 Server Board Use Disclaimer

Intel Corporation server boards support add-in peripherals and contain a number of high-density

VLSI and power delivery components that need adequate airflow to cool. Intel ensures through

its own chassis development and testing that when Intel server building blocks are used

together, the fully integrated system will meet the intended thermal requirements of these

components. It is the responsibility of the system integrator who chooses not to use Intel

developed server building blocks to consult vendor datasheets and operating parameters to

determine the amount of air flow required for their specific application and environmental

conditions. Intel Corporation cannot be held responsible if components fail or the server board

does not operate correctly when used outside any of their published operating or non-operating

limits.

Revision 1.3

1

Page 16

Server Board Overview Intel® Server Boards S3200SH/S3210SH TPS

2. Server Board Overview

The Intel® Server Boards S3210SHLX, S3200SHL, S3200SHV, and S3200SHLC are monolithic

printed circuit boards with features that are designed to support the entry server market.

2.1 Server Board Feature Set

• All board SKUs are based on the Intel® 3200/3210 Chipset

• Supports processors in LGA775 package

• 800/1066/1333 MHz Front Side Bus speed

• Four DDR2 667/800MHz unbuffered DIMM memory sockets with or without ECC

• Supports ICH9R I/O Controller, interfaced with MCH via DMI

• LX board SKU supports the following I/O slots:

− One PCIe* x16 connector to be used as a x16 link from chipset (if a VGA adapter

is inserted into this slot, the VGA card will only work at PCIe* x1 speed; this is a

chipset limitation)

− One PCIe* x8 connector to be used as a PCIe* x8 link from chipset

− Two PCI-X* 133MHz, 64bit connectors

− One PCI 5V, 32bit, 33MHz connector

• LC board SKU supports following I/O slots:

− One PCIe* x16 connector to be used as a x16 link from chipset (if a VGA adapter

is inserted into this slot, the VGA card will only work at PCIe* x1 speed; this is a

chipset limitation)

− One PCIe* x8 connector to be used as a PCIe* x8 link from chipset

− One PCIe* x8 connector routed to PCIe* x4 bus from ICH9R

− Two PCI 5V, 32bit, 33MHz connectors

• L and V board SKUs support the following I/O slots:

− One PCIe* x16 connector to be used as a x8 link from chipset (if a VGA adapter

is inserted into this slot, the VGA card will only work at PCIe* x1 speed; this is a

chipset limitation)

− One PCIe* x8 connector routed to the PCIe* x4 bus from the ICH9R

− Two PCI 5V, 32bit, 33MHz connectors

• Onboard ServerEngines* LLC Pilot II controller (Integrated BMC ), supports the following

functions:

− Integrated 2D video controller on PCIe* x1

− Super I/O on LPC

− Baseboard Management Controller (BMC) based on ARM946E-S

Revision 1.3

2

Page 17

Intel® Server Boards S3200SH/S3210SH TPS Server Board Overview

• Winbond* PC8374L super I/O chip interfaced to the ICH9R through LPC, supports the

following:

− PS/2 keyboard/mouse

− FDD

− Six SATA II connectors

• Five USB 2.0 ports: two ports on USB/LAN combo connectors at the rear of the server

board, two ports via onboard headers, and one port on an internal vertical connector

• Two Gigabit Ethernet devices interfaced to the ICH9R to support two rear panel RJ45

connectors with integrated magnetics; one is through PCIe* x1, the other one is through

PCI32

• ACPI power management

• System monitoring (temperature, voltage, and fans)

• VRD11 for processor

The server board supports the following feature set:

• Processor and Front Side Bus (FSB) support

®

Xeon® processor 3000 series, Dual-Core Intel® Xeon®

®

Xeon® processor 3200 series, and

• Intel

− Supports Dual-Core Intel

processor 3100 series, Quad-Core Intel

Quad-Core Intel

− Supports Intel

− Supports Intel

®

3200/3210 Chipset components

®

− Intel

− Intel

− Intel

3200/3210 Memory Controller Hub (MCH)

®

ICH9R I/O Controller

®

6702 PXH-V PCI-X* Hub (LX board SKU only)

®

Xeon® processor 3300 series.

®

dual-core technology

®

Extended Memory System 64 Technology (Intel® EM64T)

• Memory System

− Four DIMM sockets supporting DDR2 667/800MHz DIMMs

− Data bandwidth per channel of 4.2GB/s or 8.4GB/s in dual channel when using

DDR2 667MHz

− Support for up to two DDR2 channels for a total of four DIMMs (2 DIMMs /

channel) providing up to 8GB max memory capacity

− Support for 512MB, 1GB and 2GB DRAM modules

Notes: 1. The server board does not support DDR2-533 DIMMs.

2. The server board does not support 256MB DIMMs.

• I/O Subsystem

• Clock

− CK-505 compliant System Clock Generator

Revision 1.3

3

Page 18

Server Board Overview Intel® Server Boards S3200SH/S3210SH TPS

• Video

• ServerEngines* Integrated BMC

• External 32MB (or greater) DDR2 533MHz memory

• VGA Video external connector

• Peripheral Interface (PCIe* and PCI)

− Two different PCIe* configurations on single board, dependent on board SKU

LX board SKU: One PCIe* x16 and one PCIe* x8 slot, connected to the

PCIe* ports of the MCH

LC board SKU: One PCIe* x16 and one PCIe* x8 slot, connected to the

PCIe* ports of the MCH; one PCIe* x8 slot, connected to PCIe* x4

interface of the ICH

L and V board SKUs: Two PCIe* x8 slots, one connected to the PCIe* x8

interface of the MCH and the other connected to the PCIe* x4 interface of

the ICH

• HDD Interface

− Six SATA II ports, 300MB per second

• USB

− Two USB 2.0 ports connected to the server rear panel

− Two USB 2.0 ports connected to headers on the server board

− One USB 2.0 port connected to an internal vertical connector

• LAN

− One Gigabit Ethernet device (Tabor, MAC + PHY) connect to PCI interfaces on

the ICH9R.

− One Gigabit Ethernet PHY (Nineveh) connected to ICH9R thru GLC/LCI

interface. (not in V board SKU)

− Two 10/100/1000 Base-TX interfaces through RJ45 connectors with integrated

magnetics

− Link and speed LEDs on the RJ45 connector

• Power Supply

− SSI EEB Power Connectors

− On board Power generation

VRD 11 processor core voltage

1.2V regulator for FSB VTT

1.25V regulator for MCH core and I/O

1.05V regulator for ICH9R core

1.5V regulator for the ICH9R I/O

1.8V for DDR2 and 0.9V for DDR2 termination

3.3V SB voltage regulator

1.8V AUX, 1.2V AUX, and 0.9V AUX for Integrated BMC and its DDR2

memory

Revision 1.3

4

Page 19

Intel® Server Boards S3200SH/S3210SH TPS Server Board Overview

• System Management

− Processor on die temperature monitoring through PECI interface

− Board temperature measurement

− Fan speed monitoring and control

− Voltage monitoring

− IPMI-based server management

• Battery

− Socketed, Lithium coin cell-3V

• Sockets

− One LGA775 processor (Socket-T)

− Four DDR2 DIMM Sockets

− One battery (CR2032)

• Legacy Interfaces

− Serial

− Floppy

− PS2 keyboard

− PS2 mouse

• Power Management Modes Supported (ACPI Sleep states)

− S0 – Full on

− S1 - Power-on-suspend

− S4 – Suspend to Disk

− S5 – Soft on/off

• Connectors List

− Four 240-Pin DDR2 DIMM connectors

− PCIe*, PCI-X*, and PCI connectors (see SKU specific information)

− One RJ45 Connectors with magnetics and LEDs

− One stacked RJ45 with magnetics and LEDs and two-USB combo connector

− 34 pin floppy drive connector

− One serial port headers

− Dual stacked PS/2 keyboard and mouse connector

− USB connectors (two stacked on the rear panel and three on the server board

headers)

− SSI-EEB ATX power connectors

− One 4-pin auxiliary power connector

− One stacked DB-15 VGA/DB-9 Serial port connector

− Six 7-pin SATA II connectors

− 60-pin XDP connector

− Four 4-pin, 0.10” pitch fan headers

− 24-Pin, SSI-EEB, front panel connector

Revision 1.3

5

Page 20

Server Board Overview Intel® Server Boards S3200SH/S3210SH TPS

− One 4-pin SATA RAID Key

− One 2-pin intrusion detection

• BIOS

− EFI BIOS

• Power Management

− Support for Power Management of all capable components

− ACPI compliant motherboard and BIOS

− Sleep Switch and dual mode LED indicator

• Manufacturing

− Surface mount technology. Single sided assembly for LC/V board SKUs and

double sided assembly for the LX board SKU

− 6 layer PCB

• Form Factor

− ATX 2.0, 12’’ x 9.6’’, 1U thermally optimized, and SSI TEB Rev 2.11 compatible.

• Universal Serial Bus 2.0 (USB)

− Two external USB ports (located at the rear panel) with an additional internal

header providing two optional USB ports for front panel support

− Supports wake-up from sleeping states S1 and S4 (S3 is not supported)

− Supports legacy keyboard/mouse connections when using a PS2-USB dongle

• LPC (Low Pin Count) bus segment with one embedded device

− Super I/O controller (SMSC* SCH5027D) providing all PC-compatible I/O (floppy,

serial, keyboard, mouse, two serial com ports) and integrated hardware

monitoring.

• SSI-compliant connectors for SSI interface support

• Standard 24-pin SSI front panel, 2x12 main power connector, and 2x4 CPU power

connector

• Fan Support

− 5 general purpose 4-pin fan headers

One 4-pin processor fan header (active heat sink required)

Four 4-pin system fan headers: SYS FAN1, SYS FAN2 and SYS

FAN3 for Intel high density applications to support Intel

System SR1530SH; SYS FAN4 is for use in the Intel

®

Server

®

Entry Server

Chassis SC5299-E

• Diagnostic LEDs to display POST code indicators during boot

• Onboard SATA RAID

− Intel

®

Matrix Storage Technology supports software SATA RAID 0, 1, 10 and 5;

Microsoft Windows* driver support only.

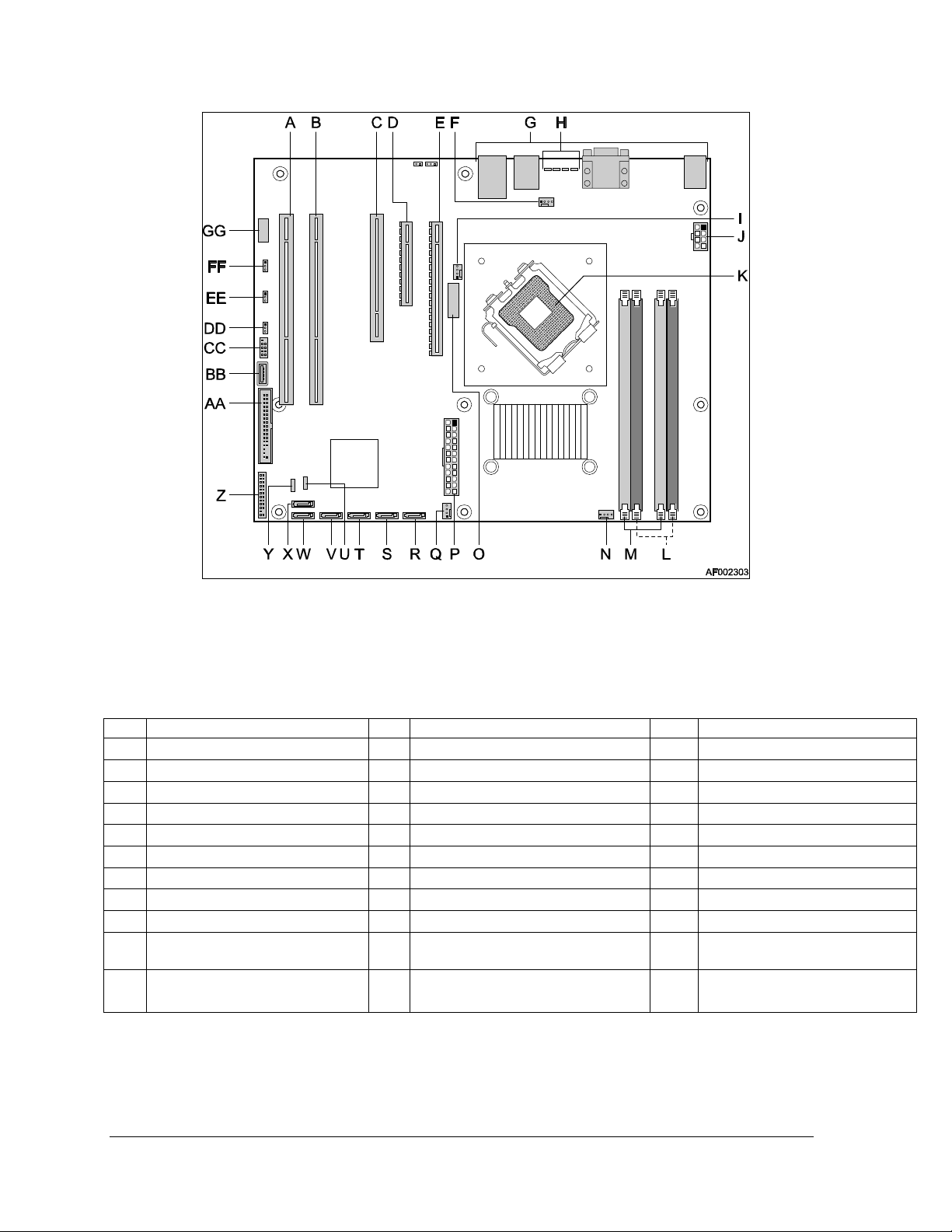

The following figure shows the board layout of the LX board SKU. Each connector and major

component is identified by letter (shown in Table 1).

Revision 1.3

6

Page 21

Intel® Server Boards S3200SH/S3210SH TPS Server Board Overview

Figure 1. Intel® Server Board S3210SHLX Diagram

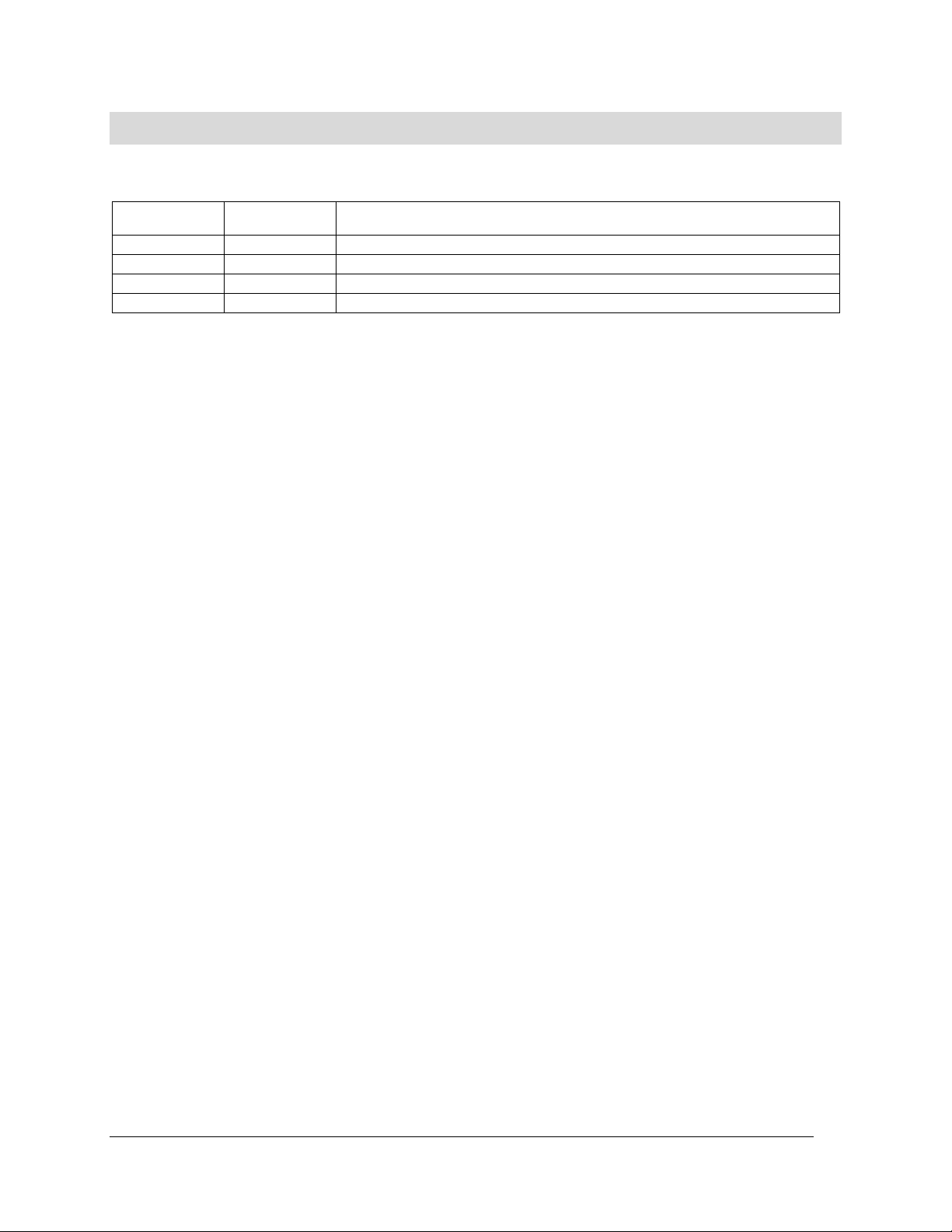

Table 1. Intel® Server Board S3210SHLX Board SKU Layout Reference

Ref Description Ref Description Ref Description

A PCI-X (64bit/133MHz) Slot 1 L Channel 2 DIMM Sockets W SATA 1

B PCI-X (64bit/133MHz) Slot 2 M Channel 1 DIMM Sockets X SATA 0

C PCI 5V (32bit/33MHz) Slot 3 N System Fan 3 Connector Y IPMB

D PCI Express* x8 O Battery Z Front Panel Header

E PCI Express* x16 P Main Power Connector AA Floppy Connector

F System Fan 1 Connector Q System Fan 2 Connector BB Internal USB

G Back Panel Connectors R SATA 5 CC External USB

H Diagnostic LEDs S SATA 4 DD CMOS Clear Jumper

I Processor Fan 1 Connector T SATA 3 EE BIOS Jumper

J 2X4 Aux Power Connector U HSBP FF NIC1 NVM Protect Mode

Jumper

K Processor Socket V SATA 2 GG Serial

Port

Revision 1.3

7

Page 22

Server Board Overview Intel® Server Boards S3200SH/S3210SH TPS

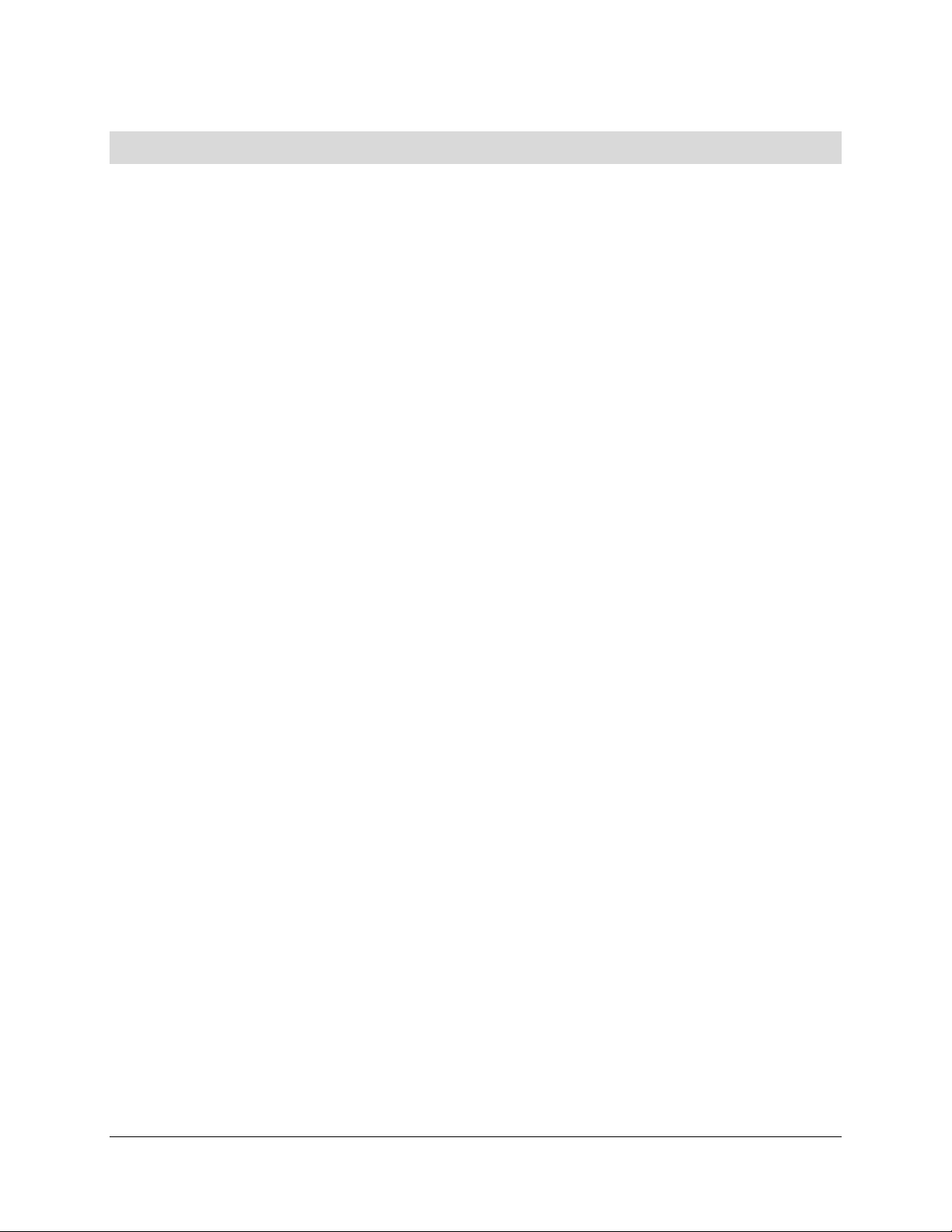

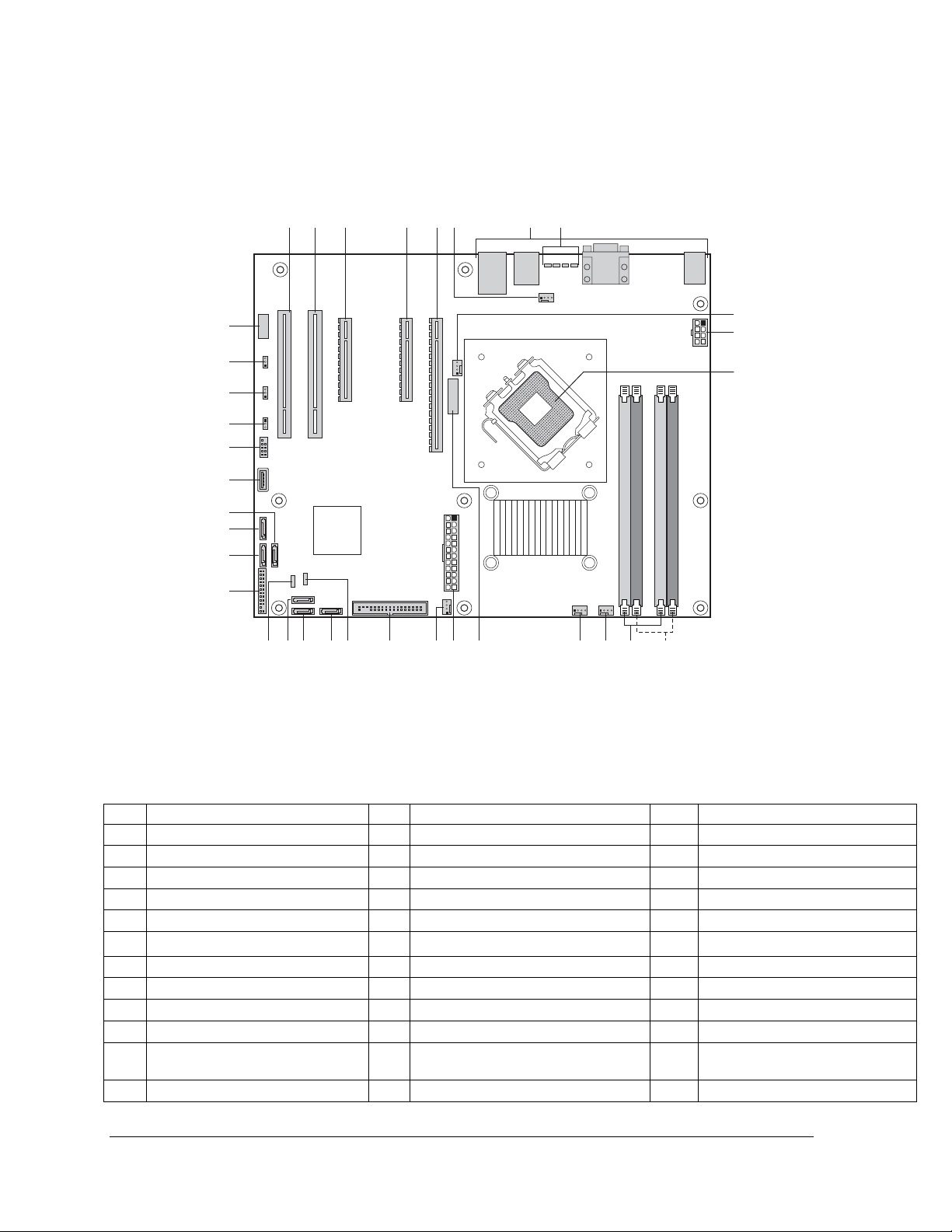

The following figure shows the board layout of the LC board SKU. Each connector and major

component is identified by letter (shown in Table 2).

HH

GG

FF

EE

DD

CC

BB

AA

A B F G H

EDC

I

J

K

Z

Y

VW U RS NOQ P M L

X T

AF002304

Figure 2. Intel® Server Board S3210SHLC Diagram

Table 2. Intel® Server Board S3210SHLC Layout Reference

Ref Description Ref Description Ref Description

A PCI (32bit/33MHz) Slot 1 L Channel 2 DIMM Sockets W SATA 2

B PCI (32bit/33MHz) Slot 2 M Channel 1 DIMM Sockets X IPMB

C PCI Express* x8 (x8 lane) N System Fan 3 Connector Y Front Panel Header

D PCI Express* x8 (x4 lane) O System Fan 4 Connector Z SATA 3

E PCI Express* x16 P Battery AA SATA 5

F System Fan 1 Connector Q Main Power Connector BB SATA 4

G Back Panel Connectors R System Fan 2 Connector CC Internal USB

H Diagnostic LEDs S Floppy Connector DD External USB

I Processor Fan 1 Connector T HSBP EE CMOS Clear Jumper

J 2X4 Aux Power Connector U SATA 0 FF BIOS Jumper

K Processor Socket V SATA1 GG NIC1 NVM Protect Mode

Jumper

HH Serial Port

Revision 1.3

8

Page 23

Intel® Server Boards S3200SH/S3210SH TPS Server Board Overview

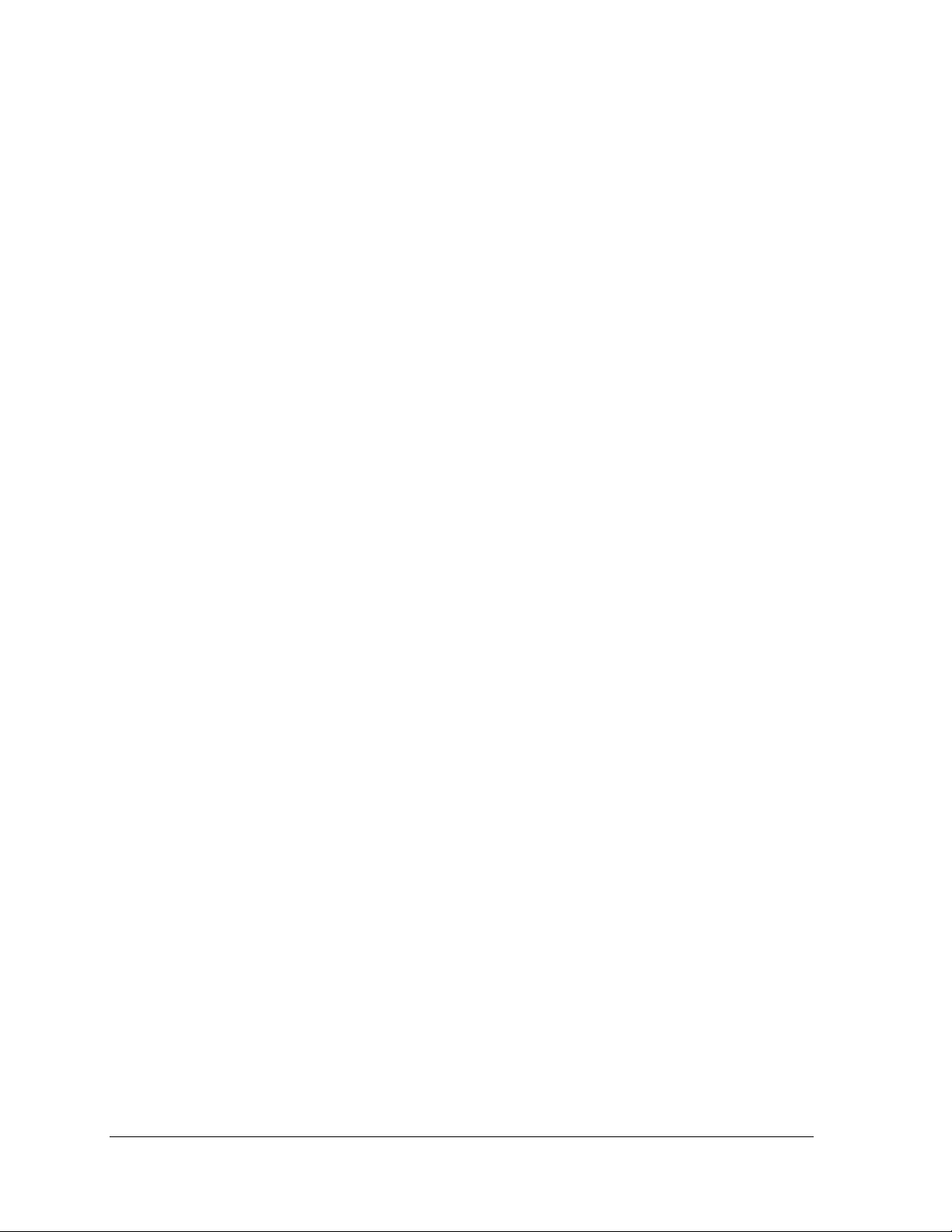

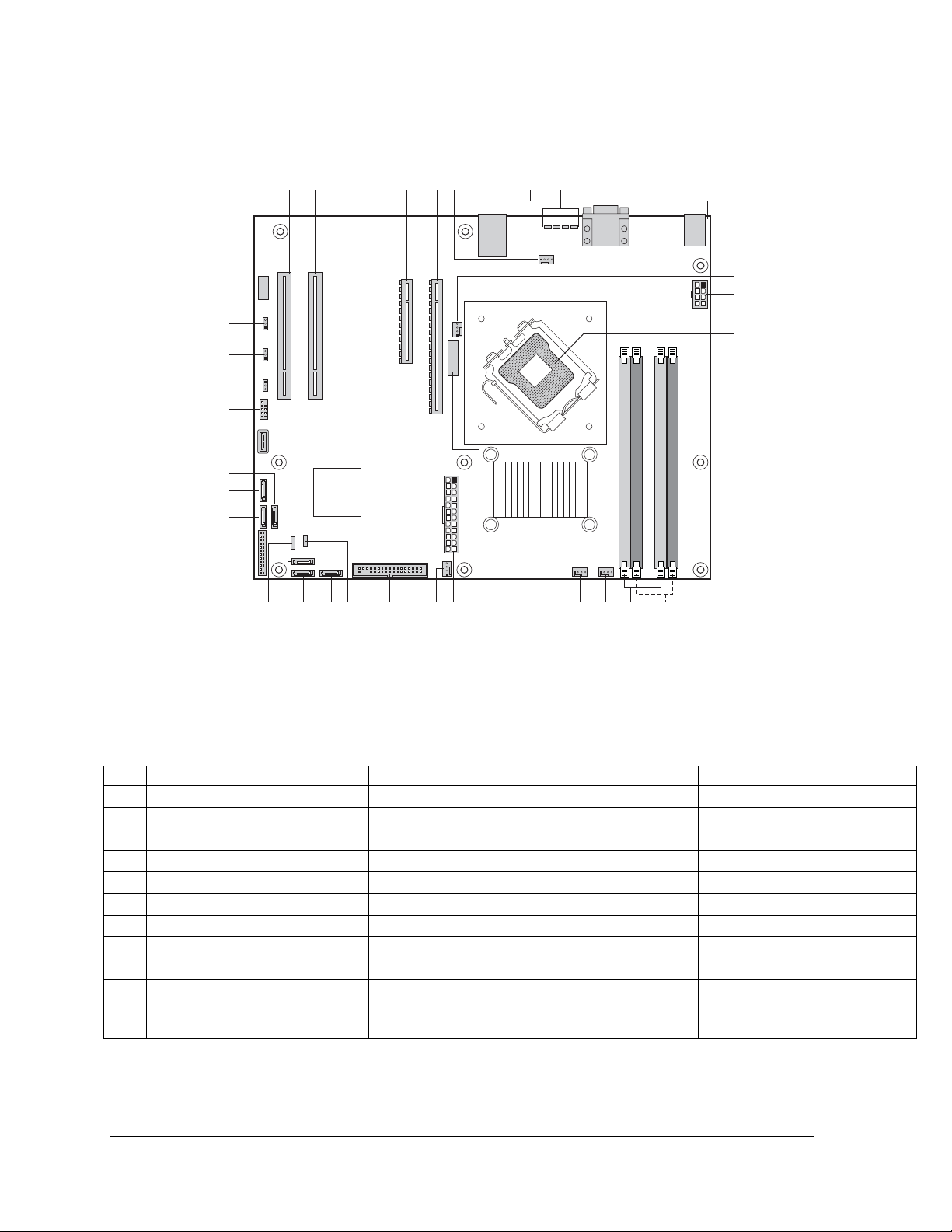

The following figure shows the board layout of the Intel® Server Boards S3200SHL/S3200SHV.

Each connector and major component is identified by letter (shown in Table 3).

GG

FF

EE

DD

CC

BB

AA

Z

Y

X

A B E F G

UV T QR MNP O L K

W S

DC

AF002310

H

I

J

Figure 3. Intel® Server Board S3200SH-L/S3200SH-V SKU Diagram

®

Table3. Intel

Ref Description Ref Description Ref Description

A PCI (32bit/33MHz) Slot 1 L Channel 1 DIMM Sockets W IPMB

B PCI (32bit/33MHz) Slot 2 M System Fan2 Connector X Front Panel Header

C PCI Express* x8 (x4 lane) N System Fan3 Connector Y SATA 3

D PCI Express* x16 (x8 lane) O Battery Z SATA 5

E System Fan 1 Connector P Main Power Connector AA SATA 4

F Back Panel Connectors Q System Fan2 BB Internal USB

G Diagnostic LEDs R Floppy Connector CC External USB

H Processor Fan 1 Connector S HSBP DD CMOS Clear Jumper

I 2X4 Aux Power Connector T SATA 0 EE BIOS Jumper

J Processor Socket U SATA1 FF NIC1 NVM Protect Mode

K Channel 2 DIMM Sockets V SATA 2 GG Serial Port

Server Boards S3200SH-L/S3200SH-V Component Layout Reference

Jumper

Revision 1.3

9

Page 24

Server Board Overview Intel® Server Boards S3200SH/S3210SH TPS

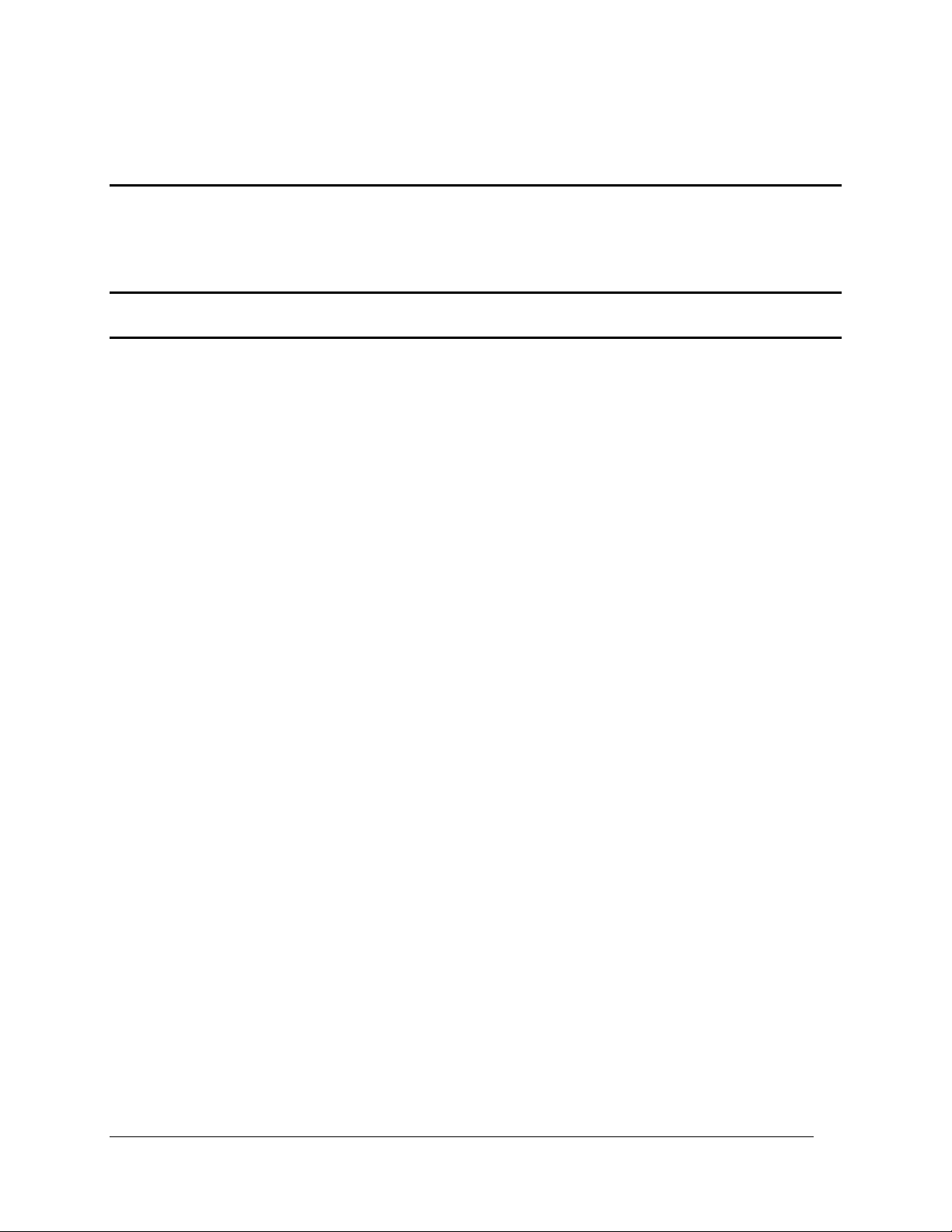

2.2 Server Board Layout

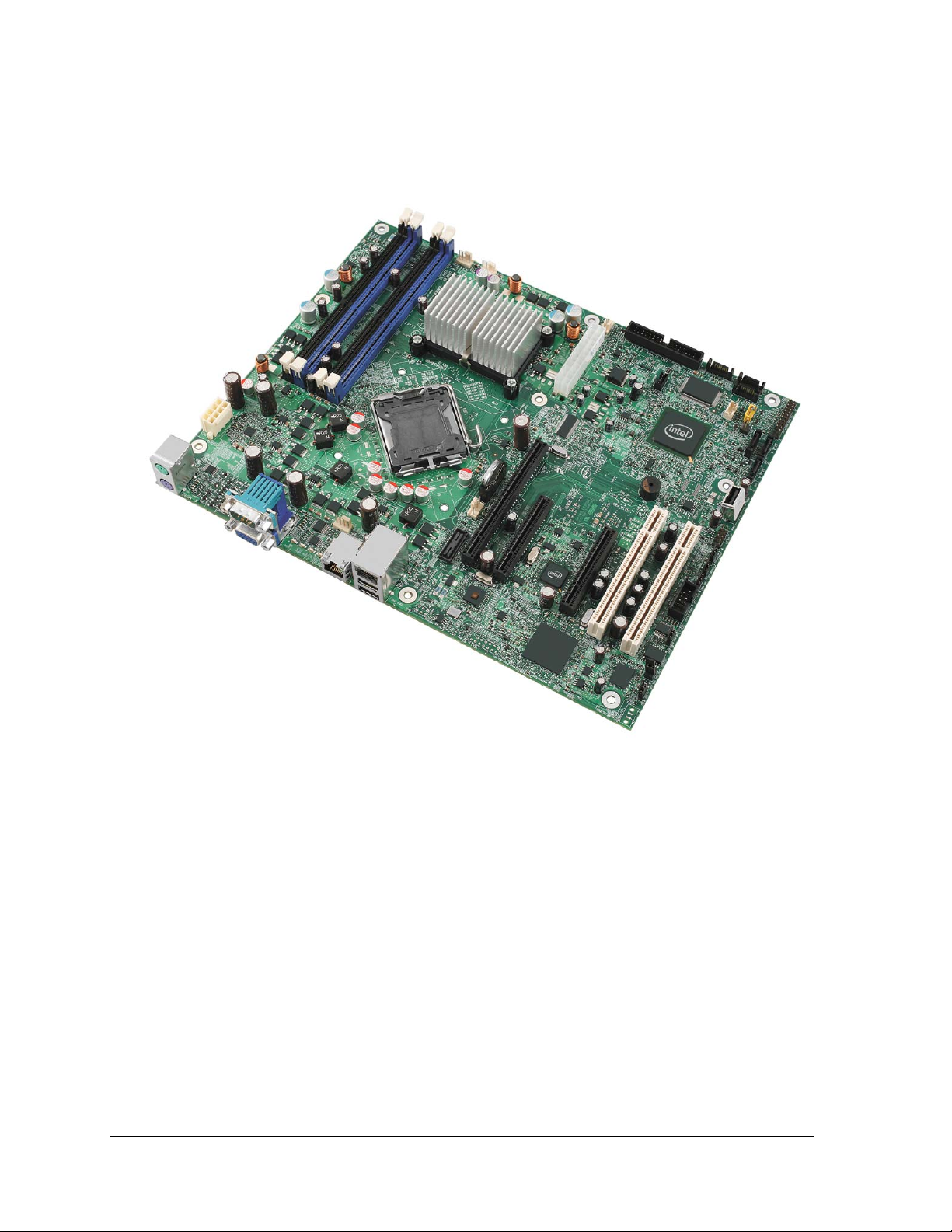

Figure 4. Intel® Server Board S3210SHLC

Revision 1.3

10

Page 25

Intel® Server Boards S3200SH/S3210SH TPS Server Board Overview

2.2.1 Server Board Mechanical Drawings

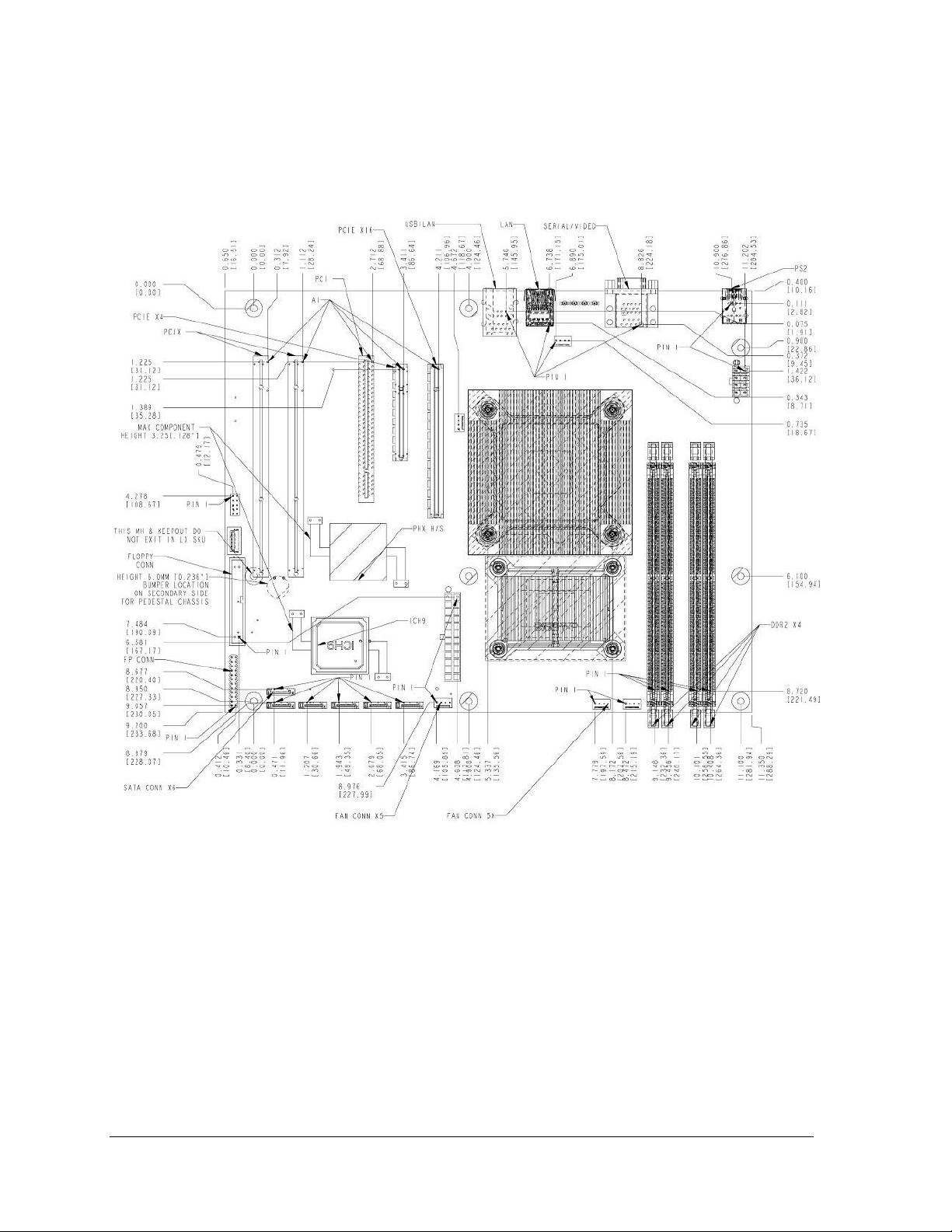

Figure 5. Intel® Server Board S3210SHLX – Hole and Component Positions

Revision 1.3

11

Page 26

Server Board Overview Intel® Server Boards S3200SH/S3210SH TPS

Figure 6. Intel® Server Boards S3210SHLC/S3200SHL/S3200SHV – Hole and Component Positions

Revision 1.3

12

Page 27

Intel® Server Boards S3200SH/S3210SH TPS Functional Architecture

3. Functional Architecture

This chapter provides a high-level description of the functionality associated with the

architectural blocks that make up the Intel

®

Server Boards S3200SH/S3210SH.

Revision 1.3

13

Page 28

Functional Architecture Intel® Server Boards S3200SH/S3210SH TPS

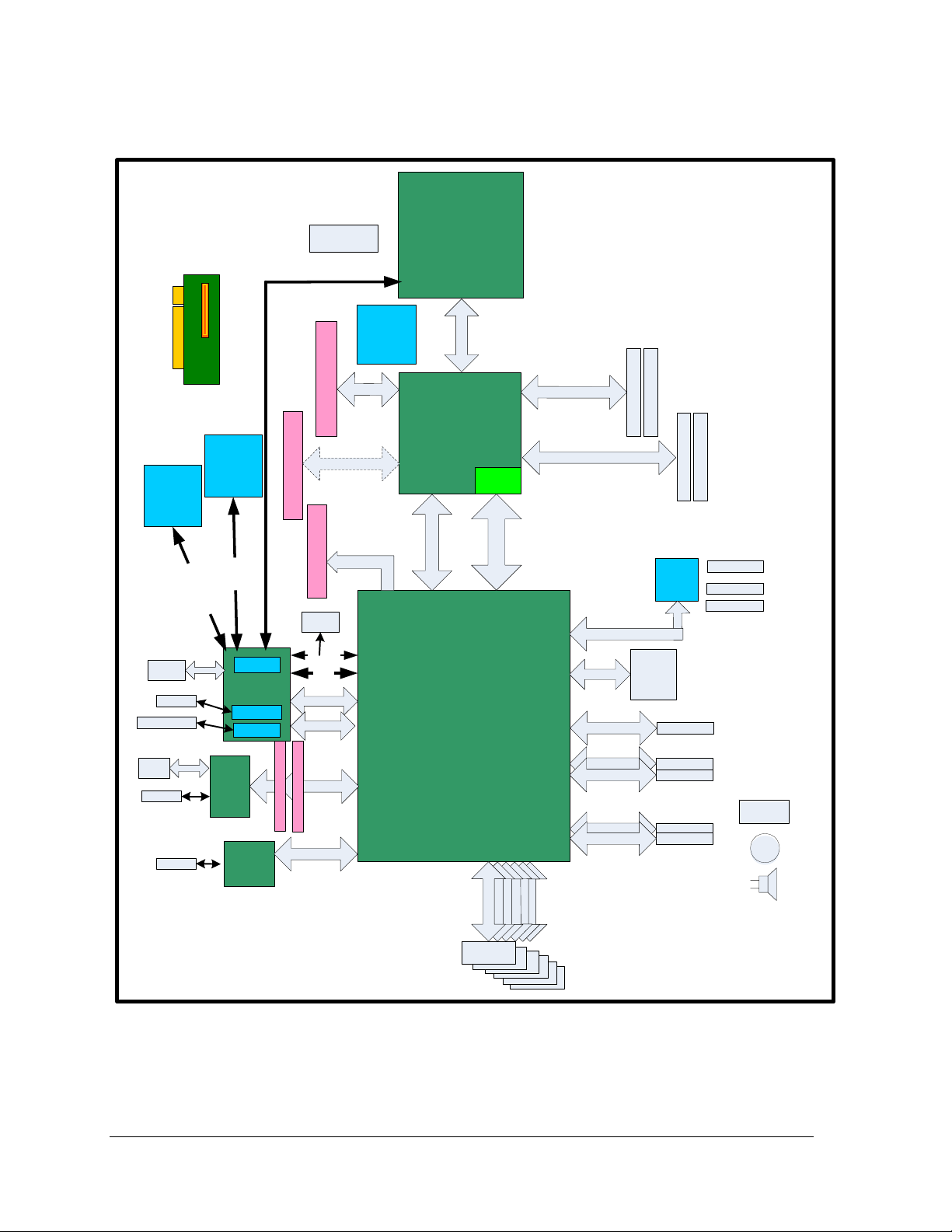

S3200SH/S3210SH LC/L/V SKU BLOCK DIAGRAM

Intel® Xeon®

ITP/XDP

1U Riser at Slot 6

PECI

Processors

3000 sequence

Fan

Speed

Control

Circuitry

Boot

Flash

VGA

Serial 1/2

RJ45

RJ45

CK505

Clock

SYNTH

X

1

6

P

C

E

I

-

PCI-E x16 (Slot 6)

Thermal/

voltage

Sensors

S

M

P

W

B

u

M

s

/

T

A

CH

BMC

SPI

Integrated

BMC

Video

SIO

SPIEEP

Tabor

Ninevah

PHY

PCI-E x8 (Slot 5)

FRU

SMBus

X1 PCI-E

PCI 33MHz

PCI 32 (Slot 1)

PCI 32 (Slot 2)

GLCI/LCI

X8 PCI-E

X4 PCI-E

PCI-E x8 (Slot 4)

USB

LPC

1333/1066/

800 FSB

Intel® 3200/

3210 MCH

ME

DMI

Controller

ICH9R

Link

DDR2 667

DDR2 667/800

D

D

I

I

M

/800

M

M

M

0

1

SIO

LPC

SPI

USB 2.0 I. USB

USB 2.0

USB 2.0

USB 2.0

BIOS

Flash

R. USB

R. USB

H. USB

H. USBUSB 2.0*

D

D

I

I

M

M

M

M

1

0

Floppy

Keyboard

Mouse

Front Panel

HDR

Batt

SATA

SATA x6

SATA

SATA

SATA x2

SPKR

Revision 1.3

14

Page 29

Intel® Server Boards S3200SH/S3210SH TPS Functional Architecture

1U Riser at Slot 6

Fan

Speed

Control

Circuitry

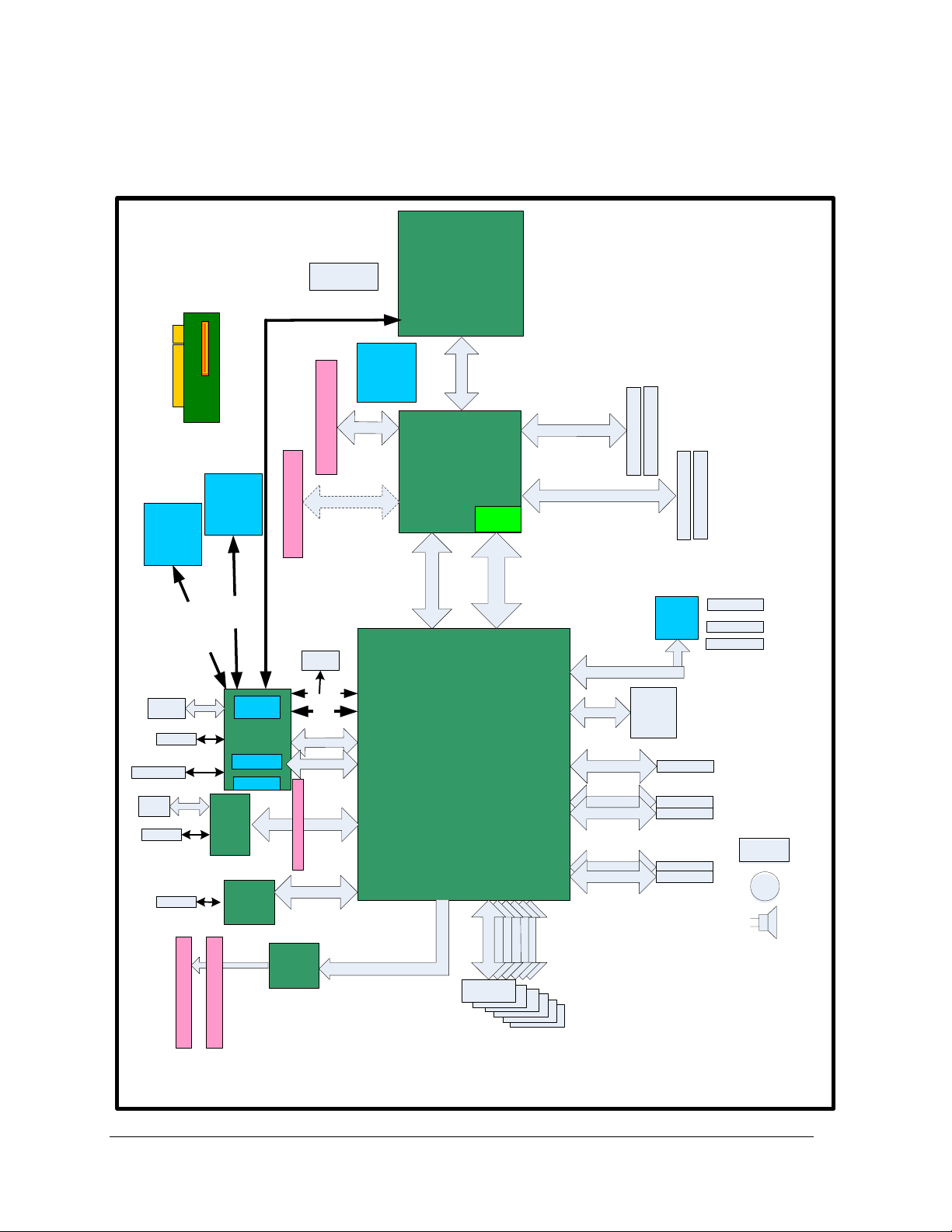

S3200SH/S3210SH SYSTEM LX SKU BLOCK DIAGRAM

Intel® Xeon®

Processors

3000 Sequence

1333/1066/

800 FSB

E

I

-

Intel® 3200/

S3210 MCH

ME

DDR2 667

DDR2 667/800

/800

D

D

I

I

M

M

M

M

0

1

D

D

I

I

M

M

M

M

1

0

Thermal/

voltage

Sensors

PECI

PCI-E x8 (Slot 5)

ITP/XDP

1

X

PCI-E x16 (Slot 6)

X8 PCI-E

CK505

Clock

SYNTH

6

P

C

Boot

Flash

VGA

Serial 1/2

RJ45

RJ45

S

M

P

W

B

u

M

s

/

T

A

CH

FRU

BMC

SPI

Integrated

BMC

Video

SIO

SPIEEP

Tabor

Ninevah

PHY

PCI-X 64/133

SMBus

USB

X

1

LPC

PCI 33MHz

PCI 32 (Slot 4)

GLCI/LCI

PXH

E

-

C

I

P

X4 PCI-E

DMI

ICH9R

Controller

SATA

SATA x6

Link

SATA

SATA

SATA x2

SIO

LPC

SPI

USB 2.0 I. USB

USB 2.0

USB 2.0

USB 2.0

BIOS

Flash

R. USB

R. USB

H. USB

H. USBUSB 2.0*

Floppy

Keyboard

Mouse

Front Panel

HDR

Batt

SPKR

PCI-X 64/133 (Slot 1)

PCI-X 64/133 (Slot 2)

Revision 1.3

15

Page 30

Functional Architecture Intel® Server Boards S3200SH/S3210SH TPS

3.1 Processor Sub-System

The server board supports the following processors:

• Dual-Core Intel

• Dual-Core Intel

• Quad-Core Intel

• Quad-Core Intel

The server board does not support the following processors:

• All Intel 5XX series, 6XX series single core processors

• All Intel 8XX series, 9XX series dual core processors

The processors built on 65nm and 45nm process technology in the 775-land package utilize

Flip-Chip Land Grid Array (FC-LGA4) package technology, and plug into a 775-land LGA

socket, referred to as the Intel

The processors in the 775-land package are based on the same core micro-architecture. They

maintain compatibility with 32-bit software written for the IA-32 instruction set, while supporting

64-bit native mode operation when coupled with supported 64-bit operating systems and

applications.

®

Xeon® processor 3000 series

®

Xeon® processor 3100 series

®

Xeon® processor 3200 series

®

Xeon® processor 3300 series

®

LGA775 socket.

3.1.1 Processor Voltage Regulator Down (VRD)

The server board has a VRD (Voltage Regulator Down) to support one processor. It is compliant

with the VRD 12 DC-DC Converter Design Guide Line and provides a maximum of 125A.

The board hardware monitors the processor VTTEN (Output enable for VTT) pin before turning

on the VRD. If the VTTEN pin of the processors is not asserted, the Power ON Logic will not

turn on the VRD.

3.1.2 Reset Configuration Logic

The BIOS determines the processor stepping and processor cache size through the CPUID

instruction. The processor information is read at every system power-on.

Note: The processor speed is the processor power-on reset default value. No manual processor

speed setting options exist either in the form of a BIOS setup option or jumpers.

Revision 1.3

16

Page 31

Intel® Server Boards S3200SH/S3210SH TPS Functional Architecture

Table 3. Processor Support Matrix

Process Name Socket

Dual-Core Intel® Xeon®

processor 3000 series

Quad -Core Intel® Xeon®

processor 3200 series

Dual-Core Intel® Xeon®

processor 3100 series

Dual-Core Intel® Xeon®

processor 3300 series

®

Intel

LGA775

®

Intel

LGA775

®

Intel

LGA775 TBD TBD 1333MHZ

Intel® LGA775 TBD TBD 1333MHZ

Core

Frequency

1.86GHz –

2.66GHz

2.13GHz –

2.40GHz

Cache size FSB Frequency

2MB or 4MB 1066MHz

8MB 1066MHz

3.2 Intel

The server board is designed around the Intel® 3200/3210 Chipset. The chipset provides an

integrated I/O bridge and memory controller, and a flexible I/O subsystem core (PCI Express*).

The chipset consists of three primary components.

3.2.1

The Intel

The role of the MCH in the system is to manage the flow of information between its four

interfaces:

• Processor Interface (FSB)

• System Memory Interface (DDR2)

• DMI interface to ICH9R South Bridge

• PCI Express* connectivity to one or two PCIe* x8 connectors

The feature list of the MCH includes:

• Processor / Host Interface

• System Memory Controller

• DMI Interface

®

3200/3210 Chipset

Intel® 3200/3210 Chipset MCH: Memory Control Hub

®

3200/3210 Chipset is designed for use with Intel® processors in a UP server platform.

− Supports LGA775 processors in a UP System configuration

− 200/266/333 MHz FSB Clock frequency

− GTL+ bus drivers with integrated GTL termination resistors

− Supports 512Mbit and 1Gbit memory technologies

− DDR2 – 667, 800 MHz

− 8GB addressable memory

− Supports unbuffered, ECC and non-ECC DIMMs

− No support for DIMMs less than 512MB and memory speeds less than 667MHz

Revision 1.3

17

Page 32

Functional Architecture Intel® Server Boards S3200SH/S3210SH TPS

− Interface to ICH9R South Bridge

− 100 MHz reference clock shared with PCIe* interface(s)

• PCIe* x8 Interface

− Connected to two PCIe* X8 connectors as shown in the block diagram

− Compliant with the PCIe* base specification

The MCH accepts access requests from the host (processor) bus and directs those accesses to

memory or to one of the PCI Express* or PCI buses. The MCH monitors the host bus,

examining addresses for each request. Accesses may be directed to the following:

• A memory request queue for subsequent forwarding to the memory subsystem

• An outbound request queue for subsequent forwarding to one of the PCI Express* or

PCI buses

The MCH also accepts inbound requests from the Intel

®

ICH9R. The MCH is responsible for

generating the appropriate controls to control data transfer to and from memory.

The MCH is a FC-BGA device and uses the proven components of the following previous

generations:

• Hub interface unit

• PCI Express* interface unit

• DDR2 memory interface unit

The MCH incorporates an integrated PCI Express* interface. The PCI Express* interface allows

the MCH to directly interface with the PCI Express* devices. The MCH also increases the main

memory interface bandwidth and maximum memory configuration with a 72-bit wide memory

interface.

The MCH integrates the following main functions:

• An integrated high performance main memory subsystem

• A PCI Express* bus which provides an interface to the PCI Express* devices (Fully

compliant to the PCI Express* Base Specification, Rev 1.0a)

• A DMI which provides an interface to the Intel

®

ICH9R

Other features provided by the MCH include the following:

• Full support of ECC on the processor bus

• Twelve deep in-order queue, two deep defer queue

• Full support of un-buffered DDR2 ECC DIMMs

• Support for 512MB, 1GB and 2GB DDR2 memory modules

Revision 1.3

18

Page 33

Intel® Server Boards S3200SH/S3210SH TPS Functional Architecture

3.2.1.1 Segment F PCIe* x8

The MCH PCIe* Lanes 0~7 provide a x8 PCIe* connection directly to the MCH. This resource

can support x1, x4, and x 8 PCIe* add-in cards or cards through the I/O riser when using the

riser slot for the L board SKU.

Table 4. Segment F Connections

Lane Device

Lane 0~7 Slot 6 (PCI Express* x16 with 8 Lanes layout)

3.2.1.2 MCH Memory Sub-System Overview

The MCH supports a 72-bit wide memory sub-system that can support a maximum of 8 GB of

DDR2 memory using 2GB DIMMs. This configuration needs external registers for buffering the

memory address and control signals. The four chip selects are registered inside the MCH and

need no external registers for chip selects.

The memory interface runs at 667/800 MT/s. The memory interface supports a 72-bit wide

memory array. It uses seventeen address lines (BA [2:0] and MA [13:0]) and supports 512MB,

1GB, and 2GB DRAM densities. The DDR DIMM interface supports single-bit error correction,

and multiple bit error detection.

3.2.1.3 DDR2 Configurations

The DDR2 interface supports up to 8GB of main memory and supports single- and doubledensity DIMMs. The DDR2 can be any industry-standard DDR2. The following table shows the

DDR2 DIMM technology supported.

Table 5. Supported DDR2 Modules

DDR2-667/800 Un-buffered

SDRAM Module Matrix

DIMM

Capacity

512MB 64M x 72 256Mbit 32M x 8 18 / 2 / 4 13 / 2 / 10

512MB 64M x 72 512Mbit 64M x 8 9 / 1 / 4 14 / 2 / 10

1GB 128M x 72 512Mbit 64M x 8 18 / 2 / 4 14 / 2 / 10

1GB 128M x 72 1Gbit 128M x 8 9 / 1 / 8 14 / 4 / 10

2GB 256M x 72 2GB 128M x 8 18 / 2 / 8 14 / 8 / 10

DIMM

Organization

SDRAM

Density

SDRAM

Organization

# SDRAM

Devices/rows/Banks

# Address bits

rows/Banks/column

3.2.1.4 Memory Population Rules and Configurations

There are a few rules that must be followed when populating memory. The server board

supports two DDR2 DIMM slots for channel A, and two DDR2 DIMM slots for channel B. They

are placed in a row and numbered from 0 to 3 with DIMM0 being closest to the MCH. The four

slots are partitioned with channel A representing the channel A DIMMs (DIMM0 and DIMM1)

and channel B representing the channel B DIMMs (DIMM2 and DIMM3).

Revision 1.3

19

Page 34

Functional Architecture Intel® Server Boards S3200SH/S3210SH TPS

Please note the following memory population rules:

• If dual channel operation is desired, channel A and channel B must be populated

identically (i.e., same capacity)

• Use DDR2 667/800 memory only

• The speed used on all the channels is the slowest DIMM in the system

• ECC or non-ECC DIMMs

• Can mix different memory technologies (size and density)

• Single Channel Mode (either channel may be used): DIMM slots (within the same

channel) may be populated in any order

• Dual Channel Interleaved Mode: DIMM slots may be populated in any order as long as

the total memory in each channel is the same.

• Dual Channel Asymmetric Mode: DIMM slots may be populated as one wishes (any

order)

3.2.2 PCI-X* Hub (PXH)

PXH-V: PCI-X* Hub (LX board SKU only) The PXH-V hub is a peripheral chip that performs

PCI/PCI-X* bridging functions between the PCI Express* interface and the PCI/PCI-X* bus. The

PXH-V contains two PCI bus interfaces that can be independently configured to operate in PCI

(33 or 66 MHz), PCI-X* Mode1 (66,100,133), for either 32 or 64 bits.

3.2.2.1 Segment E 64bit/133MHz PCI-X* Subsystem

One 64-bit PCI-X* bus segment is directed through the PXH-V. This PCI-X* segment (segment

E) provides the following:

• Two 3.3V 64-bit PCI-X* slots

On Segment E, PCI-X* is capable of speeds up to 133MHz operation and supports full-length

PCI and PCI-X* adapters.

3.2.2.1.1 Device IDs (IDSEL)

Each device under the PCI-X* hub bridge has its IDSEL signal connected to one bit of AD

[31:16], which acts as a chip select on the PCI-X bus segment in configuration cycles. This

determines a unique PCI-X* device ID value for use in configuration cycles. The following table

shows the bit to which each IDSEL signal is attached for P64-C devices and a corresponding

device description.

Revision 1.3

20

Page 35

Intel® Server Boards S3200SH/S3210SH TPS Functional Architecture

Table 6. Segment E Configuration IDs

IDSEL Value Device

18 PCI-X* Slot 1 (64bit/66-133MHz) (LX board SKU only)

17 PCI-X* Slot 2 (64bit/66-133MHz) (LX board SKU only)

3.2.2.1.2 Segment E Arbitration

PXH-V supports two PCI masters: two PCI-X* slots or one riser slot. All PCI masters must

arbitrate for PCI access using resources supplied by the PXH-V. The host bridge PCI interface

(PXH-V) arbitration lines REQx* and GNTx* are a special case in that they are internal to the

host bridge. The following table defines the arbitration connections.

Table 7. Segment D Arbitration Connections

Baseboard Signals Device

PCIX REQ_N1/GNT_N1 PCI-X Slot 1 (64bit/66-133MHz) (LX board SKU only)

PCIX REQ_N0/GNT_N0 PCI-X Slot 2(64bit/66-133MHz) ( LX board SKU only)

3.2.3 Intel® ICH9R: I/O Controller Hub 9R

3.2.3.1 Direct Media Interface (DMI)

DMI is the name given to the chip-to-chip connection between the Memory Controller Hub and

the ICH9. DMI is a x4 link that mostly adheres to the PCI Express* specification. Deviations of

the DMI from standard PCI Express* specifications are described in the ICH9 CSPEC.

3.2.3.2 Controller Link (M-Link)

Controller Link is the name given to the interconnect that connects the north bridge (MCH) to

the LAN Controller in the ICH9. The Management Engine (ME) resides in the MCH and

communicates with the ICH9 LAN Controller over this interface.

3.2.3.3 PCIe* Interfaces

The ICH9R provides six PCI Express* root ports (GEN1) which are compliant to PCI Express

Base Specification, Revision 1.1. The PCIe* root ports 1-4 can be statically configured as four x

1 ports, or ganged together to form two x 2 ports, one x 2 with two x1 ports, or one x4 port.

Ports 5 and 6 can only be used as two x1 ports or one x2. Lane reversal is supported for the x4

configuration. Each Root Port fully supports 2.5 Gb/s bandwidth in each direction.

The root ports 1-4 are combined to form a single x4 link connecting to a PCI Express* x8

connector. Port 5 and 6 are used to support the dual GBe LAN channels.

3.2.3.4 Serial ATA II Interface

The ICH9 has an integrated SATA II host controller that supports independent DMA operation

on the six Ports and supports data transfer rates of up to 300 MB/Sec. The SATA II controller

Revision 1.3

21

Page 36

Functional Architecture Intel® Server Boards S3200SH/S3210SH TPS

provides two modes of operation – a legacy mode using I/O space and an AHCI (Advanced

Host Controller Interface) mode using memory space.

3.2.3.5 PCI Interface

The ICH9 PCI interface provides a 33MHz, 3.3V, Revision 2.3 implementation. All PCI signals

are 5V tolerant, except PME#. The ICH9 integrates a PCI arbiter that supports up to seven

external PCI bus masters in addition to the internal ICH9 requests. This allows for combinations

of up to four PCI down devices and/or PCI slots.

The server board supports one NIC, the Tabor Gigabit Ethernet controller, and two PCI slots.

3.2.3.6 Low Pin Count Interface (LPC)

The Low Pin Count interface on the ICH9 provides a low system cost design interface solution

for connecting the Super I/O for the legacy interfaces such as the parallel port, serial port, floppy

drive, etc.

3.2.3.7 Compatibility Modules

The ICH9 incorporates various compatibility modules such as DMA controller, timer/counters

and interrupt controller. The DMA controller incorporates the logic of two 8237 DMA controllers,

with seven independently programmable channels. The channels 0 – 3 are hardwired to 8-Bit,

count-by-byte transfers and channels 5 to 7 are hardwired to 16-Bit, count-by-word transfers.

DMA channel 4 is used to cascade the two 8327 controllers together. The DMA controller is

used to support the LPC DMA.

The LPC DMA is handled through the LDRQ# lines from peripherals and special encoding on

LAD[3:0] from the host.

The timer/counter block contains three counters that are equivalent in function to those found in

one 8254 programmable internal timer. These three counters are combined to provide the

system timer function, and speaker tone. The 14.318MHz oscillator input provides the clock

source for these three counters.

The ICH9 provides an ISA compatible Programmable Interrupt Controller (PIC) that incorporates

the functionality of two 8259 interrupt controllers. Each 8259 supports eight interrupts that are

cascaded via one master controller interrupt 2 for fifteen programmable interrupts. The

interrupts are system timer, keyboard controller, serial ports, parallel ports, floppy disk, mouse,

DMA channels, and mapped PCI based interrupts.

3.2.3.8 Universal Serial Bus (USB) Controller

ICH9 contains two EHCI and six UHCI USB controllers providing support for twelve USB 2.0

ports. All twelve ports are high speed, full-speed, and low speed capable. ICH9’s port routing

logic determines whether a USB port is controlled by one of the UHCI controllers or by the EHCI

controller. USB 2.0 based debug port is also implemented in the ICH9.

Revision 1.3

22

Page 37

Intel® Server Boards S3200SH/S3210SH TPS Functional Architecture

3.2.3.9 Real Time Clock (RTC)

The ICH9 contains a Motorola* MS146818A functionally compatible Real Time Clock with two

128 Byte banks of battery backed RAM. The RTC performs two key functions on the server

board:

• Keeping track of time of day

• Storing system configuration data even when the system is powered down.

The RTC operates on a 32.768 KHz crystal and a 3V lithium battery.

3.2.3.10 GPIO

The ICH9 contains 61 general purpose input/output. The General Purpose Inputs and Outputs

(GPIO) are provided for custom system design.

3.2.3.11 Enhanced Power Management

The ICH9 supports the Advanced Configuration and Power Interface, Version 2.0 (ACPI) that

provides power and thermal management. The ICH9 also supports the Manageability Engine

Power Management Support for new wake events from the MCH Management Engine.

The server board is fully compliant with the Advanced Configuration and Power Interface (ACPI)

specifications, Revision 2.0.

3.2.3.12 System Management Interface

The ICH9 on the server board functions as a SMBus host controller that allows the processor to

communicate with SMBus slaves. This interface is compatible with most I2C devices. The ICH9

also supports slave functionality. The SMBus logic exists in device 31: function 3 configuration

space.

3.2.3.13 Intel

The ICH9 integrates two thermal sensors that monitor the temperature within is die. Those

sensors are used to support the Intel

engine (ME) residing in the MCH and requires SPI flash to host the Intel

®

Quiet System Technology (Intel® QST)

®

QST. The Intel® QST is controlled by the management

®

QST firmware.

Additionally ICH9 integrates four fan speed TACH sensors and three fan speed controllers,

PWMs. This allows the monitoring and controlling of up to four fans on the system. The ICH9

implements a single wire Simple Serial Transport (SST) bus that allows connection of up to five

SST thermal or voltage monitoring devices. The ICH9 also support the Platform Environmental

Control Interface (PECI) that provides access to the CPU thermal data.

The server board does not support ME or Intel

®

QST. Fan speed control is accomplished

through Integrated BMC firmware.

3.2.3.14 Serial Peripheral Interface (SPI)

The Serial Peripheral Interface (SPI) is a 4-pin interface that provides a potentially lower-cost

alternative for the system flash versus the Firmware Hub on the LPC Bus. The ICH9 supports

Revision 1.3

23

Page 38

Functional Architecture Intel® Server Boards S3200SH/S3210SH TPS

two SPI flash components using two separate chip select pins. Each component may be up to

16 MB and operate in SPI Fast Read Instructions and frequencies of 20 MHZ or 33 MHz.

The SPI Interface consists of the following:

• Clock (CLK)

• Master Out Slave In (MOSI)

• Master In Slave Out (MISO)

• Chip Select (CS#)

Communication on the SPI is done with a Master – Slave protocol.

The SPI flash may operate in two operational modes, descriptor and non-descriptor. When

operating in non-descriptor mode the SPI Flash can only support BIOS through register

accesses.

When used in descriptor mode the ICH9 allows a single SPI flash device to store system BIOS,

Firmware and Gigabit Ethernet EEPROM information.

When SPI is selected by the Boot BIOS Destination Strap and a SPI Device is detected by the

ICH9, LPC based BIOS Flash is disabled. The boot destination strap is sampled by the ICH9 at

pins GNT# and SPI_CS1# on the rising edge of the PWROK input. Alternately, the ICH9

support soft straps when operating in Descriptor Mode. The ICH9 reads the soft strap data out

of the SPI device prior to de-assertion of reset to the Manageability Engine and the Host

system.

GNT# and SPI_CS1# are both pulled-up with soft resistors internal to the ICH9. The default

BIOS flash without external straps is the FWH. For manufacturing or debug support, the BIOS

cycles may also be directed to the PCI bridge via the same external flash. Configurations other

than the default will be selected via 2.2K pull-up or pull-down resistors.

The server board will support the boot BIOS Destination Selection as defined in table below.

Table 8 Boot BIOS Destination Selection

GNT# SPI_CS1# ROUTING

0 1 Flash Cycles Routed to SPI (Default)

1 0 Flash Cycles Routed to PCI (Test only)

1 1 Flash Cycles Routed to LPC (Test only)

Revision 1.3

24

Page 39

Intel® Server Boards S3200SH/S3210SH TPS Functional Architecture

The SPI flash meets the following requirements:

• Erase size capability of 4 Kbyte or 64 Kbyte

• SPI device meets the command set per Table 9.

Command and opcode C7h for Full Chip Erase is recommended for streamlined software

development.

• Supports JEDEC ID OP Code 9FH

• Support multiple writes to a page without requiring a preceding command (minimum 512

writes)

• Ignores the upper address bit such that an address of FFFFFFFFh simply aliases to the

top of the flash memory.

• SPI Compatibility Mode 0

• Receipt of an unsupported command causes a completed cycle without impact to the

flash content

• Minimum density of 16 Mb (BIOS + Gbe)

• Power up in an unlocked state or use the write status register to disable write protection.

Table 9: SPI Required Command Codes

Commands Opcode Notes

Write Status 01h

Program Data 02h WRITE DATA / PROGRAM DATA

Read Data 03h

Write Disable 04h

Read Status 05h

Write Enable 06h

Fast Read 0Bh

Enable Write

Status Register

Erase Programmable 256B, 4kbyte, 8 Kbyte or 64 Kbyte erase

JEDEC ID 9Fh

50 or 06h

If Command is supported, 01h must be the

opcode.

If command is supported, 06h must be the

opcode

JEDEC Standard Manufacturer and Device

ID read method is defined in Standard

JESD21-C, PRN03-NV1.

The SPI Flash Memory device is the Atmel* AT26DF321 a 32-megabit, 2.7 to 3.6 volt serial

interface FLASH memory, Intel part number D64145-001/D64145-002. The AT26DF321

supports the block erase command opcodes 20H and D8H providing respectively 4-Kbytes or

64-Kbytes block erase sizes. This is installed directly onto the server board without the use of

sockets.

3.2.3.15 Manageability

The ICH9 integrates several functions designed to manage the system and lower the total cost

of ownership (TCO) of the system. These system management functions are designed to report

errors, diagnose the system, and recover from system lockups without the aid of an external

microcontroller.

Revision 1.3

25

Page 40

Functional Architecture Intel® Server Boards S3200SH/S3210SH TPS

The management engine includes a TCO Timer used to detect system locks, Process Present

Indicator used to determine that the processor fetches the first instruction after reset, ECC Error

reporting from the host controller, Function Disable to prevent disabled function from generating

interrupts and power management events, and an Intruder Detect input for system cases.

3.2.3.16 Unused ICH9 Interfaces on the Server Board

The server board does not support the following interfaces on ICH9:

1. AC’97 2.3 Controller – ICH9 integrates an Audio Codec ’97 Component Specifications,

Version 2.3 controller that can be used to attach an Audio Codec (AC), a Modem Codec

(MC), an Audio/Modem Codec (AMC) or a combination of ACs and a single MC.

2. Intel High Definition Audio

3. Management Engine (ME), SST, Fan tach and PWM, PEC controller

3.2.3.17 PCI Express* x4 Sub-system

The Intel

®

ICH9R supports one PCI Express* x4-lane interface that can also be configured as a

single x1 or x4-lane port. The PCI Express interface allows direct connection with the PXH-V or

dedicated PCIe* devices. (Fully compliant to the PCI Express* Base Specification, Rev 1.0a).

3.2.3.18 PCI

One 32-bit PCI bus segment is directed through the Intel

A. This PCI Segment A supports two PCI connectors and one embedded Intel

®

ICH9R Interface defined as segment

®

82541PI LAN

controller.

The Intel

®

ICH9R does not contain a PATA device controller in the chipset; therefore SATA

interface CDROM/DVD ROMs are recommended for use with the server board.

3.2.3.19 SATA Controller

The Intel

®

ICH9R contains six SATA ports. The data transfer rates up to 300Mbyte/s per port.

3.2.3.20 Compatibility Modules (DMA Controller, Timer/Counters, Interrupt

Controller)

®

The Intel

ICH9R provides the functionality of two-cascaded 82C59 with the capability to handle

15 interrupts. It also supports processor system bus interrupts.

3.2.3.21 Advanced Programmable Interrupt Controller (APIC)

Interrupt generation and notification to the processor is done by the APICs in the Intel

using messages on the front side bus.

®

ICH9R

3.2.3.22 Universal Serial Bus (USB) Controller

The Intel

®

ICH9R contains one EHCI USB 2.0 controller and can support four USB ports. The

USB controller moves data between main memory and up to four USB connectors. All ports

function identically and with the same bandwidth.

Revision 1.3

26

Page 41

Intel® Server Boards S3200SH/S3210SH TPS Functional Architecture

The server board provides two external USB ports on the rear panel of the server board. The

dual-stack USB connector is located within the standard ATX I/O panel area. The Universal

Serial Bus Specification, Revision 1.1, defines the external connectors.

The third/fourth USB port is optional and can be accessed by cabling from an internal 9-pin

connector located on the base board to an external USB port located either in front or the rear

of a given chassis.

3.2.3.23 Enhanced Power Management

One of the embedded functions of the Intel

®

ICH9R is a power management controller. This is

used to implement ACPI-compliant power management features. The server board supports