Page 1

EV80Cl96KB

Evaluation Board

User’s Manual

(bier Number 270738-()O]

Page 2

EV80C196KB Microcontroller Evaluation Board

Release 001

February 20,1989

Page 3

Copyright 1989, Intel Corporation

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited

to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation

assumes no responsibitlity for any errors that may appear in this document. Intel Corporation makes

no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied

in an Intel product. No other circuit patents licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use,

duplication, or disclosure is subject to restrictions stated in Intel’s Software License Agreement, or in

the case of software delivered to the U.S. government, in accordance with the software license

agreement as defined in FAR 52.227-7013.

No part of this document may be copied or reproduced in any form or by any means without prior

written consent of Intel Corporation.

Intel Corporation retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify

Intel products:

376, Above, ActionMedia, BITBUS, Code Builder, DeskWare, Digital Studio, DVI, EtherExpress,

ETOX, ExCA, FaxBACK, Grand Challenge, i, i287, i386, i387, i486, i487, i750, i860, i960, ICE,

itBX, Inboard, Intel, lnte1287, lntel386, lntel387, lntel486, lntel487, intel inside., Intellec, iPSC,

iRMX, iSBC, ISBX, iWarp, LANprint, LANSelect, LANShell, LANSight, LANSpace, LANSpool,

MAPNET, Matched, MCS, Media Mail, NetPort, NetSentry, OpenNET, Paragon, PR0750,

ProSolver, READY-LAN, Reference Point, RMX/80, SatisFAXtion, Snapln 386, Storage Broker,

SugarCube, The Computer Inside., TokenExpress, Visual Edge, and WYPIWYF.

and the combinations of CCE, ICS, iRMX, ISBC, ISBX, iSXM, MCS, or UPI and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS is a

registered trademark of Mohawk Data Sciences Corportation.

CHMOS and HMOS are patented processes of Intel Corp.

Intel Corporation and Intel’s FASTPATH are not affiliated with Kinetics, a division of Excelan,

Inc. or its FASTPATH trademark or products.

RBM is a registered trademark and AT is a trademark of International Business Machines, Inc.

Microsoft MS, MS-DOS, and XENIX are registered trademarks and Multiplan is a trademark

of Microsoft Corporation.

Addional copies of this manual or other Intel Literature may be obtained from:

Intel Corporation, Literature Sales

P.O. Box 7641

Mt. Prospect, IL 60056-7641

Page 4

CONTENTS

SECTION

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PAGE

INTRODUCTION

........................................................................................

9

GETTING STARTED WITH THE EV80Cl96KB

........................................

9

Powering

the Board ........................................................................

9

Connecting

to your PC ....................................................................

9

Starting

the Host Software ..............................................................

9

HARDWARE OVERVIEW OF THE EV80Cl96KB BOARD

......................

10

Block Diagram of the

EV80C196KB

Board..

.................................... 10

Processor

........................................................................................

30

Memory‘

............................................................................................

10

Host

Interface ..................................................................................

1 1

Digital I/O

........................................................................................

11

Analog

Inputs

.................................................................................. 1 1

Decoding

........................................................................................

12

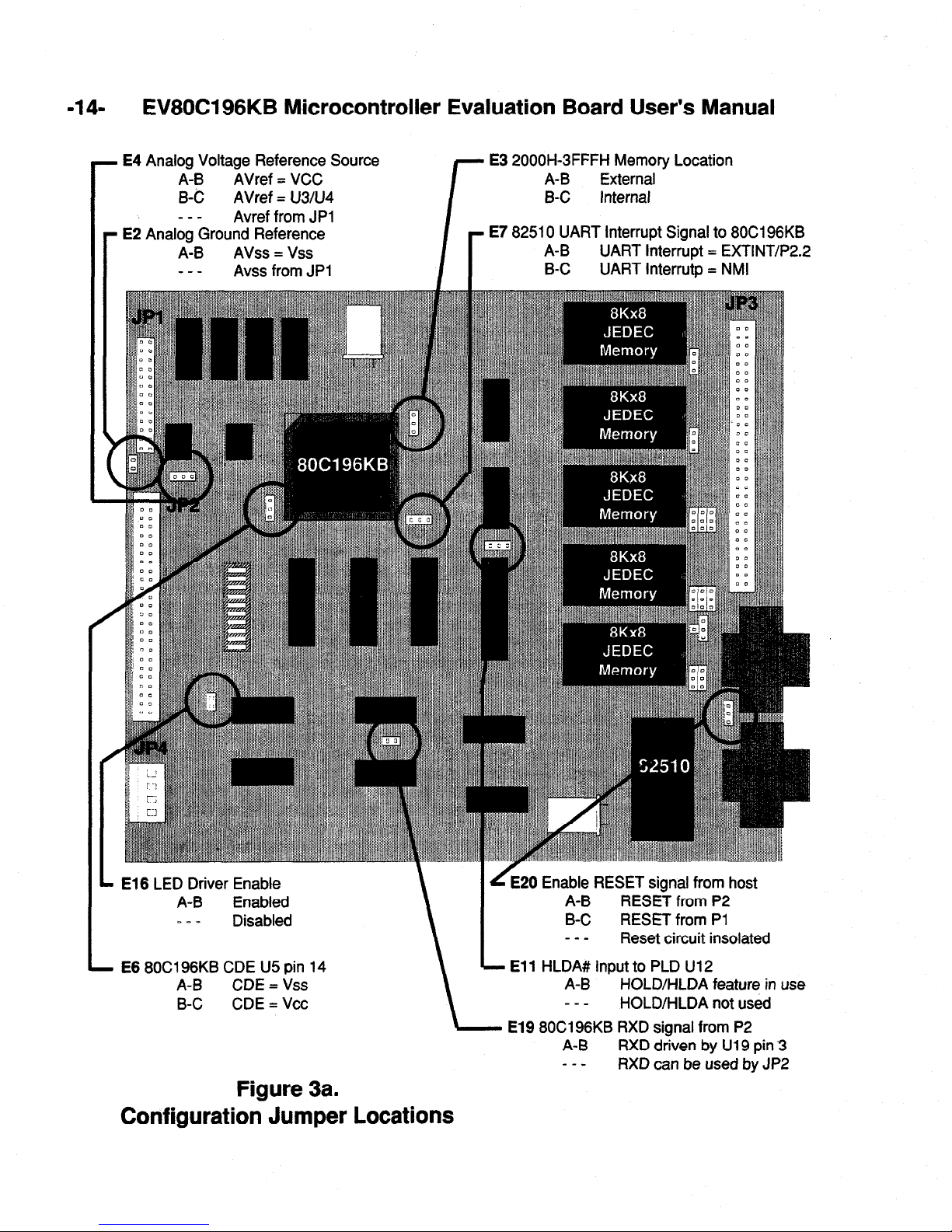

Configuration Jumper Locations

(Figure 3a)

..................................

14

Memory Configuration Jumper Locations (Figure 3b)

....................

15

Expansion Ports, Connectors and LEDs Locations (Figure 4)

........ 16

Host Serial Connector (Figure 5)

....................................................

17

8OCl96KB Serial Port Connector (Figure 6)

..................................

17

Analog Input Connector (Figure 7)

.................................................. 18

I/O Expansion

Connector (Figure 8)

................................................

18

Memory-l/O Expansion Connector (Figure 9)

.................................. 19

Power Supply

Connector (Figure 10)

..............................................

19

25pin to g-pin Adapter (Figure 11)

................................................ 20

INTRODUCTION

TO iRISM-iECM96 SOFTWARE..

..................................

21

Features

..........................................................................................

21

Restrictions

......................................................................................

22

OVERVIEW

................................................................................................

23

Embedded

Controller Monitor..

........................................................

23

USER INTERFACE

.................................................................................... 24

Background Information

..................................................................

24

Initiating and Terminating

iECM-96

................................................

25

Default

Base Commands ................................................................

28

Page 5

FILE OPERATIONS

....................................................................................

29

Loading and Saving Object Code

.................................................... 29

Other

File Operations..

......................................................................

30

PROGRAM CONTROL

................................................................................

32

Resetting the Target

........................................................................

32

Breakpoints

......................................................................................

32

Program Execution

..........................................................................

33

Program Stepping

............................................................................

35

DISPLAYING AND MODIFYING PROGRAM VARIABLES

........................ 37

Supported Data Types

......................................................................

37

. BYTE Commands

............................................................................

38

WORD Commands

..........................................................................

39

DWORD

Commands ........................................................................ 40

REAL Commands

............................................................................ 41

STACK Commands

..........................................................................

42

STRING Commands

........................................................................

42

Processor Variables

..........................................................................

43

ASSEMBLY AND DISASSEMBLY

..............................................................

44

Single Line Assembly Commands

....................................................

44

Disassembly Commands

..................................................................

45

SYMBOL OPERATIONS

............................................................................ 46

RISM

..........................................................................................................

47

RISM Variables

47

................................................................................

RISM Structure

.................................................................................

48

Receiving

Data from the Host .......................................................... 48

Sending Data to the Host

..................................................................

48

RISM Commands

..............................................................................

49

Schematics and Parts List

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ..~.......~..................~......

Appendix A

Specific iRlSM Information

-..~.............~................................~..............0..

Appendix B

Listing of IRISM-196KB

a.*.e..**..*...........*..

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ..-....*.........a

Appendix C

Timing Analysis

.*-.................*..........e....

. . . . . . . . . . . . . . . . . . . . ..~........~....~.....~......~

Appendix D

Programmable Logic Equations

. . . . . . . . ..~...~....~.........~...........~.....~.........~..

Appendix E

Standard Memory-l/O Connector

. . . ..~......~................................~~.......~..~

Appendix F

Sample Session

*“o...~~..~.....~..~.......e...~.*~.

. ..O.....................*s..*.............eo... Appendix G

Page 6

-8-

EV80C196KB Microcontroller Evaluation Board User’s Manual

Figure 1.

EV8OCl96KB Evaluation Board

Page 7

EV80C196KB Microcontroller Evaluation Board User’s Manual -90

INTRODUCTION

The EV80C196KB is a next-generation version of the EV80C196KA. The major

changes are the use of a standard memory expansion bus compatible with the

EV80C51 FB and EV80C186 boards, and the removal of the card edge bus. Also,

the HOLD/HLDA feature of the 8OC196KB is supported. The EV80C196KB is designed to be a software evaluation tool for the ROMless 8OC196KB 16-bit microcontroller. As such, ports 3 and 4 are not available for use as I/O ports unless offboard

latches/buffers and decoding logic are used. All unreserved functions of the

80C196KB are available to you except for the Non-Maskable Interrupt (NMI), the

TRAP instruction, and 512 bytes of address space. The Chip Configuration Byte is

also used by the monitor, but most of its functions are provided by external logic.

GETTING STARTED WITH THE EV80C396KB

Powering up the Board

Power (+5, +/-12 Volts) must be connected to JP4 as shown on the board’s silkscreen next to JP4 and in figure 10. Included with the board is a packet containing a

Molex connector and crimp terminals for your convenience.

Power supply requirements for the EV80C196KB board are as follows:

+ 5 VDC +I- 5 % @ 280 mA (150 mA if LED’s are disabled by

removing jumper shunt El 6)

+12VDC+/-20%@ 15mA

-12VDC+/-20%@ 15mA

Upon power-up (or after a reset) the board goes through initializations and a shifting-pattern is displayed on the Port 1 LEDs when initialization has completed properly.

Connecting to your PC

Once you have applied power to the board, you need to connect Pl to a PC serial

port. Pl is configured to interface pin-to-pin with a standard nine-pin AT@)-type

serial connector (see figure 5 for pinout). Make certain that you use a cable providing all nine signals, as they are all needed for proper operation of the host interface.

When you have connected the cable, you may observe that the 8OC196KB is held in

reset, and all the LEDs turn on. This is because one of the host signals is used to

reset the part, and the signal’is often in a reset condition prior to invoking the host

software on your PC.

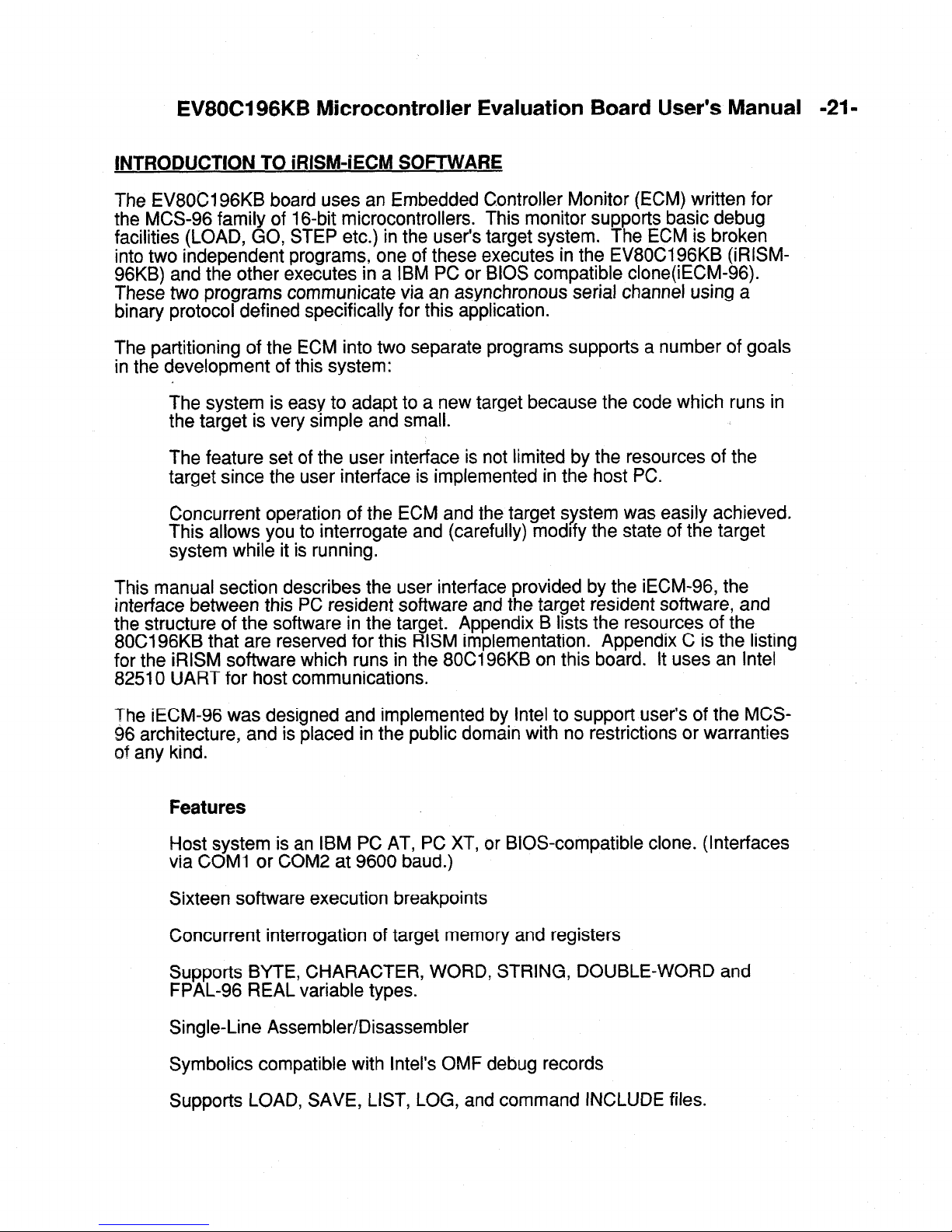

Note: if you have a 25pin serial port it will be necessary to make a 2%pin to 9pin adaptor (see figure 11 for details).

Starting the Host Software

After the you have made both connections to the board, you can invoke the host

interface. Install the disk in drive A of your system. At the DOS prompt type

“A:ECM96”eCR>. Your PC should eventually display the iECM-96 monitor screen.

If you have problems please refer to the sub-section “Initiating and Terminating

iECM-96” in the “USER INTERFACE” section of this manual. For further details on

using the monitor, refer to the “USER INTERFACE” section.

Page 8

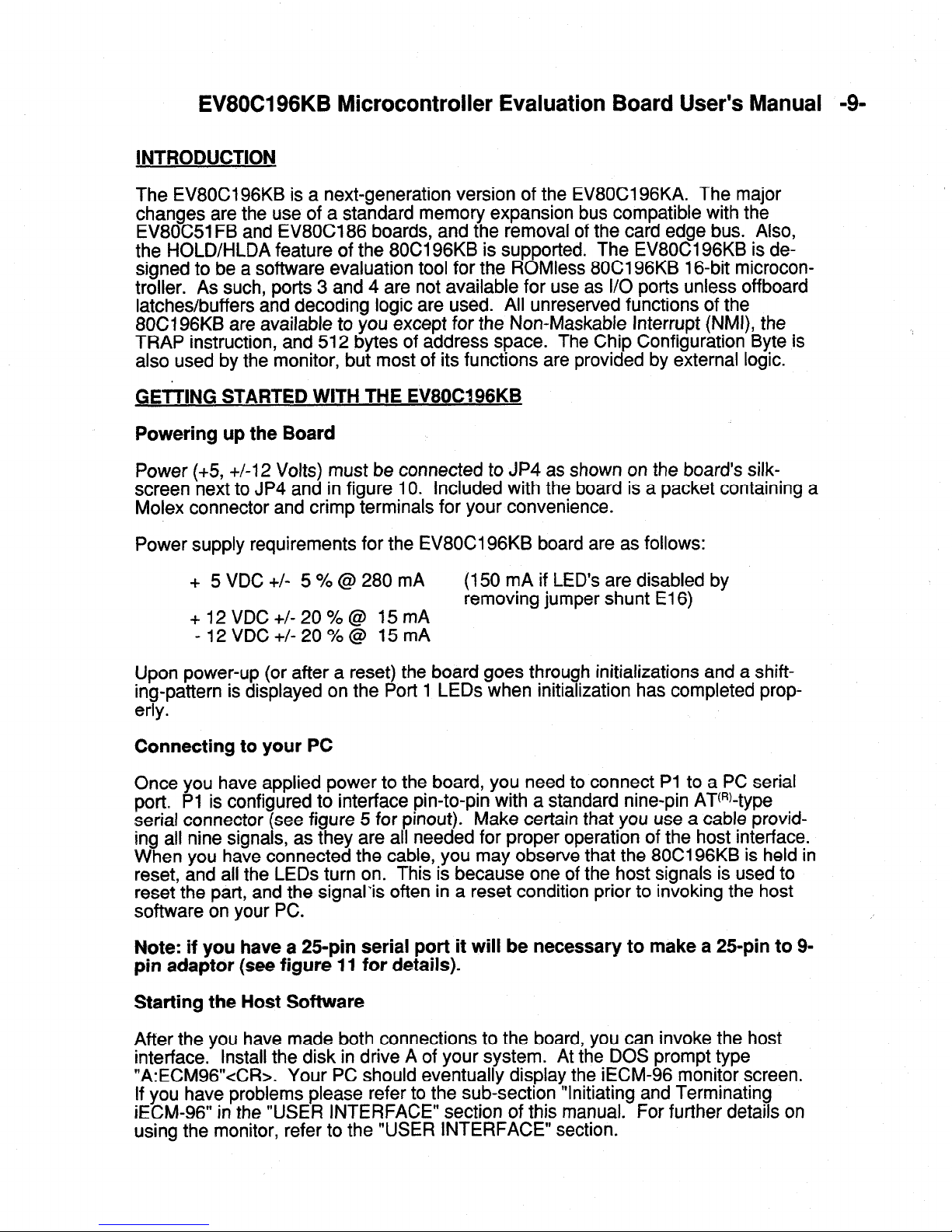

-IO-

EV80C196KB Microcontroller Evaluation Board User’s Manual

HARDWARE OVERVIEW OF THE EV80C196KB BOARD

The EV80C196KB Microcontroller Evaluation board is delivered with an 8OC196KB,

8 K-words and 8 K-bytes of user code/data memory, a UART for host communications and analog-input filtering with a precision voltage reference. Also included is

programmable chip-select, bus-width and wait-state-counter logic which allows you

to custom tailor the board to look like your own system. The board’s physical dimensions are 6 l/2” x 7 3/4” with an overall height of 3W. There are six main sections

to the EV80C196KB board: Processor, Memory, Host Interface, Digital I/O, Analog

Inputs and Decoding.

Block Diagram of the 80C196KB Board

Figure 2.

Processor

The Intel@)80C196KB is a 16-bit embedded microcontroller. Being a member of the

MCW-96 family, the 8OC196KB uses the same powerful instruction set and the

same architecture as the existing MCS-96 products. The 8OC196KB is an enhanced

CMOS version of the 8097BH. Its enhancements include up/down and capture

modes on Timer2, multiplyin

nearly twice as fast, Hold/Ho d Acknowledge logic, and power-down and idle modes

9

speeds almost 3 times as fast, overall execution

to save power. For more information, please refer to the 1989 “16-Bit Embedded

Controller Handbook,” Intel Corporation order number 270646-001 and the

8OC196KB Datasheet order number 270634-001.

Memory

There are five 28-pin memory sockets provided on the EV80C196KB board: Ul , U6,

U8, U13 and U14. The sockets are designed to support byte-wide, JEDEC-pinout,

memory devices of various types and sizes, i.e. 8K x 8 SRAM or 16K x 8 EPROM.

Ul and U8, U6 and U13 are connected as two 16-bit memory banks and U14 is

connected as an 8-bit memory bank.

Page 9

EV80C196KB Microcontroller Evaluation Board User’s Manual

-1 I-

See

appendix B and appendix C for details on reserved areas of memory.

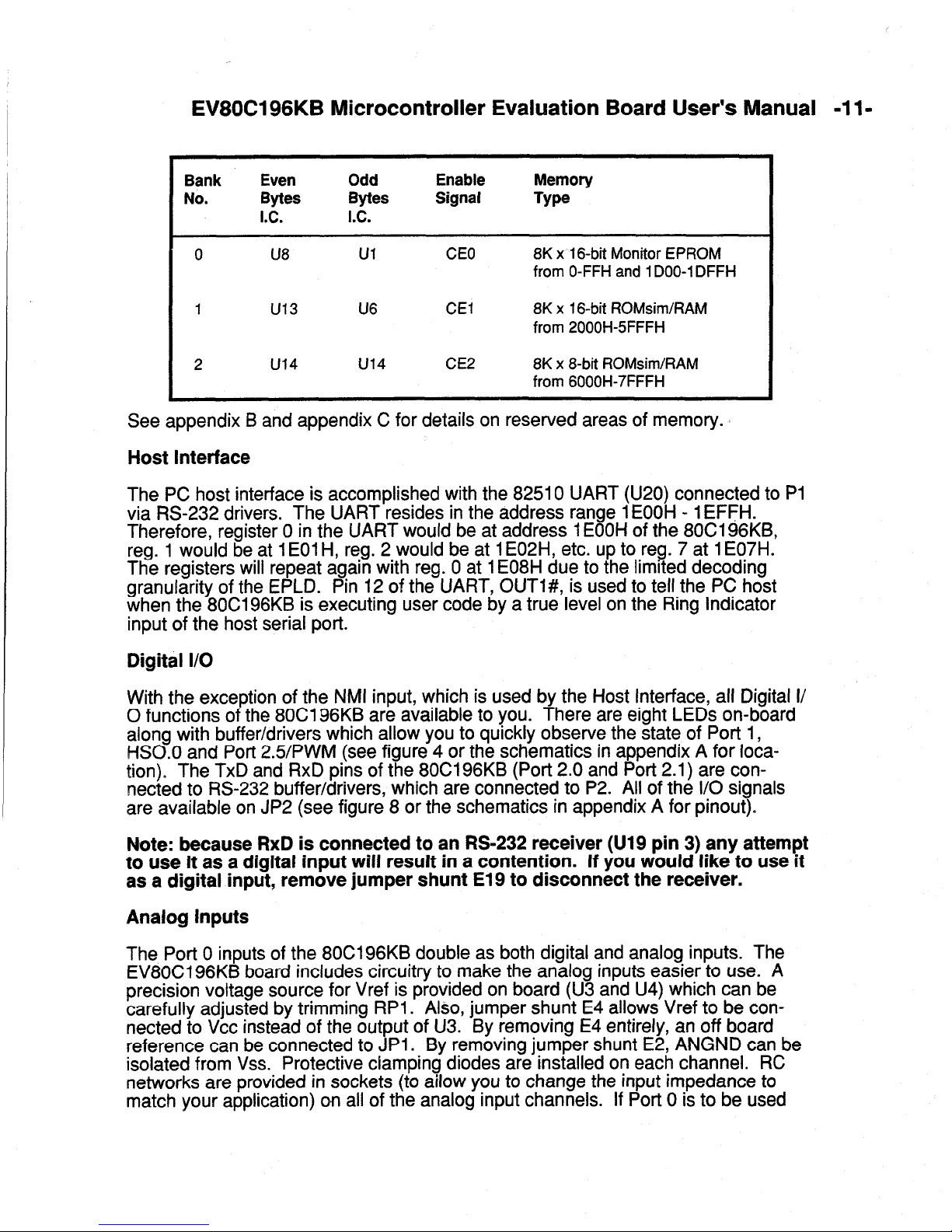

Bank

No.

Even

Bytes

Odd

Bytes

Enable

Signal

Memory

Type

I.C.

I.C.

0

U8

Ul

CEO

8K x 16-bit Monitor EPROM

from 0-FFH and 1 DOO-1 DFFH

1

u13 U6

CEi

8K x 16-bit ROMsim/RAM

from 2000H-5FFFH

2 u14

u14

CE2

8K x 8-bit ROMsim/RAM

from 6000H-7FFFH

Host Interface

,

The PC host interface is accomplished with the 82510 UART (U20) connected to Pl

via RS-232 drivers. The UART resides in the address range 1 EOOH - 1 EFFH.

Therefore, register 0 in the UART would be at address 1 EOOH of the 8OC196KB,

reg. 1 would be at 1 EOl H, reg. 2 would be at 1 E02H, etc. up to reg. 7 at 1 E07H.

The registers will repeat again with reg. 0 at 1 E08H due to the limited decoding

granularity of the EPLD. Pin 12 of the UART, OUTl#, is used to tell the PC host

when the 80C196KB is executing user code by a true level on the Ring Indicator

input of the host serial port.

Digital I/O

With the exception of the NMI input, which is used by the Host Interface, all Digital I/

0 functions of the 8OC196KB are available to you. There are eight LEDs on-board

along with buffer/drivers which allow you to quickly observe the state of Port 1,

HSO.0 and Port 2.5/PWM (see figure 4 or the schematics in appendix A for loca-

tion). The TxD and RxD pins of the 80C196KB (Port 2.0 and Port 2.1) are con-

nected to RS-232 buffer/drivers, which are connected to P2. All of the I/O signals

are available on JP2 (see figure 8 or the schematics in appendix A for pinout).

Note: because RxD is connected to an RS-232 receiver (U19 pin 3) any attempt

to use it as a digital input will result in a contention. If you would like to use it

as a digital input, remove jumper shunt El9 to disconnect the receiver.

Analog Inputs

The Port 0 inputs of the 80C196KB double as both digital and analog inputs. The

EV80C196KB board includes circuitry to make the analog inputs easier to use. A

precision voltage source for Vref is provided on board (U3 and U4) which can be

carefully adjusted by trimming RPl . Also, jumper shunt E4 allows Vref to be con-

nected to Vcc instead of the output of U3. By removing E4 entirely, an off board

reference can be connected to JPl . By removing jumper shunt E2, ANGND can be

isolated from Vss. Protective clamping diodes are installed on each channel. RC

networks are provided in sockets (to ailow you to change the input impedance to

match your application) on all of the analog input channels.

If Port 0 is to be used

Page 10

-729

EV80C196KB Microcontroller Evaluation Board User’s Manual

as a digital input, it is recommended that the capacitors be removed, and the resis-

tors replaced with wires. For additional connection information refer to figure 7 or

the schematics in appendix A. The ground and power planes beneath the analog

circuitry (Dl , D2, R3, C2, U3, U4, JPI and the analog connections on the

80Cl96KB) are isolated from the digital power and ground planes of the board to

keep noise from the analog inputs.

Decoding

The decoding logic on the EWOCl96KB board serves three purposes; to provide

Chip-Enable signals to memory and peripheral devices, to select the buswidth for

the device(s) being accessed and to provide wait-states for slow devices. This

section is provided in case you need to modify the memory configuration of the

EV80Cl96KB board. It is not necessary to understand this section for normal usage

of the board.

The heart of the decoding logic is U12, a 24-pin 5AC312 Intel EPLD or a C22VlO

programmable logic array which is socketed to allow easy changes.

For the sake of

convenience it will be referred to as “the EPLD” throughout this text. The EPLD

uses latched addresses A8-Al5 along with CLKOUT, HLDA#, RESET# and STALE

(STretched ALE) from the 8OCl96KB as decode inputs.

There are 4 enable outputs from the EPLD, all of which are low-level true, however

only one should be true at a time to avoid bus contention. They are decoded from

the address lines, and an internally-latched signal called MAP. MAP is cleared

when the RESET# input is true, and set when the Monitor EPROMs are accessed in

the address range 1 DOOH-I DFFH. MAP will always be set when the board is in the

USER mode.

pin 21 = CEO

Enables memory in Ul and U8

(monitor EPROM as shipped).

CEO

= (ADDRESS RANGE 2000H - 27FF and NOT MAP)

or ADDRESS RANGE OH - FFH

or ADDRESS RANGE 1 DOOH - 1 DFFH

pin 22 = CEl

Enables memory in U6 and U13

(user 16-bit ROMsim/RAM as shipped).

CEl

= (ADDRESS RANGE 2000H - 27FFH and MAP)

or ADDRESS RANGE 2800H - 5FFFH

pin 15-CE2

Enables memory in U14

(user 8-bit ROMsim/RAM as shipped).

CE2

= ADDRESS RANGE 6000H - 7FFFH

pin 14 - CS510 Enables U20, the 82510 UART, which is

used for host communications.

CS510 = ADDRESS RANGE 1 EOOH - 1 EFFH

Page 11

EV80C196KB Microcontroller Evaluation Board User’s Manual 4 3-

The BUSWIDTH output of the EPLD, pin 16, is fed into the buswidth pin of the

8OC196KB. Therefore, it is driven low for accesses to 8-bit memory and high for

accesses to 16-bit memory. As shipped, it goes low simultaneously with CE2 or

CS510 as these are the only areas of memory mapped as 8-bit.

Programmed into the EPLD is a 3-bit wait-state machine clocked by the rising edge

of CLKOUT from the 8OC196KB. The transition sequence of the wait-state machine

is controlled by the current state of the machine and the inputs to the EPLD (for

further details see appendix E). While the bus of the 80C196KB is idle the wait-state

machine is locked in state 0, which is called async-start. The conditions for leaving

async-start are 1) ALE being asserted, 2) HLDA# not being asserted and 3) a

value on A8 - Al5 requiring wait-states. Because the falling edge of ALE can occur

before the next rising edge of CLKOUT can clock the wait-state machine, a signal

called STALE (for Stretched ALE) is used. STALE does not go low until after the

rising edge of CLKOUT.

During async-start, the output WAIT# from the EPLD is asserted asynchronously

based upon a value on A8-A15 requiring wait-states. If no wait-states are required,

WAIT# will not be asserted and the wait-state machine will remain in async-start.

However, if one or more wait-states are needed WAIT# will be asserted and the

wait-state machine will transition out of async-start on the next rising edge of

CLKOUT. The next state entered depends on how many wait-states are needed. If

only one is required the next state is remove&old, where WAIT# is deasserted

regardless of the inputs to the EPLD. If two watt-states are needed the next state is

hold-2, where WAIT# is always asserted, then the state after that is remove-hold.

The additional states, hold-3 - hold 7, work just like hold-2 with WAIT# always

asserted. The wait-state machine wJI count through from hold-2 to hold-n to

generate n wait-states before jumping to remove-hold to deassert WAIT#. The

maximum number of wait-states is seven.

The previous paragraph described how the signal WAIT# is generated based on the

rising edge of CLKOUT. However, the 8OC196KB needs to have a valid signal on

it’s READY input pin until the falling edge of CLKOUT. Therefore, it was necessary

to clock WAIT# through a negative-edge-triggered-JK flip-flop (U15A) by the falling

edge of CLKOUT to generate a signal called WAITN#. As in the EPLD, WAITN# is

asserted asynchronously while ALE is high and WAIT# is asserted. After ALE goes

low WAITN# will remain asserted until WAIT# is deassetted and the flip-flop is

clocked. Besides the WAIT# signal, the WAITN# signal can be asserted by the

USEREADY signal from the expansion bus. As shipped, the EPLD has the following

configuration:

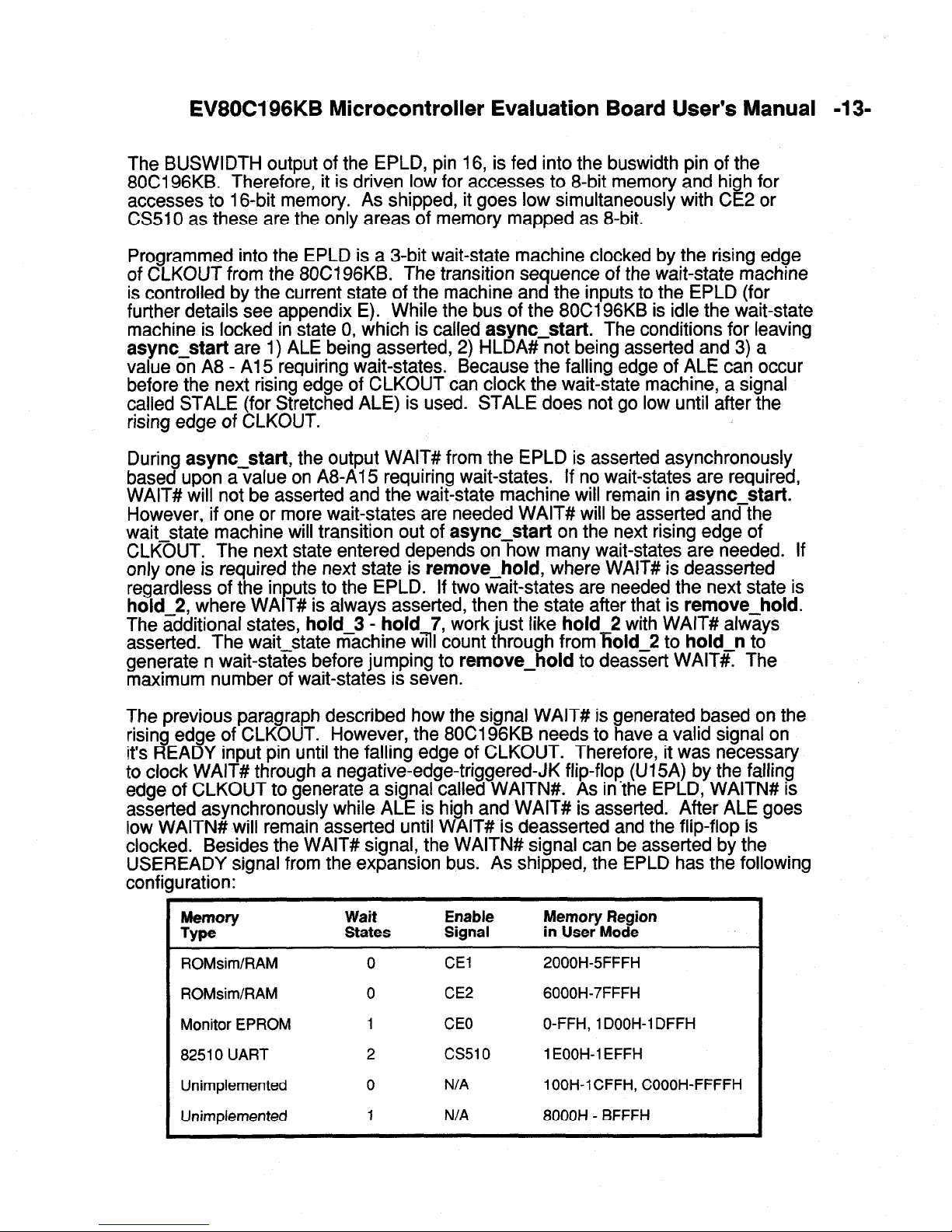

Memory

Wait

Type

States

ROMsim/RAM 0

ROMsim/RAM

0

Monitor EPROM

1

82510 UART

2

Unimplemented

0

Unimplemented

1

Enable

Signal

CEl

CE2

CEO

cs510

N/A

N/A

Memory Region

in User Mode

2000H-5FFFH

6000H-7FFFH

0-FFH, 1 DOOH- DFFH

1 EOOH-1 EFFH

1 OOH-1 CFFH, COOOH-FFFFH

8000H - BFFFH

Page 12

-14 EV8OC196KB Microcontroller Evaluation Board User’s Manual

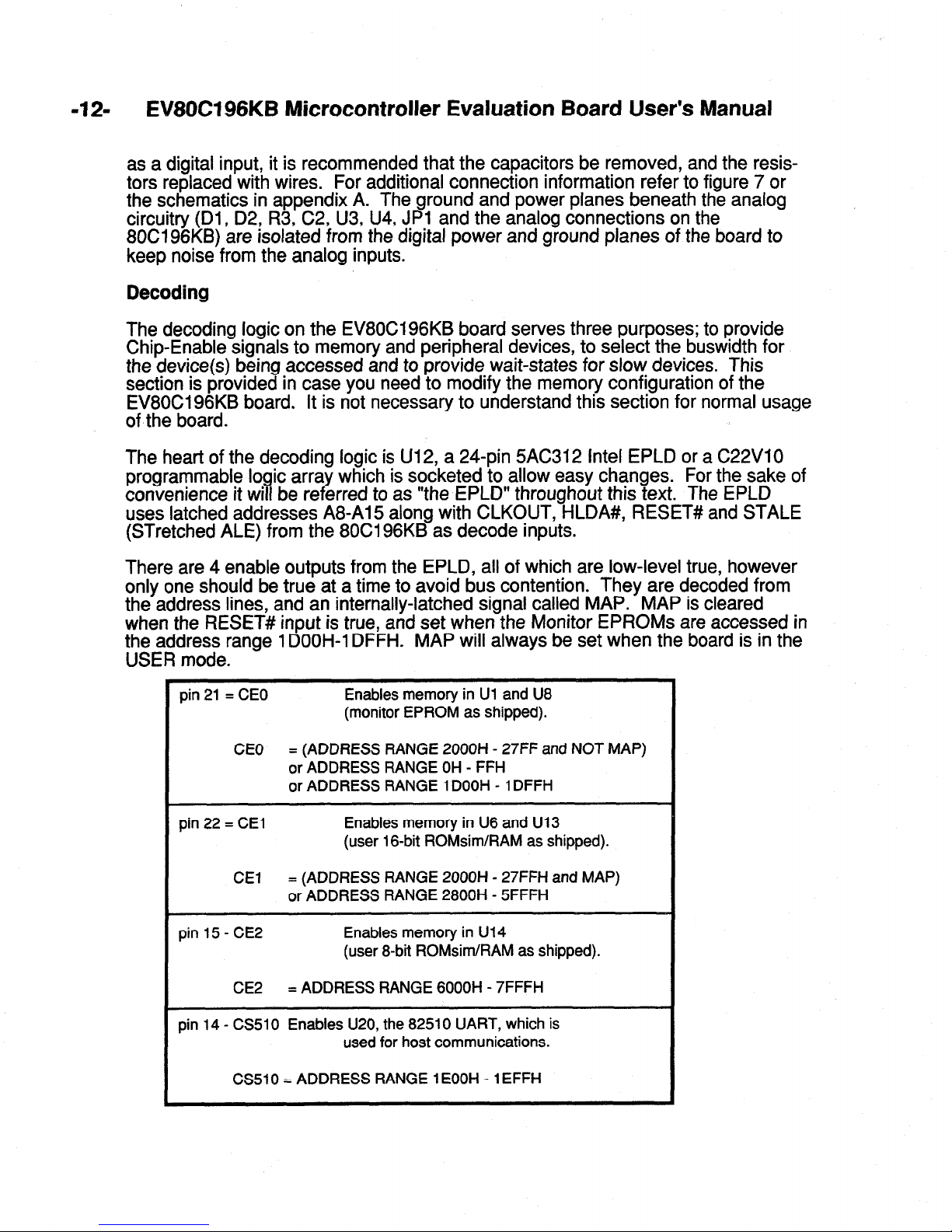

- E4 Analog Voltage Reference Source

A-B AVref = VCC

B-i: AVref = U3/U4

__-

Avref from JPl

E2 Analog Ground Reference

A-B AVss = Vss

---

Avss from JPl

E3 2000H-3FFFH Memory Location

A-B External

B-C

Internal

E7 82510 UART Interrupt Signal to 8OC196KB

A-B UART Interrupt = EXTINnP2.2

B-C

UART lnterrutp = NMI

El6 LED Driver Enable

L E20 Enable RESET signal from host

A-B

Enabled

i

1

A-B RESET from P2

__~

Disabled

B-C

RESET from Pl

-mm

Reset circuit insolated

- E6 80C196KB CDE U5 pin 14

El1 HLDA# Input to PLD U12

A-B CDE = Vss

A-B HOLD/HLDA feature in use

B-C

CDE = Vcc

---

HOLD/HLDA not used

El9 8OC196KB RXD signal from P2

A-B

RXD driven by U19 pin 3

---

RXD can be used by JP2

Figure 3a.

Configuration Jumper Locations

Page 13

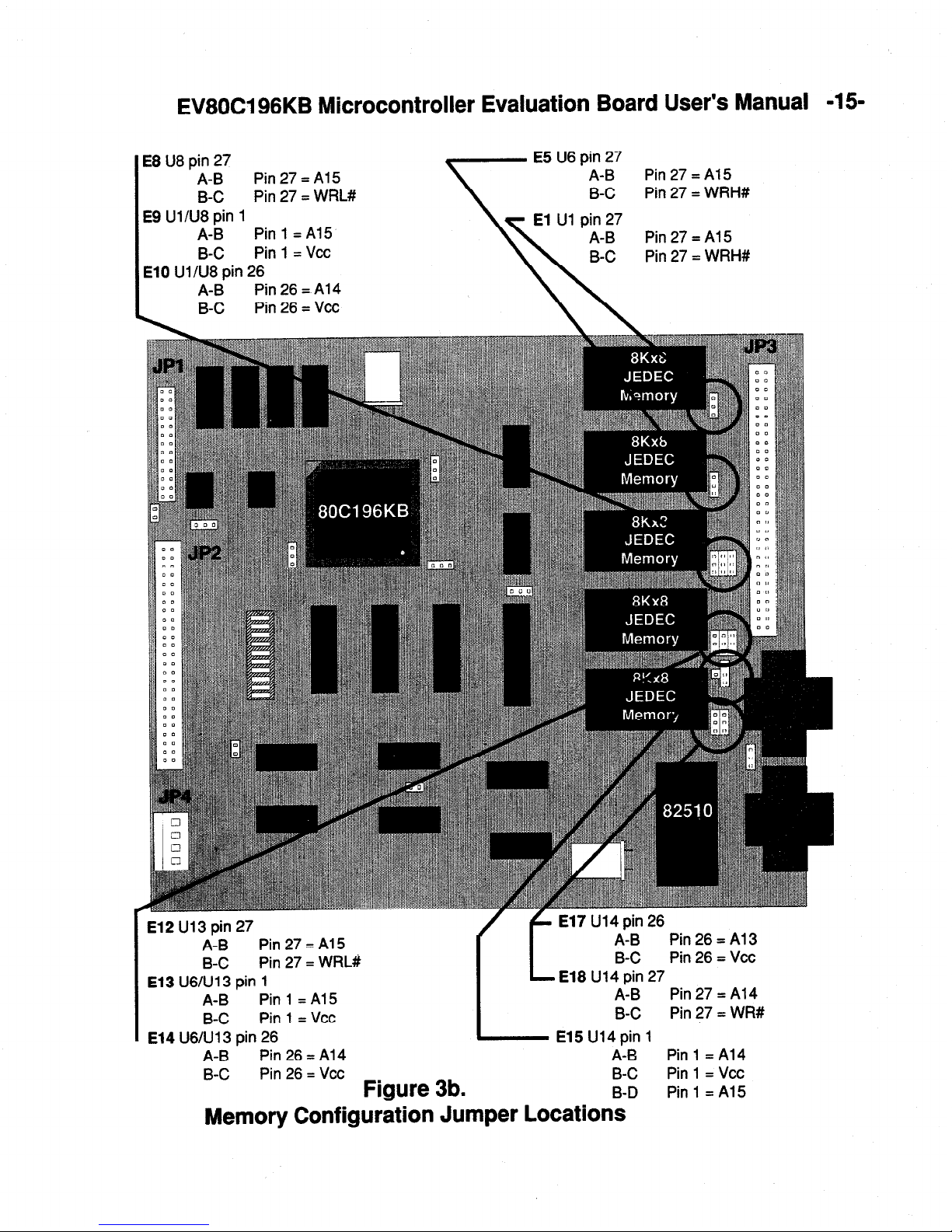

EV80C196KB Microcontroller Evaluation Board User’s Manual -15

E8 U8 pin 27

A-B

Pin 27 = Al 5

B-C

Pin 27 = WRL#

E9 UlN8 pin 1

A-B

Pin 1 = A15

B-C

Pin 1 = Vcc

El0 Ul/U8 pin 26

A-B

Pin 26 = Al 4

Pin27=A15

Pin 27 = WRH#

Pin27=A15

Pin 27 = WRH#

R-C Pin 26 = Vcc

El2 U13 pin 27

El7 U14 pin 26

A-B

Pin27=A15

L

t

A-B Pin26=A13

B-C

Pin 27 = WRL#k

B-C

Pin 26 = Vcc

El3 U6/U13 pin 1

El8 U14 pin 27

A-B

Pin 1 =A15

A-B

Pin27=A14

B-C

Pin 1 = Vcc

B-C

Pin 27 = WR#

El4 U6/U13 pin 26

El5 U14 pin 1

A-B

Pin26=A14

A-B

Pin 1 =A14

B-C

Pin 26 = Vcc

Figure 3b.

B-C

Pin 1 = Vcc

Memory Configuration Jumper LocationiD

Pin 1 =A15

Page 14

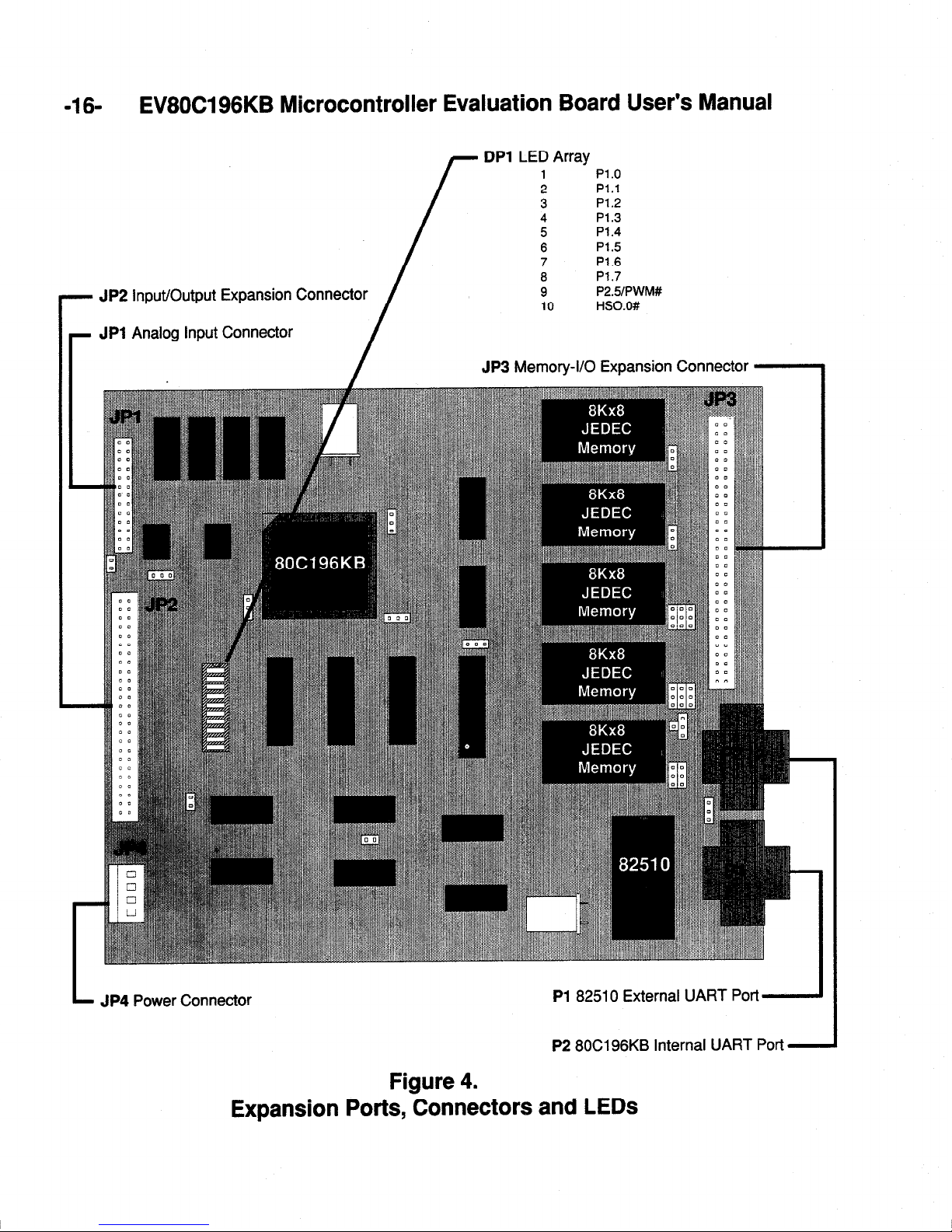

-16-

EV80C196KB Microcontroller Evaluation Board User’s Manual

/

DPl LED Array

1 P1.0

2 PI.1

3 P1.2

4 P1.3

5 P1.4

6 P1.5

7 P1.6

r

JP2 input/Output Expansion Connector

/

6

P1.7

9

P2.5/PWM#

10

HSO.O#

Ir

JPl Analog Input Connector

/

JP3 Memory-i/O Expansion Connector

L

JP4 Power Connector

Pl 82510 External UART Port-

P2 8OC196KB Internal UART Port -

Figure 4.

Expansion Ports, Connectors and LEDs

Page 15

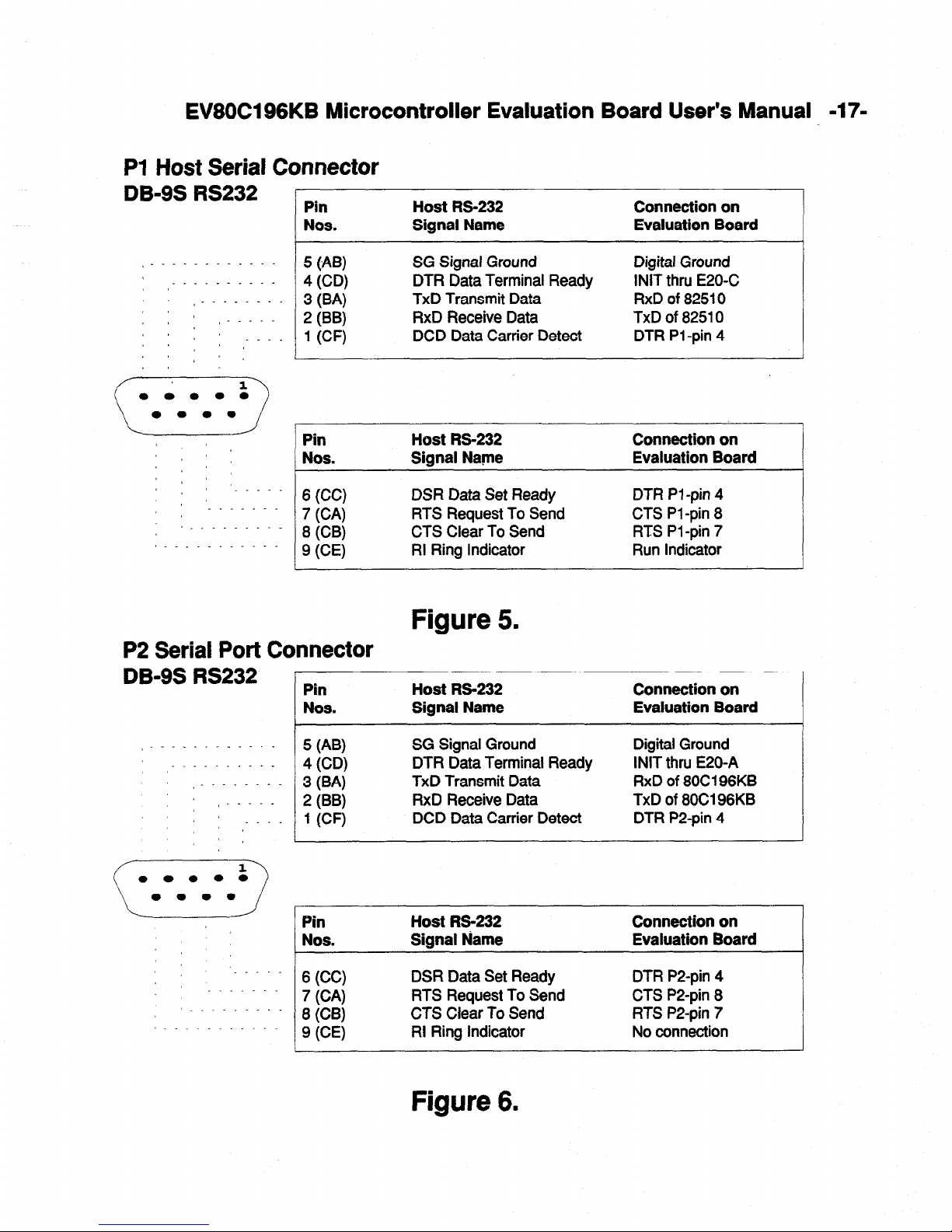

EV80C196KB Microcontroller Evaluation Board User’s Manual -17-

Pl Host Serial Connector

DB-9S RS232

Pin

Host RS-232 Connection on

Nos. Signal Name

Evaluation Board

5 (AB) SG Signal Ground

4 (CD)

DTR Data Terminal Ready

3 @A)

TxD Transmit Data

2 WV

RxD Receive Data

1 W=)

DCD Data Carrier Detect

Digital Ground

INIT thru E20-C

RxD of 82510

TxD of 82510

DTR Pl-pin 4

’

Pin

Nos.

Host M-232

Signal Name

Connection on

Evaluation Board

6 (CC)

7 (CA)

8 W

9 W

DSR Data Set Ready

RTS Request To Send

CTS Clear To Send

RI Ring Indicator

DTR Pl -pin 4

CTS Pl -pin 8

RTS Pl-pin 7

Run Indicator

P2 Serial Port Connector

DB-9S RS232

L

r

L

Figure 5.

Pin

Nos.

5 VW

4 (CD)

3 VW

2 W

1 (CF)

Host W-232

Signal Name

SG Signal Ground

DTR Data Terminal Ready

TxD Transmit Data

RxD Receive Data

DCD Data Carrier Detect

Connection on

Evaluation Board

Digital Ground

INIT thru E20-A

RxD of 8OC196KB

TxD of 8OC196KB

DTR P2-pin 4

Pin

Nos.

Host M-232

Signal Mame

Connection on

Evaluation Board

6 (CC)

7 GA)

8 W

9 W

DSR Data Set Ready

RTS Request To Send

CTS Clear To Send

RI Ring Indicator

DTR P2-pin 4

CTS PBpin 8

RTS PP-pin 7

No connection

Figure 6.

Page 16

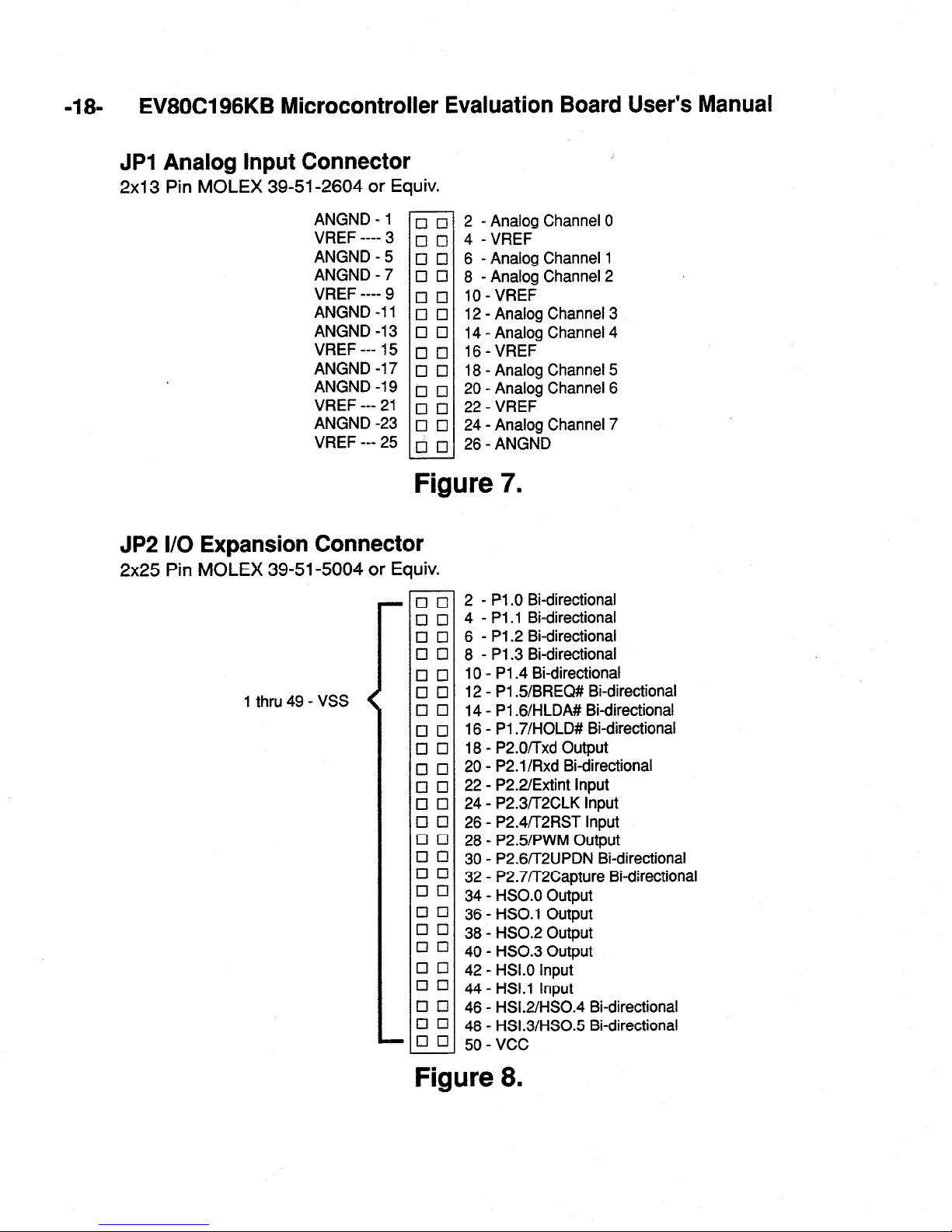

-189

EV80C196KB Microcontroller Evaluation Board User’s Manual

JPI Analog Input Connector

2x13 Pin MOLEX 39-51-2604 or Equiv.

ANGND - 1

VREF ---- 3

ANGND - 5

ANGND - 7

VREF ---- 9

ANGND -11

ANGND -13

VREF --- 15

ANGND -17

ANGND -19

VREF --- 21

ANGND -23

VREF --- 25

Figure 7.

JP2 I/O Expansion Connector

2x25 Pin MOLEX 39-51-5004 or Equiv.

1 thru 49 - VSS

2 - Analog Channel 0

4 -VREF

6 - Analog Channel 1

8 - Analog Channel 2

10 - VREF

12 - Analog Channel 3

14 - Analog Channel 4

16-VREF

18 - Analog Channel 5

20 - Analog Channel 6

22 - VREF

24 - Analog Channel 7

26 - ANGND

2 - Pl .O Bi-directional

4 - Pl .l Bi-directional

6 - P1.2 Bi-directional

8 - P1.3 Bi-directional

10 - P1.4 Bi-directional

12 - Pl .YBREQ## Bi-directional

14 - Pl .G/HLDA# Bi-directional

16 - P1.7/HOLD# Bi-directional

18 - P2.0/Txd Output

20 - P2.1/Rxd Bi-directional

22 - P22/Extint Input

24 - P2.3fl2CLK Input

26 - P2.4fl2RST Input

28 - P2.5/PWM Output

30 - P2.6!T2UPDN Bi-directional

32 - P2.7/T2Capture Bi-directional

34 - HSO.0 Output

36 - HSO.l Output

38 - HS0.2 Output

40 - HS0.3 Output

42 - HSI.0 Input

44 - HSI.l Input

46 - HSl.2/HS0.4 Bi-directional

48 - HSl.3/HS0.5 Bi-directional

50 - vcc

Figure 8.

Page 17

EV80C196KB Microcontroller Evaluation Board User’s Manual -19-

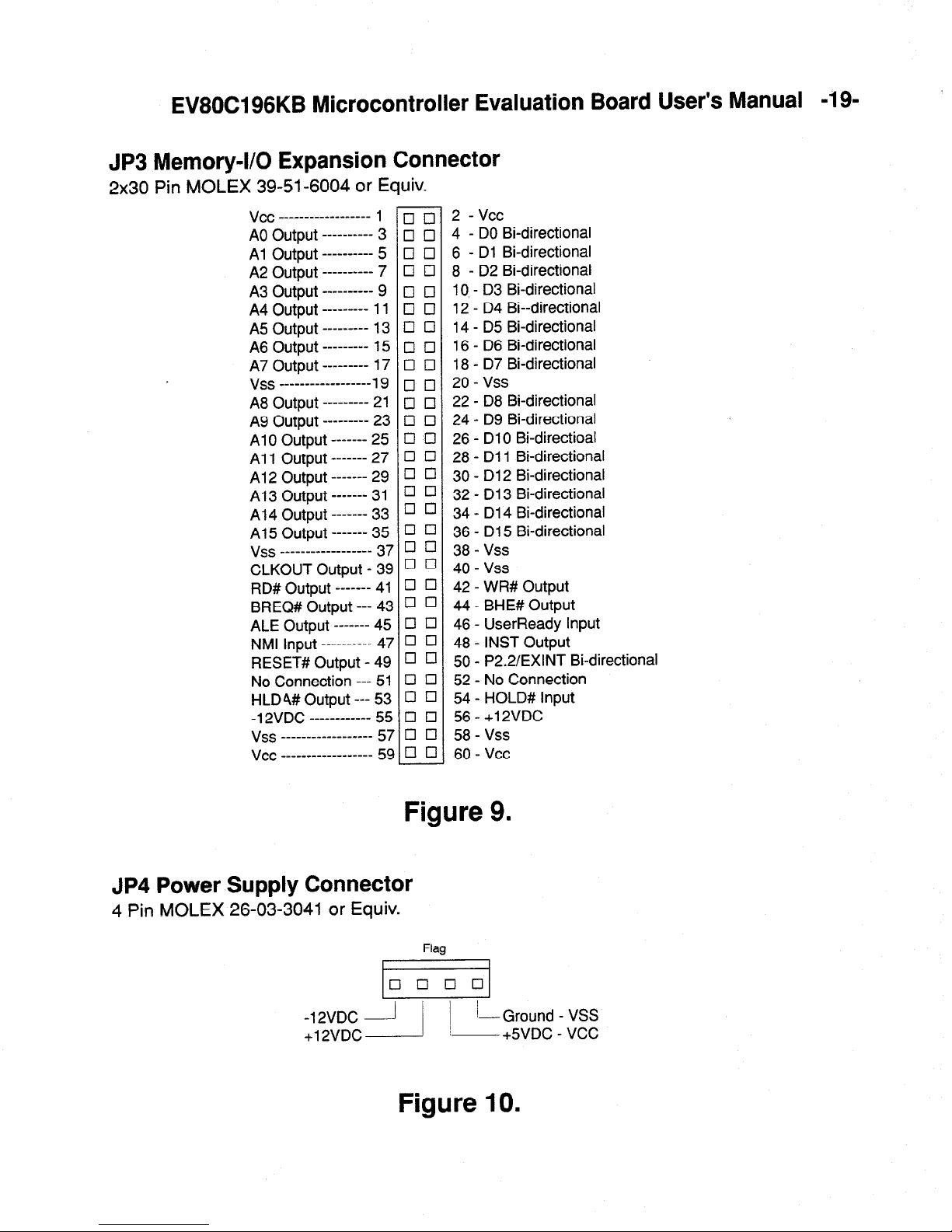

JP3 Memory-l/O Expansion Connector

2x30 Pin MOLEX 39-51-6004 or Equiv.

vcc __--------------- - 1

A0 Output ---------- 3

Al Output ---------- 5

A2 Output ---------- 7

A3 Output ---------- 9

A4 Output --------- 11

A5 Output --------- 13

A6 output --------- 15

A7 Output --------- 17

vss

_________-__------ 19

A8 output --------- 21

A9 Output --------- 23

Al 0 Output ------- 25

Al 1 Output ------- 27

Al 2 Output ------- 29

Al 3 Output ------- 31

Al 4 Output ------- 33

Al 5 Output ------- 35

vss _______---------- - 37

CLKOUT Output - 39

RD# Output ------- 41

BREQ# Output --- 43

ALE Output ------- 45

NMI Input ---------- 47

RESET# Output - 49

No Connection --- 51

HLD4# Output --- 53

-12VDC ________-_-- 55

vss _____-_--------- -- 57

vcc ___------------ --- 59

r

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

7cl

70

70

7u

70

30

3u

q u

q u

q u

q u

q u

q u

q u

q u

q u

q u

q u

q u

q n

q u

q u

q u

q u

q u

q u

q u

q u

q u

q u

2 - vcc

4 - DO Bi-directional

6 - Dl Bi-directional

8 - D2 Bi-directional

10, - D3 Bi-directional

12 - D4 Bi--directional

14 - D5 Bi-directional

16 - D6 Bi-directional

18 - D7 Bi-directional

20 - vss

22 - D8 Bi-directional

24 - D9 Bi-directional

26 - DlO Bi-directioal

28 - Dl 1 Bi-directional

30 - D12 Bi-directional

32 - D13 Bi-directional

34 - D14 Bi-directional

36 - D15 Bi-directional

38 - Vss

40 - vss

42 - WR# Output

44 - BHE# Output

46 - UserReady Input

48 - INST Output

50 - P2.2/EXINT Bi-directional

52 - No Connection

54 - HOLD# Input

56 - +12VDC

58 - Vss

60 - Vcc

Figure 9.

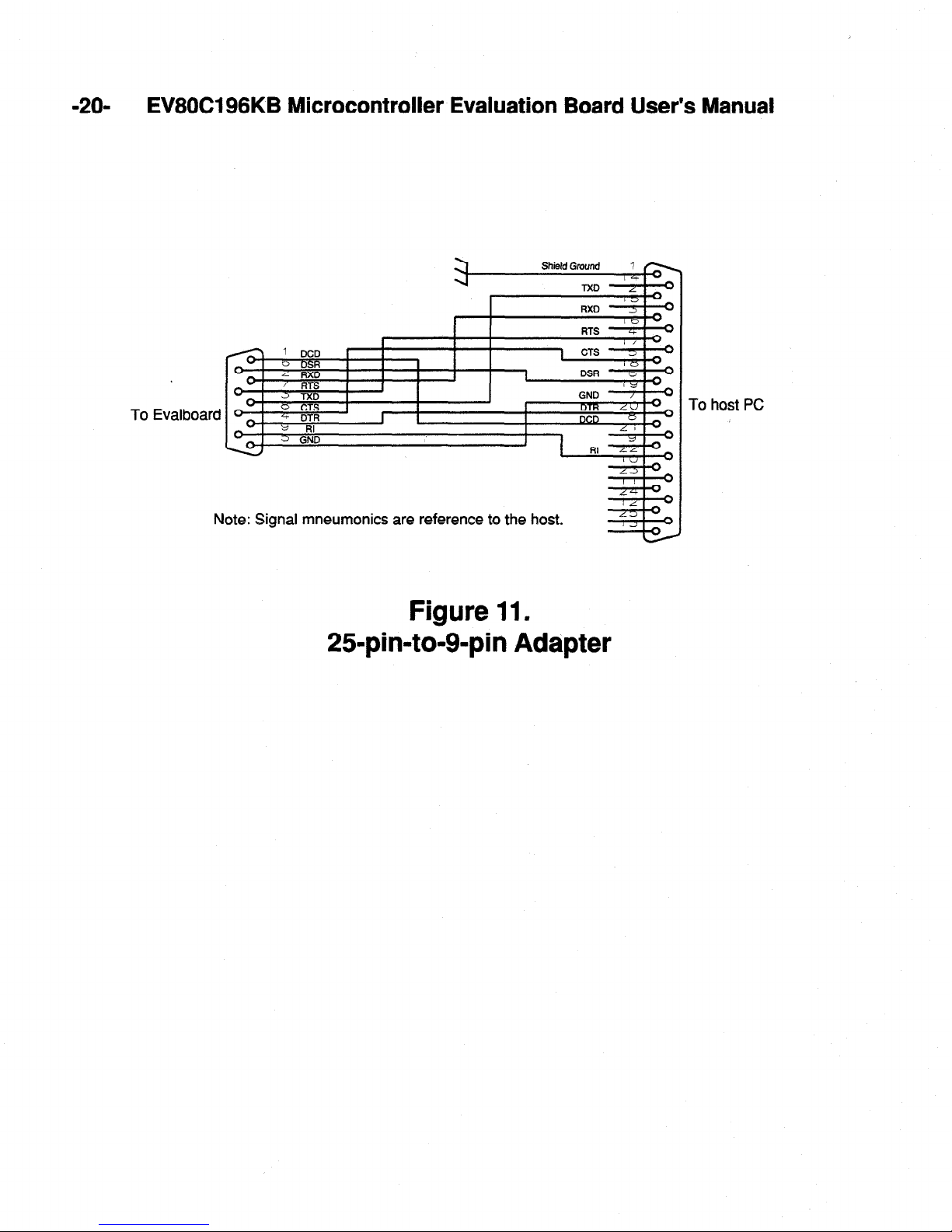

JP4 Power Supply Connector

4 Pin MOLEX 26-03-3041 or Equiv.

Figure 10.

Page 18

-2o-

EV80C196KB Microcontroller Evaluation Board User’s Manual

To Evalboard

Note: Signal mneumonics are reference to the host.

To host PC

Figure 11.

25pin-to-g-pin Adapter

Page 19

EV8OCI 96KB Microcontroller Evaluation Board User’s Manual

-211

INTRODUCTION TO iRISM-IECM SOFTWARE

The EV80C196KB board uses an Embedded Controller Monitor (ECM) written for

the MCS-96 family of 16-bit microcontrollers. This monitor supports basic debug

facilities (LOAD, GO, STEP etc.) in the user’s target system. The ECM is broken

into two independent programs, one of these executes in the EV80C196KB (iRISM96KB) and the other executes in a IBM PC or BIOS compatible clone(iECM-96).

These two programs communicate via an asynchronous serial channel using a

binary protocol defined specifically for this application.

The partitioning of the ECM into two separate programs supports a number of goals

in the development of this system:

The system is easy to adapt to a new target because the code which runs in

the target is very simple and small.

The feature set of the user interface is not limited by the resources of the

target since the user interface is implemented in the host PC.

Concurrent operation of the ECM and the target system was easily achieved.

This allows you to interrogate and (carefully) modify the state of the target

system while it is running.

This manual section describes the user interface provided by the iECM-96, the

interface between this PC resident software and the target resident software, and

the structure of the software in the target. Appendix B lists the resources of the

80C196KB that are reserved for this RISM implementation. Appendix C is the listing

for the iRlSM software which runs in the 80C196KB on this board. It uses an Intel

82510 UART for host communications.

The iECM-96 was designed and implemented by Intel to support user’s of the MCS96 architecture, and is placed in the public domain with no restrictions or warranties

of any kind.

Features

Host system is an IBM PC AT, PC XT, or BIOS-compatible clone. (Interfaces

via COMl or COM2 at 9600 baud.)

Sixteen software execution breakpoints

Concurrent interrogation of target memory and registers

Supports BYTE, CHARACTER, WORD, STRING, DOUBLE-WORD and

FPAL-96 REAL variable types.

Single-Line Assembler/Disassembler

Symbolics compatible with Intel’s OMF debug records

Supports LOAD, SAVE, LIST, LOG, and command INCLUDE files.

Page 20

EV80C196KB Microcontroller Evaluation Board User’s Manual

Restrictions

Two words of user stack are reserved for use by the iRISM-96 software.Other

memory and/or registers in the target memory will be used by the iRISM-96

software. The exact number and location of this memory is implementation

dependent. See appendix B or C for further information.

An asynchronous serial port capable of operation at 9600 baud must be

available in the target system. The RISM described in this document uses an

Intel 82510 UART. This version also uses the NMI (Non-Maskable Interrupt)

to signal that a received data character is available.

1 The TRAP instruction is reserved.

Breakpoints and program stepping will not operate if the user’s code is in

EPROM or other nonchangeable memory.

Page 21

EV8OC196KB Microcontroller Evaluation Board User’s Manual -239

OVERVIEW

Embedded Controller Monitor (ECM)

An ECM (Embedded Controller Monitor) provides basic debug capability and is

installed in your target system. Capabilities include loading object files into system

RAM, examining and modifying variables, executing code, and stepping through

code. In the past, most of these monitors have been configured to run with a standard “dumb” CRT with some form of auxiliary port for loading and saving object code

from a host system.

It is now common for a personal computer to act as the host for

program translation and also emulate a dumb CRT during user interaction with the

ECM. The ECM developed for the MCS-96 family makes the assumption that the

user interface will always be a personal computer; no provision is made for interface

to a dumb CRT. By making this assumption it is possible to reduce the size and

complexity of the code that must be installed in the target system. A term’ has been

coined for this code resident in the target -- RISM. The term RISM stands for Re-

duced instruction Set Monitor and is an obvious takeoff of the term RISC (Reduced

Instruction Set Computer) used to describe a class of computer architectures. The

RISM consists of about 300 bytes of MCS-96 code which provide primitive opera-

tions. Software running in the host uses the RISM commands to provide a complete

user interface to the target system. The advantage of this approach is that the ECM

can be readily adapted to different target systems and requires only a small part of

the available target memory space. The disadvantage is that the user interface

must be provided by a personal computer.

The structure of the RISM is a short section of initialization code and an interrupt

service routine (ISR) that processes interrupts from the host system. The RISM ISR

consists of a short prologue and then a case-jump to one of 20 to 25 command

executors. These executors are simple and short; the flow though the entire ISR

(including the prologue) is 15-20 instructions. The serial communication occurs at

9600 baud, which limits the frequency of these interrupts to 1 Khz. In the worst case

the EV80C196KB board will be slowed by the execution of a fairly short RISM ISR

every millisecond while executing user code. It is possible to operate the

EV80C196KB board so that no real-time is lost to the iECM-96 unless the user is

actively interrogating the target. (See the section “Initiating and Terminating the

iECM-96” and the description of the RISM REPORT-STATUS command for details

on this).

Page 22

-240

EV80C196KB Microcontroller Evaluation Board User’s Manual

USER INTERFACE

The user interface to the iECM-96 supports commands to initiate and configure the

ECM-96, perform I/O operations involving DOS files, execute user programs, and

interrogate variables in the target system. Interrogation can be done in a number of

formats and in most cases can be done concurrently with user code execution. A

single line assembler and disassembler are also provided.

Note: on the disk included with the Ev80C196KB is a file called DEMO.LOG.

DEMO.LOG is a sample iECM-96 session for you to invoke and become more

-familiar with the features of iECM-96. Appendix G is a printout of DEMO.LST

which was created by turning on the list feature and invoking DEMO.LOG by

typing *‘include demo.log”<CR> at the iECM-96 “*‘* prompt.

Background Information

Numeric and Symbolic Input

The command parser used by the iECM-96 software requires that numeric inputs

always start with the digits O-9. If hexadecimal numbers are entered which start with

A-F they must be preceded by a “0”.

For example, enter “OAA55” instead of “AA55”.

This requirement is similar to ASM-96. If symbolic information has been downloaded

as part of an object file (see “Loading and Saving Object Code”) then you can enter

a valid symbol name whenever a number is expected. The symbol name must be

preceded by a period (“.“) so that the parser knows to try searching the symbol

table. If the symbol is ambiguous then it will not be accepted by the parser. The

probability of ambiguous references can be reduced by specifying the module name

along with the symbol name. The module name must be preceded with a colon (“:“).

If a variable TEMP is declared both in MODULE1 and in MODULE2, then a reference to the TEMP declared by MODULE1 would be “:MODULEl .TEMP”. PLM-96

or C-96 line numbers can be called out by a pound sign (“#“) followed by the line

number.

Symbolic Output

The symbolic output routines, in general, deal only with address information. They

will not try to convert data values into symbolic form. When the symbol table is

searched for a symbol name to associate with a given value the routines also per-

form type checking. If one, and only one, symbol matches both the type and value

of the address being displayed then the output routines will display the symbol name

along with the numeric value of the address. If more than one label has been assigned to a given address then the symbolic output routines will ignore all of them.

The exception to this rule occurs when the disassembler finds multiple labels assigned to a given code address. The disassembler will display all the known symbolic labels attached to a code address.

If the symbols table gets very large the symbolic output routines will become pain-

fully slow, particularly on an 8088 based PC. This problem can be avoided by using

modular programming and translating a subset of the modules in the debug mode.

Another alternative is to use the “SYMBOLS OFF” command to suppress symbolic

output Symbolic input is not affected by this command.

Page 23

EV80C196KB Microcontroller Evaluation Board User’s Manual -25

Controlling Lengthy Commands

Most of the commands supported by iECM-96 appear to complete without delay.

Some commands (e.g. displaying or filling a large area of memory) take an appreciable length of time to complete. In general these commands can be aborted by

entering a CARRIAGE-RETURN. Those commands which display a large amount

of information can be paused by hitting the SPACE bar. After you have checked the

data currently on the screen you can depress the SPACE bar again to resume the

output.

Aborting from iECM-96

Entering a control-C will cause the iECM-96 to close any open files and return to

DOS.

Initiating and Terminating iECM=96

This section describes the commands for invoking iECM-96 from DOS and exiting

back to DOS.

ECM96

This command, entered at the DOS prompt, loads the iECM-96 software and executes it. Several options are available with this command. Option strings always

start with a hyphen (“-‘I) and can be entered in upper or lower case. The operation

of these options is described below. Any or all of these options can be entered in

any order, if the options are contradictory then the actual option accepted is the last

one entered.

-COM2, -COMl

These options tell the iECM-96 software which serial communication port is to be

used. If neither of these options is entered then COMl will be used as a default. If

iECM-96 detects valid CTS (Clear To Send) and DSR (Data Set Ready) signals from

the appropriate COM port it will sign on and display a command prompt. If the target

is stopped the command prompt will be an asterisk (“*“). If the target is already

running the prompt will be a greater-than sign (5”).

-DIAG

If CTS or DSR are not present, iECM-96 will complain about it and ask if you want to

proceed or exit. It is possible, but not likely, that iECM-96 will operate properly even

after compl’aining. It is more likely that there is a problem with the serial port or the

cabling which will prevent proper operation. If the problem is not obvious (e.g.

disconnected cable or no power to the target hardware) then the -DIAG invocation

option can be used to help isolate the problem. The -DIAG option puts the iECM-96

system in a special mode which allows many tests to be used to find interfacing

problems, or target bugs.

The diagnostic mode is intended to support debugging of boards which use the

iECM-96. It can be particularly useful in systems which have multiple address

decoding modes, such as the EV80C196KB. Upon reset this board has EPROM at

location 2080H, the address where the 8OC196KB starts execution. After executing

some initialization code, the board can change the address decoding so that

ROMsim/RAM is available in the partition which contains 2080H and the RISM is

relocated to another area. This allows you to download code which is designed to

operate in the on-chip ROM of MCS-96 family parts (2000H - 3FFFH). The diagnos-

tic mode allows the use of diagnostic routines which disappear from memory space

Page 24

-269 EV80C196KB Microcontroller Evaluation Board User’s Manual

when the RAM is mapped into the system. It also provides a simple routine to check

the communications interface between the host and the target.

In the EV80C196KB board, there is a serial port loop-back mode which allows debugging the host/board interface. Upon reset the board is in the echo mode. Until it

receives an ASCII slash (I’/“) or reverse-slash (‘7”) it will increment every character it

receives from the host and send the incremented value back to the host. It will also

display the binary code of the character the board received on the Port 1 LED%. If a

reverse slash is received by the RISM it will leave the echo mode (set USER MAP

flag true), remap memory and start normal operation. If a slash is received it-will

stop echoing incremented received data and start responding to RISM commands

with the diagnostic flag set. In this mode there are diagnostic routines resident in

EPROM which are useful for debugging the board. Initially after invoking the diagnostic mode, the Program Counter points to the beginning of a RAM test at 2200H.

See the source code listing in appendix C for further details.

Note: The target hardware will have to be reset before using the DIAG command option.

Note: When executing diagnostic routines from EPROM, certain commands

such as Breakpoints and Stepping will not work as they need to modify the

code to work properly.

When the host software is invoked in the diagnostic mode it will tell you to enter

characters on the keyboard. These characters will be sent to the target and the

response from the target will be displayed on screen. This is a simple confidence

check on the serial communication channel. You are told to enter a slash or reverse-slash to terminate this mode and proceed in either the diagnostic mode or the

normal user’s mode. If the user interface is invoked without the -DIAG option it will

immediately transmit a reverse-slash which should put the target in the normal

mode. Systems which do not implement the diagnostic mode will load the reverseslash into the RISM-DATA register where it will languish till more useful data is sent

by the host.

-8096, -8096BH, -Cl 96KB

These three options control the single line assembler and the disassembler in the

iECM-96. If the 8096 (8x9x-90) or 8096BH (8x9xBH) options are selected then the

additional instructions in the 8OC196KB will be considered invalid for both the single

line assembler and the disassembler. If none of these options are selected then the

iECM-96 will default to Cl 96KB mode.

-NOTYPES

This option will cause the object file loader to ignore type definition records in the

object module. If this is invoked then the symbolic I/O routines will only recognize

basic data types such as BYTES, WORDS, and LONGS. More complex data types

such as PLM arrays and structures will not be recognized. This option is included

because early versions of the host software got confused while loading certain type

definition records generated by C-96. These problems have been fixed but the

option was left in case similar problems remain.

Page 25

EV80C196KB Microcontroller Evaluation Board User’s Manual -27-

-POLL, -SIGNAL

These two options control how the host software detects whether or not the user’s

code is running. If poll mode is selected then the host will periodically poll the target

with a REPORT-STATUS command. This takes no additional hardware but forces

the target to waste instruction cycles responding to the poll. The signaling mode

avoids this overhead but requires that the target set the Ring Indicator modem

control line whenever it is running user code. The user interface will then check this

line before it issues a REPORT STATUS command. If neither of these options is

selected then the signal mode isselected as a default. On the EV80C196KB the

OUT1 # pin of the 82510 is used to generate this running signal. Therefore, the

signal mode is recommend.

RESET SYSTEM

RES SYSTEM

RESET

RES

This command and its abbreviations will reset the entire target hardware system if

the target system is implemented to support this operation. On the EV80C196KB

jumper shunt E20 must be installed from B to C for this command to work properly.

This command operates by dropping the DTR modem control line. This comes into

the target as DSR. After dropping DTR the iECM-96 software will wait about 1

second to allow the target to complete its initialization routines. The iECM-96 will

politely warn of this time delay and then ignore the user until it expires. Unless

special precautions are taken in the design of the target system, any data in RAM

(including downloaded object code) may be corrupted by the reset. On the

EV80C196KB, the RAM contents should not be affected by a RESET.

DOS

This command enables you to temporarily leave iECM-96 and return to DOS. Once

you have suspended iECM, you may perform other functions in DOS, including

using other software programs, such as ASM-96, as long as there is sufficient mem-

ory to do so.

To reenter iECM, type exit at the DOS prompt. iECM will return with all conditions in

effect at the time it was suspended.

QUIT

This command will close any files that iECM-96 has opened and exit to DOS. Note

that this command can be used even if the target is running. iECM-96 sets the

selected COM port to 9600 baud, 8 bits, no parity, and one STOP bit. The port will

be left in this state by iECM-96 when control is returned to DOS.

Page 26

-289

EV80C196KB Microcontroller Evaluation Board User’s Manual

Default Base Commands

These commands are used to set the default base for numeric input and output. The

valid bases are: 16 (hexadecimal) , 10 (decimal), and 8 (octal). The default base is

used to display variables. It is not used to display addresses (which are displayed in

hexadecimal) or breakpoint numbers (which are displayed in decimal). The default

base is also used to enter numbers into the command parser, but it is possible to

override the default base during input by adding a character at the end of the number which forces the appropriate base to be used. The override characters are H (or

h) for hexadecimal, T (or t) for decimal, and 0 (or o) for octal. The override character must appear immediately following the last digit of the number with no intervening space.

BASE

This command will display the current default base.

BASE=cvalid-base>

This command will set the current default base to <valid-base>. When entering this

command it is advisable to use an override character to select the new default base:

BASE=1 00

; selects octal

BASE=1 OT ; selects decimal

BASE=1 OH

; selects hexadecimal

This avoids confusion when changing bases. As an example of the confusion which

is avoided, consider the following commands entered while the base is hexadecimal.

The command:

BASE=1 0

will leave the default base as hexadecimal and the command:

BASE=1 6

will result in an error because 16H (22T) is not a valid base. The command:

BASE=OA

will select decimal as the default base but it is cleaner and simpler to use the over-

ride character:

BASE=1 OT

This works independently of the current default base and leaves a useful record in

log or list files which may be open.

Page 27

EV80C196KB Microcontroller Evaluation Board User’s Manual -29-

FILE OPERATIONS

iECM-96 uses files in the host system to load and save object code, enter predefined strings of commands, to keep a log of commands that are entered by the user,

and to keep a record of an entire debug session which includes both the characters

entered by the user and the response generated by iECM-96 on the host screen.

The commands which operate with files are described in the following sections.

Loading and Saving Object Code

iECM-96 accepts object files which are generated by Intel’s development tools.

iECM-96 will not accept files which contain unresolved externals or files which contain relocatable records. These files must be passed through RL-96 in order to

resolve the externals and/or absolutely locate the relocatable segments. iECM-96

will also not accept HEX format files. There is a utility on the disk (HEXOBJ.EXE)

for converting HEX format files to Intel object format files loadable by iECM-96.

While still in DOS type “HEXOBJ <filename>.hex <filename>.obj”cCR> to convert

<filename>.hex to a usable format for iECM-96. HEXOBJ does not attempt to convert any symbolic information contained in the HEX file. The iECM-96 commands

which operate on object files are:

LOAD <filename>

LOADSYM <filename>

SAVE caddr> TO <addr> IN <filename>

The metasymbol <filename> means that a valid MS-DOS file name must be entered

in that position of the command string.

LOAD <filename>

This command loads the content records of the object file <filename> into the target

memory and loads any associated symbolic information into a symbol table maintained in the host system’s memory.

LOADSYM <filename>

This command loads the symbolic information from <filename, into the symbol table

maintained in the host system but does not load the content records into the target’s

memory. This command is useful when you have left a debug session with the

target still running a program that has been loaded. At a later time you can reinvoke iECM-96 and interrogate the running program without stopping it. The

LOADSYM command allows the use of the symbolic information contained in the

object file without reloading the content records. (Content records cannot be loaded

while the target is running).

SAVE caddr> TO caddr> IN <filename>

This command saves a region of memory as an object file which can be reloaded

into the target memory at some latter time. No attempt is made to include any

symbolic information which may have been in the symbol table maintained in the

host system.

Page 28

-301

EV80C196KB Microcontroller Evaluation Board User‘s Manual

Other File Operations

In addition to object files, the iECM-96 makes use of include files, log files, and list

files. Include files contain commands to be executed by iECM-96, they must contain

the exact sequence of ASCII characters that you would enter from the keyboard to

execute the command. Include files can be tedious to generate with a text editor so

iECM-96 can generate log files in which are stored characters entered by the user.

The intent is that log files be used later as include files to recreate command sequences. List files keep a running record of both commands entered by the user

and of the response generated by iECM-96. Comments can be included in list and

log files to make them easier to understand. A comment starts with a semicolon (I;‘)

and ends with a carriage return or ESC. The semicolon is considered to be part of

the comment but not the CR or ESC. The command parser will ignore comments

but will put them in the list and log files.

Note: on the software disk included with the EV80C196KB is a file called

DEMO.LOG. DEMO.LOG is a sample iECM-96 session for you to invoke and

become more familiar with the features of iECM-96. Appendix G is a printout

of DEMO.LST which was created by turning on the list feature and invoking

DEMO.LOG by typing ‘*include demo.log”<CR> at the iECM-96 *‘*” prompt.

The list and log files commands allow for default filenames and allow either overwrit-

ing existing data in the file or appending data at the end of the file. This allows you

to gather list and log data in the default files which avoids the creation and manage-

ment of a large number of separate files. Log and list files are stamped with the

date and time whenever they are opened to make it easier to use this capability and

then go back and sort out the data from several debug sessions with a text editor.

The commands involved in include, log, and list operations are:

INCLUDE <filename>

F’AUSE LIST

LIST <filename>

LOG

~;XY;~~narne>

LISTON

LOGOFF

LOGON

Three of these commands require you to supply a valid file name, the rest use the

appropriate file name that has already been entered.

INCLUDE <filename>

This command will attempt to open <filename> as a read only file.

If the file can be

opened then the command parser will take commands from that file until the end of

the file is reached. The include file will then be closed. Only one include file will be

opened at a time.

Page 29

EV80C196KB Microcontroller Evaluation Board User’s Manual -31-

PAUSE

This command is documented in this section because it is intended to be used as

part of INCLUDE files. It is not really a file oriented command itself. When this

command is entered the iECM-96 will stop parsing commands until a SPACE character is entered from the keyboard (it can’t come from an INCLUDE file). This provides a method of pausing in the middle of an INCLUDE file operation until you have

a chance to see what’s going on and acknowledge the pause condition by depress-

ing the SPACE bar.

LIST

This command behaves like the LIST <filename> command described below except

that it uses the last <filename> that was entered as part of a LIST <filename> com-

mand: If no such command has been entered then the default filename “LIST.ECM”

will be used.

LIST <filename>

This command will attempt to open <filename> as a writable file.

If a file with cfile-

name> already exists then iECM-96 will ask if the file is to be overwritten or if the

new data should be appended to the end of the existing file. It will then open the file

and stamp it with the current date and time from the system clock. After this, com-

mands entered by the user and the responses generated by iECM-96 will be recorded in the file.

LOG

This command behaves like the LOG <filename> command described below except

that it uses the last <filename> that was entered as part of a LOG <filename> command. If no such command has been entered then the default filename “LOG.ECM”

will be used.

LOG <filename>

This command will attempt to open <filename> as a writable file.

If a file with cfilename> already exists then iECM-96 will ask if the file is to be overwritten or if the

new data should be appended to the end of the file.

It will then open the file and

stamp it with the current date and time. After this, commands entered by the user

will be recorded in the file. Note that this file may contain nonprintable characters

(e.g. ESC).

LISTOFF and LISTON

The LISTOFF closes a LIST file that has been specified by the LIST command. This

stops new list information from being recorded. The LISTON re-opens the list file in

the append mode so that recording can start again.

LISTON also stamps the list file

with the current date and time from the system clock.

LOGOFF and LOGON

The LOGOFF closes a log file that has been specified by the LOG command. This

stops new list information from being recorded. The LOGON re-opens the log file in

the append mode so that recording can start again. LOGON also stamps the list file

with the current date and time from the system clock.

Page 30

EV80C196KB Microcontroller Evaluation Board User’s Manual

PROGRAM CONTROL

Commands which control program execution allow you to reset the processor, set

execution breakpoints, start execution, stop execution, step, and super step. The

commands will be grouped by their major function for the sake of discussion.

Resetting the Target

The processor can be reset by executing the iECM-96 command:

RESET CHIP

This command physically resets the processor by setting the RISM-DATA register

to OXXXXOOOl and issuing a MONITOR-ESC RISM command which will cause the

target to perform a RST instruction.

Breakpoints

iECM-96 provides sixteen program execution breakpoints. If a given breakpoint is

inactive it is set to zero, if it is active then it is set to the address of the first byte of an

instruction. Breakpoints set to addresses which are not the first byte of an instruction

will cause unpredictable errors in the execution of the user’s code. When execution

is started iECM-96 saves the user code byte at any active breakpoint and substitutes a TRAP instruction for that byte. Executing a TRAP instruction will cause the

iECM-96 to restore the user code bytes where the TRAP instructions were substituted and then decrement the user’s program counter so that it points at the original

instruction. The user’s program will appear to stop execution immediately before

executing the instruction with a breakpoint set on it. All the TRAPS will be removed

from the user’s code and the original code restored.

Note: Most monitor programs similar to iECM-96 display a message on the

console when a break occurs (e.g. “Program break at 1234H”). This is not

done in iECM-96 because the system supports concurrent interrogation of the

target which the user’s code is running; it is possible (perhaps probable) that

the break will occur while you are in the middle of displaying or modifying the

state of the target. Any special break message would have to interrupt the

execution of the command. Because of this the iECM-96 does not output a

special break message. You have two ways to find out that a break occurred:

I)- The prompt will change from a greater-than 5” to an asterisk (“*“).

2). The status of the processor shown in the “control panel” at the top of the console

screen will change from “running” to “stopped”.

Commands which set the breakpoint array are:

:l[ cbp-number> ]

BR [ cbp-number> ] = <code-addr>

The square brackets in the latter two commands are part of the command syntax

and must be entered by the user, the angle brackets are part of the “meta” language

used to describe the syntax. Breakpoints can be displayed while your code is running but they cannot be modified.

Page 31

EV80C196KB Microcontroller Evaluation Board User’s Manual -33-

NOTE: BR[O] and BR[l] can also be set by the GO command by using the TILL

clause; all of the breakpoints will be cleared by the GO command if the FOREVER clause is used.

BR

This command will display all of the active breakpoints (i.e. those not set to zero).

You will also be informed if no breakpoints are active.

BR [ cbp-number> ]

This command will display the setting of the selected breakpoint and wait for input

from you. If you enter a carriage-return the command will terminate. If you enter an

ESC the next sequential breakpoint will be displayed. If you enter a numeric value

then the selected breakpoint will be loaded with the value and the iECM-96 will

again wait for input. At this point you can enter either a CARRIAGE-RETURN or an

ESC. As before, the ESC will cause the iECM-96 to display the next breakpoint and

the CARRIAGE-RETURN will terminate the command. This command will wrap

around from the last breakpoint (1%) to the first breakpoint (0).

BR [ cbp-number> ] = <code-addr>

This command sets the specific breakpoint specified by cbp-number> to the value

<code-addr>.

Program Execution

These commands start and stop execution of user code. The commands provided

are:

2: FOREVER

GO FROM <code-addr>

GO FROM <code-addr> FOREVER

GO FROM <code addr> TILL <code-addr>

GO FROM ccodezaddr> TILL <code-addr> OR <code-addr>

GO TILL <code-addr>

;AqflLL <code-addr> OR <code-addr>

If a GO with breakpoint command is entered, the user code bytes at the breakpoints

will be saved and TRAPS will be installed. When a breakpoint is reached the user’s

software will stop before the instruction which caused the breakpoint and the IECM96 software will restore the original user code.

Note that this is different from the

operation of iSBE- (and most ICE modules) which stop just afterthe instruction

executes. A problem associated with stopping before the break instruction executes

is that subsequent GO commands may run into the breakpoint before any user code

is executed. The iECM-96 avoids this problem by skipping the setting of any breakpoints set on the instruction that the current PC points to. If this happens to remove

the last breakpoint set then you will be warned but the GO will still execute with no

breakpoints enabled. IF this happens you can use the HALT command to stop the

program a

Page 32

-34- EV80C196KB Microcontroller Evaluation Board User’s Manual

None of the GO commands can be executed while the user’s code is already run-

ning; the HALT command cannot be executed if the user’s code is not running. The

GO commands which set breakpoints use BP[O] and possibly BP[l]. Any break

value already in one of these breakpoints will be overwritten and destroyed by these

GO commands. If possible the user should reserve the first two breakpoints for use

by the GO commands and set the remaining breakpoints (if required) explicitly with

the BR commands.

GO

This command starts execution of the user’s code using the current value of user’s

PC and the current breakpoint array.

GO FOREVER

This command clears the breakpoint array and starts execution at the current value

of the user’s PC.

GO FROM <code addr>

This command loads the user’s PC with <code-addr> and starts execution of the

user’s code using the current breakpoint array.

GO FROM <code-addr> FOREVER

This command loads the user’s PC with <code-addr>, clears the breakpoint array,

and starts execution of the user’s code.

GO FROM <code addr> TILL <code addr>

This command lo& the user’s PC w%h the <code-addr> which follows the FROM

keyword, sets the first breakpoint (BP[O]) to the <code-addr> which follows the TILL

keyword, and then starts execution of the user’s code.

GO FROM <code-addr> TILL <code-addr> OR <code-addr>

This command acts like the previous command except that it also sets the second

breakpoint (BP[l]) to the ccode_addr> which follows the OR keyword.

GO TILL <code-addr>

This command sets the first breakpoint (BP[O]) to <code-addr> and then starts the

execution of user code using the current setting of the user’s PC and the breakpoint

array 0

GO TILL <code-addr> OR <code addr>

This command acts like the previ&s command except that it also sets the second

breakpoint (BP11 J) to the <code-addr> which follows the OR keyword.

HALT

This command stops execution of user code by forcing the processor to execute a

jump to self instruction in a reserved location.

Page 33

EV80C196KB Microcontroller Evaluation Board User’s Manual -35,

Program Stepping

These commands allow stepping through programs one instruction at a time. Between instructions the iECM-96 commands can be used to check the state of the

variables changed by the instruction to ensure that the program is operating properly. Stepping through code allows a far more detailed look at what is going on in the

program. The price that is paid for this detail is that stepping does not occur in real

time; this makes it difficult or perhaps impossible to use on code that is tied to real

time events.

Stepping while interrupts are enabled would be confusing since interrupt service

routines will be stepped through as well as sequential code. iECM-96 avoids this

problem by artificially locking out interrupts while stepping, ignoring the state of the

interrupt enable (El) or interrupt mask.

Super-Stepping is similar to stepping except that interrupts are not artificially suppressed. Also, an interrupt service routine or a subroutine call (and the body of the

subroutine that is called) is treated as one indivisible instruction by the super-step

command. This allows the user to ignore the details of subroutines and interrupt

service routines while checking out code. Every time an instruction is “superstepped” all the service routines associated with enabled pending interrupts will be

executed. This may allow limited stepping through code while operating in a concurrent environment but the system will not operate in real time. A better approach is to

use the GO command to execute to a specified breakpoint and then step through

the code being tested looking for proper operation.

iECM-96 implements the step operation by using the TRAP instruction. To step over

a given instruction iECM-96 determines all the possible subsequent instructions and

places TRAPS at these locations. After doing this it allows the user’s program to

execute until it runs into one of these TRAPS and then restores all of the user code

bytes which were overwritten with TRAPS. If iECM-96 is to step over a conditional

branch, two possible subsequent instructions exist in the sequential code of the

program. Any other instruction can only have one “next” instruction. A TRAP is also

set at location 2080H in case the target is reset during the step.

Super-stepping is accomplished by setting TRAPS like the STEP except for CALL

instructions which are treated as a special case. During a STEP the iECM-96 will put

the TRAP at the target address of a call; during a super-step the TRAP will be

placed at the instruction following the CALL. Interrupts are suppressed during STEP

(not SS) operations by saving the user’s El bit, clearing it before the STEP occurs,

and then restoring it. In order to make sure the instruction which is executed does

not modify the El bit, several instructions (PUSHF, POPF, PUSHA, POPA, DI, El)

are simulated by the iECM-96 software rather than being executed by the target

processor. The 80C196KB instruction IDLPD is also simulated during STEP to

prevent the target from locking up. The simulation treats the IDLPD as a two byte

NO-OP. Note that the simulation of instructions only occurs during STEP operations During a GO or SS command all instructions are executed by the target.

Page 34

-360

EV80C196KB Microcontroller Evaluation Board User’s Manual

The iECM-96 commands which implement step operations are:

STEP

STEP <count>

STEP FROM <code-addr>

STEP FROM <code-addr> <count>

ss

SS <count>

SS FROM <code-addr>

SS FROM <code-addr> <count>

Aside from the style of the actual step operation, the SS and STEP commands

beha\ie the same. They will be described together and will be called single-stepping.

{STEP 1 SS}

This command single-steps one time.

{STEP 1 SS } <count>

This command single-steps <count> times.

{ STEP 1 SS } FROM <code-addr>

This command loads the user’s pc (PC) with <code-addr> and then single-steps

one time.

{ STEP 1 SS } FROM <code-addr> <count>

This command loads the user’s pc (PC) with <code-addr> and then single-steps

<count> times.

Page 35

EV80C196KB Microcontroller Evaluation Board User’s Manual -37-

DISPLAYING AND MODIFYING PROGRAM VARIABLES

iECM-96 provides commands to display and modify program variables in several

formats. In addition to simple variables such as bytes and words, more complicated

variables such as reals and character strings are supported. iECM-96 commands

allow variables to be displayed or initialized either individually or as regions of mem-

ory which contain variables of the given type.

Supported Data Types

BYTE

A BYTE is an eight-bit variable. No alignment rules are enforced for BYTE variables.

CHAR

A CHAR is a special case of a BYTE. CHAR variables are displayed as ASCII char-

acters.

WORD

A WORD is a 16-bit variable. The address of a WORD is the address of its least

significant byte. A WORD must start at an even byte address.

DWORD

A DWORD is a 32-bit variable. The address of a DWORD is the address of its least

significant byte. A DWORD must always start at an even byte address. If a DWORD

variable is to be accessed as a register by an 8096 instruction then a more restrictive alignment rule is enforced: it must start at an address which is evenly divisible

by 4. This more restrictive alignment rule will only apply to iECM-96 commands

when using the single line assembler.

REAL

A REAL is a 32-bit binary floating point number which conforms to the FPAL96

definition. The 32 bits contain a sign bit, an 8-bit exponent field, and a 23-bit fraction

field. iECM-96 commands use standard scientific notation to deal with REAL num-

bers Note that the FPAL96 has special representations for +infinity and for NaN’s

(Not a Number--used to signal error conditions) if iECM-96 detects one of these

special values it will output an appropriate text string instead of trying to display the

value in scientific notation.

STACK

A STACK variable is a 16-bit variable which resides in the system stack. The addresses of stack variables (cstack7addr> are taken to be relative to the current

stack pointer and must be word alrgned.

STRING

A STRING is a sequence of ASCII characters which are terminated by the NUL

character. The ASCII character NUL has the binary value of zero.

In addition to supporting access to variables of the above types, iECM-96 also

provides commands to access the special program variables PC (program counter),

PSW (program status word) and SP (stack pointer). These commands are dis-

cussed at the end of this section under the heading “Processor Variables”.

Page 36

-389

EV80Cl96KB Microcontroller Evaluation Board User’s Manual

BYTE Commands

There are four forms for the BYTE commands:

BYTE <byte-address>

BYTE <byte-address> = <byte-value>

BYTE <byte-address> TO <byte-address>

BYTE <byte-address> TO <byte-address> = <byte-value>

All of these commands can be used whether or not the user’s program is running.

BYTE <byte-address>

This form is used to examine and then possibly change one or more sequential

BYTE variables. When this command is invoked iECM-96 will display the

<byte-address> symbolically if a valid symbol exists for that <byte-address>.

Whether or not the symbolic display occurs, iECM-96 will display the

<byte-address> in hexadecimal notation, the value of the BYTE in the default base

and wait for an input from you. You can respond with a CARRIAGE-RETURN

character, an ESC character, or by entering a numeric value. A CARRIAGE-RE-

TURN will terminate the command. An ESC will result in the display of the next

sequential BYTE variable. If a numeric value is entered then the BYTE variable will

be set to this value and the iECM-96 will again wait for input. At this point you can

respond only with an ESC or CARRIAGE-RETURN. As before, the ESC will display

the next sequential BYTE and the CARRIAGE-RETURN will terminate the command.

BYTE <byte-address> = <byte value>

This form is used to set an indizdual BYTE variable without first checking its current

value. When invoked, this command sets the BYTE variable at <byte-address> to

<byte-value>.

BYTE <byte-address> TO cbyte_address>

This form is used to display a region of memory as a sequence of BYTE variables.

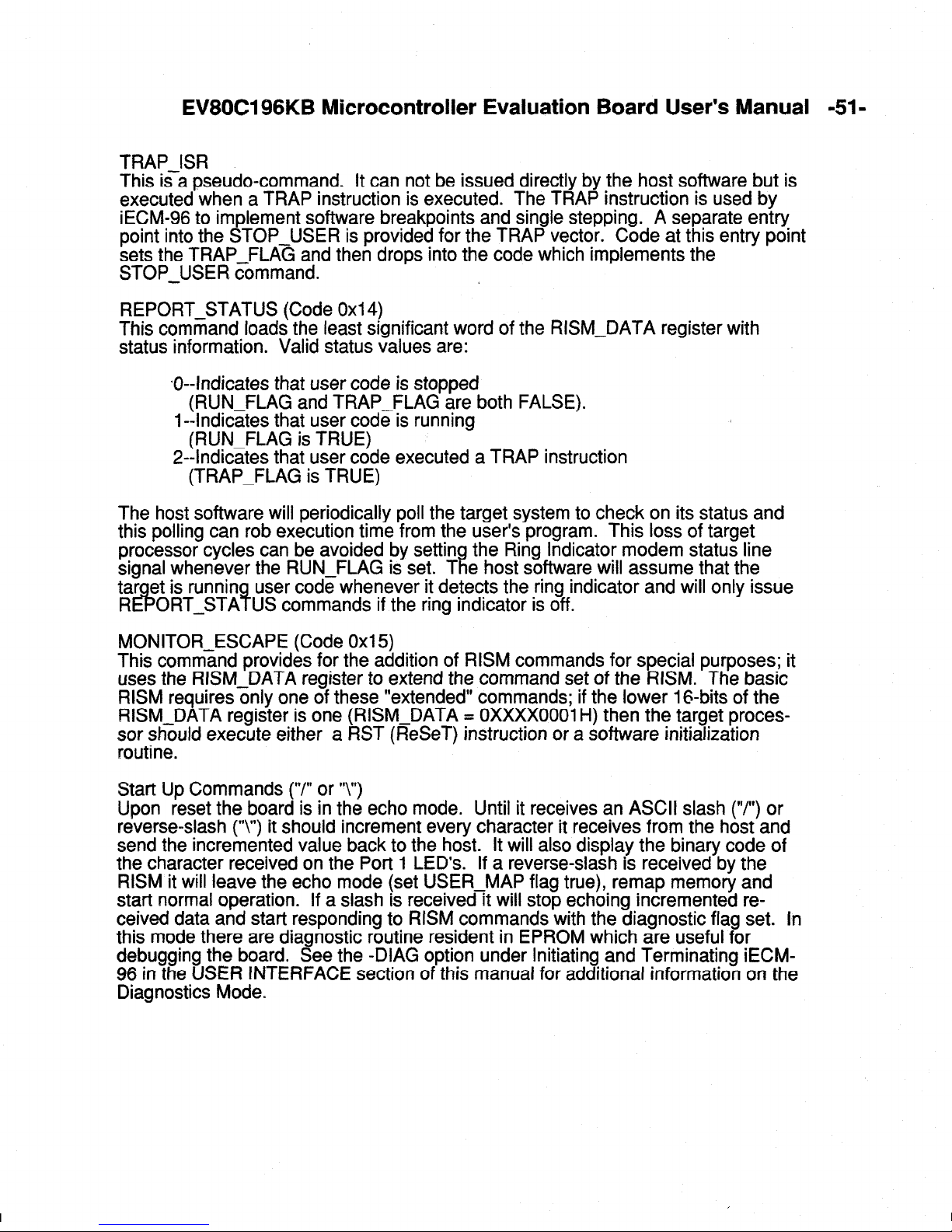

When this command is invoked, iECM-96 will start by displaying the current default