Page 1

Diversified Technology, Inc.

CPB4612

Configuration and Maintenance

Guide

Rev 1.2

CPB4612 CPCI Board

with a Intel® Pentium® M

© Copyright 2005 by Diversified Technology, Inc. All rights reserved. Printed in the

United States of America. No part of this publication may be reproduced, stored in a

retrieval system, or transmitted, in any form or by any means, electronic,

mechanical, photocopying, recording, or otherwise without prior permission of the

publisher.

Page 2

CPB4612 Configuration and Maintenance Guide

Return Shipment Information

If service or repair is required, contact DTI’s Service Department for a Return Material Authorization (RMA)

number and shipping instructions. If the product is out of warranty, or was damaged during shipment, a

purchase order will be required for the repair. The product should be returned in its original shipping

materials. Contact DTI if replacement material is required. Seal the carton securely and ship prepaid to the

following address with the RMA number on the label.

DIVERSIFIED TECHNOLOGY, INC.

Service Department

476 Highland Colony Parkway

P.O. Box 748

Ridgeland, MS 39158

RMA# ________________

To contact the Service Department:

Telephone: (601) 856-4121

Fax: (601) 856-2888

Email: tech@dtims.com

Items determined to be covered under warranty will be returned freight prepaid. Items not in warranty will be

returned freight collect, contact DTI’s Service Department.

ii

Page 3

CPB4612 Configuration and Maintenance Guide

For Your Safety

CAUTION: The cPB-4612 contains a lithium battery. This battery is not field-replaceable.

There is a danger of explosion if the battery is incorrectly replaced or handled. Do not

disassemble or recharge the battery. Do not dispose of the battery in fire. When the battery

is replaced, the same type or an equivalent type recommended by the manufacturer must be

used. Used batteries must be disposed of according to the manufacturer's instructions.

Return the board to DTI for battery service.

iii

Page 4

CPB4612 Configuration and Maintenance Guide

Revision History

Date Revision Summary of Corrections

08/31/04 1.0 Initial Release

10/12/04 1.1 Added links throughout manual.

8/19/05 1.2 Removed references to ethernet signal routing.

Update BIOS Section

iv

Page 5

CPB4612 Configuration and Maintenance Guide

Table of Contents

Return Shipment Information...................................................................................................................................ii

For Your Safety...................................................................................................................................................... iii

Revision History......................................................................................................................................................iv

Table of Contents......................................................................................................................................................v

Tables ......................................................................................................................................................................ix

Figures.....................................................................................................................................................................ix

Document Organization............................................................................................................................................x

1 INTRODUCTION......................................................................................................... 1

1.1 Product Definition................................................................................................................................................2

1.2 Features.................................................................................................................................................................4

1.3 Functional Blocks.................................................................................................................................................4

1.3.1 CompactPCI/PSB Architecture............................................................................................................................5

1.3.2 Processor..............................................................................................................................................................6

1.3.3 Chipset.................................................................................................................................................................6

1.3.4 PCI-to-PCI Bridge ...............................................................................................................................................6

1.3.5 Memory and I/O Addressing................................................................................................................................7

1.3.6 Power Ramp Circuitry.........................................................................................................................................7

1.3.7 Rear-Panel I/O .....................................................................................................................................................7

1.3.8 Video....................................................................................................................................................................7

1.3.9 PCI Mezzanine Card (PMC) Interface............................................................................................. ....................7

1.3.10 Dual 10/100/1000 Ethernet Interfaces .................................................................................................................7

1.3.11 10/100 Ethernet Interface.....................................................................................................................................8

1.3.12 IDE Hard Drive....................................................................................................................................................8

1.3.13 Serial I/O..............................................................................................................................................................8

1.3.14 Interrupts..............................................................................................................................................................8

1.3.15 Counter/Timers....................................................................................................................................................9

1.3.16 DMA....................................................................................................................................................................9

1.3.17 Real-Time Clock..................................................................................................................................................9

1.3.18 Reset ....................................................................................................................................................................9

1.3.19 Two-Stage Watchdog Timer................................................................................................................................9

1.3.20 Universal Serial Bus (USB)...............................................................................................................................10

1.3.21 System Environmental Monitor.........................................................................................................................10

1.3.22 LED Indicators...................................................................................................................................................10

1.4 Software ..............................................................................................................................................................10

2 GETTING STARTED ................................................................................................ 11

2.1 Unpacking...........................................................................................................................................................12

2.2 System Requirements.........................................................................................................................................12

2.2.1 BIOS Version.....................................................................................................................................................12

2.2.2 Connectivity.......................................................................................................................................................12

2.2.3 Electrical and Environmental.............................................................................................................................12

2.3 Memory Configuration......................................................................................................................................13

2.4 I/O Configuration...............................................................................................................................................15

2.5 Connectors..........................................................................................................................................................16

2.6 Jumper Options..................................................................................................................................................16

2.7 BIOS Configuration Overview..........................................................................................................................16

v

Page 6

CPB4612 Configuration and Maintenance Guide

2.8

Operating System Installation...........................................................................................................................17

3 CONFIGURATION.................................................................................................... 19

3.1 Switch Descriptions............................................................................................................................................21

3.1.1 PB1 (Reset)........................................................................................................................................................21

3.1.2 J16-1 (BKT-GND to GND)...............................................................................................................................21

3.1.3 J16-2 (+12V to J5-pin D1).................................................................................................................................22

3.1.4 J16-3 (+5V PMC I/O)........................................................................................................................................22

3.1.5 J16-4 (IMPI Disable).........................................................................................................................................22

3.1.6 J17-1 (Not Used)................................................................................................................................................22

3.1.7 J17-2 (CMOS Clear)..........................................................................................................................................22

3.1.8 J17-3 (Disable Onboard Video).........................................................................................................................23

3.1.9 J17-4 (Manufacture Test Mode) ........................................................................................................................23

3.1.10 J18 (Ejector Switch)...........................................................................................................................................23

4 RESET...................................................................................................................... 24

4.1 Reset Types and Sources....................................................................................................................................25

4.1.1 Hard Reset Sources............................................................................................................................................25

4.1.2 Soft Reset Sources .............................................................................................................................................25

4.1.3 Backend Power Down Sources..........................................................................................................................25

4.1.4 NMI Sources......................................................................................................................................................26

5 SYSTEM MONITORING AND CONTROL................................................................ 27

5.1 Monitoring and Control Functions...................................................................................................................28

Figure 5.1: Packet Structure ...........................................................................................................................................28

5.2 IPMB...................................................................................................................................................................28

5.3 Field Replaceable Unit (FRU) Information......................................................................................................29

5.4 Sensors.................................................................................................................................................................29

5.5 Firmware Updates..............................................................................................................................................29

5.6 SMBus Address Map .........................................................................................................................................29

6 IDE CONTROLLER .................................................................................................. 30

6.1 Features of the IDE Controller .........................................................................................................................31

6.2 Disk Drive Support.............................................................................................................................................31

6.2.1 Primary IDE Channel.........................................................................................................................................31

6.2.2 Secondary IDE Channel.....................................................................................................................................31

6.3 IDE I/O Mapping ...............................................................................................................................................31

6.4 IDE Device Drivers.............................................................................................................................................31

7 WATCHDOG TIMER................................................................................................. 32

7.1 Watchdog Timer Overview...............................................................................................................................33

7.2 PCI Configuration Registers.............................................................................................................................33

7.2.1 Base Address Register (10h)..............................................................................................................................33

7.2.2 WDT Configuration Register (60h)...................................................................................................................34

7.2.3 WDT Lock Register (68h).................................................................................................................................34

7.3 Memory Mapped Registers...............................................................................................................................35

7.3.1 Preload Value 1 (BAR+00h)..............................................................................................................................35

vi

Page 7

CPB4612 Configuration and Maintenance Guide

Preload Value 2 (BAR+04h)..............................................................................................................................35

7.3.2

7.3.3 General Interrupt Status (BAR+08h).................................................................................................................36

7.3.4 Reload Register (BAR+0Ch).............................................................................................................................36

7.4 Using the Watchdog in an Application.............................................................................................................37

7.4.1 WDT Unlocking and Programming Sequence...................................................................................................37

7.4.2 Watchdog Reset.................................................................................................................................................37

7.4.2.1 Load Preload Values..........................................................................................................................................37

7.4.2.2 Enabling the Watchdog Reset............................................................................................................................37

7.4.2.3 Reloading the Watchdog....................................................................................................................................37

8 SYSTEM BIOS.......................................................................................................... 38

8.1 BIOS Upgrade and Recovery.............................................................................................................................39

8.1.1 Flash Utility Program.........................................................................................................................................39

8.1.2 BIOS Recovery..................................................................................................................................................39

8.2 BIOS Configuration Overview..........................................................................................................................39

8.2.1 Boot Menu .........................................................................................................................................................40

8.2.2 ROM Utilities ....................................................................................................................................................41

8.2.3 System Summary...............................................................................................................................................43

8.2.4 System Setup......................................................................................................................................................44

8.2.5 IDE Config.........................................................................................................................................................46

8.2.6 Hard Disk Setup.................................................................................................................................................47

8.2.7 Boot Order .........................................................................................................................................................49

8.2.8 Peripherals ......................................................................................................................................................... 51

8.2.9 USB Configuration ............................................................................................................................................53

8.2.10 MISC Config......................................................................................................................................................55

8.2.11 Event Logging....................................................................................................................................................57

8.2.12 Security/Virus....................................................................................................................................................58

8.2.13 Exit.....................................................................................................................................................................59

8.3 Plug and Play (PnP)...........................................................................................................................................60

8.3.1 Resource Allocation...........................................................................................................................................60

8.3.2 PnP ISA Auto-configuration..............................................................................................................................60

8.3.3 PCI Auto-configuration .....................................................................................................................................60

8.3.4 Legacy ISA Configuration.................................................................................................................................61

8.3.5 Automatic Detection of Video Adapters............................................................................................................61

8.4 Console Redirection...........................................................................................................................................61

8.5 System Management BIOS (SMBIOS).............................................................................................................61

8.6 POST CODE LEDS ...........................................................................................................................................61

A SPECIFICATIONS.................................................................................................... 64

A.1 Electrical and Environmental...........................................................................................................................64

A.2 Absolute Maximum Ratings..............................................................................................................................64

A.2.1 DC Operating Characteristics ............................................................................................................................64

A.2.2 Battery Backup Characteristics..........................................................................................................................65

A.2.3 Operating Temperature......................................................................................................................................65

A.3 Reliability............................................................................................................................................................65

A.4 Mechanical..........................................................................................................................................................65

A.4.1 Board Dimensions and Weight..........................................................................................................................66

B CONNECTORS......................................................................................................... 68

B.1 Connector Locations..........................................................................................................................................69

vii

Page 8

CPB4612 Configuration and Maintenance Guide

B.2

J15 (CompactPCI Bus Connector)....................................................................................................................71

B.3 J11 (CompactPCI Bus Connector).................................................................................................................... 72

B.4 J8 (CompactPCI Connector).............................................................................................................................73

B.5 J2 (Rear Panel I/O CompactPCI Connector) ..................................................................................................74

B.6 J1 (10/100 Ethernet)...........................................................................................................................................75

B.7 J4 (Universal Serial Bus 0 connector)...............................................................................................................75

B.8 J3 (COM1 Serial Port).......................................................................................................................................76

B.9 J6, J7, J9, J10 (64bit/66Mhz PCI Mezzanine Connectors).............................................................................76

B.10 J12 and J13 (32bit/33Mhz PCI Mezzanine Connectors).................................................................................80

B.11 J14 (IDE Connector)..........................................................................................................................................82

C THERMAL CONSIDERATIONS ............................................................................... 84

C.1 Thermal Requirements......................................................................................................................................85

C.2 Temperature Monitoring...................................................................................................................................85

D DATASHEET REFERENCE ..................................................................................... 88

D.1 CompactPCI.......................................................................................................................................................89

D.2 Ethernet...............................................................................................................................................................89

D.3 Intel 855GME Chipset.......................................................................................................................................89

D.4 Pentium M processor (FCBGA Package).........................................................................................................89

D.5 PMC Specification..............................................................................................................................................90

D.6 Super I/O.............................................................................................................................................................90

E AGENCY APPROVALS............................................................................................ 92

E.1 CE Certification.................................................................................................................................................. 92

E.2 NEBS compliance...............................................................................................................................................92

E.3 Safety...................................................................................................................................................................92

E.4 Electro-magnetic Compatibility........................................................................................................................92

E.5 Regulatory Information.....................................................................................................................................92

E.5.1 FCC (USA)........................................................................................................................................................92

E.5.2 Industry Canada (Canada)..................................................................................................................................93

F CRT SPECIFICATIONS............................................................................................ 94

viii

Page 9

CPB4612 Configuration and Maintenance Guide

Tables

Jumper Cross-Reference Table........................................................................................................................ 20

Connector Assignments .................................................................................................................................... 68

J15 CompactPCI Bus Connector Pin out.......................................................................................................... 71

J11 CompactPCI Bus Connector Pin out.......................................................................................................... 72

J8 Connector Pin out......................................................................................................................................... 73

J2 Rear Panel I/O Connector Pin out................................................................................................................ 74

J4 Universal Serial Bus 0 Connector Pin out .................................................................................................... 75

Thermal Requirements...................................................................................................................................... 85

Figures

CPB-4612 Faceplate........................................................................................................................................... 3

Functional Block Diagram ................................................................................................................................... 5

Memory Address Map Example........................................................................................................................ 14

I/O Address Map ............................................................................................................................................... 15

Setup Screen .................................................................................................................................................... 17

Default Jumper Configuration ........................................................................................................................... 21

PCB Dimensions ............................................................................................................................................... 66

CPB-4612 Connectors Locations (Topside) ..................................................................................................... 69

Backplane Connectors - Pin Locations............................................................................................................. 70

ix

Page 10

CPB4612 Configuration and Maintenance Guide

Document Organization

This document describes the operation and use of the CPB-4612 Computer Processor Board with an Intel®

Pentium® M. The following topics are covered in this document.

Chapter 1, "Introduction," introduces the key features of the CPB-4612. This chapter includes a product

definition, a list of product features, and a functional block diagram with a brief description of each block. This

chapter can be used to compare the features of the CPB-4612 against the needs of a specific application.

Chapter 2, "Getting Started," provides unpacking instructions and initial setup information for the CPB-4612.

This chapter summarizes configuration information and should be read before using the board.

Chapter 3, "Configuration," describes the jumper settings on the CPB-4612. This chapter details factory

default settings and provides information about tailoring the board to the needs of specific applications.

Chapter 4, "Reset," discusses the reset types and reset sources available on the CPB-4612.

Chapter 5, "System Monitoring and Control," lists various system monitoring and control features available

on the CPB-4612.

Chapter 6, "IDE Controller," provides an introduction to the CPB-4612's IDE Controller. This chapter covers

drive configuration, IDE I/O mapping, device drivers, and the CPB-4612's support for internal and external

disk drives.

Chapter 7, "Watchdog Timer," explains the operation of the CPB-4612's watchdog timer. Sample code is

provided to illustrate how the watchdog's functions are used in an application.

Chapter 8, "System BIOS," discusses recovery from and correction of a corrupted BIOS.

Appendix A, "Specifications," contains the electrical, environmental, and mechanical specifications for the

CPB-4612.

Appendix B, “Connectors,” This chapter provides a connector location illustration and connector pin out

tables. A detailed description and pin out for each connector is given.

Appendix C, "Thermal Considerations," describes the thermal requirements for reliable operation of the

CPB-4612.

Appendix D, "Datasheet Reference," provides links to Websites with information about many of the devices

and technologies used in the CPB-4612.

Appendix E, "Agency Approvals," presents UL, CE, and FCC agency approval and certification information

for the CPB-4612.

Appendix F, "CRT Specifications,” identified features of the CRT4612 Rear Transition Module (RTM).

x

Page 11

Chapter

1 Introduction

This chapter provides an introduction to the CPB-4612 including a product definition, a list of product

features, and a functional block diagram with descriptions of each block.

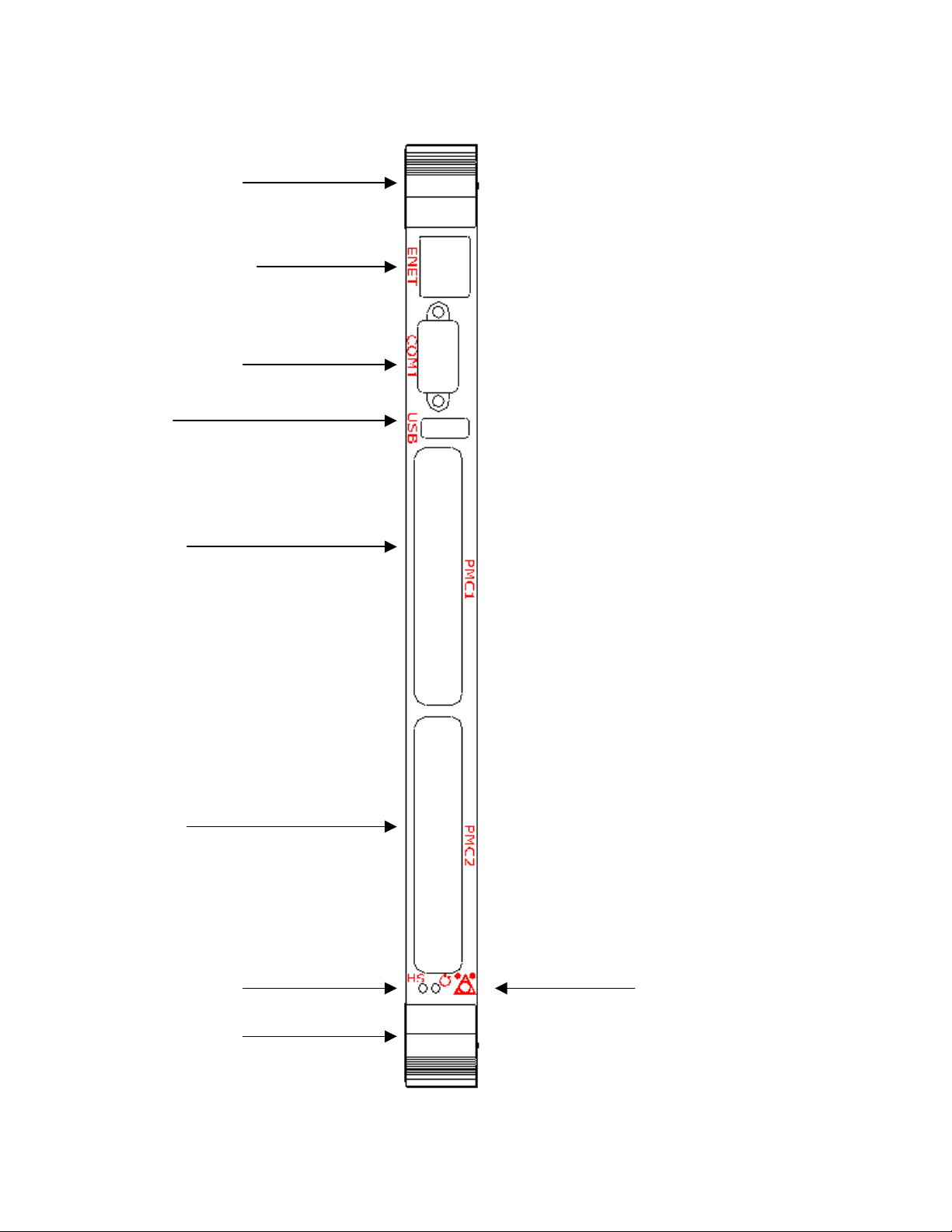

The "cPB-4612 Faceplate" illustration identifies the connectors, indicators, and switches available on the

cPB-4612's faceplate. Optional rear-panel transition boards are available to extend various faceplate

features to a system's rear-panel. For more information about compatible rear-panel transition boards,

see Appendix F.

The CPB-4612 is a 64-bit compliant CompactPCI Pentium M single board computer designed to operate

in either a system slot or a peripheral slot. The cPB-4612 provides Ethernet integration using the Intel

82559 10/100 Base-T PCI Ethernet controller and the Intel 82546EB Fast Gigabit Ethernet Multifunction

PCI Controller. The CPB4612 provides support for IDE hard drives, serial ports, and USB ports. I/O

connections are available at the rear of the chassis using one of DTI’s cRT4612 rear-panel I/O modules.

The CPB-4612 is fully compliant with both the CompactPCI standard and the PICMG 2.16 packet

switching standard.

1

1

1

Page 12

1.1 Product Definition

The cPB-4612 Computer Processor Board is a single board computer designed to work as a modular

component in a CompactPCI system. It utilizes the Intel

®

Pentium® M processor in a micro FCBGA package

along with dual Gigabit Ethernet controllers and the latest in memory and I/O technology to provide an

inexpensive, yet fast and reliable PICMG 2.16 board. The cPB-4612 is CompactPCI Packet Switching

Backplane (CompactPCI/PSB) compatible and draws its power from the J1 and J2 connectors. The cPB4612 includes an Intelligent Platform Management Bus (IPMB) for system management along with IPMI v1.5

compatible firmware.

The cPB-4612 occupies a single 6U high Eurocard slot. The board can be used in either a system master

slot or in a peripheral slot. Though the cPB-4612 is highly integrated, its capabilities can be extended with

pluggable PMC modules. DTI also provides a rear transition board, the cRT-4612, that compliments the

cPB-4612 to extend I/O access to the rear of a system. For more information about PMC options and

accessories contact your DTI sales representative.

2

Page 13

CPB-4612 Faceplate

Ejector Handle

10/100 Ethernet

COM RS-232

Serial Port

USB

PMC

PMC

Hotswap LED

Reset Switch

Ejector Handle

3

Page 14

1.2 Features

There are two SKU's of the cPB-4612. The first is the cPB-4612, which has a 64bit/66Mhz PMC site and a

32bit/33Mhz PMC site. . The second is the cPB-4612 w/ IDE, which has a 64bit/66Mhz PMC site and an

on-board 2.5” HDD IDE connector. Other features include:

• CompactPCI Specification, PICMG 2.0, Version 2.1** compliant

• CompactPCI Specification, PICMG 2.16, Version 1.0** compliant

• 6U single-slot CompactPCI form factor

• Mobile Intel Pentium M, micro FCBGA package

• Intel

• Integrated Intel Extreme Graphics 2 controller

• Dual 10/100/1000 Mb/s Ethernet (both at the J3 backplane connector to support PICMG 2.16)

• 10/100 Mb/s Ethernet (available at the front panel)

• 1 MB of Level 2 cache

• 400 MHz front side bus

• Socketed 256 MB, 512 MB, 1 GB, or 2GB of DDR SDRAM memory at 200, 266, or 333 MHz

• Dual stage watchdog timer

• IPMI support

• Option for either a single on-board PCI Mezzanine Card (PMC) slot (32-bit / 33MHz) or a primary IDE

• 64bit / 66Mhz @ 3.3V PCI Mezzanine Card (PMC) slot

• Two 16C550 RS-232 serial ports (COM1 available at the faceplate, COM2 available through the J5

• Push Button Reset on the front panel

• 1 USB on front panel, 2 USB ports available via RTM

• Rear-Panel I/O Availability (at J5) includes the following:

• Support for Microsoft Windows 2000/XP, Red Hat Linux, and Solaris 8/9

• Standard AT* Systems include:

®

855GME GMCH and 6300ESB ICH

channel that supports an on-board 2.5 inch hard disk

backplane connector)

– Secondary IDE channel

– Serial ATA

– Two USB ports

– VGA video

– Serial Port

– Two enhanced interrupt controllers (8259)

– Three counter/timers (one 8254)

– Real-time clock/CMOS RAM (146818B)

– Two enhanced DMA controllers (8237)

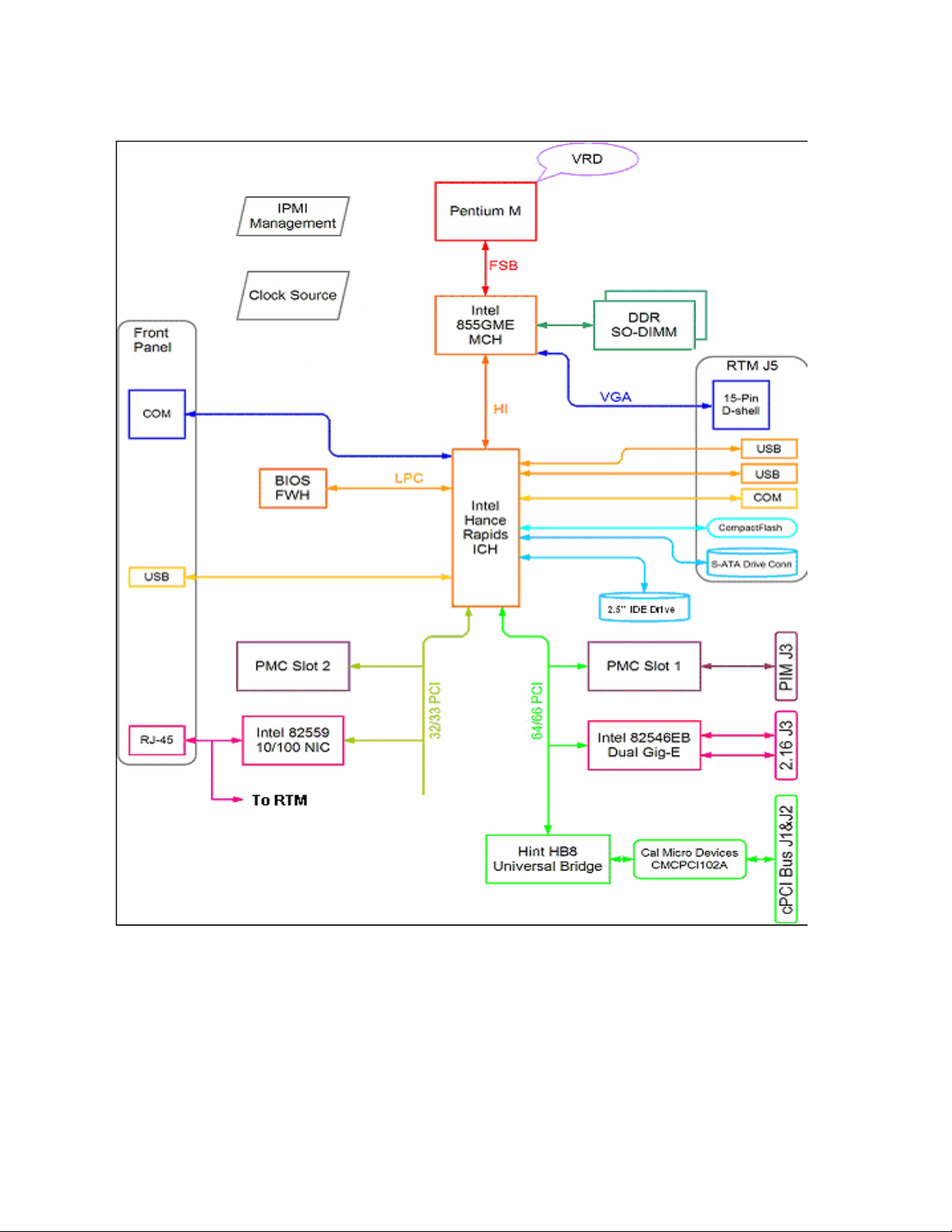

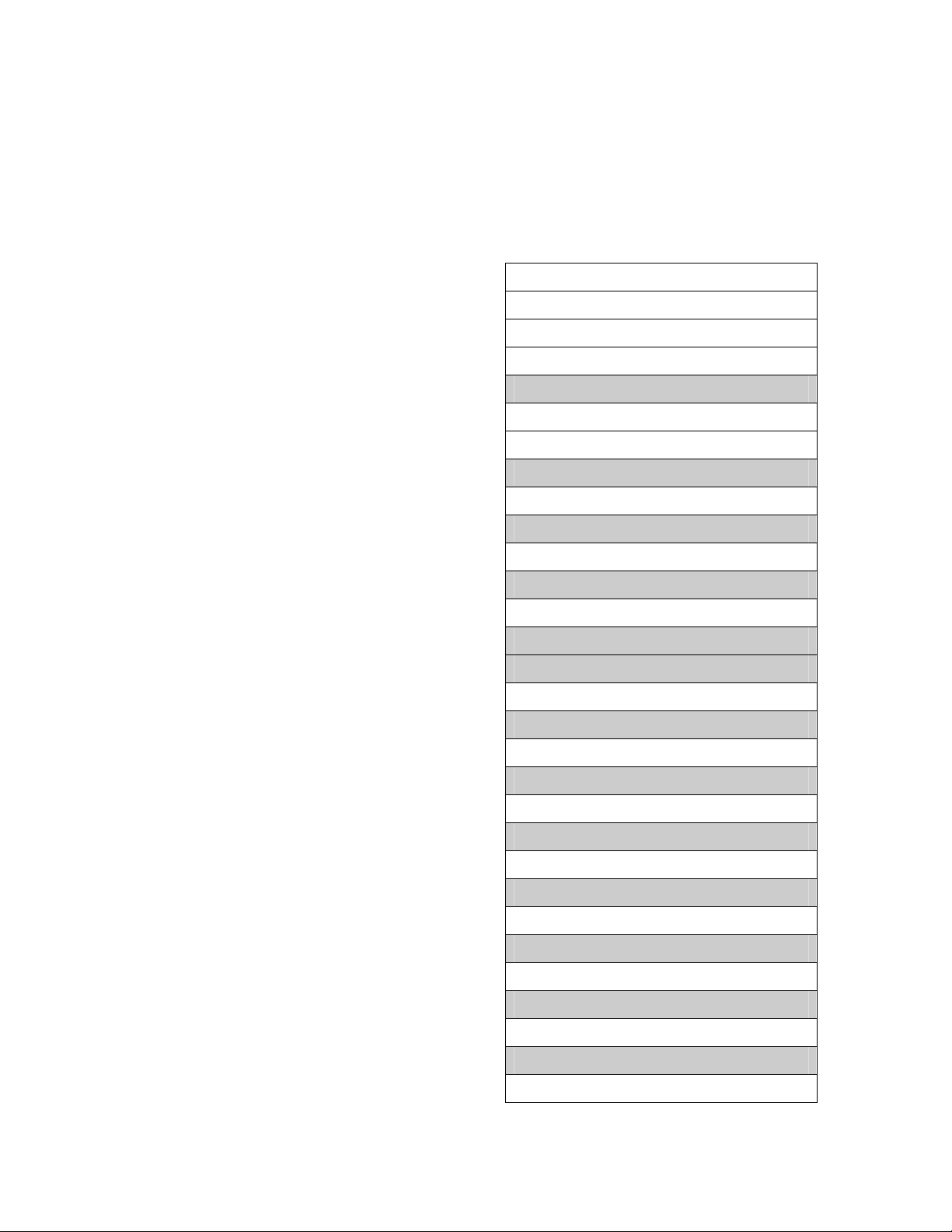

1.3 Functional Blocks

The following topics provide overviews of the cPB-4612's main features, some of which are shown in the

functional block diagram below.

4

Page 15

Functional Block Diagram

1.3.1 CompactPCI/PSB Architecture

The cPB-4612 is designed to operate in a PICMG 2.0 CompactPCI backplane. If the system is placed in a

system slot, the bridge will automatically configure itself as a transparent bridge, and the board will perform

as the host. If the board is placed in a peripheral slot, the bridge will automatically configure itself as a nontransparent bridge, and the board will perform as a peripheral device.

When used in accordance with the CompactPCI Packet Switching Backplane Specification, PICMG 2.16,

Version 1.0, the cPB-4612 functions as a "Dual Link Port Node" board. The cPB-4612 can be connected to a

5

Page 16

system's fabric-switched Link Ports A and B, and can be inserted into system or peripheral slots. The cPB4612 is keyed for insertion into compatible slots.

The "CompactPCI" topic in Appendix D contains a link to the PCI Industrial Computer Manufacturers Group.

1.3.2 Processor

The cPB-4612 uses the Mobile Pentium M in a micro FCBGA package. The 1MB or 2MB on-die transfer L2

cache is integrated with the CPU, eliminating the need for separate components and improving

performance. The FCBGA package Pentium M processor also operates with a 400 MHz Processor Side

Bus for very fast access to memory and data.

The "Mobile Pentium M (FCBGA Package)" topic in Appendix D contains a link to the datasheet for the

processor.

1.3.3 Chipset

The Intel 855GME chipset consists of two controller hubs. The 855GME Memory Controller Hub (MCH)

supports a 400MHz system bus, DDR200/266/333 memory, and an integrated graphics solution w/Intel

Extreme Graphics 2 technology. The 6300ESB I/O Controller Hub (ICH4) makes a direct connection to the

memory for faster access to peripherals. It provides the features and bandwidth required for applied

computing-usage models. The following is a list of features of the 855GME chipset:

• Designed, validated, and optimized for the Intel Pentium M with NetBurst™ micro-architecture

using proven and established building blocks

• 400MHz system bus delivers a high-bandwidth connection between the Intel Pentium M and the

platform, providing 3x the bandwidth over platforms based on Intel® Pentium® III processors

• USB controllers provide high performance peripherals with 480Mbps of bandwidth. This results

in a significant increase over previous integrated 1-4 port hubs at 12Mbps

• Dual UARTs

• Serial ATA

• 64bit/66Mhz PCI-X bus

• 32bit/33Mhz PCI bus

®

• Dual Ultra ATA/100 controllers, coupled with the Intel

software package - support faster IDE transfers to storage devices

• The Intel® Application Accelerator software provides additional performance over native ATA

drivers. The Intel Application Accelerator improves system performance by improving I/O

transfer rates and enables faster O/S load time resulting in accelerated boot times

• Embedded lifecycle support

The "Intel 855GME Chipset" topic in Appendix D contains a link to information about the chipset.

Application Accelerator - a performance

1.3.4 PCI-to-PCI Bridge

The cPB-4612 has a 64bit/66Mhz PCI-X bridge to the CompactPCI backplane. The bridge will configure

itself as a transparent bridge when the board is in a system slot, so that the cPB-4612 can be the system

host. If the cPB-4612 is placed in a peripheral slot, the bridge configures itself as a non-transparent bridge,

and will show up as a PCI device to the host. This allows use of the board in either a system or peripheral

slot.

6

Page 17

1.3.5 Memory and I/O Addressing

The cPB-4612 supports up to 2GB of DDR333/266/200 via two right-angled SODIMM sockets. Memory

can be purchased from DTI separately.

See the "Memory Configuration" and "I/O Configuration" topics in Chapter 2 for more information.

1.3.6 Power Ramp Circuitry

The cPB-4612 features a power controller with power ramp circuitry that allows the board's voltages to be

ramped in a controlled fashion. The power ramp circuitry eliminates large voltage or current spikes caused

by hot swapping boards. This controlled ramping is a requirement of the CompactPCI Hot Swap

Specification**, PICMG 2.1, Version 1.0.

The cPB-4612's power controller unconditionally resets the board when it detects that the 3.3V, 5V, and 12V

supplies are below an acceptable operating limit. Minimum voltage thresholds for the cPB-4612 are: 4.75V

(5V supply), 3.0V (3.3V supply), and 10.0V (+12V supply).

1.3.7 Rear-Panel I/O

The following I/O signals are available from the J5 connector at the back of the cPB-4612. These signals are

available for use by a rear panel transition board such as the cRT-4612.

• Serial port (COM2)

• USB Ports 2 and 3

• Secondary IDE channel

• Serial ATA channel

• Video

1.3.8 Video

The cPB-4612 supports VGA video using Intel’s 855GME video interface. The video is accessed through

the CompactPCI J5 connector. The 855GME can share up to 32MB of system memory with the internal

video.

The onboard video from the Intel 855GME may be disabled by a jumper setting. This will allow use of a PCI

video card only. If the onboard video is enabled and a PCI video card is installed, the PCI video card will be

the primary video source.

The Intel 855GME Chipset topic contains a link to the datasheet for this device.

1.3.9 PCI Mezzanine Card (PMC) Interface

The cPB-4612 provides a 64bit/66Mhz PMC site and a 32bit/33Mhz PMC site, both with front panel access.

The 64bit/66Mhz PMC site is only 3.3V tolerant. The 32bit/33Mhz can be configured to be either 3.3V or 5V

via a jumper setting. Voltage keys are also provided to prevent inadvertently placing a PMC card on PMC

site that does not support its VI/O voltage.

The cPB-4612 w/ IDE provides a 64bit/66Mhz PMC site and a 2.5” HDD IDE connector. The 64bit/66Mhz

PMC site is only 3.3V tolerant. Voltage keys are also provided to prevent inadvertently placing a PMC card

on PMC site that does not support its VI/O voltage.

The "PMC Specification" topic in Appendix D contains a link to the sponsoring organization for the PMC

specification.

1.3.10 Dual 10/100/1000 Ethernet Interfaces

The cPB-4612 provides two 10/100/1000BaseTx Ethernet channels (ENET A and ENET B) through the

Intel 82546EB Fast Gigabit Ethernet Multifunction PCI Controller. The 82546EB consists of both the Media

7

Page 18

Access Controller (MAC) and the physical layer (PHY) interface combined into a single component solution.

Both Ethernet Channels are directed to the rear connector at J3 for PICMG 2.16 support.

The "Ethernet

cPB-4612.

" topic in Appendix D contains links to the datasheets for the Ethernet devices used on the

1.3.11 10/100 Ethernet Interface

The cPB-4612 supports one 10/100 Base-TX Ethernet interface. The Intel 82559EM Ethernet controller

provides this interface. The NIC address programmed into the controller is located on labels on the board.

Link and activity LED signals are on the front panel at the RJ-45 connector.

The "Ethernet

cPB-4612.

" topic in Appendix D contains links to the datasheets for the Ethernet devices used on the

1.3.12 IDE Hard Drive

The cPB-4612 w/IDE supports an onboard ATA/100 2.5” IDE interface. This can be used to connect a 2.5”

hard drive. The IDE interface is implemented using Intel’s 6300ESB I/O Controller Hub (ICH). Note that the

onboard 2.5” IDE connector is not present on versions of the board that support the 33MHz/32 bit PMC site.

All versions of the cPB-4612 supports a second ATA/100 IDE interface through the CompactPCI J5

connector. The IDE interface is implemented using Intel’s 6300ESB I/O Controller Hub (ICH).

All versions of the cPB-4612 supports a Serial ATA/150 interface through the CompactPCI J5 connector.

The IDE interface is implemented using Intel’s 6300ESB I/O Controller Hub (ICH).

Both the 2.5” IDE drive connector and 33Mhz/32bit PMC site cannot both be present at the same time, since

they are in the same physical space on the board. Which one is populated depends on the version of the

board.

See Chapter 6, "IDE Controller", for more information.

1.3.13 Serial I/O

The cPB-4612 provides support for two RS-232 compatible serial ports. COM1 is accessible at the

faceplate through a 9-pin DSUB connector. This port is typically used for test access. COM2 is available at

the J5 Rear Panel I/O connector.

The serial port interface is implemented using Intel’s 6300ESB I/O Controller Hub (ICH).

1.3.14 Interrupts

Two enhanced, 8259-style interrupt controllers provide the cPB-4612 with a total of 15 interrupt inputs.

Interrupt controller features include support for:

• Level-triggered and edge-triggered inputs

• Individual input masking

• Fixed and rotating priorities

Interrupt sources include:

• Counter/Timers

• Serial I/O

• Keyboard

• Floppy disk

• IDE interface

8

Page 19

• Real-Time Clock

• On-board PCI devices

Enhanced capabilities include the ability to configure each interrupt level for active high-going edge or active

low-level inputs.

The cPB-4612's interrupt controllers reside in the 6300ESB device. The "Intel 855GME Chipset" topic in

Appendix D provides a link to the datasheet for this device.

1.3.15 Counter/Timers

Three 8254-style counter/timers, as defined for the PC/AT, are included on the cPB-4612. Operating modes

supported by the counter/timers include:

• Interrupt on count

• Frequency divider

• Software triggered

• Hardware triggered

• One shot

The cPB-4612's Counter/Timers reside in the Intel 6300ESB device. The "Intel 855GME Chipset" topic in

Appendix D provides a link to the datasheet for this device.

1.3.16 DMA

Two cascaded 8237-style DMA controllers are provided on the cPB-4612 for use by the on-board

peripherals.

The cPB-4612's DMA controllers reside in the Intel 6300ESB device. The "Intel 855GME Chipset" topic in

Appendix D provides a link to the datasheet for this device.

1.3.17 Real-Time Clock

The real-time clock performs timekeeping functions and includes 256 bytes of general-purpose, batterybacked, CMOS RAM. Timekeeping features include an alarm function, a maskable periodic interrupt, and a

100-year calendar. The system BIOS uses a portion of this RAM for BIOS setup information.

The cPB-4612's Real-Time Clock resides in the Intel 6300ESB device. The "Intel 855GME Chipset" topic in

Appendix D provides a link to the datasheet for this device.

1.3.18 Reset

The push-button reset on the cPB-4612's faceplate functions as a "Hard Reset". See Chapter 4, "Reset," for

more information about reset sources for the cPB-4612.

1.3.19 Two-Stage Watchdog Timer

The watchdog timer optionally monitors system operation and is programmable for different timeout periods

(from 1 microsecond to 10 minutes). It is a two-stage watchdog, meaning that it can be enabled to produce a

system management interrupt (SMI) or an IRQ (APIC 1, INT 10) before it generates a Reset. Failure to

strobe the watchdog timer within the programmed time period may result in an SMI, a reset request, or both.

A register bit can be read to indicate if the watchdog timer caused the reset event. This watchdog timer

register is not cleared on power-up, enabling system software to take appropriate action if the watchdog

generated the reboot.

See Chapter 7, "Watchdog Timer," for more information, including sample code.

9

Page 20

1.3.20 Universal Serial Bus (USB)

The Universal Serial Bus (USB) provides a common interface to slower-speed peripherals. Functions such

as keyboard, serial ports, printer port, and mouse ports can be consolidated into USB, simplifying cabling

requirements. The cPB-4612 provides one USB port at its faceplate (connector J20 is Port 0). USB Port 1

and USB port 2 are routed to the cPB-4612’s J5 Rear Panel I/O connector.

The cPB-4612’s USB channels are controlled by the Intel 6300ESB device. The "Intel 855GME Chipset"

topic in Appendix D provides a link to the datasheet for this device.

1.3.21 System Environmental Monitor

This board provides an IMPI controller for monitoring the status of the system environment. The IPMI

controller monitors the system voltages, ambient board temperature, and CPU temperature. The controller

is accessed through an IPMB bus from the backplane.

See "System Monitoring and Control" in chapter 5 for more details.

1.3.22 LED Indicators

The LEDs located at the cPB-4612’s faceplate are defined below.

• Ethernet (ENETA, RJ 45 connector):

First LED:

Green = Network connection

Blinking Green = Network activity

Second LED:

Off = 10 MB/sec

Green = 100 MB

• Hot Swap

Blue = safe to extract board

Off = not safe to extract board

1.4 Software

The cPB-4612 includes a DTI enhanced AMI Embedded BIOS loaded in on-board flash. The BIOS is userconfigurable and can boot an operating system from CompactFlash, a hard drive, CD-ROM drive, or over a

network. BIOS and firmware updates can be provided by DTI.

The cPB-4612 is compatible with all major PC operating systems, including Microsoft* Windows* 2000/XP,

Linux*, and VxWorks*. Chips may provide additional drivers for Intel peripherals, flash drives, and for

supported operating systems. Software device drivers for the cPB-4612 may be found on the DTI Product

Documentation and Software CD.

10

Page 21

Chapter

2 Getting Started

This chapter summarizes the information needed to make the cPB-4612 operational. This chapter should be

read before using the board.

2

2

11

Page 22

2.1 Unpacking

Check the shipping carton for damage. If the shipping carton and contents are damaged, notify the carrier

and DTI for an insurance settlement. Retain the shipping carton and packing material for inspection by

the carrier. Obtain authorization before returning any product to DTI. Refer to the Return Shipment

Information page for assistance.

CAUTION: This board must be protected from static discharge and physical shock. Never

remove any of the socketed parts except at a static-free workstation. Use the anti-static bag

shipped with the product to handle the board. Wear a wrist strap grounded through one of

the system's ESD Ground jacks when servicing system components.

2.2 System Requirements

The following topics briefly describe the basic system requirements and configurable features of the cPB-

4612. Links are provided to other chapters and appendices containing more detailed information.

2.2.1 BIOS Version

For proper operation, the cPB-4612 must run the DTI enhanced AMI Embedded BIOS. The revision level

is shown in the BIOS Identification string displayed during the Power On Self Test (POST).

2.2.2 Connectivity

The cPB-4612 features an ejector handle that is keyed for compatible slots. The board can only be

inserted into slots fitted with a compatible mating key.

The cPB-4612 is designed to operate in a backplane providing CompactPCI form factor interfaces at J1,

J2, J3, and J5. The J1 and J2 connectors are supplied for the CompactPCI bus, power and IPMI signals.

J3 signaling must comply with the PICMG* 2.16 Packet Switching Backplane specification. The J5

interface must have through-pins for the cPB-4612 to interface with a rear panel transition card such as

the cRT-4612. See the "Connectors" topic in Appendix B for connector descriptions.

2.2.3 Electrical and Environmental

The cPB-4612 meets the following requirements:

• +5VDC +5%, -3% @ 6.9A typical

• +3.3VDC +5%, -3% @ 2.4A typical

• +12VDC ±10% @ 20mA typical

• -12VDC may be required by a PMC peripheral installed on the cPB-4612.

12

Page 23

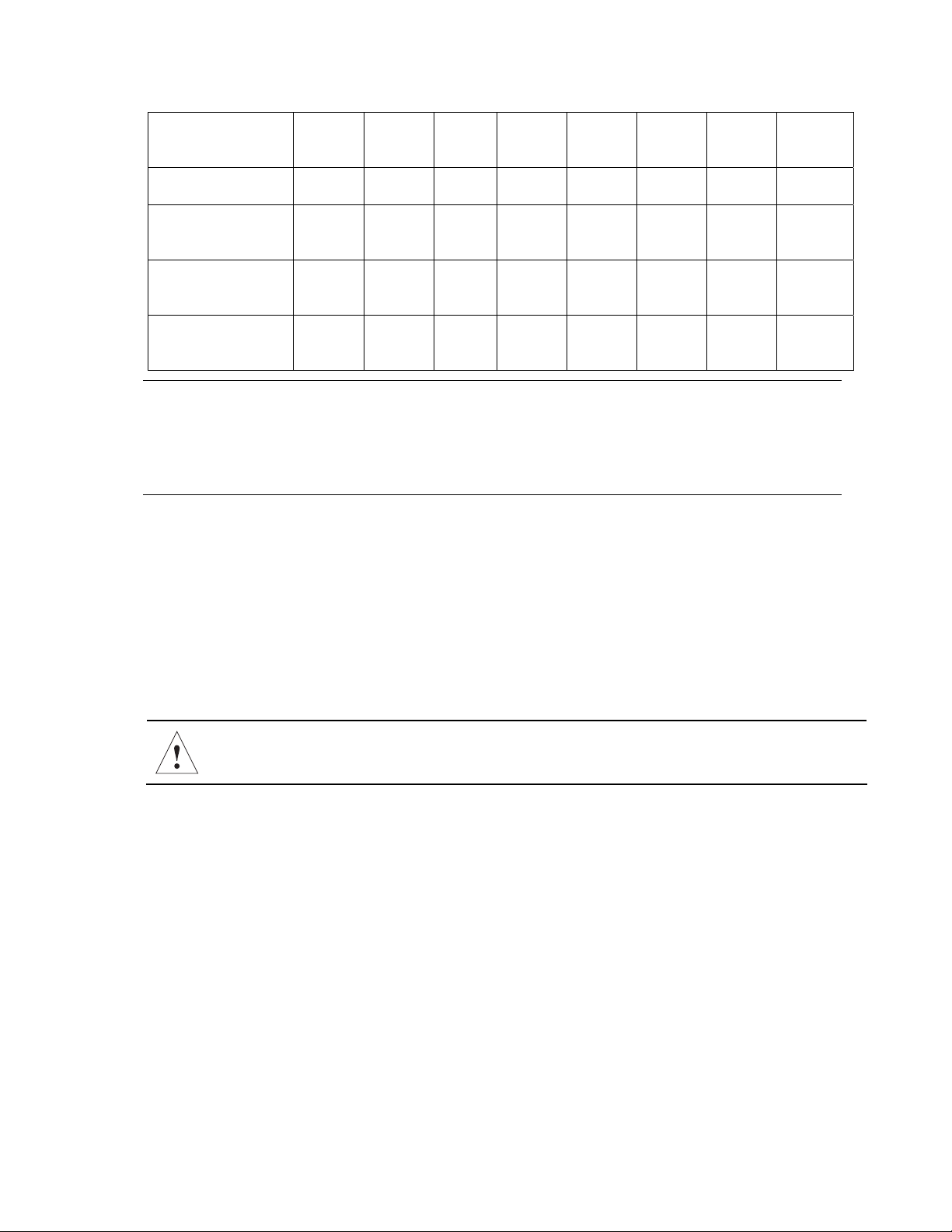

Configuration 5V

(avg)

5V

(peak)

3.3V

(avg)

3.3V

(peak)

12V

(avg)

12V

(peak)

-12V

(avg)

-12V

(peak)

1.7GHz / 512MB 6.9A TBD* 2.4A TBD* 20mA 50mA 0.0A 0.0A

Hard disk (add)

540mA 1.00A N/A N/A N/A N/A N/A N/A

(typical)

PMC card typical1

1.00A 1.70A 0.75A 1.30A 100mA 200mA 20mA 40mA

(add)

PMC card max.

2

1.50A 3.00A 2.25A 4.50A 500mA 500mA 500mA 500mA

(add)

* Peak (short duration) power supply current may be significantly higher (up to 50%) and will

vary depending upon the application.

Notes:

1. Consult manufacturer of installed PMC card for actual values.

2. In no case shall the total power dissipated by the PMC card exceed 10.0 W.

The cPB-4612 comes with a heatsink that allows the processor to operate between 0° and approximately

50°C ambient with a minimum of 200 LFM (1 meter per second) of external airflow. It is the users'

responsibility to ensure that the cPB-4612 is installed in a chassis capable of supplying adequate airflow.

The maximum power dissipation of the processor (FCBGA package) is 25W. External airflow must be

provided at all times. See Appendix A, "Specifications," and Appendix C, "Thermal Considerations," for

more details.

It is strongly recommended that the airflow be measured while the cPB-4612 is installed in its intended

location. Insert a thermistor type air velocity meter (Kane-May KM4007 or similar) through the PMC

access on the faceplate and make the air velocity measurement near the processor heat sink. Power

should not be applied to the cPB-4612 during airflow measurements (slightly disengage the cPB-4612

from the backplane connectors if necessary).

CAUTION: The processor "core" temperature must never exceed 100°C under any condition

of ambient temperature or usage. This may result in permanent damage to the processor.

The cPB-4612 may contain materials that require regulation upon disposal. Please dispose of this product

in accordance with local rules and regulations. For disposal or recycling information, please contact your

local authorities or the Electronic Industries Alliance at http://www.eiae.org/**.

2.3 Memory Configuration

The cPB-4612 components can address up to 4 GB of memory, but the board only has two SO-DIMM

sockets and can physically only hold two sticks of memory. The address space is divided between

memory local to the board and memory located on the Local PCI bus. Any memory not reserved or

occupied by a local memory device (DRAM/flash) is available to PCI memory devices.

The cPB-4612 can support up to two sticks of either 256 MB, 512 MB, 1 GB DDR SDRAM. 1MB of

L2 cache is integrated with the Pentium

®

–M processor.

13

Page 24

Memory Address Map Example

FFF80000h - FFFFFFFFh SYSTEM BIOS/Flash

8000000h - FFF7FFFFh PCI PERIPHERALS

4 GB

4 GB - 512 KB

100000h - 1FFFFFFFh SYSTEM MEMORY

E0000h - FFFFFh SYSTEM BIOS

C8000h - DFFFFh BIOS EXTENSION

C0000h - C7FFFh

A0000h - BFFFFh

0h - 9FFFFh LOCAL DRAM

VGA BIOS

VGA DISPLAY

MEMORY

512 MB

1 MB

896 KB

800 KB

768 KB

640 KB

0

14

Page 25

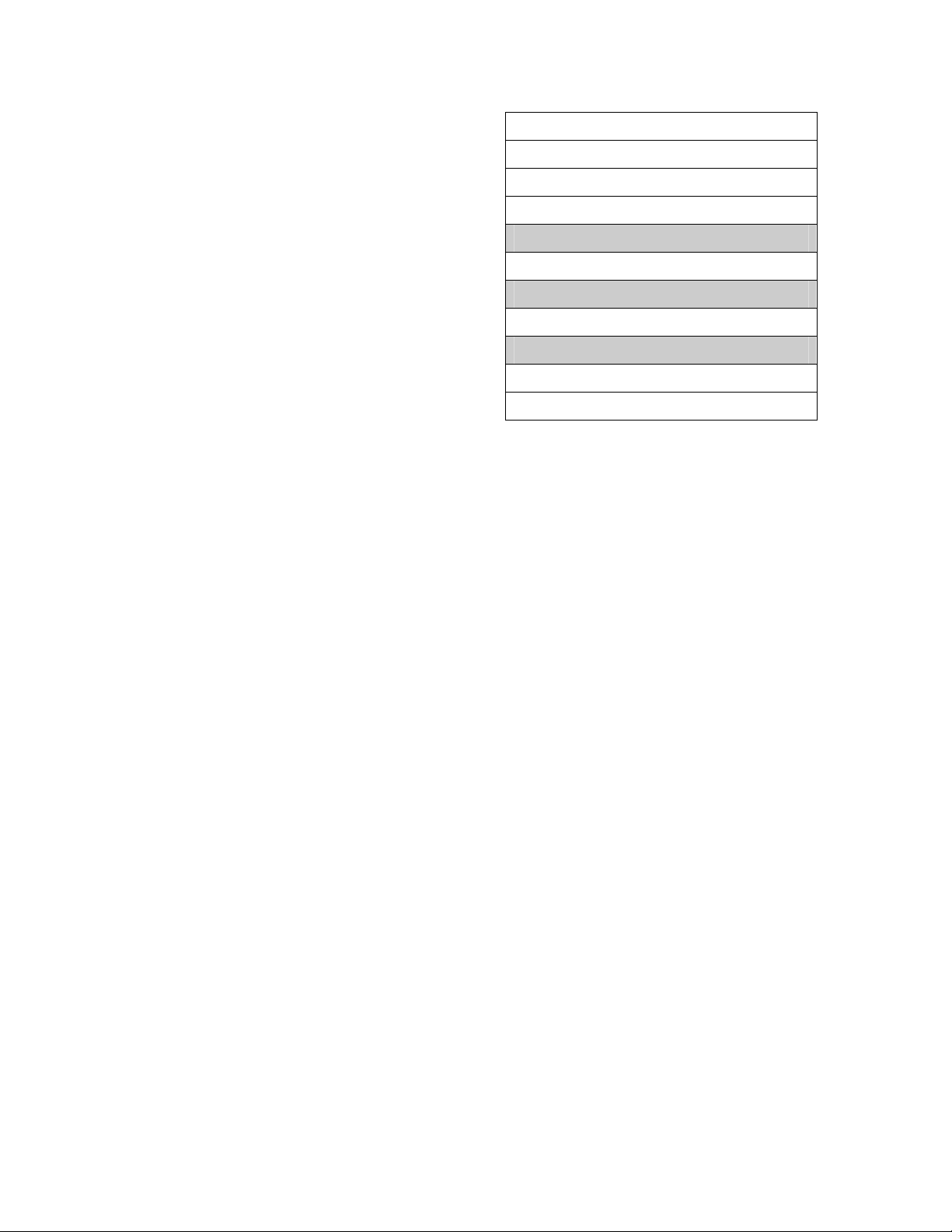

2.4 I/O Configuration

The cPB-4612 addresses up to 64 KB of I/O using a 16-bit I/O address. The cPB-4612 is populated with

many commonly used I/O peripheral devices. The I/O address location for each peripheral is shown in the

"I/O Address Map" illustration.

I/O Address Map

D00 - FFFFh PCI*

*Onboard ISA peripherals

addressed between

100h - 7FFh decode 11 bits

of address (A0h - A10h).

Therefore, these peripherals

will alias throughout the 16-bit

I/O space at the following

ranges:

x100-x3FFh

x500-x7FFh

x900-xBFFh

xD00-xFFFh

PCI devices can fully utilize

the address space from

D00 - FFFFh, since subtractive

decoding is used for the

onboard ISA devices.

CF8 - CFFh PCI Config/RST Control

780 - CF7h PCI Reserved

778 - 77Fh LPT ECP Registers

400 - 777h

3F8 - 3FFh COM1

3F0 - 3F7h Floppy / IDE Registers

3E0 - 3EFh

3B0 - 3DFh VGA Registers

380 - 3AFh

378 - 37Fh LPT

300 - 377h

2F8 - 2FFh COM2

200 - 2F7h

1F8 - 1FFh

1F0 - 1F7h Primary IDE Registers

178 - 1DFh

170 - 177h Secondary IDE Registers

100 - 16Fh

F0 - FFh Coprocessor

E0 - EFh

C0 - DFh On-board Slave DMA Controller

B4 - BFh

B2 - B3h APM Registers

B0 - B1h

A0 - AFh On-board Slave Interrupt Controller

93 - 9Fh

92h Fast RESET and Gate A20

90 - 91h

81 - 8Fh On-board DMA Page Registers

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

15

Page 26

0 - 1Fh On-board Master DMA Controller

80h Diagnostic Port

78 - 79h Reserved

70 - 77h On-board Real-Time Clock

60 - 6Fh Keyboard and System Ports

50 - 5Fh

40 - 4Fh On-board Timer/Counters

30 - 3Fh

2E - 2Fh Super I/O Configuration

22 - 2Dh

20 - 21h On-board master Interrupt Controller

Reserved

Reserved

Reserved

2.5 Connectors

The cPB-4612 includes several connectors to interface to application-specific devices. Refer to the

"Connectors" topic in Appendix B for complete connector descriptions and pin outs.

2.6 Jumper Options

The cPB-4612 provides several jumper configuration options for features that cannot be provided through

the BIOS Setup Utility. Location figures and descriptions are provided in Chapter 3, "Configuration."

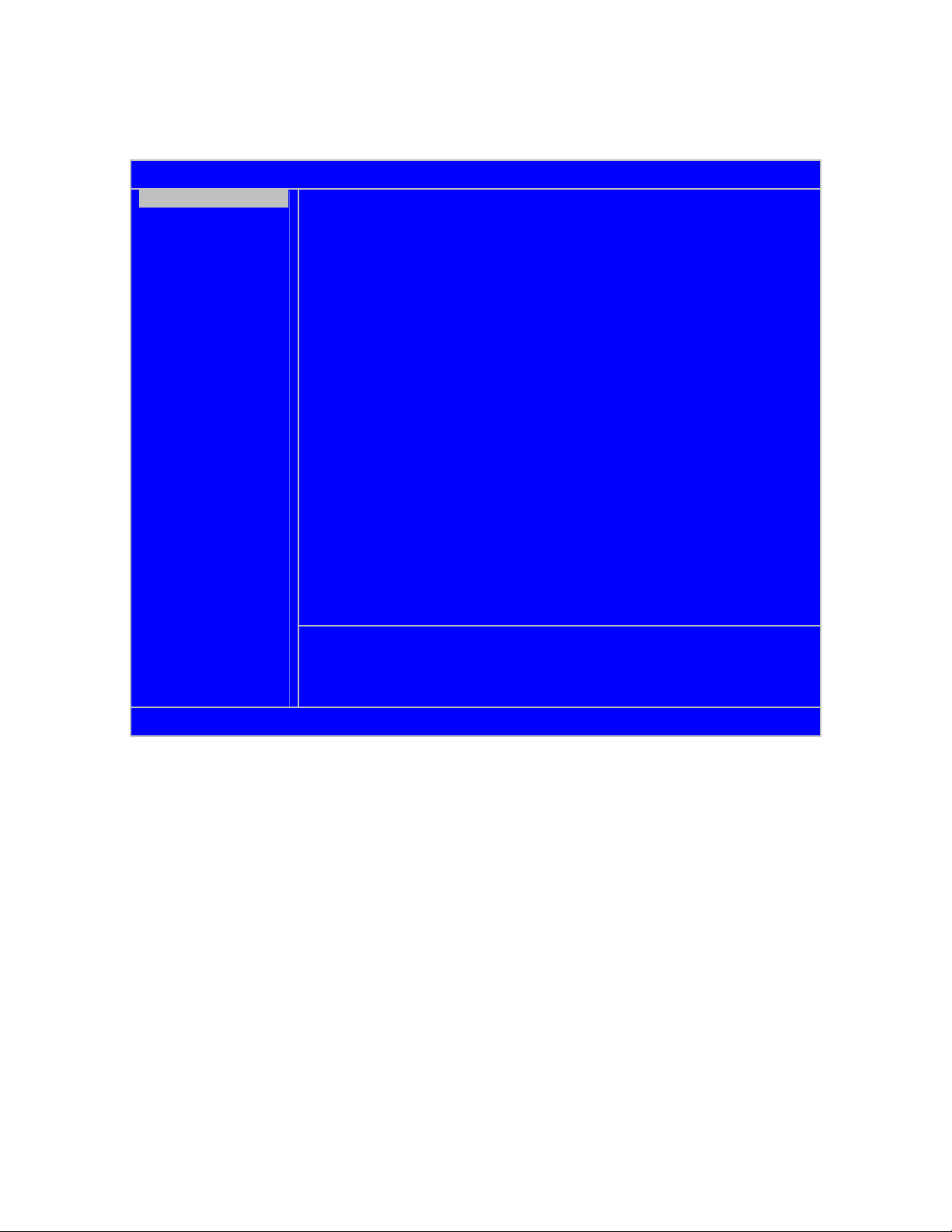

2.7 BIOS Configuration Overview

This topic presents an introduction to the cPB-4612’s BIOS.

The BIOS has many separately configurable features. These features are selected by running the built-in

Setup utility. System configuration settings are saved in a portion of battery-backed RAM in the real-time

clock device and are used by the BIOS to initialize the system at boot-up or reset. The configuration is

protected by a checksum word for system integrity.

To access the Setup utility, press F2 during the system RAM check at boot-up. When Setup runs, an

interactive configuration screen displays. Refer to the following "Setup Screen" illustration for an example.

Setup parameters are divided into different categories. The available categories are listed in a menu

down the left side of the setup screen. The parameters within the highlighted (current) category are listed

in the main (right) portion of the Setup screen. Context sensitive help can be displayed for each

parameter by highlighting the parameter and pressing F1. A legend of keys is listed at the bottom of the

Setup screen.

Use the up and down arrow keys to select a category from the menu. Use the up and down arrow keys to

select a parameter in the main portion of the screen. Use the +/– or ↔keys to change the value of a

parameter.

Solid arrows next to menu items in the main screen indicate submenus. To display a submenu, use the

up and down arrow keys to highlight the submenu and then press Enter.

16

Page 27

Setup Screen

SYSTEM CONFIGURATION SUMMARY

SYSTEM SUMMARY

SYSTEM SETUP

HARD DISK SETUP

BOOT ORDER

PERIPHERALS

USB CONFIG

MISC. CONFIG

EVENT LOGGING

SECURITY/VIRUS

Diversified Technology, Inc – cPB4612

CPU Type :Intel(R) Pentium(R) M processor 1700MHz

CPU Speed : 1.70GHz Hard Disk 0: Not Detected

L2Cache : 1024KB Hard Disk 1: Not Detected

Base RAM : 639K Hard Disk 2: Not Detected

Extended RAM: 480MB Hard Disk 3: Not Detected

Video RAM : 32MB COM Ports : 3F8 2F8 3E8

PCB Revision: 1.0 BIOS Date : 03/31/04

Memory Mode : PC2100 (266MHz) DDR SDRAM with ECC

PMC Slot 1 : PCI-X 66 MHz

PMC Slot 2 : PCI 33 MHz

USB Devices : 1 Keyboard, 1 Mouse, 1 Hub, 1 Drive

↑↓ Select Screen Enter Go to Sub Screen

F1 General Help Esc Exit

EXIT

Copyright (c) 2004, Diversified Technology, Incorporated

2.8 Operating System Installation

For more detailed information about your operating system, refer to the documentation provided by the

operating system vendor.

1. Install peripheral devices. CompactPCI* devices are automatically configured by the BIOS during

the boot sequence.

2. Most operating systems require initial installation on a hard drive from a floppy or CD-ROM drive.

These devices should be configured, installed, and tested with the supplied drivers before

attempting to load the new operating system.

3. Read the release notes and installation documentation provided by the operating system vendor.

Be sure to read any README files or documents provided on the distribution disks, as these

typically note documentation discrepancies or compatibility problems.

4. Select the appropriate boot device order in the SETUP boot menu depending on the OS

installation media used. For example, if the OS includes a bootable installation floppy, select

Removable Media as the first boot device and reboot the system with the installation floppy

installed in the floppy drive. (Note that if the installation requires a non-bootable CD-ROM, it is

necessary to boot an OS with the proper CD-ROM drivers in order to access the CD-ROM drive).

17

Page 28

5. Proceed with the OS installation as directed, being sure to select appropriate device types if

prompted. Refer to the appropriate hardware manuals for specific device types and compatibility

modes of DTI products.

6. When installation is complete, reboot the system and set the boot device order in the SETUP

boot menu appropriately.

18

Page 29

Chapter

3 Configuration

The cPB-4612 has been designed for maximum flexibility. Many features can be configured by the user

for specific applications. Most configuration options are selected through the BIOS Setup utility

(discussed in the "BIOS Configuration Overview" topic in Chapter 2). Some options cannot be software

controlled and are configured with jumpers.

3

3

19

Page 30

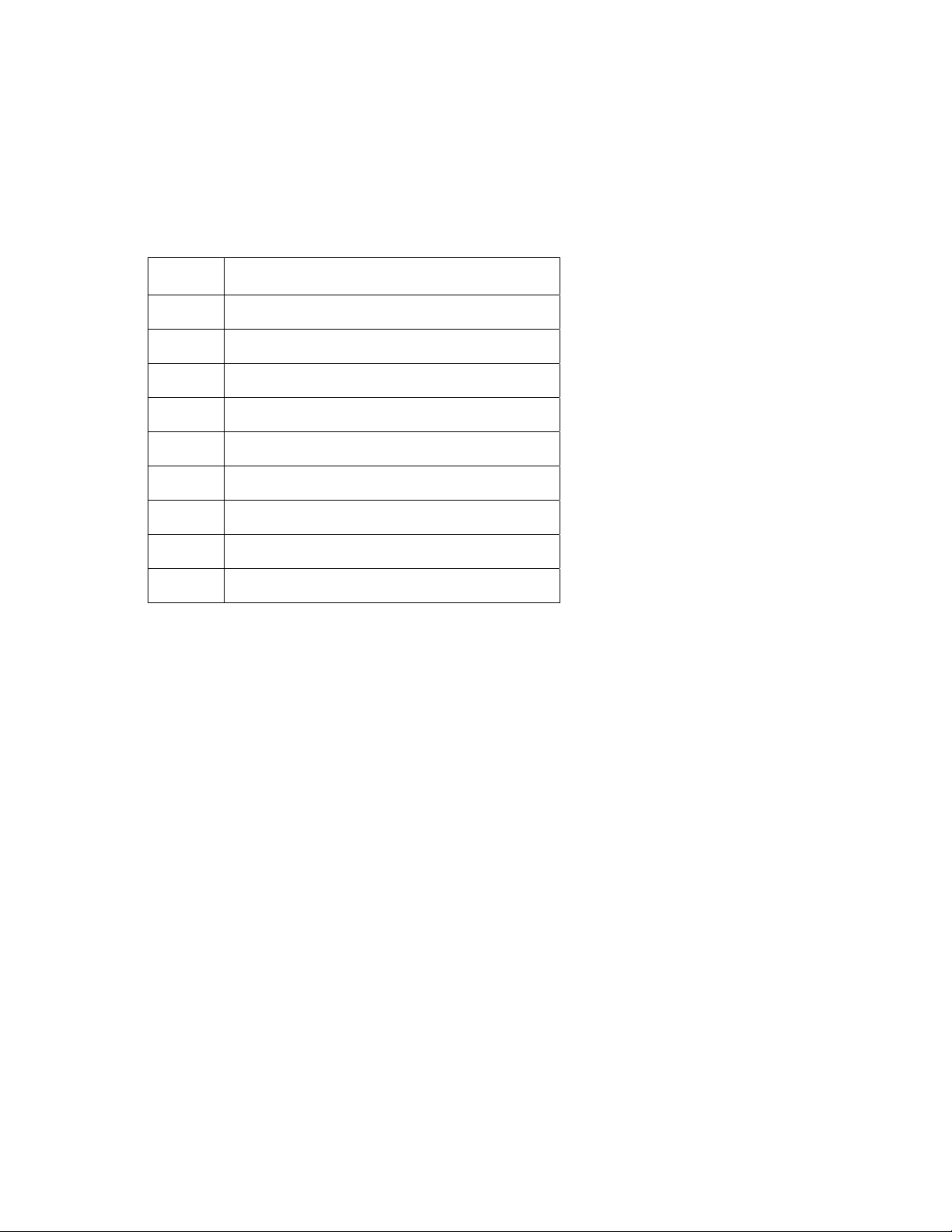

Jumper Options and Locations

The cPB-4612 contains a push-button switch on the faceplate and eight jumpers on the component side

of the board. The jumpers are listed and briefly described in the "Jumper Cross-Reference" table below.

Factory default switch settings are shown in the "Default Jumper Settings" figure.

Jumper Cross-Reference Table

Jumper Function

PB1 Reset (push-button on faceplate)

J16-1 BKT-GND to GND

J16-2 +12V to J5-pin D1

J16-3 +5V PMC I/O

J16-4 IMPI Disable

J17-1 Not Used

J17-2 CMOS Clear

J17-3 Disable Onboard Video

J17-4 Manufacture Test Mode

20

Page 31

Default Jumper Configuration

3.1 Switch Descriptions

The following topics list the switches in numerical order and provide a detailed description of each switch.

3.1.1 PB1 (Reset)

PB1 is a push-button on the front of the cPB-4612. Pressing PB1 issues a hard reset. Reset is discussed

in more detail in Chapter 4.

3.1.2 J16-1 (BKT-GND to GND)

Installing this jumper will short the bracket ground to digital ground. This may positively or negatively

affect EMI emissions, depending on the system. Proper testing would need to be performed with the

intended system to determine the best setting. The default is for no jumper.

J16-1 Function

Open Default Bracket ground is not connected to digital ground.

Closed Bracket ground is shorted to digital ground.

21

Page 32

3.1.3 J16-2 (+12V to J5-pin D1).

Installing this jumper will connect +12V to the CompactPCI connector J5, pin D1. This is only to be used

for specially designed RTM cards that may need it. The default is for no jumper.

J16-2 Function

Open Default CPCI J5-pin D1 is a no connect.

Closed CPCI J5-pin D1 is shorted to +12V.

3.1.4 J16-3 (+5V PMC I/O)

Installing this jumper sets the 32bit/33Mhz PMC site’s VI/O voltage to +5V. Having no jumper sets the

VI/O voltage to 3.3V. The 32bit/33Mhz PMC site is located on the bottom edge of the board, closest to

the jumpers.

WARNING: The voltage key for the 32bit/33Mhz PMC site must be set to match this jumper setting.

Not placing the voltage key, placing the voltage key at the wrong location, or using a PMC card that is not

tolerant of the set voltage may damage the PMC card and/or the cPB-4612 board.

J16-3 CMOS Real Time Clock

Open Default 32bit/33Mhz PMC site set to 3.3V.

Closed 32/bit/33Mhz PMC site set to 5V.

3.1.5 J16-4 (IMPI Disable)

This is for debug use only. Placing this jumper will disable the IMPI controller. This should only be used

by the manufacturer.

J16-4 CMOS Real Time Clock

Open Default Normal Operation

Closed IMPI controller disabled

3.1.6

Not used

J17-1 (Not Used)

J17-1 Function

Open Default Not used

Closed Not used

3.1.7 J17-2 (CMOS Clear)

Installing this jumper will reset the CMOS settings to their default values.

J17-2 Function

Open Default Normal operation

Closed Clears CMOS and sets registers to their default state.

22

Page 33

3.1.8 J17-3 (Disable Onboard Video)

Installing this jumper will disable the onboard video. Place this jumper if using a PCI video card only.

J17-3 Function

Open Default Onboard video is enabled.

Closed The onboard video is disabled.

3.1.9 J17-4 (Manufacture Test Mode)

Used by DTI for testing purposes. Do not install a jumper at this location.

J17-4 Function

Open Default Normal operation

Closed Board in manufacturing test mode.

3.1.10 J18 (Ejector Switch)

The ejector handles are used when cPB-4612 is inserted or removed (hot swapped) from a chassis that is

powered on. When a customer wishes to remove a board from a system that is powered on then the

ejector handles should be opened just enough to disengage the handles from the chassis, but without

fully disengaging the J-connectors from the back of the chassis. This will trigger a shutdown of the

operating system and then the BMC will power off the board and light the blue hot swap LED on the front

panel. Once the blue LED on the front of the board is lit, then it is safe to remove the board from the

chassis.

Note: In order for the shutdown sequence of the OS to take place a hot swap driver must be

installed into the OS. See the cPB-4612 support page for this driver or procure the cPB-4612

hot swap kit.

The J18 (ejector handles) need to be closed in order for the board to boot up.

J18 Function

Open Indicate the user needs to extract the board

Closed Normal Operation

23

Page 34

Chapter

4 Reset

This chapter discusses the reset types and reset sources on the cPB-4612. If necessary, the cPB-4612’s

board reset characteristics can be tailored to the requirements of a specific system.

4

4

24

Page 35

4.1 Reset Types and Sources

The cPB-4612’s reset types are listed below. The sources for each reset type are detailed in the following

topics.

• Hard Reset: All devices are held in reset.

• Soft Reset: CPU initialization only. Other devices are not reset.

• Backend Power Down: The backend logic is powered off. The board is powered on and is held in

reset.

• NMI: Non-maskable interrupt. Though not a reset in the strict sense, an NMI can have the same

effect as other resets.

4.1.1 Hard Reset Sources

System Register CF9h (6300ESB Reset Control Register)

Bits 1 and 2 in this register are used by the 6300ESB to generate a hard reset or a soft reset. During a

hard reset, the 6300ESB asserts CPURST, PCIRST#, and RSTDRV. Additionally, it resets its core and

suspends well logic.

4.1.2 Soft Reset Sources

System Register CF9h (6300ESB Reset Control Register)

Bits 1 and 2 in this register are used by the 6300ESB to generate a hard reset or a soft reset. During a

soft reset, the ICH4 asserts INIT to the CPU for 16 PCICLK. This causes the processor to enter "real

mode", initialize its internal registers, and begin instruction execution from FFFFFFF0h (the boot vector).

Keyboard Controller Reset

The keyboard controller generates a keyboard controller reset when FEh is written to port 64h. This

causes the 6300ESB to assert INIT to the CPU.

Keyboard CTRL-ALT-DEL

Simultaneously pressing these keys calls a BIOS function that reboots the system.

Note: This method does not work under operating systems that trap calls to this BIOS

function.

Watchdog Timer (System Register Address 79h)

The watchdog timer may be programmed to generate a "CPU Init" if it is not strobed within a given timeout period. This function is discussed in Chapter 7, "Watchdog Timer."

4.1.3 Backend Power Down Sources

Board Extraction

When a board is extracted from an enclosure (specifically, when the "board-select" [BD_SEL] pin is

disengaged), the hot swap controller unconditionally removes backend power from the board and holds

the board in reset.

Low Voltage

When any of the 3.3V, 5V, or 12V supply voltages are detected to be below an acceptable operating limit,

the hot swap controller unconditionally removes backend power and holds the board in reset.

25

Page 36

4.1.4 NMI Sources

Watchdog Timer (System Register Address 79h)

The watchdog timer may be programmed to generate a non-maskable interrupt if it is not strobed within a

given time-out period. This function is discussed in Chapter 7, "Watchdog Timer."

26

Page 37

Chapter

5 System Monitoring and Control

The cPB4612 has an IPMI System Monitor that complies with PICMG® 2.9 specification, and complies

with IPMI Specification 1.5. This allows a PICMG 2.9 compliant chassis that utilizes a chassis manager,

or Baseboard Management Controller (BMC) to detect the presence of the cPB4612 and make Field

Replaceable Unit (FRU) information, and Sensor Device Records (SDR’s) available. Sensors monitor

voltages, CPU and system temperature, and other inputs, including the front latch, which can generate

events that are recorded in the BMC’s System Event Log (SEL). The IPMI System Monitor has both an

IPMB and a dedicated basic serial interface, so that it is possible for the cPB4612 to acquire FRU and

sensor information directly from the IPMI System Monitor. The firmware on the IPMI System Monitor can

be upgraded via the serial interface or over IPMB.

5

5

27

Page 38

5.1 Monitoring and Control Functions

The IPMI System Monitor has a dedicated serial interface to the host processor on the cPB4612. It is a

16550-compatible UART that is configurable in SETUP. If this interface is not required, it can be

disabled. Otherwise, it will be given a unique serial port address and interrupt. Note that the interrupt

cannot coincide with the other COM ports; it is not shareable.

The serial interface is fixed at 9600 baud, 8 data bits, 1 stop bit, no parity, full duplex. It complies with

IPMI serial “basic” mode, as detailed in IPMI Spec 1.5, section 13.4, which permits IPMB packets to be

transmitted and received using framing bytes and escape sequences. The packet structure otherwise is

identical to the IPMB:

Figure 5.1: Packet Structure

Because the serial interface in this case is dedicated, the responder address and requester address bytes

can be anything. The IPMI System Monitor, though, will always put its actual IPMB slave address in the

rsAddr field of a response packet.

The IPMI 1.5 specification defines a basic mode serial port as a single session interface, since there is no

session ID in the packet. This IPMI System Monitor, at this time, does not support Get Session Challenge

and Activate Session commands, because the serial interface is dedicated to the IPMI system monitor,

and the interface is always “up.”

5.2 IPMB

The IPMB is an I2C® interface that is routed through the backplane and connects to the BMC in the

chassis to allow discovery of the IPMI System Monitor. Its operation is covered in the IPMI specification.

It is always active.

28

Page 39

5.3 Field Replaceable Unit (FRU) Information

Board information, such as serial number, date of manufacture, OEM name, part number, etc., are

retrievable from the FRU. It complies with the IPMI FRU 1.0 Specification. The information in the FRU

can be customized to add other product information, such as asset tag, other part numbers, etc.

5.4 Sensors

The sensors that the cPB4612 supports with the IPMI System Monitor can be retrieved in the Sensor

Data Records (SDR’s) via normal IPMI commands. They include:

System Ambient Temperature +12V

CPU Temperature +1.5V

VTT DDR +1.8V

CPU Core Voltage ONCTL#

+3.3V SLOT

+5V Front Latch

These sensors (with the exception of ONCTL and SLOT), when enabled by the BMC, will generate

sensor events on the IPMB. These events will normally be logged by the BMC and time-date stamped.

On temperature and voltage sensors, if sensor readings cross any of the non-critical, critical, or nonrecoverable thresholds, the IPMI System Monitor will generate IPMB event data to inform the BMC. The

IPMI System Monitor allows the BMC, via IPMI commands, to override its sensor thresholds

5.5 Firmware Updates

Firmware updates are possible through either the serial or IPMB interface. A special utility will be