Page 1

Intel® 31244 PCI-X to Serial ATA

Controller

Design Guide

April 2004

Order Number: 273651-003

Page 2

Intel® 31244 PCI-X to Serial ATA Controller

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTELR PRODUCTS. EXCEPT AS PROVIDED IN INTEL’S TERMS

AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS

OR IMPLIED WARRANTY RELATING TO SALE AND/OR USE OF INTEL PRODUCTS, INCLUDING LIABILITY OR WARRANTIES RELATING TO

FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT, OR OTHER

INTELLECTUAL PROPERTY RIGHT.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the

presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by

estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for

future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

®

The Intel

published specifications. Current characterized errata are available on request.

This Design Guide as well as the software described in it is furnished under license and may only be used or copied in accordance with the terms of

the license. The information in this manual is furnished for informational use only, is subject to change without notice, and should not be construed as

a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this

document or any software that may be provided in association with this document.

Except as permitted by such license, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any

means without the express written consent of Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486,

i960, iCOMP, InstantIP, Intel, Intel Centrino, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade,

Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel

SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XScale, IPLink, Itanium, MCS, MMX, MMX logo, Optimizer logo, OverDrive,

Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, SmartDie,

Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, VoiceBrick, VTune, and Xircom are

trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2004, Intel Corporation

31244 PCI-X to Serial ATA Controller may contain design defects or errors known as errata which may cause the product to deviate from

2 Design Guide

Page 3

Intel® 31244 PCI-X to Serial ATA Controller

Contents

Contents

1 About This Document .................................... .. ..... .. ..... ....... ..... .. ..... .. ..... ....... ..... .. ..... .. ..... ..... ...........9

1.1 Reference Documentatio n........ ............... .............. ............................ ............................. ......9

1.2 Terminolog y and Def in i tions ...................... ............................ ............... ............................ ....9

2 Overview........................................................................................................................................13

2.1 Features..............................................................................................................................13

2.2 Applications ........................................................................................................................ 15

3Intel

4 Routing Guidelines........................................................................................................................ 25

5Intel

®

31244 PCI-X to Serial ATA Controller Package ..................................................................17

3.1 Signal Pin Descriptions................................................................................................ .......18

3.1.1 VA0, VA1 (V

3.2 Package/Marking Info rmation.............................................................................................22

3.3 Ball Map By Function..........................................................................................................23

4.1 General Rout ing Guidelines.... ............................. ............................ .............. .....................25

4.2 Crosstalk.............................................................................................................................26

4.3 EMI Considerations ....... .............. ............................ ............................. ............................ ..27

4.4 Power Distrib ut ion and Decouplin g....... ............................. ............................ .....................28

4.4.1 Decoupling.............................................................................................................28

4.4.1.1 Intel

4.5 Trace Impedance ................................................................................................................29

4.5.1 Differential Impedance........................................................................ ................. ..29

®

31244 PCI-X to Serial ATA Controller Interface Ports.........................................................31

5.1 Serial ROM Interface .......................................................................................................... 31

5.2 JTAG Interface....................................................................................................................31

5.3 PCI-X Interf a c e....... .............. ............................ ............................. ............................ .........32

5.4 Serial ATA Interface............................................................................................................33

5.4.1 Direct Port Access (DPA).......................................................................................33

5.4.2 Extended Voltage Mode ..................................................................... ...................33

5.4.3 LED Inte r face...... ............................ ............... ............................ ............................34

5.4.4 Reference Clock Generation ................................................ ....... ................. .........35

) Pin Requirements.............................. ............................ .........21

CCPLL

®

31244 PCI-X to Serial ATA Controller Decoupling.......................28

6 Printed Circuit Board (PCB) Methodology.....................................................................................37

6.1 Intel

6.2 Extended Voltage Mode ................................................................................................... ..39

7 PCI-X Layout Guide lines .................................................... ............................. ..............................47

7.1 PCI Voltage Levels .............................................................................................................47

7.2 PCI/X Clocki ng Modes............ .............. ............................. ............................ .....................48

Design Guide 3

®

31244 PCI-X to Serial ATA Controller

Normal Mode (standard SATA driver) ................................................................................ 38

6.1.1 Intel

6.2.1 Backplane Topologies ........................................................................................... 40

6.2.2 Motherboard Stackup for Backplane Designs.......................................... ............ ..42

6.2.3 Backplane Stripline Stackup.................................................................................. 44

6.2.4 Cable Intercon nect With Backpl ane.......................................................................45

®

31244 PCI-X to Serial ATA Controller HBA Stackup...................................39

Page 4

Intel® 31244 PCI-X to Serial ATA Controller

Contents

7.3 PCI General Layout Guidelines.............................................. ............ ....... ....... ............ ......49

7.4 PCI-X Layout Guidelines For Slot Configurations............................................................... 50

7.4.1 Protection Circuitry for Add-in Cards..................................................................... 50

7.4.2 PCI Clock La yo ut Guide lines............................................... ............................ ......51

7.4.3 Connecting Intel

to Single-Slot ......................................................................................................... 52

7.4.4 Embedded Intel

Single PCI-X Load.................................................................................................53

7.4.5 Embedded Intel

®

31244 PCI-X to Serial ATA Controller

®

31244 PCI-X to Serial ATA Controller

®

31244 PCI-X to Serial ATA Controller

Design With Multiple PCI-X Loa ds.........................................................................54

8 Cables and Connectors.................................................................................................................55

8.1 Cabling................................................................................................................................55

8.1.1 Serial ATA Cable....................................... ............................ ............................ ....58

9 Voltage Power Delivery.......................... ............................. .......................................... ................59

®

9.1 Intel

31244 PCI-X to Serial ATA Controller Core

Supply Voltage: Providing 2.5V in 3.3 V System............................................................... 59

10 Test Methodology.... ......................................................................................................................61

10.1 Extended Voltage Mode .. ...................................................................................................63

10.1.1 Extended Voltage Mode Receiver Mode l ..............................................................63

10.1.2 Extended Voltage Mode Driver Model...................................................................64

11 Terminati o n s: Pu ll-down/Pull-ups........... ............... ............................ ............................ ................65

®

12 Intel

IQ31244 PCI-X to Serial ATA Controller Evaluation Platform Board...................................67

12.1 Features..............................................................................................................................68

13 Debug Connectors and Logic Analyzer Connectivity ....................................................................69

13.1 Probing PCI-X Signals........................................................................................................69

14 Design for Manufacturing..............................................................................................................75

15 Thermal Solutions..........................................................................................................................77

15.1 Thermal Recommendations................................................................................................77

16 References....................................................................................................................................79

16.1 Related Documents............................................................................................................79

16.2 Electronic Information.........................................................................................................80

®

A Intel

IQ31244 Controller Evaluation Platform Board Bill of Materials..........................................81

4 Design Guide

Page 5

Intel® 31244 PCI-X to Serial ATA Controller

Contents

Figures

1Intel® 31244 PCI-X to Serial ATA Controller Block Diagram......................................................14

2 Quad Serial ATA Host Bus Adapter............................................................................................15

3 Pa cka g ing Considerations................................... ............................. ............................ ..............17

4 Package Information: 256-pin PBGA . .........................................................................................22

5 PBG A Ma p ped By Pin Fun c ti o n. ............... .............. ............................ ............................. ...........23

6 Exa mples of Stubless a n d Shor t Stu b Trac e s........................ ............................. .......................25

7 Crosstalk Effects on Trace Distance and Height........................................................................26

8 PCB Ground Layout Around Connectors................................................................. .......... ....... ..26

9 C ro ss Se ction of Differential Trace.................................. ............................. ............................ ..29

10 LED and Serial EEPROM Configurations...................................................................................34

11 Intel

12 Intel

13 Write Backplane Topology..........................................................................................................40

14 Read Backplane Topology................................................................................ ....... ............ .......41

15 Microst r i p St ackup .................................................... ............................. .....................................43

16 Stripl i n e St ackup....................................... ............................ .............. ........................................ 44

17 Single-Slot Topology...................................................................................................................52

18 Embedded Intel

19 Embedded PCI-X Design With Multiple Loads ...........................................................................54

20 Serial ATA Direct Connect..........................................................................................................55

21 Serial ATA Connectors Cable to Host Connections ...................................................................56

22 Serial ATA Host Connectors.......................................................................................................57

23 Serial ATA Cable Signal Connections ........................................................................................58

24 Serial ATA Eye Diagram.............................................................................................................62

25 Extended Mode Receiver Example ............................................... .......... .. ....... ....... .......... ....... ..63

26 Extended Mode Driver Example.................................................................................................64

27 Intel

®

31244 PCI-X to Serial ATA Controller Connection Scheme - Normal Mode....................38

®

31244 PCI-X to Serial ATA Controller HBA Stackup........................................................39

®

31244 PCI-X to Serial ATA Controller

Design with Single PCI-X Load...................................................... ..... ....... ..... .. ....... ..... ....... ..... ..53

®

IQ31244 PCI-X to Serial ATA Controller Evaluation Platform Board

Block Diagram ............................................................................................................................67

Design Guide 5

Page 6

Intel® 31244 PCI-X to Serial ATA Controller

Contents

Tables

1 Refer e n ce Documents......................... ............................. ............................ .............. ..................9

2 Ter mi n o log y and Def in ition........... ............... ............................ .............. ............................. ..........9

3 Serial ATA Sig nals Pin Descriptions...........................................................................................18

4 PCI-X Bus Pin Descriptions........................................................................................................ 19

5 Configuration Pin Descriptions...................................................................................................20

6 JTAG Pin Descriptions ...............................................................................................................20

7 Serial ROM Interface Pin Descriptions .......................................................................................21

8 Power Su ppl y Pin Descriptio n s.......................... .............. ............................ ............................. .21

9 Normal Voltage Mode ................................................................................................................. 33

10 Extended Voltage Mode .............................................................................................................33

11 Normal Voltage Mode.................................................................................................................38

12 Motherboard Sta cku p , Microstrip......... ............... ............................ ............................ ................42

13 Motherboard Mi cro s trip Parameters............................................... ............................ ............... .42

14 Backplane Stripline Stackup. ......................................................................................................44

16 Backplane Stackup, Offset Stripline ....................................................................................... ....45

15 Backplane Stackup, Microst rip ................................................................................................... 45

17 Cable Specifi ca tion.......................... ............................ ............................. ..................................45

18 PCI/X Voltage Levels........................................................................ ................. ......... ................47

19 PCI-X Clocking Modes........................ ............................. ............................ ..............................48

20 Add-on Card R outing Parameters..............................................................................................49

21 PCI-X Slot Guidelines................................................ .............. ............................ .......................50

22 Wiring Lengths fo r Single Slot..................... .............. ............................ ............................. ........52

23 Wiring Lengths for Embedded Intel

with Single PCI -X Loa d... ............................. .............. ............................ ............................. ........53

24 Wire Lengths For Multiple PCI-X Load Embedded

25 Serial ATA Signal Definitions......................................................................................................55

26 Interface Timing and SI Requirements . ......................................................................................61

27 Timing Require men t....... ............................. ............................ ............................ .......................62

28 Extended Voltage Mode Receiver ..............................................................................................63

29 Extended Mode Driver......................................................................................... ....... ................64

30 Termination s: Pull-up/Pull-down.................................................................................................65

31 Logic Analyzer Pod 1....................................... ....... ............ ....... ....... .......... ....... ....... ....... ...........69

32 Logic Analyzer Pod 2....................................... ....... ............ ....... ....... .......... ....... ....... ....... ...........70

33 Logic Analyzer Pod 3....................................... ....... ............ ....... ....... .......... ....... ....... ....... ...........71

35 Logic Analyzer Pod 5....................................... ....... ............ ....... ....... .......... ....... ....... ....... ...........72

34 Logic Analyzer Pod 4....................................... ....... ............ ....... ....... .......... ....... ....... ....... ...........72

36 Logic Analyzer Pod 6....................................... ....... ............ ....... ....... .......... ....... ....... ....... ...........73

37 Thermal Resistance ....................................................................................................................77

38 544-Lead H-PBGA Package Thermal Characteristics................................................................77

39 Design References.....................................................................................................................79

40 Intel Related Documentation......................................................................................................79

41 Electronic In formation............ .............. ............... ............................ ............................ ................80

®

31244 PCI-X to Serial ATA Controller Design..................................................................54

Intel

®

31244 PCI-X to Serial ATA Controller

6 Design Guide

Page 7

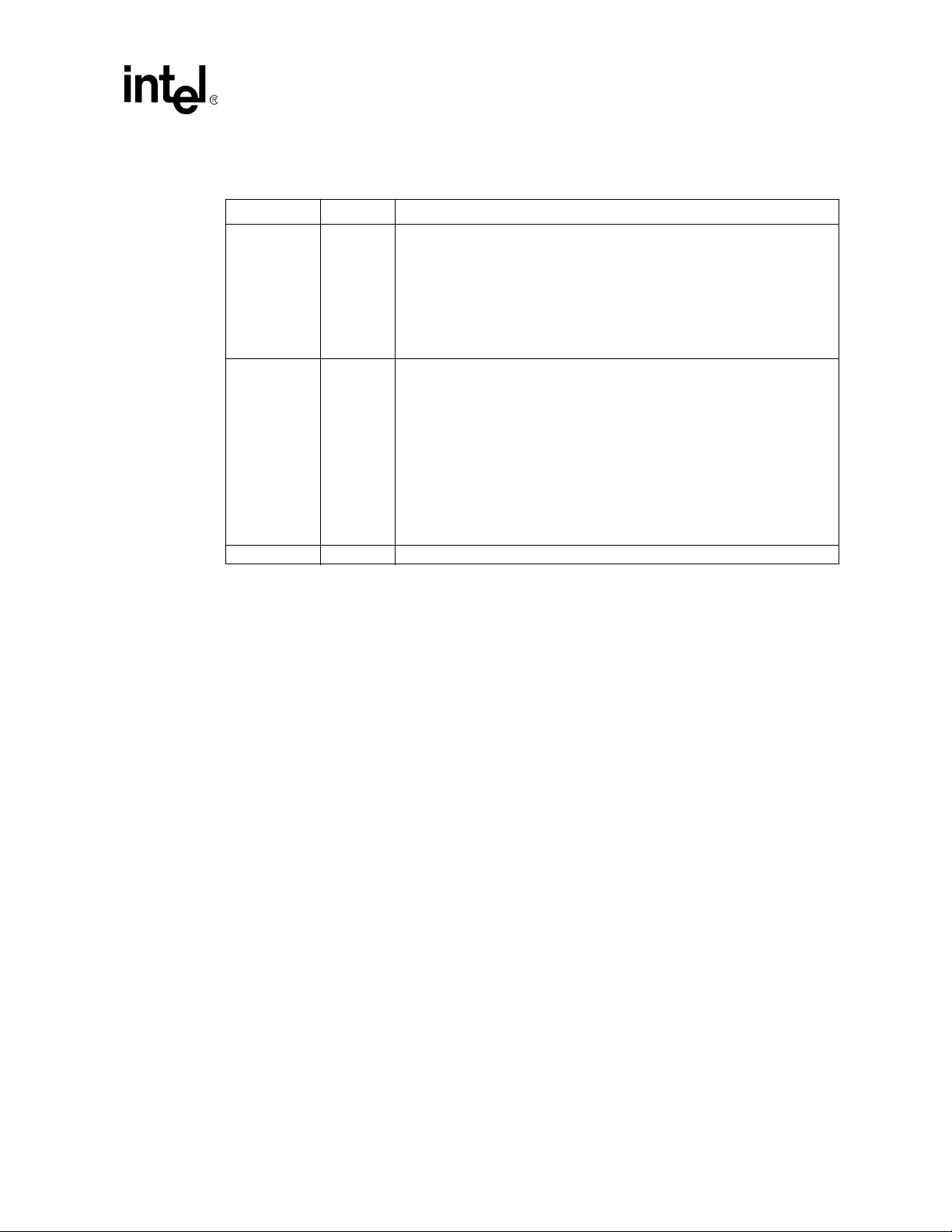

Revision History

Date Revision # Description

April 2004 003 Removed Section 5.4.5, “Spread Spectrum Clocking” on page 35.

December 2002 002 In Section 2.1, added a new table titled “Serial ROM Interface Pin Descriptions”.

October 2002 001 Initial release of this document.

Intel® 31244 PCI-X to Serial ATA Controller

Contents

Removed SSC pin in Table 2, “Terminology and Definition” on page 9.

Updated SSCEN pin in Table 5, “Configurat i on Pi n De scr ipt i on s ” on p ag e 20 and

T able 30, “Terminations: Pull-up/Pull-down” on page 65.

Removed Section 9.1, “Power Delivery for the Intel® 31244 PCI-X to Serial A TA

Controller (TBD)” on page 59.

In Ap pendix A, “Intel

Materials”, replaced Bill of Materials table with a URL to the Intel

In Sectio n 2.1, adde d no te to Table 2, “Ser ial ATA Signal Pi n Des cr i pt io ns”,

indicating that LED2 and LED3 as dual purpose pins.

Replaced Figure 5, “PBGA Mapped by Pin Function” with a rev ised illustration.

Added cont en t to Sect ion 3.4 .1. 1, “In te l GD31 24 4 PC I-X to Se ria l ATA Co nt rol le r

Decoupling”, regarding the use of at le ast twelve 0.1 µF capacitors to decouple

the VCC 2.5 V signal.

Removed Section 3.4.1.2, “PCI-X Decoupling”.

In Table 30, “Terminations: Pullup/Pulldown”, revised row with si gnal name of

TRST# to include TDI#, TMS#, and TCK as 4.7K pull-ups.

In Appendix A, revised the Bill of Materials.

®

IQ31244 Controller Ev aluation Platform Board Bill of

®

website.

Design Guide 7

Page 8

Intel® 31244 PCI-X to Serial ATA Controller

Contents

This page intentionally left blank.

8 Design Guide

Page 9

About This Document 1

1.1 Reference Documentation

For the latest revision and documentation number, con tac t your Intel representative.

Table 1. Reference Documents

Document Intel Document Number or Source

®

Intel

Artisea PCI-X to Serial ATA Controller Developer’s Manual 273603

®

Artisea PCI-X to Serial ATA Controller Datasheet 273595

Intel

®

Packaging Databook 240800

Intel

Printed Circuit Board (PCB)Test Methodology User’s Guide,

Revision 1.6

Termina t in g D iff er e nt ial Signal s on PCBs, by St eve Kaufer and

Kelee Crisafulli. Pr inted Circuit Design Magazine, March 1999

1.2 Terminology and Definitions

http://developer.intel.com/design/chipsets/

applnots/298179.htm

298179

http://www.pcdmag.com

T able 2. Terminology and Definition (Sheet 1 of 3)

Term Definition

Stripline

Microstrip

Prepreg

Core

Material used fo r the lam inatio n pro cess of manufact uri ng PCBs. It co ns is t s of a lay er of

epoxy ma terial that is placed between two cores. This layer melts into epoxy when heated

and forms around adjacent traces.

Material used for the lamination process of manufacturing PCBs. This material is two sided

laminate with copper on each side. The core is an internal layer that is etched.

Stripline in a PCB is composed of the

conductor inserted in a dielectric with GND

planes to the top and bottom.

NOTE: An easy way to distinguish stripline

from microstrip is th at you need to

strip a way laye rs of the boa rd to vi ew

the trace on stripline.

Microstrip in a PCB is composed of the

conductor on the top layer above the

dielectric with a ground plane below

Design Guide 9

Page 10

Intel® 31244 PCI-X to Serial ATA Controller

About This Document

Tab le 2. Term ino logy an d Definition (Sheet 2 of 3)

Term Definition

Layer 1: copper

Prepre g

Layer 2: GND

Core

PCB

Example of a Four-Layer Stack

Layer 3: VCC

Prepreg

Layer 4: copper

JEDEC Provides standards for th e semiconductor industry.

A network that tr ansmits a coup led signal to another network is aggress or network.

Zo

Aggressor

Zo

Victim Network

Aggressor Network

Printe d circuit board.

Example manufacturing process consists of

the following steps:

• Consists of alternat in g lay er s o f cor e and

prepreg stacked

• The finished PCB is heated and cured.

• The via holes are drilled

• Plating cover s holes and outer su rfaces

• Etching removes unwanted copper

• Board is tinned, co ated with solder mask

and silk scre en ed

Zo

Zo

Victim

Network

A networ k t hat rece iv es a co up led cr os s-t a lk si gna l fro m a noth er n etwor k is a c alle d t he vict i m

network

The trace of a PCB that completes an electrical connection between two or more

components.

Stub Branch from a t runk terminat ing at the pad of an agent.

CRB Customer Reference Board

HBA Host Bus Adapte r

TX + / TX -

RX + / RX -

These si gnals are the outbound high-sp eed different ial signals that are connected to the

serial ATA cable.

These signals are the inbound high-speed differential sig nals that are connected to th e serial

ATA cable.

TX This is a transmit port that contains the basic high-spe ed driver electronics.

RX This is a receiver port contains the basic high-speed receiver electronics.

Termination

calibration

PLL

Voltage

Regulator

This bl ock is used to establish the impedance of the RX block in order to properly termi nate

the high-speed serial cable.

This bl ock is used to synchronize an inte rnal clocking reference so that the input high-speed

data stream may be properly decoded.

This bl ock stabilizes the internal voltages used in the other blocks so that reliable operation

may be achieved. This bloc k may or may not be required for proper operation of the balance

of the circuitry . The need for thi s block is impleme ntation specific.

TxData Serially encoded 10b data attached to the high-speed serial differential line driver.

10 Design Guide

Page 11

T able 2. Terminology and Definition (Sheet 3 of 3)

Term Definition

RxData Serially encoded 10b data attached to the high-speed serial differential line receiver.

10b encoding

Jitter Jitter is a high-frequency, semi-random displacement of a signal from its ideal location.

ISI

Differential

Signal

The 8B/10B encoding scheme transmits eight bits as a 10- bit code group. This encoding is

used with Gigabit Ethernet, Fibre Channel and InfiniBand*.

Inter-symbol interference. Data-dependent deterministic jitt er caused by the ti me differences

required for the signal to arrive at the receiver threshold when starting from different places in

bit sequences (symbols).

For example media attenuates the peak amplitude of the bit sequence [0,1,0,1...], more than

it attenuates the peak amplitude of the bit sequence [0,0,0,0,1,1,1,1...], thus the time required

to reach the receiver threshold with the [0,1,0,1...] sequence is less than required from the

[0,0,0,0,1,1,1,1...] sequence.

The run length of 4 produces a higher amplitude which takes more time to overcome when

changing bit values and therefore produces a time difference compared to the run length of

1-bit sequence. When different run lengths are mixed in the same transmission the different

bit sequences (symbols) therefore interfere with each other.

ISI is expected whenev er any bit sequence has frequency components that are pro pagated

at different rates by the transmission media. This translates into high-high-frequency,

data-dependent, jitter.

A signal derived by t aking the dif fe rence between tw o condu ctors. In this spec a di f ferenti al signal

is comprised of a positive conductor and a negative conductor. The differential signal is the

voltage on the positive conductor minus the voltage on the negative conductor (i.e., TX+ – TX-).

Intel® 31244 PCI-X to Serial ATA Controller

About Th i s Do cum ent

Design Guide 11

Page 12

Intel® 31244 PCI-X to Serial ATA Controller

About This Document

This page left intentionally blank.

12 Design Guide

Page 13

Intel® 31244 PCI-X to Serial ATA Controller

Overview

Overview 2

This document provides layout infor ma tion and guidelines for designing platform or add-in board

applications with the Intel

that this docu ment be used as a guideline. Intel recommends employing best-known design

practices with board-level simulation, signal integrity testing and validation for a robust design.

Designers should not e that th is guide focu ses upon spec ific de sign consi derat ions for th e GD31244

and is not intend ed to be an all-inclusive list of all good design practices. It is recommended that

this guide is used as a s tarting point and use empirical data to optimize your particular design.

Note: This pre-silicon analysis information is preliminary and subjec t to change. Sections marked with

TBD are to be updated in future revisions.

2.1 Features

The GD31244 is a state-of-the- art, PCI-X to Serial ATA Controller with four Serial ATA ports

running at 1.5 Gbits/s. The device is targeted at embedded applications suc h as PC mothe r boards,

as well as standalone PCI- X Host Bus Adapter (HBA) cards and RAID controllers.

The GD31244 is both a PCI-X Bus Master and Slave, which automatically switches modes as

required.

As a PCI-X Sla ve, the device supports:

• I/O Reads • Configura tion Read

• I/O Wri tes • Configura tion Write

• Memory Read Bus Cycles

®

31244 PCI-X to serial ATA controller (GD312 44). It is recommended

As a PCI-X Bu s Master, this device supports:

• Single Memory Reads • Lin e M emory Reads

• Multiple Memory Reads • Memory Writes

This device is compliant with a PCI-X bus operating at up to 64 bits at 133 MHz, resulting in burst

data rates of 1064 Mbytes/s. The GD31244 provides four Serial ATA ports running at 1.5 Gbits/s

transfe r r ate, which are compliant to the Serial ATA: High speed Serialized AT Attachment

Specificati on, Revision 1.0e. The GD31244 derives its Serial ATA c locks from an internal PLL,

with a reference clock of 37.5 MHz provided externally or from a crystal.

The GD31244 is fully compatible with parallel ATA operating system drivers and software. The

chip may be configured in compatibility mode, mapping the PCI-X configuration space to match

the x86 standa rd Pri mary a nd Se condary IDE port s. To support both o n-boa rd para lle l IDE, plus the

four Serial ATA ports, the chip may be configured for native PCI-X mode, allowing Plug-and-Play

BIOS and operating systems to map the Serial ATA drives to non-conflicting task file and I/O

address space. For higher performance in systems where compatibility is not required, all four

channels may be configured as Direct P ort Acc ess ( DPA).

Design Guide 13

Page 14

Intel® 31244 PCI-X to Serial ATA Controller

Overview

Feature Highlights:

• Four SATA Channels at 1.5 Gbits/s

• Serial ATA: High speed Serialized AT Att achment Specification, Revision 1.0e Compli ant

• 64-bit/133 MHz PCI-X Bus. Backwards com p atible to 32-bit/33 MHz and 64-bit/66 MHz

• Compatible with existing Operating Sy stems

• Supports native PCI IDE

• Hot-Plug Drives

• Su pports Master/Slav e Mode for Compati bility with existing Operating Systems

• Sup ports SATA Direct Port Access (Master/Master Mode)

• Independent DMA Masters for ea ch SATA Channe l

• 3.3 V and 2.5 V Supply, 2 W maximum

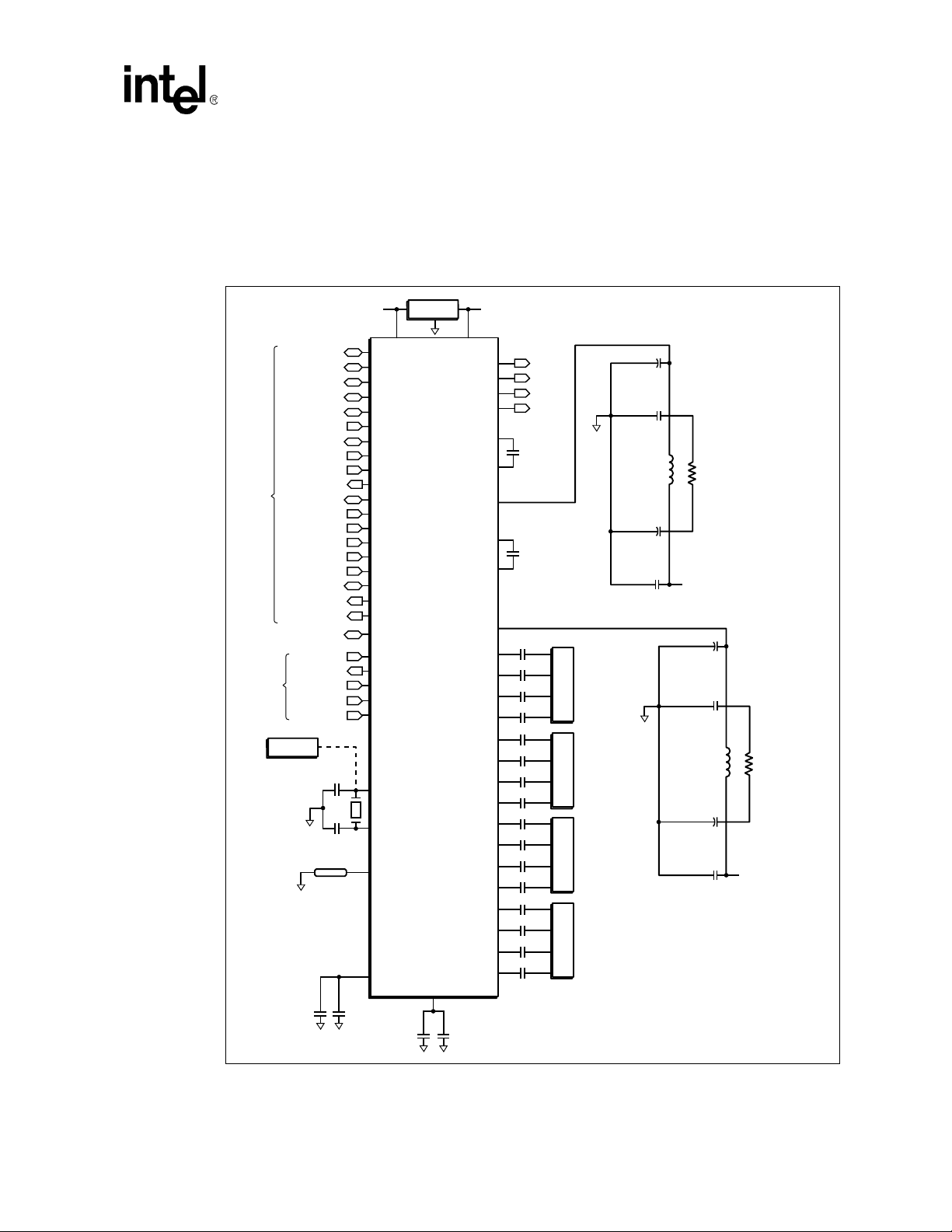

Figure 1. Inte l

®

31244 PCI-X to Serial ATA Controller Block Diagram

LED0

P_AD(63:0)

P_CBE(7:0)

P_PAR

P_PAR64

P_FRAME#

P_TRDY#

P_IRDY#

P_STOP#

P_DEVSEL#

P_REQ#

P_REQ64#

P_ACK64#

P_GNT#

P_CLK

P_RST#

P_PERR#

P_SERR#

P_INTA#

PCI-X

64-bit

133 MHz

Interface

LED1

LED2

LED3

Dual

Port

FIFO

and

Transport

Engine

I/O

Serial ATA

Transport/Link

Layer

Serial ATA

Transport/Link

Layer

Serial ATA

Transport/Link

Layer

Serial ATA

Transport/Link

Layer

PHY

I/F

PHY

I/F

PHY

I/F

PHY

I/F

Serializer

Deserializer

Serializer

Deserializer

Serializer

Deserializer

Serializer

Deserializer

00B

00B

00B

00B

TX0P

TX0N

RX0N

RX0P

TX1P

TX1N

RX1N

RX1P

TX2P

TX2N

RX2N

RX2P

TX3P

TX3N

RX3N

RX3P

A9194-03

14 Design Guide

Page 15

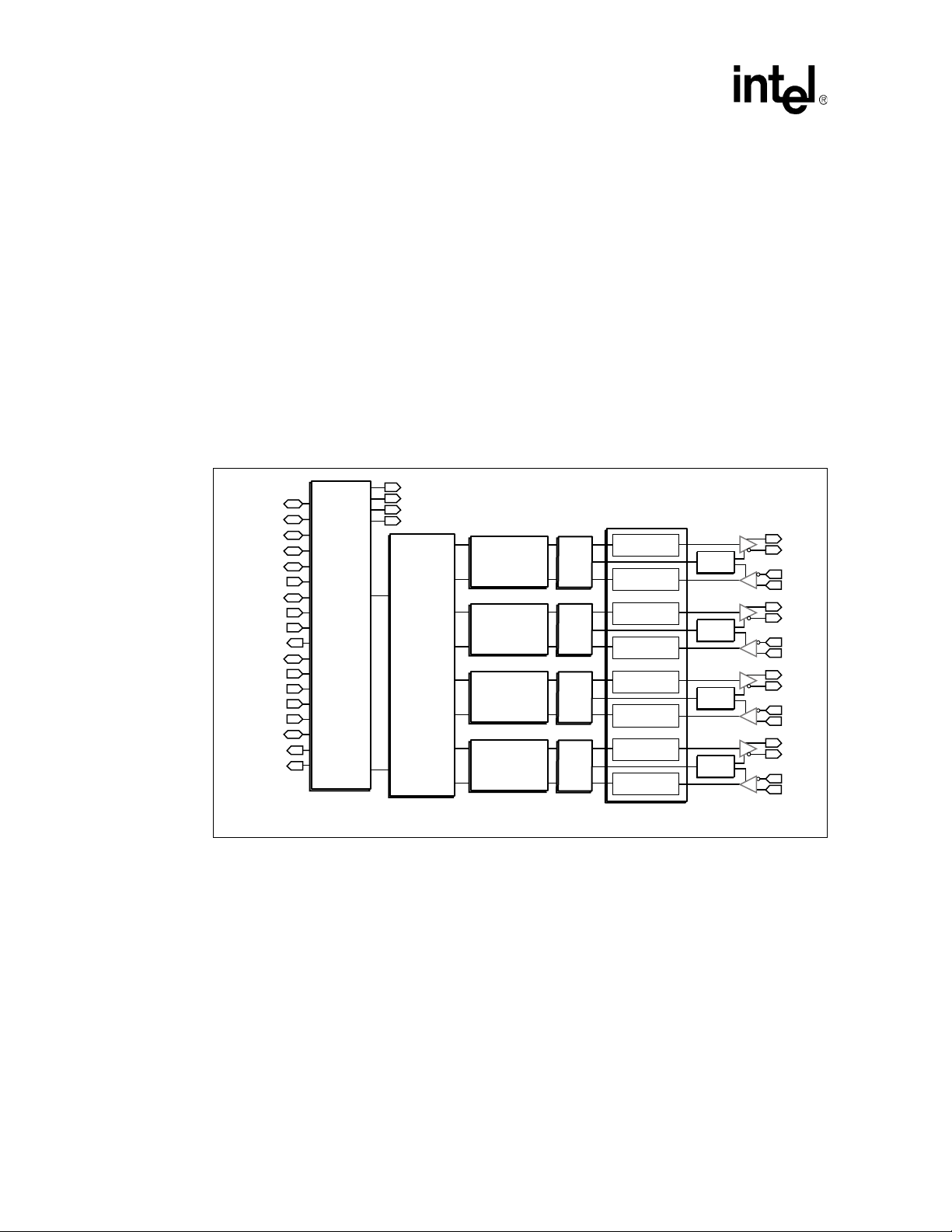

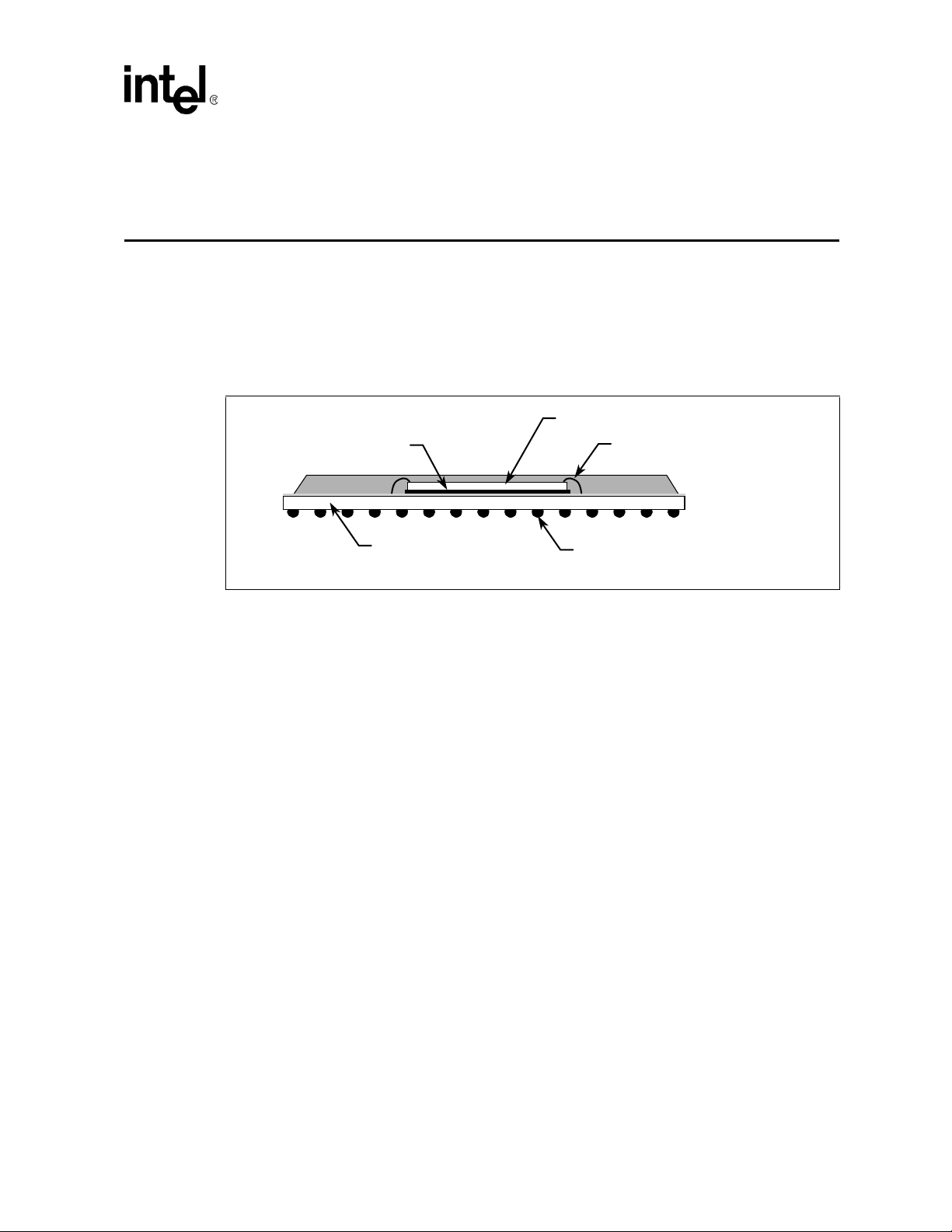

2.2 Applications

The GD31244 may be used to build a Serial ATA Host Bus Adapter which connects to the PCI-X

bus. Control for external activity LEDs, a 37.5 MHz Crystal, a voltage regulator and some external

resistors and capacitors are needed.

Figure 2. Quad Serial ATA Host Bus Adapter

P_AD[63:0]

P_CBE[7:0]

P_PAR

P_PAR64

P_FRAME#

P_TRDY#

P_IRDY#

P_STOP#

P_DEVSEL#

P_REQ#

P_REQ64#

P_ACK64#

PCI-X Bus

P_GNT#

P_CLK

P_IDSEL

P_RST#

P_PERR#

P_SERR#

P_INTA#

V

CC5REF

JTAG

TRST#

Oscillator

37.5 MHz

1000

+

TDI

TD0

TCK

TMS

18 pF

18 pF

Ω, 1%

VIO VCC

CLKIN

CLKOUT

RBIAS

V18A

0.1 µF10 µF

10 µF

Regulator

®

Intel

31244

PCI-X

to

Serial

ATA

Controller

V18B

+

CAP0

CAP1

CAP2

CAP3

RX0P

RX0N

TX0P

TX0N

RX1P

RX1N

TX1P

TX1N

RX2P

RX2N

TX2P

TX2N

RX3P

RX3N

TX3P

TX3N

0.1 µF

VA1

VA0

2.5V3.3V

22µF,

TANT,

EIA-A,

6.3V

.1µF,

0603,

x7R

10 µH

22µF,

TANT,

EIA-A,

6.3V

.1µF,

0603,

x7R

+

20Ω

0603, 1%

+

2.5V

+

22µF,

TANT,

EIA-A,

6.3V

.1µF,

0603,

x7R

10 µH

22µF,

TANT,

EIA-A,

6.3V

.1µF,

0603,

x7R

20Ω

0603, 1%

+

2.5V

B0418-02

0.1 µF

0.015 µF

0.01 µF

0.01 µF

0.01 µF

0.01 µF

0.01 µF

0.01 µF

0.01 µF

0.01 µF

0.01 µF

0.01 µF

0.01 µF

0.01 µF

0.01 µF

0.01 µF

0.01 µF

0.01 µF

LED0

LED1

LED2

LED3

Serial

ATA

Port 0

Connector

Serial

ATA

Port 1

Connector

Serial

ATA

Port 2

Connector

Serial

ATA

Port 3

Connector

Design Guide 15

Page 16

Intel® 31244 PCI-X to Serial ATA Controller

Overview

This page left intentionally blank.

16 Design Guide

Page 17

Intel® 31244 PCI-X to Serial ATA Controller

®

31244 PCI-X to Serial ATA Controller Package

Intel

Intel® 31244 PCI-X to Seri al ATA

Controller Package 3

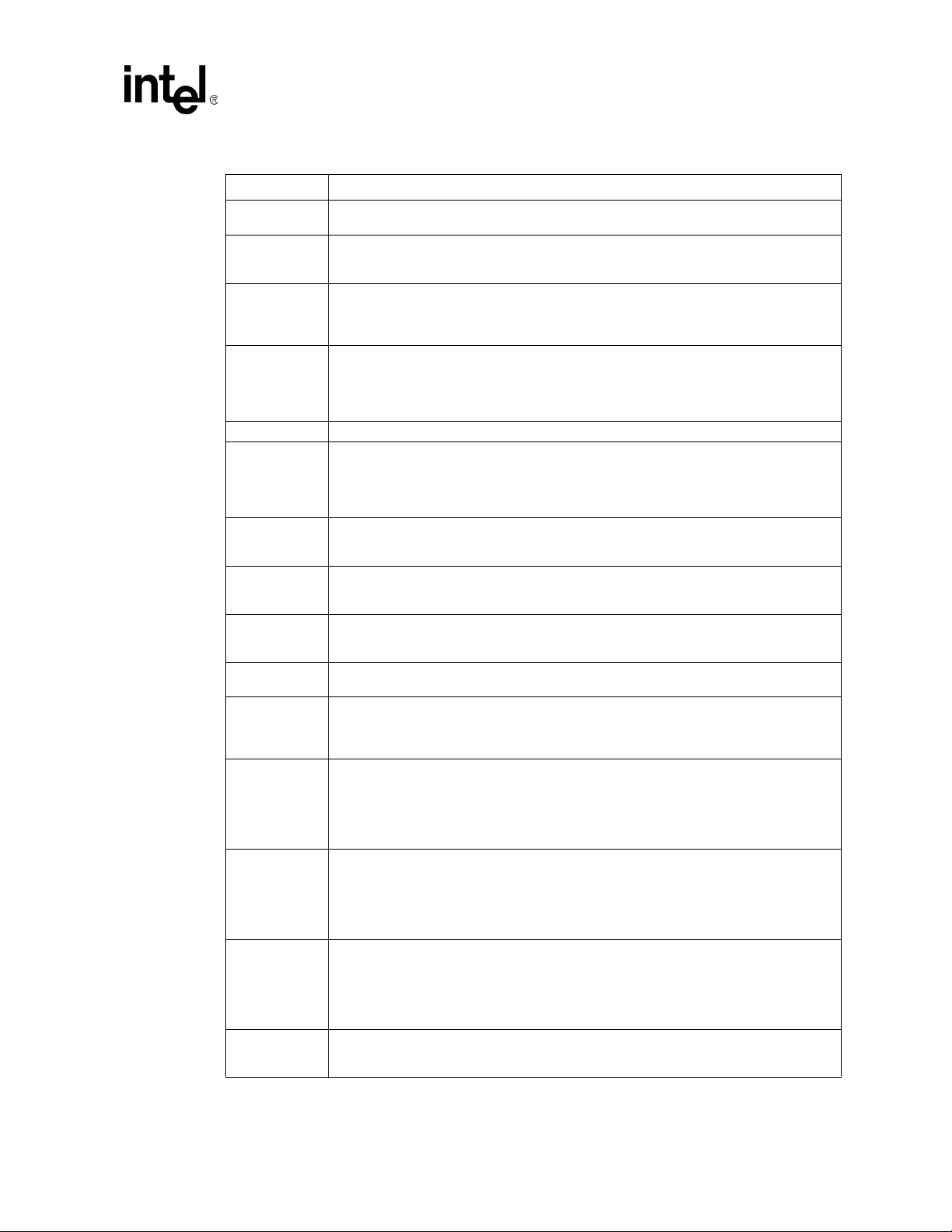

The GD31244 signals, are located on a 256-pin Plastic Ball Grid Array (PBGA) package to simplify

signal routin g and s ys tem implementat ion. For detailed signal descripti ons r efer to the Intel

31244 PCI-X to Serial ATA Controller Datasheet. Contact your Intel sales representative to obtain

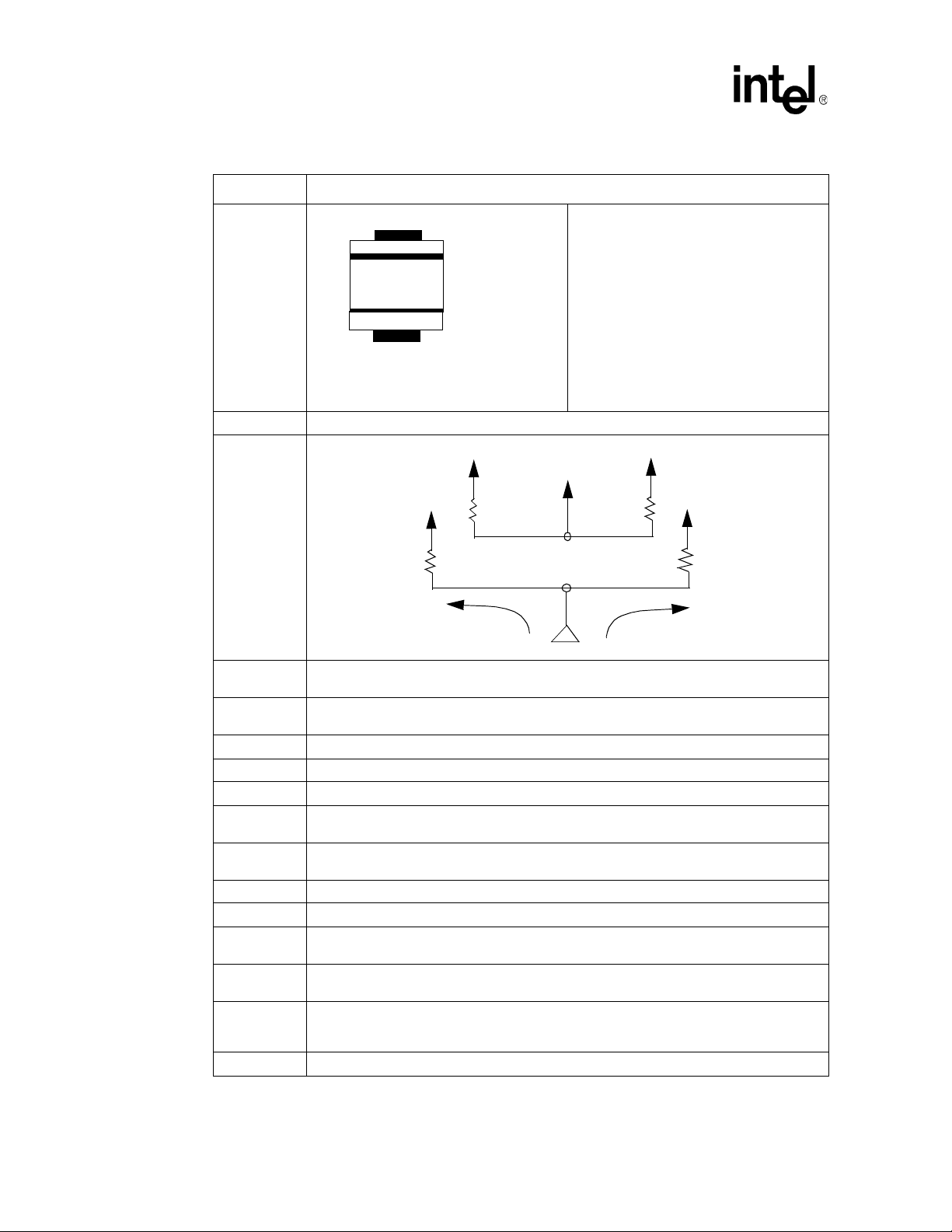

a copy of this document. The construction of the packages is shown in Figure 3.

Figure 3. Packaging Consideration s

Die Attach Epoxy

Polyimide Dielectic

Die

Wirebond

Eutectic Solder Balls

A9196-02

®

Design Guide 17

Page 18

Intel® 31244 PCI-X to Serial ATA Controller

®

31244 PCI-X to Serial ATA Controller Package

Intel

3.1 Sig na l Pin Descriptions

The signal pin descriptions for the GD31244 are provided as a reference. A complete list is also

available in the Intel

®

31244 PCI-X to Serial ATA Controller Datasheet.

Tab le 3. Serial ATA Signals Pin Descriptions

Name Description

TX0P, TX0N,

TX1P, TX1N,

TX2P, TX2N,

TX3P, TX3N

RX0P, RX0N,

RX1P, RX1N,

RX2P, RX2N,

RX3P, RX3N

CLKOUT OUTPU T - LVTTL: This is connected to one sid e of the 37.5 MHz crystal.

CLKIN

CLKO Buffered output of the 37.5 MHz clock.

RBIAS

CAP0, CAP1

LED0, LED1,

†

LED2

, LED3

† LED2 and LED3 are dual purpose pins. Refer to Table 7.

OUTPUT - Differential High-Speed Outputs: These are the differential serial outputs for

each channel. When disabled, these outputs are drive n to their DC-Bias point.

INPUT - Differential High-Speed Inputs: These are the differential serial inputs for each

channel.

INPUT - LVTTL: This is the reference clock input for the clock multiplier unit at 37.5 MHz. It

may be connected to either an external clock source or one side of a crystal.

INPUT - ANALOG: This pi n i s p ul l -down t o g rou nd w ith a 10 00Ω, 1% resistor in order to set

the internal termination resistors to 1000 Ω.

Analog: An external 0.1 µF (+/- 10%) capacitor is connected between these pins to set the

Clock Multiplier PLL loop filter response.

OUTPUT - LVTTL: These are the Activity LED outputs for channel 0, channel1, channel 2

†

and chan nel 3 (active LOW with 10 mA maximum sink capability).

18 Design Guide

Page 19

®

31244 PCI-X to Serial ATA Controller Package

Intel

Table 4. PCI-X Bus Pin Descriptions (Sheet 1 of 2)

Name Description

CAP2, CAP3

P_ACK64#

P_AD[63:0]

P_C/BE[7:0]#

P_CLK All PCI bus signals are referenced to this clock.

P_DEVSEL#

P_FRAME#

P_GNT#

P_IDSEL

P_INTA#

P_IRDY#

P_PAR

P_PAR64

P_PERR#

P_REQ#

Analog: An external 0.015 µF (+/- 10%) capacitor is connected between these pins to set

the PCI PLL loop filter response.

BIDIRECTIONAL - LVTTL: Indicates that the device has positively decoded its address as

the target of the current access and the target is willing to transfer data using the full 64-bit

data bus.

BIDIRECTIONAL - LVTTL PCI Address and Data: The address and data lines are

multiplexed on these pins. A bus transaction consists of an address phase followed by one

or more da ta ph as es . P _AD[ 63 :56] co nt ai ns t he mos t sig ni fic ant by te and P _AD [7: 0] con ta in

the lea s t significant byte.

BIDIRECTIONAL - LVTTL: Com man d and By te E nab le. The bus command and byte enable

signals are multiplexed on these pins. During the address phase, the P_CBE# lines define

the bus comma nd . Dur i ng th e da t a phas e, th e P_C BE # lin es ar e used as Byt e Enabl e s. The

Byte Enables are valid for the entire data phase and det ermine which byt e lanes carry

mean in gfu l da t a.

BIDIRECTIONAL - L V TTL wi th Pull-Up Resistor: Devi ce Sele ct. This signal is asserted by

the target once it has detected its address. As a bus master, the P_DEVSEL# is an input

signa l to th e I n tel

bus has been selected. As a bus slave, the GD31244 asserts P_DEVSEL# to indicate that it

has decoded its address as the target of the current tran saction.

BIDIRECTIONAL - LVTTL with Pull-Up Resistor: Cycle Frame. This signal is driven by the

current master to indicate the beginning and duration of a transaction. P_FRAME# is

asserted to indicate the start of a transaction and de-asserted during the final data phase.

INPUT - LVTTL. Grant: This signal is asserted b y the bus arbiter and indicates to t he

GD31244 that access to the bus has been granted. This is a point-to-point signal and every

mast er ha s its ow n GN T# .

INPUT - LVTTL. Initializati on Dev ice Select: This signal is used as a chip select during

PCI-X conf i gur at ion r ea d an d writ e tra ns act i on s. Thi s si gn al is pro vi ded by the ho st in PC I-X

systems.

OUTPUT - Open Drain Interrupt A: This signal is used to request an inter rupt by the

GD31244. This is an active low , level triggered interrupt signal.

BIDIRECTIONAL - LVTTL with Pull-Up Resistor: Initiator Ready. This signal indicates the

bus master ability to complete the current data phase and is used in conjunction with the

target ready (P_TRDY#) signal. A data phase is complet ed on any clock cycle where both

P_IRDY# and P_TRDY# are asserted LOW.

BIDIRECTIONAL - L V T TL: Parity. Pa rit y i s e ven ac ross P_ AD[3 1: 0] and P _CB E[ 3: 0]# li ne s.

It is stable and valid one clock after the address phase. For data phases, P_PAR is stable

and vali d one clock after either P_IRDY# is asserted on a write or P_TRDY# is asserted on

a read.Once P_PAR is valid, it remains valid until on e clock after th e completion of th e

current data phase. The master drives P_PAR for address and write data phases; and the

target, for read data phases.

BIDIRECTIONAL - LVTTL: Parity for 64-bit Accesses. Parit y is ev en ac r oss P_A D[ 63 :0 ] an d

P_CBE[7:0]# lines. It is stable and valid one clock after the address phase. For data phases,

P_PAR64 is stable and valid one clock after either P_IRDY# is asserted on a write or

P_TRDY# is asserted on a read.Once P_PAR64 is valid, it remains valid until one clock after

the comple ti on of th e cur re nt dat a ph as e. The mas t er dr i ves P_PAR64 for addr e ss a nd wri te

data ph ases; and the target, for read data phases.

BIDIRECTIONAL - LVTTL with P ull- Up Resistor: Parity Error. This signal is used to report

data p arity errors dur ing all PCI-X t ransactions except a Special Cycle. This signal is

asse rt e d tw o cl oc k cy cles afte r th e err o r was detecte d by th e de vi c e re c ei ving data. Th e

minimum duration of P_PERR# is one clock for each data phase where an error is detected.

A device cannot report a parity error until it has claimed the access by asserting

P_DEVSEL# and completed a data phase.

OUTPUT - LVTTL. Request: This signal indicates to the bus arbiter that the GD31244

desires use of the bus. This is a point-to-point signal and every bus master has its own

P_REQ#.

®

31244 PC I- X to ser ial ATA co nt ro ll er i nd ic at ing w h ethe r any d evi ce on the

Intel® 31244 PCI-X to Serial ATA Controller

Design Guide 19

Page 20

Intel® 31244 PCI-X to Serial ATA Controller

®

31244 PCI-X to Serial ATA Controller Package

Intel

Tab le 4. PCI-X Bus Pin Descriptions (Sheet 2 of 2)

Name Description

P_REQ64#

P_RST#

P_SERR#

P_STOP#

P_TRDY#

TEST0 INPUT - LVTTL: Test input. Set LOW for normal operation.

TOUT OUTPUT - T est pin. Do not use.

BIDIRECTIONAL - LVTTL: Indicates the attempt of a 64-bit transaction on the PCI bus.

When the target is 64-bit capable, the target acknowledges the attempt with the assertion of

P_ACK64#.

INPUT - LVTTL Reset: This signal is used to place PCI-X registers , sequencers, and

signal s into a consistent state. When P_RST# is asserted, all PCI-X output signals are

tri-stated.

OUTPUT - Open Drain with Pull-Up Resistor: System Error. This signal is used to report

address parity errors. When an error is detected, P_SERR# is driven LOW for a single

PCI-X clock.

BIDIRECTIONAL - LVTTL with Pull-Up Resistor: Stop. This signal is driven by the targe t

to indicate to the initiator that it wishes to stop the current transaction. As a bus slave,

P_STOP # is dr i ven by the GD 31 244 t o i n for m t he bu s ma st er t o stop t he curr e nt t r ansac ti o n.

As a bus master, P_ST OP# is received by the GD31244 to stop the current transaction.

BIDIRECTIONAL - LVTTL with Pull-Up Resistor: Target Ready. This signal indicates t he

selected device’s ab ility to complete the current data phase and is used in conjunction with

P_IRDY#. A data phase is completed on any clock cycle where both P_IRDY# and

P_TRDY# are asserted LOW.

Tab le 5. Configuration Pin Descriptions

Name Type Description

32BITPCI# INPUT

DPA_MODE# INP UT

SSCEN INPUT Tie this pin to GND.

Tab le 6. JTAG Pin Descriptions

Name Description

TDO

TDI

TCK

TMS

TRST#

TEST DATA OUTPUT: is the serial output pin for the JTAG feature. TDO is dri v en on the

falling edge of TCK during the SHIFT-IR and SHIFT-DR states of the Test Access Port. At

other times, TDO floats. The behavior of TDO is in dependent of P_RST#.

TEST DATA INPUT : is the serial input pin for the JTAG feature. TDI is sampled on the rising

edge of TCK, during the S HI FT-IR and SHIFT-DR states of the Test Ac ce ss Por t. Thi s sig nal

has a weak internal pull -up to ensure proper operation when this signal is unconnected.

TEST CLOCK: is an input which provides the clocking function for the IEEE 1149.1

Boundary Scan T esting (JTAG). State info rmation and data are clocked into the component

on the rising edge and data is clocked out of the component on the falling edge.

TEST MODE SELECT: is an in pu t samp led at th e ri sin g ed ge of TCK to select the operation

of the test logic for IEEE 1149.1 Boundary Scan testing. This signal has a weak internal

pull-up to ensure proper operation when this signal is unconnected.

TEST RESET: an input that asynchronously resets the Test Access Port (TAP) controller

function of IEEE 1149.1 Boundary Scan Testing (JTAG). This signal has a weak internal

pull-up.

Pin number A2. This pin control s the state of the “64 bit device” status

bit 16, in the PCI-X Status Regi ster. When pulled down, reports a 0, a

32-bit bus. When pulled up, reports 1, a 64-bit device.

INPUT - LVTTL: When HIGH or open, selects Master/Slave Mode for

software compatibility. When LOW, selects Master-Master mode for

high performance.

20 Design Guide

Page 21

®

Intel

Table 7. Serial ROM Interface Pin Descriptio ns

Name Description

Intel® 31244 PCI-X to Serial ATA Controller

31244 PCI-X to Serial ATA Controller Package

SDI

SDO (LED3)

SCLK (LED2)

SCS#

INPUT - LVTTL with Pull Up: Connects to the serial data output (SDO) of the Serial ROM.

Customers are recommended to add pads for both a pull-up and a pull-down resistor for

possible use in the future.

OUTPUT - LVTTL: Connects to the serial data input (SDI) of the Serial ROM. This is also

the ac tivity LED output for Channel 3 when all four LEDs are activated (active LOW).

OUTPUT - LVTTL: Connects to the clock input (SCLK) of the serial ROM. This is also the

acti vity LED output for Channel 2 when all four LEDs are activated (active LOW) .

OUTPUT - LVTTL with Pull Up: Connects to the chip select input (SCS#) of the Serial

ROM.

Table 8. Power Supply Pin Descriptions

Name Description

OUTPUT: This is the reg ul at ed 1 . 8V supply ge ner at ed i nt ern al ly. Bypa ss wit h 0.1 a nd 1 0µF

capacitors.

V18A, V18B

V

CC5REF

VA0 , VA1

V

SS

V

CC

V

IO

, V

V

CC0

V

, V

CC2

V18A and V18B are each outputs of internal voltage regulators. They need to be separately

bypassed to ground with 0.1 and 10 µF capacitors separately, they must not be connected

together.

Voltage Clamp I/O: In 5 V tolerant systems, this is connected to a 5 V supply. In 3.3 V

powere d systems this is connected to 3.3 V. In PCI add-in cards, this is normally connected

to I/O Power (10 A, 16 A, 19 B, 59 A and 59 B). The user must ensure that the value of

V

the GD31244 not just PCI inputs. For example, when the Serial ROM device is 5 V I/O this

pin must be 5 V regardless of the PCI bus.

2.5 V Analog Power Supply: Separate filtering is recommended. VA0 supplies the PCI

PLL. VA1 supplies the CMU.

Ground.

2.5 V Digital Logic Power Supply.

3.3 V PCI I/O Power Supply.

,

CC1

2.5 V High-Speed I/O Power Supply for each channel.

CC3

is hig h enou gh t o ensu r e c ompli an ce to t he V

CC5REF

speci fic ati o n on ev ery i n put to

IH(MAX)

3.1.1 VA0, VA1 (V

CCPLL

) Pin Requirements

To reduce clock skew, the VA0 and VA1 balls for the Phase Lock Loop (PLL) circuit are each

isolat ed o n the pac kag e. The lowpa s s fi lter, as shown in Figure 2, reduces noise induced clock ji tt er

and its effects on timing relationships in system designs. The 22 µF bulk capacitors must be low

ESR solid tantalum and the 0.1 µF ceramic capacitor must be of the type X7R. The node

connecting VA0 and VA1, must be as short as possible.

Design Guide 21

Page 22

Intel® 31244 PCI-X to Serial ATA Controller

®

31244 PCI-X to Serial ATA Controller Package

Intel

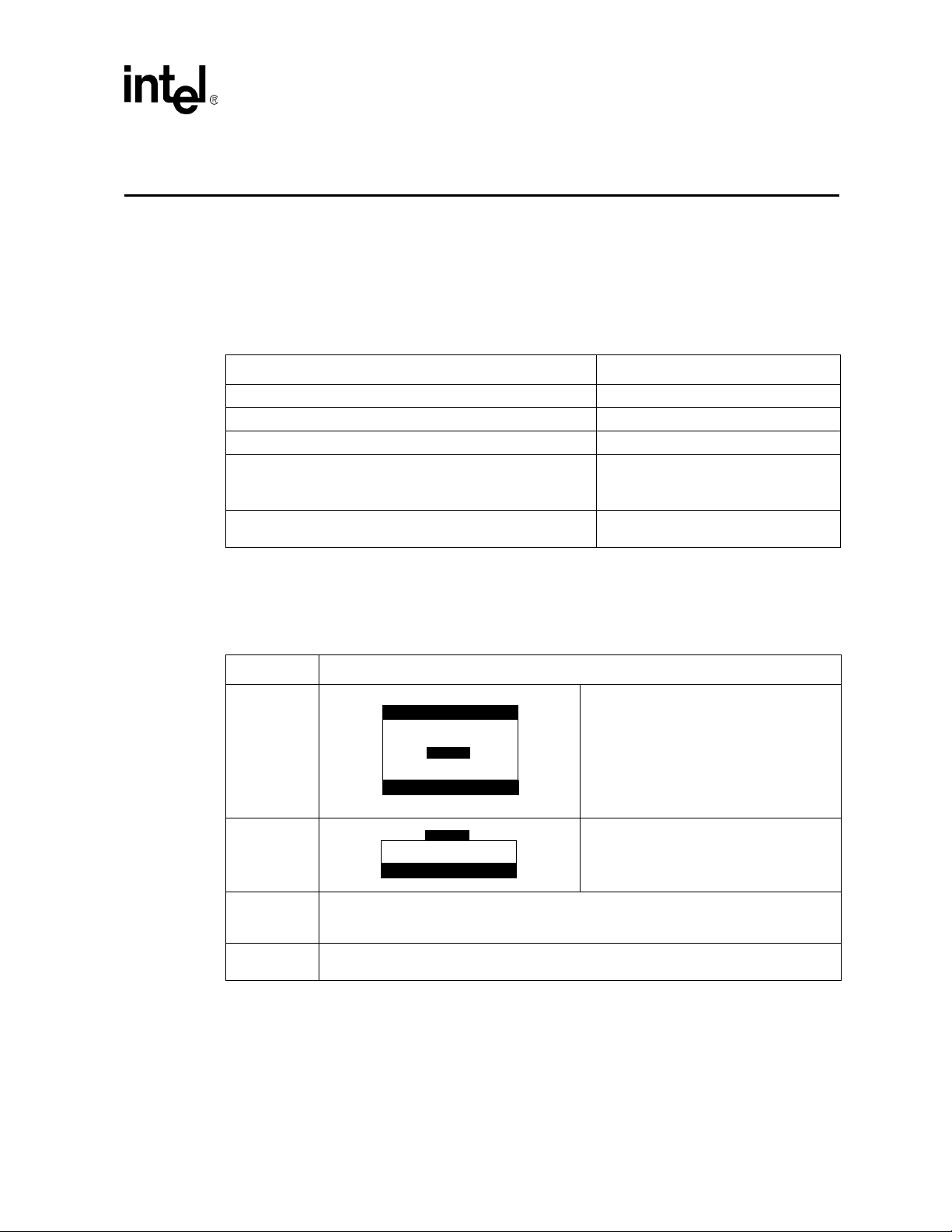

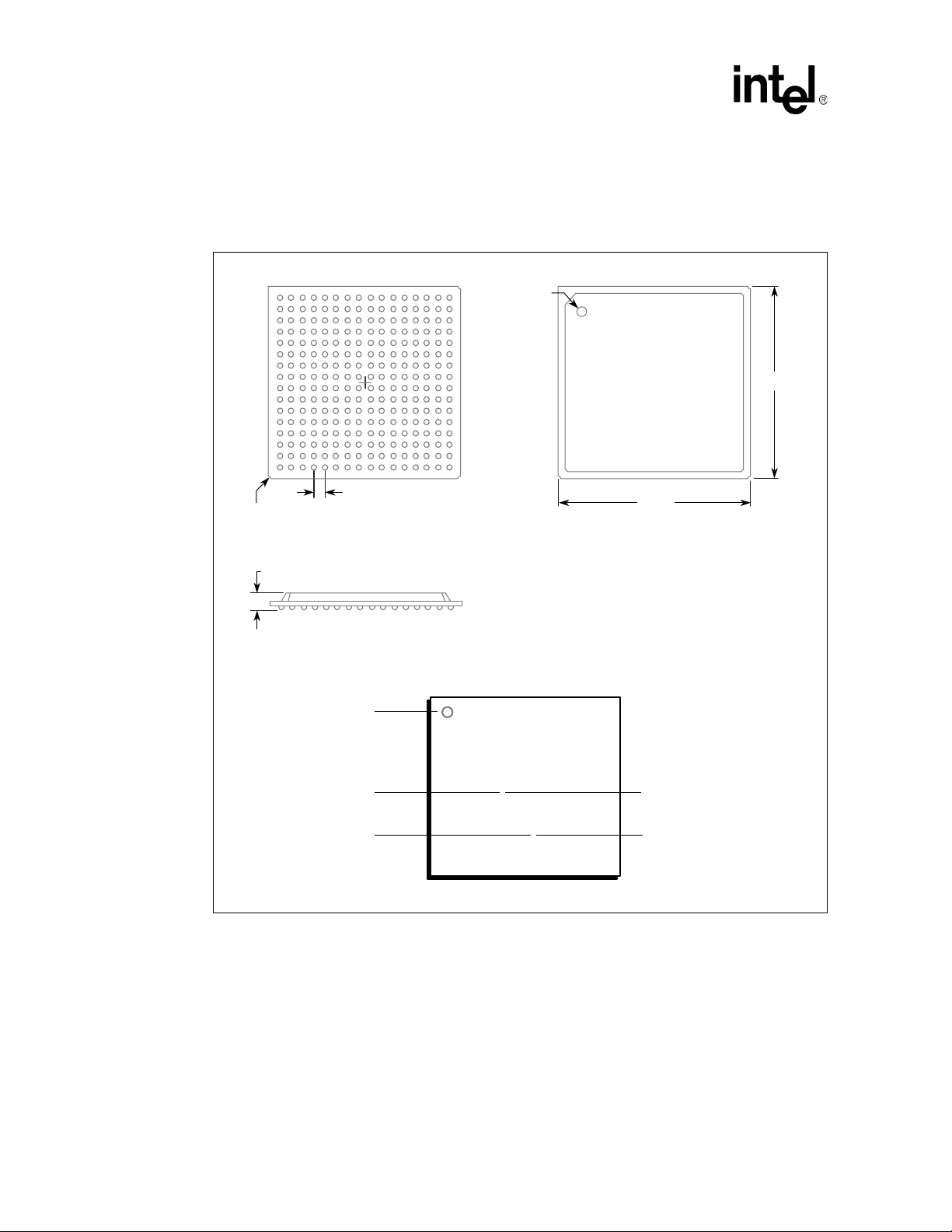

3.2 Package/Marking Information

The package is marked wit h three lines of text as shown in Figure 4. (The figure is not to scale.)

Figure 4. Package Information: 256-pin PBGA

12

1416

10

8

11

13

15

This page left intentionally blank.

3x 0.50 R

1.0 mm, Typ

BOTTOM VIEW TOP VIEW

13254769

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

Pin A1

Indicator

17mm

17mm

2.06 ± 0.3

SIDE VIEW

Pin A1 Identifier

Part Number Package Suffix

Date Code

Intel® 31244 XX

#### AAAA

Lot Tracking Code

A9626-02

22 Design Guide

Page 23

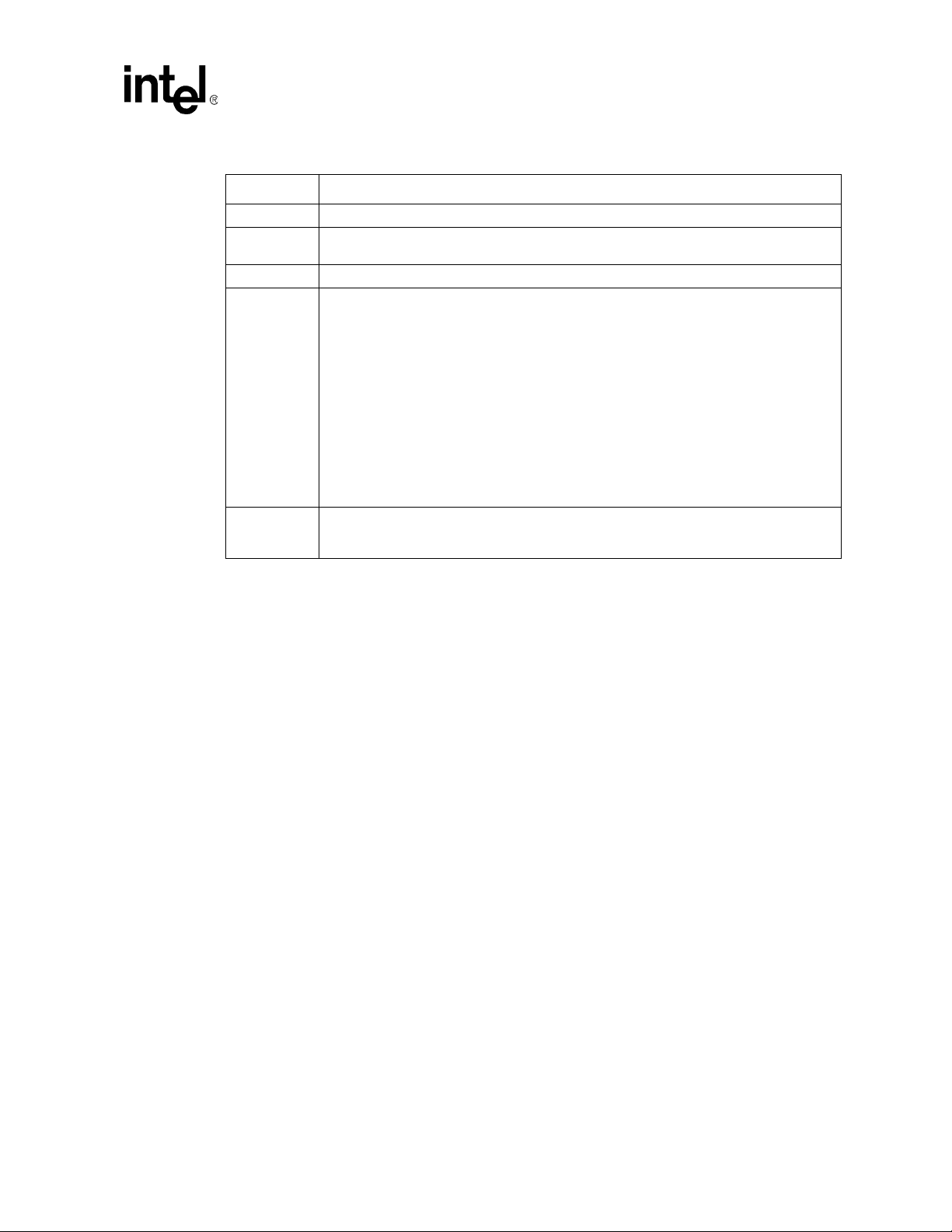

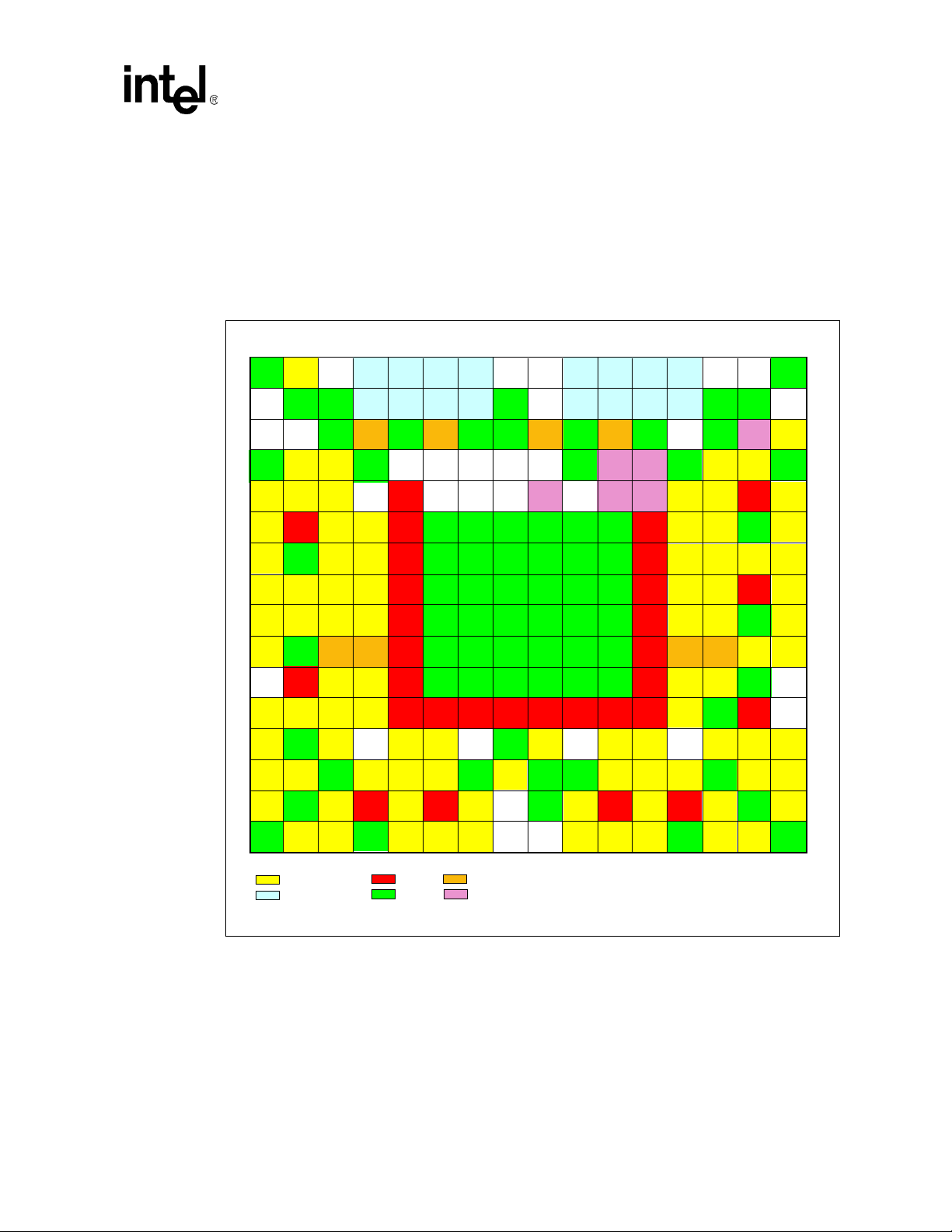

3.3 Ball Map By Function

Figure 5 shows the 544 BGA pins mapped by pin function. This diagram is helpful in placing

components aroun d the GD31244 for the layout of a PCB. To simplify routing and minimize the

number of cross traces, keep this layout in mind when placing components on your board. Name

signals, by desig n, are located on the PBGA package to simpl ify signal routing and s ys tem

implementation.

Figure 5. PB GA M apped By Pin Func ti on

1 2 3 4 5 6 7 8 9 101112 131415 16

32BIT

VSS

A A

B B

VCCREF VSS VSS TXOP RX0N TX1P RX1N VSS TX2P RX2N TX3P RX3N VSS VSS VCCREFVA1

LED3 TX0N RX0P TX1N RX1P CAP0 CAP1 TX2N RX2P TX3N RX3P CLKIN CLKOUT VSS

PCI#

LED2 P_AD32VCC

C

D D

E E

F F

G G

H H

J J

K K

L L

M M

N N

P P

R

T T

SCS# VSS VCC0 VCC1 VSS VSS VSS VSS TDO

VSS P_RST# P_INTA# VSS LED0 MS_DA SSCEN VSSVCC TRST# TCK VSS P_AD33

P_REQ# P_AD31 P_GNT# CLKO SDI LED1 TOUT TEST0 RBIAS TDI TMS P_AD36 P_AD35 VI0 P_AD34VIO

VIO

VSS

P_AD28 VIO P_AD29 P_AD30

P_AD25 VSS P_AD26 P_AD27

P_AD23 P_IDSEL P_CBE3 P_AD24 P_AD46 P_AD45 VIO P_AD44

P_AD19 P_AD20 P_AD21 P_AD22

P_AD18 VSS VCC VCC

V18A VIO

P_

TRDY#

P_

SERR#

P_

PERR#

P_PAR VSS P_AD15 VIO

VSS P_CBE1 P_AD14 VSS

12345678910111213141516

P_

IRDY#

P_

P_AD16

DEVSEL#

VSS

P_CBE2 VCCREF

P_

VSS P_AD13

STOP#

PCI-X Interface Pins

SERDES section

VIO

VIO

VIO

VIO

VIO

P_AD17

P_

VIO

FRAME#

P_AD12

P_AD11 P_CBE0 VSS P_CLK VSS VSS

P_AD10

P_AD9

VIO 3.3V

VSS

VSS VSS VSS VIO

VSS VSS VSS VSS

VSS

VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS VSS

VSS VSS VSS VSS VSS

VSS VSS VSS VSS

VIO

VIO VIOVIO

VCCREF

P_AD8

VIO P_AD6 VA0 VSS P_AD3 VIO P_CBE6

P_AD7 P_AD5 CAP3 CAP2 P_AD2

VCC is 2.5V

JTAG Section

VCC2VSS VCC3VSS

VCC

VSS VSS

VSS P_AD4

VIO

VCCREF

VSS VIO

VSS

VSSVSS

VIO

P_AD1

P_

REQ64#

P_

ACK64#

P_AD39 P_AD38 VSS P_AD37

P_AD43 P_AD42 P_AD41 P_AD40

VIO

P_AD49 P_AD48 VSS P_AD47

VIO

VCC VCC P_AD51 P_AD50

VIO

P_AD53 P_AD52 VSS V18B

VIO

VIO

P_AD0

P_CBE7

P_CBE5

VSS VIO VCCREF

P_AD54

VCCREF P_AD57

P_CBE4 VSS P_AD59

P_AD63 VSS

VIO

VSS P_AD62 P_AD61

P_

VSS

PAR64

P_AD56 P_AD55

P_AD58

P_AD60

VSS

B0419-02

C

R

Design Guide 23

Page 24

Intel® 31244 PCI-X to Serial ATA Controller

®

31244 PCI-X to Serial ATA Controller Package

Intel

This page left intentionally blank.

24 Design Guide

Page 25

Intel® 31244 PCI-X to Serial ATA Controller

Rout ing Gu idelines

Routing Guidelines 4

This chapter provi des routing guidelines for layout and design of a printed circuit board using the

GD31244. The high-speed clocking required when de s igning with the GD31244 requires special

attention to signal integrity. In fact, it is highly recommended that the board design be simulated to

determine optimum layout for signal integrity. The information in this chapter provides guidelines

to aid the designer with board layout. S everal factors influe nce the signal integrity of a GD31244

design. These factors include:

• power distribution • decoupling

• minimizing cros st alk • layout conside r ations when routing the SATA bus

4.1 General Routing Guidelines

This section deta ils general routing guidelines for connecting the GD31244. The order in which

signals are routed varies from desi gner to designer. Some designers prefer to route a ll clock signals

first, while others prefer to route all high-speed bus signals first. Either order may be used,

provided the guidelines listed here are followed.

Route the GD31244 address/data and control si gnals using a da isy chain topology. This topology

assumes that no stubs are used to connect any devices on the net. Figure 6, shows two possible

techniques to achieve a stubless trace. When it is not possible to apply one of the se two techniques

due to congestion, a very short stub is allowed - do not exceed 250 mils.

Note: A rule of the thumb for stub trace length is to make sure that the stub length is less than or equal to

the one-quarter of the signal transition.

Example:

• Nominal trace velocity To = 190 ps/in

• Typical signal slew rate = 2 V/ns

• Low-to- H ig h Voltage differential (0.3V

• Rise Ti me T

=.66 V *(1 ns/2 V) = 330 ps

R

to 0.5 VCC) =0.66 V

CC

• Equivalent Distance = 330 ps/T o = 1. 74in

• Stub length less than 1/4 of the length =0 .44 in

Figure 6. Examples of Stubless and Short Stub Traces

Stubless Short Stub

<250 Mils

A7690-01

Design Guide 25

Page 26

Intel® 31244 PCI-X to Serial ATA Controller

1

Routing Guidelines

4.2 Crosstalk

Crosstalk i s ca used by capa citi ve and ind uctive c oupling bet ween sign al s. Cr osst alk i s compos ed of

both backwar d and for ward cross talk compon ents. B ackward crosst alk c reate s an indu ced sign al on

victim network that propagates in the opposite direction of the aggressor signal. Forward crosstal k

creates a signal that propagates in the same direction as the aggressor signal.

Circuit board a nalysis software is used to analyze your board layo ut for crosstalk problems.

Examples of 2D analysis tools inc lude Parasitic Parameters from ANSOFT

*

Design

. Crosstalk prob lems occur when circuit etch line s run in parallel. When board analysis

software is not available, the layout maintain s minimum spacing between parallel circuit signals

lines.

• A general guideline to use is, that space distance between adjacent signals be a least 3.3 times

the distance from signal trace to the nearest return plane. The coupled noise between adjacent

traces decreases by the square of the distance between the adjacent traces.

• It is also recommended to sp ec ify the height of the above reference plane when laying out

traces and provide this parameter to the PCB manufacturer. By moving trac es closer to the

nearest reference plane, the coupled noise decreases by the squ are of the distance to the

referen ce p la n e.

Figure 7. Crosstalk Effects on Trace Distance and Height

P

H

aggressor victim

Reference Plane

• Avoid slots in the ground plane. Slots inc r eases mutual inductance thus incre as ing crosstalk.

• Make sure that ground plane surrounding connector pin fields are not completely cleared out.

When this area i s compl etely clea red out, aro und the c onnect or pins , all the ret urn curre nt must

flow togeth er around the pin field increasing crossta lk. The preferred method of laying out a

connector in th e GND laye r is shown in Figure 8B.

*

and XFS from Quad

Reduce Crosstalk:

- Maximize P

- Minimize H

A9259-01

Figure 8. PCB Gr ound Layout Around Connectors

Connector

Connector Pins

GND PCB Layer

A. Incorrect method B. Correct method

A9260-0

26 Design Guide

Page 27

4.3 EMI Considerations

It is highly recommended that good EMI design practices be followed when desi gning with the

®

31244 PCI-X to serial ATA controller.

Intel

• To minimize EMI on your PCB a useful technique is to not extend the power planes to the

edge of the board.

• Another technique is to surround the perimeter of your PCB layers with a GND trace. Thi s

helps to shield the PCB with grounds minimizing radiati on.

The below link may provide some us eful general EMI guidelines considerations:

http://developer.intel.com/design/auto/mcs96/applnots/272673.htm

Intel® 31244 PCI-X to Serial ATA Controller

Rout ing Gu idelines

Design Guide 27

Page 28

Intel® 31244 PCI-X to Serial ATA Controller

Routing Guidelines

4.4 Power Distribution and Decoupl ing

Have ample decoupling to ground, for the power pl anes, to minimize the effects of the switching

currents. Three types of decoupling a re: the bulk, the high-frequency ceramic, and the inter-plane

capacitors.

• Bulk capacitance consist of el ectrolytic or ta ntalum capacitors. These capacitors supply large

reservoirs of charge, but they are useful only at lower frequenc ies due to lead inductanc e

effects. The bulk capacitors may be located anywhere on the board.

• For fast switching currents, high-fre quency low-inductance ca pacitors are most effective.

Place these ca pac itors as close to the device being decoupled as possible. This minimizes the

parasitic resistance and inductance associated with board traces and vias.

• Use an inter-plane c apacitor between power a nd ground planes to reduce the effective plane

impedance at high frequencies. The general guideline for placing capacitors is to plac e

high-frequ ency ceramic capacitors as close as possibl e to the module.

4.4.1 Decoupling

Inadequate high-freque ncy decoupling re su lts in intermittent and unreliable beh avior. A general

guideline recommends that you use th e largest easily available capacitor in the lowest inductance

package.

4.4.1.1 Intel® 31244 PCI-X to Serial ATA Controller Decoupling

It is rec om me nded that to decouple the VCC 2.5 V, use at least t welve 0.1 µF capacitors in as close

proximity to the GD31244 VCC pins as possible. When feasible, locate these ca pacitors on the

back of the board, close to the GD31244 VCC ball.

28 Design Guide

Page 29

4.5 Trace Impedance

e

All signal layers require controlled impedance of 50 Ω +/- 15%, microstrip or stripline w here

appropriate, unless otherwise specified. Select in g the appropriat e boa rd st ack-up to minimize

impedance variations is very important. When calculating flight times, it is important to consider

the minimum and m aximum t race impedanc e bas ed on th e swit chi ng neig hbori ng tr aces. Use wider

spaces between traces, since this may minimize trace-to-trace coupling, and reduce cross talk.

All recommendat ions described in this document assume a T

otherwise specified. When a different stack up is used the trace widths must be adjusted

appropriately. When wider traces are used, the trace spacing must be adjusted accordingly

(linearly).

It is highly recommend ed tha t a 2D Field Solver be used to design the high-speed traces. The

following Impedance Calculator URLs pro vide approximations for the trace impe dance of various

topologies. They may be used to generate the starting point for a full 2D Field solver.

http://emclab.umr.edu/pcbtlc/

http://www.westak.com/techcenter/imped/

The following websit e link provides a useful basic guideline for calcul ating trace parameters:

http://www.ultracad.com/calc.htm

Note: Using stripline transmission lines may give better results than microstrip. This is due to the

difficulty of precisely controlling the dielectric constant of the solde r mask, and the difficulty in

limiting the plated thicknes s of microstrip conductors, which may substantially increase cross-talk.

4.5.1 Differ e nt ial Impe da nc e

The Serial ATA standard defines a 100 ohms differential impedance. This section provide s some

basic background information on the differentia l impedance calculations. In the cros s section of

Figure 9 shows the cross section of two traces of a differential pair .

Figure 9. Cross Section of Differential Trace

5mil50Ω signal trace, unless

wid

Ground reference plan

To calculate the coupled impedance requires a 2x2 matrix. The diagonal val ues in the matrix

represent the impedance of the traces to ground and the off-diag onal values provide a measu re of

how tightly the traces are coupled. T he differential impedance is the val u e of the line-to-l ine

resistor terminator that optimally terminates pure diff erential signals. The two by two matrix is

shown below as:

Example 1. Two-by-two Differential Impedance Matrix

Z11 Z12

Zo

=

Z21 Z22

Design Guide 29

Page 30

Intel® 31244 PCI-X to Serial ATA Controller

Routing Guidelines

For a symmetric trace Z11 = Z22, the differential impeda nce may be calcula ted from this equation:

Z

differential

For two traces to be symmetric, they must have the same width, thickness and height above the ground

1

With the traces terminated with the appropriate differential, impedance ringing is minimized.

plane.

= 2(Z11-Z12)

1. “Terminatin g Differe nti al Signals on PCBs ”, Ste ve Kauf er and Kelee Crisa fu lli, Prin te d Circu it D esi gn, Ma rc h 1999

30 Design Guide

Page 31

®

31244 PCI-X to Serial ATA Controller Interface Ports

Intel

Intel® 31244 PCI-X to Serial ATA Controller

Intel® 31244 PCI-X to Seri al ATA

Controller Interf ac e Ports 5

5.1 Serial ROM Interface

In add-in card applications, firmware may be downloaded to the syste m from a Serial EEPROM or

Serial Flash ROM, through the Serial ROM Interface. This industry standard, 4-pin interface,

allows any size of device, up to 128 Kbytes, to be connected to the Intel

ATA controller. This SPI int erfa ce was designed for compatibility with an ST Microelectronics*

M25P10-A or Atmel* AT25F1024 device. Two of the pins are dual purpose to sup port four LED

port activity indicators. This four pin interface is defined as foll ows:

1. SDI INPUT: Connects to the serial data output (S O) of the Serial EEPROM. Data is shifted

out of the EEPROM on the falling edge of SCLK. Customers are recom mended to add pads

for both a pull-up and a pull-down resistor for possib le use in the future.

2. SDO OUTPUT: Connects to the serial data input (SI) of the Serial EEPROM. Data is latched

into the Serial EEPROM on the rising edge of SCLK. This is als o the activity LED output for

Channel 3 when all four LEDs are act ivated (active LOW).

3. SCLK OUTPUT: Connects to the clock input (SCK) of the Serial EEPROM. This is also the

activity LED output for Channel 2 when all four LEDs are activated (active LOW).

®

GD31244 PCI-X to serial

4. SCS# OUTPUT: Conne cts to the chip selec t input (CS#) of the Serial EEPROM.

5.2 JTAG Interface

An IEEE 1149.1 compatible JTAG interface and boundary scan func tionality is provided to assist

on-board testing of the device. A BSDL test file is provided by Intel.

Design Guide 31

Page 32

Intel® 31244 PCI-X to Serial ATA Controller

®

31244 PCI-X to Serial ATA Controller Interface Ports

Intel

5.3 PCI-X Interface

The 64-bit, 133 MHz PCI-X interface is fully compliant with the PCI Local Bus Specification,

Revision 2.2 and the PCI-X Ad dendum to the PCI L oc al Bus Sp ecific a t io n, Revision 1.0a. The

PCI-X bus supports up to 1064 Mbytes/s transfer rate of burst data. The GD31244 is backwards

compatible with 32-bit/33 MHz, 32-bit/66 MHz and 64-bit/66 MHz operation. The PCI logic

supports Plug -n-P lay operation, which allows hardware and firmwar e to re solve all setup conflicts

for the user. The GD31244 supports both slave and master data transfe rs. The devices res ponds to

the following bus cycles as a slave:

• I/O Reads • Configuration Read

• I/O Writes • Configuration Write

• Memory Read Bus Cyc les

As a master, the GD31244 responds to:

• Single Memory Reads • Line Memory Reads

• Multiple Memory Reads • Memory Writes

During sys tem initialization, the Configuration Manager of the host system reads the configuration

space of each PCI-X device. Aft er har dware r eset, the GD31244 only responds to PCI-X

Configuration cycles in anti cipation of being initialized by the Configuration Manager. Ea ch

PCI-X devic e is addressable individually by the use of unique IDSEL# signals which, when

asserted, indicate that a configuration read or write is occurring to this device. The Configuration

Manager reads the setup registers of each device on the PCI-X bus and then, based on thi s

informatio n, assigns system resources to each supported function through Type 0 configuration

reads and writ es. Type 1 configuration cycles are i gnore d. This sche me allo ws the GD31244 and it s

external ROM to be relocated in the memory and I/O space. Interrupts, DMA Channels and other

system resources may be reallocated appropriately.

32 Design Guide

Page 33

®

31244 PCI-X to Serial ATA Controller Interface Ports

Intel

5.4 Serial ATA Interface

Four 1.5 Gbits/s Serial ATA ports are located on the GD31244, to support point-to-point

connectivi ty to disk drives, CDROMs, DVD ROMs or any other Ser ial ATA target device. Each

port is compliant with the “Serial ATA: High speed Serialized AT Att achme nt Specification,

Revision 1.0e. High-speed diff erential duplex serial lines se nd 8B/10B encoded data to and from

the GD31244 and the target at a maximum raw data rate of 1.2 Gbits/s (150 Mbytes/s). Copies of

the targets Task File Registers are maintained on the GD31244 and transferred as needed to the

target. The Serial ATA protocol is software compatible with all existing operating systems that

support ATA devices, however, perfo rmance and reliability are improved since all data is CRC

checked.

5.4.1 Direct Port Access (DPA)

The SATA Dire ct Port Access architecture allows for independent control of the SATA devices.

Unlike ATA master/slave con f iguration where only one drive may operate at a time, DPA allows

multiple drivers to be accessed concurrently. In addition, each port supports its own DMA cha nnel

allowing each port to transfer data independently (between a device and memory).

The DPA mode does change the register layout from PCI IDE. Therefore, legacy device drivers do

not support this mode. DPA requires the registers (incl uding the Command Block , Control Block,

DMA, and SATA superset) for each drive is available at all times. Instead of using I/O space, these

registers are mapped to a single 4 KB block. Each port has 512 KB; the remaining 2 048KB are for

the common port registers. The 4 KB block is mapped using one PCI BAR register.

Intel® 31244 PCI-X to Serial ATA Controller

5.4.2 Ext en de d Voltage Mode

The SATA voltages were designed primarily for a cable connection to the hard drives. In certain

applications , s uch as NAS/SAN enclosures, the hard disk drives (HDD) are conne cted to a

backplane, not a cable (typically in desktop systems). Due to the frequency of the SATA interface,

the backplane cre ates a significant attenuation of the SATA signals. In an effort to simplify system

designs, the GD3124 4 of fers an extended voltage range to help all eviate this issue . T his extended

voltage range allows standard SATA HDD to be used with SATA backplanes.

The firmware may be place int o the Exte rnal Voltage Mode by setting bit 14 in PHY Configuration

Register Address 140H to 1. This forces the firmware to operate with this extended vol tage range.

Table 9. Normal Volta ge Mode

Parameter Description Minimum Maximum Units

∆

V

OUT

∆

V

IN

Table 10. Extended Voltage Mode

Parameter Description Minimum Maximum Units

∆

V

OUT

∆

V

IN

TXx output differential peak-to-peak voltage swing 400 600 mVp -p

RXx input dif ferential peak-to-peak voltage swing 325 600 mVp-p

TXx output differential peak-to-peak voltage swing 800 2000 mVp-p

RXx input dif ferential peak-to-peak volt age swing 175 2000 mVp-p

Design Guide 33

Page 34

Intel® 31244 PCI-X to Serial ATA Controller

3.3V

3.3V

3.3V

®

31244 PCI-X to Serial ATA Controller Interface Ports

Intel

5.4. 3 LED Interface

Serial ATA interfaces on disk drives do not include the traditional ATA output, which drives an

LED to indicate that the drive is active. The GD31244 compensates for this missing function by

adding four LED outputs , which sink 10 mA. In Master/Slave com patibility mode, LED0 goes

LOW to turn on an Activity LED, anytime there is activity on either Channel 0 or Channel 1.

Likewise , LED1 goes LOW to turn on an Activity LED, anytime there is activity on either

Channel 2 or Channel 3. These two outputs may be wire -ORed toge ther to use one LED for al l four

ports. During EEPROM tra nsfers, the LED function on SCLK and SDO is suspended. A buffer

may be required when the LEDs are located off-bo ard a nd an EEPROM is used.

When GD31244 is configure d in Dir ect Port Acce ss mode (DPA_MODE# is LOW), then each port

is assigned its own LED as follows:

• Port 0 on LE D0

• Port 1 on LE D1

• Port 2 on LE D2

• Port 3 on LE D3

During EEPROM transfers, the LED function on SCLK and SDO is suspende d. A buffer may be

required when the LEDs are loc ated off-board and an EEPROM is use d. Figure 10 shows a th e

common configurations of using the serial EEPROM in conjunction with the LEDs.

Figure 10. LED and Serial EEPROM Configurations

Serial EEPROM

SDO

SDI

SCS#

SCLK

LED0

LED1

4 LEDs

DPA Mode

No EEPROM

LED

LED

LED

LED

470W

3.3V

3.3V

3.3V

3.3V

SDO

SDI

SCS#

SCLK

LED0

LED1

B. Typi cal HBA:A. Server Application:

2 LEDs

Master/Slave Mode

EEPROM for Boot co de

LED

LED

SI

SO

CS#

SCK

470W

3.3V

3.3V

Serial EEPROM

LED

LED

LED

LED

SI

SO

CS#

SCK

SDO

SDI

SCS#

SCLK

*

LED0

LED1

C. Typi cal HBA:

4 LEDs

Master/Slave or DPA Mode

EEPROM for Boot code

* Optional Buffers for off-board LEDs

470W

3.3V

3.3V

3.3V

3.3V

34 Design Guide

Page 35

5.4.4 Reference Clock Generation

A 37.5 MHz reference clock with a +/- 100 ppm accuracy is required for proper operati on of the

GD31244. This is generated from an external oscillator connected directly to the XI input.

Optionally, a 37.5 MHz crystal may be connected between the XI and XO pins with a 20 pF

capacitor from XI to ground and another from XO to ground. The following are th e crystal

characteristics:

• Frequency: 37.5 MHz +/- 100 ppm

• Mode: Fundamental

• Type: Parallel resonant

• ESR: 30 Ohms maximum

• Load Capacitance: 20 pF