Page 1

MF/HF MARINE TRANSCEIVER

iM802

SERVICE

MANUAL

Page 2

INTRODUCTION

This service manual describes the latest service information

for the IC-M802 MF/HF MARINE TRANSCEIVER at the time

of publication.

DANGER

NEVER connect the transceiver to an AC outlet or to a DC

power supply that uses more than 16 V. This will ruin the

transceiver.

DO NOT expose the transceiver to rain, snow or any liquids.

DO NOTre v erse the polarities of the power supply when con-

necting the transceiver.

DO NOT apply an RF signal of more than 20 dBm (100 mW)

to the antenna connector. This could damage the transceiver’s front end.

ORDERING PARTS

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit order numbers

2. Component part number and name

3. Equipment model name and unit name

4. Quantity required

<SAMPLE ORDER>

1110004080 S.IC µPC2709T IC-M802 MAIN UNIT 5 pieces

8810005770 Screw BiH M3×8 ZK IC-M802 Top cover 10 pieces

Addresses are provided on the inside back cover for your

convenience.

REPAIR NOTES

1. Make sure a problem is internal before disassembling the

transceiver.

2. DO NOT open the transceiver until the transceiver is

disconnected from its power source.

3. DO NOT force any of the variable components. Turn

them slowly and smoothly.

4. DO NOT short any circuits or electronic parts. An insu-

lated tuning tool MUST be used for all adjustments.

5. DO NOT keep power ON for a long time when the trans-

ceiver is defective.

6. DO NOT transmit power into a signal generator or a

sweep generator.

7. ALWAYS connect a 50 dB to 60 dB attenuator between

the transceiver and a deviation meter or spectrum analyzer when using such test equipment.

8. READ the instructions of test equipment thoroughly

before connecting equipment to the transceiver.

To upgrade quality, any electrical or mechanical par ts and

internal circuits are subject to change without notice or

obligation.

MODEL

IC-M802

VERSION

U.S.A.

Canada

Other

SYMBOL

USA

CAN

OTH

Page 3

TABLE OF CONTENTS

SECTION 1 SPECIFICATIONS

SECTION 2 INSIDE VIEWS

SECTION 3 CIRCUIT DESCRIPTION

SECTION 4 ADJUSTMENT PROCEDURES

SECTION 5 PARTS LIST

SECTION 6 MECHANICAL PARTS AND DISASSEMBLY

6 - 1 RC-25....................................................................................................................................................... 6 - 1

6 - 2 SP-24....................................................................................................................................................... 6 - 1

6 - 3 HM-135 .................................................................................................................................................... 6 - 1

6 - 4 IC-M802 ................................................................................................................................................... 6 - 1

SECTION 7 SEMI-CONDUCTOR INFORMATION

SECTION 8 BOARD LAYOUTS

8 - 1 HM-135

8 - 1 - 1 SW BOARD ............................................................................................................................ 8 - 1

8 - 1 - 2 MAIN BOARD......................................................................................................................... 8 - 1

8 - 2 RC-25

8 - 2 - 1 JACK BOARD......................................................................................................................... 8 - 1

8 - 2 - 2 CONNECT BOARD ................................................................................................................ 8 - 1

8 - 2 - 3 SENSOR BOARD................................................................................................................... 8 - 1

8 - 2 - 4 VR BOARD............................................................................................................................. 8 - 2

8 - 2 - 5 DISPLAY BOARD................................................................................................................... 8 - 3

8 - 3 IC-M802

8 - 3 - 1 DSP BOARD ............................................................................................................................8 - 5

8 - 3 - 2 MAIN UNIT.............................................................................................................................. 8 - 7

8 - 3 - 3 FILTER BOARD...................................................................................................................... 8 - 9

8 - 3 - 4 PLL UNIT.............................................................................................................................. 8 - 11

8 - 3 - 5 PA UNIT................................................................................................................................ 8 - 12

8 - 3 - 6 DRIVER BOARD................................................................................................................... 8 - 13

8 - 3 - 7 VARISTOR-1 BOARD ........................................................................................................... 8 - 13

8 - 3 - 8 VARISTOR-2 BOARD ........................................................................................................... 8 - 14

SECTION 9 BLOCK DIAGRAM

SECTION 10 WIRING DIAGRAM

SECTION 11 VOLTAGE DIAGRAMS

11 - 1 RC-25 and HM-135......................................................................................................... ........................11 - 1

11 - 2 IC-M802

11 - 2 - 1 MAIN UNIT (1)...................................................................................................................... 11 - 2

11 - 2 - 2 MAIN UNIT (2)...................................................................................................................... 11 - 3

11 - 2 - 3 MAIN UNIT (3)...................................................................................................................... 11 - 4

11 - 2 - 4 PA UNIT................................................................................................................................ 11 - 5

11 - 2 - 5 PLL UNIT (1)......................................................................................................................... 11 - 6

11 - 2 - 6 PLL UNIT (2)......................................................................................................................... 11 - 7

11 - 2 - 7 DSP BOARD......................................................................................................................... 11 - 8

11 - 2 - 8 FILTER BOARD.................................................................................................................... 11 - 9

Page 4

• IC-M802

‘‘

GENERAL

• Frequency coverage :

• Mode : TX/RX J3E (USB/LSB), J2B (AFSK), F1B (FSK), A1A (CW)

H3E [OTH]

RX H3E [USA], [CAN]

DSC J2B [USA], [CAN]

• Antenna impedance : 50 Ω

• Frequency stability : ±10 Hz [USA], [CAN],

±20 Hz [OTH]

• Power supply requirement : 13.6 V DC ±15% Negative ground

• Current drain (at 13.6 V DC) : RX; 3.0 A at Max. output power

TX; 30 A typical at Max. audio output

• Usable temperature range : –20˚C to +55˚C; –4˚F to +131˚F

• Dimensions (projections not included) :

240(W) × 94(H) × 238.4(D) mm; 2 7⁄16(W) × 3 11⁄16(H) × 9 3⁄8(D) in.

• Weight : 4.7 kg; 10.4 lb; 165.8 oz

‘‘

TRANSMITTER

• Output power : 150, 60, 20 W PEP

• Spurious emissions : –62 dB

• Carrier suppressions : 40 dB

• Unwanted sideband suppresion : 55 dB

• Microphone impedance : 600 Ω

‘‘

RECEIVER

• Sensitivity :

(Receiver)

(DSC) [USA], [CAN] : 0 dBµVe.m.f. (J2B; 2.1875, 4.2075, 6.3120, 8.4145, 12.5770, 16.8045 MHz)

• Squelch sensitivity :

• Spurious response rejection : More than 70 dB

• Clarity variable range : ±150 Hz

1 - 1

SECTION 1 SPECIFICATIONS

MODE

J3E, A1A

J2B, F1B

H3E

FREQUENCY

0.5–1.5999 MHz

1.6–1.7999 MHz

1.8–29.9999 MHz

1.6–1.7999 MHz

1.8–29.9999 MHz

1.5–1.5999 MHz

1.6–1.7999 MHz

1.8–3.9999 MHz

20 dB SINAD

30 dBµVe.m.f.

13 dBµVe.m.f.

8 dBµVe.m.f.

13 dBµVe.m.f.

8 dBµVe.m.f.

44 dBµVe.m.f.

30 dBµVe.m.f.

24 dBµVe.m.f.

10 dB S/N

16 dBµV

–1 dBµV

–6 dBµV

–1 dBµV

–6 dBµV

30 dBµV

16 dBµV

10 dBµV

MODE

J3E at 12.230 MHz

H3E at 1.000 MHz

Threshold

Less than +20 dBµV

Less than +30 dBµV

Tight

Less than +90 dBµV

Less than +110 dBµV

Receive

Transmit

DSC receive

[USA], [CAN]

500 kHz–29.9999 MHz

1.6000–2.9999 MHz 4.0000–4.9999 MHz

6.0000–6.9999 MHz 8.0000–8.9999 MHz

12.0000–13.9999 MHz 16.0000–17.9999 MHz

18.0000–19.9999 MHz 22.0000–22.9999 MHz

25.0000–27.5000 MHz

2.1875 MHz, 4.2075 MHz, 6.3120 MHz, 8.4145 MHz,

12.5770 MHz, 16.8045 MHz

Page 5

1 - 2

• RC-25 Remote controller

‘‘

GENERAL

• Microphone impedance : 600 Ω

• Audio output power : More than 5 mW at 16 Ω headphone with 10 % distortion

• Audio output impedance : 8–16 Ω

• Usable temperature range : –20˚C to +55˚C; –4˚F to +131˚F

• Dimension (projections not included) : 220(W)

× 110(H) × 84.4(D) mm; 8 21⁄32(W) × 4 11⁄32(H) × 3 5⁄16(D) in.

• Weight : 570 g; 1.3 lb; 20.1 oz

• SP-24 External speaker

‘‘

GENERAL

• Impedance : 4 Ω

• Input power : Rated input; 5 W

Maximum input; 7 W

• Usable temperature range : –20˚C to +60˚C; –4˚F to +140˚F

• Dimension (projections not included) : 110(W)

× 110(H) × 84.4(D) mm; 4 11 ⁄32(H) × 4 11 ⁄32(H) × 3 5⁄16(D) in.

• Weight : 370 g; 0.82 lb; 13.1 oz

All stated specifications are subject to change without notice or obligation.

Page 6

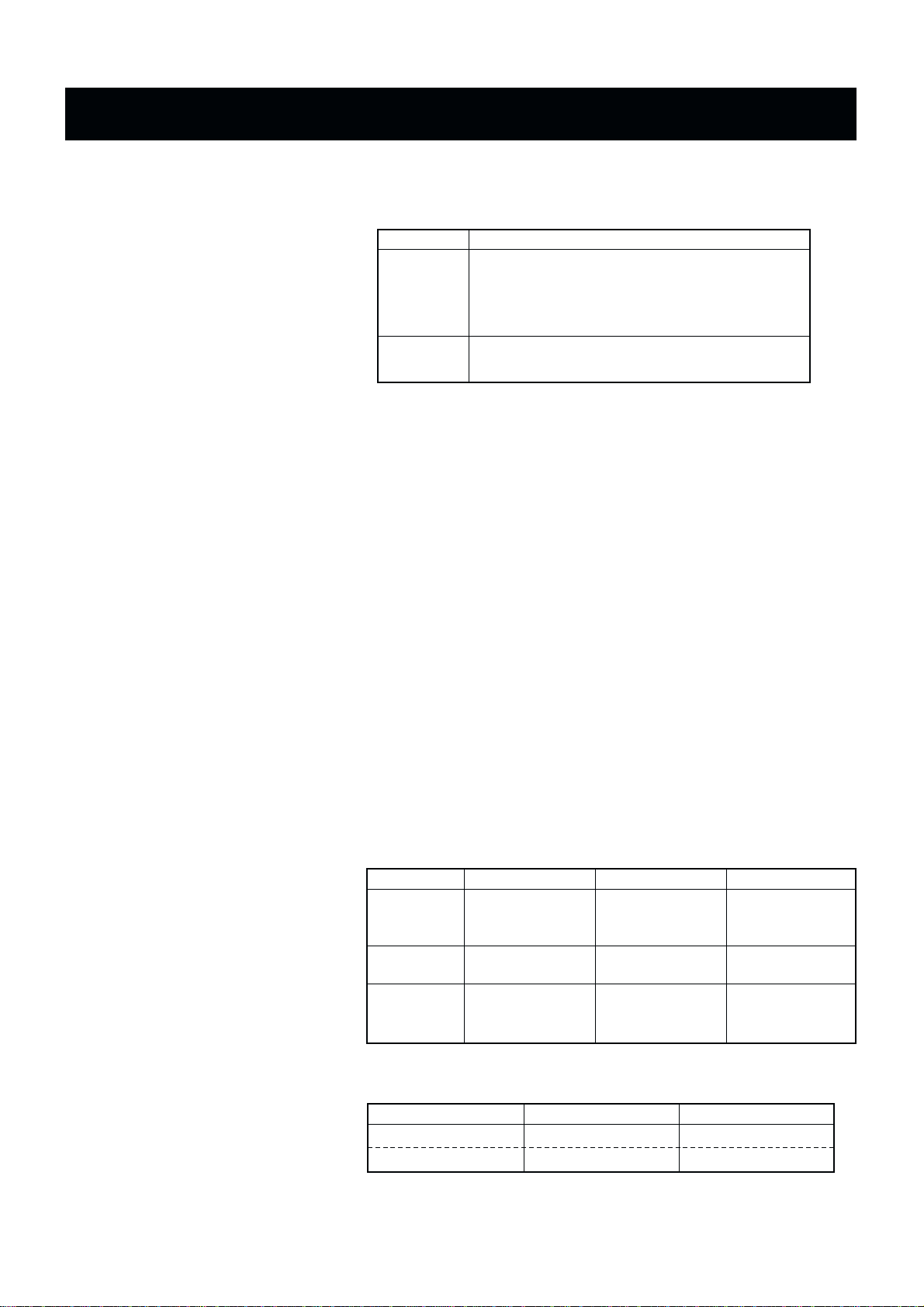

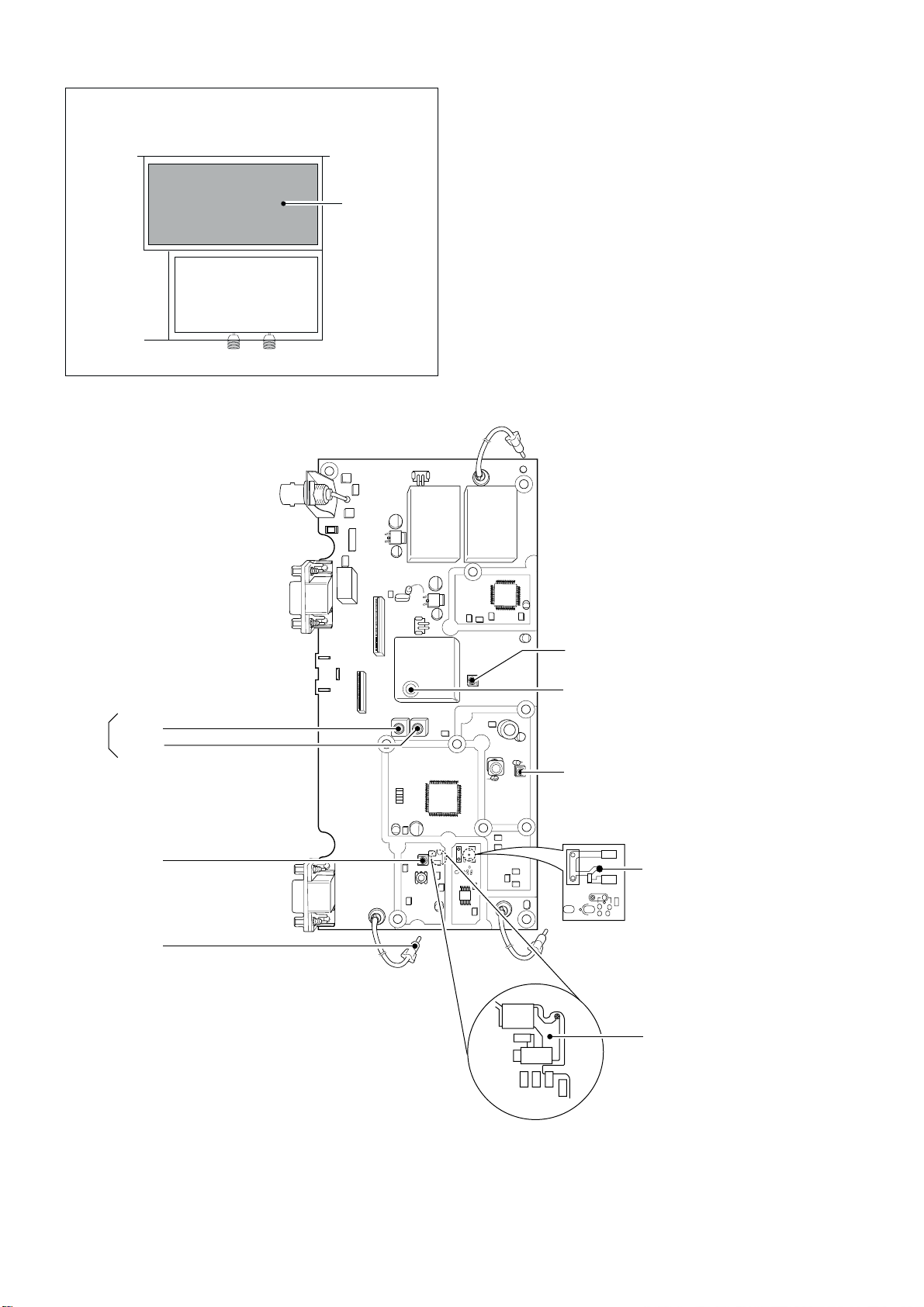

SECTION 2 INSIDE VIEWS

2 - 1

• RC-25

• IC-M802

VR BOARD

Reset IC

(IC8202: S-80942ANMP)

CPU

(IC8201: HD64F2134AFA20)

LCD unit

(DS8220: HLC770-018800)

Power amplifier

(IC8270: TA7368F)

DISPLAY BOARD

SENSOR BOARD

VR BOARD

Reset IC

(IC8202: S-80942CNMC)

CPU

(IC8201: HD64F2134AFA20)

LCD unit

(DS8220: HLC7700-018800)

Power amplifier

(IC8270: TA7368F)

DISPLAY BOARD

SENSOR BOARD

MAIN UNIT

DSP BOARD

CPU

(IC3303: M30624MGA)

2nd mixer

(D302: HSB88WS)

1st mixer circuit

1st IF amplifier

(Q203: 3SK131)

MAIN UNIT

DSC 1st mixer

D2301: HSB88WS

[USA],[CAN] only

DSC 2nd mixer

IC2701: TA4107F

[USA],[CAN] only

DSP BOARD

CPU

IC3303: M30624FGAFP

[USA],[CAN]

M30620FCAFP

[OTH]

2nd mixer

(D302: HSB88WS)

1st mixer circuit

1st IF amplifier

(Q203: 3SK131)

PA UNIT

VARISTOR-2 BOARD

VARISTOR-1 BOARD

FAN controller

(IC6501: TS522ID)

DRIVER BOARD

Page 7

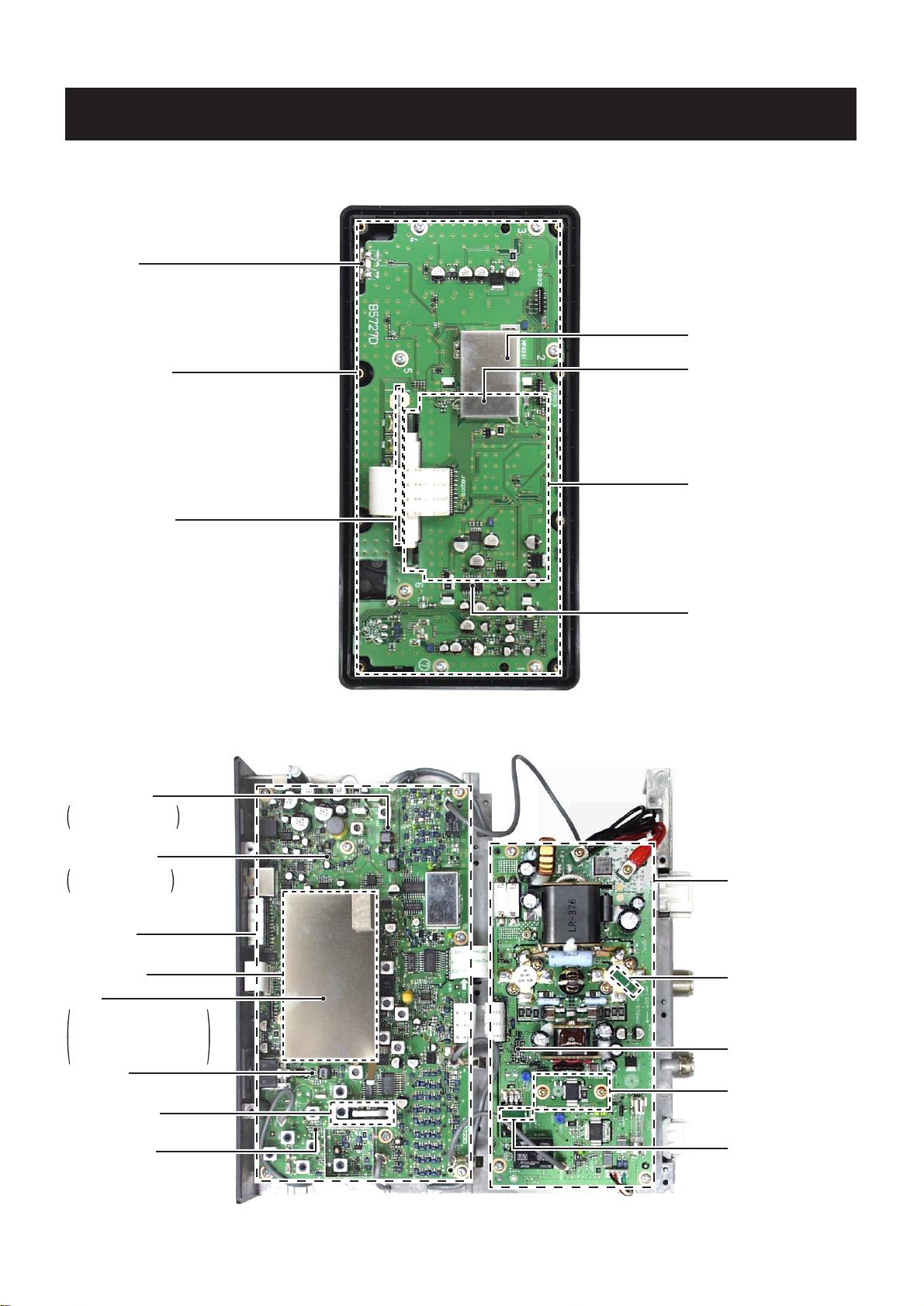

3 - 1

SECTION 3 CIRCUIT DESCRIPTION

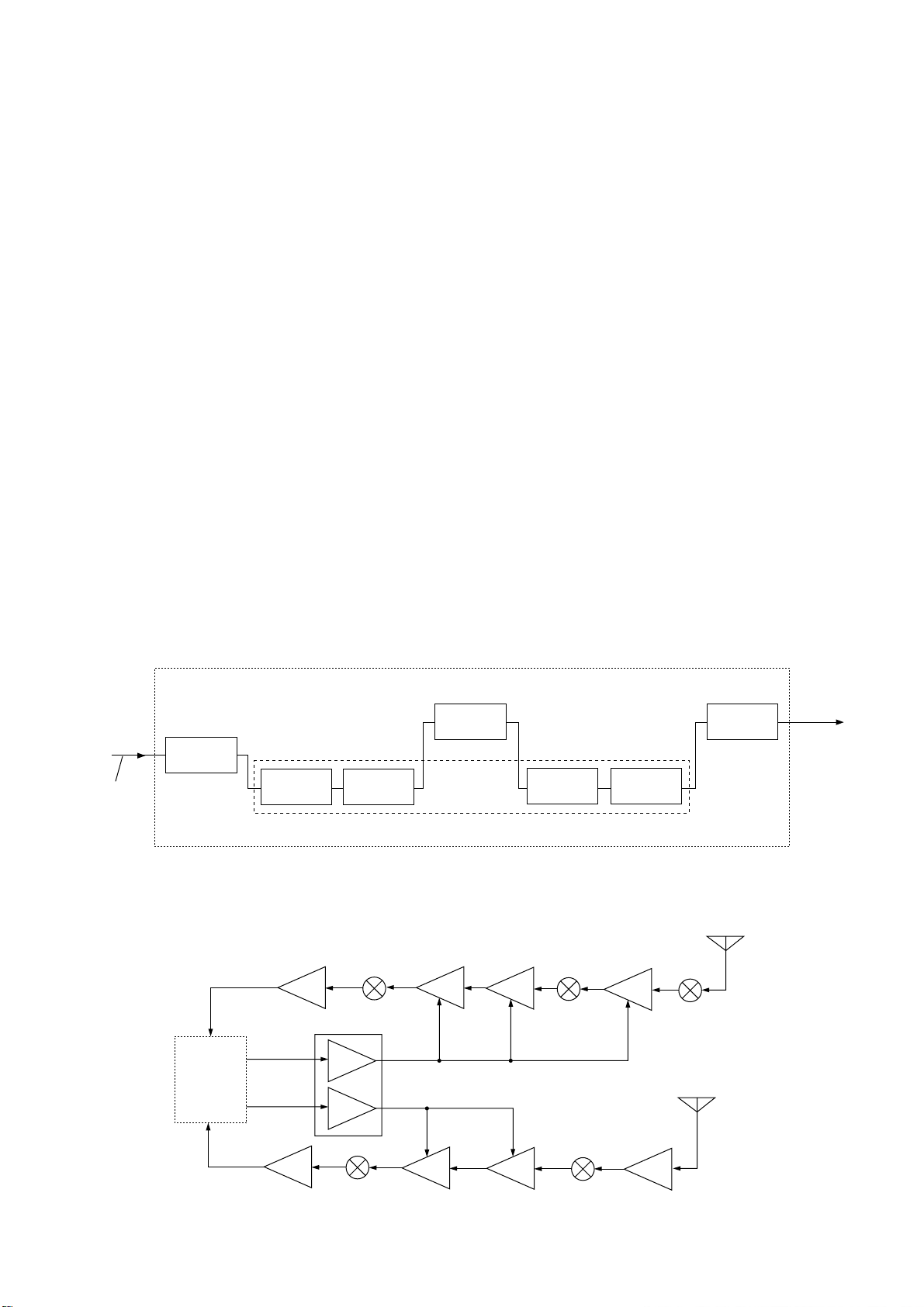

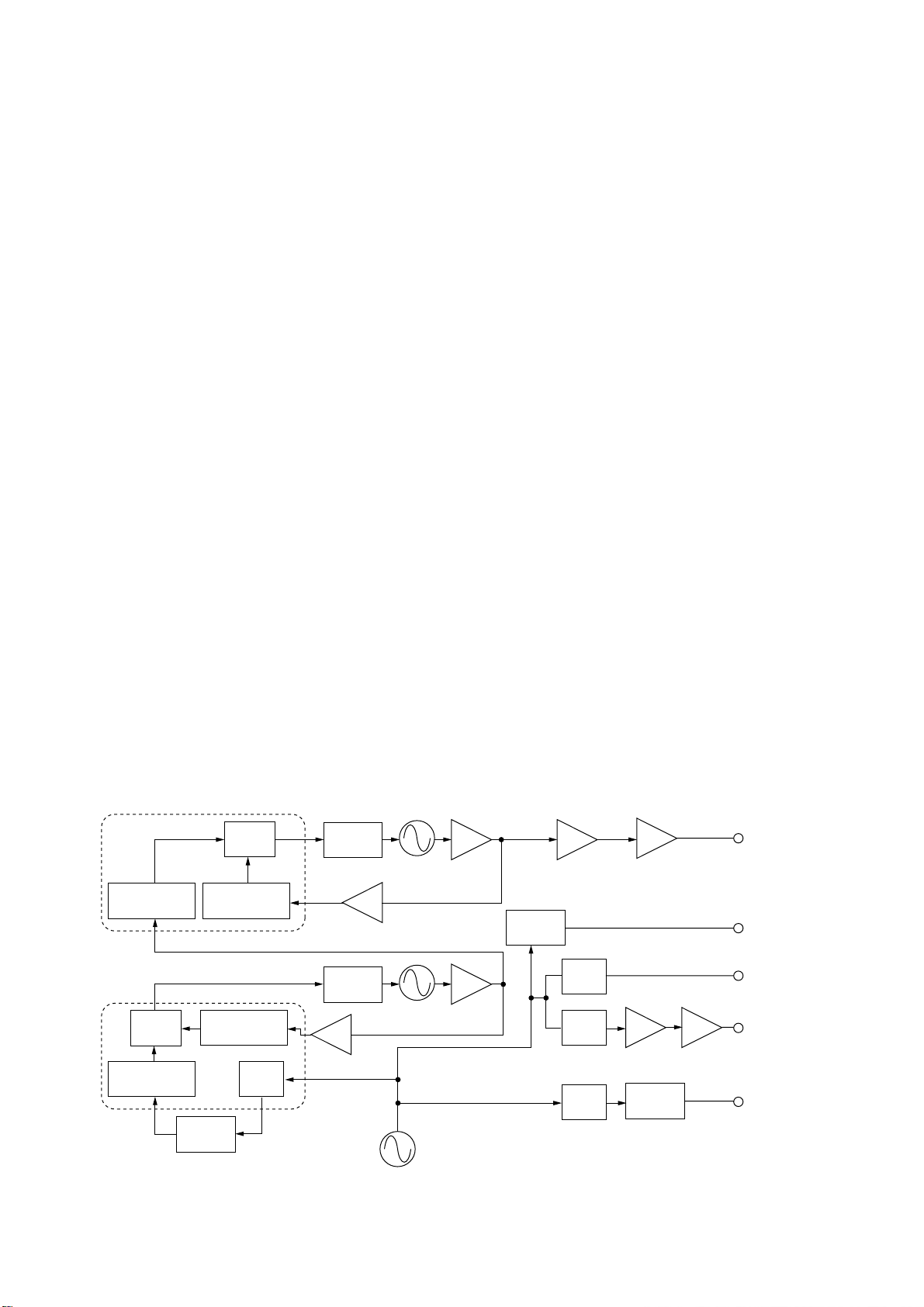

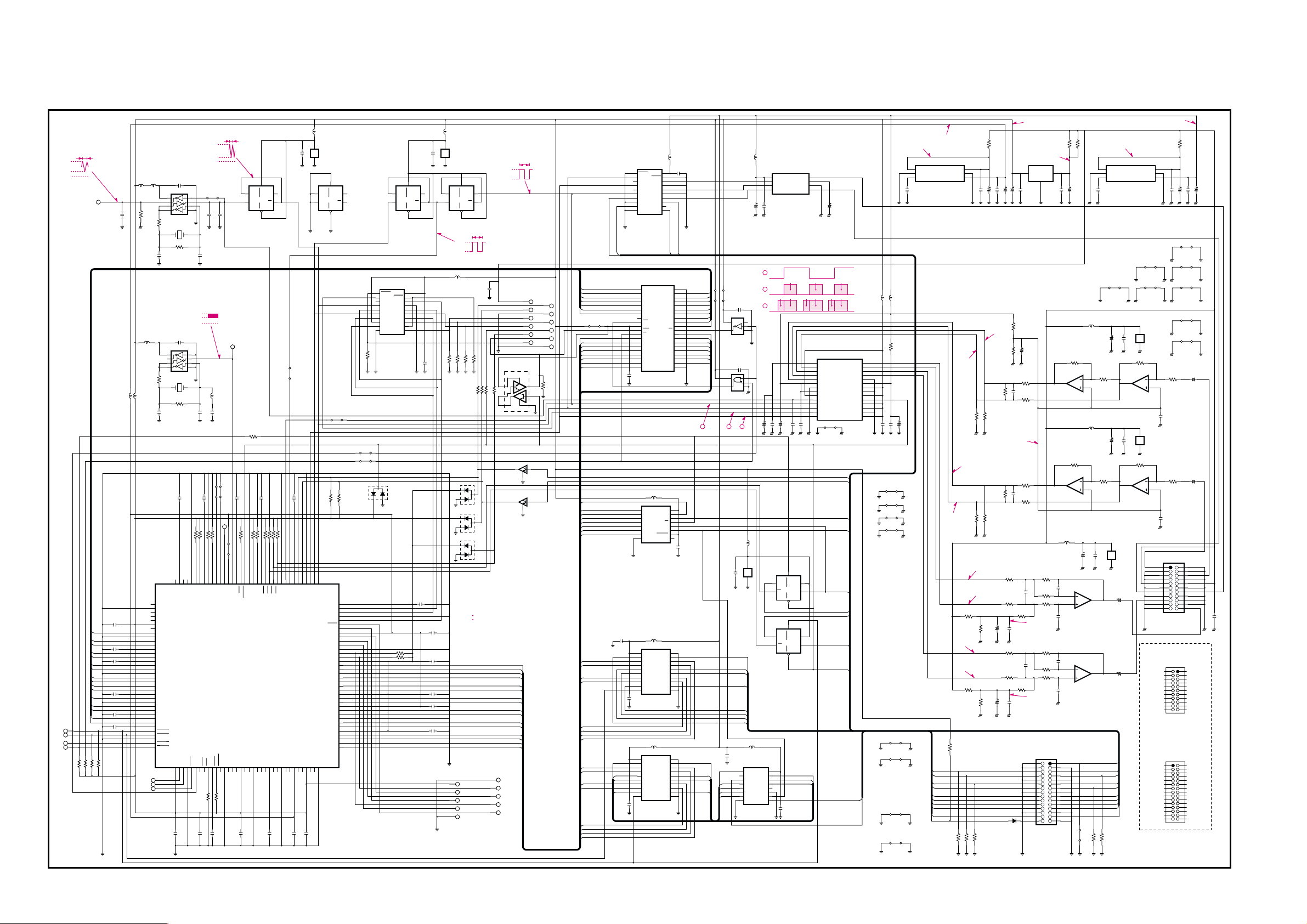

3-1 RECEIVER CIRCUITS

3-1-1 RF FILTER CIRCUIT (FILTER AND MAIN

UNITS)

Received signals from the antenna connector are applied to

the transmit/receive switching and protection relay (FILTER

unit; RL7301) which is controlled by the CPU via the “TRXS”

line. The signals pass through the 30 MHz cut-off low-pass

filter (FILTER unit; L7321, C7321–C7323, C7325), and then

applied to the MAIN unit via the J7321.

The signals pass through the transmit/receive switch (D53)

and 1.6 MHz cut off high-pass filter (L51–L54, C54, C56,

C57, C59, C61–C64), and are then applied to one of the

bandpass filters (including one low-pass filter for below 2.0

MHz). These filters are selected by the filter control signals

(B0–B8) as described in the table below.

The filtered signals pass through the 33 MHz cut-off lowpass filter (L202, L203, C202–C206), and are then applied

to the 1st mixer circuit (Q201, Q202).

3-1-2 1ST MIXER AND IF CIRCUITS (MAIN UNIT)

The 1st mixer circuit converts the received signals into a

fixed frequency, 64.445 kHz 1st IF signal using PLL output

frequency. By changing the PLL frequency, only the desired

frequency is picked up at the pair of crystal filters (FI301a,

FI301b) via the 64.445 kHz bandpass filter (FI201) at the

next stage.

The IF amplifier (Q203) and resonator circuits are designed

between the filter pair. The PLL output signal (1LO) enters

the MAIN unit via the J601 and is amplified at the 1st LO

amplifier (Q601). The amplified signal is passed through the

100 MHz cut-off low-pass filter (L604, L605, C604,

C606–C610) to suppress harmonics components, and then

applied to the 1st mixer circuit (Q201, Q202).

3-1-3 2ND MIXER AND IF CIRCUITS (MAIN UNIT)

The 1st IF signal from the crystal filter (FI301b) is converted

again into a 455 kHz 2nd IF signal at the 2nd mixer circuit

(D302, L303, L304). The 2nd LO signal (2LO) from the PLL

unit enters the MAIN unit via the J301 to be applied to the

2nd mixer circuit.

3-1-4 3RD MIXER AND IF CIRCUITS (MAIN UNIT)

The 2nd IF signal passes through the low-pass filter (L305,

L306, C307–C311), and then applied to the IF amplifier

(Q401) via the ceramic bandpass filter (FI401). The amplified signal passes through the ceramic bandpass filter

(FI402), and then applied to the 3rd mixer circuit via the IF

amplifier (Q501). The 2nd IF signal is converted into a 12

kHz 3rd IF signal at the 3rd mixer circuit (IC501). The 3rd LO

signal (3LO) from the PLL unit enters the MAIN unit via the

J3601 to be applied to the 3rd mixer circuit.

3-1-5 DSP RECEIVER CIRCUIT (MAIN AND DSP

UNITS)

The DSP (Digital Signal Processor) circuit enables digital IF

filter, digital noise reduction, digital PSN (Pulse Shift

Network), phase demodulation, digital automatic notich, and

etc.

The 3rd IF signal is applied to the IF amplifier (MAIN unit;

IC1002, pin 5) after being passed through the low-pass filter

(MAIN unit; IC1002, pins 3, 1). The amplified 12 kHz 3rd IF

signal is amplified at the differential amplifiers (IC651a/b),

and is then applied to the A/D convertor section in the

CODEC IC (IC501) on the DSP board (EX-2432). At the

same time, the converted signal is level-shifted 5 V to 3.3 V

in the IC (IC501).

LPF

Antenna

FILTER unit

to transmit/receiver switch

LPF

FI301A

FI301B

FI401

FI402

Q401

Q5013rd mixer

IC501

IC1002

1st mixer

Q201

Q202

2nd mixer

Q201

Q202

1st LO

64—94 MHz

BPF

2—30 MHz

0.5—1.9999 MHz

BPF

Crystal

BPF

Crystal

IF

amp.

BPF

Crystal

LPF

IF

amp.

IF

amp.

DSP

UNIT

2nd LO

64 MHz

3rd LO

443 kHz

Frequency (MHz)

0.5–1.999

2–2.999

3–4.999

5–6.999

7–9.999

10–13.999

14–17.999

18–19.999

20–21.999

22–23.999

24–29.999

BPF ctrl signal

B0

B1

B2

B3

B4

B5

B6

B7

B8

LPF ctrl signal

L0

L1

L2

L3

L4

L5

L6

L7

• RECEIVER CONSTRUCTION

Page 8

3 - 2

The level-shifted signal is applied to the DSP IC (IC301) for

the digital IF filter, demodulator, automatic notch and noise

reduction, etc.

The output signal from the DSP IC is applied to the D/A converter section in the CODEC IC (IC501) to convert into the

analog audio signals. Also the signals are level-shifted 3.3 V

to 5 V at the level converter section in the IC (IC501).

The level-shifted audio signals are passed through the

active filter (IC701a), and then applied to the MAIN unit via

J901 (pin 17) as the DRAF signal.

3-1-6 AGC CIRCUIT (DSP AND MAIN UNITS)

The AGC (Automatic Gain Control) circuit reduces IF amplifier gain and attenuates IF signal to keep the audio output at

a constant level.

The receiver gain is determined by the voltage on the AGC1

line from the DSP unit. The D/A converter for the AGC

(IC102) supplies control voltage to the AGC1 line and sets

the receiver gain with the [RF/SQL] control.

The 3rd IF signal from the CODEC IC (IC501) is detected at

the AGC detector section in the DSP IC (IC301). The output

signal from the DSP IC is level-shifted at the level converter

(IC101) and applied to the D/A converter (IC102). The AGC

voltage is amplified at the buffer amplifier section in the

IC102 and applied to the MAIN unit to control the AGC1 line.

When receiving strong signals, the detected voltage increases and the AGC1 voltage decreases. As the AGC1 voltage

is used for the bias voltage of the IF amplifiers (MAIN unit;

Q203, Q401, Q501), IF amplifier gain is decreased.

3-1-7 AF AMPLIFIER CIRCUIT (DSP AND MAIN

UNITS)

The AF amplifier amplifies the audio signals to the suitable

driving level for the speaker.

The AF signals from the DSP unit are passed through the

transmit/receive switch (MAIN unit; IC1703, pins 1, 6) via the

“DSPO1” signal, and then applied to the AF amplifier (MAIN

unit; IC1702, pin 5) after being passed through the low-pass

filter (MAIN unit; IC1702, pins 3, 1). The amplified signal

passes through the the SQL gate (MAIN unit; IC1701, pins

7, 1) which is controlled by the CPU (IC3303, pin 49) via the

“SQLC” signal. The signal is applied to the electronic volume

IC (MAIN unit; IC1603, pin 2) which can control the volume

attenuation by AFG voltage from the CPU (MAIN unit;

IC3303). Beep, tone, side tone, monitor signals are applied

to the the elecronic volume IC too. The signal is applied to

the AF mute swtich, and then amplified at the AF power

amplifier (IC1601, pin 1). The amplified signal is applied to

the speaker (SP-24) after being passed through the speaker jack (J1451) via the “AFO” signal.

DSP

UNIT

IC1101

AGC1

2

6

1

7

AGC2

AGC

AGC

IC1002

DSPI1

IF

amp.

IC2702

DSPI2

AMP.

Q2502

IF

amp.

Q2401

IF

amp.

Q2301

Q2302

RF

amp.

Q501

IF

amp.

Q401

IF

amp.

Q203

From the

antenna

IF

amp.

From the

DSC antenna

Differential

converter

IC651b/a

DSP UNITMAIN UNIT

CODEC IC (IC501)

IC301 IC701a

DSPO1

AF

signals

DSPI1

(12 kHz)

3rd IF

signal

A/D

converter

D/A

converter

Level

converter

Active

filter

Level

converter

DSP IC

• DSP CIRCUIT

• AGC CIRCUIT

Page 9

3 - 3

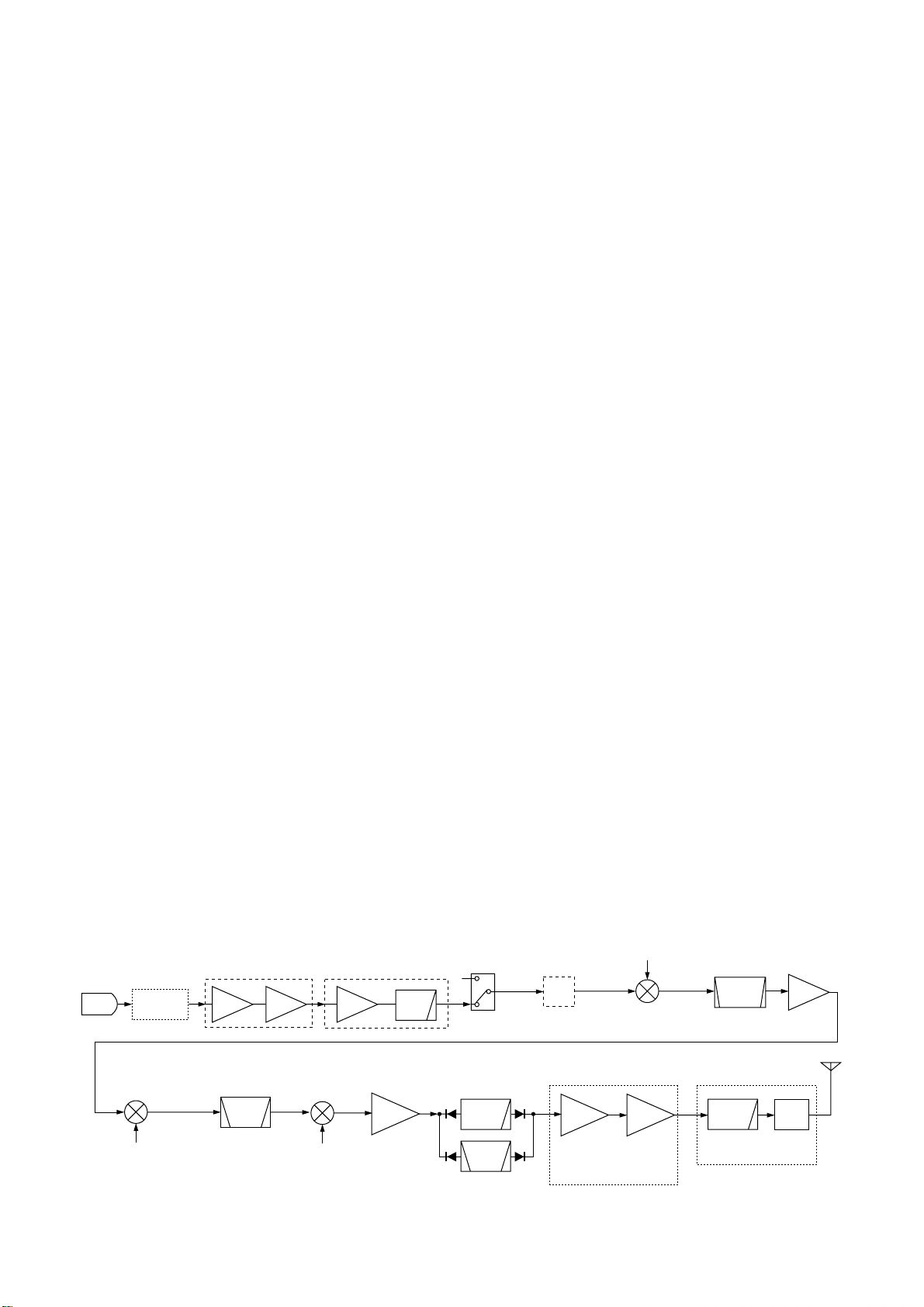

3-2 TRANSMITTER CIRCUITS

3-2-1 MICROPHONE AMPLIFIER CIRCUIT

(RC-25, MAIN AND DSP UNITS)

The microphone amplifier circuit amplifies microphone audio

signal to a level needed for the DSP circuit.

Audio signals from the [MIC] connector (J8701, pin 1) are

amplified at the AF amplifier (IC8280, pin 3), and then

applied to the gate modulator IC (MAIN unit; IC2001, pin 3)

via the J2051, pin 1 as “FMOD” signal. The signal is applied

to the DSP unit after being passed through the limitter amplifier and low-pass filter IC (MAIN unit; IC1051, pins 3, 7) as

“DSPI1” signal.

3-2-2 DSP TRANSMITTER CIRCUIT (DSP UNIT)

The DSP (Digital Signal Processor) circuit enables PSN

(Phase Shift Network)/Low Power/Phase modulator, transmitter monitor, side tone, and etc.

The microphone audio signals from the MAIN unit via the

“DISPI1” line are amplified at the differential amplifiers

(IC651a/b), and are then applied to the A/D converter section in the CODEC IC (IC501). at the same time, the converted signals are level-shifted 5 V to 3.3 V in the IC (IC501).

The level shifted signals are applied to the DSP IC (IC301)

and modulated at the DSP IC to p[roduce the 12 kHz transmitter IF signal.

The modulated IF signal from the DSP IC is applied to the

D/A convertor section in the CODEC IC (IC501) to convert

into the analog IF signal. Also the signal is level-shifted 3.3

V to 5 V at the level converter section in the IC (IC501).

The level-shifted IF signal is passed through the active filter

(IC701a), and then applied to the MAIN unit via J901 (pin

17) as the “DSPO1” signal.

3-2-3 SPEECH COMPRESSOR CIRCUIT

(DSP UNIT)

The DSP (Digital Signal Processor) circuit enables PSN

The speech compressor compresses the transmitter audio

input signals to increase the average output level (average

talk power).

When the speech compressor function is ON, the level-shifted signal from the CODEC IC (IC501) is applied to the DSP

IC (IC301) and compressed at the DSP IC to obtain an average audio level.

At the same time, the compressed signals are modulated at

the DSP IC and applied to the D/A converter section in the

CODEC IC (IC501).

3-2-4 IF AMPLIFIER AND MIXER CIRCUITS

(MAIN UNIT)

The modulated 3rd IF signal from the DSP unit (“DSPO1”

signal: 12 kHz) passes through the transmit/receive swtich

(IC1703, pins 1, 5), and then applied to the 3rd mixer circuit

(IC901, pin 3). The applied 3rd IF signal is mixed with the

3rd LO signal from the DDS circuit (PLL unit; IC5701) to produce a 455 kHz 2nd IF signal.

The 2nd IF signal is output from IC901, pin 5 and passes

through the ceramic bandpass filter (FL402) to suppress the

unwanted signals via the D404. The filtered 2nd IF signal is

amplified at the 2nd IF amplifier (Q801), and then applied to

the 2nd mixer circuit after being passed through the D303

and low-pass filter (L304–L306, C304–C311, R306).

The 2nd IFsignal is mixed with 64 MHz 2nd LO signal, coming from the PLL circuit, at the 2nd mixer circuit (D302) to

obtain 64.455 MHz 1st IF signal. The 1st IF signal is passed

through the crystal bandpass filter (FI301A, FI301B) to cut

off the unwanted signals. The signal is applied to the transmitter mixer circuit (Q702, Q703) to obtain the desired signal via the transmit/receive switch (D301) and attenuator.

The operating (transmitting) frequency is produced at the 1st

IF mixer circuit (Q210, Q202) by mixing the 1st IF and 1st

LO signals. The mixed signal is then applied to the RF circuit.

FI402

Q801

MIC

BPF

Ceramic

LPF

6

IC1001

DSPI1 DSPO1

(12 kHz)

455 kHz

3rd LO

(443 kHz)

DSP

UNIT

IC1051IC2001

Controller

7

1

3

1

57

AMP. AMP.VCA

AMP.

2nd mixer

D302

2nd LO (64.00 MHz)

FI301b/a

64.455 kHz

Bandwidth:

15 kHz

Q401

BPF

Crystal

RF

amp.

1st mixer

Q702, Q703

1st LO

(64—94 MHz)

LPF

BPFs

2—30 MHz

0.5—1.9999 MHz

IC1

YGR

LPFs

PA UNIT FILTER UNIT

Antenna

D7271,

D7272

PWR

DET

Q6101, Q6801,

Q6851, Q6401,

Q6402

AMPs

• TRANSMIT CONSTRUCTION

Page 10

3 - 4

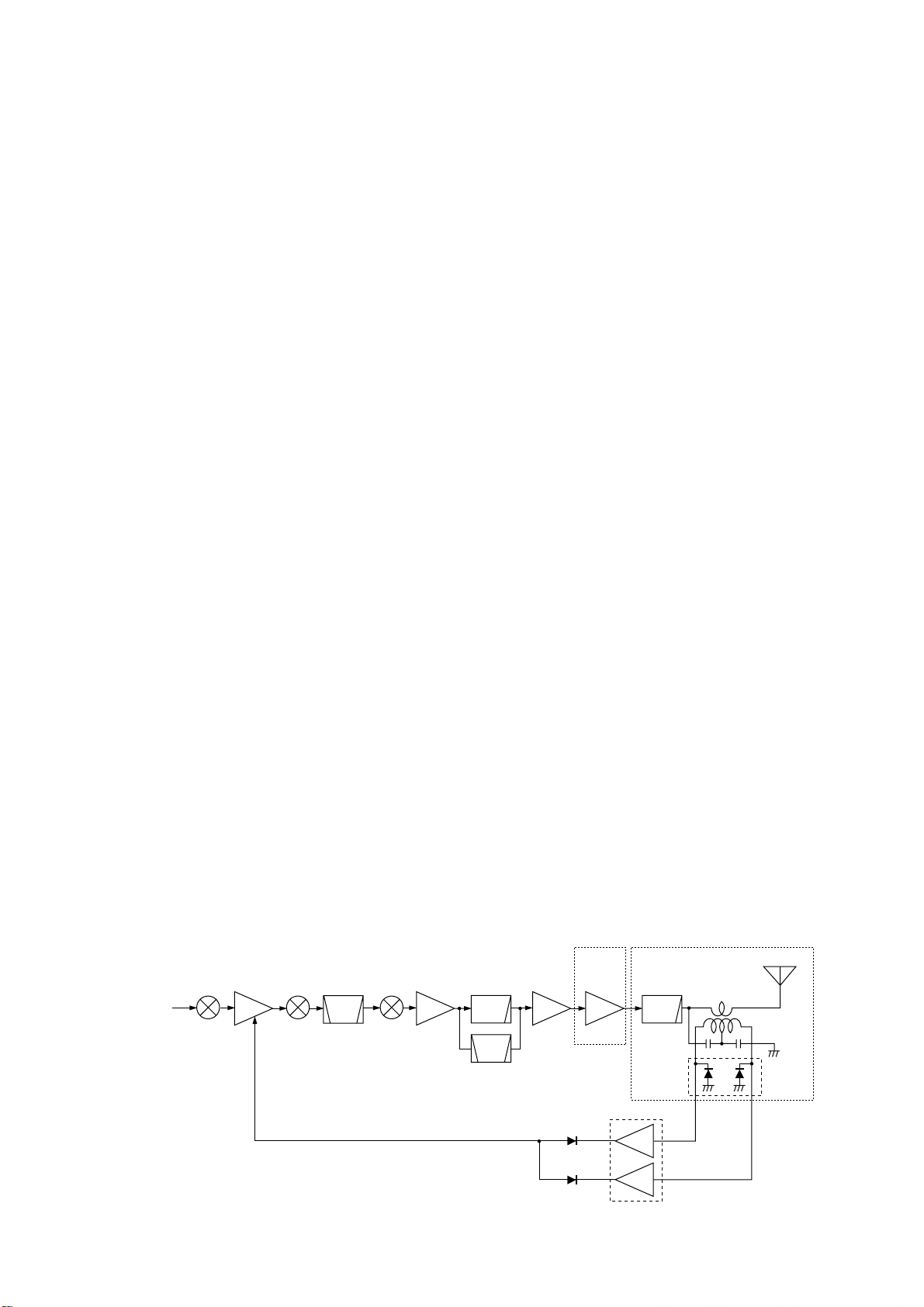

3-2-5 RF CIRCUIT (MAIN, PA UNITS AND DRIVER

BOARD)

The RF circuit amplifies operating (transmitting) frequency

to obtain 150 W of RF output.

The signal from the 1st IF mixer is passed through one of the

low-pass filter or bandpass filters (Refer to page 4-1 bandpass filters used), and then applied to the YGR amplifier

(IC1, pin 1) after being passed through the attenuator

(R5–R7). The amplified signal passes through the low-pass

filter (L1–L3, C1–C7) and attenuator (R1–R3), and then

applied to the PA unit via J1.

The signal applied from the MAIN unit is amplified at 2

amplifiers (PA unit; Q6101 and Q6801). A part of output signal from 2 amplifiers are applied to the amplifiers to improve

the frequency characteristic by feedback. The amplified signal is applied to the drive amplifier (DRIVER board; Q6851)

via the J6301 as “DRVI” signal. The signal from the DRIVER

board passes through the impedance converter (PA unit;

L6301), and then applied to push-pull amplifiers (PA unit;

Q6401, Q6402) to obtain a stable 150 W of RF output

power. A part of the RF output power returns to the amplifiers to obtain a stable gain between 1.6 MHz and 27.5 MHz

bands by using feedback transformer (L6404). The output

power is applied to the filter unit via the J6401 as “FLIN” signal.

The amplified signal is applied to the one of the 8 low-pass

filters which are composed chebychev type.

• 1.6–1.9999 MHz signal

The signal is applied to the relay (FILTER unit; RL7031)

which is controlled by the band control IC (MAIN unit;

IC3602) as the “L1M” signal via the buffer amplifier (MAIN

unit; IC1301, pin 11). The signal passes through the lowpass filter (FILTER unit; L7036–L7038, C7033–C7039,

C7041–C7045, C7049), and then applied to the RL7032.

• 2–2.9999 MHz signal

The signal is applied to the relay (FILTER unit; RL7061)

which is controlled by the band control IC (MAIN unit;

IC3602) as the “L2M” signal via the buffer amplifier (MAIN

unit; IC1301, pin 12). The signal passes through the lowpass filter (FILTER unit; L7066–L7068, C7063–C7084,

C7086, C7087), and then applied to the RL7062.

• 3–4.9999 MHz signal

The signal is applied to the relay (FILTER unit; RL7091)

which is controlled by the band control IC (MAIN unit;

IC3602) as the “L4M” signal via the buffer amplifier (MAIN

unit; IC1301, pin 12). The signal passes through the lowpass filter (FILTER unit; L7096–L7098, C7094–C7096,

C7098–C7101, C7105–C7107), and then applied to the

RL7092.

• 5–6.9999 MHz signal

The signal is applied to the relay (FILTER unit; RL7121)

which is controlled by the band control IC (MAIN unit;

IC3602) as the “L6M” signal via the buffer amplifier (MAIN

unit; IC1301, pin 14). The signal passes through the lowpass filter (FILTER unit; L7126–L7128, C7124–C7132,

C7136, C7137), and then applied to the RL7122.

• 7–9.9999 MHz signal

The signal is applied to the relay (FILTER unit; RL7151)

which is controlled by the band control IC (MAIN unit;

IC3602) as the “L8M” signal via the buffer amplifier (MAIN

unit; IC1301, pin 15). The signal passes through the lowpass filter (FILTER unit; L7066–L7068, C7063–C7084,

C7086, C7087), and then applied to the RL7152.

• 10–13.9999 MHz signal

The signal is applied to the relay (FILTER unit; RL7181)

which is controlled by the band control IC (MAIN unit;

IC3602) as the “L12M” signal via the buffer amplifier (MAIN

unit; IC1301, pin 16). The signal passes through the lowpass filter (FILTER unit; L7182–L7184, C7183–C7188,

C7193), and then applied to the RL7182.

Antenna

power

detector

LPF

LPF

Filter: L0

1.6—1.9999 MHz

Filter: L1

2—2.9999 MHz

Filter: L2

3—4.9999 MHz

Filter: L3

5—6.9999 MHz

Filter: L4

7—9.9999 MHz

Filter: L5

10—13.9999 MHz

Filter: L6

14—19.9999 MHz

Filter: L7

low-pass filter control signals

from the MAIN unit

20—29.9999 MHz

LPF

LPF

LPF

LPF

LPF

LPF

(L1M, L2M, L4M, L6M, L8M, L16M, L22M)

Transmitter signals

from the PA unit.

• RF FILTER CIRCUIT

Page 11

3 - 5

• 14–19.9999 MHz signal

The signal is applied to the relay (FILTER unit; RL7211)

which is controlled by the band control IC (MAIN unit;

IC3602) as the “L16M” signal via the buffer amplifier (MAIN

unit; IC1301, pin 17). The signal passes through the lowpass filter (FILTER unit; L7216–L7218, C7214, C7216,

C7217, C7221–C7225), and then applied to the RL7212.

• 20–29.9999 MHz signal

The signal is applied to the relay (FILTER unit; RL7241)

which is controlled by the band control IC (MAIN unit;

IC3602) as the “L22M” signal via the buffer amplifier (MAIN

unit; IC1301, pin 18). The signal passes through the lowpass filter (FILTER unit; L7245, L7246, L7248,

C7242–C7244, C7247–C7249, C7253, C7254), and then

applied to the RL7242.

The filtered signal is applied to the antenna connector after

being passed through the RL7301 and J7311.

3-2-6 ALC CIRCUIT (FILTER AND MAIN UNITS)

The ALC (Automatic Level Control) circuit controls the gain

of IF amplifiers in order for the transceiver to output a constant RF power set by the [RF PWR] control even when the

supplied voltage shifts, etc.

The RF power level is detected at the power detector circuit

(Filter unit; D7271) to be converted into DC voltage and

applied to the MAIN unit as the FOR signal.

The FOR signal is applied to the comparator (IC1201, pin 2).

The “POCV” signal, controlled by the [RF PWR] control via

the I/O expander (IC3606, pin 5), is also applied to the other

input (pin 3) for reference. The compared signal is output

from pin 1 and applied to the IF amplifier in the MAIN (Q801)

unit to control amplifying gain.

When the FOR signal exceeds the POCV voltage, ALC bias

voltage from the comparator controls the IF amplifiers. This

adjusts the output power to a specified level from the [RF

PWR] control until the FOR and POCV voltages are equalized.

3-2-7 APC CIRCUIT (FILTER AND MAIN UNITS)

The APC (Automatic Power Control) circuit protects the

power amplifiers on the PA unit from high SWR and excessive current.

• SWR APC CIRCUIT (FILTER AND MAIN UNITS)

The reflected wave signal appears and increases on the

antenna connector. When the antenna is mismatched,

D7272 of the power detector circuit (D7271, D7272, L7272)

in the FILTER unit detects the signal and applies it to the

ALC amplifier (IC1201, pin 9) in the MAIN unit as “REF” signal. The output signal decreases the bias voltage of the RF

APC amplifier to reduce the output power.

• CURRENT APC CIRCUIT (FILTER AND MAIN UNITS)

The power transistor current is detected from the different

voltage between both terminals of a 0.012 Ω resistor

(R6651) on the PA board. The detected voltage is applied to

the differential amplifier (IC6501). When the current of the

final transistors is more than 30 A, the detected voltage is

applied to the APC amplifier controller (IC1201) in the MAIN

unit to reduce the gate-2 voltage of the IF amplifier (Q801)

and thus reduce the output power.

3-2-8 RF METER CIRCUIT (MAIN UNIT)

The output of ALC amplifier (IC1201, pin 12) is applied to the

CPU (IC3303, pin 97) as “RFML” signal to indicate the transmit power level on the display.

For antenna current meter indication, the “ANTM” signal

from the optional AT-130E is applied to the meter amplifier

(IC1201, pin 12) via the J6701 in the PA unit.

3-2-9 MONITOR CIRCUIT (DSP AND MAIN UNITS)

The micorphone audio signals can be monitored to check

voice characteristics.

A portion of the transmit IF signal from the DSP IC (IC301)

is mixed with a 12 kHz LO signal to demodulate into the AF

signals. The demodulated signals are level-shifted 3.3 V to

5 V at the level converter (IC102) to convert into the analog

AF signals. The AF signals are then applied to the MAIN unit

as “MONI” signal.

The “MONI” signal from the DSP unit is amplified at the AF

amplifier (MAIN unit; IC1603, pin 2), and then applied to the

VCA amplifier to control the AF volume (pin 7). The amplified

signal passes through to the AF mute circuit (MAIN unit;

IC1602, pins 1, 7) which is controlled by the CPU via the

expander IC (MAIN unit; IC3603) as the “AFMS” signal. The

AF signal is applied to the AF power amplifier circuit (MAIN

unit; IC1601, pin 1) to drive a speaker.

2

D7271

D7272

IC1201

9

1

8

LPF LPFs

BPFs

ALC

ALC amplifier

Antenna

FILTER UNITPA

UNIT

Power

detector

IF

ALC

Q801

TX

signals

Crystal

BPF

3rd mixer 2nd mixer 1st mixer

RF YGR PA

ALC

• ALC CIRCUIT

Page 12

3 - 6

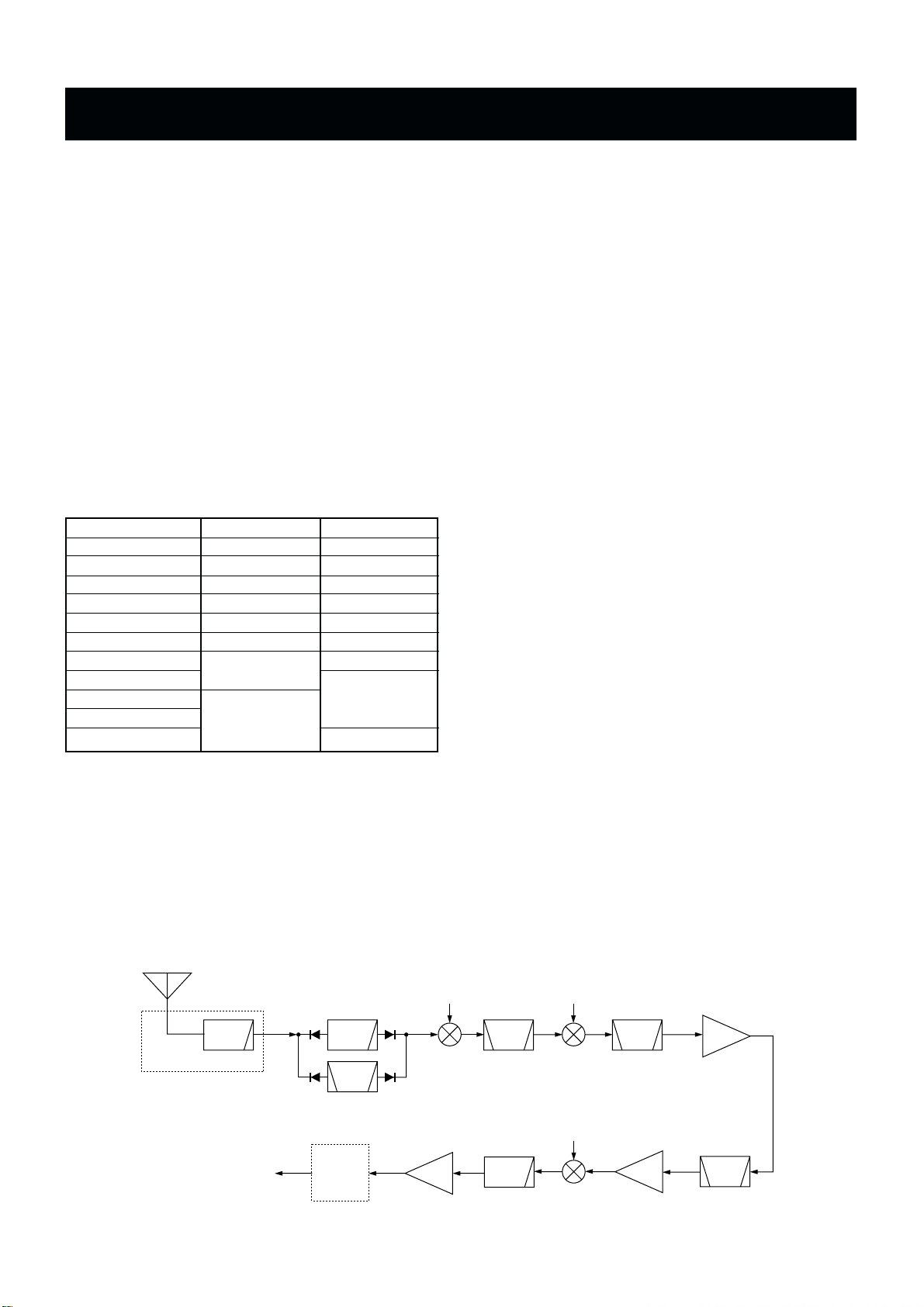

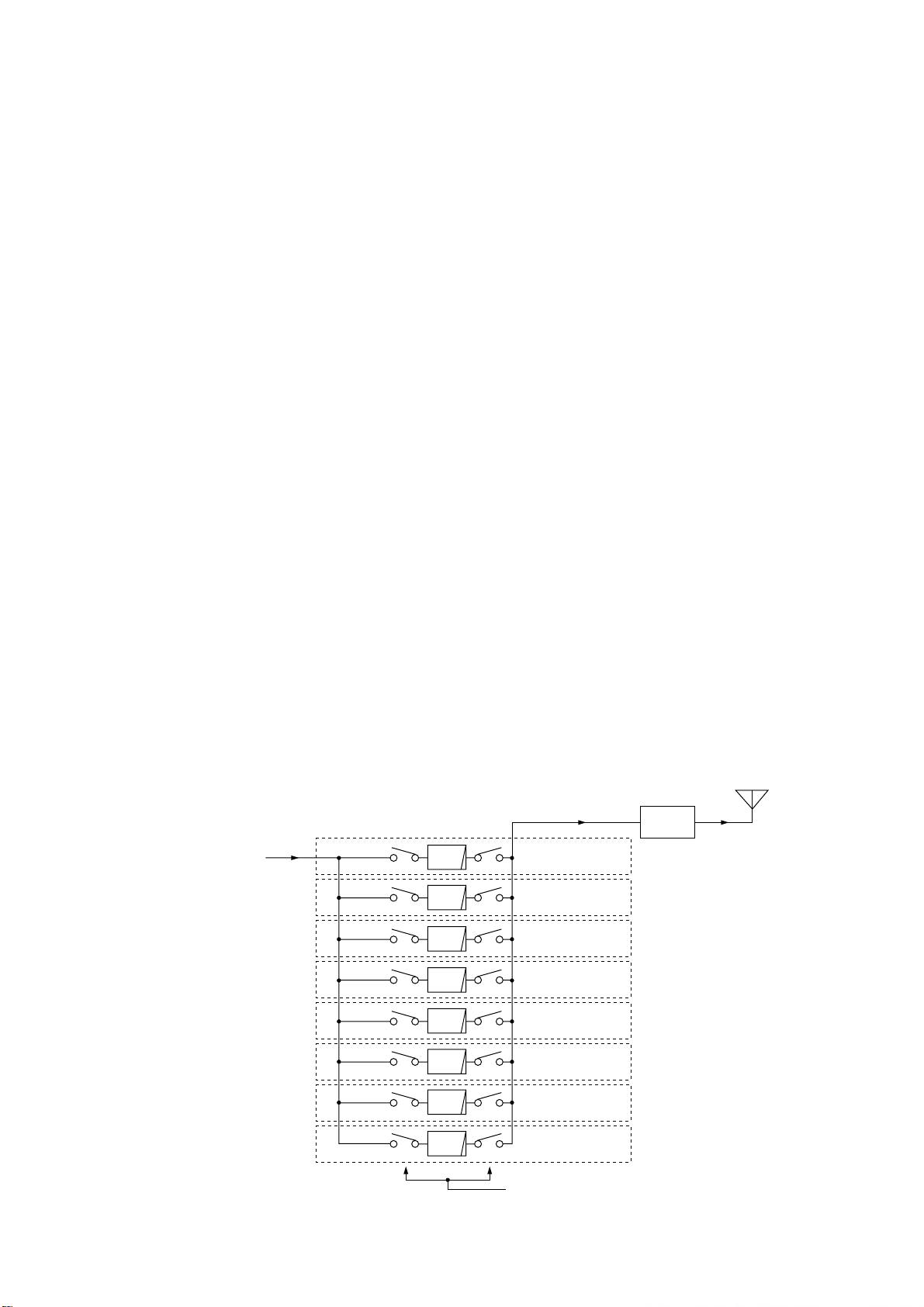

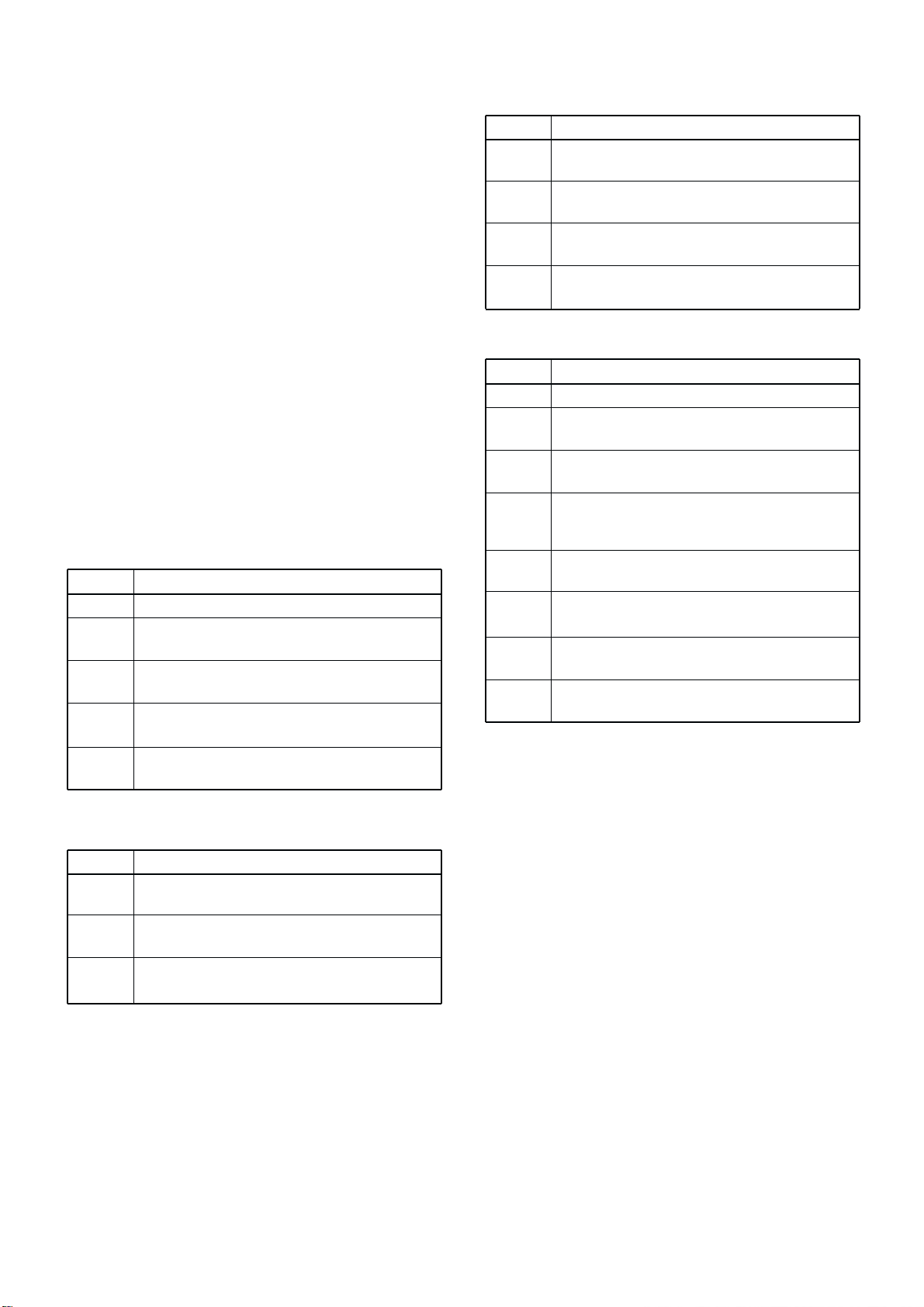

3-3 PLL CIRCUITS

3-3-1 GENERAL

The PLL circuits generate a reference frequency (32.000

MHz); 1st LO frequencies (64.485–94.455 MHz); 2nd LO

frequency (64 MHz), 3rd LO frequency (433.000 kHz).

The 1st LO PLL adopts a mixer-less dual loop PLL system.

The BFO uses a DDS and a 2nd LO as a fixed frequency

double that the crystal oscillator.

3-3-2 1ST LO PLL (PLL UNIT)

The 1st LO PLL contains a main and reference loop as a

dual loop system.

The reference loop generates an approximate 10.5 MHz frequency using a DDS circuit, and the main loop generates a

64.485 to 94.455 MHz frequency using the reference loop

frequency.

(1) REFERENCE LOOP PLL

The oscillated signal at the reference VCO (Q5301, D5301)

is amplified at the amplifiers (Q5302, Q5351) and is then

applied to the DDS IC (IC5101, pin 46). The signal is then

divided and detected on phase with the DDS generated frequency.

The detected signal output from the DDS IC (pin 56) is converted into DC voltage (lock voltage) at the loop filter

(R5136, R5146, C5112) and then fed back to the reference

VCO circuit (Q5301, D5301).

(2) MAIN LOOP PLL

The oscillated signal at one of the main loop VCOs (Q5521,

D5521, L5523) is amplified at the buffer amplifiers (Q5601,

Q5604) and is then applied to the PLL IC (IC5401, pin 6).

The signal is then divided and detected on phase with the

reference loop output frequency.

The detected signal output from the PLL IC (pin 2) is converted into a DC voltage (lock voltage) at the loop filter and

then fed back to one of the VCO circuits (Q5521, D5521,

L5523).

The oscillated signal from the buffer amplifier (Q5601) is

also applied to the MAIN unit as a 1st LO signal after being

amplified at LO (Q5602) and buffer (Q5603) amplifiers or

passed through the bandpass filter (L5602–L5604,

C5610–C5616).

3-3-3 2ND LO AND REFERENCE OSCILLATOR

CIRCUITS (PLL UNIT)

The reference oscillator (X5251; [USA], [CAN], X5281;

[OTH]) generates a 32.0 MHz frequency for the DDS circuits

as a system clock and for the LO output. The oscillated signal is doubled at the doubler circuit (Q5202) and the 64.0

MHz frequency is picked up at the double tuned filter

(L5203, L5204). The 64.0 MHz signal is applied to the RF

circuit as a 2nd LO signal.

3-3-3 3RD LO CIRCUIT (PLL UNIT)

The DDS IC (IC5701) generates a 10-bit digital signal using

the 32 MHz system clock. The digital signal is converted into

an analog wave signal at the D/A converter (R5701–R5720).

The converted analog wave is passed through the bandpass

filter (L5781–L5783, C5781–C5785) and then applied to the

MAIN unit as the 3rd LO signal (433.000 kHz) via the attenuator (R5781–R5783).

Phase

detector

Programmable

divider

Programmable

divider

Loop filter

Doubler

DDS

DDS

DDS

DDS

D/A

convertor

D/A

convertor

Buff LO

Buff

Loop filter

Buff

PLL IC (IC5401)

MAIN loop VCO

Q5601 Q5602

Q5202

Q5801

Q5901

Q5302

Q5301, D5301

Q5351

Reference OSC. (32 MHz)

X5251; [USA], [CAN]

X5281; [OTH]

Reference loop VCO

IC5701

Q5882 Q5881

Q5603

Q5521,

D5521,

L5523

DDS IC

(IC5101)

LO

LO

AMP.

Buff

1st LO

(64–94 MHz)

2nd LO

(64 MHz)

DSC 2nd LO

(10.7103 MHz)

[USA], [CAN] only

DSC 1st LO

(12.8875–

27.5045 MHz)

[USA], [CAN] only

3rd LO

(443 kHz)

Phase

detector

Programmable

divider

Programmable

divider

• PLL CIRCUIT

Page 13

3 - 7

3-4 DSC CIRCUITS ([USA], [CAN] ONLY)

3-4-1 DSC BANDPASS FILTER AND RF AMPLIFIER

CIRCUITS (MAIN UNIT)

The RF circuit filters out-of-band signals and amplifiers signals within the range of frequency coverage.

(1) 2–7 MHz signals

The signals from the antenna connector (J2101) pass

through the bandpass filter (L2201, L2202, L2207, L2210,

L2213, L2216, L2219, L2220, L2225, L2228, L2231, C2201,

C2204, C2207, C2210, C2213, C2216, C2219, C2222,

C2225, C2228, C2234, C2240) to obtain desired 2–6 MHz

signals and suppress any undesired signals.

(2) 8 MHz signals

The signals from the antenna connector (J2101) pass

through the bandpass filter (L2204, L2208, L2211, L2214,

L2217, L2221, L2222, L2229, L2232, C2202, C2205,

C2208, C2210, C2211, C2214, C2217, C2220, C2223,

C2226, C2236, C2241) to obtain desired 8 MHz signals and

suppress any undesired signals.

(3) 12 MHz signals

The signals from the antenna connector (J2101) pass

through the bandpass filter (L2235–L2242, L2244, L2245,

C2229, C2235, C2237, C2239, C2243–C2250,

C2252–C2254, C2263, C2264) to obtain desired 12 MHz

signals and suppress any undesired signals.

(4) 16 MHz signals

The signals from the antenna connector (J2101) pass

through the bandpass filter (L2205, L2206, L2209, L2212,

L2215, L2218, L2223, L2224, L2230, L2233, C2203, C2206,

C2209, C2212, C2215, C2218, C2221, C2224, C2226,

C2227, C2238, C2242) to obtain desired 16 MHz signals

and suppress any undesired signals.

The filtered signals are amplified at the RF amplifiers

(Q2301, Q2302), and then applied to the 1st mixer circuit

(D2301).

3-4-2 DSC 1ST MIXER AND 1ST IF CIRCUITS

(MAIN UNIT)

The 1st mixer circuit converts the received signal into a fixed

frequency of the 1st IF signal with a PLL output frequency.

By changing the PLL frequency, only the desired frequency

will pass through a crystal filter at the next stage of the 1st

mixer.

The signals from the RF circuit are mixed at the 1st mixer

(D2301) with a 1st LO signal coming from the PLL circuit to

produce a 10.7 MHz 1st IF signal.

The 1st IF signal is applied to the crystal bandpass filters

(FI231) to suppress out-of-band signals. The filtered 1st IF

signal is amplified at the 1st IF amplifiers (Q2401, Q2501),

then applied to the 2nd mixer circuit (IC2701, pin 3).

3-4-3 DSC 2ND IF AND DSP CIRCUITS

(MAIN AND DSP UNITS)

The 2nd mixer circuit converts the 1st signal into a 2nd IF

signal. A double conversion superheterodyne system (which

converts receive signals twice) improves the image rejection

ratio and obtain stable receiver gain.

The 1st IF signal from the 1st IF amplifiers is applied to the

2nd mixer IC (IC2701, pin 3), and is mixed with the 2nd LO

signal to the converted into a 12 kHz 2nd IF signal.

The 12 kHz 2nd IF signal from the 2nd mixer (IC2701, pin 5)

is applied to the 2nd IF amplifier (IC2702, pin 3), and then

passes through the low-pass filter (IC2702, pins 5, 7). The

signal is applied to the DSP unit as the “DSPI2” signal.

The signal is amplified at the differential amplifier (DSP unit;

IC601), and is then applied to the A/D converter secition in

the CODEC IC (DSP unit; IC501). At the same time, the converted signal is level-shifted 5 V to 3.3 V in the IC (DSP unit;

IC501).

The level-shifted signal is applied to the DSP IC (DSP unit;

IC301) for the digital IF filter, demodulator and noise reduction, etc.

The output signal from the DSP IC is applied to the D/A converter section in the CODEC IC (DSP unit; IC501) to convert

into the analog audio signals. Also the signals are level-shifted 3.3 V to 5 V at the level converter section in the IC.

The level-shifted audio signals are passed through the

active filter (IC701b), and then applied to the MAIN unit via

the J1102 (pin 21) as the “DSPO2” signal.

3-4-4 DSC AGC CIRCUIT (DSP AND MAIN UNITS)

The receiver gain is determined by the voltage on the AGC2

line from the DSP unit. The D/A converter for the AGC

(IC102) supplies control voltage to the AGC2 line and sets

the DSC receiver gain.

The 3rd IF signal from the CODEC IC (IC501) is detected at

the AGC detector section in the DSP IC (IC301). The output

signal from the DSP IC is level-shifted at the level converter

(IC101) and applied to the D/A converter (IC102). The AGC

voltage is amplified at the buffer amplifier section in the

IC102 and applied to the MAIN unit to control the AGC2 line.

When receiving strong signals, the detected voltage increases and the AGC2 voltage decreases. As the AGC2 voltage

is used for the bias voltage of the IF amplifiers (MAIN unit;

Q2401, Q2501), IF amplifier gain is decreased.

3-5 FRONT UNIT (RC-25)

3-5-1 LCD CIRCUIT (DISPLAY AND CONNECT

BOARDS)

The LCD (CONNECT board; DS8220) is controlled by the

LCD driver (CONNECT board; IC8240) via the drive signals

(CL1, RES, CS, RS, WR, RD, DB0–DB7) from the display

board. The LCD’s back light employs 24 LED

(DS8300–DS8323). The LED are controlled by dimmer

(Q8300, Q8301) and dimmer controller (IC8280) circuits.

3-5-2 MICROPHONE CIRCUIT (DISPLAY BOARD)

The AF signals from the microphone are amplified at the AF

amplifier (IC8280) via the “MIC” signal. The signal is applied

to the IC-M802’s main unit through the J8903 via the “MI”

signal.

Page 14

3 - 8

3-5-3 GROUP AND CHANNEL DIALS CIRCUIT

(DISPLAY AND SENSOR BOARDS)

• GROUP DIAL

The signals from the group dial (SENSOR board; S8801) is

applied to the FRONT CPU (IC8201, pins 76, 77) via the

“GPA” and “GPB” signals.

• CHANNEL DIAL

The signals from the channel dial (SENSOR board; S8802)

is applied to the FRONT CPU (IC8021, pins 74, 75) via the

“CHA” and “CHB” signals.

3-5-4 KEY’S BACK LIGHTS CIRCUIT (DISPLAY

BOARD)

The key”s back lights compose DS8340–DS8350, and are

controlled by the dimmer circuit (Q8340–Q8345). The dimmer circuit is controlled by the CPU via the “DIMMER” signal from the FRONT CPU.

3-5-5 RESET CIRCUIT (DISPLAY BOARD)

The reset IC (IC8202) resets the FRONT CPU (IC8201)

when IC-M802 is power ON or OFF.

3-6 POWER SUPPLY CIRCUITS

3-6-1 PA UNIT VOLTAGE LINE

LINE

HV13

HV

S13V

PA8V

PAT8

DESCRIPTION

The voltage from an external power supply.

The same voltage as the HV13 line passed

through the fuse (F6701).

The same voltage as the HV13 line passes

through the switching relay (RL6701).

8 V for transmitter circuits regulated by the +8

regulator circuit (IC6601).

8 V for transmitter circuits regulated by the T8

regulator circuit (Q6601, Q6602).

3-6-2 DISPLAY BOARD (RC-25) VOLTAGE LINE

LINE

HV13

10V

5V

DESCRIPTION

The voltage from PA and MAIN units via the

J8602.

Common 10 V converted from the 13 V line and

regulated by the +10 regulator circuit (IC8301).

Common 5 V converted from the 5 V line and

regulated by the +5 regulator circuit (IC8290).

3-6-3 PLL UNIT VOLTAGE LINE

LINE

HV13

H5V

5V

8VL

DESCRIPTION

The voltage from PA and MAIN units via the

J5001.

Common 5 V line from the MAIN unit via the

J5071.

Common 5 V converted from the 13 V line and

regulated by the +5 regulator circuit (IC5001).

Common 8 V converted from the 13 V line and

regulated by the +8 regulator circuit (IC5031).

3-6-4 MAIN UNIT VOLTAGE LINE

LINE

S13V

R13V

8V

–5V

T8

R8

5V

H5V

DESCRIPTION

The voltage from the PA unit via the J1901.

Receive 13 V converted from the S13V line and

regulated by the R13 regulator circuit (IC1303).

Common 8 V converted from the 13 V line and

regulated by the +8 regulator circuit (IC1502).

Common –5 V converted from the 13 V line and

regulated by the –5 V DC-DC converter (IC1551,

D1551, D1552)

Transmit 8 V converted from the S13V line and

regulated by the T8 regulator circuit (Q1501).

Receive 8 V converted from the S13V line and

regulated by the R8 regulator circuit (Q1502).

Common 5 V converted from the 13 V line and

regulated by the +5 regulator circuit (IC1501).

Common 5 V converted from the 5 V line and

regulated by the +5 regulator circuit (IC3101).

Page 15

3 - 9

Pin

number

90

92

93

94

97

Port

name

ECK

ASEN

TEMP

NSEN

RFML

Description

Outputs serial clock signal for the

EEPROM (IC3301, pin 6).

Input port for the SEND signal from

the accessory connector (J1801).

Input port for the power amplifier temperature signal from the PA unit.

Input port for the SEND signal from

the AF/MOD connector (PLL unit;

J5051, pin 8) via the J3602.

Input port for the RF/ANTC meter’s

voltage from the meter amplifier

(IC1201, pin 14).

MAIN CPU (MAIN UNIT; IC3303)–continued

3-7-2 OUTPUT EXPANDER IC FOR THE PLL

STROBE (IC3601)

Pin

number

4

5

6

7

14

Port

name

PST1

PST2

PST3

PST4

PST5

Description

Outputs strobe signal for the DDS IC

(PLL unit; IC5101, pin 91).

Outputs strobe signal for the PLL IC

(PLL unit; IC5401, pins 13).

Outputs strobe signal for the DDS IC

(PLL unit; IC5701, pin 41).

Outputs strobe signal for the DDS IC

(PLL unit; IC5801, pin 41).

Outputs strobe signal for the DDS IC

(PLL unit; IC5901, pin 41).

3-7 PORT ALLOCATIONS

3-7-1 MAIN CPU (MAIN UNIT; IC3303)

Pin

number

1

2

3

4

6

7

11

19

23

24

26

27

28

29

30

32

33

34

37

38

47

48

49

79

80

89

Port

name

TXS

RXS

PSEL

BEEP

PDAT

PCK

UNLK

PWRS

DRES

STBO

RQO

RQI

DO

NMEI

NMEO

NMEI2

LSTB

DSTB

LCK

LDAT

MSTB

PSTB

SQLC

STAT

KEYS

EDT

Description

Outputs T8 regulator circuit (MAIN

unit; Q1501) control signal.

Outputs R8 regulator circuit (MAIN

unit; Q1502) control signal.

Outputs serial strobe signal to the

latch control IC (IC3601, pin 1).

Outputs beep audio signals.

Outputs serial data signal for the PLL

circuits.

Outputs serial clock signal for the PLL

circuit.

Input port for PLL unlock signal.

Outputs switching relay (PA unit;

RL6701) control signal.

Outputs the RESET signal.

Outputs strobe signal for the DSP unit.

Outputs data signal for the DSP unit.

Outputs serial data signal for the DSP

unit.

Input port for the serial data signal

from the DSP unit.

Input port for the NMEA signal.

Outputs NMEA signal for PLL unit.

Input port for the GPS signal from the

PLL unit.

Outputs serial strobe signal for the

IC3602, IC3603.

Outputs strobe signal for the D/A converter IC (IC3606).

Outputs serial clock signal for

IC3602–IC3605, D/A converter IC

(IC3606) and DSP unit.

Outputs serial data signal for the

IC3602, IC3603 and D/A converter IC

(IC3606).

Outputs serial strobe signal for the

IC3603, IC3605.

Outputs PLL strobe control signal for

the LATCH controller (IC3601).

Outputs squelch control signal for the

SQL switching IC (IC1701).

Outputs the optional antenna tuner

start control signal for the PA unit via

the J1901.

Input port for the optional antenna

tuner key control signal via the PA

unit.

I/O port for the serial data signals

from/to the EEPROM (IC3301, pin 5).

3-7-3 OUTPUT EXPANDER IC FOR THE FILTER

UNIT (IC3602)

Pin

number

4

5

6

7

11

12

13

14

Port

name

L0S

L1S

L2S

L3S

L7S

L6S

L5S

L4S

Description

Outputs 0.5–1.999999 MHz low-pass

filter control signal.

Outputs 2–2.999999 MHz low-pass filter control signal.

Outputs 3–4.999999 MHz low-pass filter control singnal.

Outputs 5–6.999999 MHz low-pass filter control signal.

Outputs 20–30 MHz low-pass filter

control signal.

Outputs 14–19.999999 MHz low-pass

filter control signal.

Outputs 10–13.999999 MHz low-pass

filter control signal.

Outputs 7–9.999999 MHz low-pass filter control signal.

Page 16

3 - 10

3-7-5 OUTPUT EXPANDER IC (IC3603)

Pin

number

4

5

6

11

13

14

Port

name

NMS

EMS

MMS

NMRS

AFMS

CSEN

Description

Outputs NBDP MOD control signal for

the gate mod IC (IC2001, pin 10).

Outputs external MOD control signal

for the gate mode IC (IC2001, pin 11).

Outputs microphone MOD control signal for the gate mode IC (IC2001, pin

9).

Outputs NMEA/RS-232C switching

singnal.

Outputs AF mute control signal.

Outputs SEND control signal for the

buffer amplifier (IC1303, pin 6).

3-7-6 OUTPUT EXPANDER IC (IC3605)

Pin

number

4

5

6

7

14

Port

name

B8S

DBP1

DBP2

DBP3

DBP4

Description

Outputs 24–30 MHz bandpass filter

control signal.

Outputs bandpass filter control signal

for DSC circuit (For 2.1875, 4.2075,

6.3120 MHz).

Outputs bandpass filter control signal

for the DSC circuit (8.4145 MHz).

Outputs bandpass filter control signal

for the DSC circuit (12.5770 MHz).

Outputs bandpass filter control signal

for the DSC circuit (16.8045 MHz).

3-7-4 OUTPUT EXPANDER IC FOR BANDPASS FIL-

TERS (IC3604)

Pin

number

4

5

6

7

11

12

13

14

Port

name

B0S

B1S

B2S

B3S

B7S

B6S

B5S

B4S

Description

Outputs 0.5–1.999999 MHz bandpass

filter control signal.

Outputs 2–2.999999 MHz bandpass

filter control signal.

Outputs 3–4.999999 MHz bandpass

filter control singnal.

Outputs 5–6.999999 MHz bandpass

filter control signal.

Outputs 18–23.999999 MHz bandpass filter control signal.

Outputs 14–17.999999 MHz bandpass filter control signal.

Outputs 10–13.999999 MHz bandpass filter control signal.

Outputs 7–9.999999 MHz bandpass

filter control signal.

3-7-7 D/A CONVERTER IC (IC3606)

Pin

number

5

6

11

13

Port

name

POCV

AFG

FANS

TRXS

Description

Outputs transmit power control signal.

The signal is applied to the ALC amplifier (IC1201, pin 3) and RF amplifier

(Q701).

Outputs the VCA control signal. The

signal is applied to the VCA amplifier

(IC1603, pin 8) and RC-25 controller

via the J2051, pin 5.

Outputs the cooling fan control signal.

The signal is applied to the fan controller (PA unit; IC6501, Q6501).

Outputs the transmitter/receiver

switching signal. The signal is applied

to the switching relay circuit (FILTER

unit; RL7301).

Page 17

3 - 11

3-7-8 FRONT CPU PORT ALLOCATIONS (RC-25,

DISPLAY BOARD; IC8201)

Pin

number

17

21

22

23

24

25

26

28

31

32

33

34

35

36

41–46

48–55

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

Port

name

DSEL

FUNK

TXK

RXK

FCHK

T0K

ENTK

PWRK

PMUT

FPTT

AFGL

M1AD

M2AD

M3AD

CL1

RS

RD

WR

RES

CS

DB7–DB0

T9K

T8K

T7K

T6K

T5K

T4K

T3K

T2K

T1K

EMLK

SETK

MODK

TUNK

DALK

CSCK

DSTK

Description

Outputs DISTRESS LED control signal.

Input port for the

O switch.

Input port for the [TX] switch.

Input port for the [RX] switch.

Input port for the [FREQ/CH] switch.

Input port for the [0] switch.

Input port for the [ENT] switch.

Input port for the [POWER] switch.

Input port for the phone plug insert

detection signal.

Input port for the [PTT] switch from the

microphone connector (J8701, pin 5).

Input port for the AF volume control.

Input port for the using microphone

detection signal.

Input port for the switch signal on the

microphone.

Input port for the microphone connecting detection.

Output LCD drive signals.

Output LCD drive signals.

Input port for the [9] switch.

Input port for the [8] swtich.

Input port for the [7] swtich.

Input port for the [6] switch.

Input port for the [5] switch.

Input port for the [4] switch.

Input port for the [3] switch.

Input port for the [2] switch.

Input port for the [1] switch.

Input port for [e-mail]/[DSC]/[TS]

switches.

Input port for the [SET] switch.

Input port for the [MODE] switch.

Input port for the [TUNE] switch.

Input port for [CANCEL]/[TELCALL]/

[TXF] switches.

Input port for [DSC]/[CALL]/[CH0]/

[SELCALL] switches.

Input port for the [DISTRESS]/[CALL]/

[ALM] switches.

Page 18

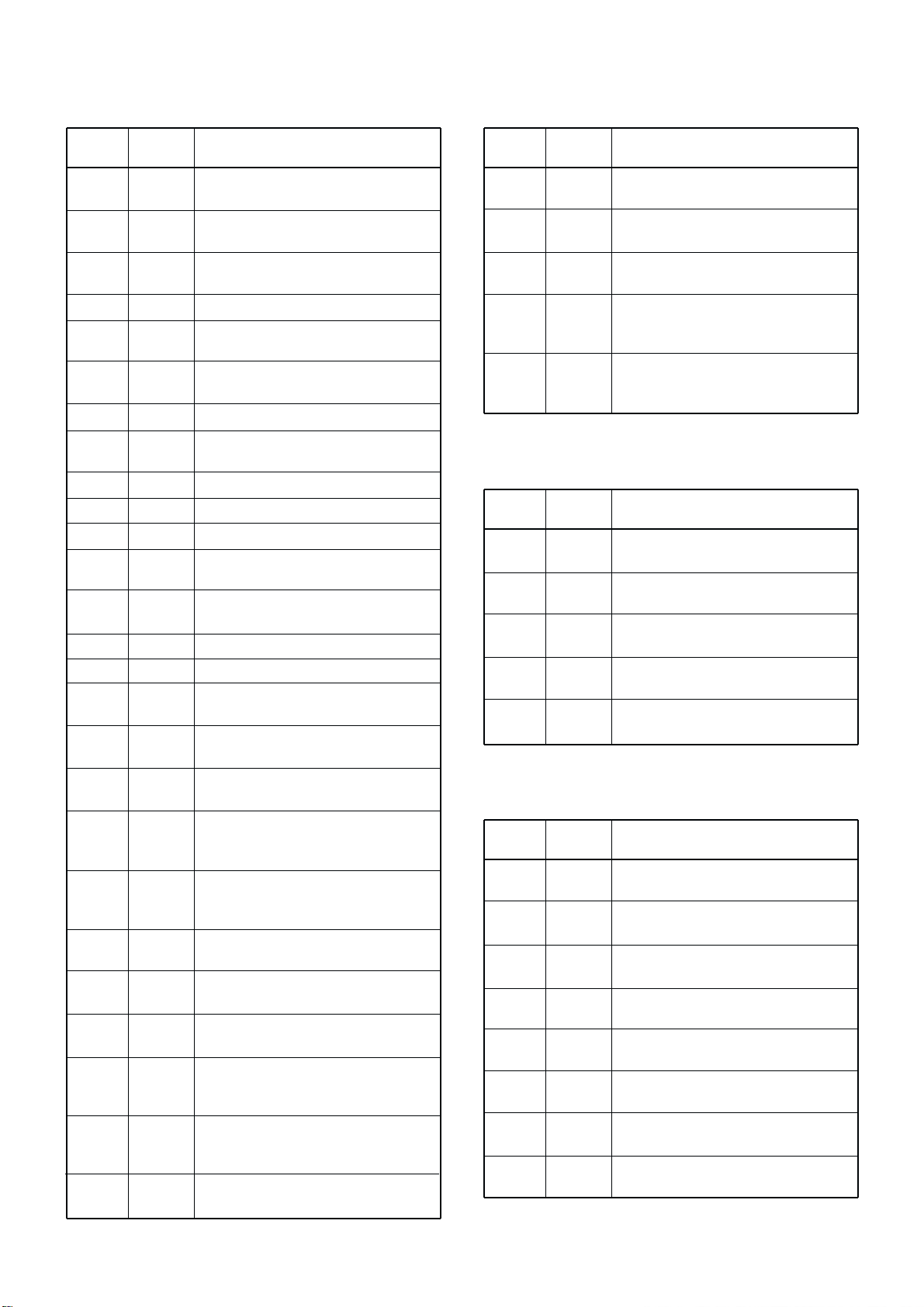

4 - 1

4-1 PREPARATION

When adjusting the contents on page 4-9, a JIG CABLE (see illustration as shown below) is required.

Some adjustments must be performed on the “ADJUSTMENT MODE”. Entering the “ADJUSTMENT MODE”, see the next page.

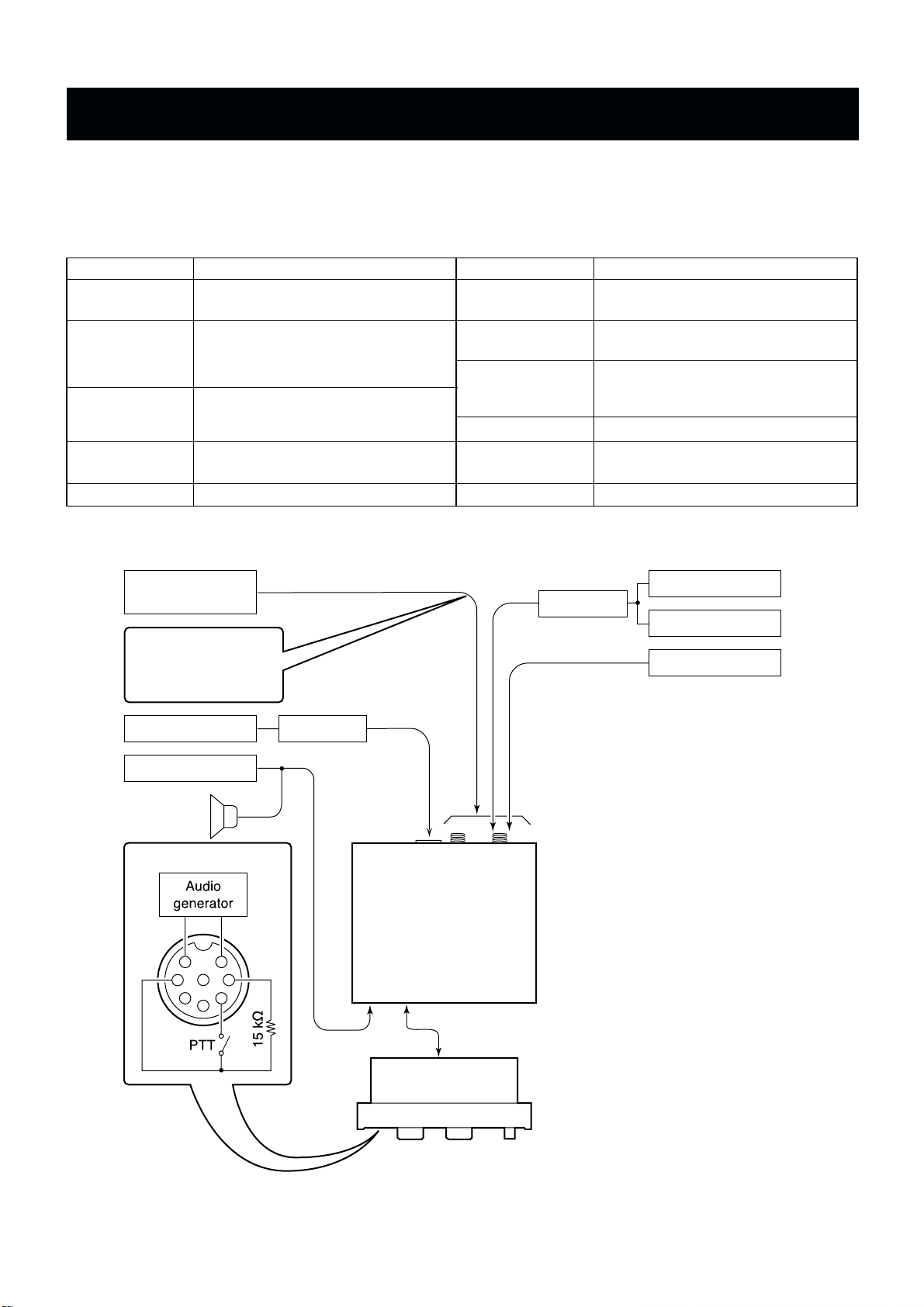

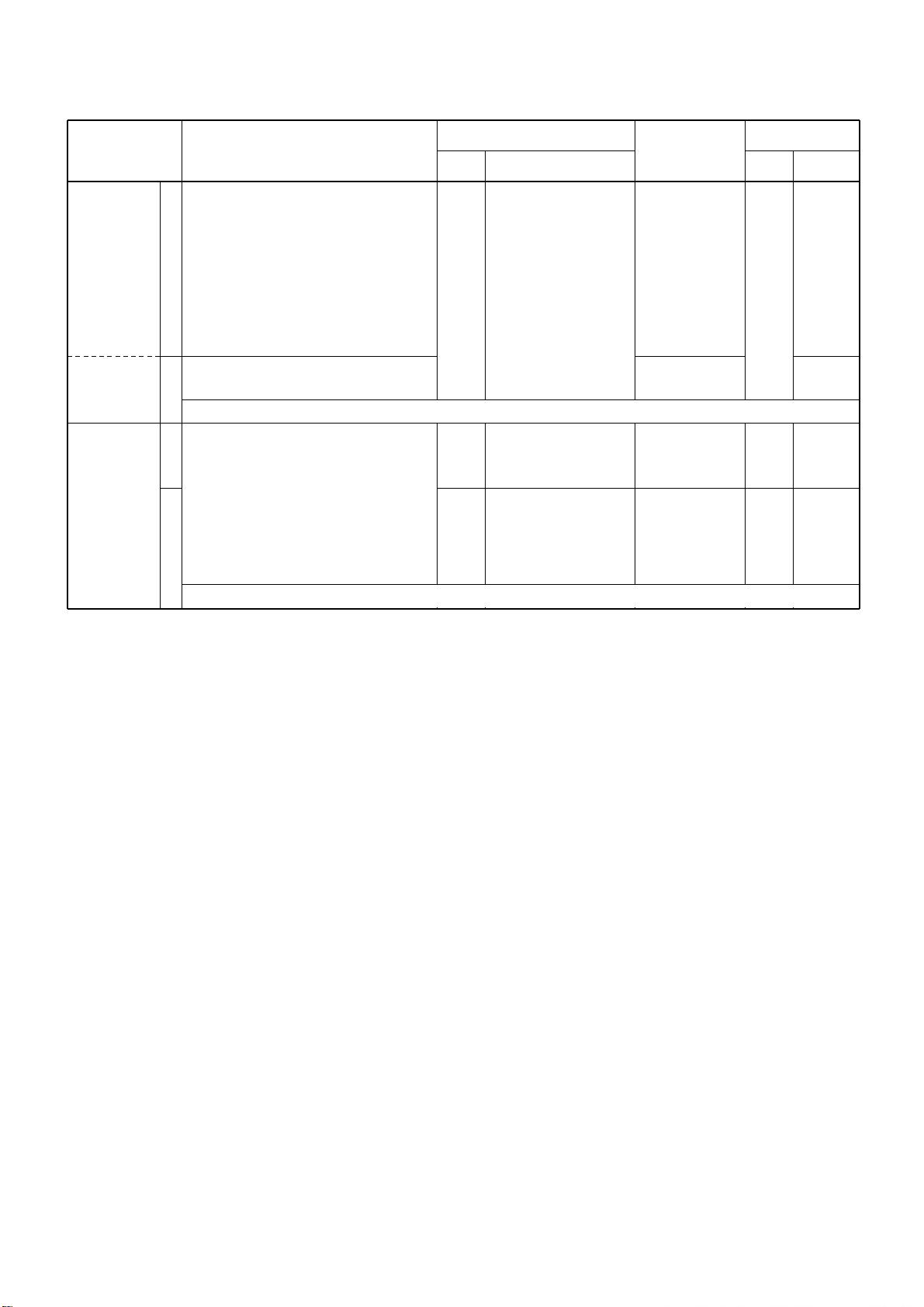

■ REQUIRED TEST EQUIPMENT

SECTION 4 ADJUSTMENT PROCEDURES

EQUIPMENT

DC power supply

RF power meter

(terminated type)

Frequency counter

FM deviation meter

Digital multimeter

GRADE AND RANGE

Output voltage : 13.6 V DC

Current capacity : 30 A or more

Measuring range : 1–100 W

Frequency range : 0.5–30 MHz

Impedance : 50 Ω

SWR : Less than 1.2 : 1

Frequency range : 0.1–600 MHz

Frequency accuracy : ±1 ppm or better

Sensitivity : 100 mV or better

Frequency range : DC–600 MHz

Measuring range : 0 to ±5 kHz

Input impedance : 10 MΩ/V DC or better

EQUIPMENT

Audio generator

Attenuator

Standard signal

generator (SSG)

DC voltmeter

Oscilloscope

AC millivoltmeter

GRADE AND RANGE

Frequency range : 300–3000 Hz

Output level : 1–500 mV

Power attenuation : 40 or 50 dB

Capacity : 100 W or more

Frequency range : 0.5–30 MHz

Output level : 0.1 µV–32 mV

(–127 to –17 dBm)

Input impedance : 50 kΩ/V DC or better

Frequency range : DC–20 MHz

Measuring range : 0.01–20 V

Measuring range : 10 mV–10 V

to [SP]

to [CONTROLLER]

[MIC] connector

to antenna connector 1/2

to antenna connector 1

Speaker

6

5

4

2

3

8

7

1

Modulation analyzer

Distortion meter

Standard signal

generator

CAUTION!

DO NOT transmit while

an SSG is connected to

the antenna connector 1.

DC power supply Ammeter

Attenuator

Spectrum scope

+_

RF power meter

• CONNECTION

Page 19

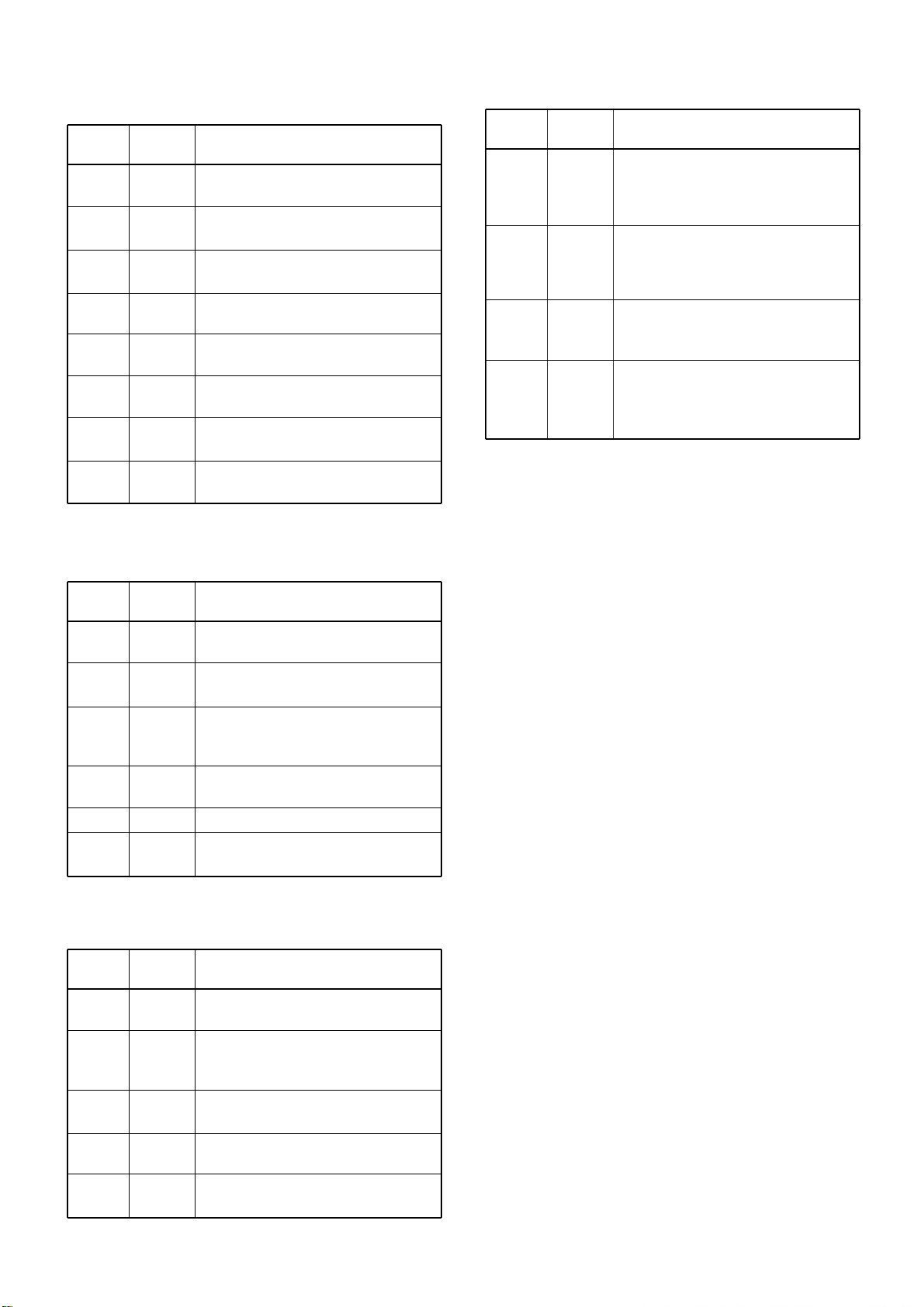

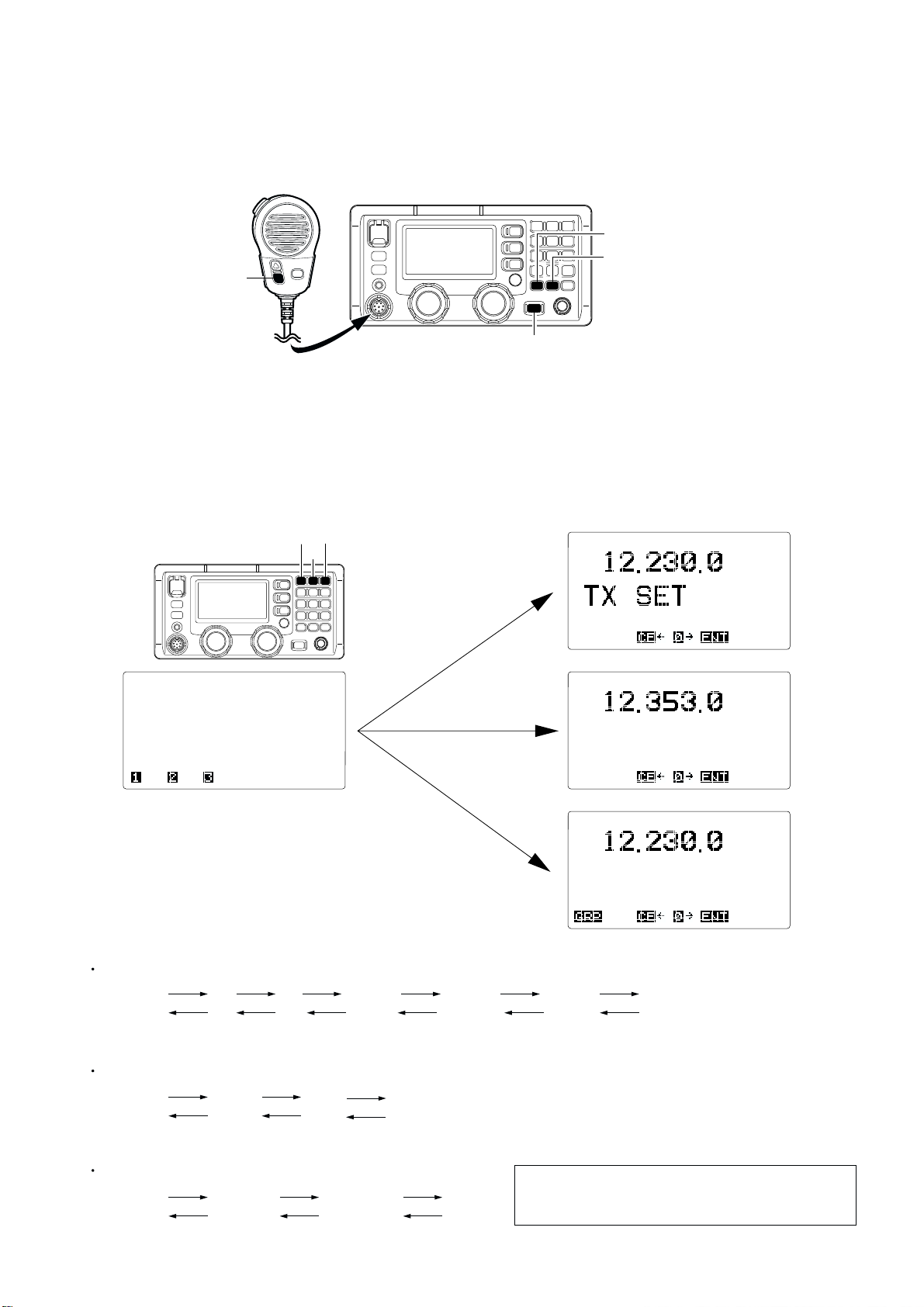

■ ENTERING THE ADJUSTMENT MODE

1 Turn the power OFF.

2 Push and hold the HM-135’s [DOWN] key, [TX] and [RX] buttons, then turn the power ON.

NOTE: Inserting the 15 kΩ resistor between 2 pin and 6 pin of HM-135 works same as pushing and holding HM-135’s [DOWN]

key (See the illustration on page 4-1).

■ OPERATING ON THE ADJUSTMENT MODE

• Enter the TX adjustment from the MAIN menu. : Push the [1] button

• Enter the RX adjustment from the MAIN menu. : Push the [2] button

• Enter the DSC adjustment from the MAIN menu. : Push the [3] button (except [OTH])

• Change the next adjustment item. : Push the [0] button

• Return to the pre-adjustment item. : Push the [CE] button

4 - 2

ADJUST

*** ***

MODE

RX

J3E

SET

DSC

ADJUSTMENT

8414.5

FRQ

ADJUST

*** ***

MODE

RX

J3E

SET

RX TOTAL GAIN

54(1.647)

ADJUST

*** ***

MODE

RX

J3E

SET

ADJUST

*** ***

MODE

[CANCEL]

BACK

TO HERE

[1] TX

[2]

RX

RX

[3] DSC

DSC

0.80-000

2.91-000

0.78

TX

[1]

[2]

[3]

Push [1]

Main menu

TX adjustment menu

RX adjustment menu

DSC adjustment menu

Push [2]

Push [3]

[RX]

[POWER]

[TX]

[DOWN] key

Connect to [MIC] connector.

MAIN

menu

TX ADJUSTMENT ITEM CHANGING

[1] [0] [0] [0] [0] [0]

[CE][CE][CE][CE][CE][CE]

TX

set

TX

gain

TX power

(High)

TX power

(Middle)

TX power

(Low)

TX tune

power

MAIN

menu

RX ADJUSTMENT ITEM CHANGING

DSC ADJUSTMENT ITEM CHANGING

[2] [0]

[0]

[CE]

[CE][CE]

RX total

gain

S level

zero

S level

8

MAIN

menu

[3] [0]

[CE][CE]

*DSC

demodulation

DSC

adjustment

DSC

self check

[0]

[CE]

*NOTE: DO NOT adjust the “DSC DEMODULATION”.

Thus, after adjusting the “DSC adjustment”,

push the [0] button twice to skip it.

Page 20

4 - 3

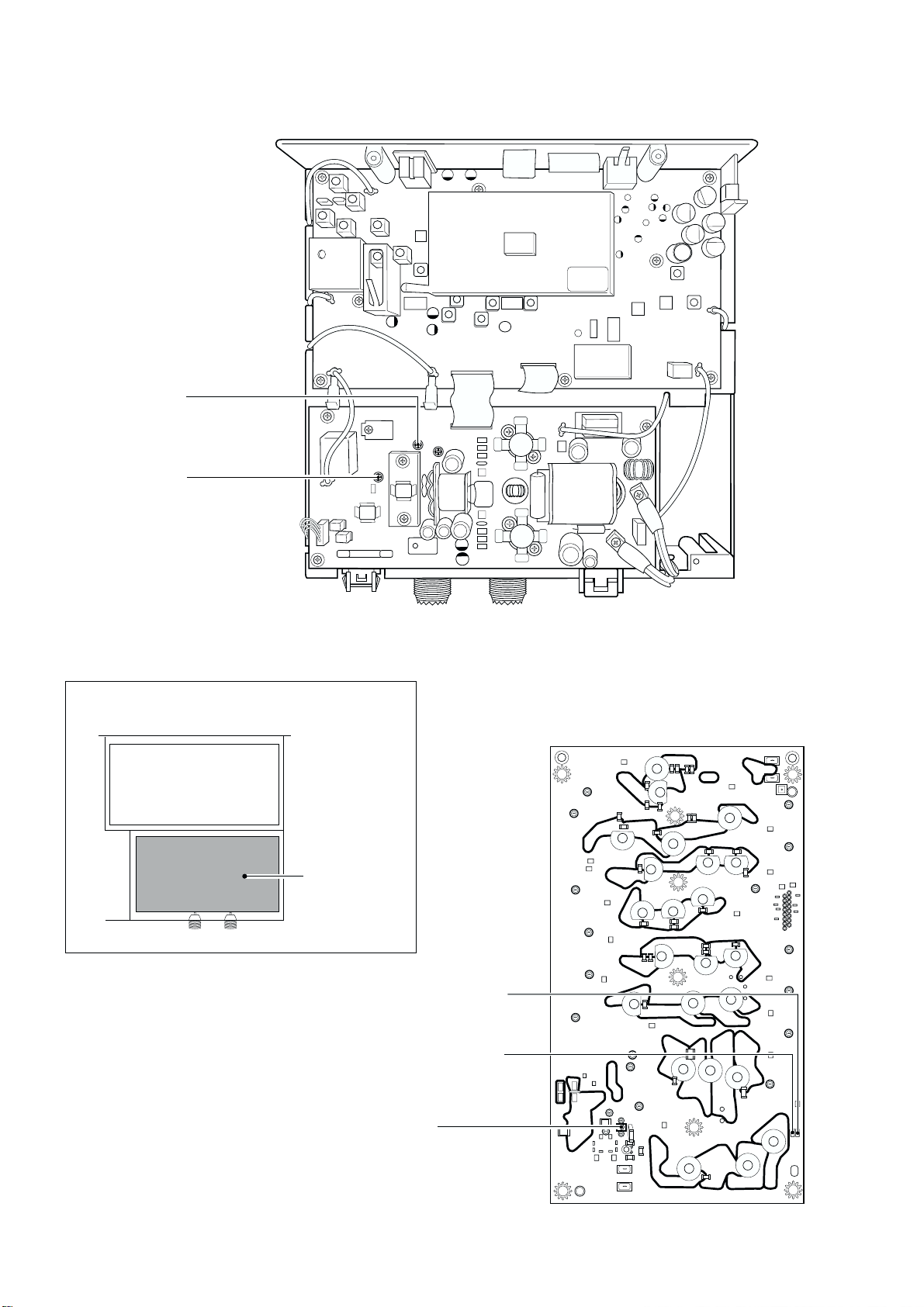

4-2 PLL UNIT ADJUSTMENT

LPL LOCK

VOLTAGE

HPL LOCK

VOLTAGE

REFERENCE

FREQUENCY

1

2

1

2

1

2

• Operating frequency : 0.5000 MHz

• Mode : J3E

• Receiving

• Operating frequency : 0.4999 MHz

• Receiving

• Operating frequency : 29.9999 MHz

• Mode : J3E

• Receiving

• Operating frequency : 0.0300 MHz

• Receiving

• Wait for 5 minutes after power ON.

• Terminate P5201 on the PLL unit to

ground with a 50 Ω resister.

• Receiving

PLL

PLL

PLL

Connect a digital multi

meter or oscilloscope

to check point

CP5301.

Connect a digital multi

meter or oscilloscope

to check point

CP5401.

Connect an RF voltmeter to check point

P5201.

Connect a frequency

counter to check point

P5201.

1.0 V

Less than 4.0 V

4.2 V

More than 0.8 V

Maximum level

63.999990 MHz

([USA], [CAN])

64.000000 MHz

([OTH])

PLL

PLL

PLL

C5305

Verify

C5521

Verify

L5203,

L5204

X5251

([USA],

[CAN])

C5294

([OTH])

ADJUSTMENT ADJUSTMENT CONDITIONS

UNIT LOCATION

VALUE

UNIT ADJUST

MEASUREMENT ADJUSTMENT

Page 21

4 - 4

HPL lock voltage check point

CP5401

C5394

Reference frequency adjustment (USA, CAN)

X5251

LPL lock voltage check point

CP5301

Reference frequency check point

P5201

LPL lock voltage adjustment

C5305

LPL lock voltage adjustment

L5203

L5204

Reference frequency adjustment (OTH)

C5521

HPL lock voltage adjustment

• PLL UNIT TOP VIEW

PLL unit

• IC-M802 BOTTOM VIEW

Page 22

4 - 5

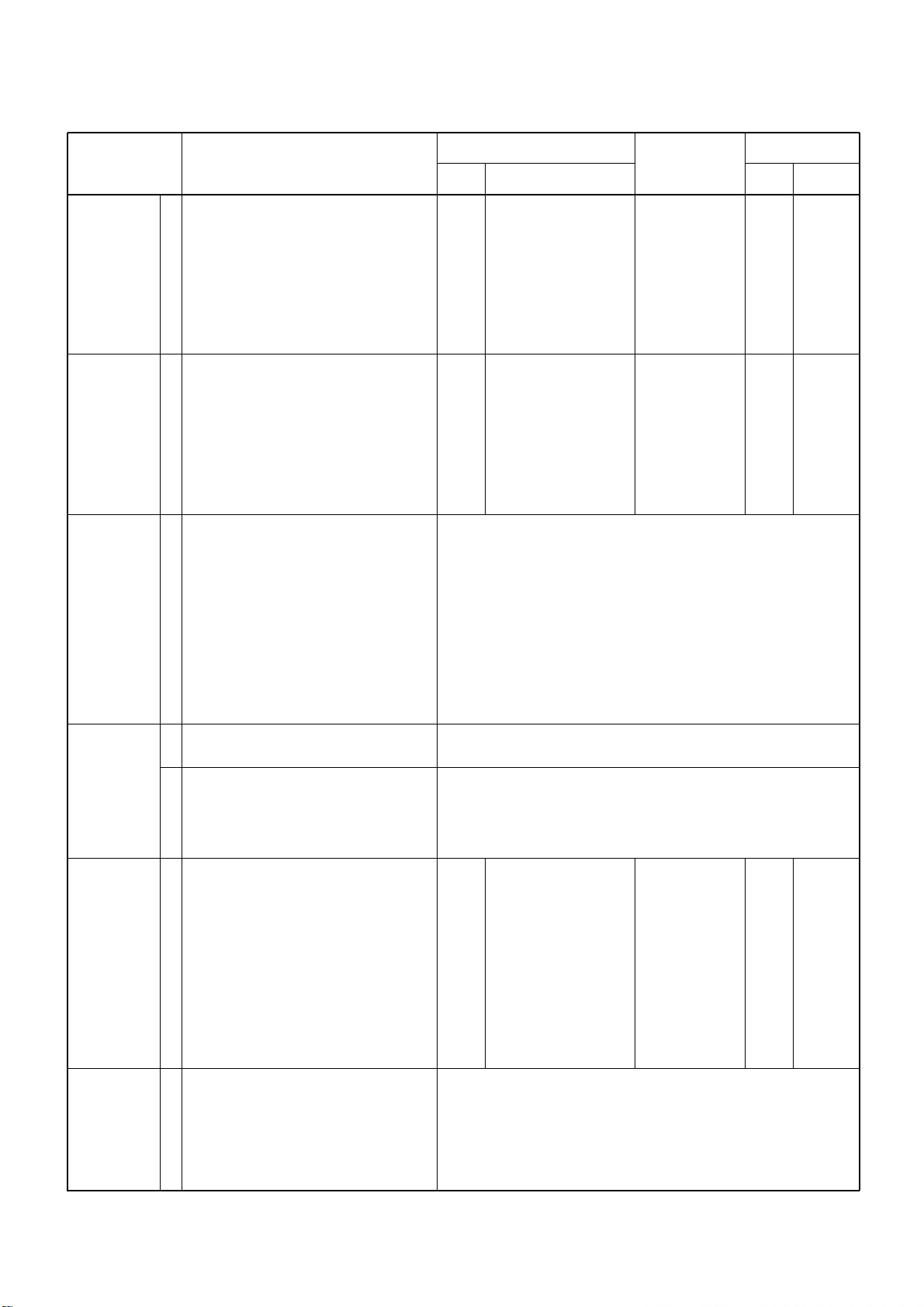

4-3 PA AND FILTER UNITS ADJUSTMENT

IDLING

CURRENT

(For drive

FETs)

(For final

transistors)

SWR

DETECTOR

12• Operating frequency : 12.2350 MHz

• Mode : J3E

• Apply no audio signal to the [MICRO-

PHONE] connector.

• Disconnect J6702.

• Preset R6304 and R6412 on the PA

unit to max. counter clockwise.

• Connect a dummy load or RF power

meter to the [ANT] connector.

• Transmitting

• Transmitting

• Operating frequency : 22.0000 MHz

• Mode : J3E

• Connect the CP7332 (FOR line) on

the FILTER unit to ground.

• Connect an audio generator to the

[MICROPHONE] connector and set

as:

Frequency : 1.5 kHz

• Transmitting

Rear

panel

Rear

panel

FIL-

TER

Connect an ammeter

(10 A) between an

external power supply

and the transceiver.

Connect an RF power

meter to the [ANT]

connector.

Connect a DC voltmeter to check point,

CP7331.

2.0 A

0.7 A

140 W

Minimum level

PA

Audio

gen-

erator

FIL-

TER

R6304

R6412

Output

level

C7275

ADJUSTMENT ADJUSTMENT CONDITIONS

UNIT LOCATION

VALUE

UNIT ADJUST

MEASUREMENT ADJUSTMENT

• After adjustment, connect J6701 to the PA unit.

1

2

• After adjustment, disconnect CP7332 (FOR line) on the FILTER unit from ground.

Page 23

SWR detector check point

CP7331 (REF line)

Connect to ground

CP7332 (FOR line)

SWR detector adjustment

C7275

4 - 6

R6304

Idling current adjustment

(For drive FETs)

R6412

Idling current adjustment

(For final transistors)

• IC-M802 TOP VIEW

• FILTER UNIT BOTTOM VIEW

FILTER unit

• IC-M802 BOTTOM VIEW

Page 24

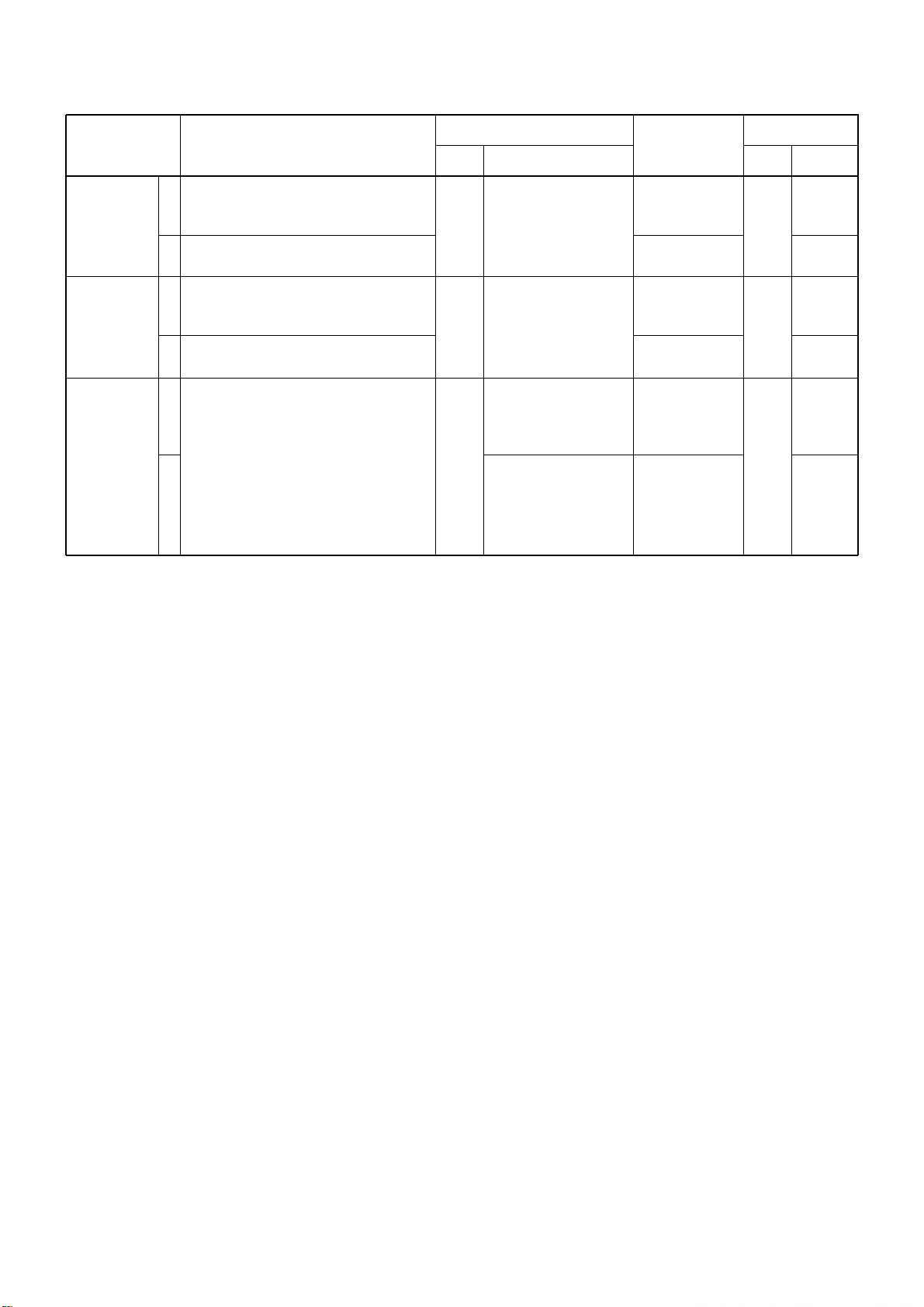

4-4 RECEIVER ADJUSTMENTS

”TOTAL GAIN”, “S-METER” and “DSC PEAK” adjustments must be performed at “ADJUSTMENT MODE”.

NOISE NULL

POINT

RECEIVER

GAIN

TOTAL GAIN

S-METER

DSC PEAK

([USA],[CAN]

only)

DSC SELF

CHECK

([USA],[CAN]

only)

1

1

1

1

2

1

1

• Operating frequency : 0.5 MHz

• Mode : H3E

• Preset L402 and L405 to max. clock-

wise.

• Preset L401, L403, L404 and L801 to

max. counter clockwise.

• Set the standard signal generator to

OFF (no signal output).

• Receiving

• Operating frequency : 12.2310 MHz

• Mode : J3E

• Connect a standard signal generator

to the [ANT] connector and set as:

Frequency : 12.2310 MHz

Level : 0.5 µV*

(–113 dBm)

Modulation : OFF

• Receiving

• While pushing HM-135’s “DOWN” key,

[TX] and [RX] switches, then turn

power ON.

• Push [2] swtich to enter the RX adjustment mode.

• Connect a standard signal generator

to the [ANT] connector and set as:

Frequency : 12.3540 MHz

Level : 320 µV*

(–57 dBm)

Modulation : OFF

• Receiving

• Set the standard signal generator to

OFF (no signal output).

• Set the standard signal generator as:

Frequency : 12.3540 MHz

Level : 10 mV*

(–27 dBm)

• Receiving

• Push [3] switch to enter the DSC

adjustment mode.

LCD displayed :“DSC ADJUSTMENT”.

• DSC frequency : 8.4145 MHz

• Connect a standard signal generator

to the [DSC ANT] connector and set

as:

Frequency : 8.4145 MHz

Level : 0.5 µV*

(–113 dBm)

Modulation : OFF

• Receiving

• LCD displayed :”DSC SELF CHECK”

• DSC frequency : 8.4145 MHz

• Connect an RF power meter to the

[DSC ANT] connector on the rear

panel.

• Receiving

Front

panel

Front

panel

Front

panel

Connect an AC millivoltmeter to the [SP]

jack with a 4 Ω dummy

load.

Connect an AC millivoltmeter to the [SP]

jack with a 4 Ω dummy

load.

Connect an AC millivoltmeter to the [SP]

jack with a 4 Ω dummy

load.

Minimum output

level

Maximum out-

put level

Maximum out-

put level

MAIN

MAIN

MAIN

L207

L208,

L209,

L210,

L301,

L302,

L307

L2306,

L2307

ADJUSTMENT ADJUSTMENT CONDITIONS

UNIT LOCATION

VALUE

UNIT ADJUST

MEASUREMENT ADJUSTMENT

*The output level of the standard signal generator (SSG) is indicated as the SSG’s open circuit.

• Push the [ENT] switch to write the adjustment value in the mem-

ory.

• Push the [ENT] switch to write the adjustment value in the memory.

• Push the [ENT] switch to write the adjustment value in the memory.

4 - 7

• Push the [ENT] switch, and then verify to return to the “Main

menu” on the LCD display.

When this check is failure, displayed “NG” on LCD, and beep

sound.

Page 25

4 - 8

L307

Receiver gain adjustment

Noise null point adjustment

L302

L208

L209

L301

L210

L207

DSC peak adjustment

L2307

L2306

[ENT]

• IC-M802 TOP VIEW

• RC-25 FRONT PANEL

Page 26

4 - 9

4-5 TRANSMITTER ADJUSTMENTS

The following adjustments must be performed at “ADJUSTMENT MODE” after “SWR DETECTOR” and “RECEIVER” ADJUST-

MENTS in the SECTION 4-3 and 4-4.

TRANSMIT

PEAK AND

TOTAL GAIN

(TX PEAK)

(TOTAL GAIN)

TX POWER

(HIGH)

(MIDDLE)

(LOW)

TUNE

POWER

AM CARRIER POWER

([OTH] only)

1

2

1

2

1

2

1

2

1

2

1

2

• While pushing HM-135’s DOWN key,

[TX] and [RX] switches, turn power

ON.

• Connect an audio generator to the

[MICROPHONE] connector and set

as:

Frequency : 1.5 kHz

Level : 10 mV

• Push [1] swtich to enter the TX adjustment mode

(LCD displayed: “TX SET”)

.

• Push [ENT] switch, then the transceiver is transmitting.

• After setting 75 W, push the [ENT] key

to write the adjustment value in the

memory.

• LCD displayed :“TX POWER HIGH”

• Set the audio generator as:

Frequency : 1.5 kHz

Level : 100 mV

• After setting 140 W, push the [ENT]

key to write the adjustment value in

the memory.

• LCD displayed :“TX POWER MID”

• Set the audio generator as:

Frequency : 1.5 kHz

Level : 100 mV

• After setting 70 W, push the [ENT] key

to write the adjustment value in the

memory.

• LCD displayed :“TX POWER LOW”

• Set the audio generator as:

Frequency : 1.5 kHz

Level : 100 mV

• After setting 20 W, push the [ENT] key

to write the adjustment value in the

memory.

• LCD displayed :“TX POWER TUNE”

• Set the audio generator as:

Frequency : 1.5 kHz

Level : 100 mV

• After setting 10 W, push the [ENT] key

to write the adjustment value in the

memory.

• LCD displayed :“TX POWER H3E”

• Set the audio generator as:

Frequency : 1.5 kHz

Level : OFF

• After setting 45 W, push the [ENT] key

to write the adjustment value in the

memory.

Rear

panel

Rear

panel

Rear

panel

Rear

panel

Rear

panel

Rear

panel

Connect an RF power

meter to the [ANT]

connector.

Connect an RF power

meter to the [ANT]

connector.

Connect an RF power

meter to the [ANT]

connector.

Connect an RF power

meter to the [ANT]

connector.

Connect an RF power

meter to the [ANT]

connector.

Connect an RF power

meter to the [ANT]

connector.

Maximum out-

put power

75 W

140 W

70 W

20 W

10 W

45 W

MAIN

RC-25

RC-25

RC-25

RC-25

RC-25

RC-25

L706

[CH]

DIAL

[CH]

DIAL

[CH]

DIAL

[CH]

DIAL

[CH]

DIAL

[CH]

DIAL

ADJUSTMENT ADJUSTMENT CONDITIONS

UNIT LOCATION

VALUE

UNIT ADJUST

MEASUREMENT ADJUSTMENT

Page 27

[CH]

[ENT]

Transmit peak and total gain

adjustment

L706

R6516

Ic-APC adjustment

J3101 pin 15

Connect to ground

when adjusting IC-APC

4 - 10

• IC-M802 TOP VIEW

• RC-25 FRONT PANEL

TRANSMITTER ADJUSTMENTS(CONTINUE)

1 • Operating frequency : 12.2350 MHz

• Mode : J3E

• Set the audio generator as:

Frequency : 1.5 kHz

Level : 100 mV

• Preset R6516 on the PA unit to center

position.

• Connect the J3101 pin 15 (FOR line)

on the MAIN unit to ground.

• Transmitting

Rear

panel

Connect an ammeter

(50 A) between an

external power supply

and the transceiver.

34.5 A PA R6516

ADJUSTMENT ADJUSTMENT CONDITIONS

UNIT LOCATION

VALUE

UNIT ADJUST

MEASUREMENT ADJUSTMENT

IC-APC

• After adjustment, disconnect J3101 pin 15 (FOR line) on the MAIN unit from ground.

2

Page 28

[MAIN UNIT]

5-1 IC-M802

[MAIN UNIT]

IC1 1110004080 S.IC µPC2709T-E3

IC501 1110005460 S.IC TA4107F (TE12L)

IC901 1110005460 S.IC TA4107F (TE12L)

IC1001

1130006220 S.IC TC4W53FU (TE12L)

IC1002

1110005450 S.IC TS522IDT

IC1051

1110005450 S.IC TS522IDT

IC1101

1110005450 S.IC TS522IDT

IC1201

1110005140 S.IC NJM3403AV-TE1

IC1301

1160000130 S.IC TD62783AF (TP1)

IC1302

1160000130 S.IC TD62783AF (TP1)

IC1303

1160000130 S.IC TD62783AF (TP1)

IC1501

1180000420 S.IC TA78L05F (TE12R)

IC1502

1180002180 S.IC TA78M08F (TE16L)

IC1551

1110001400 S.IC µPC1555G2-T1

IC1601

1110003090 IC LA4425A

IC1602

1130006220 S.IC TC4W53FU (TE12L)

IC1603

1110003300 S.IC M5282FP 70CD

IC1701

1130006220 S.IC TC4W53FU (TE12L)

IC1702

1110005450 S.IC TS522IDT

IC1703

1130006220 S.IC TC4W53FU (TE12L)

IC2001

1130008230 S.IC BU4053BCFV-E2

IC2701

1110005460 S.IC TA4107F (TE12L) [USA], [CAN]

IC2702

1110005450 S.IC TS522IDT [USA], [CAN]

IC3101

1180000420 S.IC TA78L05F (TE12R)

IC3201

1130005720 S.IC TC7W04F (TE12L)

IC3301

1130011210 S.IC CAT24WC64J-TE13 [OTH]

1140009240 S.IC HN58X24128FPI [USA], [CAN]

IC3302

1110005770 S.IC

S-80942CNMC-G9C-T2

[OTH], [CAN]

1130009110 S.IC

S-80942ANMP-DD6-T2

[USA]

IC3303

1140010050 S.IC M30620FCAFP [OTH]

1140010632 S.IC M30624FGAFP D5 [USA], [CAN]

IC3601

1130007700 S.IC BU4094BCF-E2

IC3602

1130007700 S.IC BU4094BCF-E2

IC3603

1130007700 S.IC BU4094BCF-E2

IC3604

1130007700 S.IC BU4094BCF-E2

IC3605

1130007700 S.IC BU4094BCF-E2

IC3606

1110003690 S.IC M62354GP 75EC

Q51 1530003090 S.TRANSISTOR 2SC4213-B (TE85R)

Q201 1560000720 S.FET 2SK2171-4-TD

Q202 1560000720 S.FET 2SK2171-4-TD

Q203 1580000620 S.FET 3SK131-T2 MAS

Q401 1580000620 S.FET 3SK131-T2 MAS

Q501 1580000620 S.FET 3SK131-T2 MAS

Q601 1530003150 S.TRANSISTOR 2SC4673D-TD

Q701 1580000620 S.FET 3SK131-T2 MAS

Q702 1580000620 S.FET 3SK131-T2 MAS

Q703 1580000620 S.FET 3SK131-T2 MAS

Q801 1580000620 S.FET 3SK131-T2 MAS

Q1203 1510000770 S.TRANSISTOR 2SA1586-GR (TE85R)

Q1204 1510000770 S.TRANSISTOR 2SA1586-GR (TE85R)

Q1205 1530003090 S.TRANSISTOR 2SC4213-B (TE85R)

Q1206 1530003090 S.TRANSISTOR 2SC4213-B (TE85R) [OTH]

Q1207 1510000770 S.TRANSISTOR 2SA1586-GR (TE85R) [OTH]

Q1501 1540000440 S.TRANSISTOR 2SD1619-T-TD

Q1502 1540000440 S.TRANSISTOR 2SD1619-T-TD

Q1503 1590000680 S.TRANSISTOR DTC114EUA T106

Q1504 1590000680 S.TRANSISTOR DTC114EUA T106

Q1601 1590000680 S.TRANSISTOR DTC114EUA T106

Q1801 1540000440 S.TRANSISTOR 2SD1619-T-TD

Q2101 1590000680 S.TRANSISTOR DTC114EUA T106 [USA], [CAN]

Q2102 1530002690 S.TRANSISTOR 2SC4116-GR (TE85R)

[USA], [CAN]

Q2301 1560000720 S.FET 2SK2171-4-TD [USA], [CAN]

Q2302 1560000720 S.FET 2SK2171-4-TD [USA], [CAN]

Q2401 1580000620 S.FET 3SK131-T2 MAS [USA], [CAN]

Q2501 1580000620 S.FET 3SK131-T2 MAS [USA], [CAN]

Q3001 1590000680 S.TRANSISTOR DTC114EUA T106

Q3004 1530002690 S.TRANSISTOR 2SC4116-GR (TE85R)

D51 1750000810 S.DIODE UM9957F/TR

D52 1750000810 S.DIODE UM9957F/TR

S.=Surface mount

D53 1790001770 S.DIODE MA80WK-(TX)

D101 1790001770 S.DIODE MA80WK-(TX)

D102 1790001770 S.DIODE MA80WK-(TX)

D103 1790001770 S.DIODE MA80WK-(TX)

D104 1790001770 S.DIODE MA80WK-(TX)

D105 1790000620 S.DIODE MA77 (TX)

D106 1790001770 S.DIODE MA80WK-(TX)

D107 1790001770 S.DIODE MA80WK-(TX)

D108 1790001770 S.DIODE MA80WK-(TX)

D109 1790001770 S.DIODE MA80WK-(TX)

D110 1790000620 S.DIODE MA77 (TX)

D201 1790001770 S.DIODE MA80WK-(TX)

D301 1790001770 S.DIODE MA80WK-(TX)

D302 1750000430 S.DIODE HSB88WSTR

D303 1790001770 S.DIODE MA80WK-(TX)

D401 1790000620 S.DIODE MA77 (TX)

D402 1790000620 S.DIODE MA77 (TX)

D403 1790000620 S.DIODE MA77 (TX)

D404 1790000620 S.DIODE MA77 (TX)

D601 1730002280 S.ZENER MA8091-M (TX)

D602 1790001770 S.DIODE MA80WK-(TX)

D901 1790001770 S.DIODE MA80WK-(TX)

D1102 1790001240 S.DIODE MA2S728-(TX)

D1201 1790001240 S.DIODE MA2S728-(TX)

D1202 1790001250 S.DIODE MA2S111-(TX)

D1203 1790001250 S.DIODE MA2S111-(TX)

D1204 1790001250 S.DIODE MA2S111-(TX)

D1205 1790001250 S.DIODE MA2S111-(TX)

D1206 1790000620 S.DIODE MA77 (TX)

D1207 1790001250 S.DIODE MA2S111-(TX)

D1501 1790001670 S.DIODE RB706F-40T106

D1502 1790001670 S.DIODE RB706F-40T106

D1551 1730002320 S.ZENER MA8051-M (TX)

D1552 1790001670 S.DIODE RB706F-40T106

D1554 1730002280 S.ZENER MA8091-M (TX)

D1801 1790001250 S.DIODE MA2S111-(TX)

D2101 1790001240 S.DIODE MA2S728-(TX) [USA], [CAN]

D2102 1790001250 S.DIODE MA2S111-(TX) [USA], [CAN]

D2103 1750000810 S.DIODE UM9957F/TR [USA], [CAN]

D2104 1750000810 S.DIODE UM9957F/TR [USA], [CAN]

D2201 1790001770 S.DIODE MA80WK-(TX) [USA], [CAN]

D2202 1790001770 S.DIODE MA80WK-(TX) [USA], [CAN]

D2203 1790001770 S.DIODE MA80WK-(TX) [USA], [CAN]

D2204 1790001770 S.DIODE MA80WK-(TX) [USA], [CAN]

D2301 1750000430 S.DIODE HSB88WSTR [USA], [CAN]

D3001 1790001670 S.DIODE RB706F-40T106

D3002 1790001670 S.DIODE RB706F-40T106

D3003 1790001670 S.DIODE RB706F-40T106

D3004 1790001250 S.DIODE MA2S111-(TX)

D3006 1790001670 S.DIODE RB706F-40T106

D3007 1790001670 S.DIODE RB706F-40T106

D3301 1790001250 S.DIODE MA2S111-(TX)

D3302 1790001250 S.DIODE MA2S111-(TX)

D3336 1790001250 S.DIODE MA2S111-(TX)

D3337 1790001250 S.DIODE MA2S111-(TX)

FI201 2010002600 XTAL FL-345 (64.455 MHz)

FI231 2010001880 MONOLITH FL-231 (10.700 MHz) [USA], [CAN]

FI301 2010002470 XTAL FL-315 (64.45500 MHz)