Page 1

VHF TRANSCEIVER

iF110

iF111

iF121

SERVICE

MANUAL

Page 2

INTRODUCTION

This service manual describes the latest service information

for the IC-F110, F111 and F121 VHF TRANSCEIVER at the

time of publication.

DANGER

NEVER connect the transceiver to an AC outlet or to a DC

power supply that uses more than 16 V. This will ruin the

transceiver.

DO NOT expose the transceiver to rain, snow or any liquids.

DO NOT reverse the polarities of the power supply when

connecting the transceiver.

DO NOT apply an RF signal of more than 20 dBm (100 mW)

to the antenna connector. This could damage the transceiver’s front end.

ORDERING PARTS

Be sure to include the following four points when ordering

replacement parts:

1. 10-digit order numbers

2. Component part number and name

3. Equipment model name and unit name

4. Quantity required

<SAMPLE ORDER>

1110003490 S.IC TA31136FN IC-F110 MAIN UNIT 5 pieces

8810009990 Screw

PH BT M3×8 ZK

IC-F110 Bottom cover 10 pieces

Addresses are provided on the inside back cover for your

convenience.

REPAIR NOTES

1. Make sure a problem is internal before disassembling the

transceiver.

2.

DO NOT open the transceiver until the transceiver is

disconnected from its power source.

3. DO NOT force any of the variable components. Turn

them slowly and smoothly.

4.

DO NOT short any circuits or electronic parts. An insulated tuning tool MUST be used for all adjustments.

5. DO NOT keep power ON for a long time when the trans-

ceiver is defective.

6.

DO NOT transmit power into a signal generator or a

sweep generator.

7. ALWAYS connect a 40 dB to 50 dB attenuator between

the transceiver and a deviation meter or spectrum analyzer when using such test equipment.

8.

READ the instructions of test equipment thoroughly

before connecting equipment to the transceiver.

To upgrade quality, any electrical or mechanical parts and

internal circuits are subject to change without notice or

obligation.

MODEL

IC-F110

IC-F111

IC-F121

VERSION

Europe

General

General

U.S.A.

SYMBOL

EUR

GEN

GEN

USA

Page 3

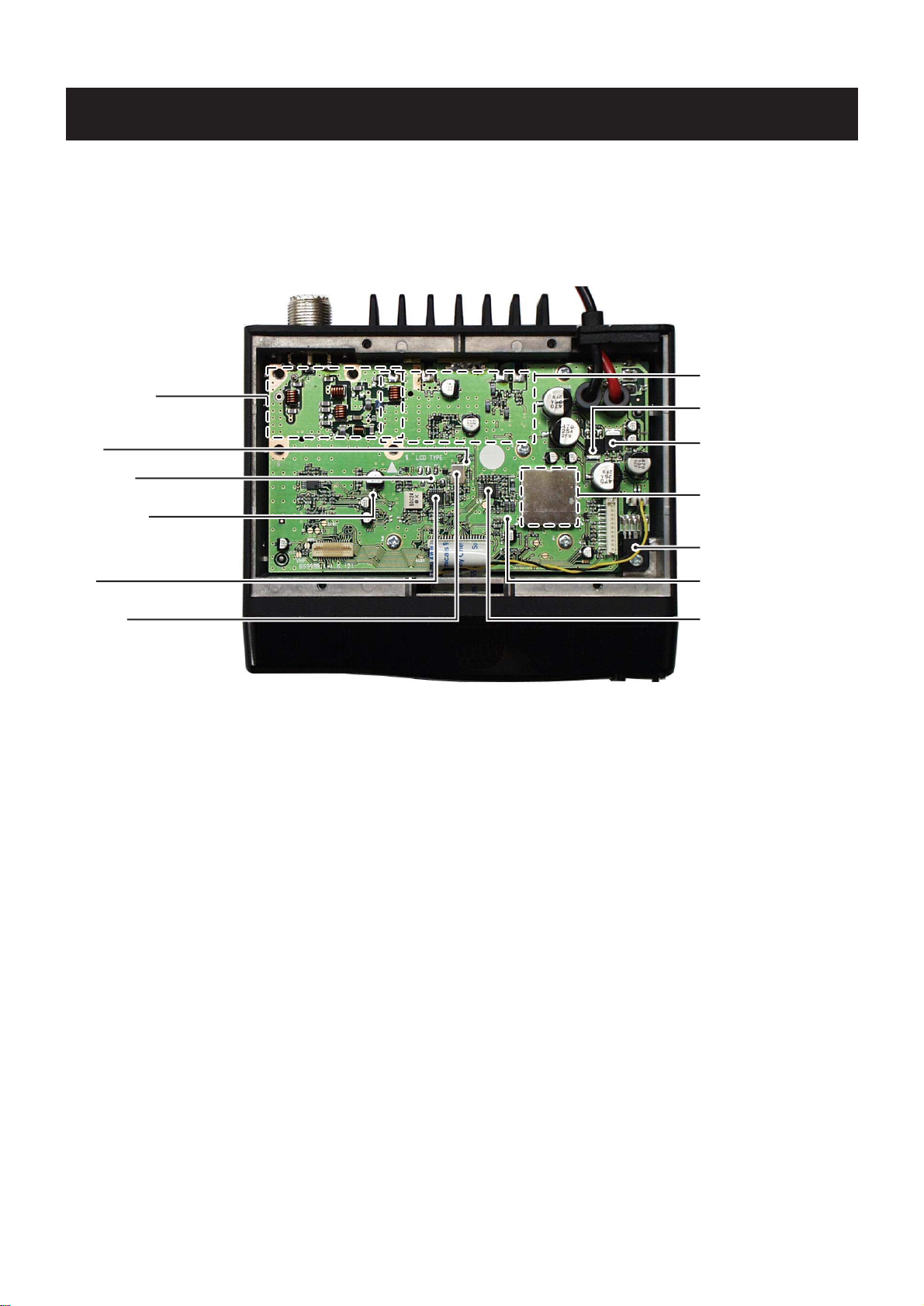

TABLE OF CONTENTS

SECTION 1 SPECIFICATIONS

SECTION 2 INSIDE VIEW

SECTION 3 DISASSEMBLY INSTRUCTIONS

SECTION 4 CIRCUIT DESCRIPTION

4 - 1 RECEIVER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 - 1

4 - 2 TRANSMITTER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 - 2

4 - 3 PLL CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 - 3

4 - 4 POWER SUPPLY CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 - 4

4 - 5 PORT ALLOCATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 - 4

SECTION 5 ADJUSTMENT PROCEDURES

5 - 1 PREPARATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 - 1

5 - 2 PLL ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 - 4

5 - 3 SOFTWARE ADJUSTMENT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 - 5

SECTION 6 PARTS LIST

SECTION 7 MECHANICAL PARTS AND DISASSEMBLY

SECTION 8 SEMI-CONDUCTOR INFORMATION

SECTION 9 BOARD LAYOUTS

9 - 1 FRONT UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 - 1

9 - 2 MAIN UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 - 3

SECTION 10 BLOCK DIAGRAM

SECTION 11 VOLTAGE DIAGRAMS

11 - 1 FRONT UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 - 1

11 - 2 MAIN UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 - 2

EXPLICIT DEFINITIONS

136 – 174 MHz

FREQUENCY COVERAGE CHANNEL SPACING

Narrow/Wide-type

Narrow/Middle-type

12.5 kHz/ 25.0 kHz

12.5 kHz/ 20.0 kHz

15.0 kHz/ 30.0 kHz

Page 4

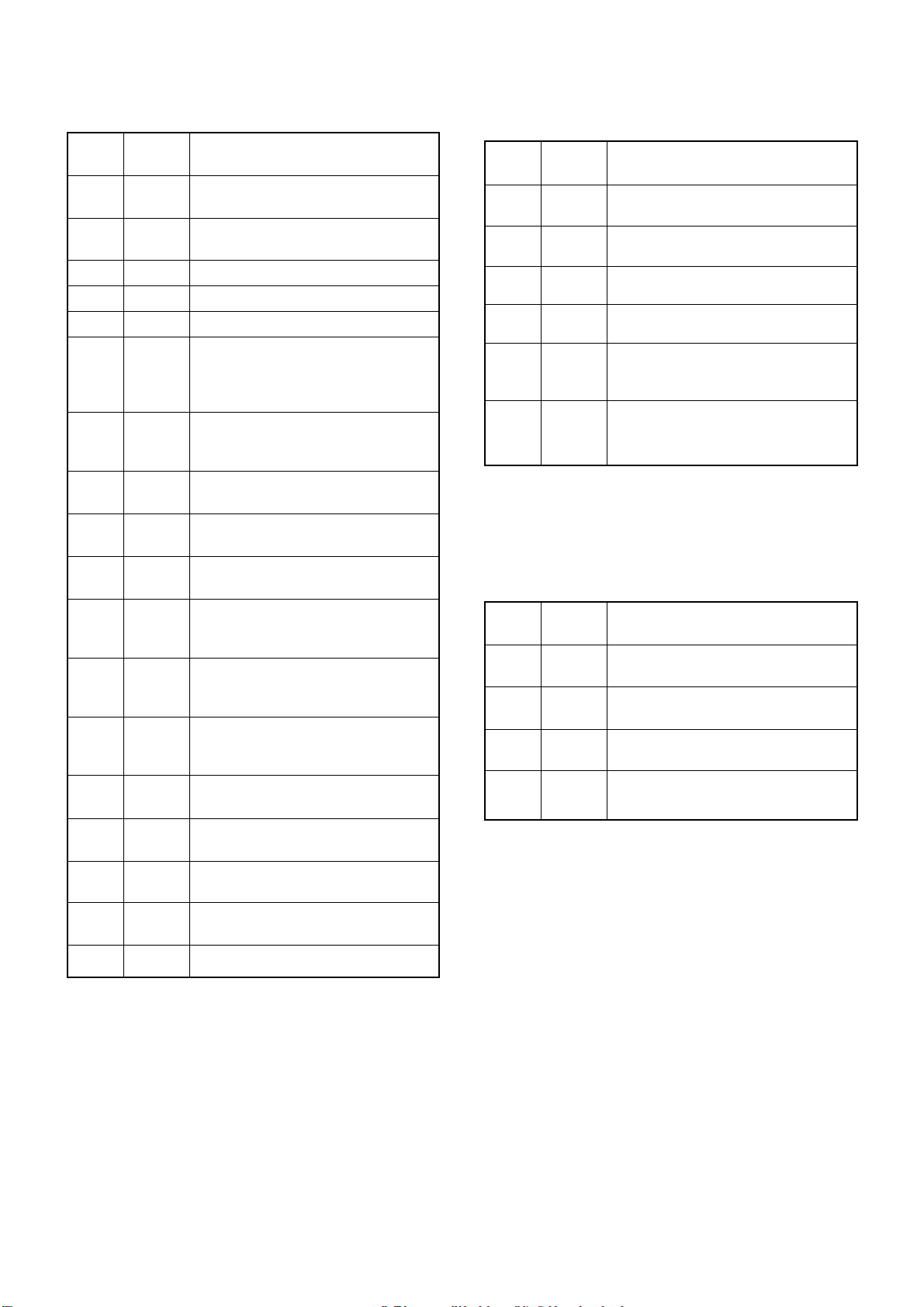

1 - 1

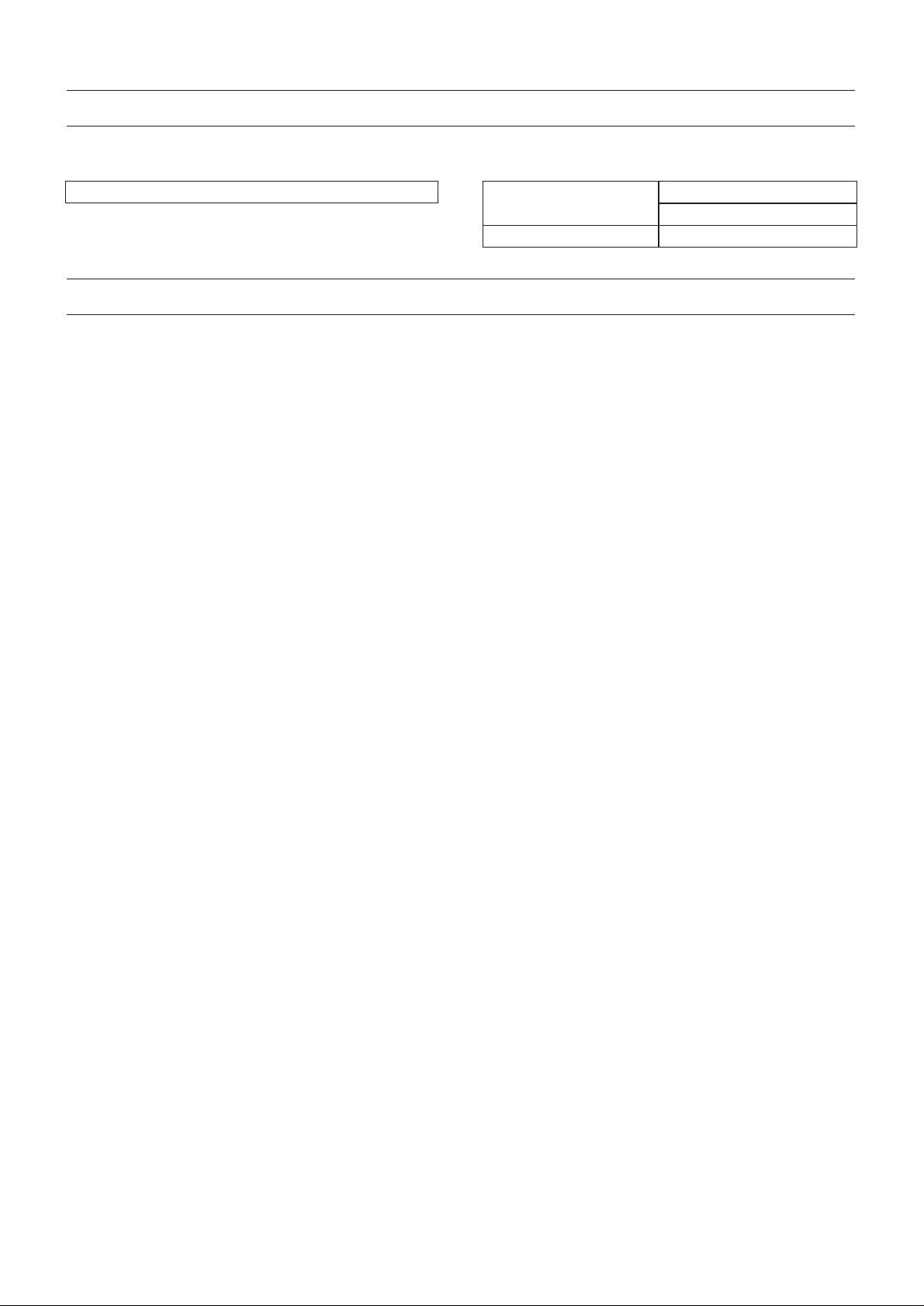

SECTION 1 SPECIFICATIONS

All stated specifications are subject to change without notice or obligation.

Measurement method

Frequency coverage

Type of emission

Number of conventional channels

Antenna impedance

Power supply voltage (negative ground)

Current drain (approx.)

Usable temperature range

Dimensions (proj. not included)

Weight

RF output power

Modulation system

Maximum permissible deviation

Frequency error

Spurious emissions

Adjacent channel power

Audio frequency response

Audio hormonic distortion

FM hum and noise (typical)

(without CCICT filter)

Residual modulation (typical)

(with CCICT filter)

Limitting charact of modulator

Microphone connector

Receive system

Intermediate frequencies

Sensitivity (typical)

Squelch sensitivity (at threshold)

Hum and noise

Adjcent channel selectivity

Spurious response

Intermoduration

Audio output power

External SP connector

[GEN], [USA] [EUR]

RECEIVER TRANSMITTER GENERAL

EIA-152-C/204D or TIA-603 ETS 300 086

136.000–174.000 MHz

N/W: (12.5 kHz; Narrow/25 kHz; Wide): 8K50F3E/16K0F3E [EUR]

(12.5 kHz; Narrow/25 kHz; Wide): 11K0F3E/16K0F3E [GEN]

(15 kHz; Narrow/30 kHz; Wide): 11K0F3E/16K0F3E [USA]

N/M (12.5 kHz; Narrow/20 kHz; Middle): 8K50F3E/14K0F3E [EUR]

maximum 128 channels

50 Ω nominal (SO-239)

13.6 V DC nominal 13.2 V DC nominal

TX; 7.0 A (at 25 W), 14.0 A (at 50 W)

Rx; 1200 mA (maximum audio)

300 mA (stand-by)

–30˚C to +60˚C (–22˚F to +140˚F) –25˚C to +55˚C

150(W)

× 40(H) × 117.5(D) mm; 5

29

⁄32(W) × 49⁄16(H) × 45⁄8(D) inch [25 W]

150(W) × 40(H) × 167.5(D) mm; 529⁄32(W) × 49⁄16(H) × 619⁄32(D) inch [50 W]

0.8 kg; 1 lb 12 oz [25 W], 1.1 kg; 2 lb 7 oz [50 W]

High/Low2/Low1: 25 W/10 W/2.5 W [25 W]

High/Low2/Low1: 50 W/25 W/5 W [50 W]

Variable reactance frequency modulation

±2.5 kHz [Narrow], ±4.0 kHz [Middle], ±5.0 kHz [Wide]

±5.0 ppm ±1.5 kHz

70 dB (typical) 0.25 µW ≤ 1GHz, 1.0 µW > 1 GHz

60 dB minimum [Narrow]; 70 dB minimum [Middle], [Wide]

+2 dB to –5 dB of 6 dB/octave

Range from 300 Hz to 2550 Hz [Narrow] / 3000 Hz [Middle], [Wide]

3% typical at 1 kHz (40% deviation)

34 dB (min.), 40 dB (typ.) [Narrow]

—

40 dB (min.), 46 dB (typ.) [Wide]

40 dB (min.), 50 dB (typ.) [Narrow]

– 43 dB (min.), 53 dB (typ.) [Middle]

45 dB (min.), 55 dB (typ.) [Wide]

70 – 100% of maximum deviation

8-pin modular (600 Ω)

Double-conversion superheterodyne system

1st: 46.35 MHz, 2nd: 450 kHz

0.25 µV typical at 12 dB SINAD –4 dBµV (emf) typical at 20 dB SINAD

0.25 µV typical –4 dBµV (emf) typical

34 dB (min.), 40 dB (typ.) [Narrow]

40 dB (min.), 50 dB (typ.) [Narrow]

40 dB (min.), 45 dB (typ.) [Wide]

43 dB (min.), 53 dB (typ.) [Middle]

45 dB (min.), 55 dB (typ.) [Wide]

60 dB (min.), 65 dB (typ.) [Narrow]

70 dB (min.), 75 dB (typ.) [Middle]/[Wide]

75 dB

70 dB (min.), 74 dB (typ.) 65 dB (min.), 67 dB (typ.)

4 W typical at 10% distortion with a 4 Ω load

2-conductor 3.5 (d) mm (

1

⁄8")/4 Ω

Page 5

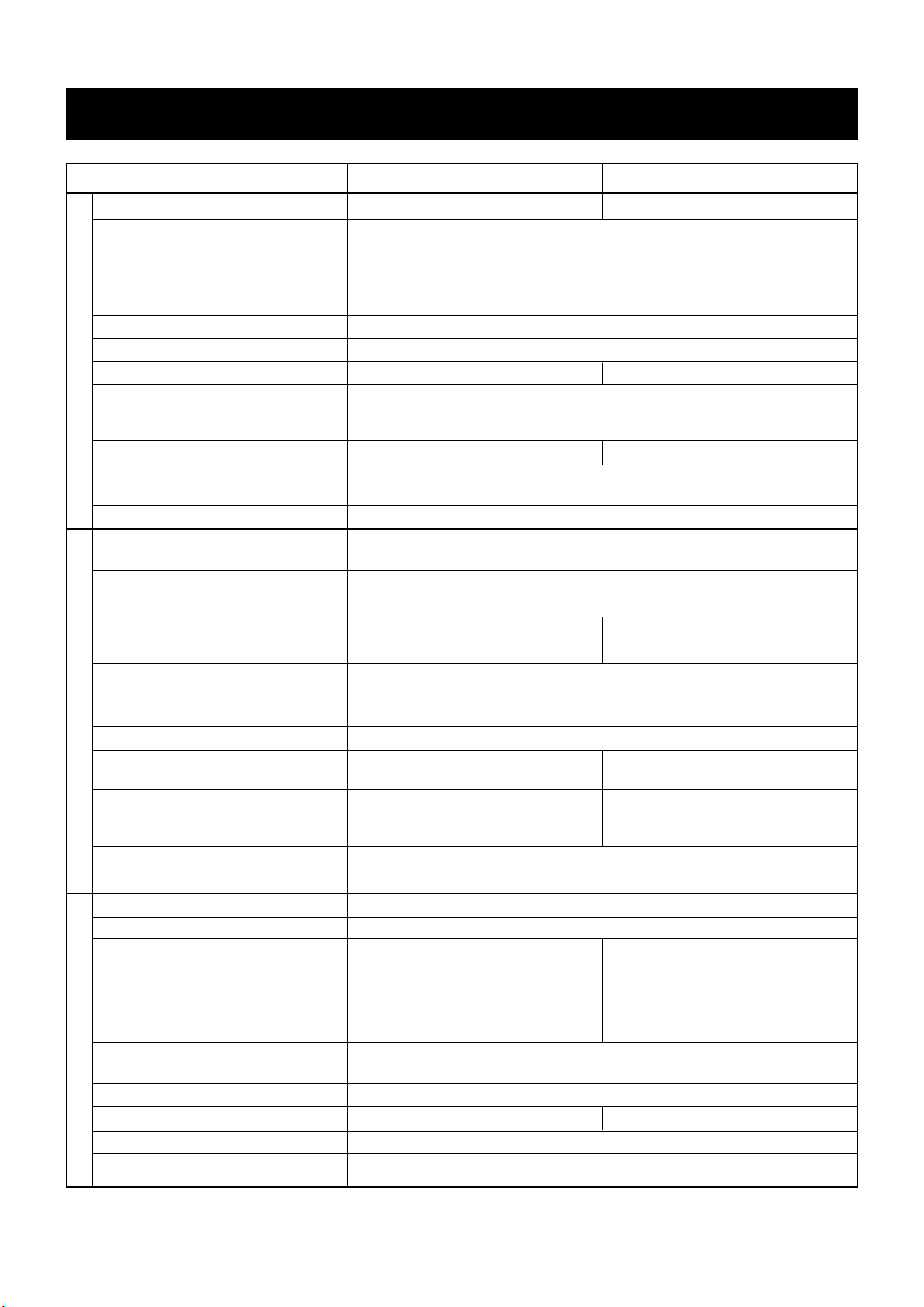

2 - 1

SECTION 2 INSIDE VIEW

Antenna switch/

Low-pass filter circuit

Mixer*

(Q3: 3SK299)

2nd IF filter*

(FI2: ALFYM450F=K)

D/A converter*

(IC6: M62363FP-650C)

IF IC

(IC1: TA31136FN)

1st IF filter

(FI1: FL-335)

* Located under side of the point.

Final FET module

(IC3: S-AV33)

CPU 5V regurator*

(IC10: AN78L05M)

8V regurator

(IC9: TA7808F)

VCO circuit

AF amplifier

(IC8: LA4425A)

Reference crystal oscillator*

(X2: CR-740 15.3 MHz)

PLL IC

(IC4: MB15A02PFV-1)

Page 6

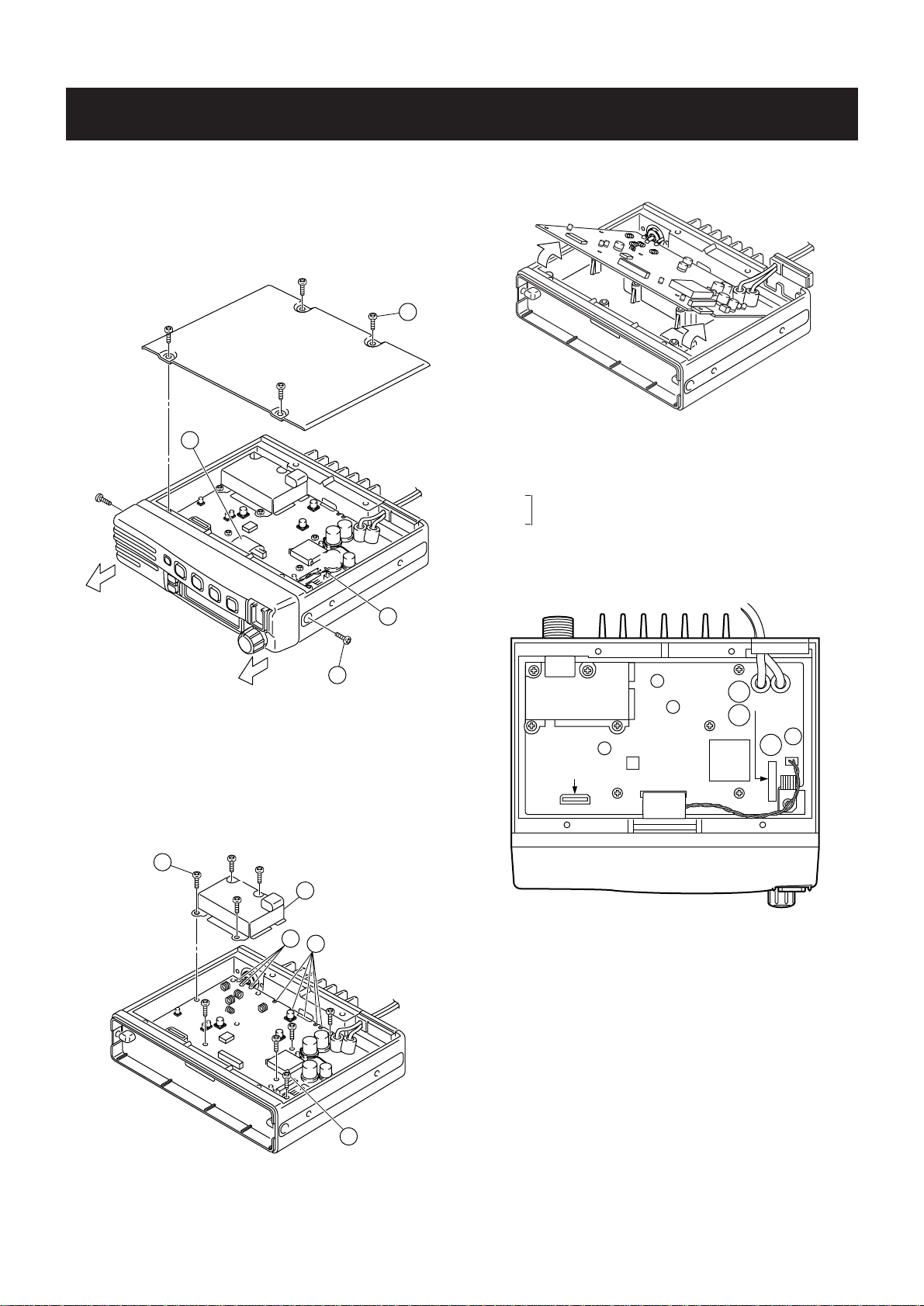

3 - 1

SECTION 3 DISASSEMBLY INSTRUCTIONS

• Opening case

➀ Unscrew 4 screws A, and remove the bottom cover.

➁ Disconnect the flat cable B from J2.

➂ Disconnect the cable C from J7.

➃ Unscrew 2 screws D, and remove the front unit.

B

C

D

A

J2

J7

➄ Unscrew 8 screws E.

➅ Remove the filter case F.

➆ Unscrew the screw G.

➇ Unsolder 3 points H from the antenna connector.

➈ Unsolder 4 points I from IC3.

E

F

G

H

I

➉ Lift up the front portion of the main unit and remove it.

• Installation location

UT-105 SmarTrank 2 logic board

UT-108 DTMF decoder unit

UT-109

Voice scrambler unit

UT-110

UT-111 Trunking unit

OPC-617 ACC cable (for external terminal connection)

UT-105

UT-108

UT-109

UT-110

UT-111

OPC-617

J1

J6

Page 7

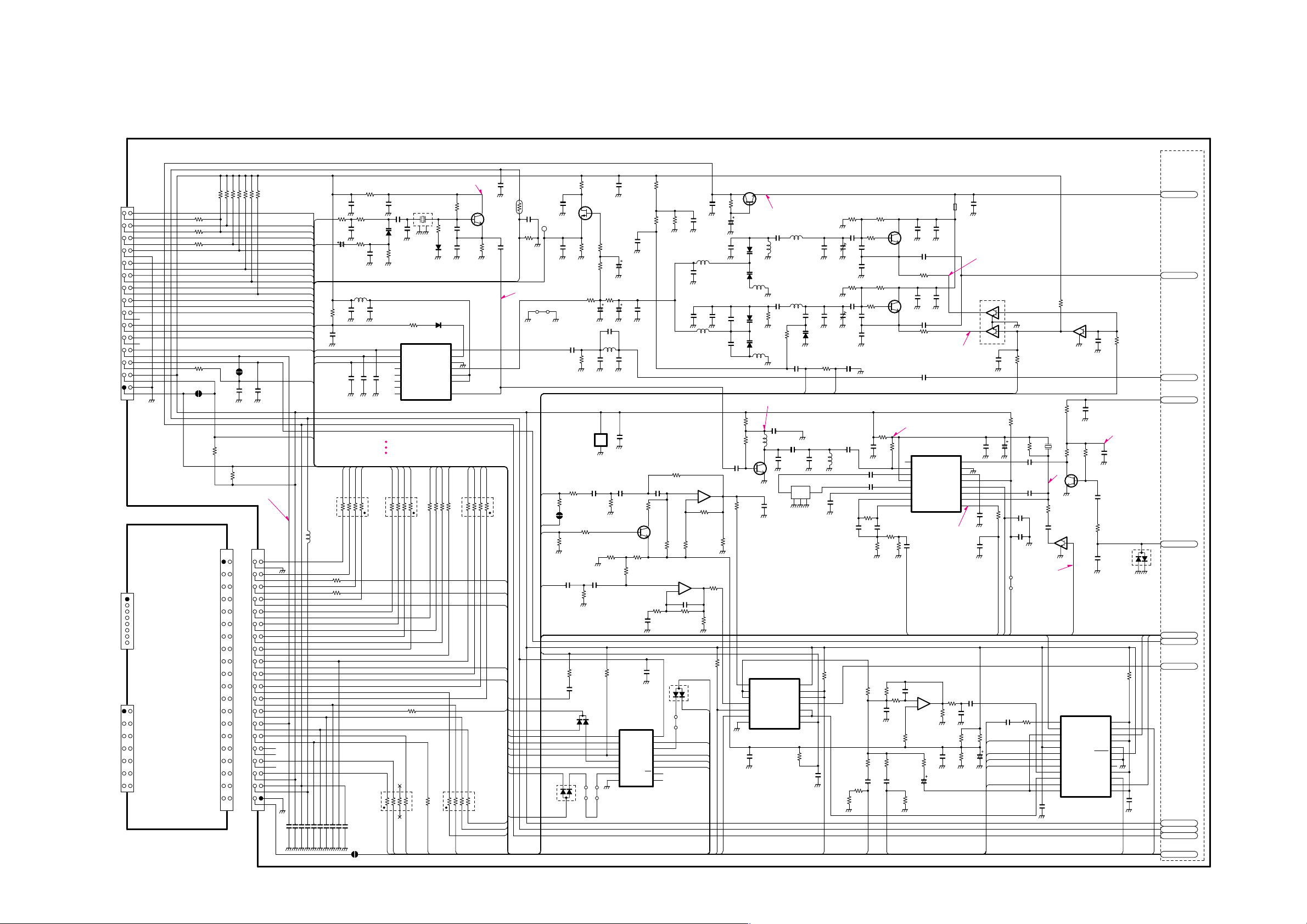

SECTION 4 CIRCUIT DESCRIPTION

4 - 1

4-1 RECEIVER CIRCUITS

4-1-1 ANTENNA SWITCHING CIRCUIT

(MAIN UNIT)

The antenna switching circuit functions as a low-pass filter

while receiving and as resonator circuit while transmitting.

This circuit does not allow transmit signals to enter the

receiver circuits.

Received signals enter the antenna connector and pass

through the low-pass filters (L1–L3, C1, C2, C6–8). The filtered signals are then applied to the RF circuit passed

through the

λ⁄4 type antenna switching circuit (D5–D7, D48,

L4, L6).

4-1-2 RF CIRCUIT (MAIN UNIT)

The RF circuit amplifies signals within the range of frequency coverage and filters out-of-band signals.

The signals from the antenna switching circuit pass through

the two-stage tunable bandpass filters (D8, D4). The filtered

signals are amplified at the RF amplifier (Q2) and then enter

other two-stage bandpass filters (D9, D10) to suppress

unwanted signals. The filtered signals are applied to the 1st

mixer circuit (Q3).

The tunable bandpass filters (D4, D8–D10) employ varactor

diodes to tune the center frequency of the RF passband for

wide bandwidth receiving and good image response rejection. These diodes are controlled by the CPU (FRONT unit;

IC1) via the D/A converter (IC6).

The gate control circuit reduces RF amplifier gain and attenuates RF signal to keep the audio output at a constant level.

The receiver gain is determined by the voltage on the “RSSI”

line from the FM IF IC (IC1, pin 12). The gate control circuit

(Q1) supplies control voltage to the RF amplifier (Q2) and

sets the receiver gain.

When receiving strong signals, the “RSSI” voltage increases

and the gate control voltage decreases. As the gate control

voltage is used for the bias voltage of the RF amplifier (Q2),

then the RF amplifier gain is decreased.

4-1-3 1ST MIXER AND 1ST IF CIRCUITS

(MAIN UNIT)

The 1st mixer circuit converts the received signals to a fixed

frequency of the 1st IF signal with the PLL output frequency.

By changing the PLL frequency, only the desired frequency

will pass through a MCF (Monolithic Crystal Filter; FI1) at the

next stage of the 1st mixer.

The RF signals from the bandpass filter are applied to the

1st mixer circuit (Q3). The applied signals are mixed with the

1st LO signal coming from the RX VCO circuit (Q14) to produce a 46.35 MHz 1st IF signal. The 1st IF signal passes

through a MCF (Monolithic Crystal Filter; FI1) to suppress

out-of-band signals. The filtered signal is amplified at the 1st

IF amplifier (Q4) and applied to the 2nd IF circuit.

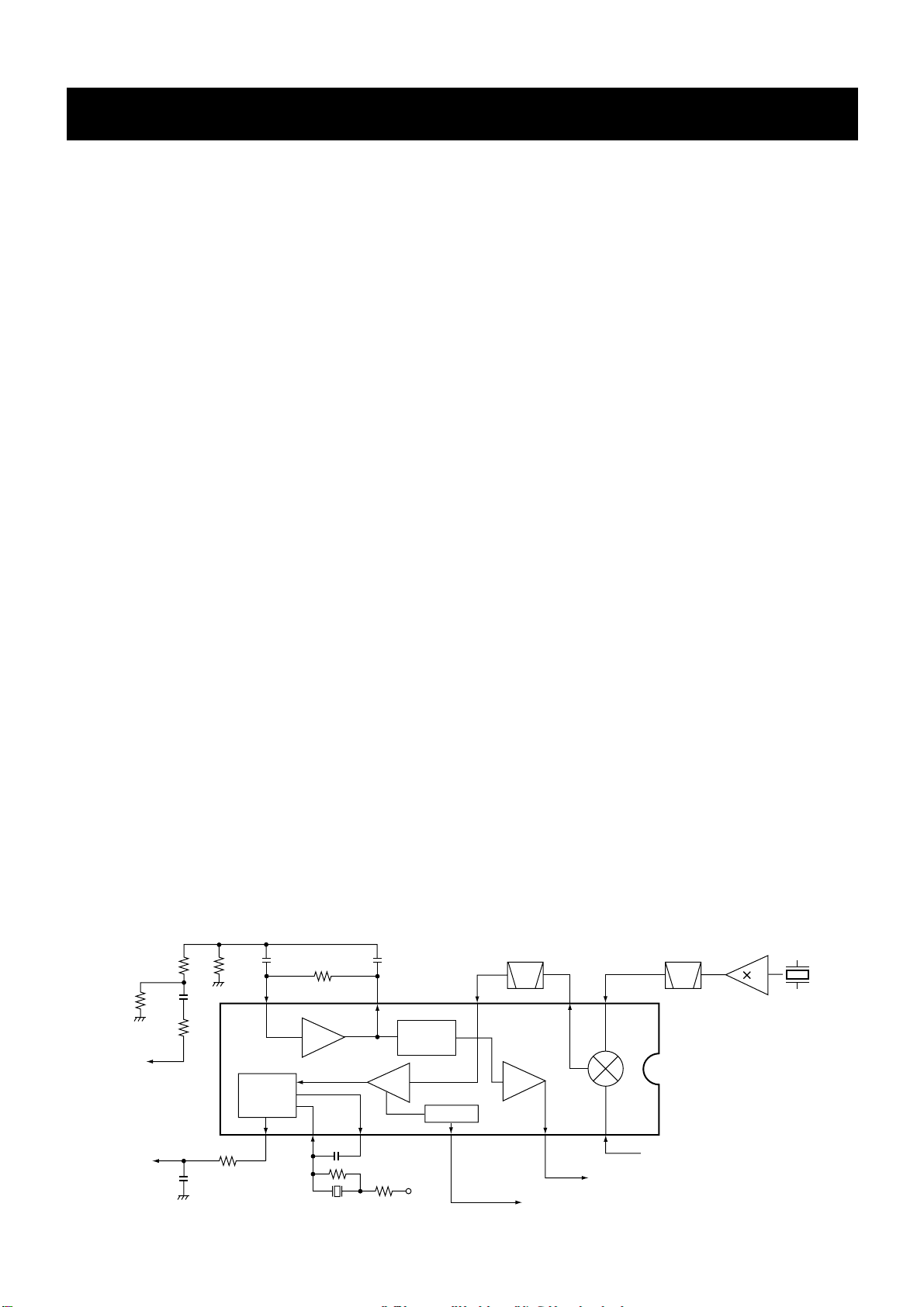

4-1-4 2ND IF AND DEMODULATOR CIRCUITS

(MAIN UNIT)

The 2nd mixer circuit converts the 1st IF signal to a 2nd IF

signal. A double-conversion superheterodyne system

improves the image rejection ratio and obtains stable receiver gain.

The 1st IF signal from the 1st IF amplifier (Q4) is applied to

the 2nd mixer section of the FM IF IC (IC1, pin 16) and is

then mixed with the 2nd LO signal for conversion to a 450

kHz 2nd IF signal.

IC1 contains the 2nd mixer, limiter amplifier, quadrature

detector, active filter and noise amplifier circuits, etc. A

tripled frequency from the PLL reference oscillator is used

for the 2nd LO signal (45.9 MHz).

The 2nd IF signal from the 2nd mixer (IC1, pin 3) passes

through a ceramic filter (FI2) to remove unwanted heterodyned frequencies. It is then amplified at the limiter amplifier section (IC1, pin 5) and applied to the quadrature detector section (IC1, pins 10, 11 and X1) to demodulate the 2nd

IF signal into AF signals.

The AF signals are output from pin 9 (IC1) and are then

applied to the AF amplifier circuit.

• 2ND IF AND DEMODULATOR CIRCUIT

"SQLIN" signal

AF signals

8

Active

filter

FM

detector

X1 Discriminator

Limiter

amp.

7

Noise

detector

5V

RSSI

2nd IF filter

450 kHz

FI2

5

"RSSI" signal to the CPU

45.9 MHz

32

Mixer

161311109

"NOIS" signal to the CPU

BPF

IC1

TA31136FN

1st IF from the IF amplifier (Q4)

Q34

3

X2

15.3 MHz

Page 8

4 - 2

4-1-5 AF AMPLIFIER CIRCUIT (MAIN UNIT)

The AF amplifier circuit amplifies the demodulated AF signals to drive a speaker.

The AF signals from the FM IF IC (IC1, pin 9) are applied to

the active filter circuit (IC16). The active filter circuit (highpass filter) removes CTCSS or DTCS signals.

The filtered AF signals are output from pin 14 (IC16) and are

applied to the de-emphasis circuit (R117, C378) with frequency characteristics of –6 dB/octave, and then passed

through the analog switch (IC14, pins 1–3) and low-pass filter (IC5). The filtered signal is applied to the electronic volume controller (IC6, pin 9).

The output AF signals from the electronic volume controller

(IC6, pin 10) are passed through the analog switch (IC14

pins 9–11) and are applied to the AF amplifier (IC15) and AF

power amplifier (IC8) to drive the speaker.

4-1-6 RECEIVER MUTE CIRCUITS

(MAIN AND FRONT UNITS)

• NOISE SQUELCH

The noise squelch circuit cuts out AF signals when no RF

signals are received. By detecting noise components in the

AF signals, the squelch circuit switches the AF mute switch.

Some noise components in the AF signals from the FM IF IC

(IC1, pin 9) are passed through the level controller (IC6, pins

1, 2). The level controlled signals are applied to the active filter section in the FM IF IC (IC1, pin 8). Noise components

about 10 kHz are amplified and output from pin 7.

The filtered signals are converted to the pulse-type signals

at the noise detector section and output from pin 13 (NOIS).

The NOIS signal from the FM IF IC is applied to the CPU

(FRONT unit; IC1, pin 53). The CPU then analyzes the noise

condition and controls the AF mute signal via “AFON” line

(D44, D45) to the AF mute circuit (Q35, Q36, D29, D30).

• CTCSS AND DTCS

The tone squelch circuit detects AF signals and opens the

squelch only when receiving a signal containing a matching

subaudible tone (CTCSS or DTCS). When tone squelch is in

use, and a signal with a mismatched or no subaudible tone

is received, the tone squelch circuit mutes the AF signals

even when noise squelch is open.

A portion of the AF signals from the FM IF IC (IC1, pin 9)

passes through the low-pass filter (IC16) to remove AF

(voice) signals and is applied to the CTCSS or DTCS

decoder inside the CPU (FRONT unit; IC1, pin 60) via the

“CDEC” line to control the AF mute switch.

4-2 TRANSMITTER CIRCUITS

4-2-1 MICROPHONE AMPLIFIER CIRCUIT

(MAIN AND FRONT UNITS)

The microphone amplifier circuit amplifies audio signals

within +6 dB/octave pre-emphasis characteristics from the

microphone to a level needed for the modulation circuit.

The AF signals (MIC) from the MIC jack (FRONT unit; J1)

are amplified at the AF amplifier (FRONT unit; IC5) and

applied to the MAIN unit via J2 (pin 28). The AF signal are

applied to the limiter amplifier (IC5, pin 5).

The entered signals are pre-emphasized with +6dB/octave

at a limiter amplifier, then passed through the analog switch

(IC14, pins 2–4) and splatter filter (IC5, pins 2, 1). The output signals from the splatter filter are applied to the level

controller (IC6, pin 9).

The deviation level controlled signals are then applied to the

modulation circuit (D18) as the “MOD” signal after being

passed through the analog switch (IC14, pins 9, 8).

4-2-2 MODULATION CIRCUIT

(MAIN AND FRONT UNITS

The modulation circuit modulates the VCO oscillating signal

(RF signal) using the microphone audio signals.

The AF signals from the analog switch (IC14, pin 8) change

the reactance of varactor diode (D18) to modulate the oscillated signal at the TX VCO circuit (Q13, D16, D31). The

modulated VCO signal is amplified at the buffer amplifiers

(Q11, Q10) and is then applied to the drive amplifier circuit

via the T/R switch (D14).

The CTCSS/DTCS signals from the CPU (FRONT unit; IC1,

pins 22–24) are passed through the low-pass filter (FRONT

unit; IC5), and mixer and splatter filter (IC5), and are then

applied to the VCO circuit.

4-2-3 DRIVE AMPLIFIER CIRCUIT (MAIN UNIT)

The drive amplifier circuit amplifies the VCO oscillating signal to the level needed at the power amplifier.

The RF signal from the buffer amplifier (Q10) passes

through the T/R switch (D14) and is amplified at the drive

amplifier circuit (Q8). The amplified signal is applied to the

power amplifier circuit.

Page 9

4 - 3

4-2-4 POWER AMPLIFIER CIRCUIT (MAIN UNIT)

The power amplifier circuit amplifies the driver signal to an

output power level.

The RF signal from the drive amplifier (Q8) is passed

through the low-pass filter circuit (L18, L43, C89, C90, C92,

C380, C381, C510) and applied to the power module (IC3)

to obtain 25 W or 50 W of RF power.

The amplified signal is passed through the antenna switching circuit (D2), low-pass filter and APC detector, and is then

applied to the antenna connector.

Control voltage for the power amplifier (IC3, pin 2) comes

from the APC amplifier (IC2) to stabilize the output power.

The transmit mute switch (D28) controls the APC amplifier

when transmit mute is necessary.

4-2-5 APC CIRCUIT (MAIN UNIT)

The APC circuit protects the power amplifier from a mismatched output load and stabilizes the output power.

The APC detector circuit detects forward signals and reflection signals at D1 and D11 respectively. The combined voltage is at minimum level when the antenna impedance is

matched at 50 Ω, and is increased when it is mismatched.

The detected voltage is applied to the APC amplifier (IC2,

pin 3), and the power setting “T2” signal from the D/A converter (IC6, pin 22), controlled by the CPU (FRONT unit;

IC1), is applied to the other input for reference. When antenna impedance is mismatched, the detected voltage exceeds

the power setting voltage. Then the output voltage of the

APC amplifier (IC2, pin 4) controls the input current of the

drive amplifier (Q8) and power module (IC3) to reduce the

output power.

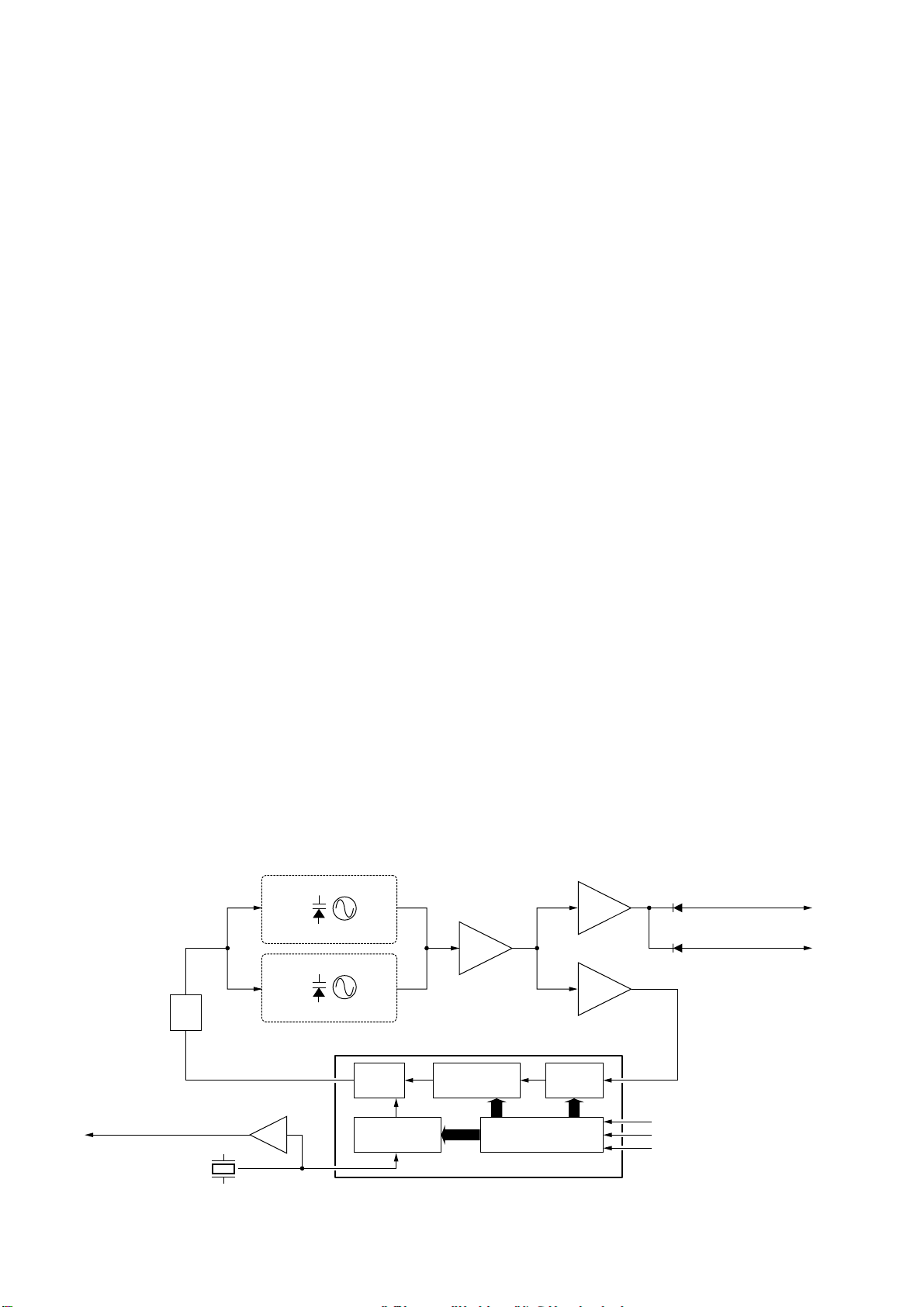

4-3 PLL CIRCUITS

4-3-1 PLL CIRCUIT (MAIN UNIT)

A PLL circuit provides stable oscillation of the transmit frequency and receive 1st LO frequency. The PLL output compares the phase of the divided VCO frequency to the reference frequency. The PLL output frequency is controlled by

the divided ratio (N-data) of a programable divider.

The PLL circuit contains the TX/RX VCO circuit (Q13, Q14).

The oscillated signal is amplified at the buffer amplifiers

(Q11, Q12) and then applied to the PLL IC (IC4, pin 8) via

the low-pass filter (L32, C298–C300).

The PLL IC contains a prescaler, programable counter, programable divider and phase detector, etc. The entered signal is divided at the prescaler and programable counter section by the N-data ratio from the CPU. The reference signal

is generated at the reference oscillator (X2) and is also

applied to the PLL IC. The PLL IC detects the out-of-step

phase using the reference frequency, and outputs it from

pin 5. The output signal is passed through the loop filter

(R97/C149, R96/C147), and is then applied to the VCO circuit as the lock voltage.

If the oscillated signal drifts, its phase changes from that of

the reference frequency, causing a lock voltage change to

compensate for the drift in the oscillated frequency.

4-3-2 VCO CIRCUIT (MAIN UNIT)

The VCO circuit contains a separate RX VCO (Q14, D33,

D34) and TX VCO (Q13, D16, D18, D31). The oscillated signal is amplified at the buffer amplifiers (Q11, Q10) and is

then applied to the T/R switch circuit (D14, D15). Then the

receive 1st LO (Rx) signal is applied to the 1st mixer (Q3)

and the transmit (Tx) signal to the drive amplifier circuit (Q8).

A portion of the signal from the buffer amplifier (Q11) is fed

back to the PLL IC (IC4, pin 8) via the buffer amplifier (Q12)

and low-pass filter (L32, C298–C300) as the comparison

signal.

• PLL CIRCUIT

2nd LO signal to

the FM IF IC

45.9 MHz

15.3 MHz

Loop

filter

X2

Q14, D33, D34

Q13, D18, D19, D31

Tripler

Q34

×3

RX VCO

TX VCO

5

1

Phase

detector

Programmable

divider

Buffer

Q11

Programmable

counter

Buffer

Q10

Buffer

Q12

IC4 MB15A02PFV1

Prescaler

Shift register

10

11

D15

to 1st mixer circuit

D14

to transmitter circuit

8

SCK

9

SO

PLST

Page 10

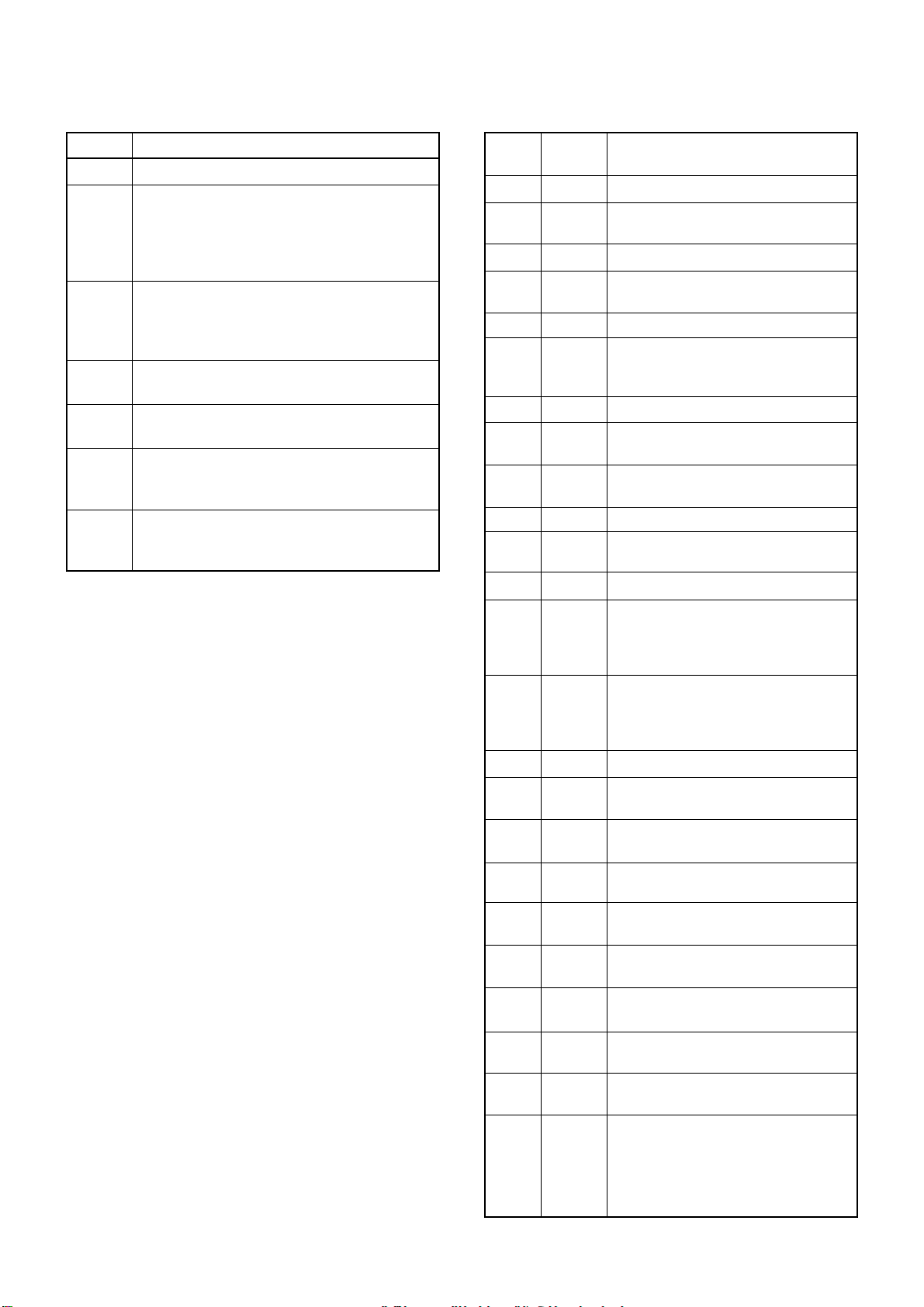

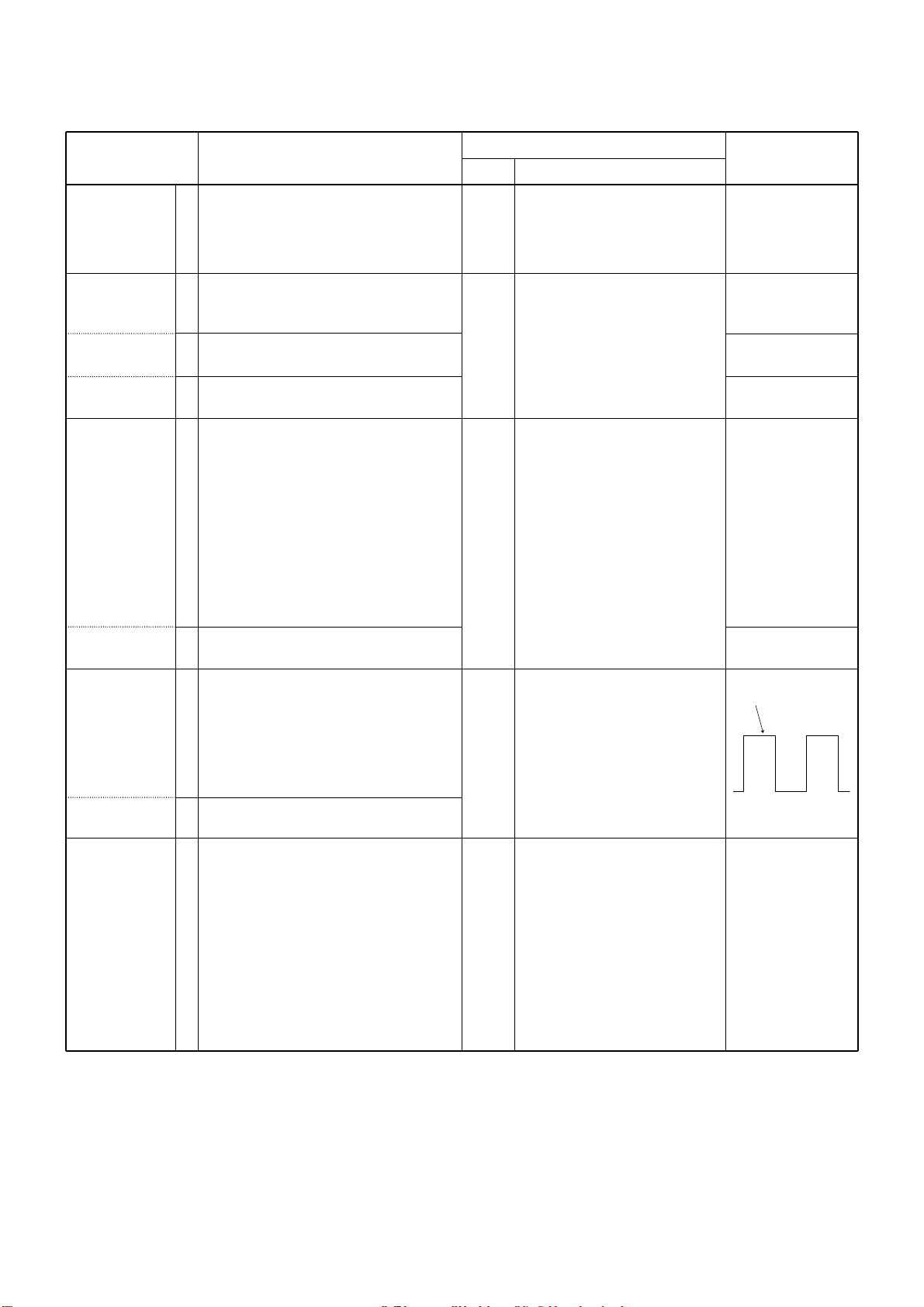

4 - 4

Description

The voltage from a DC power supply.

The same voltage as the HV line which is controlled by the power switching circuit (Q23, Q24).

When the [POWER] switch is pushed, the CPU

outputs the “PWON” control signal to the power

switching circuit to turn the circuit ON.

Common 5 V for the CPU converted from the HV

line by the CPU5V regulator circuit (IC10). The

circuit outputs the voltage regardless of the

power ON/OFF condition.

Common 8 V converted from the VCC line by the

8V regulator circuit (IC9).

Common 5 V converted from the 8 V and CPU5

lines by the 5V regulator circuit (Q27, Q28).

Receive 8 V controlled by the R8 regulator circuit

(Q26, Q30) using the “RXC” signal from the

expander IC (IC17, pin 4).

Transmit 8 V controlled by the T8 regulator circuit

(Q25, Q29, D23) using the “TMUT” signal from

the expander IC (IC17, pin 13).

Line

HV

VCC

CPU5V

8V

5V

R8V

T8V

Input port for the internal temperature.

Input port for the low voltage detection

from the connected power supply.

Input port for reset signal.

Output ports for 5/2 tone and DTMF

signals.

Outputs the CPU clock shift signal.

Outputs cut-off frequency control signal

to the low-pass filter (MAIN unit; IC5)

for CTCSS/DTCS switching.

Input port for the key matrix.

Output ports for 5/2 tone and DTMF

signals.

Input port for the PLL unlock signal

from the PLL IC (MAIN unit; IC4).

Input port for the key matrix.

Output ports for CTCSS/DTCS signals.

Input ports for the key matrix.

Outputs the clock signal to the PLL IC

(MAIN unit; IC4), D/A converter (MAIN

unit; IC6), LED driver (IC4) and optional board (connect to MAIN unit; J1).

Outputs the data signal to the PLL IC

(MAIN unit; IC4), D/A converter (MAIN

unit; IC6) and optional board (connect

to MAIN unit; J1).

Output port for beep sound signal.

I/O port for the data signal for the EEPROM (IC3)

Outputs the clock signal for the EEPROM (IC3).

Outputs the clock signal for the LCD

driver (IC6, pin 17).

Outputs the data signal for the LCD driver (IC6, pin 48).

Outputs the strobe signal for the PLL

IC (MAIN unit; IC4).

Outputs the strobe signal for the D/A

converter IC (MAIN unit; IC6).

Outputs the strobe signal for the

expander IC (IC17).

Outputs the control signal for the LCD

driver IC (IC6).

Outputs the control signal for the power

switching circuit (MAIN unit; Q24,

Q23).

1

2

7

13–14

15

16

17, 18

19–20

21

22

23–25

26, 27

28

29

30

31

32

33

34

36

37

38

39

41

TEMP

BATV

RES

SENC0–

SENC1

CSFT

DUSE

KS0, KS1

SENC2–

SENC3

UNLK

KR0

CENO0–

CENO2

KR1, KR2

SCK

SO

BEEP

ESDA

ESCL

LSCK

LSO

PLST

DAST

EXST

EXOE

PWON

Pin Port

Description

number name

4-4 POWER SUPPLY CIRCUITS

4-4-1 VOLTAGE LINES (MAIN UNIT)

4-5 PORT ALLOCATIONS

4-5-1 CPU (FRONT UNIT; IC1)

Page 11

Outputs dimmer control signal.

High: Dimmter is ON.

Outputs backlight control signal.

High: Backlight is ON.

Output LCD segment signals.

Output LCD common signals.

4 - 5

I/O ports for the optional board control

signals.

Input port for the clock sigal from the

optional board via J1.

Input port for the cloning signal.

Output port for the cloning signal.

Input port for the POWER switch.

• Input port for the remote power control signal from the external connector.(J6)

• Input port for the dimmer control.

Input port for the “NOIS” signal from

the FM IF IC (MAIN unit; IC1) for noise

squelch operation.

Input port for interruption signal from

the optional board via J1.

Outputs chip select signal for the

optional board via J1.

Input port for the PTT switch from

microphone.

Input port for the PTT switch from the

external connector (J6).

Low : External PTT switch is ON.

Input port for the microphone hanger

detection signal.

Low : Microphone on hook.

Input port for the AF volume control

signal (R14).

High : [VOL] is maximum clockwise.

Input port for the CTCSS/DTCS decoding signals.

Input port for the single tone decoding

signal.

Input port for the optional board detection signal.

Input port for receiving signal strength

level detection.

Input port for the PLL lock voltage.

44–46

48

49

50

51

52

83

54

55

56

57

58

59

60

61

62

63

64

OPT3–

OPT1

SI

CLI

CLO

POSW

IGSW

NOIS

CIRQ

CCS

PTT

EPTT

HANG

AFVI

CDEC

SDEC

OPV1V2

RSSI

LVIN

Pin Port

Description

number name

Outputs transmit/receive control signal.

High: While receiving.

Outputs audio output control signal.

High: While receiving.

Outputs wide/narrow control signal.

High: Wide is selected.

Outputs receiving mute control signal.

Low: While receiving is muting.

Outputs transmitting mute control signal.

Low: While transmitting is muting.

Outputs the microphone mute control

signal.

Low: While the microphone is muting.

4

5

6

7

13

14

RXC

AFON

NWC

RMUT

TMUT

MMUT

Pin Port

Description

number name

1

2

3–34

35–38

LIGT1

LIGT2

SEG32–

SEG1

COM4–

COM1

Pin Port

Description

number name

4-5-3 LCD DRIVER (FRONT UNIT; IC6)

4-5-2 OUTPUT EXPANDER (MAIN UNIT; IC17)CPU-Continued

Page 12

5 - 1

SECTION 5 ADJUSTMENT PROCEDURES

5-1 PREPARATION

When you adjust the contents on pages 5-5 and 5-6, SOFTWARE ADJUSTMENT, the optional CS-F100 ADJ

ADJUST-

MENT SOFTWARE (Rev. 1.0 or later), *OPC-1122 JIG CABLE

(modified OPC-1122 CLONING CABLE; see illustration below)

are required.

■ SYSTEM REQUIREMENTS

• IBM PC compatible computer with an RS-232C serial port

(38400 bps or faster).

• Microsoft Windows 95/98 or Windows ME

• Intel Pentium 100 MHz processor or faster

• At least 16 MB RAM and 10 MB of hard disk space

• 640×480 pixel display (800×600 pixel display recommend-

ed)

■ ADJUSTMENT SOFTWARE INSTALLATION

q Boot up Windows.

- Quit all applications when Windows is running.

w Insert the ‘CS-F100’ into the appropriate CD drive.

e Select ‘Run’ from the [Start] menu.

r Type the setup program name using the full path name,

then push [Enter] key.

(ex. D:\CSF100ADJ\Setup.exe)

t Follow the prompts.

y Program group ‘CS-F100 ADJ’ appears in the ‘Programs’

folder of the [Start] menu.

■ STARTING SOFTWARE ADJUSTMENT

q Connect IC-F110 and PC with *OPC-1122 JIG CABLE.

w Turn the transceiver power ON.

e Boot up Windows, and click the program group ‘CS-F100

ADJ’ in the ‘Programs’ folder of the [Start] menu, then

CS-F100 ADJ’s window appears.

r Click ‘Connect’ on the CS-F100 ADJ’s window, then

appears IC-F110’s up-to-date condition.

t Set or modify adjustment data as desired.

IBM is a registered trademark of International Bussiness

Machines Corporation in the U.S.A. and other countries.

Microsoft and Windows are registered trademarks of

Microsoft Corporation in the U.S.A. and other countries.

Screen shots produced with permission from Microsoft

Corporation. All other products or brands are registered

trademarks or trademarks of their respective holders.

• *OPC-1122 (JIG CABLE)

OPC-1122

(Cloning cable)

PTTE

PTT

MIC

MICE

Electrolytic

capacitor

47 F

Add a jumper wire here

PTT switch

+

Audio generator

300 Hz to 3 kHz

AC

millivoltmeter

Page 13

5 - 2

Personal

computer

to the MIC

connector

to an RS-232C port

DB9 female plug

RS-232C cable

(straight)

*OPC-1122

(JIG CABLE)

AC millivoltmeter

Audio generator

FM deviation meter

(DC measurable)

Attenuator

40 dB or 50 dB

to the antenna connector

to DC cable

Standard signal generator

127 to 17 dBm

(0.1 V to 32 mV)

CAUTION:

DO NOT transmit while

the SSG is connected to

the antenna connector.

RF power meter

50 / 1 50 W

DC power supply

13.2 V / 15 A

Frequency

counter

• CONNECTIONS

■ REQUIRED TEST EQUIPMENT

EQUIPMENT

DC power supply

RF power meter

(terminated type)

Frequency counter

FM deviation meter

DC voltmeter

GRADE AND RANGE

Output voltage : 13.2 V DC

Current capacity : 15 A or more

Measuring range : 1–100 W

Frequency range : 100–300 MHz

Impedance : 50 Ω

SWR : Less than 1.2 : 1

Frequency range : 0.1–300 MHz

Frequency accuracy : ±1 ppm or better

Sensitivity : 100 mV or better

Frequency range : DC–300 MHz

Measuring range : 0 to ±10 kHz

Input impedance : 50 kΩ/V DC or better

EQUIPMENT

Audio generator

Standard signal

generator (SSG)

Oscilloscope

AC millivoltmeter

External speaker

Attenuator

GRADE AND RANGE

Frequency range : 300–3000 Hz

Measuring range : 1–500 mV

Frequency range : 0.1–300 MHz

Output level : 0.1 µV–32 mV

(–127 to –17 dBm)

Frequency range : DC–20 MHz

Measuring range : 0.01–20 V

Measuring range : 10 mV–10 V

Input impedance : 4 Ω

Capacity : 7 W or more

Power attenuation : 40 or 50 dB

Capacity : 50 W or more

Page 14

5 - 3

• SCREEN DISPLAY EXAMPLE

CS-F100 ADJ Rev.1.0

File

Option

1

COM 1: OPEN

Connect

2

Reload (F5) Disp para

10

12

14

16

4

5

6

7

8

9

11

13

15

[A / D]

VIN : 178 : B2h : 19.96 V

TEMPS : 177 : B1h : 26.44 ’C

LVIN : 176 : B0h : 3.45 V

SD : 23 : 17h : 0.45 V

CH No. : 01 RX Freq = 136.200000, TX Freq = < RF Power: High Mode: Wide

Power (Hi) : 198 [ # # # # # # # # # # # # # # # # # ]

Power (L2) : 115 [ # # # # # # # # # ]

Power (L1) : 52 [ # # # # ]

BAL W : 155 [ # # # # # # # # # # # ]

BAL Ratio : 128 [ # # # # # # # # # ]

MOD W : 212 [ # # # # # # # # # # # # # # # # # ]

MOD Ratio : 132 [ # # # # # # # # # ]

CTCS/DTCS : 186 [ # # # # # ]

SQL : 0 [ # # # # # # # # # # # # # # # ]

BPF ALL : [Enter] to sweep

BPF T1 : 21 [ # # # # # # # # # # # ] [Enter] to sweep

BPF T2 : 4 [ # # # # # # # # # ] [Enter] to sweep

TXF : [Enter] to start

S-Meter : [Enter] to start

[D / A]

BPF T1 : 197 : 32h : 0.98 V

T2/POW : 172 : 32h : 0.98 V

REF : 125 : 2Dh : 0.88 V

MOD BAL : 149 : 36h : 21.18

Dev : 0 : 00h : 0.00 V

CTCSS : 174 : AEh : 3.41 V

SQL Lev : 0 : 00h : 0.00

AGC : 255 : FFh : 5.00 V

3

NOTE:

1

2

3

4

5

6

7

8

The above values for settings are example only.

Each transceiver has its own specific values for each setting.

: Transceiver’s connection state

: Reload adjustment data

: Receive sensitivity measurement

: Connected DC voltage

: PLL lock voltage

: Operating channel select

: RF output power

: Modulation balance

9

: FM deviation

: CTCSS/DTCS deviation

10

: Squelch level

11

: Receive sensitivity (automatically)

12

: Receive sensitivity (manually)

13

: Reference frequency

14

: S-meter

15

: Adjustment items

16

Page 15

5 - 4

5-2 PLL ADJUSTMENT

PLL LOCK

VOLTAGE

1

2

3

4

• Operating freq. : 174.000 MHz

• Receiving

• Output power : Low1

• Transmitting

• Operating freq. : 136.000 MHz

• Receiving

• Output power : Low1

• Transmitting

MAIN Connect a digital multi-

meter or an oscilloscope to the check

point, “LV”.

3.2 V

3.6 V

0.9–1.5 V

0.8–1.4 V

MAIN C134

C133

Verify

ADJUSTMENT ADJUSTMENT CONDITIONS

UNIT LOCATION

VALUE

UNIT ADJUST

MEASUREMENT ADJUSTMENT

DC power supply

13.2 V / 15 A

LV

PLL lock voltage

check point

C134

PLL lock voltage

adjustment for RX

C133

PLL lock voltage

adjustment for TX

Page 16

5 - 5

5-3 SOFTWARE ADJUSTMENT

Select an operation using [↑] / [↓] keys, then set specified value using [←] / [→] keys on the connected computer keyboard.

1

1

2

3

1

2

1

2

1

• Operating freq. : 174.000 MHz

• Output power : Low1

• Connect the RF power meter or 50 Ω

dummy load to the antenna connector.

• Transmitting

• Operating freq. : 155.000 MHz

• Output power : High

• Transmitting

• Output power : Low2

• Transmitting

• Output power : Low1

• Transmitting

• Operating freq. : 155.000 MHz

• Output power : Low1

• IF bandwidth : Wide

• Connect an audio generator to the [MIC]

jack through the JIG cable and set as:

1.0 kHz/40 mVrms

• Set an FM deviation meter as:

HPF : OFF

LPF : 20 kHz

De-emphasis: OFF

Detector : (P–P)/2

• Transmitting

• IF bandwidth : Narrow

• Transmitting

• Set to the DTCS set channel, and push

[Connect] on the Adjustment software.

• Operating freq. : 155.000 MHz

• Output power : Low1

• Transmitting

• IF bandwidth : Narrow

• Transmitting

• Operating freq. : 155.000 MHz

• Output power : Low1

• IF bandwidth : Wide

• CTCSS : 151.4 Hz

• DTCS code : 007

• Set the FM deviation meter as:

HPF : OFF

LPF : 20 kHz

De-emphasis: OFF

Detector : (P–P)/2

• No audio applied to the [MIC] connector.

• Transmitting

REFERENCE

FREQUENCY

[TXF]

OUTPUT

POWER

[Power (Hi)]

[Power (L2)]

[Power (L1)]

FM

DEVIATION

[MOD W]

[MOD Ratio]

MODULATION

BALLANCE

[BAL W]

[BAL Ratio]

CTCSS/DTCS

DEVIATON

[CTCS/DTCS]

Rear

panel

Rear

panel

Rear

panel

Rear

panel

Rear

panel

Loosely couple a frequnecy

counter to the antenna connector.

Connect an RF power meter to

the antenna connector.

Connect an FM deviation meter

to the antenna connector

through the attenuator.

Connect an FM deviation meter

with an oscilloscope to the

antenna connector through an

attenuator.

Connect an FM deviation meter

to the antenna connector

through the attenuator.

174.0000 MHz

25.0 W (25 W type)

50.0 W (50 W type)

10.0 W (25 W type)

25.0 W (50 W type)

2.5 W (25 W type)

5.0 W (50 W type)

±4.1 kHz [N/W]

±3.3 kHz [N/M]

±2.1 kHz

±0.7 kHz [N/W]

±0.56 kHz [N/W]

ADJUSTMENT ADJUSTMENT CONDITION

MEASUREMENT

VALUE

UNIT

LOCATION

Set to square wave

form

Page 17

5 - 6

*The output level of the standard signal generator (SSG) is indicated as the SSG’s open circuit.

SOFTWARE ADJUSTMENT – continued

Select an operation using [↑] / [↓] keys, then set specified value using [←] / [→] keys on the connected computer keyboard.

Minimum distortion

level

Set “SQL level” to

close squelch.

Then set “SQL level”

at the point where

the audio signals

just appears.

1

1

1

2

• Operating freq. : 136.000 MHz

• IF bandwidth : Wide

• Connect a standard signal generator to

the antenna connector and set as:

Frequency : 136.000 MHz

Level : 10 µV* (–87 dBm)

Modulation : 1 kHz

Deviation : ±3.5 kHz [N/W]

±2.8 kHz [N/M]

• Receiving

• Operating freq. : 136.000 MHz

• IF bandwidth : Narrow

• Connect an SSG to the antenna con-

nector and set as:

Frequency : 136.000 MHz

Level : 0.2 µV* (–121 dBm)

Modulation : 1 kHz

Deviation : ±1.75 kHz

• Receiving

• Operating freq. : 136.000 MHz

• IF bandwidth : Wide

• Connect an SSG to the antenna con-

nector and set as:

Frequency : 136.000 MHz

Level : 14 µV* (–84 dBm)

Modulation : 1 kHz

Deviation : ±3.5 kHz [N/W]

±2.8 kHz [N/M]

• Receiving

• Set an SSG as:

Level : 0.45 µV* (–114 dBm)

RX

SENSITIVITY

[BPF T1],

[BPF T2]

SQUELCH

LEVEL

[SQL]

S-METER

[S-METER]

(S3 LEVEL)

(S1 LEVEL)

MAIN

Rear

panel

Connect a SINAD meter with a

4 Ω load to the external [SP]

jack.

Connect a SINAD meter with a

4 Ω load to the external [SP]

jack.

ADJUSTMENT ADJUSTMENT CONDITION

MEASUREMENT

VALUE

UNIT

LOCATION

CONVENIENT:

The BPF T1–BPF T2 can be adjusted automatically.

q-1: Set the cursol to “BPF ALL” on the adjustment program and then push [ENTER] key.

q-2: The connected PC tunes BPF T1, BPF T2 to peak levels.

or

w-1: Set the cursol to BPF T1 or BPF T2 as desired.

w-2: Push [ENTER] key to start tuning.

w-3: Repeat w-1 and w-2 to perform additional BPF tuning.

• Adjusting S3 and S1’s S-meter level automatically when

push the return key on the key board.

Page 18

[FRONT UNIT][FRONT UNIT]

IC1 1140011260 S.IC HD6433687A11FP (FX-2622A)

IC2 1110005770 S.IC S-80942CNMC-G9C-T2

IC3 1140008650 S.IC HN58X2464TI

IC5 1110005340 S.IC NJM12902V-TE1

IC6 1130009090 S.IC LC75834W

Q1 1530002850 S.TRANSISTOR 2SC4116-BL (TE85R)

Q2 1590001050 S.TRANSISTOR DTC114TUA T106

Q3 1590000430 S.TRANSISTOR DTC144EUA T106

Q5 1590001050 S.TRANSISTOR DTC114TUA T106

D1 1790000950 S.ZENER MA8056-M (TX)

D2 1790000950 S.ZENER MA8056-M (TX)

D3 1790000950 S.ZENER MA8056-M (TX)

D4 1790000620 S.DIODE MA77 (TX)

D5 1790001250 S.DIODE MA2S111-(TX)

X1 6050009520 S.XTAL CR-520 (19.6608 MHz+)

L1 6200003640 S.COIL MLF1608E 100K-T

L2 6200001980 S.COIL NL 252018T-1R0J

R7 7030009160 S.RESISTOR ERJ2GEJ 181 X (180 Ω)

R8 7030009160 S.RESISTOR ERJ2GEJ 181 X (180 Ω)

R9 7030005000 S.RESISTOR ERJ2GEJ 471 X (470 Ω)

R11 7030009280 S.RESISTOR ERJ2GE

R12 7030009140 S.RESISTOR ERJ2GEJ 272 X (2.7 kΩ)

R14 7210003020 VARIABLE EVU-F2KFK1 B14 (10KB)

R15 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R16 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R18 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R19 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R20 7030008300 S.RESISTOR ERJ2GEJ 184 X (180 kΩ)

R21 7030005720 S.RESISTOR ERJ2GEJ 563 X (56 kΩ)

R22 7030005220 S.RESISTOR ERJ2GEJ 223 X (22 kΩ)

R23 7030005240 S.RESISTOR ERJ2GEJ 473 X (47 kΩ)

R24 7030005240 S.RESISTOR ERJ2GEJ 473 X (47 kΩ)

R25 7030005220 S.RESISTOR ERJ2GEJ 223 X (22 kΩ)

R26 7030005240 S.RESISTOR ERJ2GEJ 473 X (47 kΩ)

R27 7030005240 S.RESISTOR ERJ2GEJ 473 X (47 kΩ)

R28 7030005040 S.RESISTOR ERJ2GEJ 472 X (4.7 kΩ)

R29 7030008290 S.RESISTOR ERJ2GEJ 183 X (18 kΩ)

R30 7030005110 S.RESISTOR ERJ2GEJ 224 X (220 kΩ)

R31 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R32 7030005240 S.RESISTOR ERJ2GEJ 473 X (47 kΩ)

R33 7030005220 S.RESISTOR ERJ2GEJ 223 X (22 kΩ)

R34 7030005220 S.RESISTOR ERJ2GEJ 223 X (22 kΩ)

R35 7030005070 S.RESISTOR ERJ2GEJ 683 X (68 kΩ)

R36 7030005070 S.RESISTOR ERJ2GEJ 683 X (68 kΩ)

R37 7030005070 S.RESISTOR ERJ2GEJ 683 X (68 kΩ)

R38 7030005070 S.RESISTOR ERJ2GEJ 683 X (68 kΩ)

R39 7030005070 S.RESISTOR ERJ2GEJ 683 X (68 kΩ)

R40 7030005240 S.RESISTOR ERJ2GEJ 473 X (47 kΩ)

R41 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R42 7030007350 S.RESISTOR ERJ2GEJ 393 X (39 kΩ)

R43 7030005060 S.RESISTOR ERJ2GEJ 333 X (33 kΩ)

R44 7030005100 S.RESISTOR ERJ2GEJ 154 X (150 kΩ)

R45 7030005530 S.RESISTOR ERJ2GEJ 100 X (10 Ω)

R46 7030005160 S.RESISTOR ERJ2GEJ 105 X (1 MΩ)

R47 7030008010 S.RESISTOR ERJ2GEJ 123 X (12 kΩ)

R48 7030008010 S.RESISTOR ERJ2GEJ 123 X (12 kΩ)

R49 7030008010 S.RESISTOR ERJ2GEJ 123 X (12 kΩ)

R50 7410001130 S.ARRAY EXB28V102JX

R51 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R52 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R54 7410001130 S.ARRAY EXB28V102JX

R55 7410000770 S.ARRAY EXB-V4V 102JV (1 kΩ)

R56 7410001130 S.ARRAY EXB28V102JX

R57 7030005160 S.RESISTOR ERJ2GEJ 105 X (1 MΩ)

R58 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R59 7310002740 S.TRIMMER RV-150 (RH03A3A14X0FC) 103

S.=Surface mount

R60 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R65 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R67 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R68 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R73 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R74 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R75 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R76 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R77 7030005030 S.RESISTOR ERJ2GEJ 152 X (1.5 kΩ)

R78 7030005240 S.RESISTOR ERJ2GEJ 473 X (47 kΩ)

R79 7410000770 S.ARRAY EXB-V4V 102JV (1 kΩ)

R80 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R81 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R82 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R83 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R84 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R85 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R86 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R87 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R88 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R89 7030005090 S.RESISTOR ERJ2GEJ 104 X (100 kΩ)

R90 7030006610 S.RESISTOR ERJ2GEJ 394 X (390 kΩ)

C1 4030018100 S.CERAMIC ECJ0EB1H681K

C2 4030017420 S.CERAMIC ECJ0EC1H470J

C3 4030017420 S.CERAMIC ECJ0EC1H470J

C4 4030017420 S.CERAMIC ECJ0EC1H470J

C5 4030017420 S.CERAMIC ECJ0EC1H470J

C6 4030017420 S.CERAMIC ECJ0EC1H470J

C7 4030017420 S.CERAMIC ECJ0EC1H470J

C8 4030017460 S.CERAMIC ECJ0EB1E102K

C9 4030017460 S.CERAMIC ECJ0EB1E102K

C10 4030017460 S.CERAMIC ECJ0EB1E102K

C11 4030017420 S.CERAMIC ECJ0EC1H470J

C12 4030017460 S.CERAMIC ECJ0EB1E102K

C14 4030017460 S.CERAMIC ECJ0EB1E102K

C15 4030016780 S.CERAMIC ECJ0EB1C153K

C16 4030016930 S.CERAMIC ECJ0EB1A104K

C17 4030017740 S.CERAMIC ECJ0EB1E821K

C19 4030016930 S.CERAMIC ECJ0EB1A104K

C20 4030018110 S.CERAMIC ECJ0EB1H272K

C21 4030018240 S.CERAMIC ECJ0EB1E562K

C22 4030017710 S.CERAMIC ECJ0EC1H181J

C23 4030018090 S.CERAMIC ECJ0EB1C822K

C24 4030017510 S.CERAMIC ECJ0EC1H680J

C25 4030016790 S.CERAMIC ECJ0EB1C103K

C26 4030016930 S.CERAMIC ECJ0EB1A104K

C27 4030017450 S.CERAMIC ECJ0EB1E271K

C28 4030016930 S.CERAMIC ECJ0EB1A104K

C29 4550006050 S.TANTALUM TEMSVA 0J 106M8L

C30 4030017030 S.CERAMIC ECJ0EB1A273K

C31 4030017400 S.CERAMIC ECJ0EC1H220J

C32 4030017640 S.CERAMIC ECJ0EC1H150J

C33 4030017510 S.CERAMIC ECJ0EC1H680J

C34 4030017730 S.CERAMIC ECJ0EB1E471K

C35 4030016930 S.CERAMIC ECJ0EB1A104K

C36 4030016930 S.CERAMIC ECJ0EB1A104K

C37 4030017420 S.CERAMIC ECJ0EC1H470J

C38 4030017420 S.CERAMIC ECJ0EC1H470J

C41 4030017460 S.CERAMIC ECJ0EB1E102K

C50 4030017420 S.CERAMIC ECJ0EC1H470J

C54 4030017420 S.CERAMIC ECJ0EC1H470J

C69 4030017420 S.CERAMIC ECJ0EC1H470J

C74 4030017420 S.CERAMIC ECJ0EC1H470J

C75 4030016930 S.CERAMIC ECJ0EB1A104K

C76 4030016930 S.CERAMIC ECJ0EB1A104K

C77 4030016950 S.CERAMIC ECJ0EB1A473K

C78 4030017460 S.CERAMIC ECJ0EB1E102K

C79 4030016930 S.CERAMIC ECJ0EB1A104K

C80 4030016930 S.CERAMIC ECJ0EB1A104K

C81 4030017460 S.CERAMIC ECJ0EB1E102K

C82 4030017420 S.CERAMIC ECJ0EC1H470J

C83 4030017420 S.CERAMIC ECJ0EC1H470J

C84 4030017420 S.CERAMIC ECJ0EC1H470J

C85 4030017420 S.CERAMIC ECJ0EC1H470J

6 - 1

SECTION 6 PARTS LIST

REF ORDER

DESCRIPTION

NO. NO.

REF ORDER

DESCRIPTION

NO. NO.

A: [F110] B: [F111] and [F121] C: IC-F110 for [EUR]

D: IC-F110 for [GEN] E: IC-F110 for 25 kHz F: IC-F110 for 20 kHz

Page 19

S.=Surface mount

[MAIN UNIT][FRONT UNIT]

J1 6450002210 CONNECTOR 3017-8821 <KIN>

J2 6510022470 S.CONNECTOR 40FLT-SM1-TB

DS1 5040002310 S.LED SML-311YTT86

DS2 5040002310 S.LED SML-311YTT86

DS3 5040002310 S.LED SML-311YTT86

DS4 5040002310 S.LED SML-311YTT86

DS5 5040002310 S.LED SML-311YTT86

DS6 5040002310 S.LED SML-311YTT86

DS7 5040002310 S.LED SML-311YTT86

DS8 5040002310 S.LED SML-311YTT86

DS9 5040002310 S.LED SML-311YTT86

DS11 5030002510 LCD L2-0607TAY

SP1 2510001220 SPEAKER C052SB500-13

W1 8900010500 CABLE OPC-1046

EP1 0910055684 PCB B 5910D

EP2 8930059170 LCD CONTACT SRCN-2622-SP-N-W

IC1 1110003490 S.IC TA31136FN (D,EL)

IC2 1110002750 S.IC TA75S01F (TE85R)

IC3 1150002100 IC S-AV32 (I)

B

1150002110 IC S-AV33 (I) A

IC4 1140005990 S.IC MB15A02PFV1-G-BND-ER

IC5 1110005330 S.IC NJM12904V-TE1

IC6 1190000350 S.IC M62363FP-650C

IC8 1110003090 IC LA4425A

IC9 1180001250 S.IC TA7808F (TE16L)

IC10 1180000970 S.IC AN78L05M-(E1)

IC14 1130008090 S.IC BU4066BCFV-E1

IC15 1110002750 S.IC TA75S01F (TE85R)

IC16 1110005340 S.IC NJM12902V-TE1

IC17 1130007570 S.IC BU4094BCFV-E2

Q1 1560000840 S.FET 2SK1829 (TE85R)

Q2 1580000730 S.FET 3SK293 (TE85L)

Q3 1580000760 S.FET 3SK299-T1 U73

Q4 1530002600 S.TRANSISTOR 2SC4215-O (TE85R)

Q5 1590000430 S.TRANSISTOR DTC144EUA T106

Q8 1530000370 S.TRANSISTOR 2SC3356-T1B

Q10 1530003310 S.TRANSISTOR 2SC5107-O (TE85R)

Q11 1530003310 S.TRANSISTOR 2SC5107-O (TE85R)

Q12 1530003310 S.TRANSISTOR 2SC5107-O (TE85R)

Q13 1530002920 S.TRANSISTOR 2SC4226-T1 R25

Q14 1530002920 S.TRANSISTOR 2SC4226-T1 R25

Q15 1590001400 S.TRANSISTOR XP1214 (TX)

Q16 1590000430 S.TRANSISTOR DTC144EUA T106

Q17 1530002850 S.TRANSISTOR 2SC4116-BL (TE85R)

Q18 1560000540 S.FET 2SK880-Y (TE85R)

Q19 1530002600 S.TRANSISTOR 2SC4215-O (TE85R)

Q20 1530002850 S.TRANSISTOR 2SC4116-BL (TE85R)

B only

Q23 1550000020 S.FET 2SJ377 (TE16R)

Q24 1590000430 S.TRANSISTOR DTC144EUA T106

Q25 1540000550 S.TRANSISTOR 2SD1664 T100Q

Q26 1510000920 S.TRANSISTOR 2SA1577 T106 Q

Q27 1510000920 S.TRANSISTOR 2SA1577 T106 Q

Q28 1590001190 S.TRANSISTOR XP6501-(TX) .AB

Q29 1590001050 S.TRANSISTOR DTC114TUA T106

Q30 1590000430 S.TRANSISTOR DTC144EUA T106

Q31 1590001450 S.FET 2SJ144-GR (TE85R)

Q33 1590000430 S.TRANSISTOR DTC144EUA T106

Q34 1530002850 S.TRANSISTOR 2SC4116-BL (TE85R)

Q35 1590000990 S.TRANSISTOR DTC363EK T146

Q36 1590000430 S.TRANSISTOR DTC144EUA T106

Q37 1590000430 S.TRANSISTOR DTC144EUA T106

Q38 1530003090 S.TRANSISTOR 2SC4213-B (TE85R)

D1 1790001210 S.DIODE 1SS375-TL

D2 1750000510 S.DIODE UM9401F A only

D3 1710001060 DIODE XB15A407 B only

D4 1750000720 S.VARICAP HVC375BTRF

D5 1750000510 S.DIODE UM9401F

D6 1790000620 S.DIODE MA77 (TX)

D7 1790001240 S.DIODE MA2S728-(TX)

D8 1750000720 S.VARICAP HVC375BTRF

D9 1750000710 S.VARICAP HVC350BTRF

D10 1750000710 S.VARICAP HVC350BTRF

D11 1790001210 S.DIODE 1SS375-TL

D12 1790001210 S.DIODE 1SS375-TL

B only

D14 1790000620 S.DIODE MA77 (TX)

D15 1790000620 S.DIODE MA77 (TX)

D16 1750000770 S.VARICAP HVC376BTRF

D18 1720000470 S.VARICAP 1SV239 (TPH3)

D20 1790001250 S.DIODE MA2S111-(TX)

D21 1750000830 S.VARICAP HVC362TRF

D22 1790000700 DIODE DSA3A1

D23 1750000370 S.DIODE DA221 TL

D26 1790001250 S.DIODE MA2S111-(TX)

D27 1790001250 S.DIODE MA2S111-(TX)

D28 1790001240 S.DIODE MA2S728-(TX)

D29 1790001250 S.DIODE MA2S111-(TX)

D31 1750000770 S.VARICAP HVC376BTRF

D33 1750000770 S.VARICAP HVC376BTRF

D34 1750000770 S.VARICAP HVC376BTRF

D37 1790001250 S.DIODE MA2S111-(TX)

D40 1750000520 S.DIODE DAN222TL

D42 1160000140 S.DIODE DAP222 TL

D43 1160000140 S.DIODE DAP222 TL

D44 1790001250 S.DIODE MA2S111-(TX)

D45 1790001250 S.DIODE MA2S111-(TX)

D48 1750000580 S.DIODE 1SV307 (TPH3)

A only

D49 1750000370 S.DIODE DA221 TL

D50 1790001250 S.DIODE MA2S111-(TX)

D51 1790001210 S.DIODE 1SS375-TL

FI1 2030000150 S.MONOLITH FL-335 (46.350 MHz)

FI2 2020001840 CERAMIC ALFYM450F=K

FI3 2040001440 S.LC

NFE31PT152Z1E9L (NFM60R20T152)

FI4 2040001440 S.LC

NFE31PT152Z1E9L (NFM60R20T152)

FI5 2040001440 S.LC

NFE31PT152Z1E9L (NFM60R20T152)

B only

X1 6070000190

S.DISCRIMINATOR

CDBCB450KCAY24-R0 (CDBC450CX24)

X2 6050011510 S.XTAL CR-740 (15.300 MHz)

L1 6200010050 S.COIL AS080547-47N

L2 6200010050 S.COIL AS080547-47N

L3 6200010050 S.COIL AS080547-47N

L4 6200010430 S.COIL 0.50-2.0-6TL

L5 6200010420 S.COIL FHW1210HC 1R0JGT

L6 6200010400 S.COIL ELJRE 39NJ 39N

L7 6200008090 S.COIL

LQW2BHN68NJ01L (LQN21A 68NJ04)

L8 6200008090 S.COIL

LQW2BHN68NJ01L (LQN21A 68NJ04)

L9 6200007750 S.COIL

LQW2BHN56NJ01L (LQN21A 56NJ04)

L10 6200004660 S.COIL MLF1608A 1R8K-T

L11 6200007750 S.COIL

LQW2BHN56NJ01L (LQN21A 56NJ04)

L12 6200009180 S.COIL ELJRE R10J-F3

L13 6200001620 S.COIL ELJFC 1R0K-F

L16 6200010050 S.COIL AS080547-47N

L18 6200009170 S.COIL ELJRE 47NJ-F2 A only

L19 6200009150 S.COIL ELJRE 82NJ-F3

L21 6200009150 S.COIL ELJRE 82NJ-F3

L22 6200009160 S.COIL ELJRE 68NJ-F3

L25 6200009460 S.COIL 0.25-1.9-7TL 67N

L26 6200008390 S.COIL 0.25-1.9-9TL

L27 6200002000 S.COIL NL 252018T-3R3J

L28 6200002000 S.COIL NL 252018T-3R3J

L29 6200004660 S.COIL MLF1608A 1R8K-T

L31 6200007750 S.COIL

LQW2BHN56NJ01L (LQN21A 56NJ04)

L32 6200010390 S.COIL ELJRE 33NJ-F3

L33 6200004480 S.COIL MLF1608D R82K-T

L35 6200003540 S.COIL MLF1608D R22K-T

6 - 2

REF ORDER

DESCRIPTION

NO. NO.

REF ORDER

DESCRIPTION

NO. NO.

[MAIN UNIT]

REF ORDER

DESCRIPTION

NO. NO.

A: [F110] B: [F111] and [F121] C: IC-F110 for [EUR]

D: IC-F110 for [GEN] E: IC-F110 for 25 kHz F: IC-F110 for 20 kHz

Page 20

S.=Surface mount

[MAIN UNIT][MAIN UNIT]

L37 6200003640 S.COIL MLF1608E 100K-T

L38 6200009460 S.COIL 0.25-1.9-7TL 67N

L39 6200008150 S.COIL 0.35-1.6-7TL 44N

L41 6200009160 S.COIL ELJRE 68NJ-F3

L42 6200003550 S.COIL MLF1608A 4R7K-T

L43 6200005740 S.COIL ELJRE 47NG-F

R1 7030000620 S.RESISTOR MCR10EZHJ 100 kΩ

R2 7030000220 S.RESISTOR MCR10EZHJ 47 Ω (470)

R3 7030000220 S.RESISTOR MCR10EZHJ 47 Ω (470)

R4 7030003370 S.RESISTOR ERJ3GEYJ 271 V (270 Ω)

R5 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

A

7030003610 S.RESISTOR ERJ3GEYJ 273 V (27 kΩ) B

R6 7030003610 S.RESISTOR ERJ3GEYJ 273 V (27 kΩ) B

7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ) A

R7 7030003370 S.RESISTOR ERJ3GEYJ 271 V (270 Ω)

R8 7030006070 S.RESISTOR ERJ12YJ101U (100 Ω)

R9 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

B only

R10 7030003730 S.RESISTOR ERJ3GEYJ 274 V (270 kΩ)

B only

R11 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R12 7030005530 S.RESISTOR ERJ2GEJ 100 X (10 Ω)

R13 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R14 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R15 7030003730 S.RESISTOR ERJ3GEYJ 274 V (270 kΩ)

R16 7030003370 S.RESISTOR ERJ3GEYJ 271 V (270 Ω)

R17 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R18 7030004050 S.RESISTOR ERJ3GEYJ 1R0 V (1 Ω)

R19 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R20 7030003370 S.RESISTOR ERJ3GEYJ 271 V (270 Ω) C

7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω) D, B

R21 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R22 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R23 7030003700 S.RESISTOR ERJ3GEYJ 154 V (150 kΩ)

R26 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R27 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R28 7030003210 S.RESISTOR ERJ3GEYJ 120 V (12 Ω)

R29 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R31 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R32 7030003340 S.RESISTOR ERJ3GEYJ 151 V (150 Ω)

R33 7030003340 S.RESISTOR ERJ3GEYJ 151 V (150 Ω)

R34 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R35 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R36 7030003510 S.RESISTOR ERJ3GEYJ 392 V (3.9 kΩ)

R37 7030003490 S.RESISTOR ERJ3GEYJ 272 V (2.7 kΩ)

E, B

7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ) F

R38 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R39 7030003280 S.RESISTOR ERJ3GEYJ 470 V (47 Ω)

R40 7030003460 S.RESISTOR ERJ3GEYJ 152 V (1.5 kΩ)

R42 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R43 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R44 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R45 7030003700 S.RESISTOR ERJ3GEYJ 154 V (150 kΩ)

R46 7030003480 S.RESISTOR ERJ3GEYJ 222 V (2.2 kΩ)

R48 7030003710 S.RESISTOR ERJ3GEYJ 184 V (180 kΩ)

B only

R49 7520000230 S.POSISTOR PRF18BD471QB1RB

B only

R50 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R51 7030003770 S.RESISTOR ERJ3GEYJ 564 V (560 kΩ)

A

7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ) B

R52 7030003580 S.RESISTOR ERJ3GEYJ 153 V (15 kΩ)

R53 7030004050 S.RESISTOR ERJ3GEYJ 1R0 V (1 Ω) A

7030003360 S.RESISTOR ERJ3GEYJ 221 V (220 Ω) B

R54 7030003550 S.RESISTOR ERJ3GEYJ 822 V (8.2 kΩ) B

7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ) A

R55 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R56 7030003700 S.RESISTOR ERJ3GEYJ 154 V (150 kΩ)

R57 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R58 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R59 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

B

7030003590 S.RESISTOR ERJ3GEYJ 183 V (18 kΩ) A

R60 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R61 7030003280 S.RESISTOR ERJ3GEYJ 470 V (47 Ω)

R62 7030003290 S.RESISTOR ERJ3GEYJ 560 V (56 Ω)

R63 7030003580 S.RESISTOR ERJ3GEYJ 153 V (15 kΩ)

R67 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

A

7030003300 S.RESISTOR ERJ3GEYJ 680 V (68 Ω) B

R68 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R69 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R70 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R71 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R73 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R74 7030003690 S.RESISTOR ERJ3GEYJ 124 V (120 kΩ)

R75 7030003690 S.RESISTOR ERJ3GEYJ 124 V (120 kΩ)

R76 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R77 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R78 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R79 7030005351 S.RESISTOR ERA3YED 182V

R80 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R83 7030005351 S.RESISTOR ERA3YED 182V

R84 7030006571 S.RESISTOR ERA3YED 392V

R85 7030006571 S.RESISTOR ERA3YED 392V

R86 7030003690 S.RESISTOR ERJ3GEYJ 124 V (120 kΩ)

R89 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R90 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R91 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

R92 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R93 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R95 7030003380 S.RESISTOR ERJ3GEYJ 331 V (330 Ω)

C

7030003360 S.RESISTOR ERJ3GEYJ 221 V (220 Ω) D, B

R96 7030003480 S.RESISTOR ERJ3GEYJ 222 V (2.2 kΩ)

R97 7030004050 S.RESISTOR ERJ3GEYJ 1R0 V (1 Ω)

R98 7030003480 S.RESISTOR ERJ3GEYJ 222 V (2.2 kΩ)

R99 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R100 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R101 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R103 7030003700 S.RESISTOR ERJ3GEYJ 154 V (150 kΩ)

R104 7030003450 S.RESISTOR ERJ3GEYJ 122 V (1.2 kΩ)

R105 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R106 7030003670 S.RESISTOR ERJ3GEYJ 823 V (82 kΩ)

R110 7030003280 S.RESISTOR ERJ3GEYJ 470 V (47 Ω)

R111 7030003500 S.RESISTOR ERJ3GEYJ 332 V (3.3 kΩ)

R112 7030003610 S.RESISTOR ERJ3GEYJ 273 V (27 kΩ)

R113 7030003480 S.RESISTOR ERJ3GEYJ 222 V (2.2 kΩ)

R114 7030003570 S.RESISTOR ERJ3GEYJ 123 V (12 kΩ)

R115 7030003510 S.RESISTOR ERJ3GEYJ 392 V (3.9 kΩ)

R116 7030003570 S.RESISTOR ERJ3GEYJ 123 V (12 kΩ)

R117 7030003710 S.RESISTOR ERJ3GEYJ 184 V (180 kΩ)

R118 7030003570 S.RESISTOR ERJ3GEYJ 123 V (12 kΩ)

R119 7030003530 S.RESISTOR ERJ3GEYJ 562 V (5.6 kΩ)

R120 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R121 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R122 7030003530 S.RESISTOR ERJ3GEYJ 562 V (5.6 kΩ)

R123 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R124 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R125 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R126 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R127 7030003630 S.RESISTOR ERJ3GEYJ 393 V (39 kΩ)

R128 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R129 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R130 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R133 7030003710 S.RESISTOR ERJ3GEYJ 184 V (180 kΩ)

R134 7030003610 S.RESISTOR ERJ3GEYJ 273 V (27 kΩ)

R135 7030003730 S.RESISTOR ERJ3GEYJ 274 V (270 kΩ)

R136 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R137 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ)

R138 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R139 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R141 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R142 7410001130 S.ARRAY EXB28V102JX

R143 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R144 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R145 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R146 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R147 7410001130 S.ARRAY EXB28V102JX

R148 7410001130 S.ARRAY EXB28V102JX

R149 7410001130 S.ARRAY EXB28V102JX

R150 7410001130 S.ARRAY EXB28V102JX

R156 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R159 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R183 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R184 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

R185 7030003690 S.RESISTOR ERJ3GEYJ 124 V (120 kΩ)

R186 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R187 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R188 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R191 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R192 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R193 7030003760 S.RESISTOR ERJ3GEYJ 474 V (470 kΩ)

R194 7030003480 S.RESISTOR ERJ3GEYJ 222 V (2.2 kΩ)

6 - 3

REF ORDER

DESCRIPTION

NO. NO.

REF ORDER

DESCRIPTION

NO. NO.

A: [F110] B: [F111] and [F121] C: IC-F110 for [EUR]

D: IC-F110 for [GEN] E: IC-F110 for 25 kHz F: IC-F110 for 20 kHz

Page 21

S.=Surface mount

[MAIN UNIT][MAIN UNIT]

R195 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R196 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R197 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R198 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R199 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R200 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R201 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R202 7030000440 S.RESISTOR MCR10EZHJ 3.3 kΩ

A

7030000480 S.RESISTOR MCR10EZHJ 6.8 kΩ (682) B

R203 7030000440 S.RESISTOR MCR10EZHJ 3.3 kΩ A

7030000480 S.RESISTOR MCR10EZHJ 6.8 kΩ (682) B

R204 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R205 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R209 7510001470 S.THERMISTOR NTCG20 4AG 473JT

R210 7030005871 S.RESISTOR ERA3YKD 104V (100 kΩ)

R211 7030003290 S.RESISTOR ERJ3GEYJ 560 V (56 Ω)

R212 7030003380 S.RESISTOR ERJ3GEYJ 331 V (330 Ω)

R213 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R214 7030003460 S.RESISTOR ERJ3GEYJ 152 V (1.5 kΩ)

R215 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R216 7030003460 S.RESISTOR ERJ3GEYJ 152 V (1.5 kΩ)

R217 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R218 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R219 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R220 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R221 7030003640 S.RESISTOR ERJ3GEYJ 473 V (47 kΩ)

R222 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R223 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R224 7030003280 S.RESISTOR ERJ3GEYJ 470 V (47 Ω)

R225 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R226 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R227 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R228 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R229 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R230 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ)

R231 7030004050 S.RESISTOR ERJ3GEYJ 1R0 V (1 Ω)

R232 7030003630 S.RESISTOR ERJ3GEYJ 393 V (39 kΩ)

R234 7030003550 S.RESISTOR ERJ3GEYJ 822 V (8.2 kΩ)

R235 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R236 7030003450 S.RESISTOR ERJ3GEYJ 122 V (1.2 kΩ)

R237 7030003780 S.RESISTOR ERJ3GEYJ 684 V (680 kΩ)

R238 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R240 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R241 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R242 7030003630 S.RESISTOR ERJ3GEYJ 393 V (39 kΩ)

R243 7030003670 S.RESISTOR ERJ3GEYJ 823 V (82 kΩ)

R244 7030003750 S.RESISTOR ERJ3GEYJ 394 V (390 kΩ)

R245 7030003710 S.RESISTOR ERJ3GEYJ 184 V (180 kΩ)

R247 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R248 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R249 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R250 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R251 7030003760 S.RESISTOR ERJ3GEYJ 474 V (470 kΩ)

R252 7030003400 S.RESISTOR ERJ3GEYJ 471 V (470 Ω)

R261 7030005160 S.RESISTOR ERJ2GEJ 105 X (1 MΩ)

R262 7030005160 S.RESISTOR ERJ2GEJ 105 X (1 MΩ)

R263 7030005160 S.RESISTOR ERJ2GEJ 105 X (1 MΩ)

R264 7030005070 S.RESISTOR ERJ2GEJ 683 X (68 kΩ)

R265 7030008290 S.RESISTOR ERJ2GEJ 183 X (18 kΩ)

R266 7030005240 S.RESISTOR ERJ2GEJ 473 X (47 kΩ)

R267 7030005600 S.RESISTOR ERJ2GEJ 273 X (27 kΩ)

R268 7030005050 S.RESISTOR ERJ2GEJ 103 X (10 kΩ)

R269 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R270 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R271 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R285 7030003320 S.RESISTOR ERJ3GEYJ 101 V (100 Ω)

R287 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R290 7030003420 S.RESISTOR ERJ3GEYJ 681 V (680 Ω)

R291 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R297 7030005651 S.RESISTOR ERA3YKD 304V (300 kΩ)

R298 7030005871 S.RESISTOR ERA3YKD 104V (100 kΩ)

R304 7030003600 S.RESISTOR ERJ3GEYJ 223 V (22 kΩ)

R310 7030003550 S.RESISTOR ERJ3GEYJ 822 V (8.2 kΩ)

R311 7030003360 S.RESISTOR ERJ3GEYJ 221 V (220 Ω)

R312 7030003720 S.RESISTOR ERJ3GEYJ 224 V (220 kΩ)

R313 7030003800 S.RESISTOR ERJ3GEYJ 105 V (1 MΩ)

R314 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R315 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R316 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R317 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R318 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R319 7030003590 S.RESISTOR ERJ3GEYJ 183 V (18 kΩ)

R320 7030003760 S.RESISTOR ERJ3GEYJ 474 V (470 kΩ)

R321 7030003560 S.RESISTOR ERJ3GEYJ 103 V (10 kΩ)

R322 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R323 7030005220 S.RESISTOR ERJ2GEJ 223 X (22 kΩ)

R324 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R325 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R326 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R327 7030005120 S.RESISTOR ERJ2GEJ 102 X (1 kΩ)

R328 7030004040 S.RESISTOR ERJ3GEYJ 4R7 V (4.7 Ω)

R329 7030000440 S.RESISTOR MCR10EZHJ 3.3 kΩ

A

7030000480 S.RESISTOR MCR10EZHJ 6.8 kΩ (682) B

R330 7030003520 S.RESISTOR ERJ3GEYJ 472 V (4.7 kΩ)

R331 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R332 7030003620 S.RESISTOR ERJ3GEYJ 333 V (33 kΩ)

R333 7030003680 S.RESISTOR ERJ3GEYJ 104 V (100 kΩ)

R334 7030003760 S.RESISTOR ERJ3GEYJ 474 V (470 kΩ)

R335 7030003440 S.RESISTOR ERJ3GEYJ 102 V (1 kΩ)

R336 7030003660 S.RESISTOR ERJ3GEYJ 683 V (68 kΩ)

C1 4030011170 S.CERAMIC

GRM31M2C2H180JV01L (GRM42-6 CH)

C2 4030011180 S.CERAMIC

GRM31M2C2H220JV01L (GRM42-6 CH)

A

4030011270 S.CERAMIC

GRM31M2C2H200JV01L (GRM42-6 CH)

B

C3 4030011340 S.CERAMIC C1608 CH 1H 471J-T

C4 4030007040 S.CERAMIC C1608 CH 1H 180J-T A

4030007030 S.CERAMIC C1608 CH 1H 150J-T B

C5 4030011340 S.CERAMIC C1608 CH 1H 471J-T

C6 4030011180 S.CERAMIC

GRM31M2C2H220JV01L (GRM42-6 CH)

A

4030011270 S.CERAMIC

GRM31M2C2H200JV01L (GRM42-6 CH)

B

C7 4030011290 S.CERAMIC

GRM31M2C2H240JV01L (GRM42-6 CH)

A

4030011170 S.CERAMIC

GRM31M2C2H180JV01L (GRM42-6 CH)

B

C8 4030011180 S.CERAMIC

GRM31M2C2H220JV01L (GRM42-6 CH)

A

4030011270 S.CERAMIC

GRM31M2C2H200JV01L (GRM42-6 CH)

B

C9 4030011180 S.CERAMIC

GRM31M2C2H220JV01L (GRM42-6 CH)

A

4030011270 S.CERAMIC

GRM31M2C2H200JV01L (GRM42-6 CH)

B

C10 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C11 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C12 4030011340 S.CERAMIC C1608 CH 1H 471J-T

C13 4030007090 S.CERAMIC C1608 CH 1H 470J-T

C14 4030017200 S.CERAMIC

GRM31BR32J102KY01L (GHM1030 R)

C15 4030008560 S.CERAMIC C1608 CH 1H 300J-T

C17 4030007020 S.CERAMIC C1608 CH 1H 120J-T

C18 4030011770 S.CERAMIC C1608 CH 1H 060B-T

C19 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C20 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C21 4030009540 S.CERAMIC C1608 CH 1H 1R5B-T

C22 4030009540 S.CERAMIC C1608 CH 1H 1R5B-T

C25 4030011770 S.CERAMIC C1608 CH 1H 060B-T

C26 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C27 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C28 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C29 4030009910 S.CERAMIC C1608 CH 1H 040B-T

C30 4030007050 S.CERAMIC C1608 CH 1H 220J-T

C31 4030011600 S.CERAMIC C1608 JB 1E 104K-T

C32 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C33 4030011600 S.CERAMIC C1608 JB 1E 104K-T

C34 4030017460 S.CERAMIC ECJ0EB1E102K

C35 4030017490 S.CERAMIC C1608 JB 1A 105K-T

C36 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C37 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C38 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C39 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C40 4030009540 S.CERAMIC C1608 CH 1H 1R5B-T

C41 4030007050 S.CERAMIC C1608 CH 1H 220J-T

C42 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C43 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C44 4030009530 S.CERAMIC C1608 CH 1H 030B-T

C45 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C48 4030007090 S.CERAMIC C1608 CH 1H 470J-T

6 - 4

REF ORDER

DESCRIPTION

NO. NO.

REF ORDER

DESCRIPTION

NO. NO.

A: [F110] B: [F111] and [F121] C: IC-F110 for [EUR]

D: IC-F110 for [GEN] E: IC-F110 for 25 kHz F: IC-F110 for 20 kHz

Page 22

S.=Surface mount

[MAIN UNIT][MAIN UNIT]

C49 4030007040 S.CERAMIC C1608 CH 1H 180J-T

C50 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C51 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C52 4030007060 S.CERAMIC C1608 CH 1H 270J-T

C53 4030006900 S.CERAMIC C1608 JB 1H 103K-T

C54 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C55 4030009910 S.CERAMIC C1608 CH 1H 040B-T

C56 4030007040 S.CERAMIC C1608 CH 1H 180J-T

C57 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C58 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C59 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C60 4030006900 S.CERAMIC C1608 JB 1H 103K-T

C61 4030007130 S.CERAMIC C1608 CH 1H 101J-T

C62 4030007120 S.CERAMIC C1608 CH 1H 820J-T

C63 4030017420 S.CERAMIC ECJ0EC1H470J

C64 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C65 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C66 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C67 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C68 4030007130 S.CERAMIC C1608 CH 1H 101J-T

C69 4030007140 S.CERAMIC C1608 CH 1H 121J-T

C70 4030007140 S.CERAMIC C1608 CH 1H 121J-T

C71 4030011600 S.CERAMIC C1608 JB 1E 104K-T

C72 4030006860 S.CERAMIC C1608 JB 1H 102K-T

B only

C73 4030017490 S.CERAMIC C1608 JB 1A 105K-T

C74 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C75 4550006050 S.TANTALUM TEMSVA 0J 106M8L

C76 4030006900 S.CERAMIC C1608 JB 1H 103K-T

C77 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C78 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C79 4030011810 S.CERAMIC C1608 JB 1A 224K-T

C80 4030011600 S.CERAMIC C1608 JB 1E 104K-T

C81 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C82 4030011270 S.CERAMIC

GRM31M2C2H200JV01L (GRM42-6 CH)

A

4030011120 S.CERAMIC

GRM31M2C2H100JV01L (GRM42-6 CH)

B

C83 4030011180 S.CERAMIC

GRM31M2C2H220JV01L (GRM42-6 CH)

A

4030011120 S.CERAMIC

GRM31M2C2H100JV01L (GRM42-6 CH)

B

C84 4030007090 S.CERAMIC C1608 CH 1H 470J-T

C85 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C86 4030007090 S.CERAMIC C1608 CH 1H 470J-T

C87 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C88 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C89 4030007040 S.CERAMIC C1608 CH 1H 180J-T A only

C90 4030007040 S.CERAMIC C1608 CH 1H 180J-T

A only

C91 4510005750

S.ELECTROLYTIC

ECEV1EA220SP

C92 4030007030 S.CERAMIC C1608 CH 1H 150J-T

C93 4030007030 S.CERAMIC C1608 CH 1H 150J-T A

4030007020 S.CERAMIC C1608 CH 1H 120J-T B

C94 4030007090 S.CERAMIC C1608 CH 1H 470J-T

C95 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C96 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C97 4030007090 S.CERAMIC C1608 CH 1H 470J-T

C99 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C100 4030007010 S.CERAMIC C1608 CH 1H 100D-T

C101 4030009540 S.CERAMIC C1608 CH 1H 1R5B-T

C102 4030007010 S.CERAMIC C1608 CH 1H 100D-T

C103 4030009530 S.CERAMIC C1608 CH 1H 030B-T

C104 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C105 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C106 4030007090 S.CERAMIC C1608 CH 1H 470J-T

C107 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C108 4030006900 S.CERAMIC C1608 JB 1H 103K-T

C109 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C110 4030011340 S.CERAMIC C1608 CH 1H 471J-T

C111 4030007090 S.CERAMIC C1608 CH 1H 470J-T

C113 4030009560 S.CERAMIC C1608 CH 1H R75B-T

C114 4030007070 S.CERAMIC C1608 CH 1H 330J-T

C115 4030007070 S.CERAMIC C1608 CH 1H 330J-T

C116 4030006900 S.CERAMIC C1608 JB 1H 103K-T

C117 4030011340 S.CERAMIC C1608 CH 1H 471J-T

C118 4030009500 S.CERAMIC C1608 CH 1H 0R5B-T

C119 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C120 4030011340 S.CERAMIC C1608 CH 1H 471J-T

C121 4030007040 S.CERAMIC C1608 CH 1H 180J-T

C122 4030007070 S.CERAMIC C1608 CH 1H 330J-T

C123 4030007110 S.CERAMIC C1608 CH 1H 680J-T

C124 4030011280 S.CERAMIC C1608 CH 1H 271J-T

C126 4030007070 S.CERAMIC C1608 CH 1H 330J-T

C127 4030007030 S.CERAMIC C1608 CH 1H 150J-T

C129 4030009510 S.CERAMIC C1608 CH 1H 010B-T

C131 4030009510 S.CERAMIC C1608 CH 1H 010B-T

C132 4030011600 S.CERAMIC C1608 JB 1E 104K-T

C133 4610001590 S.TRIMMER TZC3R100A110R00

C134 4610001590 S.TRIMMER TZC3R100A110R00

C135 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C136 4030009530 S.CERAMIC C1608 CH 1H 030B-T

C138 4030007090 S.CERAMIC C1608 CH 1H 470J-T

C139 4030011600 S.CERAMIC C1608 JB 1E 104K-T

C140 4030011600 S.CERAMIC C1608 JB 1E 104K-T

C141 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C142 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C143 4030006860 S.CERAMIC C1608 JB 1H 102K-T

C144 4030007090 S.CERAMIC C1608 CH 1H 470J-T

C145 4030010760 S.CERAMIC C1608 CH 1H 331J-T

C146 4550006150 S.TANTALUM ECST1CY105R

C147 4550006390 S.TANTALUM TEMSVA 1C 335M-8L

C148 4510004630

S.ELECTROLYTIC

ECEV1CA100SR

C149 4550000550 S.TANTALUM TESVA 1V 224M1-8L

C151 4030011600 S.CERAMIC C1608 JB 1E 104K-T

C152 4030007090 S.CERAMIC C1608 CH 1H 470J-T

C153 4030007090 S.CERAMIC C1608 CH 1H 470J-T

C154 4030007090 S.CERAMIC C1608 CH 1H 470J-T

C155 4030011280 S.CERAMIC C1608 CH 1H 271J-T

C156 4030007090 S.CERAMIC C1608 CH 1H 470J-T

C157 4030007130 S.CERAMIC C1608 CH 1H 101J-T

C158 4030007130 S.CERAMIC C1608 CH 1H 101J-T