Page 1

HYUNDAI MICRO ELECTRONICS

8-BIT SINGLE-CHIP MICROCONTROLLERS

GMS90X51C

GMS90X52C

GMS90X54C

User’s Manual (Ver. 1.0)

+<81'$,

Semiconductor Group of Hyundai Electronics Industrial Co., Ltd.

MicroElectronics

Page 2

Version 1.0

Published by

MCU Application Team

HYUNDAI MicroElectronics All right reserved.

2001

2001

20012001

Additional information of this manual may be served by HYUNDAI MicroElectronics offices in Korea or Distributors and Representatives listed at address directory.

HYUNDAI MicroElectronics reserves the right to make changes to any information here in at any time without

notice.

The information, diagrams and other data in this manual are correct and reliable; however, HYUNDAI MicroElectronics is in no way responsible for any violat ion s of patent s or other ri gh ts of the t hird par ty generated by

the use of this manual.

Page 3

GMS90X5XC Series HYUNDAI MicroElectronics

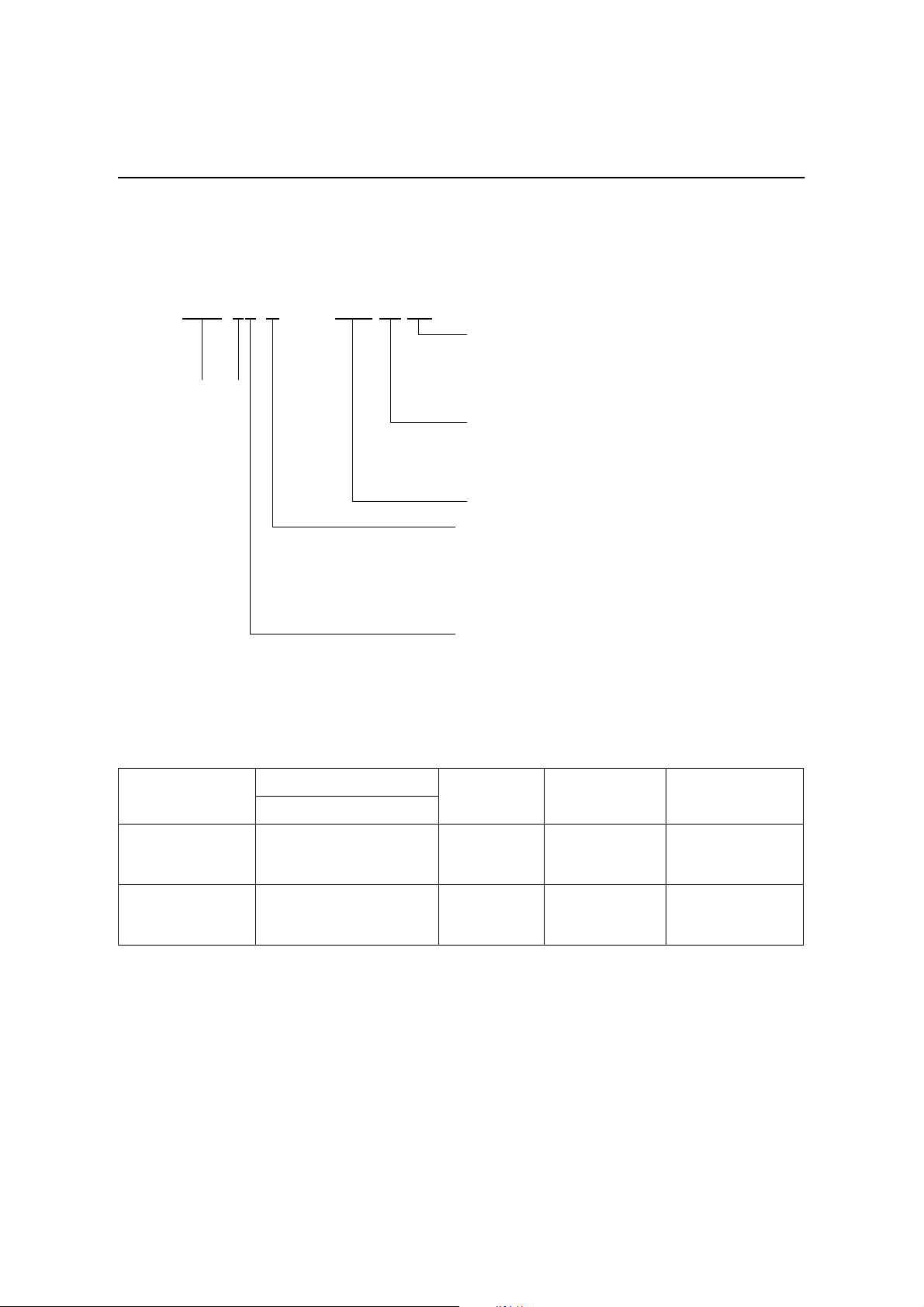

Device Naming Structure

GMS90X5XC

Mask ROM version

HYUNDAI MicroElectronics MCU

- GCXXX XX XX

ROM size

1:

2:

4:

Operating Voltage

C:L:4.25~5.5V

GMS90X5XC Series Selection Guide

Frequency

Blank:

16: 16MHz

24:

40:

Package Type

Blank:

PL:

Q:

ROM Code serial No.

12MHz

24MHz

40MHz

40PDIP

44PLCC

44MQFP

4k bytes

8k bytes

16k bytes

2.7~3.6V

Operating

Voltage

(V)

4.25~5.5 4K

2.7~3.6 4K

Jan. 2001 Ver 1.0

ROM size

MASK

8K

16K

8K

16K

(bytes)

RAM size

(bytes)

128

256

256

128

256

256

Device Name

GMS90C51C

GMS90C52C

GMS90C54C

GMS90L51C

GMS90L52C

GMS90L54C

Operating

Frequency

12/24/40

12/24/40

12/24/40

12/16

12/16

12/16

(MHz)

Page 4

GMS90X5XC Series HYUNDAI MicroElectronics

GMS90C51C GMS90L51C(Low voltage versions)

• Fully compatible to standard MCS-51 microcontroller

• Wide operating frequency up to 40MHz

(for more detail, see “GMS90X5XC Series Selection Guide”)

• X2 Speed Improvement capability (

20MHz @5V (Equivalent to 40MHz @5V)

8MHz @3V (Equivalent to 16MHz @3V)

•4K × 8 ROM

• 128 × 8 RAM

• 64K external program memory space

• 64K external data memory space

• Four 8-bit ports

• Two 16-bit Timers / Counters

•USART

• Programmable ALE pin enable / disable (Low

• Five interrupt sources, two priority levels

• Power saving Idle and power down mode

• 2.7Volt low voltage version available

• P-DIP-40, P-LCC-44, P-MQFP-44 package

6 clocks/machine cycle

EMI

)

)

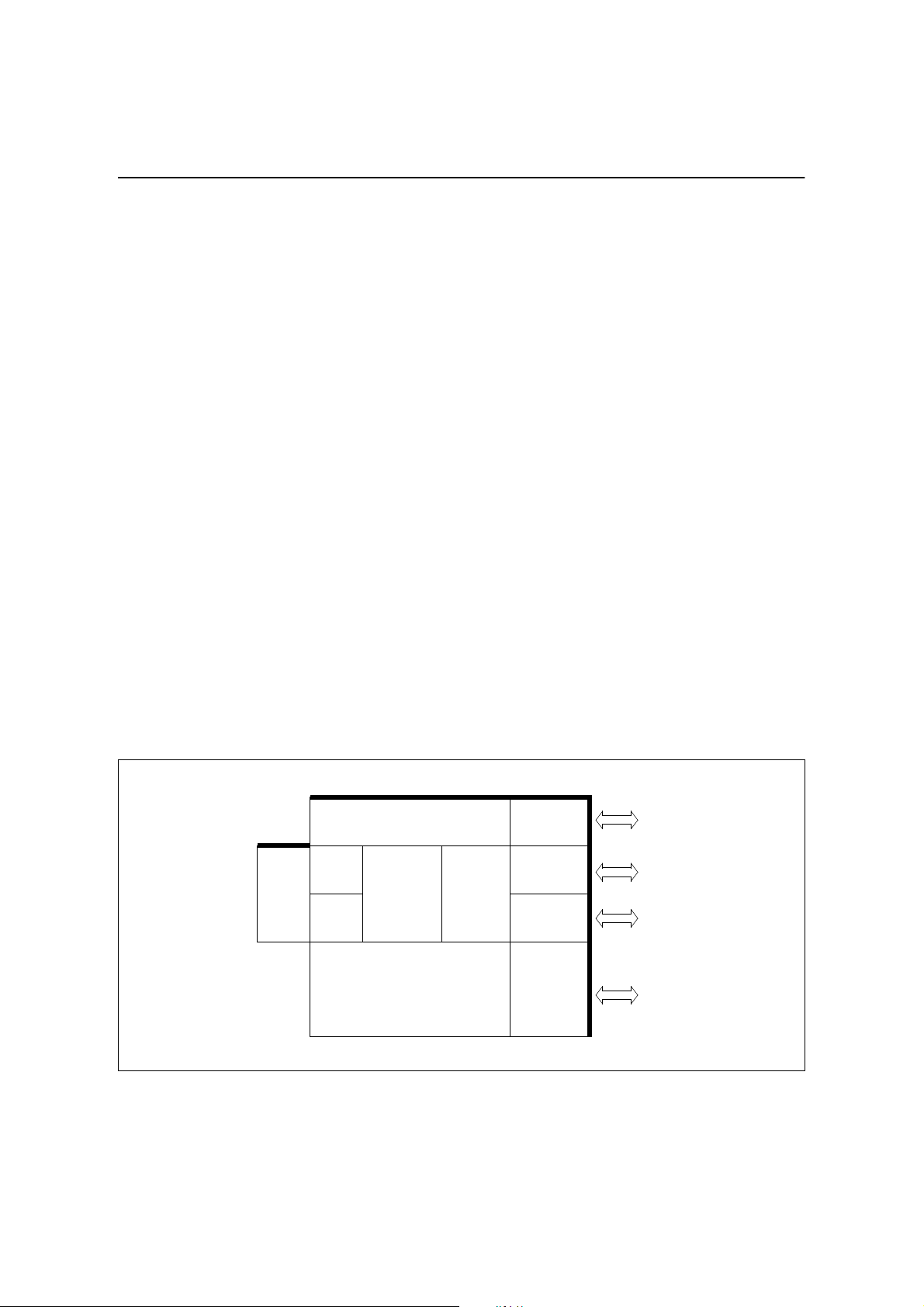

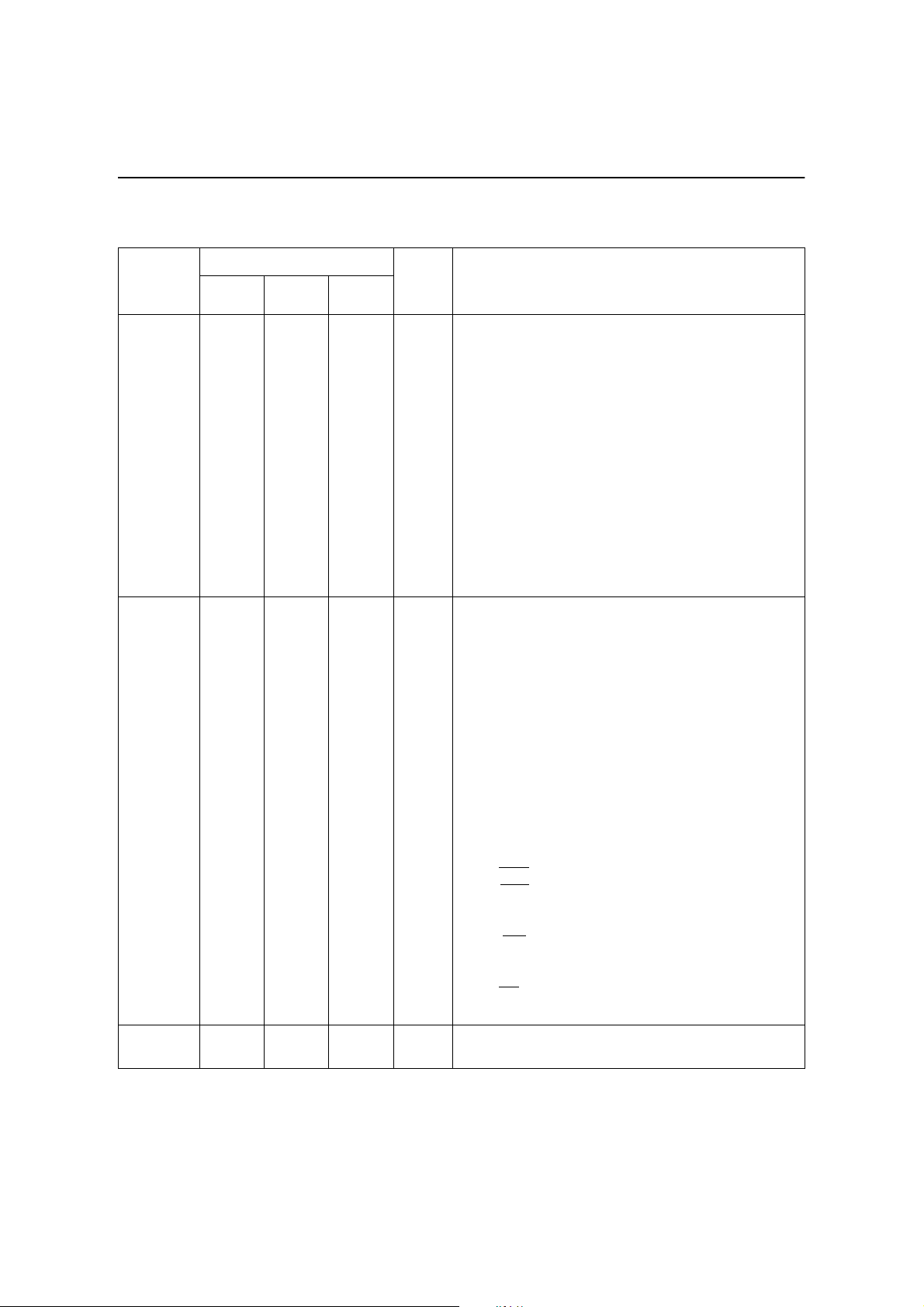

Block Diagram

Jan. 2001 Ver 1.0

T 0

T 1

ROM / EPROM

RAM

128 × 8

CPU

4K × 8

8-BIT

USART

PORT 0

PORT 1

PORT 2

PORT 3

I/O

I/O

I/O

I/O

Page 5

GMS90X5XC Series HYUNDAI MicroElectronics

GMS90C52C/54C GMS90L52C/54C(Low voltage versions)

• Fully compatible to standard MCS-51 microcontroller

• Wide operating frequency up to 40MHz

(for more detail, see “GMS90X5XC Series Selection Guide”)

• X2 Speed Improvement capability (

20MHz @5V (Equivalent to 40MHz @5V)

8MHz @3V (Equivalent to 16MHz @3V)

•8K/16K bytes ROM

• 256 × 8 RAM

• 64K external program memory space

• 64K external data memory space

• Four 8-bit ports

• Three 16-bit Timers / Counters (Timer2 with up/down counter feature)

•USART

• One clock output port

• Programmable ALE pin enable / disable (Low

• Six interrupt sources, two priority levels

• Power saving Idle and power down mode

• 2.7Volt low voltage version available

• P-DIP-40, P-LCC-44, P-MQFP-44 package

6 clocks/machine cycle

EMI

)

)

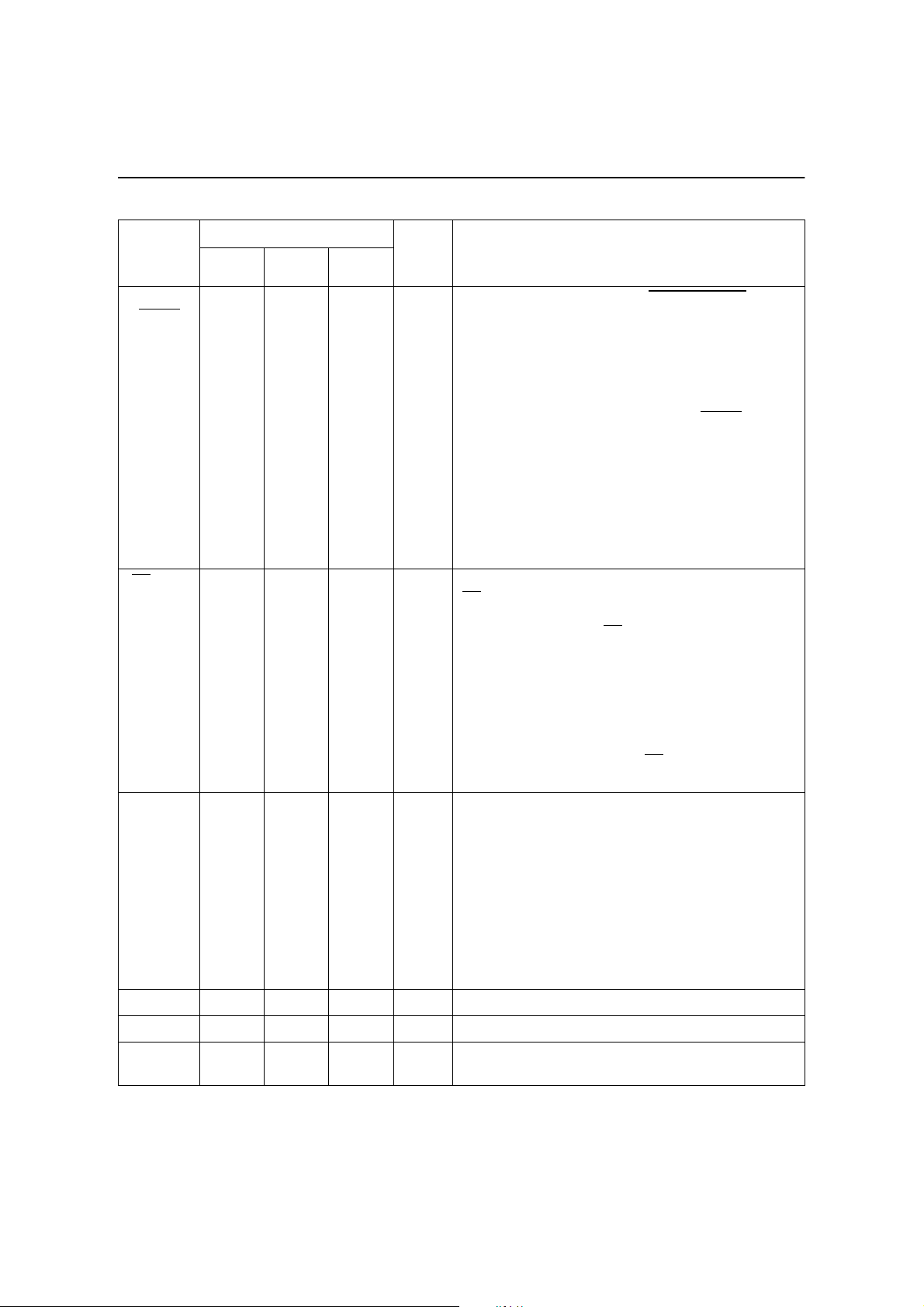

Block Diagram

T 2

RAM

256 × 8

T 0

CPU

T 1

ROM / EPROM

GMS90X52C: 8K × 8

GMS90X54C: 16K × 8

8-BIT

USART

PORT 0

PORT 1

PORT 2

PORT 3

I/O

I/O

I/O

I/O

Jan. 2001 Ver 1.0 1

Page 6

HYUNDAI MicroElectronics GMS90X5XC Series

PIN CONFIGURATION

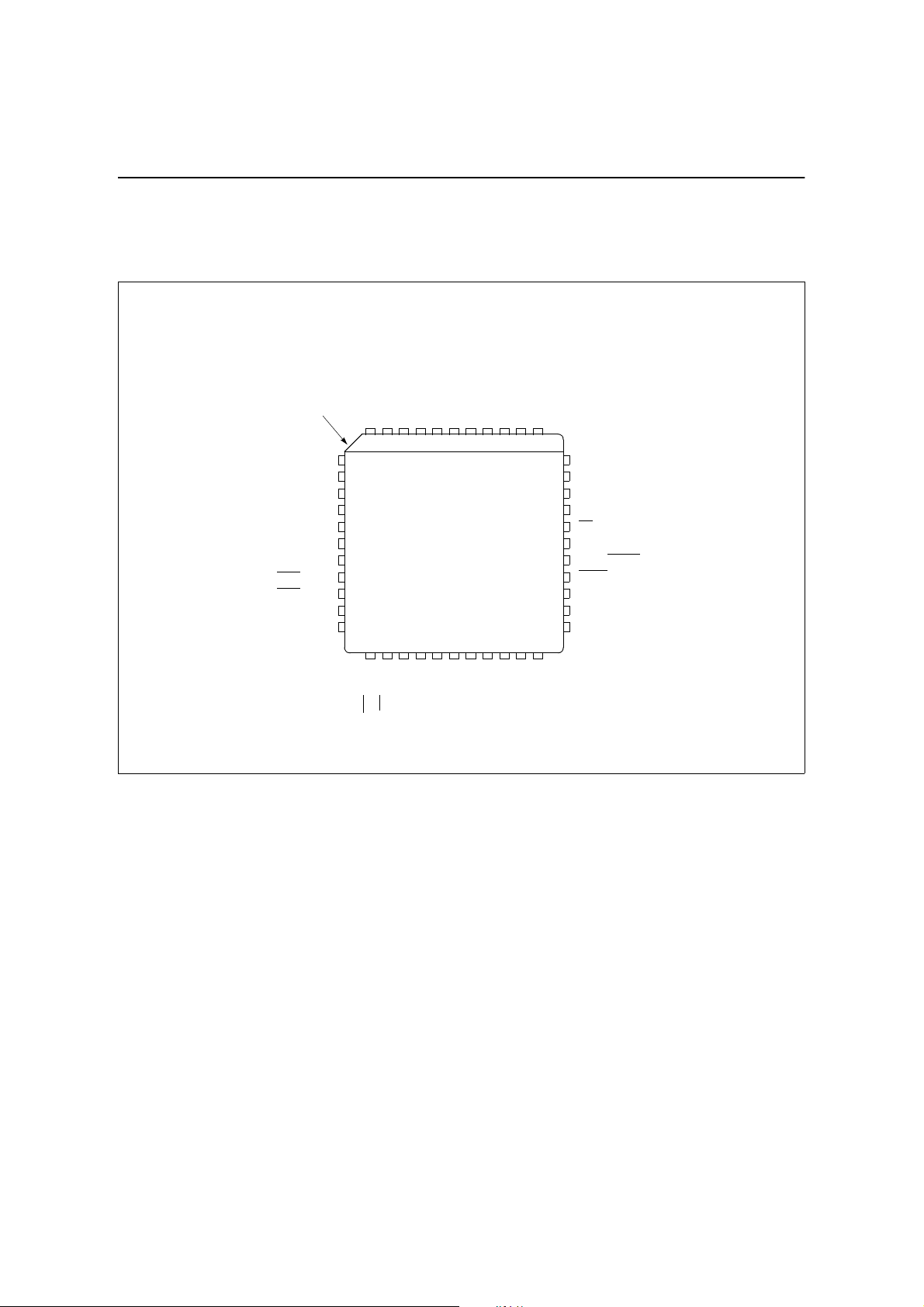

44-PLCC Pin Configuration (top view)

N.C.: Do not connect.

INDEX

CORNER

RESET

RxD / P3.0

N.C.*

TxD / P3.1

/ P3.2

INT0

/ P3.3

INT1

T0 / P3.4

T1 / P3.5

P1.5

P1.6

P1.7

P1.4

P1.3

P1.2

P1.1 / T2EX

65432

7

8

9

10

11

12

13

14

15

16

17

1819202122232425262728

/ P3.7

XTAL2

XTAL1

RD

WR / P3.6

P1.0 / T2

N.C.*

1

SS

V

N.C.*

CC

V

4443424140

P2.0 / A8

P0.0 / AD0

P2.1 / A9

P0.1 / AD1

P0.2 / AD2

P0.3 / AD3

P0.4 / AD4

39

P0.5 / AD5

38

P0.6 / AD6

37

P0.7 / AD7

36

/ V

EA

35

34

33

32

31

30

29

P2.2 / A10

P2.4 / A12

P2.3 / A11

PP

N.C.*

ALE / PROG

PSEN

P2.7 / A15

P2.6 / A14

P2.5 / A13

2 Jan. 2001 Ver 1.0

Page 7

GMS90X5XC Series HYUNDAI MicroElectronics

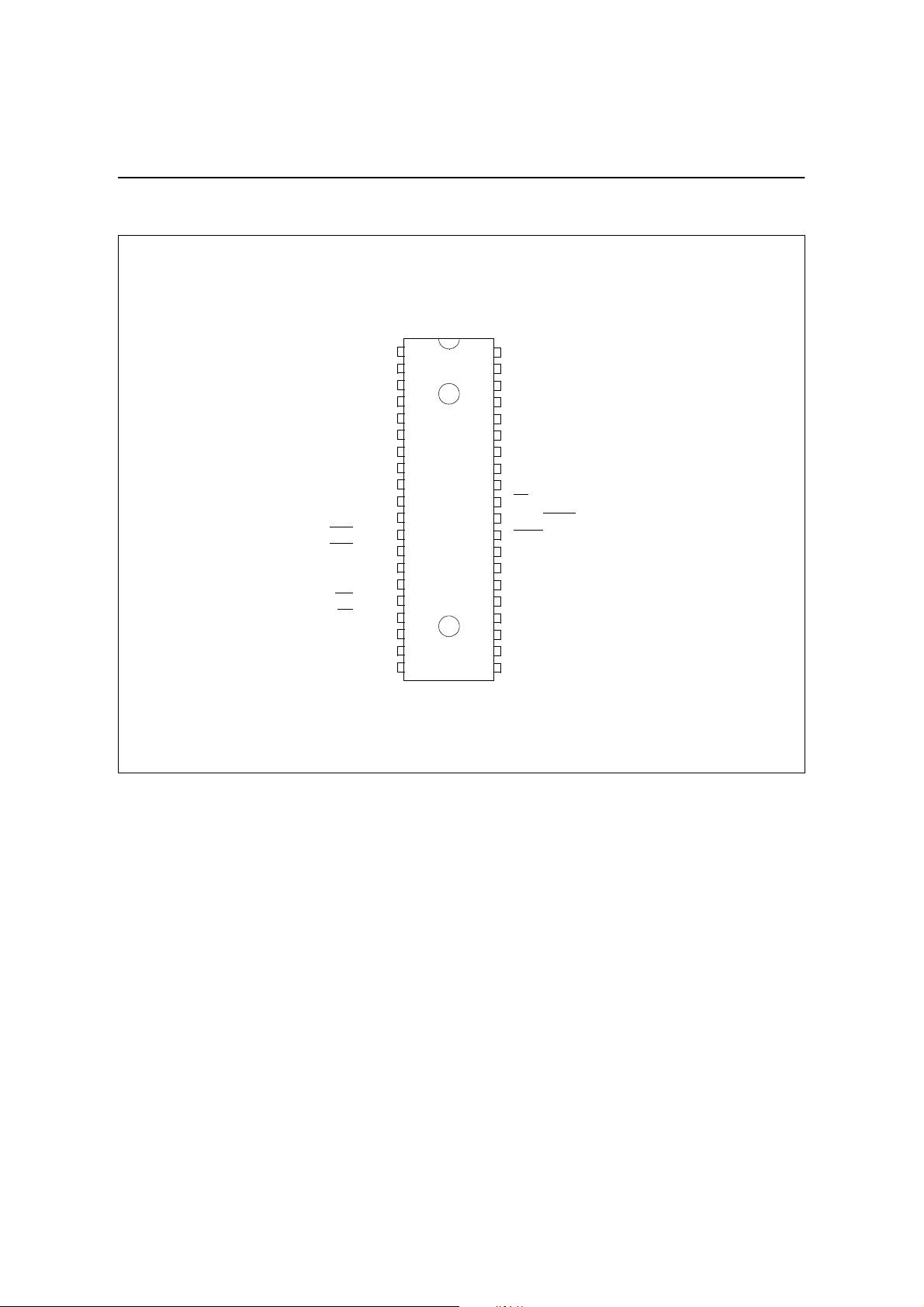

40-PDIP Pin Configuration (top view)

T2 / P1.0

T2EX / P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

RESET

RxD / P3.0

TxD / P3.1

INT0

/ P3.2

/ P3.3

INT1

T0 / P3.4

T1 / P3.5

WR

/ P3.6

RD

/ P3.7

XTAL2

XTAL1

V

V

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

SS

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

CC

P0.0 / AD0

P0.1 / AD1

P0.2 / AD2

P0.3 / AD3

P0.4 / AD4

P0.5 / AD5

P0.6 / AD6

P0.7 / AD7

EA

/ V

PP

ALE / PROG

PSEN

P2.7 / A15

P2.6 / A14

P2.5 / A13

P2.4 / A12

P2.3 / A11

P2.2 / A10

P2.1 / A9

P2.0 / A8

Jan. 2001 Ver 1.0 3

Page 8

HYUNDAI MicroElectronics GMS90X5XC Series

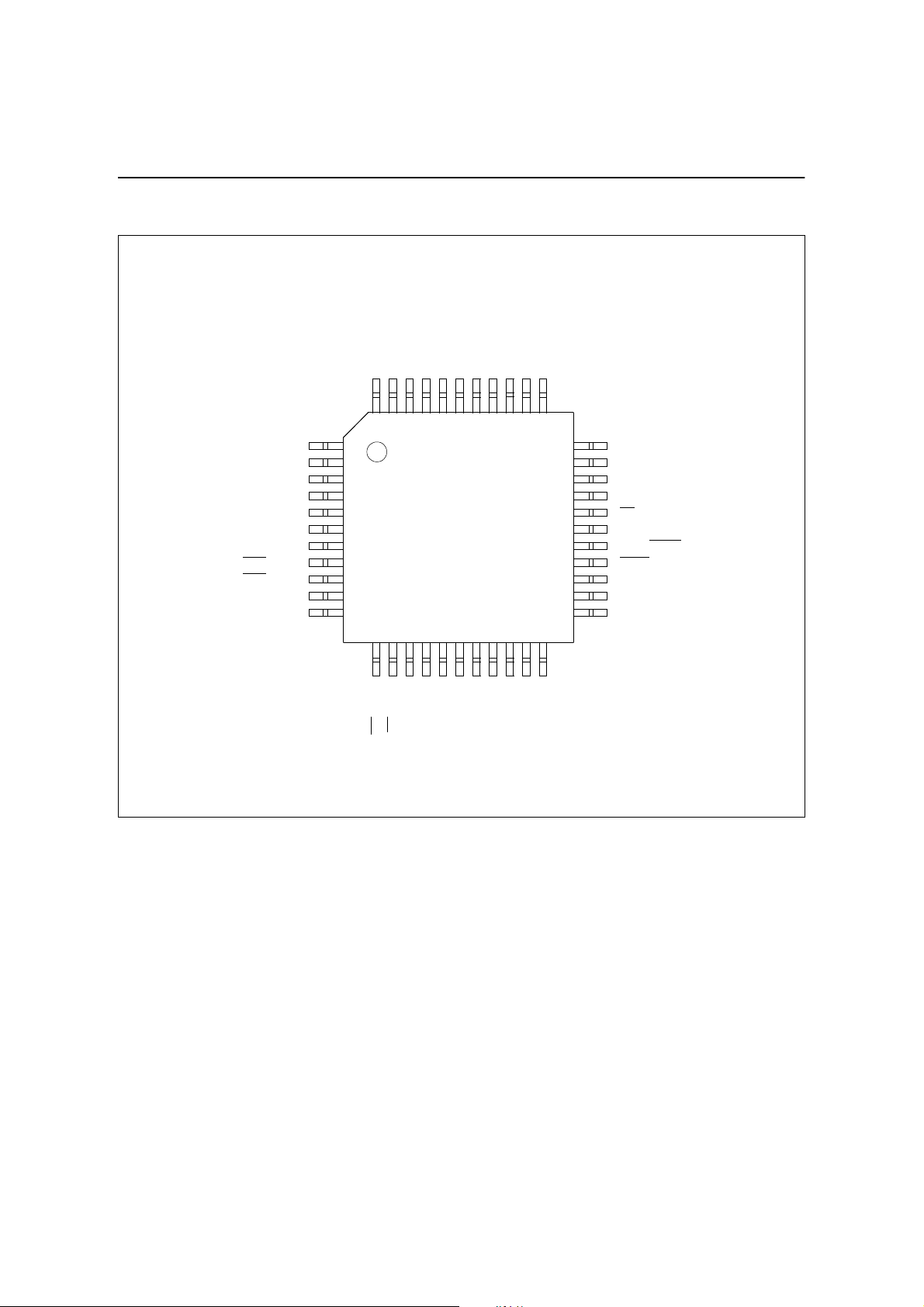

44-MQFP Pin Configuration (top view)

CC

P0.0 / AD0

P0.1 / AD1

P0.2 / AD2

P0.3 / AD3

33

32

31

30

29

28

27

26

25

24

23

P0.4 / AD4

P0.5 / AD5

P0.6 / AD6

P0.7 / AD7

/ V

EA

PP

N.C.*

ALE / PROG

PSEN

P2.7 / A15

P2.6 / A14

P2.5 / A13

P1.5

P1.6

P1.7

RESET

RxD / P3.0

N.C.*

TxD / P3.1

/ P3.2

INT0

/ P3.3

INT1

T0 / P3.4

T1 / P3.5

P1.4

P1.3

P1.2

P1.1 / T2EX

P1.0 / T2

N.C.*

V

4443424140393837363534

1

2

3

4

5

6

7

8

9

10

11

1213141516171819202122

N.C.: Do not connect.

SS

V

/ P3.7

XTAL2

RD

WR / P3.6

N.C.*

XTAL1

P2.0 / A8

P2.1 / A9

P2.2 / A10

P2.4 / A12

P2.3 / A11

4 Jan. 2001 Ver 1.0

Page 9

GMS90X5XC Series HYUNDAI MicroElectronics

Logic Symbol

V

CCVSS

XTAL1

XTAL2

RESET

EA/V

PP

ALE/PROG

PSEN

Port 0

8-bit Digital I/O

Port 1

8-bit Digital I/O

Port 2

8-bit Digital I/O

Port 3

8-bit Digital I/O

Jan. 2001 Ver 1.0 5

Page 10

HYUNDAI MicroElectronics GMS90X5XC Series

PIN DEFINITIONS AND FUNCTIONS

Pin Number

Symbol

P1.0-P1.7 2-9

PLCC-44PDIP-40MQFP-

1-8

44

40-44,

1-3

2

3

2

P3.0-P3.7 11,

1

2

1

40

41

40

10-17 5, 7-13 I/O

13-19

11

13

14

15

16

17

18

19

10

11

12

13

14

15

16

17

5

7

8

9

10

11

12

13

XTAL2 20 18 14 O

Input/

Output

I/O

Function

Port1

Port 1 is an 8-bit bidirectional I/O port with internal

pull-ups. Port 1 pins that have 1s written to them are

pulled high by the intern al pu ll-u p res is tors and c an be

used as inputs. As inputs, port 1 pins that are

externally pulled low will source current because of

the pulls-ups (I

, in the DC characteristics). Pins P1.0

IL

and P1.1 also. Port1 also receives the low-order

address byte during program memory verification.

Port1 also serves alternate functions of Timer 2.

P1.0 / T2 :Timer/counter 2 external count input

P1.1 / T2EX :Timer/counter 2 trigger input

In GMS90X52C/54C:

P1.0 / T2, Clock Out : Timer/counter 2 external count

input, Clock Out

Port 3

Port 3 is an 8-bit bidirectional I/O port with internal

pull-ups. Port 3 pins that have 1s written to them are

pulled high by the intern al pu ll-u p res is tors and c an be

used as inputs. As inputs, port 3 pins that are

externally pulled low will source current because of

the pulls-ups (I

, in the DC characteristic s). Port 3 also

IL

serves the special features of the 80C51 family, as

listed below.

P3.0 / RxD

receiver data input (asynchronous) or

data input output(s yn chronous) of serial

interface 0

P3.1 / TxD

transmitter data output (asynchronous)

or clock output (synchronous) of the

serial interface 0

P3.2 /INT0

P3 .3 / IN T 1

P3.4 /T0

P3.5 /T1

P3.6 / WR

interrupt 0 input/timer 0 gate control

interrupt 1 input/timer 1 gate control

counter 0 input

counter 1 input

the write control signal latche s t he data

byte from port 0 into the external data

memory

P3.7 /RD

the read control signal enables the

external data memory to port 0

XTAL2

Output of the inverting oscillator amplifier.

6 Jan. 2001 Ver 1.0

Page 11

GMS90X5XC Series HYUNDAI MicroElectronics

Symbol

Pin Number

PLCC-44PDIP-40MQFP-

44

Input/

Output

XTAL1 21 19 15 I

P2.0-P2.7 24-31 21-28 18-25 I/O

PSEN

32 29 26 O

RESET 10 9 4 I

Function

XTAL1

Input to the inverting oscillator amplifier and input to

the internal clock generator circuits.To drive the

device from an external clock source, XTAL1 should

be driven, while XTAL2 is left unconnected. There are

no requirements on the duty cycle of the external

clock signal, since the input to the internal clocking

circuitry is divided down by a divide-by-two flip-flop.

Minimum and maximum high and low times as well as

rise fall times specified in the AC characteristics must

be observed.

Port 2

Port 2 is an 8-bit bidirectional I/O port with internal

pull-ups. Port 2 pins that have 1s written to them are

pulled high by the intern al pu ll-u p res is tors and c an be

used as inputs. As inputs, port 2 pins that are

externally pulled low will source current because of

the pulls-ups (I

, in the DC characteristics).Port 2

IL

emits the high-order address byte during fetches from

external program memory and during accesses to

external data memory that use 16-bit addresses

(MOVX @DPTR). In this application it uses strong

internal pull-ups when emitting 1s. During accesses to

external data memory that use 8-bit addresses

(MOVX @Ri), port 2 emits the contents of the P2

special function register.

The Program Store Enable

The read strobe to external program memory when

the device is executing code from the external

program memory. PSEN is activated twice each

machine cycle, except that two PSEN

activati ons are

skipped during each access to external data memory.

PSEN is not activated during fetches from internal

program memory.

RESET

A high level on this pin for two machine cycles while

the oscilla tor is runni ng resets the device. An interna l

diffused resistor to V

only an external capacitor to V

permits power-on reset using

SS

CC

.

Jan. 2001 Ver 1.0 7

Page 12

HYUNDAI MicroElectronics GMS90X5XC Series

Symbol

ALE /

Pin Number

PLCC-44PDIP-40MQFP-

44

33 30 27 O

Input/

Output

PROG

EA

/ V

PP

35 31 29 I External Access Enable / Program Supply Voltage

P0.0-P0.7 36-43 32-39 30-37 I/O

V

SS

V

CC

N.C. 1,12

22 20 16 44 40 38 -

-6,17

23,34

28,39

Function

The Address Latch Enable / Program pulse

Output pulse for latching the low byte of the address

during an access to external memory. In normal

operation, ALE is emitted at a constant rate of 1/6 the

oscillator frequency, and can be used for external

timing or clocking. Note that one ALE pulse is skipped

during each access to external data memory. This pin

is also the program pulse input (PROG

EPROM programming.

If desired, ALE operation can be disabled by setting

bit 0 of SFR location 8E

. With this bit set, the pin is

H

weakly pulled high. The ALE disable feature will be

terminated by reset. Setting the ALE-disable bit has

no affect if the microcontroller is in external execution

mode.

must be external held low to enable the device to

EA

fetch code from external program memory locations

0000H to FFFFH. If EA is held high, the device

executes from internal program memory unless the

program counter contains an address greater than its

internal memory size. This pin also receives the

12.75V programming supply voltage (V

EPROM programming.

Note; however, that if any of the Lock bits are

programmed, EA

will be internally

latched on reset.

Port 0

Port 0 is an 8-bit open-drain bidirectional I/O port.

Port 0 pins that have 1s written to them float and can

be used as high-impedance inputs.

Port 0 is also the multipl exed low-orde r address and

data bus during accesses to external program and

data memory. In this application it uses strong internal

pull-ups when emitting 1s. Port 0 also outputs the

code bytes during program verification in the

GMS97X5X. External pull-up resistors are required

during program verification.

Circuit ground potential

Supply terminal

No connection

-

for all operating modes

) during

) during

PP

8 Jan. 2001 Ver 1.0

Page 13

GMS90X5XC Series HYUNDAI MicroElectronics

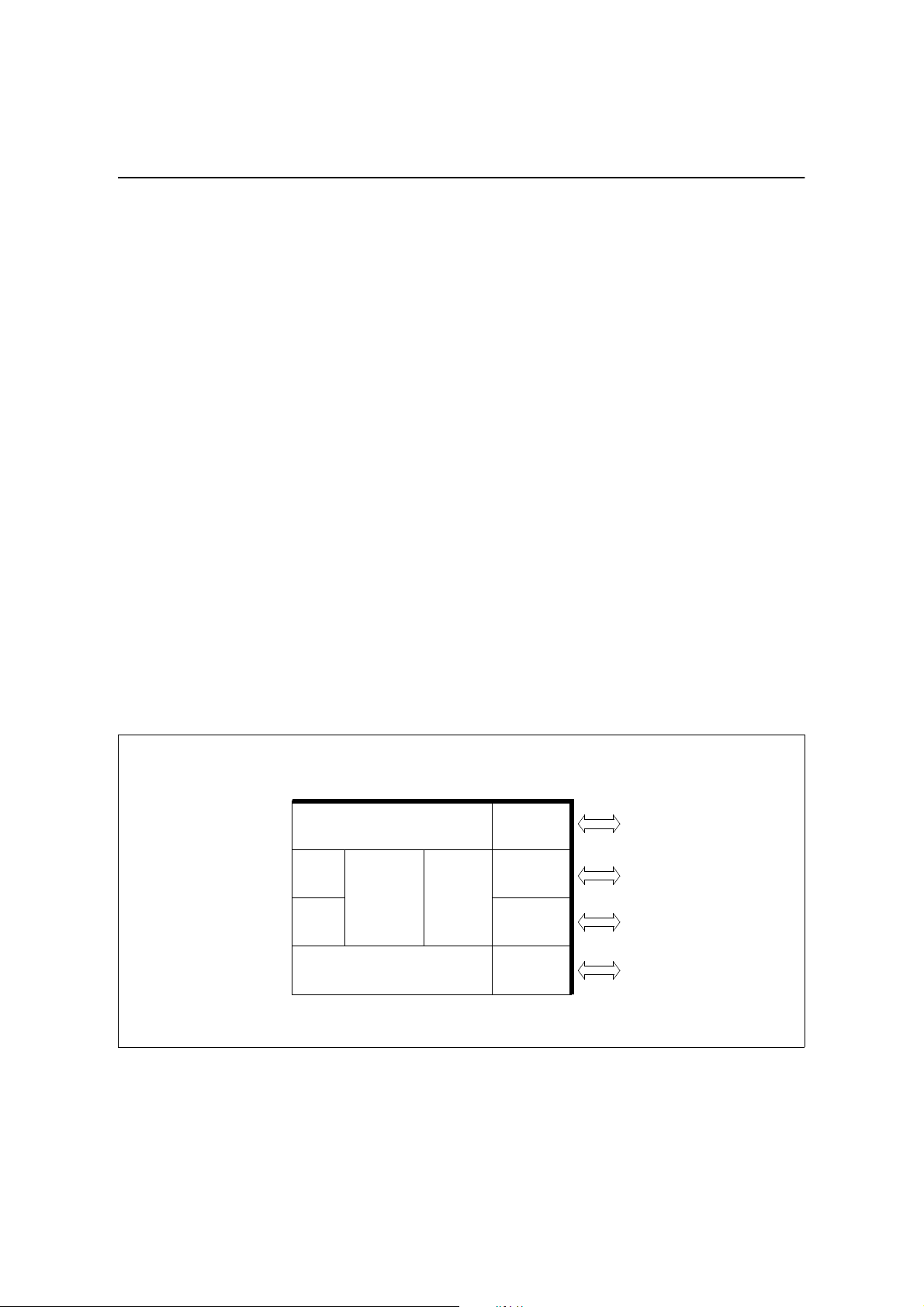

FUNCTIONAL DESCRIPTION

The GMS90X5XC series is fully compatible to the standard 8051 microcontroller family.

It is compatible with the general 8051 family. While maintaining all architectural and operational characteristics

of the general 8051 family.

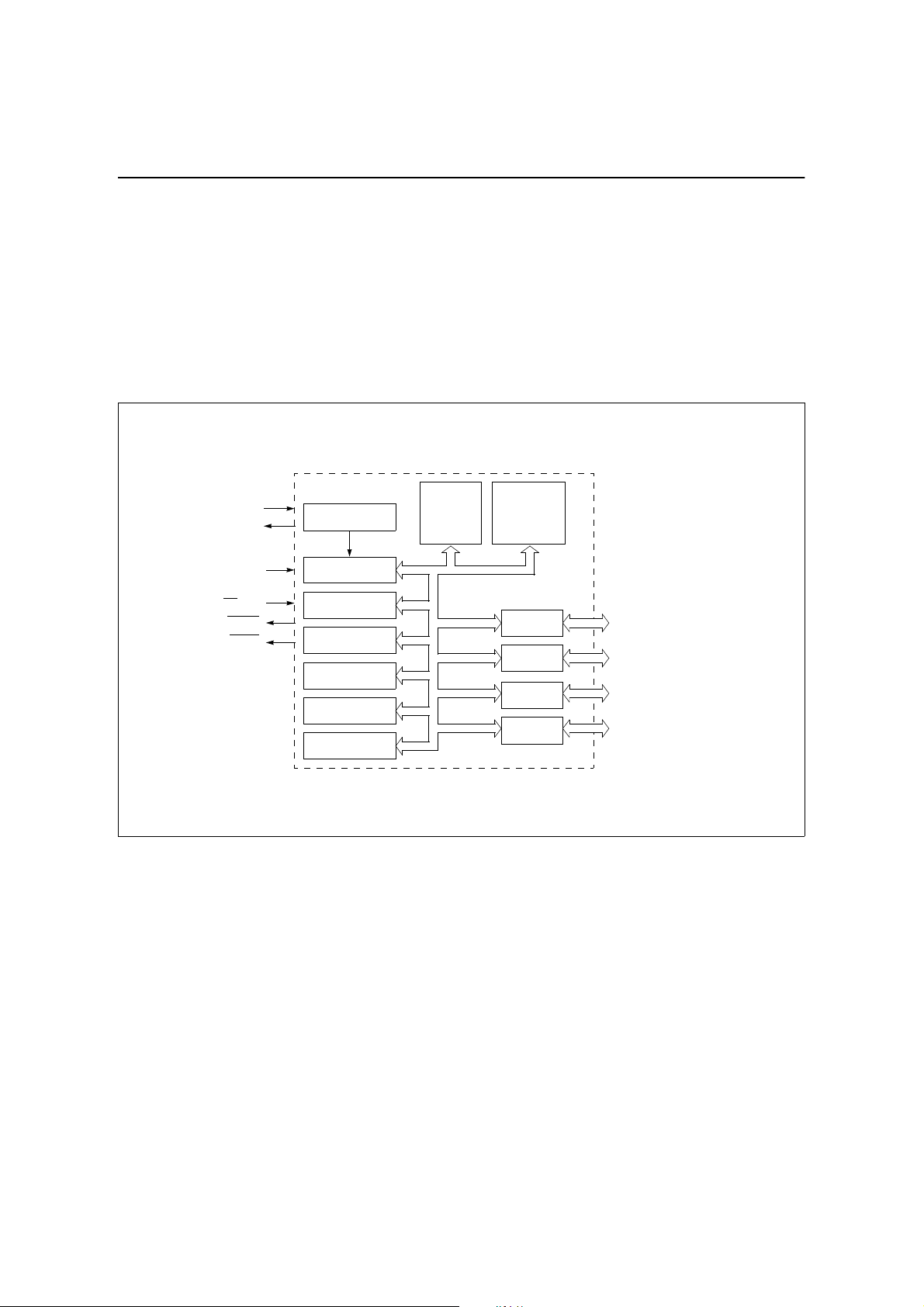

Figure 1 shows a block diagram of the GMS90X5XC series

XTAL1

XTAL2

RESET

EA

/V

ALE/PROG

PSEN

OSC & TIMING

CPU

PP

Timer 0

Timer 1

Timer 2

Interrupt Unit

Serial Channel

RAM

128/256×8

Figure 1. Block Diagram of the GMS90X5XC series

ROM/EPROM

4K/8K/16K

Port 0

Port 1

Port 2

Port 3

Port 0

8-bit Digit. I/O

Port 1

8-bit Digit. I/O

Port 2

8-bit Digit. I/O

Port 3

8-bit Digit. I/O

Jan. 2001 Ver 1.0 9

Page 14

HYUNDAI MicroElectronics GMS90X5XC Series

CPU

The GMS90X5XC series is efficient both as a controller and as an arithmetic processor. It has exten sive facilities for binary and BCD arithmetic and excels in its bit-handling capabilities. Efficient use of program memory

results from an i nstructio n set consist ing of 44% o ne-byte, 41% two-byte, and 15% three-byt e instruction s. With

a 12 MHz crystal, 58% of the instructions are executed in 1.0µs (40MHz: 300ns).

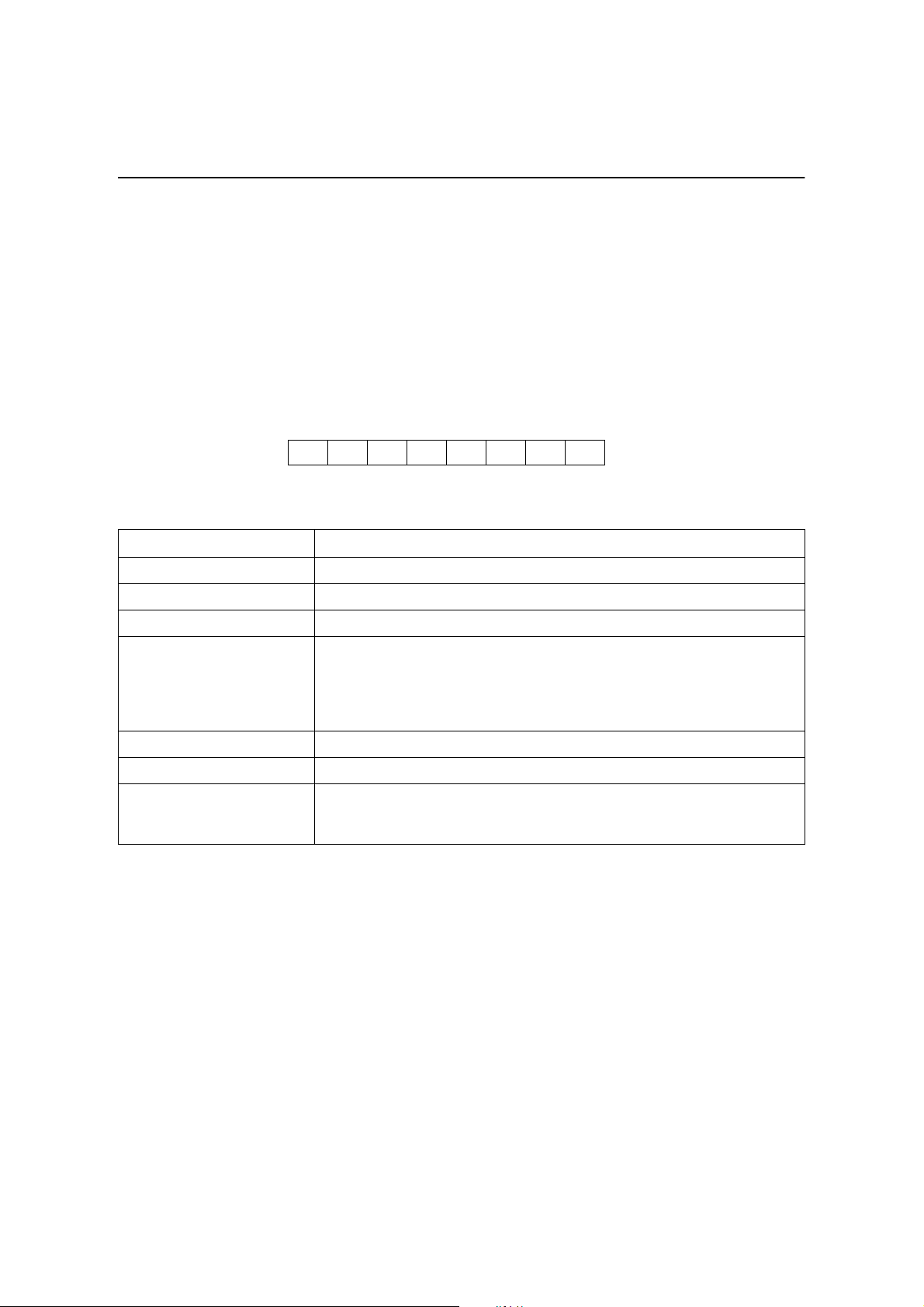

Special Function Register PSW

LSB

PSW

Bit No.

Addr. D0

MSB

76543210

H

CY AC F0 RS1 RS0 OV F1 P

Bit Function

Carry Flag

Auxiliary Carry Flag

(for BCD operations)

General Purpose Flag

Register Bank select control bits

Bank 0 selected, data address 00

Bank 1 selected, data address 08H - 0F

Bank 2 selected, data address 10H - 17

Bank 3 selected, data address 18H - 1F

H

- 07

H

H

H

H

Overflow Flag

General Purpose Flag

Parity Flag

Set/cleared by hardware each instruction cycle to indicate an odd/even

number of "one" bits in the accumulator, i.e. even parity.

RS1

0

0

1

1

CY

AC

F0

RS0

0

1

0

1

OV

F1

P

Reset value of PSW is 00H.

10 Jan. 2001 Ver 1.0

Page 15

GMS90X5XC Series HYUNDAI MicroElectronics

SPECIAL FUNCTION REGISTERS

All registers, except the program co unter and the four general pu rpose register banks, r eside in the special fu nction register area.

The 28 special function registers (SFR) include pointers and registers that provide an interface b etween the CPU

and the other on-chip peripherals. There are also 128 directly addressable bits within the SFR area.

All SFRs are listed in Table 1, Table 2, and Table 3.

In Table 1 they are organized in numeric order of their addresses. In Table 2 they are organized in groups which

refer to the functional blocks of the GMS90X5XC series. Table 3 illustrates the contents of the SFRs

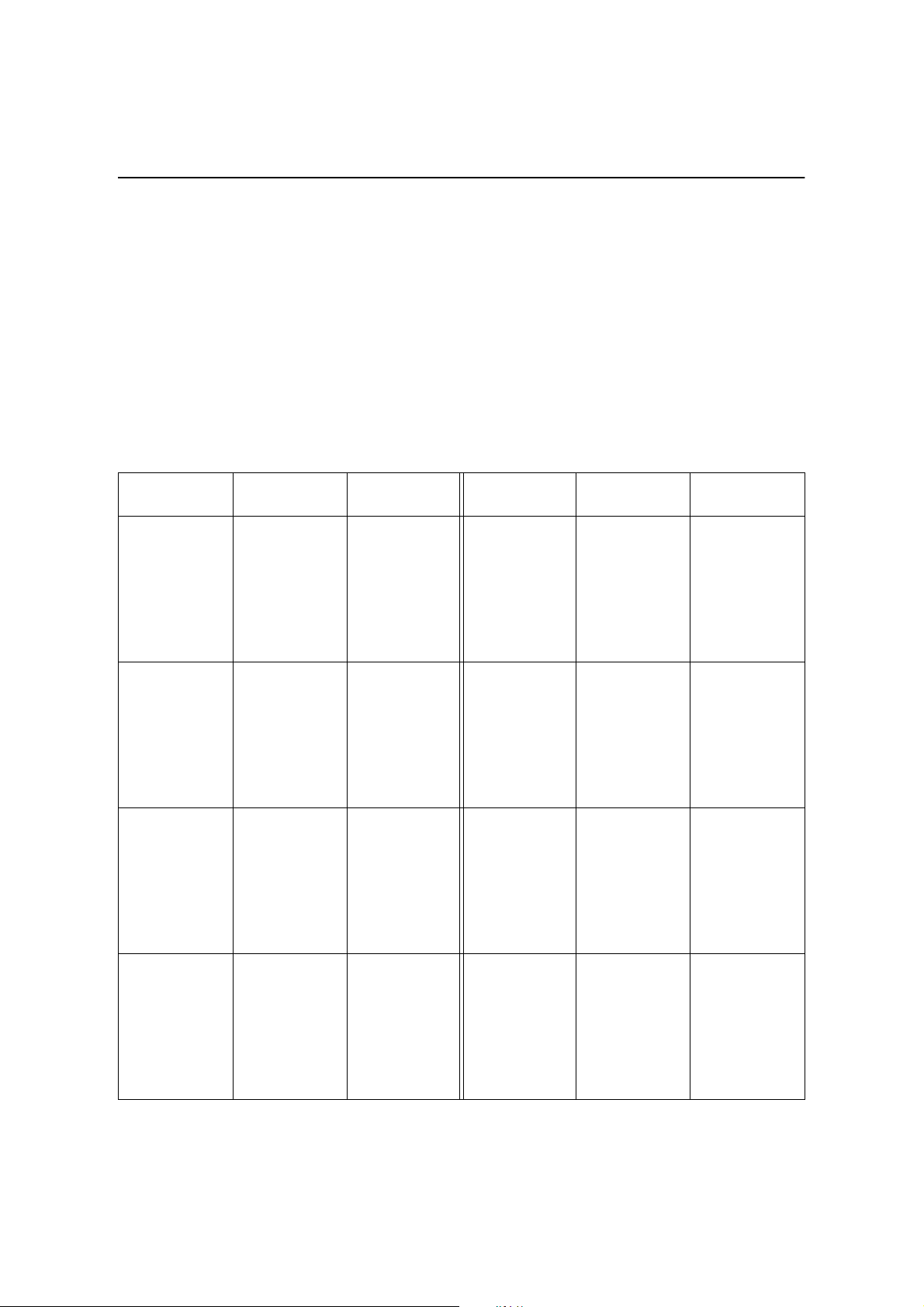

Table 1. Special Function Registers in Numeric Order of their Addresses

Address Register

80H

81H

82H

83H

84H

85H

86H

87H

90H

91H

92H

93H

94H

95H

96H

97H

A0H

A1H

A2H

A3H

A4H

A5H

A6H

A7H

B0H

B1H

B2H

B3H

B4H

B5H

B6H

B7H

1)

P0

SP

DPL

DPH

reserved

reserved

reserved

PCON

1)

P1

reserved

reserved

reserved

reserved

reserved

reserved

reserved

3)

P2

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

P3

reserved

reserved

reserved

reserved

reserved

reserved

reserved

Contents after

0XXX0000

Reset

FFH

07H

00H

00H

XXH

XXH

XXH

FF

00

XXH

XXH

XXH

XXH

XXH

XXH

FFH

XXH

XXH

XXH

XXH

XXH

XXH

XXH

FFH

XXH

XXH

XXH

XXH

XXH

XXH

XXH

Address Register

88H

89H

8AH

8BH

2)

2)

2)

2)

B

H

H

2)

2)

2)

2)

2)

2)

2)

2)

2)

2)

2)

2)

2)

8CH

8DH

8EH

8FH

98H

99H

9AH

9BH

9CH

9DH

9EH

9FH

A8H

A9H

AAH

ABH

ACH

ADH

AEH

AFH

B8H

2)

2)

2)

2)

2)

2)

2)

B9H

BAH

BBH

BCH

BDH

BEH

BFH

(cont’d)

TCON

TMOD

TL0

TL1

TH0

TH1

AUXR0

CKCON

SCON

SBUF

reserved

reserved

reserved

reserved

reserved

reserved

1)

IE

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

IP

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

1)

Contents after

XXXXXXX0

Reset

00H

00H

00H

00H

00H

00H

2)

XXH

00H

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

0X000000B

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

XX000000B

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

B

2)

2)

Jan. 2001 Ver 1.0 11

Page 16

HYUNDAI MicroElectronics GMS90X5XC Series

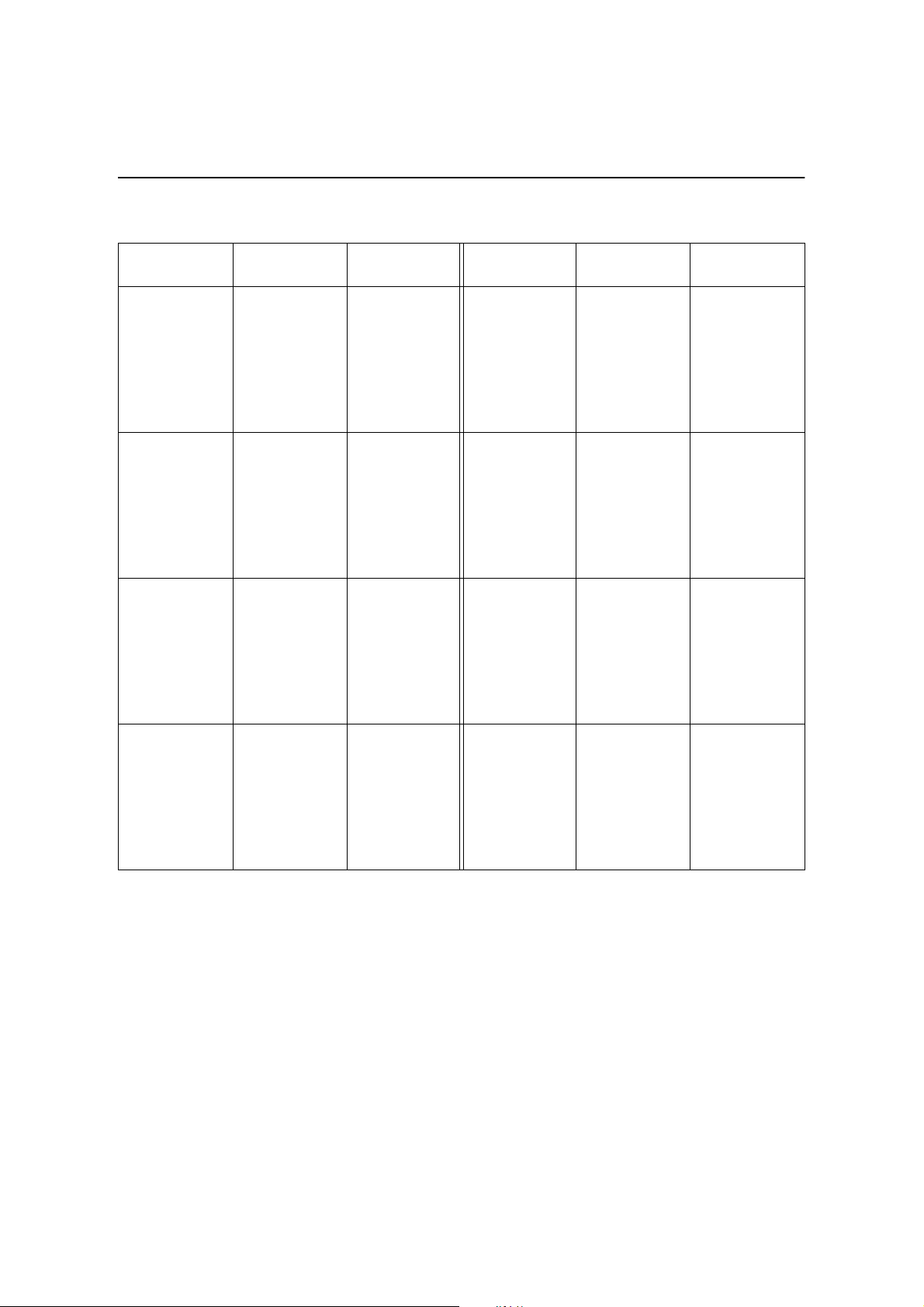

Table 1. Special Function Registers in Numeric Order of their Addresses

Address Register

C0H

C1H

C2H

C3H

C4H

C5H

C6H

C7H

D0H

D1H

D2H

D3H

D4H

D5H

D6H

D7H

E0H

E1H

E2H

E3H

E4H

E5H

E6H

E7H

F0H

F1H

F2H

F3H

F4H

F5H

F6H

F7H

1) Bit-addressable Special Function Register.

2) X means that the value is indeterminate and the location is reserved.

3) Bit-addressable Special Function Register.

4) These Registers are in the GMS90X52C/54C only.

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

PSW

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

ACC

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

B

reserved

reserved

reserved

reserved

reserved

reserved

reserved

Contents after

Reset

XX

H

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

FFH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

00H

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

00H

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

Address Register

3)

C8H

4)

C9H

3)

CAH

3)

CBH

3)

CCH

3)

CDH

CEH

CFH

D8H

D9H

DAH

DBH

DCH

DDH

DEH

DFH

E8H

E9H

EAH

EBH

ECH

EDH

EEH

EFH

F8H

F9H

FAH

FBH

FCH

FDH

FEH

FFH

(cont’d)

T2CON

T2MOD

RC2L

RC2H

TL2

TH2

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

1)

Contents after

Reset

00H

XXXXXX00

2)

B

00H

00H

00H

00H

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

2)

XXH

12 Jan. 2001 Ver 1.0

Page 17

GMS90X5XC Series HYUNDAI MicroElectronics

Table 2. Special Function Registers - Functional Blocks

Block Symbol Name Address

CPU ACC

B

DPH

DPL

PSW

SP

Interrupt System IE

IP

Ports P0

P1

P2

P3

Serial Channels PCON

SBUF

SCON

Timer 0/ Timer 1 TCON

TH0

TH1

TL0

TL1

TMOD

Timer 2 T2CON

T2MOD

RC2H

RC2L

TH2

TL2

AUXR0

Power Saving

PCON

Accumulator

B-Register

Data Pointer, High Byte

Data Pointer, Low Byte

Program Status Word Register

Stack Pointer

Interrupt Enable Register

Interrupt Priority Register

Port 0

Port 1

Port 2

Port 3

3)

Power Control Register

Serial Channel Buffer Reg.

Serial Channel 0 Control Reg.

Timer 0/1 Control Register

Timer 0, High Byte

Timer 1, High Byte

Timer 0, Low Byte

Timer 1, Low Byte

Timer Mode Register

Timer 2 Control Register

Timer 2 Mode Register

Timer 2 Reload Capture Reg., High Byte

Timer 2 Reload Capture Reg., Low Byte

Timer 2, High Byte

Timer 2, Low Byte

Aux. Register 0

3)

Power Control Register 87H 0XXX0000B

Modes

E0H

F0H

83H

82H

D0H

81H

A8H

B8H

80H

90H

A0H

B0H

87H

99H

98H

88H

8CH

8DH

8AH

8BH

89H

C8H

C9H

CBH

CAH

CDH

CCH

8EH

1)

1)

1)

1)

1)

1)

1)

1)

1)

1)

1)

1)

Contents

after Reset

00H

00H

00H

00H

00H

07H

0X000000B

XX000000B

FFH

FFH

FFH

FFH

0XXX0000B

2)

XXH

00H

00H

00H

00H

00H

00H

00H

00H

00H

00H

00H

00H

00H

XXXXXXX0B

2)

2)

2)

2)

2)

1) Bit-addressable Special Function register

2) X means that the value is indeterminate and the location is reserved

3) This special function register is listed repeatedly since some bit of it also belong to other functional blocks

Table 3. Contents of SFRs, SFRs in Numeric Order

Address Register

Bit 76543210

80H P0

Jan. 2001 Ver 1.0 13

Page 18

HYUNDAI MicroElectronics GMS90X5XC Series

Table 3. Contents of SFRs, SFRs in Numeric Order

Address Register

81H SP

82H DPL

83H DPH

87H PCON

88H TCON TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

89H TMOD GATE C/T

8AH TL0

8BH TL1

8CH TH0

8DH TH1

8EH AUXR0

8FH CKCON

90H P1

Bit 76543210

SMOD

-

-

---GF1GF0PDEIDLE

M1 MT GATE C/T M1 M0

------A0

------X2

98H SCON SM0 SM1 SM2 REN TB8 RB8 TI RI

99H SBUF

A0H P2

A8H IE EA - ET2 ES ET1 EX1 ET0 EX0

B0H P3

B8H IP - - PT2 PS PT1 PX1 PT0 PX0

SFR bit and byte addressable

SFR not bit addressable

- : this bit location is reserved

14 Jan. 2001 Ver 1.0

Page 19

GMS90X5XC Series HYUNDAI MicroElectronics

Table 3. Contents of SFRs, SFRs in Numeric Order

Address Register

Bit 76543210

C8H T2CON TF2 EXF2 RCLK TCLK

(cont’d)

EXEN2

TR2 C/T2

C9HT2MOD -----CAH RC2L

CBH RC2H

CCH TL2

CDH TH2

D0H PSW CY AC F0 RS1 RS0 OV F1 P

E0H ACC

F0H B

† indicates resident in the GMS90X52C/54C, not in 90X51C.

8EH

A0

A0 : ALE Signal Disable bit

0 : Enable ALE Signal (Generated ALE Signal)

1 : Disable ALE Signal (Not Generated ALE Signal)

CP/RL2

†

T2OE

DCEN

8FH

X2

X2 : CPU & Peripheral Clock Select bit

0 : Select 12 clock periods per machi ne cycle

1 : Select 6 clock periods per machine cycle

†

C9H

T2OE

T2OE : Timer2 Output Enable bit

0 : Disable Timer2 Output

1 : Enable Timer2 Output

SFR bit and byte addressable

SFR not bit addressable

- : this bit location is reserved

Jan. 2001 Ver 1.0 15

Page 20

HYUNDAI MicroElectronics GMS90X5XC Series

X2 MODE

The GMS90X5XC core needs only 6 clock periods per machine cycle. This feature called ”X2” provides the

following advantages:

• Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

• Save power consumption while keeping same CPU power (oscillator power saving).

• Save power consumption by dividing dynamically operating frequency by 2 in operating and idle

modes.

• Increase CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is in serted between the XTAL1 signal and th e

main clock input of the core (phase generator). This divider may be disabled by software.

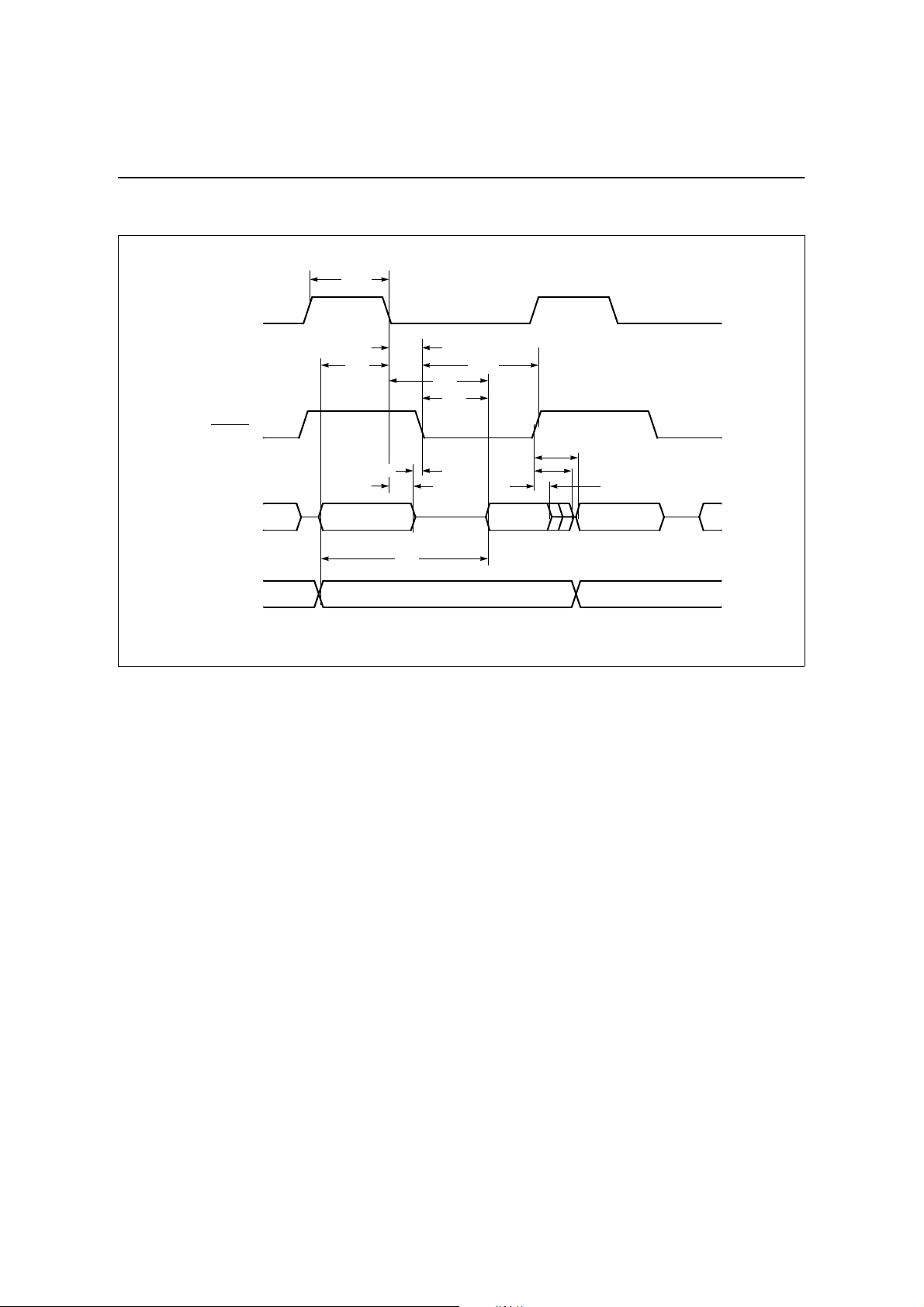

X2 Mode Description

The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and

peripherals. This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mo de, as this divider is bypassed,

the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 2. shows the clock generation block

diagram. X2 bit is validated on XTAL1

Figure 3.shows the mode switching waveforms:

÷

2 rising edge to avoid glitches when switching from X2 to STD mode.

f

XTAL1

Figure 2. Clock Generation Diagram

OSC

2

÷

0

1

X2

CKCON Register

State Machine: 6 clokc cyles

CPU control

The X2 bit in the CKCON register allows to switch from 12 clock cycles per instruction to 6 clock cycles and

vice versa. At reset, the standard speed is activated (STD mode). Setting this bit activates the X2 feature(X2

mode).

CAUTION

In order to prevent any incorrect operation while operating in X2 mode, user must be aware that all peripherals

using clock frequency as time reference (UART, timers) will have their time reference divide d by two. For example a free running timer generating an interrupt every 30 ms will then generate an interrupt every 15 ms.

UART with 2400 baud rate will have 4800 baud rate.

16 Jan. 2001 Ver 1.0

Page 21

GMS90X5XC Series HYUNDAI MicroElectronics

XTAL1

XTAL1:2

X2 bit

CPU Clock

STD Mode STD Mode

Figure 3. Mode Swithcing Waveforms

.

X2 Mode

Jan. 2001 Ver 1.0 17

Page 22

HYUNDAI MicroElectronics GMS90X5XC Series

TIMER / COUNTER 0 AND 1

Timer/Counter 0 and 1 can be used in four operating modes as listed in Table 4:

Table 4. Timer/Counter 0 and 1 Operating Modes

Mode Description

TMOD Input Clock

Gate C/T M1 M0 internal external (Max.)

0 8-bit timer/counter with a

XX00f

÷(12×32) f

OSC

OSC

÷(24×32)

divide-by-32 prescaler

1 16-bit timer/counter X X 0 1 f

2 8-bit timer/counter with

XX10 f

÷12 f

OSC

÷12 f

OSC

OSC

OSC

÷24

÷24

8-bit auto-reload

3 Timer/counter 0 used as

XX11 f

÷12 f

OSC

OSC

÷24

one 8-bit timer/counter and

one 8-bit timer Timer 1

stops

In the "timer" function (C/T

f

/12.

OSC

= "0") the register is incremented every machine cycle. Therefore the count rate is

In the "counter" function the register is incremented in response to a 1-to-0 transition at its corresponding external input pin (P3.4/T0, P3.5/T1). Since it takes two machine cycles to detect a falling edge the max. count rate

is f

/24. External inputs INT0 and INT1 (P3.2, P3.3) can b e programmed to functi on as a gate to facilit ate

OSC

pulse width measurements. Figure 4 illustrates the inpu t clock logic.

12

f

OSC

÷

f

OSC

12

÷

C/T

TMOD

0

P3.4/T0

P3.5/T1

Max.

f

OSC

P3.2 / INT0

P3.3 / INT1

/24

TR0 / 1

TCON

Gate

TMOD

1

&

=1

1

≥

Timer 0/1

Input Clock

Figure 4. Timer/Counter 0 and 1 Input Clock Logic

18 Jan. 2001 Ver 1.0

Page 23

GMS90X5XC Series HYUNDAI MicroElectronics

TIMER 2

Timer 2 is a 16-bit timer/Counter with an up/down count feature. It can operate either as timer or as an event

counter which is selected by bit C/T2

Table 5. Timer/Counter 2 Operating Modes

(T2CON.1). It has three operating modes as shown in Table 5.

Mode

16-bit Auto-

Reload

RCLK or

TCLK

0

0

T2CON T2MOD T2CON

CP/RL2 TR2 DCEN EXEN2 internal

0

1

0

P1.1/

T2EX

0

X

Remarks

reload upon overflow

0

1

0

↓

1

reload trigger (fall-

Input Clock

÷ 12 Max.

f

OSC

external

(P1.0/T2)

f

OSC

ing edge)

16-bit

Capture

0

0

0

0

1

1

X

0

Down counting

0

1

1

X

1

Up counting

1

1

X

0

X↓16 bit Timer/ Coun-

ter (only up-count-

÷ 12 Max.

f

OSC

f

OSC

ing)

Baud Rate

Generator

0

1

1

1

X

1

X

1

X

0

capture TH2,TL2

→

RC2H,RC2L

X↓no overflow

interrupt request

÷ 12 Max.

f

OSC

f

OSC

(TF2)

1

X

1

X

1

extra external interrupt ("Timer 2")

Off X X 0 X X X Timer 2 stops - -

Note: ↓ = falling edge

÷24

÷ 24

÷ 24

Jan. 2001 Ver 1.0 19

Page 24

HYUNDAI MicroElectronics GMS90X5XC Series

2

SMOD

32

------------------

Timer 1 overflow

()×

2

SMOD

32

------------------

f

OSC

12 256 TH1

()–[]×

--------------------------------------------------

×

SERIAL INTERFACE (USART)

The serial port is full du plex and can operate in four modes (one synchronous mode, t hree asynchronous modes )

as illustrated in Table 6. The possible baud rates can be calculated using the formulas give n in Table 7.

Table 6. USART Operating Modes

Mode

Baudrate Description

SM0 SM1

SCON

f

OSC

0 0 0 Serial data enters and exits through RxD.

------------

12

TxD outputs the shift clock. 8-bit are transmitted/received (LSB first)

1 0 1 Time r 1/2 overfl ow rate 8-bit UA RT

10 bits are transmitted (through TxD) or

received (RxD)

f

2 1 0 or 9-bit UART

------------

OSC

32

f

OSC

------------

64

11 bits are transmitted (TxD) or received (RxD)

3 1 1 Time r 1/2 overfl ow rate 9-bit UA RT

Like mode 2 except the variable baud rate

Table 7. Formulas for Calculating Baud rates

Baud Rate

derived from

Oscillator 0

Timer 1 (16-bit timer)

(8-bit timer with

8-bit auto reload)

Timer 2 1,3

Interface Mode Baudrate

f

OSC

------------

12

SMOD

2

------------------

×

2

64

f

OSC

1,3

1,3

f

--------------------------------------------------------------------------------- -

32 65536 RC2H RC2L

OSC

,()–[]×

20 Jan. 2001 Ver 1.0

Page 25

GMS90X5XC Series HYUNDAI MicroElectronics

INTERRUPT SYSTEM

The GMS90X5XC series provides 5 (4K bytes ROM version) or 6 (above 8K bytes ROM version) interrupt

sources with two priority levels. Figure 5 gives a general overview of the interrupt sources and illustrates the

request and control flags.

High

Priority

Timer 0 Overflow

TF0

TCON.5

ET0

IE.1

PT0

IP.1

Low

Priority

P1.1/

T2EX

P3.2/

INT0

P3.3/

INT1

Timer 1 Overflow

Timer 2 Overflow

EXEN2

T2CON.3

UART

IT0

TCON.0

IT1

TCON.2

TF2

T2CON.7

EXF2

T2CON.6

RI

SCON.0

TI

SCON.1

TF1

TCON.7

1

≥

1

≥

IE0

TCON.1

IE1

TCON.3

ET1

IE.3

ET2

IE.5

ES

IE.4

EX0

IE.0

EX1

IE.2

EA

IE.7

PT1

IP.3

PT2

IP.5

PS

IP.4

PX0

IP.0

PX1

IP.2

: Low level triggered

: Falling edge triggered

Figure 5. Interrupt Request Sources

Jan. 2001 Ver 1.0 21

Page 26

HYUNDAI MicroElectronics GMS90X5XC Series

Table 8. Interrupt Sources and their Corresponding Interrupt Vectors

Source (Request Flags) Vectors Vector Address

RESET

IE0

TF0

IE1

TF1

RI + TI

TF2 + EXF2

RESET

External interrupt 0

Timer 0 interrupt

External interrupt 1

Timer 1 interrupt

Serial port interrupt

Timer 2 interrupt

0000H

0003H

000BH

0013H

001BH

0023H

002BH

A low-priority interrupt can itself be interrupted by a high-priority interrupt, but not by another low priority interrupt. A high-priority interrupt cannot be interrupted by any other interrupt source.

If two requests of different priority level are received simultaneously, the request of higher priority is serviced.

If requests of the same priority are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling

sequence as shown in Table 9.

Table 9. Interrupt Priority-Within-Level

Interrupt Source Priority

External Interrupt 0

Timer 0 Interrupt

External Interrupt 1

Timer 1 Interrupt

Serial Channel

Timer 2 Interrupt

IE0

TF0

IE1

TF1

RI + TI

TF2 + EXF2

High

↓

↓

↓

↓

Low

22 Jan. 2001 Ver 1.0

Page 27

GMS90X5XC Series HYUNDAI MicroElectronics

Power Saving Modes

Two power down modes are available, the Idle Mode and Power Down Mode.

The bits PDE and IDLE of the register PCON select the Power Down mode or the Idle mode, respectively. If

the Power Down mode and the Idle mode are set at the same time, the Power Down mode takes precedence.

Table 10 gives a general overview of the power saving modes.

Table 10. Power Saving Modes Overview

Entering

Mode

Instruction

Example

Leaving by Remarks

Idle mode ORL PCON, #01H - Enabled interrupt

- Hardware Reset

Power-Down mode ORL PCON, #02H Hardware Reset Oscillator is stopped, contents of on-

In the Power Down mode of operatio n, V

however, that V

is not reduced before the Power Down m ode is invoked, and th at VCC is restored to its normal

CC

can be reduced to minimize power consump tion. It must be ensured,

CC

CPU is gated off

CPU status registers maintain their

data.

Peripherals are active

chip RAM and SFR’s are maintained

(leaving Power Down Mode means

redefinition of SFR contents).

operating level, before the Power Down mode is terminated. The reset signal that terminates th e Power Down

mode also restarts the oscillator. The reset should not be activated before V

is restored to its normal operating

CC

level and must be held active long enough to allow the oscillator to rest art and stabilize (similar to po wer-on

reset).

Jan. 2001 Ver 1.0 23

Page 28

HYUNDAI MicroElectronics GMS90X5XC Series

ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings

Ambient temperature under bias (TA)......................................................................................-40 to + 85 °C

Storage temperature (T

Voltage on V

pins with respect to ground (VSS) .................................................................-0.5V to 6.5V

CC

Voltage on any pin with respect to ground (V

)...................................................................................................... -65 to + 150 °C

ST

) ..........................................................-0.5V to VCC + 0.5V

SS

Input current on any pin during overload condition............................................................-15mA to +15mA

Absolute sum of all input currents during overload condition...........................................................|100mA|

Power dissipation ....................................................................................................................................1.5W

Note: Stresses above those listed under "Abs olute Maximum Ratings" may cau se permanent da mage of the device. This is a stress rating only and functional operation of the device at these or any other conditions above

those indicated i n the operat ional sec tions of th is speci fication is not imp lied. Exposure to absolu te maxim um rating conditions for longer periods may affect device reliability. During overload conditions (V

the Voltage on V

mum ratings.

pins with respect to ground (VSS) must not exceed the values defined by the absolute maxi-

CC

> VCC or VIN < VSS)

IN

24 Jan. 2001 Ver 1.0

Page 29

GMS90X5XC Series HYUNDAI MicroElectronics

DC Characteristics

DC Characteristics for GMS90C51C/52C/54C

= 5V + 10%, -15%; VSS=0V; TA= 0°C to 70°C

V

CC

Parameter Symbol

Input low voltage

(except EA

Input low voltage (EA

, RESET)

)V

Input low voltage (RESET) V

Input high voltage (except

XTAL1, EA

, RESET)

Input high voltage to XTAL1 V

Input high voltage to EA

,

V

IL

IL1

IL2

V

IH

IH1

V

IH2

0.2VCC + 0.9 VCC + 0.5 V -

Limit Values

Min. Max.

Unit Test Conditions

-0.5 0.2VCC - 0.1 V -

-0.5 0.2VCC - 0.3 V -

-0.5 0.2VCC + 0.1 V -

0.7V

0.6V

CC

CC

VCC + 0.5 V VCC + 0.5 V -

RESET

Output low voltage

V

OL

-0.45VI

= 1.6mA

OL

1)

(ports 1, 2, 3)

Output low voltage

(port 0, ALE, PSEN

)

Output high voltage

(ports 1, 2, 3)

Output high voltage

(port 0 in external bus

V

V

V

OL1

OH

OH1

-0.45VI

2.4

0.9V

2.4

0.9V

CC

CC

-VI

-VI

= 3.2mA

OL

= -80µA

OH

= -10µA

I

OH

= -800µA

OH

IOH= -80µA

1)

2)

2)

mode, ALE, PSEN)

Logic 0 input current

I

IL

-10 -50

µ

AVIN= 0.45V

(ports 1, 2, 3)

Logical 1-to-0 transition cur-

I

TL

-65 -650

µ

AVIN= 2.0V

rent (ports 1, 2, 3)

Input leakage current

I

LI

-

±

1

µ

A 0.45 < VIN < V

CC

(port 0, EA)

Pin capacitance C

Power supply current:

Active mode, 12MHz

Idle mode, 12MHz

Active mode, 24 MHz

Idle mode, 24MHz

Active mode, 40 MHz

Idle mode, 40 MHz

Power Down Mode

1) Capacitive loading on ports 0 and 2 may cause spurious noise pulses to be superimposed on the VOL of ALE and port 3.

The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operation. In the worst case (capacitive loading: > 50pF at 3.3V, > 100pF at 5V), the noise pulse on ALE

line may exceed 0.8V. In such cases it may be desirable to qualify ALE with a schmitt-trigger, or use an address latch with

a schmitt-trigger strobe input.

3)

3)

3)

3)

3)

3)

3)

I

I

I

I

I

I

I

IO

CC

CC

CC

CC

CC

CC

PD

-10pFf

-

-

-

-

-

-

-

21

4.8

36.2

8.2

58.5

12.5

50

mA

mA

mA

mA

mA

mA

µ

A

= 1MHz

C

T

= 25°C

A

V

= 5V

CC

VCC= 5V

VCC= 5V

VCC= 5V

VCC= 5V

VCC= 5V

VCC= 5V

4)

5)

4)

5)

4)

5)

6)

Jan. 2001 Ver 1.0 25

Page 30

HYUNDAI MicroElectronics GMS90X5XC Series

2) Capacitive loading on ports 0 and 2 may cause the VOH on ALE and PSEN to momentarily fall below the 0.9VCC specification when the address lines are stabilizing.

3) I

Max at other frequencies is given by:

CC

active mode: I

idle mode: I

where f

OSC

(active mode) is measured with:

4) I

CC

XTAL1 driven with t

= Port0 = RESET = VCC; all other pins are disconnected. ICC would be slightly higher if a crystal oscillator is used (appr.

EA

1mA).

(Idle mode) is measured with all output pins disconnected and with all peripherals disabled;

5) I

CC

XTAL1 driven with t

RESET = EA

(Power Down Mode) is measured under following conditions:

6) I

PD

= Port0 = VCC; RESET = VSS; XTAL2 = N.C.; XTAL1 = VSS; all other pins are disconnected.

EA

= 1.27 × f

CC

= 0.28 × f

CC

+ 5.73

OSC

+ 1.45 (except OTP devices)

OSC

is the oscillator frequency in MHz. ICC values are given in mA and measured at VCC = 5V.

, t

CLCH

CLCH

= 5ns, VIL = VSS + 0.5V, VIH = VCC - 0.5V; XTAL2 = N.C.;

CHCL

, t

= 5ns, VIL = VSS + 0.5V, VIH = VCC - 0.5V; XTAL2 = N.C.;

CHCL

= VSS; Port0 = VCC; all other pins are disconnected;

26 Jan. 2001 Ver 1.0

Page 31

GMS90X5XC Series HYUNDAI MicroElectronics

DC Characteristics for GMS90L51C/52C/54C

= 3.3V + 0.3V, -0.6V; VSS=0V; TA= 0°C to 70°C

V

CC

Parameter Symbol

Input low voltage V

Input high voltage V

Output low voltage

V

(ports 1, 2, 3)

Output low voltage

(port 0, ALE, PSEN

Output high voltage

)

V

V

(ports 1, 2, 3)

Output high voltage

V

(port 0 in external bus

mode, ALE, PSEN

)

Logic 0 input current

(ports 1, 2, 3)

Logical 1-to-0 transition current (ports 1, 2, 3)

Input leakage current

(port 0, EA

)

Pin capacitance C

Power supply current:

Active mode, 16 MHz

Idle mode, 16MHz

Power Down Mode

3)

3)

3)

OL

OL1

OH

OH1

I

IL

I

TL

I

LI

I

CC

I

CC

I

PD

Limit Values

Unit Test Conditions

Min. Max.

IL

IH

IO

-0.5 0.8 V -

2.0 VCC + 0.5 V -

-0.45

0.30

-0.45

0.30

2.0

0.9V

2.0

0.9V

CC

CC

-VI

-VI

-1 -50

-25 -250

-

±

1

-10pFf

-

-

-

15

5

10

VIOL= 1.6mA

IOL= 100µA

VIOL= 3.2mA

IOL= 200µA

= -20µA

OH

I

= -10µA

OH

= -800µA

OH

IOH= -80µA

µ

AVIN= 0.45V

µ

AVIN= 2.0V

µ

A 0.45 < VIN < V

= 1MHz

C

= 25°C

T

A

V

mA

mA

µ

A

= 3.6V

CC

VCC= 2.6V

VCC=2~ 5.5V

1)

1)

1)

1)

2)

2)

CC

4)

5)

6)

Jan. 2001 Ver 1.0 27

Page 32

HYUNDAI MicroElectronics GMS90X5XC Series

AC Characteristics

Explanation of the AC Symbols

Each timing symbol has 5 characters. The first character is always a ‘t’ (stand for time). The other characters,

depending on their positions, stand for the name of a signal or the logical status of that signal. The following is

a list of all the characters and what they stand for.

A: Address

C: Clock

D: Input Data

H: Logic level HIGH

I: Instruction (program memory contents)

L: Logic level LOW, or ALE

P: PSEN

Q: Output Data

R: RD

signal

AC Characteristics for GMS90X5XC series (12MHz version)

T: Time

V: Valid

signal

W: WR

X: No longer a valid logic level

Z: Float

For example,

= Time from Address Valid to ALE Low

t

AVLL

t

= Time from ALE Low to PSEN Low

LLPL

VCC= 5V :

V

= 3.3V :

CC

Variable clock :

= 5V + 10%, − 15%; VSS= 0V; TA= 0°C to 70°C

V

CC

for port 0. ALE and PSEN outputs = 100pF; CL for all other outputs = 80pF)

(C

L

= 3.3V + 0.3V, − 0.6V; VSS= 0V; TA= 0°C to 70°C

V

CC

(C

for port 0. ALE and PSEN outputs = 50pF; CL for all other outputs = 50pF)

L

Vcc = 5V : 1/t

Vcc = 3.3V : 1/t

= 3.5 MHz to 12 MHz

CLCL

= 1 MHz to 12 MHz

CLCL

External Program Memory Characteristics

Parameter Symbol

ALE pulse width t

Address setup to ALE t

Address hold after ALE t

ALE low to valid instruction in t

ALE to PSEN t

PSEN

pulse width t

PSEN

to valid instr uction in t

Input instruction hold after PSEN t

Input instruction float after PSEN

Address valid after PSEN

Address to valid instruction in t

Address float to PSEN

LHLL

AVLL

LLAX

LLIV

LLPL

PLPH

PLIV

PXIX

t

PXIZ

t

PXAV

AVIV

t

AZPL

†

†

12 MHz Oscillator

Variable Oscillator

1/t

= 3.5 to 12MHz

CLCL

Unit

Min. Max. Min. Max.

127 - 2t

43 - t

30 - t

-233 -4t

58 - t

215 - 3t

-150 -3t

-40 - ns

CLCL

-40 - ns

CLCL

-53 - ns

CLCL

-100 ns

CLCL

-25 - ns

CLCL

-35 - ns

CLCL

-100 ns

CLCL

0- 0 - ns

-63 -t

75 - t

-8 - ns

CLCL

-302 -5t

-20 ns

CLCL

-115 ns

CLCL

0- 0 - ns

28 Jan. 2001 Ver 1.0

Page 33

GMS90X5XC Series HYUNDAI MicroElectronics

†

Interfacing the GMS90X5XC series to devices with float times up to 75 ns is permissible. This limited bus contention will not

cause

any damage to port 0 Drivers.

Jan. 2001 Ver 1.0 29

Page 34

HYUNDAI MicroElectronics GMS90X5XC Series

AC Characteristics for GMS90X5XC series (12MHz)

External Data Memory Characteristics

Parameter Symbol

pulse width t

RD

WR

pulse widt h t

Address hold after ALE t

RD

to valid data in t

Data hold after RD

Data float after RD

ALE to valid data in t

Address to valid data in t

ALE to WR

or RD t

Address valid to WR or RD t

WR

or RD high to ALE high t

Data valid to WR

transition t

Data setup before WR t

Data hold after WR

Address float after RD

RLRH

WLWH

LLAX2

RLDV

t

RHDX

t

RHDZ

LLDV

AVDV

LLWL

AVWL

WHLH

QVWX

QVWH

t

WHQX

t

RLAZ

12 MHz Oscillator

Variable Oscillator

1/t

= 3.5 to 12MHz

CLCL

Unit

Min. Max. Min. Max.

400 - 6 t

400 - 6 t

53 - t

-252 -5t

-100 - ns

CLCL

-100 - ns

CLCL

-30 - ns

CLCL

-165 ns

CLCL

0- 0 - ns

-97 -2t

-517 -8t

-585 -9t

200 300 3t

203 - 4t

43 123 t

33 - t

433 - 7t

33 - t

-50 3 t

CLCL

-130 - ns

CLCL

-40 t

CLCL

-50 - ns

CLCL

-150 - ns

CLCL

-50 - ns

CLCL

-70 ns

CLCL

-150 ns

CLCL

-165 ns

CLCL

+50 ns

CLCL

+40 ns

CLCL

-0 - 0 ns

Advance Information (12MHz)

External Clock Drive

Variable Oscillator

Parameter Symbol

(Freq. = 3.5 to 12MHz)

Unit

Min. Max.

Oscillator period (VCC=5V)

Oscillator period (V

CC

=3.3V)

High time t

Low time t

Rise time t

Fall time t

t

CLCL

t

CLCL

CHCX

CLCX

CLCH

CHCL

83.3

83.3

20 t

20 t

CLCL

CLCL

285.7

1

- t

- t

CLCX

CHCX

ns

ns

ns

-20ns

-20ns

30 Jan. 2001 Ver 1.0

Page 35

GMS90X5XC Series HYUNDAI MicroElectronics

AC Characteristics for GMS90X5XC series (16MHz version)

= 3.3V + 0.3V, −0.6V; VSS= 0V; TA= 0°C to 70°C

V

CC

(CL for port 0. ALE and PSEN outputs = 50pF; CL for all other outputs = 50pF)

External Program Memory Characteristics

Parameter Symbol

16 MHz Oscillator

Variable Oscillator

= 3.5 to 16MHz

1/t

CLCL

Unit

Min. Max. Min. Max.

ALE pulse width t

Address setup to ALE t

Address hold after ALE t

ALE low to valid instruction in t

ALE to PSEN t

PSEN

pulse width t

PSEN

to valid instr uction in t

Input instruction hold after PSEN t

Input instruction float after PSEN

Address valid after PSEN

Address to valid instruction in t

Address float to PSEN

†

Interfacing the GMS90X5XC series to devices with float times up to 35 ns is permissible. This limited bus contention will not

cause

any damage to port 0 Drivers.

LHLL

AVLL

LLAX

LLIV

LLPL

PLPH

PLIV

PXIX

t

PXIZ

t

PXAV

AVIV

t

AZPL

†

†

85 - 2t

23 - t

23 - t

-150 -4t

38 - t

153 - 3t

-88 -3t

-40 - ns

CLCL

-40 - ns

CLCL

-40 - ns

CLCL

-100 ns

CLCL

-25 - ns

CLCL

-35 - ns

CLCL

-100 ns

CLCL

0- 0 - ns

-43 -t

55 - t

-8 - ns

CLCL

-198 -5t

-20 ns

CLCL

-115 ns

CLCL

0- 0 - ns

Jan. 2001 Ver 1.0 31

Page 36

HYUNDAI MicroElectronics GMS90X5XC Series

AC Characteristics for GMS90X5XC series (16MHz)

External Data Memory Characteristics

Parameter Symbol

pulse width t

RD

WR

pulse widt h t

Address hold after ALE t

RD

to valid data in t

Data hold after RD

Data float after RD

ALE to valid data in t

Address to valid data in t

ALE to WR

or RD t

Address valid to WR or RD t

WR

or RD high to ALE high t

Data valid to WR

transition t

Data setup before WR

Data hold after WR

Address float after RD

RLRH

WLWH

LLAX2

RLDV

t

RHDX

t

RHDZ

LLDV

AVDV

LLWL

AVWL

WHLH

QVWX

t

QVWH

t

WHQX

t

RLAZ

16 MHz Oscillator

Variable Oscillator

1/t

= 3.5 to 16MHz

CLCL

Unit

Min. Max. Min. Max.

275 - 6 t

275 - 6 t

23 - t

-183 -5t

-100 - ns

CLCL

-100 - ns

CLCL

-40 - ns

CLCL

-130 ns

CLCL

0- 0 - ns

-75 -2t

-350 -8t

-398 -9t

138 238 3t

120 - 4t

28 97 t

13 - t

288 - 7t

23 - t

−

50 3t

CLCL

-130 - ns

CLCL

−

35 t

CLCL

−

50 - ns

CLCL

-150 - ns

CLCL

−

40 - ns

CLCL

-50 ns

CLCL

-150 ns

CLCL

-165 ns

CLCL

+50 ns

CLCL

+35 ns

CLCL

-0 - 0 ns

Advance Information (16MHz)

External Clock Drive

Variable Oscillator

Parameter Symbol

(Freq. = 3.5 to 16MHz)

Unit

Min. Max.

Oscillator period t

High time t

Low time t

Rise time t

Fall time t

CLCL

CHCX

CLCX

CLCH

CHCL

62.5 285.7 ns

17 t

17 t

CLCL

CLCL

- t

- t

CLCX

CHCX

ns

ns

-17ns

-17ns

32 Jan. 2001 Ver 1.0

Page 37

GMS90X5XC Series HYUNDAI MicroElectronics

AC Characteristics for GMS90X5XC series (24MHz version)

= 5V + 10%, −15%; VSS= 0V; TA= 0°C to 70°C

V

CC

(CL for port 0. ALE and PSEN outputs = 100pF; CL for all other outputs = 80pF)

External Program Memory Characteristics

Parameter Symbol

24 MHz Oscillator

Variable Oscillator

= 3.5 to 24MHz

1/t

CLCL

Unit

Min. Max. Min. Max.

ALE pulse width t

Address setup to ALE t

Address hold after ALE t

ALE low to valid instruction in t

ALE to PSEN t

PSEN

pulse width t

PSEN

to valid instr uction in t

Input instruction hold after PSEN t

Input instruction float after PSEN

Address valid after PSEN

Address to valid instruction in t

Address float to PSEN

†

Interfacing the GMS90X5XC series to devices with float times up to 35 ns is permissible. This limited bus contention will not

cause

any damage to port 0 Drivers.

LHLL

AVLL

LLAX

LLIV

LLPL

PLPH

PLIV

PXIX

t

PXIZ

t

PXAV

AVIV

t

AZPL

†

†

43 - 2t

17 - t

17 - t

-80 -4t

22 - t

95 - 3t

-60 -3t

-40 - ns

CLCL

-25 - ns

CLCL

-25 - ns

CLCL

-87 ns

CLCL

-20 - ns

CLCL

-30 - ns

CLCL

-65 ns

CLCL

0- 0 - ns

-32 -t

37 - t

-5 - ns

CLCL

-148 -5t

-10 ns

CLCL

-60 ns

CLCL

0- 0 - ns

Jan. 2001 Ver 1.0 33

Page 38

HYUNDAI MicroElectronics GMS90X5XC Series

AC Characteristics for GMS90X5XC series (24MHz)

External Data Memory Characteristics

Parameter Symbol

pulse width t

RD

WR

pulse widt h t

Address hold after ALE t

RD

to valid data in t

Data hold after RD

Data float after RD

ALE to valid data in t

Address to valid data in t

ALE to WR

or RD t

Address valid to WR or RD t

WR

or RD high to ALE high t

Data valid to WR

transition t

Data setup before WR t

Data hold after WR

Address float after RD

RLRH

WLWH

LLAX2

RLDV

t

RHDX

t

RHDZ

LLDV

AVDV

LLWL

AVWL

WHLH

QVWX

QVWH

t

WHQX

t

RLAZ

24 MHz Oscillator

Variable Oscillator

1/t

= 3.5 to 24MHz

CLCL

Unit

Min. Max. Min. Max.

180 - 6t

180 - 6t

15 - t

-118 -5t

-70 - ns

CLCL

-70 - ns

CLCL

-27 - ns

CLCL

-90 ns

CLCL

0- 0 - ns

-63 -2t

-200 -8t

-220 -9t

75 175 3t

67 - 4t

17 67 t

5-t

170 - 7t

15 - t

-50 3 t

CLCL

-97 - ns

CLCL

-25 t

CLCL

-37 - ns

CLCL

-122 - ns

CLCL

-27 - ns

CLCL

-20 ns

CLCL

-133 ns

CLCL

-155 ns

CLCL

+50 ns

CLCL

+25 ns

CLCL

-0 - 0 ns

Advance Information (24MHz)

External Clock Drive

Variable Oscillator

Parameter Symbol

(Freq. = 3.5 to 24MHz)

Unit

Min. Max.

Oscillator period t

High time t

Low time t

Rise time t

Fall time t

CLCL

CHCX

CLCX

CLCH

CHCL

41.7 285.7 ns

12 t

12 t

CLCL

CLCL

- t

- t

CLCX

CHCX

ns

ns

-12ns

-12ns

34 Jan. 2001 Ver 1.0

Page 39

GMS90X5XC Series HYUNDAI MicroElectronics

AC Characteristics for GMS90X5XC series (33MHz version)

= 5V + 10%, −15%; VSS= 0V; TA= 0°C to 70°C

V

CC

(CL for port 0. ALE and PSEN outputs = 100pF; CL for all other outputs = 80pF)

External Program Memory Characteristics

Parameter Symbol

33 MHz Oscillator

Variable Oscillator

= 3.5 to 33MHz

1/t

CLCL

Unit

Min. Max. Min. Max.

ALE pulse width t

Address setup to ALE t

Address hold after ALE t

ALE low to valid instruction in t

ALE to PSEN t

PSEN

pulse width t

PSEN

to valid instr uction in t

Input instruction hold after PSEN t

Input instruction float after PSEN

Address valid after PSEN

Address to valid instruction in t

Address float to PSEN

†

Interfacing the GMS90X5XC series to devices with float times up to 35 ns is permissible. This limited bus contention will not

cause

any damage to port 0 Drivers.

LHLL

AVLL

LLAX

LLIV

LLPL

PLPH

PLIV

PXIX

t

PXIZ

t

PXAV

AVIV

t

AZPL

†

†

40 - 2t

10 - t

10 - t

-56 -4t

15 - t

80 - 3t

-35 -3t

-20 - ns

CLCL

-20 - ns

CLCL

-20 - ns

CLCL

-65 ns

CLCL

-15 - ns

CLCL

-20 - ns

CLCL

-55 ns

CLCL

0- 0 - ns

-20 -t

25 - t

-5 - ns

CLCL

-91 -5t

-10 ns

CLCL

-60 ns

CLCL

0- 0 - ns

Jan. 2001 Ver 1.0 35

Page 40

HYUNDAI MicroElectronics GMS90X5XC Series

AC Characteristics for GMS90X5XC series (33MHz)

External Data Memory Characteristics

Parameter Symbol

pulse width t

RD

WR

pulse widt h t

Address hold after ALE t

RD

to valid data in t

Data hold after RD

Data float after RD

ALE to valid data in t

Address to valid data in t

ALE to WR

or RD t

Address valid to WR or RD t

WR

or RD high to ALE high t

Data valid to WR

transition t

Data setup before WR t

Data hold after WR

Address float after RD

RLRH

WLWH

LLAX2

RLDV

t

RHDX

t

RHDZ

LLDV

AVDV

LLWL

AVWL

WHLH

QVWX

QVWH

t

WHQX

t

RLAZ

33 MHz Oscillator

Variable Oscillator

1/t

= 3.5 to 33MHz

CLCL

Unit

Min. Max. Min. Max.

132 - 6t

132 - 6t

10 - t

-81 -5t

-50 - ns

CLCL

-50 - ns

CLCL

-20 - ns

CLCL

-70 ns

CLCL

0- 0 - ns

-46 -2t

-153 -8t

-183 -9t

71 111 3t

66 - 4t

10 40 t

5-t

142 - 7t

10 - t

-20 3 t

CLCL

-55 - ns

CLCL

-20 t

CLCL

-25 - ns

CLCL

-70 - ns

CLCL

-20 - ns

CLCL

-15 ns

CLCL

-90 ns

CLCL

-90 ns

CLCL

+20 ns

CLCL

+20 ns

CLCL

-0 - 0 ns

Advance Information (33MHz)

External Clock Drive

Variable Oscillator

Parameter Symbol

(Freq. = 3.5 to 24MHz)

Unit

Min. Max.

Oscillator period t

High time t

Low time t

Rise time t

Fall time t

CLCL

CHCX

CLCX

CLCH

CHCL

30.3 285.7 ns

11.5 t

11.5 t

CLCL

CLCL

- t

- t

CLCX

CHCX

ns

ns

-5ns

-5ns

36 Jan. 2001 Ver 1.0

Page 41

GMS90X5XC Series HYUNDAI MicroElectronics

AC Characteristics for GMS90X5XC series (40MHz version)

= 5V + 10%, − 15%; VSS= 0V; TA= 0°C to 70°C

V

CC

(CL for port 0. ALE and PSEN outputs = 100pF; CL for all other outputs = 80pF)

External Program Memory Characteristics

Parameter Symbol

40 MHz Oscillator

Variable Oscillator

= 3.5 to 40MHz

1/t

CLCL

Unit

Min. Max. Min. Max.

ALE pulse width t

Address setup to ALE t

Address hold after ALE t

ALE low to valid instruction in t

ALE to PSEN

pulse width t

PSEN

to valid instr uction in t

PSEN

Input instruction hold after PSEN

Input instruction float after PSEN

Address valid after PSEN

Address to valid instruction in t

Address float to PSEN

†

Interfacing the GMS90X5XC series to devices with float times up to 20 ns is permissible. This limited bus contention will not

cause any damage to port 0 Drivers.

LHLL

AVLL

LLAX

LLIV

t

LLPL

PLPH

PLIV

t

PXIX

t

PXIZ

t

PXAV

AVIV

t

AZPL

†

†

35 - 2t

10 - t

10 - t

-55 -4t

10 - t

60 - 3t

-25 -3t

0- 0 - ns

-15 -t

20 - t

-65 -5t

5- 5 - ns

−

15 - ns

CLCL

−

15 - ns

CLCL

−

15 - ns

CLCL

−

45 ns

CLCL

−

15 - ns

CLCL

−

15 - ns

CLCL

−

50 ns

CLCL

−

10 ns

CLCL

−

5- ns

CLCL

−

60 ns

CLCL

Jan. 2001 Ver 1.0 37

Page 42

HYUNDAI MicroElectronics GMS90X5XC Series

AC Characteristics for GMS90X5XC series (40MHz)

External Data Memory Characteristics

Parameter Symbol

pulse width t

RD

WR

pulse widt h t

Address hold after ALE t

RD

to valid data in t

Data hold after RD

Data float after RD

ALE to valid data in t

Address to valid data in t

ALE to WR

or RD t

Address valid to WR or RD t

WR

or RD high to ALE high t

Data valid to WR

transition t

Data setup before WR t

Data hold after WR

Address float after RD

RLRH

WLWH

LLAX2

RLDV

t

RHDX

t

RHDZ

LLDV

AVDV

LLWL

AVWL

WHLH

QVWX

QVWH

t

WHQX

t

RLAZ

at 40 MHz Clock

Variable Clock

1/t

= 3.5 to 40MHz

CLCL

Unit

Min. Max. Min. Max.

120 - 6t

120 - 6t

10 - t

-75 -5t

-30 - ns

CLCL

-30 - ns

CLCL

-15 - ns

CLCL

-50 ns

CLCL

0- 0 - ns

-38 -2t

-150 -8t

-150 -9t

60 90 3t

70 - 4t

10 40 t

5-t

125 - 7t

5-t

-15 3 t

CLCL

-30 - ns

CLCL

-15 t

CLCL

-20 - ns

CLCL

-50 - ns

CLCL

-20 - ns

CLCL

-12 ns

CLCL

-50 ns

CLCL

-75 ns

CLCL

+15 ns

CLCL

+15 ns

CLCL

-0 - 0 ns

Advance Information (40MHz)

External Clock Drive

Variable Oscillator

Parameter Symbol

(Freq. = 3.5 to 40MHz)

Unit

Min. Max.

Oscillator period t

High time t

Low time t

Rise time t

Fall time t

CLCL

CHCX

CLCX

CLCH

CHCL

25 285.7 ns

10 t

10 t

CLCL

CLCL

- t

- t

CLCX

CHCX

ns

ns

-10ns

-10ns

38 Jan. 2001 Ver 1.0

Page 43

GMS90X5XC Series HYUNDAI MicroElectronics

t

LHLL

ALE

t

LLPL

t

LLIV

t

PLIV

t

PLPH

INSTR.

IN

t

PXAV

t

PXIZ

t

PXIX

A0-A7

PSEN

PORT 0

t

AVLL

t

LLAX

A0-A7

t

AZPL

t

AVIV

PORT 2

A8-A15 A8-A15

Figure 6. External Program Memory Read Cycle

Jan. 2001 Ver 1.0 39

Page 44

HYUNDAI MicroElectronics GMS90X5XC Series

ALE

t

LHLL

PSEN

t

LLWL

RD

t

AVLL

t

LLAX2

PORT 0

PORT 2

A0-A7 from

RI or DPL

t

AVWL

t

P2.0-P2.7 or A8-A15 from DPH

Figure 7. External Data Memory Read Cycle

ALE

t

LHLL

t

AVDV

LLDV

t

t

RLAZ

RLDV

t

RLRH

t

WHLH

t

RHDZ

t

RHDX

DATA IN A0-A7 from PCL INSTR. IN

A8-A15 from PCH

t

WHLH

PSEN

t

LLWL

t

WLWH

WR

t

t

LLAX2

A0-A7 from

RI or DPL

t

AVWL

QVWX

P2.0-P2.7 or A8-A15 from DPH

t

QVWH

DATA OUT

t

WHQX

A0-A7 from PCL

A8-A15 from PCH

INSTR. IN

PORT 0

PORT 2

t

AVLL

Figure 8. External Data Memory Write Cycle

40 Jan. 2001 Ver 1.0

Page 45

GMS90X5XC Series HYUNDAI MicroElectronics

V

0.5V

−

CC

0.45V

0.2VCC + 0.9

Test Points

0.2V

− 0.1

CC

AC Inputs during testing are driven at V

Timing measurements are made a V

−

0.5V for a logic ‘1’ and 0.45V for a logic ‘0’.

CC

for a logic ‘1’ and V

IHmin

for a logic ‘0’.

ILmax

Figure 9. AC Testing: Input, Output Waveforms

V

0.1

−

OH

+ 0.1

V

OL

V

LOAD

V

V

LOAD

LOAD

+ 0.1

− 0.1

Timing Reference Points

0.2VCC − 0.1

For timing purposes a port pin is no longer floating when a 100mV change from load voltage

occurs and begins to float when a 100mV change from the loaded VOH / VOL level occurs.

IOL / IOH ≥ 20mA.

Figure 10. Float Waveforms

t

t

CLCH

CLCL

t

CLCX

V

0.5V

−

CC

0.45V

0.7 V

0.2 V

CC

CC

0.1

−

t

CHCX

t

CHCL

Figure 11. External Clock Cycle

Jan. 2001 Ver 1.0 41

Page 46

HYUNDAI MicroElectronics GMS90X5XC Series

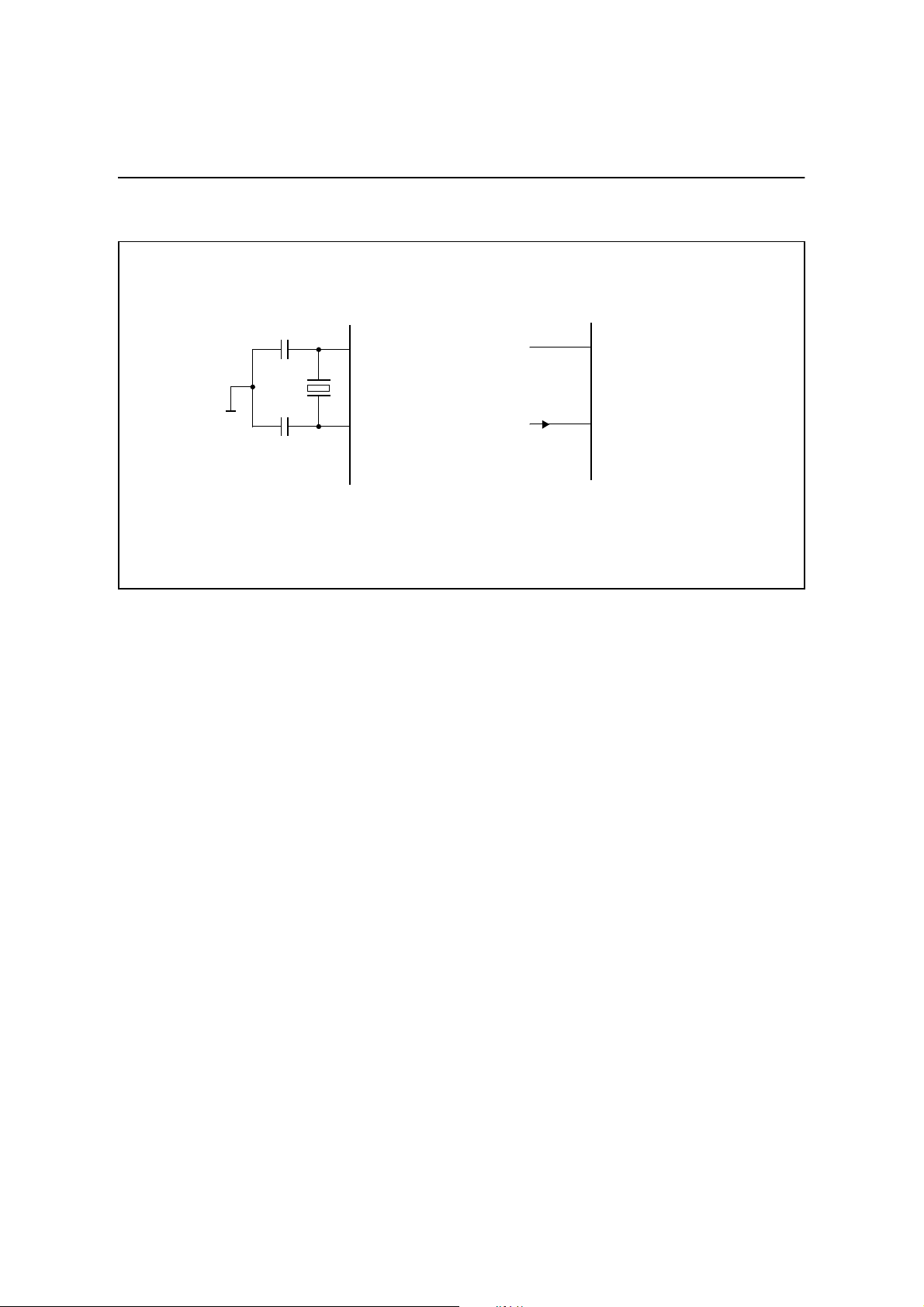

OSCILLATOR CIRCUIT

CRYSTAL OSCILLATOR MODE DRIVING FROM EXTERNAL SOURCE

C2

C1

XTAL2

P-LCC-44/Pin 20

P-DIP-40/Pin 18

M-QFP-44/Pin 14

XTAL1

P-LCC-44/Pin 21

P-DIP-40/Pin 19

M-QFP-44/Pin 15

N.C.

External Oscillator

Signal

XTAL2

P-LCC-44/Pin 20

P-DIP-40/Pin 18

M-QFP-44/Pin 14

XTAL1

P-LCC-44/Pin 21

P-DIP-40/Pin 19

M-QFP-44/Pin 15

C1, C2 = 30pF ±10pF for Crystals

For Ceramic Resonators, contact resonator manufacturer.

Figure 12. Recommended Oscillator Circuits

Oscillation circuit is designed to be used either with a ceramic resonator or crystal oscillator. Since each crystal

and ceramic resonator have their own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

42 Jan. 2001 Ver 1.0

Page 47

GMS90X5XC Series HYUNDAI MicroElectronics

Plastic Package P-LCC-44

(Plastic Leaded Chip-Carrier)

44PLCC

UNIT: INCH

0.695

0.685

0.021

0.013

min. 0.020

0.630

0.590

0.656

0.650

0.032

0.026

0.656

0.650

0.695

0.685

0.050 BSC

0.012

0.0075

0.120

0.090

0.180

0.165

Jan. 2001 Ver 1.0 43

Page 48

HYUNDAI MicroElectronics GMS90X5XC Series

Plastic Package P-DIP-40

(Plastic Dual in-Line Package)

40DIP

UNIT: INCH

2.075

2.045

0.600 BSC

0.550

0-15

0.530

12

0

.

0

8

0

.0

°

0

0.200 max.

0.022

0.015

0.065

0.045

0.100 BSC

min. 0.015

0.140

0.120

44 Jan. 2001 Ver 1.0

Page 49

GMS90X5XC Series HYUNDAI MicroElectronics

Plastic Package P-MPQF-44

(Plastic Metric Quad Flat Package)

44MQFP

13.45

12.95

2.10

1.95

UNIT: MM

0-7

°

3

3

2

1

.

.

0

0

10.10

9.90

9.90

10.10

13.45

12.95

SEE DETAIL "A"

2.35 max.

0.45

0.30

0.80 BSC

0.25

0.10

DETAIL "A"

1.60

REF

1.03

0.73

Jan. 2001 Ver 1.0 45

Page 50

HYUNDAI MicroElectronics GMS90X5XC Series

46 Jan. 2001 Ver 1.0

Page 51

MASK ORDER & VERIFICATION SHEET

GMS90X5XC-GC

Customer should write inside thick line box.

1. Customer Information

2. Device Information

Company Name

Application

YYYY MM DD

Order Date

Tel:

Fax:

Name &

Signature:

3. Marking Specification

40PD IP or 44PLC C 44M Q FP

HME

C

GMS90 -GC

5

➀➁

Y YWW K OR EA

SIEMENS ’92

ROM size

4K

8K

16K

ROM Protection

File Name: ( .HEX)

Check Sum:

Mask Data

HME

C

5

90 -G C

➀➁

YYW W KO REA

SIEMENS ’92

Package

44MQFP

44PLCC

40PDIP

Without

Vol. / Freq.

12MHz

5V

3V

Normal Super

(Please check mark into )

➀

C: 5V

L: 3V

24MHz

40MHz

12MHz

16MHz

HitelChollianInternet

ROM size

➁

1: 4K

2: 8K

4: 16K

Customer’s part num ber

4. Delivery Schedule

Customer Sample

Risk Order

YYYY MM DD

YYYY MM DD

5. ROM Code Verification

Ve rifica tio n Date:

YYYY MM DD

P lea se co n firm ou r ve rific atio n d ata .

Check Sum:

Tel:

Fax:

Name &

Signature:

Date

Quantity

HME Confirmation

pcs

pcs

This box is written after “5.Verification”.

YYYY MM DD

Approval Date:

I ag re e w ith y ou r ve rifica tio n da ta a n d c on fir m y o u to

make mask set.

Tel:

Fax:

Name &

Signature:

HYUNDAI MicroElectronics

Loading...

Loading...