1

2

3

4

5

6

7

8

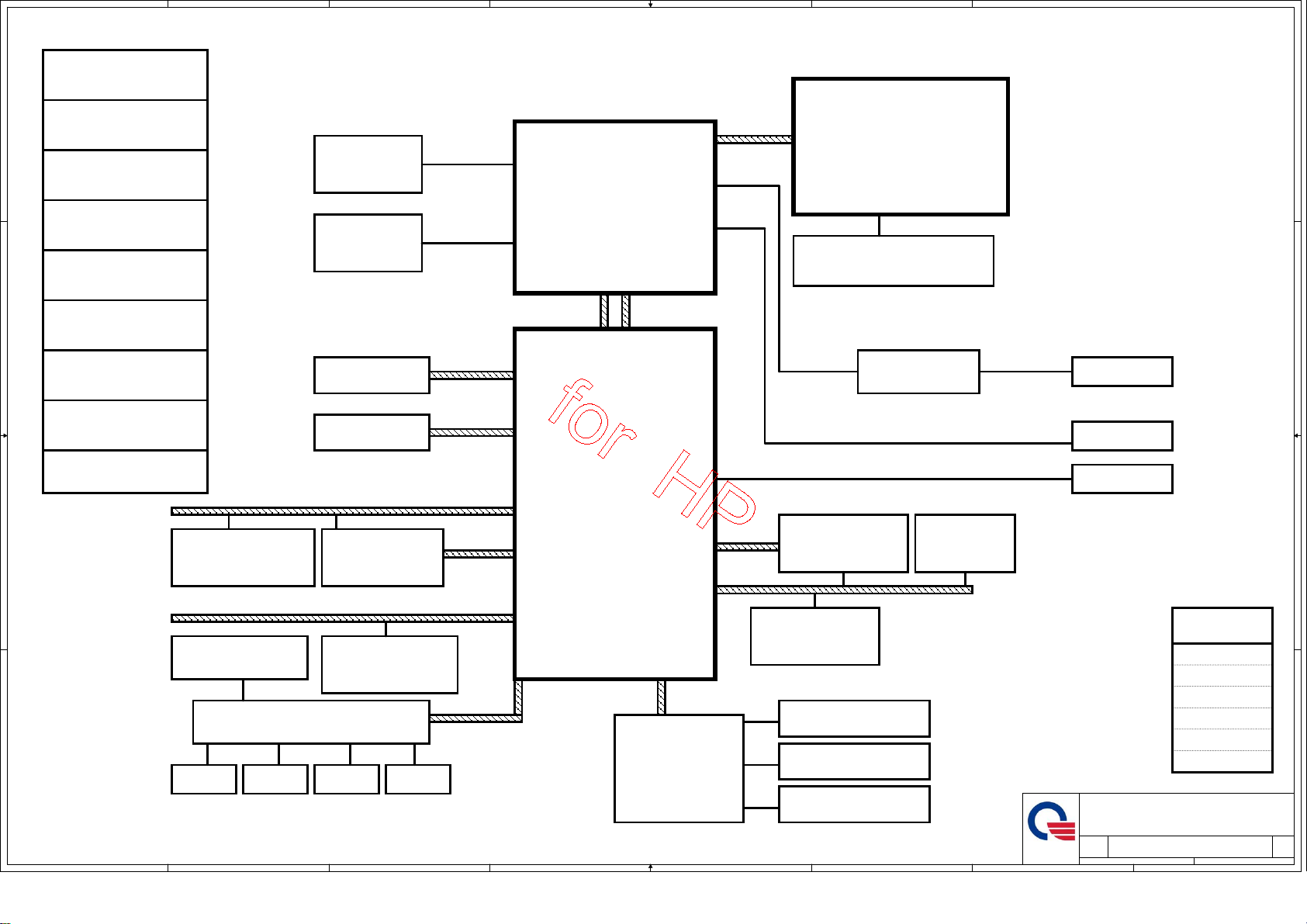

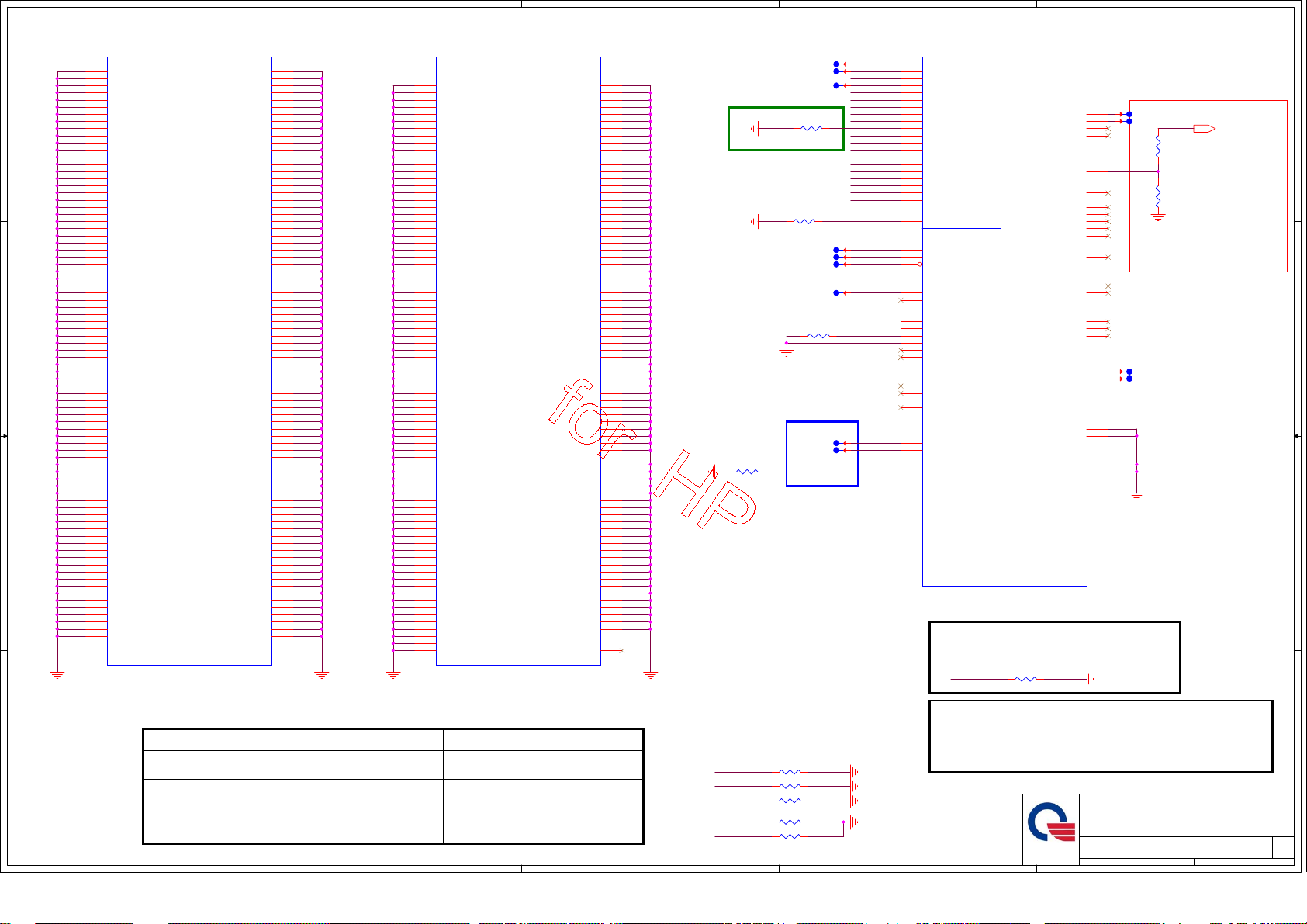

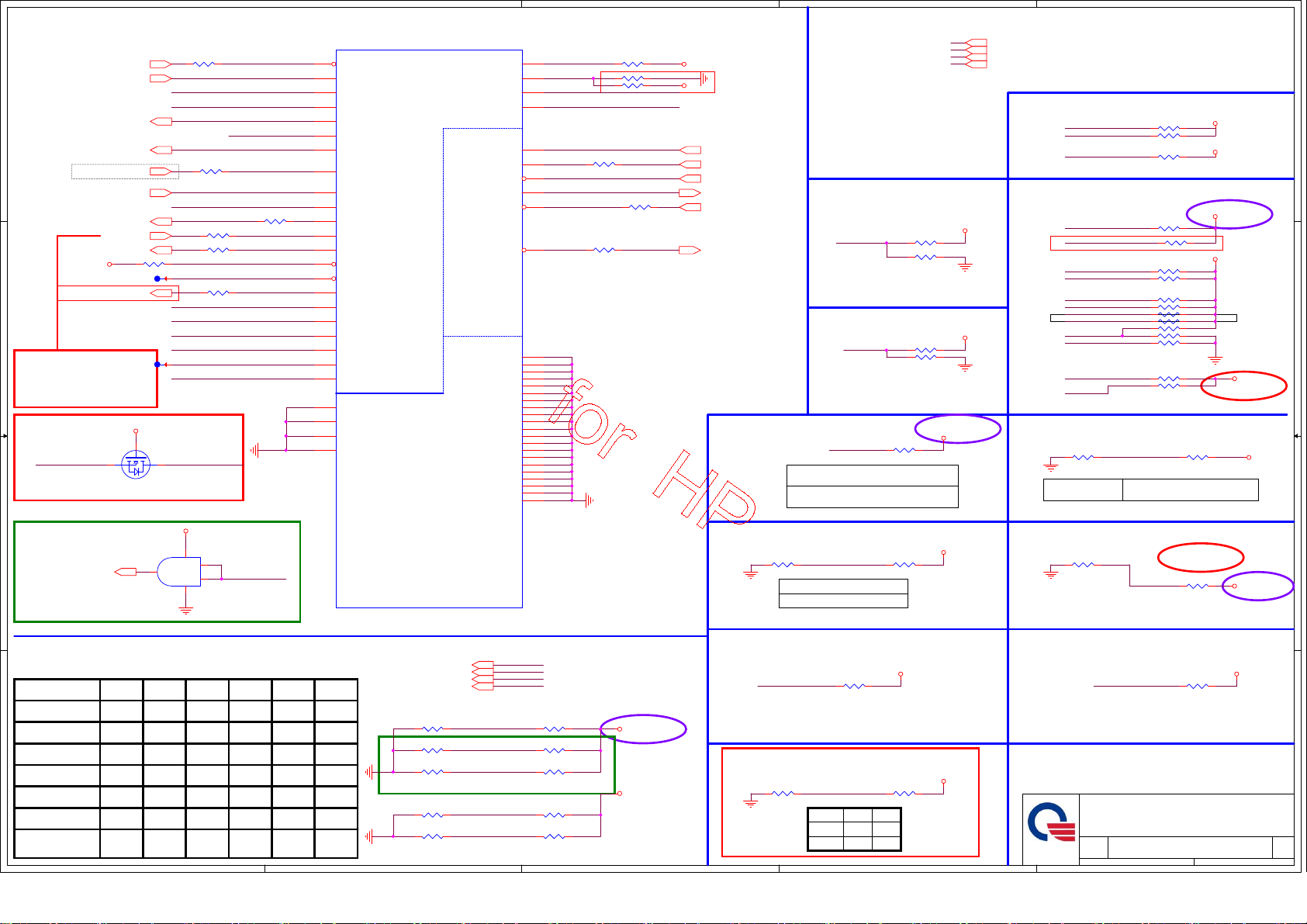

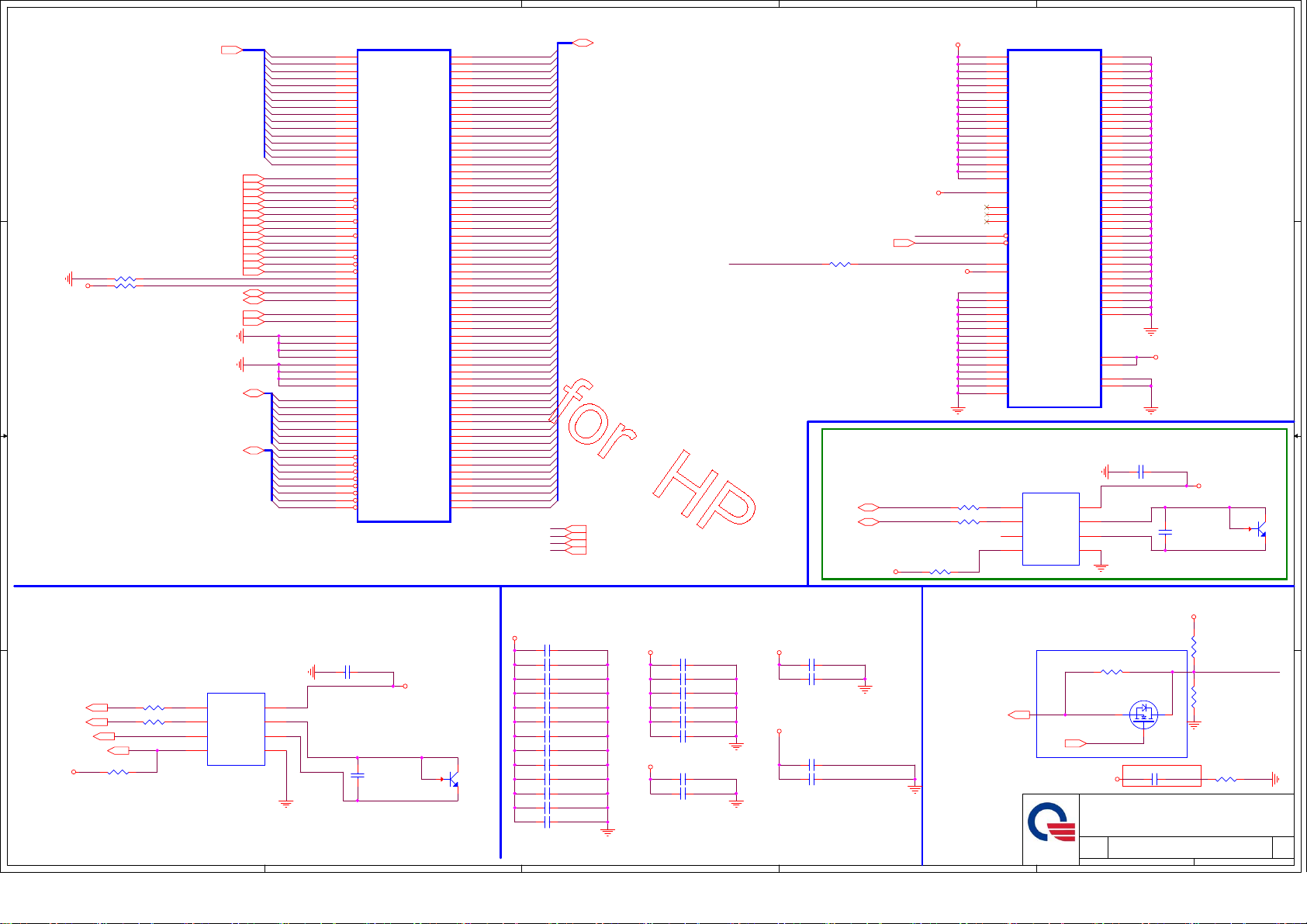

R63 INTEL SYSTEM DIAGRAM

+3V/+5V S5

PG.36

A A

B B

+1.05V

PG.37

CPU Core

PG.40~41

DDR3L

PG.38

Charge

PG.35

Dis-Charge

PG.39

+VGACORE

PG.42

+1.5 VGA

PG.43

+1.0V/+1.8/ +3 VGA

PG.44

SODIMM1

ax. 4GB

M

PG.12

SODIMM2

Max. 4GB

PG.13

HDD

ODD

PG.33

PG.33

1600MT/s

DDR3 L

Channel A

1600MT/s

DDR3 L

C

hannel B

SATA0

SATA1

INTEL

Haswell

Processor : Daul / Quad Core

Power : 37 / 47 (Watt)

Package : rPGA947

Size : 37.5 x 37.5 (mm)

PG.2~5

FDI

DMI

INTEL PCH

Lynx Point

PCI-E x8

eDP (5.4Gb/s)

DDI (5.4Gb/s)

DP Port B

CRT

AMD

M

ars / SUN XT

29mm X 29mm

TDP 35W / 25W

PG.14~20

DDR3 900MHz

VRAM

128Mx16x8,128bit

eDP

RTD 2136 S/R

DP to LVDS Converter

PG.21~22

PAGE 23

LVDS Interface

PG.25

PG.26

PG.25

LVDS

HDMI

CRT

01

PCI-E x 1

LANE2 LANE1

C C

LAN

RTL8166EH

10/100

G.30

WLAN

BT COMBO

PG.34P

USB 2.0

PORT10

PCI-E x 1

LANE3

Accelerometer

PG.34

SMBUS

EnE KB3940QF A1

D D

TPKB

PG.32PG.32 PG.32PG.31

1

2

Card Reader

RTS5237

KBC

PG.31

FA

3

PG.27

LPC

NROM

Power : 3.5 Watt

Package : FCBGA695

Size : 20 x 20 (mm)

PG.6~11

AUDIO

CODEC

ALC 3227

4

USB 3.0

USB3.0 Ports

USB 2.0

USB2.0 Ports

PG.28

5

X2

PG.29

PORT1,2

PORT0,1

PG.29

Speaker

HP/MIC

Analog MIC

Webcam

PG.28

PG.29

PG.29

6

PG.25

PORT4

Stackup

PROJECT : R63

PROJECT : R63

PROJECT : R63

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

7

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

TOP

GND

1

IN

IN2

VCC

BOT

1 44Friday, December 21, 2012

1 44Friday, December 21, 2012

1 44Friday, December 21, 2012

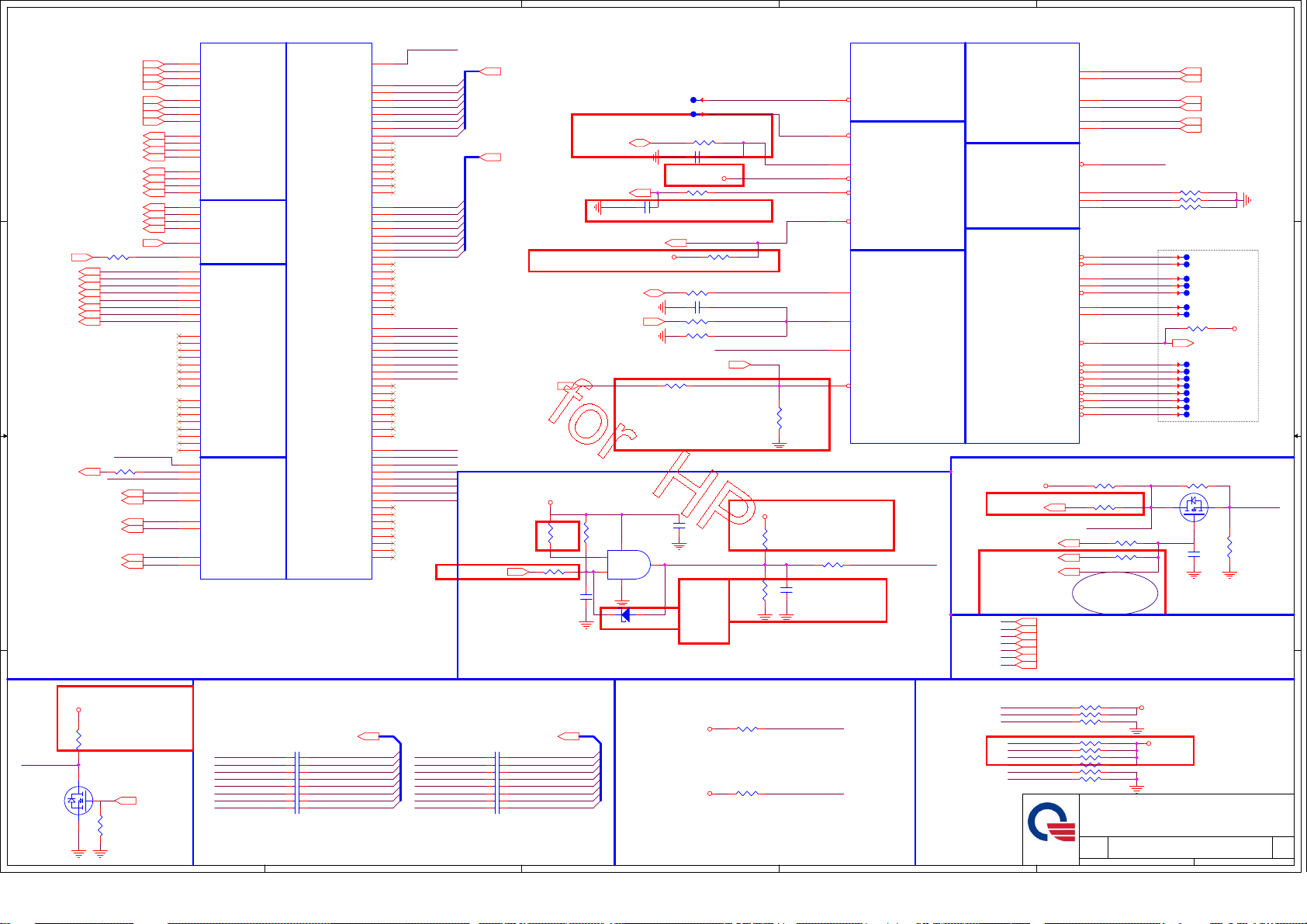

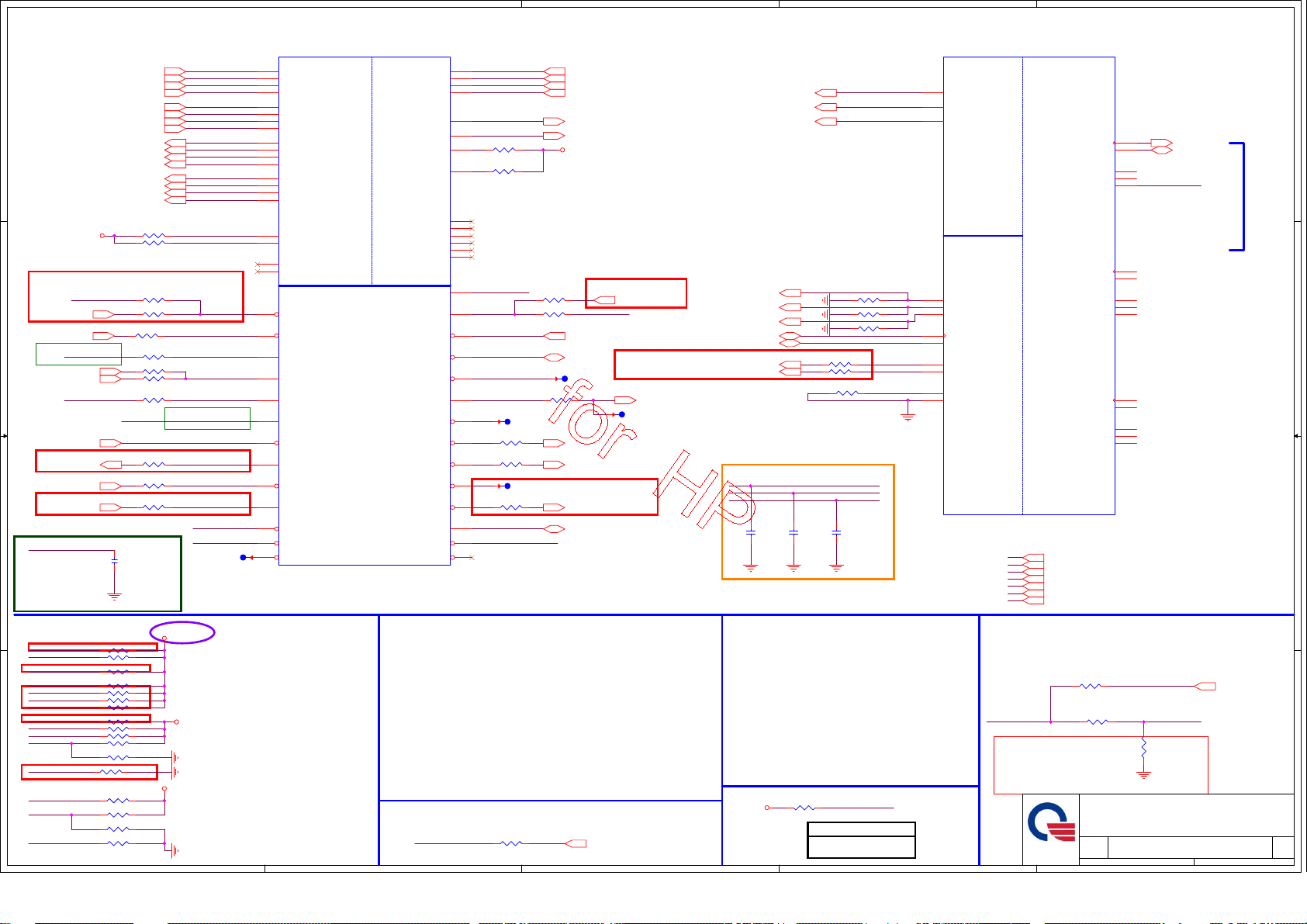

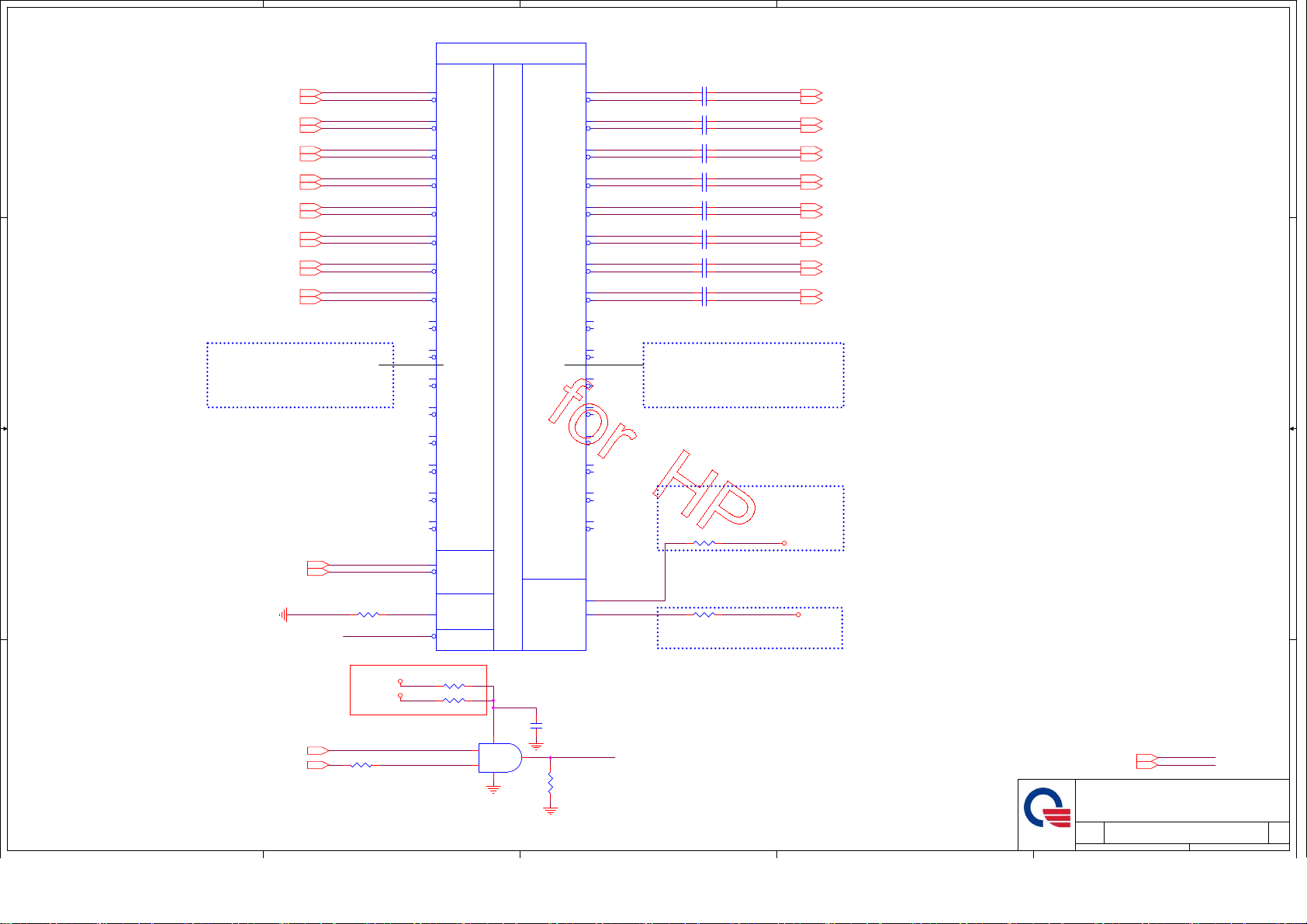

8

1A

1A

1A

5

4

3

2

1

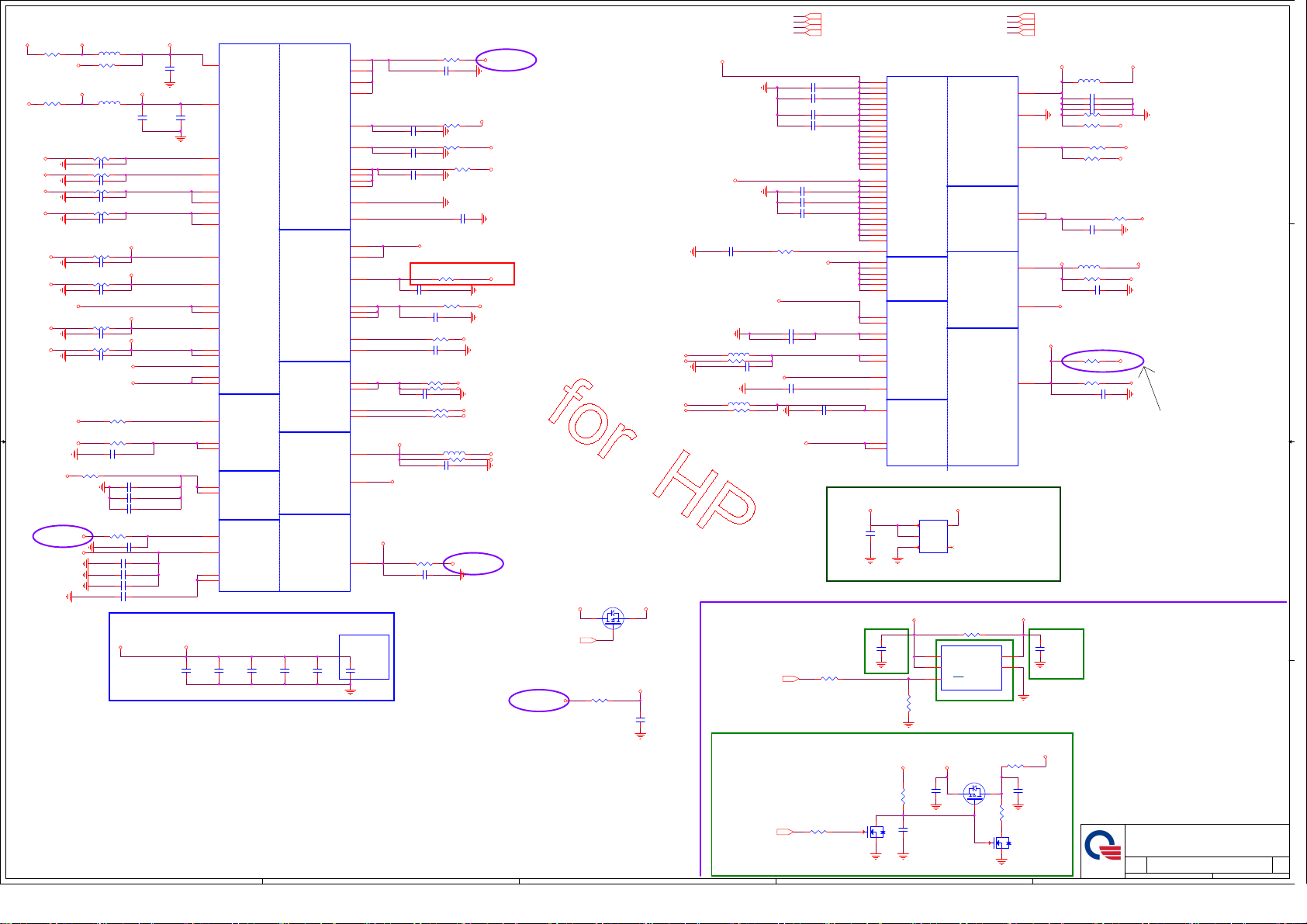

Haswell Processor (DMI,PEG,FDI) Haswell Processor (CLK,MISC,JTAG)

U24A

FDI_CSYNC_R

EDP_AUXP

EDP_AUXN

EDP_TXP0

EDP_TXP1

EDP_TXN0

EDP_TXN1

EDP_HPD 24,25

D21

DMI_RX#[0]

C21

DMI_RX#[1]

B21

DMI_RX#[2]

A21

DMI_RX#[3]

D20

DMI_RX[0]

C20

DMI_RX[1]

B20

DMI_RX[2]

A20

DMI_RX[3]

D18

DMI_TX#[0]

C17

DMI_TX#[1]

B17

DMI_TX#[2]

A17

DMI_TX#[3]

D17

DMI_TX[0]

C18

DMI_TX[1]

B18

DMI_TX[2]

A18

DMI_TX[3]

P33

FDI_TX#[0]

N32

FDI_TX#[1]

R33

FDI_TX[0]

P32

FDI_TX[1]

J29

FDI_INT

H29

FDI_CSYNC

T28

DDIB_TX#[0]

T30

DDIB_TX#[1]

U29

DDIB_TX#[2]

U31

DDIB_TX#[3]

U28

DDIB_TX[0]

U30

DDIB_TX[1]

V29

DDIB_TX[2]

V31

DDIB_TX[3]

T34

DDIC_TX#[0]

U35

DDIC_TX#[1]

U32

DDIC_TX#[2]

U33

DDIC_TX#[3]

U34

DDIC_TX[0]

V35

DDIC_TX[1]

T32

DDIC_TX[2]

V33

DDIC_TX[3]

P29

DDID_TX#[0]

N28

DDID_TX#[1]

P31

DDID_TX#[2]

N30

DDID_TX#[3]

R29

DDID_TX[0]

P28

DDID_TX[1]

R31

DDID_TX[2]

P30

DDID_TX[3]

E24

eDP_RCOMP

R27

EDP_DISP_UTIL

P27

eDP_HPD

N27

eDP_AUX

M27

eDP_AUX#

R35

eDP_TX[0]

P34

eDP_TX[1]

P35

eDP_TX#[0]

N34

eDP_TX#[1]

HSW_RPGA_EDS_PGA

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

DMI

Intel(R) DDI FDI

eDP

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PCI EXPRESS* - GRAPHICS

PEG_RX#[9]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

PEG x8 disable (UMA only remove)

PEG_TX[0..7]14 PEG_TX#[0..7]14

C_PEG_TX0

C_PEG_TX1

C_PEG_TX2

C_PEG_TX3

C_PEG_TX4

C_PEG_TX5

C_PEG_TX6

C_PEG_TX7

C688 0.22U/10V_4

C705 0.22U/10V_4

C698 0.22U/10V_4

C708 0.22U/10V_4

C699 0.22U/10V_4

C690 0.22U/10V_4

C715 0.22U/10V_4

C730 0.22U/10V_4

0.22uF AC coupling Caps for PCIE GEN1/2/3 0.22uF AC coupling Caps for PCIE GEN1/2/3

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

DMI_TXN06

DMI_TXN16

DMI_TXN26

DMI_TXN36

DMI_TXP06

DMI_TXP16

D D

FDI_CSYNC6

IN_D2#26

IN_D1#26

IN_D0#26

IN_CLK#26

IN_D226

IN_D126

IN_D026

C C

B B

A A

IN_CLK26

FDI_CSYNC & FDI_INT

Trace length < 10000 Mils

Impendance = 50 ohm

EDP_DISP_UTIL6,24,25

+VCCIO_OUT

INT_eDP_HPD_Q

Q12

ME2N7002E

DMI_TXP26

DMI_TXP36

DMI_RXN06

DMI_RXN16

DMI_RXN26

DMI_RXN36

DMI_RXP06

DMI_RXP16

DMI_RXP26

DMI_RXP36

FDI_TXN06

FDI_TXN16

FDI_TXP06

FDI_TXP16

FDI_INT6

R71 *0_4/S

DPB_LANE0_N

DPB_LANE1_N

DPB_LANE2_N

DPB_LANE3_N

DPB_LANE0_P

DPB_LANE1_P

DPB_LANE2_P

DPB_LANE3_P

eDP_RCOMP

R59 *0_4

INT_eDP_HPD_Q

EDP_AUXP24

EDP_AUXN24

EDP_TXP024

EDP_TXP124

EDP_TXN024

EDP_TXN124

4/30 CRB V1.0 -> 10K

R218

10K_4

3

2

R219

1

100K_4

5

E23

M29

K28

M31

L30

M33

L32

M35

L34

E29

D28

E31

D30

E35

D34

E33

E32

L29

L28

L31

K30

L33

K32

L35

K34

F29

E28

F31

E30

F35

E34

F33

D32

H35

H34

J33

H32

J31

G30

C33

B32

B31

A30

B29

A28

B27

A26

B25

A24

J35

G34

H33

G32

H31

H30

B33

A32

C31

B30

C29

B28

C27

B26

C25

B24

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

C_PEG_TX#0

C_PEG_TX#1

C_PEG_TX#2

C_PEG_TX#3

C_PEG_TX#4

C_PEG_TX#5

C_PEG_TX#6

C_PEG_TX#7

C_PEG_TX0

C_PEG_TX1

C_PEG_TX2

C_PEG_TX3

C_PEG_TX4

C_PEG_TX5

C_PEG_TX6

C_PEG_TX7

4

PEG_COMP

C_PEG_TX#0

C_PEG_TX#1

C_PEG_TX#2

C_PEG_TX#3

C_PEG_TX#4

C_PEG_TX#5

C_PEG_TX#6

C_PEG_TX#7

PEG_RX#[0..7] 14

H_PECI (50ohm)

Route on microstrip only

Spacing > 18 mils

Trace Length: 15 inch

HPECI Ra,Ca need placement close to EC.

PEG_RX[0..7] 14

THERMTRIP# (50ohm)

Trace Length: 1.1~12 inches

Rb need placment near PCH

4/3

0 CRB 1.0 Add

PM_SYNC (50ohm)

Trace Length: 1~11.25 inches

H_PWRGOOD (50ohm)

Trace Length: 1~11.25 inches

EC_PECI9,31

PROCHOT# (50ohm)

Trace Length <11 inches

H_PROCHOT#31,40

C38

Cb

47P/50V_4

PM_THRMTRIP#R9,31

PM_SYNC6

H_PWRGOOD9

CPU RESET#

PLTRST#8,14,27,30,31,34

CPU_PLTRST# (50ohm)

Trace Length: 10~17 inches

7/26: DB phase modify

SM_DRAMPWROK Processor Input.

+3VS5

10/22: SI modify

51216PG38

R75

100K_4

R65 *0_4/S

10/12: SI modify

PM_DRAM_PWRGD (50ohm)

e Length: 2~7 inches

Trac

C697 0.22U/10V_4

C707 0.22U/10V_4

C703 0.22U/10V_4

C714 0.22U/10V_4

C704 0.22U/10V_4

C700 0.22U/10V_4

C716 0.22U/10V_4

C733 0.22U/10V_4

0.047U/10V_4

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

C929

PM_DRAM_PWRGD_C (50ohm)

Trace Length: < 1 inches

R66

100K_4

U2

2

1

74AHC1G09GW

3 5

D15 *MEK500V-40

Ra

Ca

+VCCST

SKTOCC#

TP_CATERR#

H_PECI

H_PROCHOT#_R

TP50

TP46

R537 43_4

C770 *47P/50V_4

4/30 CRB 1.0 Add

R263 56.2/F_4

Cb need placment near VR

PM_THRMTRIP#_R

R354 *100/F_4

+1.05V

R533 *0_4/S

C729 *0.1U/10V_4

R502 *0_4/S

R503 10K_4

CPU_PLTRST#R9,31

R531 *1.5K/F_4

To change the resistor values in the DRAMPWROK logic to reduce the

leakage on VDDPWRGOOD

C44

0.1U/10V_4

4

PM_DRAM_PWRGD_C

5: SI Del

10/1

Rb

PM_SYNC_R

H_PWRGOOD_R

PM_DRAM_PWRGD_R

+1.35V_CPU

R80

1.8K/F_4

R79

3.3K_4

R532

*750/F_4

DG 498556 -> 1.8K

R78 0_4

C930

*0.047U/10V_4

DG 498556 -> 3.3K

DP & PEG Compensation

+VCCIOA_OUT

+VCCIOA_OUT

3

R138 24.9/F_4

eDP_RCOMP

Trace length < 100 Mils

Trace Width 20 Mils Trace Spacing 25 Mils

R132 24.9/F_4

PEG_RCOMP

Trace length < 400 MILS

Trace width = 12 MILS

Trace spacing = 15 MILS

eDP_RCOMP

PEG_COMP

U24B

AP32

SKTOCC#

AN32

CATERR#

AR27

PECI

AK31

FC_AK31

AM30

PROCHOT#

AM35

THERMTRIP#

AT28

PM_SYNC

AL34

UNCOREPWRGOOD

AC10

SM_DRAMPW ROK

AT26

RESET#

HSW_RPGA_EDS_PGA

PM_DRAM_PWRGD_R

PM_DRAM_PWRGD_R (50ohm)

Trace Length: 0.5~1 inches

Processor pull-up (CPU)

2

BCLK

BCLK#

SSC_DPLL_REF_CLK

MISC

THERMALPWR MANAGEMENT

DDR3_DRAMRST#_R (50ohm)

Trace Length < 6 inches

SSC_DPLL_REF_CLK#

DPLL_REF_CLK

DPLL_REF_CLK#

CLOCKS

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

DDR3

MISC

PRDY#

PREQ#

TCK

TMS

TRST#

TDI

TDO

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

+1.35VSUS

BPM#[5]

BPM#[6]

BPM#[7]

JTAG & BPM

DDR3_DRAMRST#12,13

DDR3 DRAM RESET

R471 *1K_4

R472 *0_4/S

10/18: SI modify

DRAMRST_CNTRL_PCH8

DRAMRST_CNTRL_EC31

DRAMRST_CNTRL_DDR3,12,13

FOR DS3

+VCCIO_OUT 4,40

+VCCIOA_OUT 4

+1.05V 4,9,10,11,31,34,37

+1.35V_CPU 3,4,12,13,38

+1.35VSUS 3,4,12,13,38

+3VS5 6,7,9,10,34,36,38,39,42,44

+3V 6,7,8,9,10,12,13,14,23,24,25,26,27,28,29,30,31,32,33,34,39,40,42,44

H_PROCHOT#

CLK_DPLL_SSCLKP

CLK_DPLL_SSCLKN

XDP_TDO

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TCLK

XDP_TRST#

NB5

NB5

NB5

R257 62_4

R128 *10K_4

R129 *10K_4

R234 51_4

R239 *51_4

R226 *51_4

R269 *51_4

R246 51_4

R519 51_4

Custom

Custom

Custom

Host CLK:

Trace length < 11000 MILS

Trace spacing = 15 ,20 MILS, Impendence 90 ohm

E26

CLK_CPU_BCLKP

D26

CLK_CPU_BCLKN

E27

CLK_DPLL_SSCLKP

F27

CLK_DPLL_SSCLKN

H28

CLK_DPLL_NSCCLKP

G28

CLK_DPLL_NSCCLKN

AN3

CPU_DRAMRST#

AP3

SM_RCOMP_0

AR3

SM_RCOMP_1

AP2

SM_RCOMP_2

SM_RCOMP[0] W:12mils/S:15mils/L: 500mils,

SM_RCOMP[1] W:12mils/S:15mils/L: 500mils,

SM_RCOMP[2] W:12mils/S:15mils/L: 500mils,

AR29

XDP_PRDY#

AT29

XDP_PREQ#

AM34

XDP_TCLK

AN33

XDP_TMS

AM33

XDP_TRST#

AM31

XDP_TDI_R

AL33

XDP_TDO

AP33

XDP_DBRST#

AR30

XDP_BPM0

AN31

XDP_BPM1

AN29

XDP_BPM2

AP31

XDP_BPM3

AP30

XDP_BPM4

AN28

XDP_BPM5

AP29

XDP_BPM6

AP28

XDP_BPM7

CPU_DRAMRST#_R

0529 remove

R825 pull

hi due to

EC is

output pin

R468*0_4

R467*0_4

+VCCIO_OUT

+1.05V

R250 100/F_4

R526 75/F_4

R525 100/F_4

R524 *1K_4

R785 *0_4/S

3

C628

*0.047U/10V_4

check

PROJECT : R63

PROJECT : R63

PROJECT : R63

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

SNB 1/4 (PCIE&DMI&FDI)

SNB 1/4 (PCIE&DMI&FDI)

SNB 1/4 (PCIE&DMI&FDI)

1

02

CLK_CPU_BCLKP 8

CLK_CPU_BCLKN 8

CLK_DPLL_SSCLKP 8

CLK_DPLL_SSCLKN 8

CLK_DPLL_NSCCLKP 8

CLK_DPLL_NSCCLKN 8

TP100

CPU XDP

TP57

TP42

TP41

TP94

TP36

TP39

+3V

XDP_DBRST# 6

TP101

TP53

TP59

TP99

TP95

TP56

TP97

TP58

1

CPU_DRAMRST#

Q29

2

*ME2N7002E

R464

*4.99K/F_4

2 44Friday, December 21, 2012

2 44Friday, December 21, 2012

2 44Friday, December 21, 2012

1A

1A

1A

5

4

3

2

1

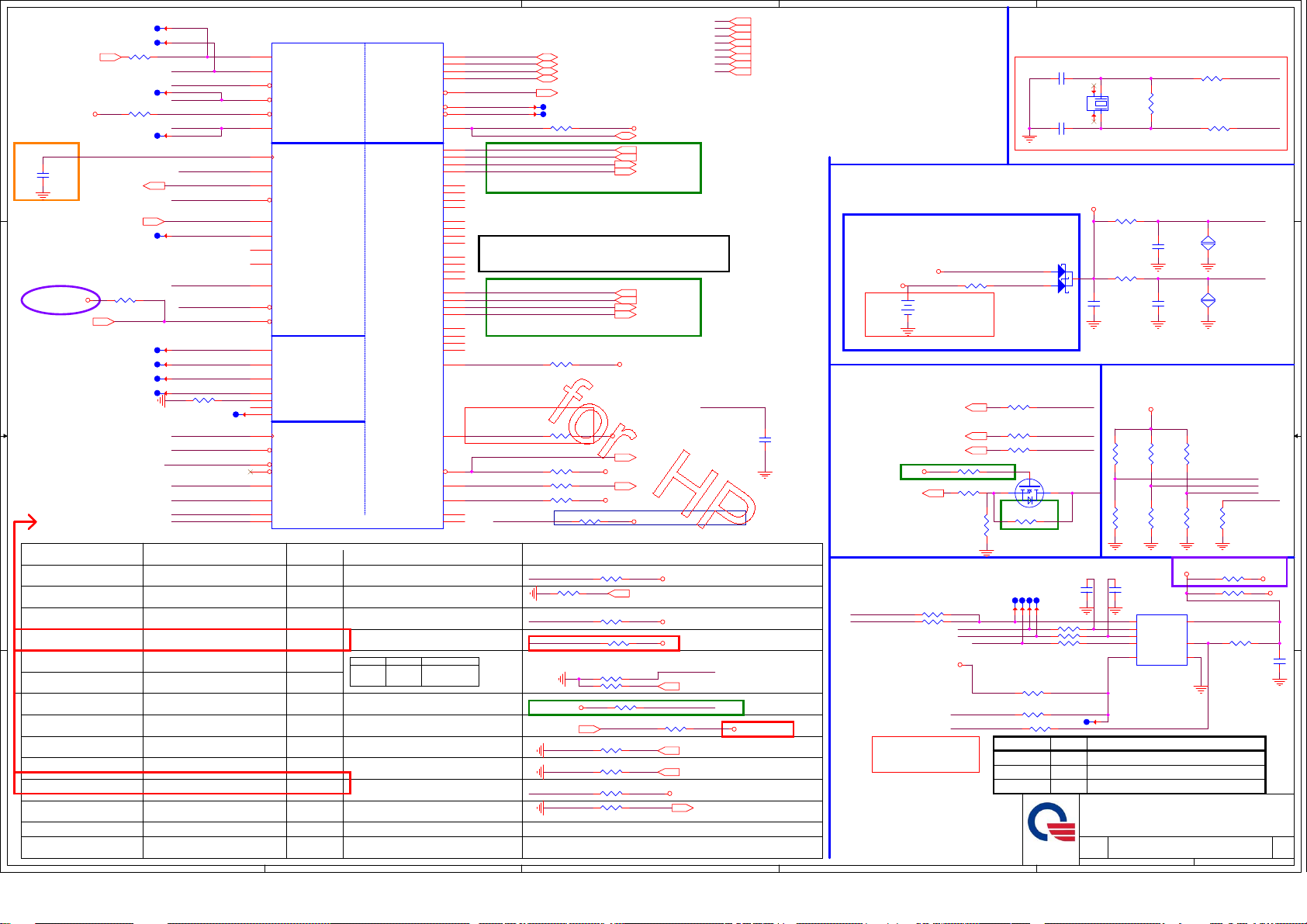

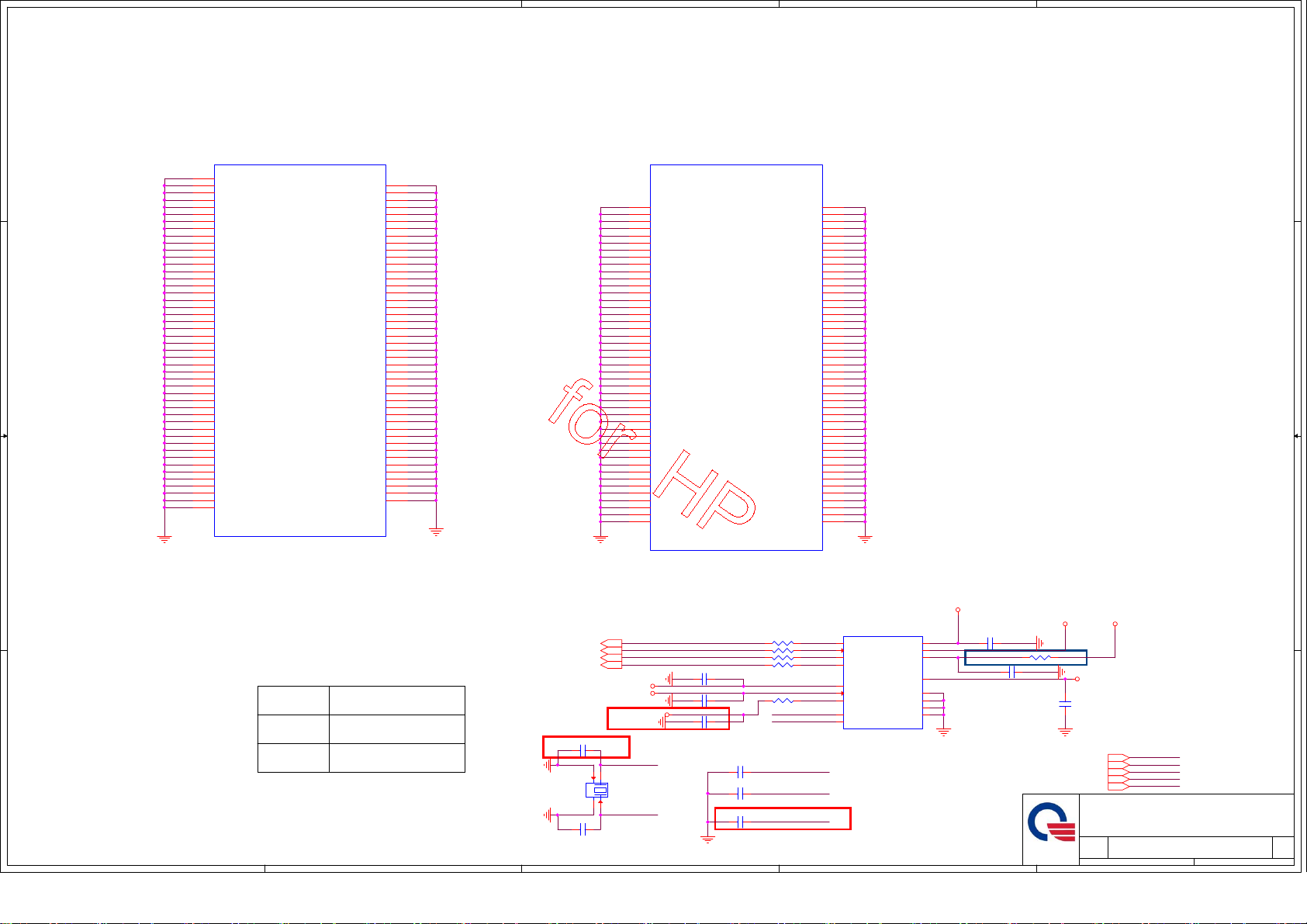

Haswell Processor (DDR3)

U24C

D D

M_A_DQ[63:0]12

C C

B B

M_A_BS#012

M_A_BS#112

M_A_BS#212

M_A_CAS#12

M_A_RAS#12

M_A_WE#12

TP16

RSVD_V10 must be grounded

CPU SM_VREF

A A

R260 *0_6/S

R285 *0_6/S

1

R282

*1K_4 R279

5

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

2

DRAMRST_CNTRL

AR15

AT14

AM14

AN14

AT15

AR14

AN15

AM15

AM9

AN9

AM8

AN8

AR9

AT9

AR8

AT8

AJ9

AK9

AJ6

AK6

AJ10

AK10

AJ7

AK7

AF4

AF5

AF1

AF2

AG4

AG5

AG1

AG2

J1

J2

J5

H5

H2

H1

J4

H4

F2

F1

D2

D3

D1

F3

C3

B3

B5

E6

A5

D6

D5

E5

B6

A6

E12

D12

B11

A11

E11

D11

B12

A12

V5

U5

AD1

U8

U6

U7

AC7

V10

3

Q16

*ME2N7002E

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

RSCD_AC7

RSCD_V10

HSW_RPGA_EDS_PGA

8/31: Intel suggestion

+VREF_CA_CPU

DRAMRST_CNTRL_DDR 2,12,13

DDR SYSTEM MEMORY A

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

+SM_VREF+SM_VREF

SA_CLK[0]

SA_CLK#[0]

SA_CKE[0]

SA_CLK[1]

SA_CLK#[1]

SA_CKE[1]

SA_CLK[2]

SA_CLK#[2]

SA_CKE[2]

SA_CLK[3]

SA_CLK#[3]

SA_CKE[3]

SA_CS#[0]

SA_CS#[1]

SA_CS#[2]

SA_CS#[3]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

SM_VREF

4

V4

U4

AD9

V3

U3

AC9

V2

U2

AD8

V1

U1

AC8

M7

L9

M9

M10

M8

L7

L8

L10

AP15

AP8

AJ8

AF3

J3

E2

C5

C11

AP14

AP9

AK8

AG3

H3

E3

C6

C12

V8

AC6

V9

U9

AC5

AC4

AD6

AC3

AD5

AC2

V6

AC1

AD4

V7

AD3

AD2

AM3

+SM_VREF

F16

SMDDR_VREF_DQ0_M3

F13

SMDDR_VREF_DQ1_M3

R261 *0_6

*0.1U/10V_4

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

C400

R470*1K_4

R469*1K_4

+1.35V_CPU

R278

*1K/F_4

*1K/F_4

M_A_CLKP0 12

M_A_CLKN0 12

M_A_CKE0 12

M_A_CLKP1 12

M_A_CLKN1 12

M_A_CKE1 12

M_A_CS#0 12

M_A_CS#1 12

M_A_ODT0 12

M_A_ODT1 12

M_A_DQSN[7:0] 12

M_A_DQSP[7:0] 12

M_A_A[15:0] 12

SMDDR_VREF_DQ0_M3 12

SMDDR_VREF_DQ1_M3 13

R283 *0_6

1

Q17

*ME2N7002E

2

MAIND

3

M_B_DQ[63:0]13

DDR_VTTREF 12,38

MAIND 10,39

3

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS#013

M_B_BS#113

M_B_BS#213

M_B_CAS#13

M_B_RAS#13

M_B_WE#13

TP30

RSVD_R10 must be grounded

U24D

AR18

SB_DQ[0]

AT18

SB_DQ[1]

AM17

SB_DQ[2]

AM18

SB_DQ[3]

AR17

SB_DQ[4]

AT17

SB_DQ[5]

AN17

SB_DQ[6]

AN18

SB_DQ[7]

AT12

SB_DQ[8]

AR12

SB_DQ[9]

AN12

SB_DQ[10]

AM11

SB_DQ[11]

AT11

SB_DQ[12]

AR11

SB_DQ[13]

AM12

SB_DQ[14]

AN11

SB_DQ[15]

AR5

SB_DQ[16]

AR6

SB_DQ[17]

AM5

SB_DQ[18]

AM6

SB_DQ[19]

AT5

SB_DQ[20]

AT6

SB_DQ[21]

AN5

SB_DQ[22]

AN6

SB_DQ[23]

AJ4

SB_DQ[24]

AK4

SB_DQ[25]

AJ1

SB_DQ[26]

AJ2

SB_DQ[27]

AM1

SB_DQ[28]

AN1

SB_DQ[29]

AK2

SB_DQ[30]

AK1

SB_DQ[31]

L2

SB_DQ[32]

M2

SB_DQ[33]

L4

SB_DQ[34]

M4

SB_DQ[35]

L1

SB_DQ[36]

M1

SB_DQ[37]

L5

SB_DQ[38]

M5

SB_DQ[39]

G7

SB_DQ[40]

J8

SB_DQ[41]

G8

SB_DQ[42]

G9

SB_DQ[43]

J7

SB_DQ[44]

J9

SB_DQ[45]

G10

SB_DQ[46]

J10

SB_DQ[47]

A8

SB_DQ[48]

B8

SB_DQ[49]

A9

SB_DQ[50]

B9

SB_DQ[51]

D8

SB_DQ[52]

E8

SB_DQ[53]

D9

SB_DQ[54]

E9

SB_DQ[55]

E15

SB_DQ[56]

D15

SB_DQ[57]

A15

SB_DQ[58]

B15

SB_DQ[59]

E14

SB_DQ[60]

D14

SB_DQ[61]

A14

SB_DQ[62]

B14

SB_DQ[63]

R7

SB_BS[0]

P8

SB_BS[1]

AA9

SB_BS[2]

P7

SB_CAS#

R6

SB_RAS#

P6

SB_WE#

AG8

RSVD_AG8

R10

RSVD_R10

HSW_RPGA_EDS_PGA

SB_CLK[0]

SB_CLK#[0]

SB_CKE[0]

SB_CLK[1]

SB_CLK#[1]

SB_CKE[1]

SB_CLK[2]

SB_CLK#[2]

SB_CKE[2]

SB_CLK[3]

SB_CLK#[3]

SB_CKE[3]

SB_CS#[0]

SB_CS#[1]

SB_CS#[2]

SB_CS#[3]

SB_ODT[0]

SB_ODT[1]

SB_ODT[2]

SB_ODT[3]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY B

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

+1.35V_CPU 2,4,12,13,38

+VREF_CA_CPU 12

2

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

AA4

Y4

AF10

AA3

Y3

AG10

AA2

Y2

AG9

AA1

Y1

AF9

P4

R2

P3

P1

R4

R3

R1

P2

AP18

AP11

AP5

AJ3

L3

H9

C8

C14

AP17

AP12

AP6

AK3

M3

H8

C9

C15

R8

Y5

Y10

AA5

Y7

AA6

Y6

AA7

Y8

AA10

R9

Y9

AF7

P9

AA8

AG7

M_B_CLKP0 13

M_B_CLKN0 13

M_B_CKE0 13

M_B_CLKP1 13

M_B_CLKN1 13

M_B_CKE1 13

M_B_CS#0 13

M_B_CS#1 13

M_B_ODT0 13

M_B_ODT1 13

M_B_DQSN0

M_B_DQSN1

M_B_DQSN2

M_B_DQSN3

M_B_DQSN4

M_B_DQSN5

M_B_DQSN6

M_B_DQSN7

M_B_DQSP0

M_B_DQSP1

M_B_DQSP2

M_B_DQSP3

M_B_DQSP4

M_B_DQSP5

M_B_DQSP6

M_B_DQSP7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

NB5

NB5

NB5

M_B_DQSN[7:0] 13

M_B_DQSP[7:0] 13

M_B_A[15:0] 13

PROJECT : R63

PROJECT : R63

PROJECT : R63

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

SNB 2/4 (DDR3 I/F)

SNB 2/4 (DDR3 I/F)

SNB 2/4 (DDR3 I/F)

1

03

3 44Friday, December 21, 2012

3 44Friday, December 21, 2012

3 44Friday, December 21, 2012

1A

1A

1A

5

4

3

2

1

Haswell Processor (POWER)

IN 95A

+VCC_CORE

D D

C C

B B

C650

22U/6.3VS_8

C286

22U/6.3VS_8

C651

22U/6.3VS_8

C644

22U/6.3VS_8

C695

22U/6.3VS_8

C667

22U/6.3VS_8

C271

22U/6.3VS_8

C666

*22U/6.3VS_8

C682

22U/6.3VS_8

C649

10U/6.3V_8

C709

22U/6.3VS_8

C711

22U/6.3VS_8

C194

22U/6.3VS_8

C285

22U/6.3VS_8

C710

22U/6.3VS_8

C158

22U/6.3VS_8

C196

22U/6.3VS_8

C195

*22U/6.3VS_8

C159

22U/6.3VS_8

C694

10U/6.3V_8

VCC Output Decoupling Recommendations

470uFx4 7343

22uFx8

22uFx11

10uFx11

A A

TOP socket side

4 on TOP, 4 on BOT near socket edge

0805

0805

TOP, inside socket cavity

0805

BOT, inside socket cavity

5

C668

22U/6.3VS_8

C284

22U/6.3VS_8

C270

22U/6.3VS_8

C646

22U/6.3VS_8

C713

22U/6.3VS_8

C269

22U/6.3VS_8

C683

22U/6.3VS_8

C645

22U/6.3VS_8

C681

10U/6.3V_8

C712

10U/6.3V_8

U24F

AA26

VCC1

AA28

VCC2

AA34

VCC3

AA30

VCC4

AA32

VCC5

AB26

VCC6

AB29

VCC7

AB25

VCC8

AB27

VCC9

AB28

VCC10

AB30

VCC11

AB31

VCC12

AB33

VCC13

AB34

VCC14

AB32

VCC15

AC26

VCC16

AB35

VCC17

AC28

VCC18

AD25

VCC19

AC30

VCC20

AD28

VCC21

AC32

VCC22

AD31

VCC23

AC34

VCC24

AD34

VCC25

AD26

VCC26

AD27

VCC27

AD29

VCC28

AD30

VCC29

AD32

VCC30

AD33

VCC31

AD35

VCC32

AE26

VCC33

AE32

VCC34

AE28

VCC35

AE30

VCC36

AG28

VCC37

AG34

VCC38

AE34

VCC39

AF25

VCC40

AF26

VCC41

AF27

VCC42

AF28

VCC43

AF29

VCC44

AF30

VCC45

AF31

VCC46

AF32

VCC47

AF33

VCC48

AF34

VCC49

AF35

VCC50

AG26

VCC51

AH26

VCC52

AH29

VCC53

AG30

VCC54

AG32

VCC55

AH32

VCC56

AH35

VCC57

AH25

VCC58

AH27

VCC59

AH28

VCC60

AH30

VCC61

AH31

VCC62

AH33

VCC63

AH34

VCC64

AJ25

VCC65

AJ26

VCC66

AJ27

VCC67

AJ28

VCC68

AJ29

VCC69

AJ30

VCC70

AJ31

VCC71

AJ32

VCC72

AJ33

VCC73

AJ34

VCC74

AJ35

VCC75

G25

VCC76

H25

VCC77

J25

VCC78

K25

VCC79

L25

VCC80

M25

VCC81

N25

VCC82

P25

VCC83

R25

VCC84

T25

VCC85

U25

VCC86

U26

VCC87

V25

VCC88

V26

VCC89

W26

VCC90

W27

VCC91

Y25

VCC92

Y26

VCC93

Y27

VCC94

Y28

VCC95

Y29

VCC96

Y30

VCC97

Y31

VCC98

Y32

VCC99

Y33

VCC100

Y34

VCC101

Y35

VCC102

K26

VCC103

F25

VCC104

HSW_RPGA_EDS_PGA

POWER

PEG AND DDR

CORE SUPPLY

SENSE LINES SVID

4

AB11

VDDQ1

AB2

VDDQ2

AB5

VDDQ3

AB8

VDDQ4

AE11

VDDQ5

AE2

VDDQ6

AE5

VDDQ7

AE8

VDDQ8

AH11

VDDQ9

K11

VDDQ10

N11

VDDQ11

N8

VDDQ12

T11

VDDQ13

T2

VDDQ14

T5

VDDQ15

T8

VDDQ16

W11

VDDQ17

W2

VDDQ18

W5

VDDQ19

W8

VDDQ20

K27

RSVD

L27

RSVD

T27

RSVD

V27

RSVD

N26

RSVD

AL27

RSVD

AK27

RSVD

E17

RSVD

W32

RSVD

AL16

RSVD

AL13

RSVD

J27

RSVD

AN35

VCCIO_OUT

VCCIO2PCH

VCOMP_OUT

VSS_AP35

VIDALERT#

VIDSCLK

VIDSOUT

PWR_DEBUG

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

VCC_SENSE

VSS_SENSE

+VCCIO_OUT_R

A23

+VCCIO_PCH_R

F22

+VCCIOA_OUT_R

AP35

AM28

H_CPU_SVIDALRT#

AM29

H_CPU_SVIDCLK

AL28

H_CPU_SVIDDAT

H27

PWR_DEBUG_R

AP34

VSS

AT34

VSS

AL22

VSS

AT33

VSS

AM21

VSS

AM25

VSS

AM22

VSS

AM20

VSS

AM24

VSS

AL19

VSS

AM23

VSS

AT32

VSS

AT35

AR35

AR32

AL26

R223 100_4

AL35

AK35

R222 100_4

Sense resistor should be placed within 2

inches (50.8 mm) of the processor socket

Trace Impendence 50 ohm

+1.35V_CPU 4.2A+VCC

C648

22U/6.3VS_8

C273

22U/6.3VS_8

C642

22U/6.3VS_8

C693

22U/6.3VS_8

C665

10U/6.3V_8

C197

10U/6.3V_8

C679

10U/6.3V_8

VCC_SENSE 40

VSS_SENSE 40

C161

22U/6.3VS_8

C198

22U/6.3VS_8

C160

22U/6.3VS_8

C221

22U/6.3VS_8

C691

10U/6.3V_8

C680

10U/6.3V_8

C664

10U/6.3V_8

R610_4

R5180_4

+VCC_CORE

+1.35V_CPU

C647

22U/6.3VS_8

C643

22U/6.3VS_8

C692

22U/6.3VS_8

C274

10U/6.3V_8

C272

10U/6.3V_8

C243

10U/6.3V_8

C162

10U/6.3V_8

R513*0_1206/S

R466*0/F_1206

R87*0_1206/S

TP1

Layout note: It is recommended to shield VIDSOUT signal by

routing it in between the VIDSCLK and VIDALERT# signals.

Place PU resistor

close to CPU

Place PU resistor close to CPU

The VIDALERT# signal must have a damping resistor to prevent

overshoot

3

VDDQ Output Decoupling Recommendations

BOT socket side

5 onTOP, 6 on BOT inside socket cavity

0805

5 onTOP, 5 on BOT inside socket cavity0805

A

300m

300

mA

4/30: DG 498550

Haswell PWR_DEBUG requires a 150-Ohm pull-up resistor to PCH 1.05-V VCC

Cor

7/26: DB sch modify, Del R23

R253

130/F_4

C337 0.1U/10V_4

R247 75/F_4

R248 43_4

+

+VCCIO_OUT

+VCCIO_PCH

+VCCIOA_OUT

H_CPU_SVIDCLK

H_CPU_SVIDDAT

+VCCIO_OUT

H_CPU_SVIDALRT#

330uFx2 7343

22uFx11

10uFx10

C231

*330U/2V_7343

+VCCIO_OUT

e when routed to XDP

Place PU resistor

close to VR

DG V0.7 -> 110 Ohm

SCH V0.7 -> 130 Ohm

DG V0.7 -> 44 Ohm

SCH

0: CRB 1.0 add

4/3

R256 *0_8

SVID CLK

VR_SVID_CLK 40

SVID DATA

VR_SVID_DATA 40

SVID ALERT

V0.7 -> 43 Ohm

VR_SVID_ALERT# 40

2

+3VPCU

R774

16.5K/F_4

R776

+VCCST+1.05V

C392

*22U/6.3VS_8

C381

*22U/6.3VS_8

Power Test Propose

+1.05V +VCCIO_OUT+1.05V

R60

150/F_4

PWR_DEBUG_R

R62

*10K_4

CPU VDDQ

+1.35V_CPU

Note: please keep plane is enough for VDDQ 4.2A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

+VCCIOA_OUT 2

+VCCIO_OUT 2,40

+VCCIO_PCH 10

+1.5V 6,7,8,10,28,34,38,44

+1.35V_CPU 2,3,12,13,38

+1.05V 2,9,10,11,31,34,37

+VCC_CORE 40,41

+VCCST 2

+1.35VSUS 2,3,12,13,38

IO Thrm Protect

For 65 degree, 1.8v limit, (SW)

THRM_MOINTOR 31

C62

0.1U/10V_4

R775

3.3K/F_4

100K_4 NTC

1 2

For

75 degree, 1.2v limit, (HW)

C54

0.1U/10V_4

1 2

R510 *0_8

R462 0_6

THRM_MOINTOR1 31

+VCCIO_PCH+1.05V

CRB 1.0 stuff

+1.35VSUS

Placement close to CPU.

C235 0.1U/10V_4

C225 *0.1U/10V_4

PROJECT : R63

PROJECT : R63

PROJECT : R63

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

SNB 3/4 (POWER)

SNB 3/4 (POWER)

SNB 3/4 (POWER)

1

04

C753

10U/6.3V_6

C631

*4.7U/6.3V_6

4 44Friday, December 21, 2012

4 44Friday, December 21, 2012

4 44Friday, December 21, 2012

P

1A

1A

1A

5

4

3

2

1

Haswell Processor (GND)

U24G

A10

VSS1

A13

VSS2

A16

VSS3

A19

VSS4

A22

VSS5

A25

VSS6

A27

D D

C C

B B

VSS7

A29

VSS8

A3

VSS9

A31

VSS10

A33

VSS11

A4

VSS12

A7

VSS13

AA11

VSS14

AA25

VSS15

AA27

VSS16

AA31

VSS17

AA29

VSS18

AB1

VSS19

AB10

VSS20

AA33

VSS21

AA35

VSS22

AB3

VSS23

AC25

VSS24

AC27

VSS25

AB4

VSS26

AB6

VSS27

AB7

VSS28

AB9

VSS29

AC11

VSS30

AD11

VSS31

AC29

VSS32

AC31

VSS33

AC33

VSS34

AC35

VSS35

AD7

VSS36

AE1

VSS37

AE10

VSS38

AE25

VSS39

AE29

VSS40

AE3

VSS41

AE27

VSS42

AE35

VSS43

AE4

VSS44

AE6

VSS45

AE7

VSS46

AE9

VSS47

AF11

VSS48

AF6

VSS49

AF8

VSS50

AG11

VSS51

AG25

VSS52

AE31

VSS53

AG31

VSS54

AE33

VSS55

AG6

VSS56

AH1

VSS57

AH10

VSS58

AH2

VSS59

AG27

VSS60

AG29

VSS61

AH3

VSS62

AG33

VSS63

AG35

VSS64

AH4

VSS65

AH5

VSS66

AH6

VSS67

AH7

VSS68

AH8

VSS69

AH9

VSS70

AJ11

VSS71

AJ5

VSS72

AK11

VSS73

AK25

VSS74

AK26

VSS75

AK28

VSS76

AK29

VSS77

AK30

VSS78

AK32

VSS79

E19

VSS80

HSW_RPGA_EDS_PGA

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AK34

AK5

AL1

AL10

AL11

AL12

AL14

AL15

AL17

AL18

AL2

AL20

AL21

AL23

E22

AL3

W9

AL4

AL5

AL6

AL7

AL8

AL9

AM10

AM13

AM16

AM19

E25

AM32

AM4

AM7

AN10

AN13

AN16

AN19

AN2

AN21

AN24

AN27

AN30

AN34

AN4

AN7

AP1

AP10

AP13

AP16

AP19

AP4

AP7

W25

Y11

AR13

AR16

AR19

AR2

AR22

AR25

AR28

AR31

AR34

AR4

AR7

AT10

AT13

AT16

AT19

AT21

AT24

AT27

AT3

AT30

AT4

AT7

B10

B13

B16

B19

B2

B22

U24H

B34

VSS161

B4

VSS162

B7

VSS163

C1

VSS164

C10

VSS165

C13

VSS166

C16

VSS167

C19

VSS168

C2

VSS169

C22

VSS170

C24

VSS171

C26

VSS172

C28

VSS173

C30

VSS174

C32

VSS175

C34

VSS176

C4

VSS177

C7

VSS178

D10

VSS179

D13

VSS180

D16

VSS181

D19

VSS182

D22

VSS183

D25

VSS184

D27

VSS185

D29

VSS186

D31

VSS187

D33

VSS188

D35

VSS189

D4

VSS190

D7

VSS191

E1

VSS192

E10

VSS193

E13

VSS194

E16

VSS195

E4

VSS196

E7

VSS197

F10

VSS198

F11

VSS199

F12

VSS200

F14

VSS201

F15

VSS202

F17

VSS203

F18

VSS204

F20

VSS205

F21

VSS206

F23

VSS207

F24

VSS208

F26

VSS209

F28

VSS210

F30

VSS211

F32

VSS212

F34

VSS213

F4

VSS214

F6

VSS215

F7

VSS216

F8

VSS217

F9

VSS218

G1

VSS219

G11

VSS220

G2

VSS221

G27

VSS222

G29

VSS223

G3

VSS224

G31

VSS225

G33

VSS226

G35

VSS227

G4

VSS228

G5

VSS229

H10

VSS230

H26

VSS231

H6

VSS232

H7

VSS233

J11

VSS286

J26

VSS287

J30

VSS288

J32

VSS289

J34

VSS290

J6

VSS291

K1

VSS292

HSW_RPGA_EDS_PGA

VSS

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

VSS293

VSS294

VSS295

VSS296

VSS297

VSS298

VSS299

VSS300

VSS301

VSS302

VSS303

VSS304

VSS305

VSS306

VSS307

VSS308

VSS309

VSS310

VSS311

VSS312

VSS313

VSS314

VSS315

VSS316

RSVD

K10

K2

K29

K3

K31

K33

K35

K4

K5

K7

K8

K9

L11

L26

L6

M11

M26

M28

M30

M32

M34

M6

N1

N10

N2

N29

N3

N31

N33

N35

N4

N5

N6

N7

N9

P11

P26

P5

R11

R26

R28

R30

R32

R34

R5

T1

T10

T29

T3

T31

T33

T35

T4

T6

T7

T9

U11

U27

V11

V28

V30

V32

V34

W1

W10

W3

W35

W4

W6

W7

AR10

J28

H11

AL24

F19

T26

AK33

12/11: Intel suggestion WW39 CPU date code can

remove

R201 49.9/F_4

Haswell Processor (RESERVED, CFG)

U24E

AT20

R28049.9/F_4

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG_RCOMP

RSVD30

RSVD38

RSVD39

TESTLO

CFG[0]

AR20

CFG[1]

AP20

CFG[2]

AP22

CFG[3]

AT22

CFG[4]

AN22

CFG[5]

AT25

CFG[6]

AN23

CFG[7]

AR24

CFG[8]

AT23

CFG[9]

AN20

CFG[10]

AP24

CFG[11]

AP26

CFG[12]

AN25

CFG[13]

AN26

CFG[14]

AP25

CFG[15]

AR21

CFG[16]

AP21

CFG[17]

AR23

CFG[18]

AP23

CFG[19]

AT31

CFG_RCOMP

AT1

RSVD_TP

AT2

RSVD_TP

AD10

RSVD_TP

A34

RSVD_TP

A35

RSVD_TP

W29

RSVD_TP

W28

RSVD_TP

G26

TESTLO_G26

W33

RSVD

AL30

RSVD

AL29

RSVD

C35

RSVD_TP

B35

RSVD_TP

AL25

RSVD_TP

W30

RSVD_TP

W31

RSVD_TP

W34

TESTLO

HSW_RPGA_EDS_PGA

CFG

RESERVED

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

FC_G6

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

C23

B23

D24

D23

G6

AR33

AM27

AM26

F5

AM2

K6

E18

U10

P10

B1

NC

A2

AR1

E21

E20

AP27

AR26

AL31

AL32

CFG[3] (PHYSICAL_DEBUG_ENABLED (DFX PRIVACY))

0 Enable; SET DFX ENABLED BIT IN DEBUG

1 , Disable;

CFG3

R272 *1K_4

TP98

TP96

TP55

R786 *1K_4

TP51

TP54

TP24

TP88

R124 49.9/F_4

For CPU debug.

TP9

TP10

05

TP87

TP86

10/12: SI modify

near the Processor pin (within ~1.5")

TP7

TP8

R131

*6.04K_4

R130

*2.67K_4

EC_PWROK 6,31

Processor Strapping

The CFG signals have a default value of '1' if not terminated on the board.

1 0

A A

CFG2

(PEG Static Lane Reversal)

CFG4

(DP Presence Strap)

CFG7

(PEG Defer Training)

5

Normal Operation Lane Reversed

Disable; No physical DP attached to eDP

PEG train immediately following

xxRESETB de assertion

4

Enable; An ext DP device is connected to eDP

PEG wait for BIOS training

CFG2

R275 *1K_4

CFG4

R271 1K_4

CFG7

R273 *1K_4

CFG5

R274 1K_4

CFG6

R270 *1K_4

3

CFG[6:5] (PCIE Port Bifurcation Straps)

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2 disabled

01: Reserved - (Device 1 function 1 disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

PROJECT : R63

PROJECT : R63

PROJECT : R63

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

SNB 4/4 (GND)

SNB 4/4 (GND)

SNB 4/4 (GND)

1

1A

1A

5 44Friday, December 21, 2012

5 44Friday, December 21, 2012

5 44Friday, December 21, 2012

1A

5

4

3

2

1

Lynx Point (DMI,FDI,PM)

U33C

TP75

AW22

DMI0RXN

AR20

DMI1RXN

AP17

DMI2RXN

AV20

DMI3RXN

AY22

DMI0RXP

AP20

DMI1RXP

AR17

DMI2RXP

AW20

DMI3RXP

BD21

DMI0TXN

BE20

DMI1TXN

BD17

DMI2TXN

BE18

DMI3TXN

BB21

DMI0TXP

BC20

DMI1TXP

BB17

DMI2TXP

BC18

DMI3TXP

BE16

DMI_IREF

AY17

DMI_IRCOMP

AW17

TP12

AV17

TP7

R6

SUSACK#

AM1

SYS_RESET#

AD7

SYS_PWROK

F10

PWROK

AB7

APWROK

H3

DRAMPWROK

J2

RSMRST#

J4

SUSWARN#/SUSPWRDNACK/GPIO30 (SUS)

(+3V

S5)

K1

PWRBTN#

E6

ACPRESENT / GPIO31(DSW)

(DSW)

K7

BATLOW# / GPIO72 (SUS)

N4

DSW (+3VS5)

RI#

AB10

TP21

LPT_PCH_M_EDS/BGA

DMI

FDI

DSWVRMEN

SUS_STAT# / GPIO61 (SUS)

SUSCLK / GPIO62 (SUS)

SLP_S5# / GPIO63 ( SUS)

System Power Management

SLP_WLAN#/ GPIO29 ( DSW )

DMI_RXN02

DMI_RXN12

DMI_RXN22

DMI_RXN32

DMI_RXP02

D D

+1.5V

DMI_RXP12

DMI_RXP22

DMI_RXP32

DMI_TXN02

DMI_TXN12

DMI_TXN22

DMI_TXN32

DMI_TXP02

DMI_TXP12

DMI_TXP22

DMI_TXP32

R672 *0_4/S

R671 7.5K/F_4

DMI_IREF

DMI_COMP

5/16 for DS3

SUSWARN#

SUSACK#EC31

C C

XDP_DBRST#2

IMVP_PWRGD6,40

SYS_PWROK

EC_PWROK5,31

EC_PWROK_R

12/17 PV modify

RSMRST#31

5/16 for DS3

SUSWARN#EC31

DNBSWON#31

5/16 for DS3 5/16 for DS3

AC_PRESENT31

B B

SYS_PWROK_R

R6510_4

R573 0_4

R612 *0_4

R634 0_4

R640 0_4

R604 0_4

R603 0_4

R565 0_4

C827

*0.1U/10V_4

R387*0_4

R6060_4

SUSACK#

XDP_DBRST#1

SYS_PWROK_R

EC_PWROK_R

APWROK_R

PM_DRAM_PWRGD

RSMRST#

SUSWARN#

DNBSWON#_R

AC_PRESENT_R

PM_BATLOW#

PM_RI#

Reserve for power on sequence

PCH Pull-high/low(CLG)

PM_DRAM_PWRGD

PM_RI#

SUS_STAT#

PCIE_WAKE#

SLP_LAN#

SUSACK#

SUSWARN#

PCIE_WAKE#

PM_BATLOW#

DNBSWON#_R

AC_PRESENT_R

A A

DPWROK

CLKRUN#

XDP_DBRST#

RSMRST#

R806 *200/F_4

R624 10K_4

R803 *10K_4

R625 *1K_4

R579 *10K_4

R605 *10K_4

R626 *10K_4

R798 1K_4

R586 8.2K_4

R660 *10K_4

R580 10K_4

R566 *100K_4

R794 100K/F_4

R633 10K_4

R590 1K_4

R614 *1K_4

R643 10K_4

5

+3V_DEEP_SUS

10/14: SI phase modify

+3VS5

10/12: SI phase modify

+3V

for DS3

INT HDMI Detect Function

4

FDI_RXN0

FDI_RXN1

FDI_RXP0

FDI_RXP1

FDI_CSYNC

FDI_INT

FDI_IREF

FDI_RCOMP

TP16

TP15

TP10

TP17

TP13

DPWROK

WAKE#

(+3V

CLKRUN#

(+3VS5)

(+3VS5)

(+3VS5)

SLP_S4#

SLP_S3#

SLP_A#

SLP_SUS#

PMSYNCH

SLP_LAN#

DPB_HPD_Q

TP5

)

AJ35

AL35

AJ36

AL36

AL39

AL40

AT45

AR44

AV43

AY45

AV45

AW44

AU42

AU44

C8

L13

K3

AN7

U7

Y6

Y7

C6

H1

F3

F1

AY3

G5

D2

DPWROK

R714 *0_4/S

R713 7.5K/F_4

DSWVREN

PCIE_WAKE#

CLKRUN#

SUS_STAT#

PCH_SUSCLK_L

TP72

R662 0_4

R607 0_4

TP71

R663 0_4

SLP_LAN#

R721 *0_4/S

R627 0_4

R661 *0_4

PCIE_WAKE# 27,30,31,34

CLKRUN# 31

R599 0_4

SUSC# 31

SUSB# 31

SLP_SUS#EC 31

FDI_TXN0 2

FDI_TXN1 2

FDI_TXP0 2

FDI_TXP1 2

FDI_CSYNC 2

FDI_INT 2

+1.5V

for DS3

RSMRST#

TP66

PM_SYNC 2

HDMI_HPD_CON 26

DPWROK_EC 31

DG V0.7 -> 33 ohm

SCH V0.7 -> 0 ohm

PCH_SUSCLK 7,31

TP107

3

LVDS_BLON25

DISP_ON25

DPST_PWM2,24,25

PD Res place close to PCH

PCH to Res routeing 37.5 ohm Impedance.

Res to connector filter routeing 50ohm Impedance.

CRT_B23

CRT_G23

CRT_R23

DDCCLK23

DDCDATA23

HSYNC_COM23

VSYNC_COM23

DAC_IREF (50ohm)

Trac

Trace spacing = 30 MILS

R430 150/F_4

R431 150/F_4

R432 150/F_4

R719 33_4

R717 33_4

R716 649/F_4

e length < 500 MILS

Reserve from EMI request

CRT_B

CRT_G

C577

C578

*5.6P/16V_4

*5.6P/16V_4

R665 330K_4

+3V_RTC

On Die DSW VR Enable

High = Enable (Default)

Low = Disable

Lynx Point ( DDI)

U33D

K36

EDP_BKLTEN

G36

EDP_VDD_EN

N36

EDP_BKLTCTL

T45

CRT_BLUE

U44

CRT_GREEN

V45

CRT_RED

M43

CRT_DDC_CLK

M45

CRT_DDC_DATA

DAC_IREF

6 DB Modify

7/2

N42

N44

U40

U39

2

CRT_HSYNC

CRT_VSYNC

DAC_IREF

CRT_IRTN

LPT_PCH_M_EDS/BGA

CRT_R

C579

*5.6P/16V_4

DSWVREN

PCH_HSYNC_R

PCH_VSYNC_R

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPB_AUXN

DDPB_AUXP

DDPB_HPD

R40

R39

H45

H43

K40

DPB_HPD_Q

SDVO_CLK 26

SDVO_DATA 26

LVDS

DDPC_HPD

DDPD_HPD

R35

R36

K43

K45

K38

N40

N38

J42

J44

H39

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPC_AUXN

DDPC_AUXP

DDPD_CTRLCLK

DDPD_CTRLDATA

DDPD_AUXN

Digital Display Interface

DDPD_AUXP

CRT

+3V_DEEP_SUS 7,8,9,10,39

+3V_RTC 7,10,11

+1.05V 2,4,9,10,11,31,34,37

+3VPCU 4,7,9,11,25,31,32,34,35,36

+3VS5 2,7,9,10,34,36,38,39,42,44

+3V 2,7,8,9,10,12,13,14,23,24,25,26,27,28,29,30,31,32,33,34,39,40,42,44

+5V 7,23,26,28,29,32,33,34,39

System PWR_OK(CLG)

7/26 DB Modify

R608 *0_4/S

SYS_PWROK EC_PWROK

R585 *0_4

10/17: SI Modify change to 10 Kohm

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

IMVP_PWRGD

R635

10K_4

PROJECT : R63

PROJECT : R63

PROJECT : R63

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PCH 1/6 (DMI/FDI/VIDEO)

PCH 1/6 (DMI/FDI/VIDEO)

PCH 1/6 (DMI/FDI/VIDEO)

1

06

INT. HDMI

IMVP_PWRGD 6,40

6 44Monday, December 24, 2012

6 44Monday, December 24, 2012

6 44Monday, December 24, 2012

1A

1A

1A

5

TP65

TP69

CLKGEN_RTC_X111

D D

+3V_RTC

Reserve for EMI

C849

*10P/50V_4

for DS3

+3V_DEEP_SUS

SIO_EXT_SCI#31

C C

R760 0_4

TP114

R668 1M_4

TP74

ACZ_SPKR28

ACZ_SDIN028

TP79

R686 10K_4

SIO_EXT_SCI#

TP112

TP113

TP111

TP108

check

PCH Strap Table

B B

Pin Name Strap description Sampled Configuration

SPKR

No reboot mode setting PWROK

GNT3# / GPIO55 Top-Block Swap Override

Lynx Point (HDA,JTAG,SATA)

RTC_X1

RTC_X2

RTC_RST#

SRTC_RST#

SM_INTRUDER#

PCH_INVRMEN

ACZ_BCLK

ACZ_SYNC

ACZ_SPKR

ACZ_RST#

ACZ_SDOUT

GPIO33

PCH_JTAG_TCK_R

PCH_JTAG_TMS

PCH_JTAG_TDI_R

PCH_JTAG_TDO_R

R391 0_4

TP68

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_CS1#

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

PCH_SPI_IO3

U33A

B5

RTCX1

B4

RTCX2

D9

RTCRST#

B9

SRTCRST#

A8

INTRUDER#

G10

INTVRMEN

B25

HDA_BCLK

A22

HDA_SYNC

AL10

SPKR

C24

HDA_RST#

L22

HDA_SDIN0

K22

HDA_SDIN1

G22

HDA_SDIN2

F22

HDA_SDIN3

A24

HDA_SDO

(+3V)

B17

HDA_DOCK_EN# / GPIO33

(+

3VS5)

C22

HDA_DOCK_RST# / GPIO13

AB3

JTAG_TCK

AD1

JTAG_TMS

AE2

JTAG_TDI

AD3

JTAG_TDO

F8

TP25

C26

TP22

AB6

TP20

AJ11

SPI_CLK

AJ7

SPI_CS0#

AL7

SPI_CS1#

AJ10

SPI_CS2#

AH1

SPI_MOSI

AH3

SPI_MISO

AJ4

SPI_IO2

AJ2

SPI_IO3

LPT_PCH_M_EDS/BGA

PWROK

INTVRMEN Integrated 1.05V VRM enable ALWAYS

HDA_DOCK_EN#/GPIO33

GNT1# / GPIO51

GPIO19

Flash Descriptor Security

Only for Interposer

Boot BIOS Selection 1 [bit-1]

Boot BIOS Selection 0 [bit-0]

PWROK

PWROK

ROK

PW

HDA_SYNC On-Die PLL VR Voltage Select RSMRST

HDA_SDO PWROKFlash Descriptor Security

GPIO8

A A

GPIO28 0 = Disable

RSVD Internel PURSMRST#

On-die PLL Voltage Regulator RSMRST#

SPI_MOSI iTPM function Disable APWROK 0 = Default (weak pull-down 20K)

5

PLL On-Die Voltage

egulator Enable

R

RSMRST#

GPIO62 / SUSCLK

4

A20

LAD0

C20

LAD1

A18

LAD2

C18

LAD3

B21

LFRAME#

D21

LDRQ0#

RTCIHDA

LDRQ1# / GPIO23

SATA 6G LPC

SATA4RXN / PERN1

SATA4RXP / PERP1

SATA4TXN / PETN1

SATA4TXP / PETP1

SATA5RXN / PERN2

SATA5RXP / PERP2

SATA5TXN / PETN2

SATA5TXP / PETP2

SATA_RCOMP

SATA0GP / GPIO21

SATA1GP / GPIO19

SPI JTAG

0

= Default (weak pull-down 20K)

1 = Setting to No-Reboot mode

0 = "top-block swap" mode

1

= Default (Int PU)

0 = Disable

= Enable

1

0 = Override

1 = Default (weak pull-up 20K)

GNT0#GNT1#

11

00

0 = Support by 1.8V (weak pull-down)

1 = Support by 1.5V

0 = Security Effect (Int PD)

1 = Can be Overridden

= Enable (Int PU)

1

(+3V)

SERIRQ

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA1RXP

SATA1TXN

SATA1TXP

SATA2RXN

SATA2RXP

SATA2TXN

SATA2TXP

SATA3RXN

SATA3RXP

SATA3TXN

SATA3TXP

SATA_IREF

SATALED#

(+3V)

(+

3V)

TP9

TP8

G20

AL11

BC8

BE8

AW8

AY8

BC10

BE10

AV10

AW10

BB9

BD9

AY13

AW13

BC12

BE12

AR13

AT13

BD13

BB13

AV15

AW15

BC14

BE14

AP15

AR15

AY5

SATA_RCOMP

Impedance = 50 ohm

Trace length < 500 mils

Trace spacing = 15 mils

BD4

AP3

AT1

AU2

BA2

BB2

Boot Location

SPI

LPC

1 = Enable

0 = Disable

1 = Enable (Int PU)

4

LAD0 31,34

LAD1 31,34

LAD2 31,34

LAD3 31,34

PCH_DRQ#0

PCH_DRQ#1

SERIRQ

LFRAME# 31,34

TP115

TP78

R581 8.2K_4

+3V

SERIRQ 31

SATA_RXN4 33

SATA_RXP4 33

SATA_TXN4 33

SATA_TXP4 33

11/29: Pre PV modify

DG recommended that AC coupling capacitors should be

close to the connector (<100 mils) for optimal signal quality.

SATA_RXN0 33

SATA_RXP0 33

SATA_TXN0 33

SATA_TXP0 33

11/29: Pre PV modify

SATA_RCOMP

DG V0.7 -> 750 ohm

SCH V0.7 -> 0 ohm

SATA_IREF

DGT_STOP#

BBS_BIT0

DGT_STOP#

R368 7.5K/F_4

R372 *0_4/S

R584 10K_4

R611 0_4

R629 *10K_4

R587 10K_4

+1.5V

+1.5V

SATA_LED# 32

+3V

DGPU_HOLD_RST# 9,14

+3V

+3V

Circuit

ACZ_SPKR

PCH_INVRMEN

GPIO33

[Need external pull-down for LPC BIOS]

Default weak pull-up on GNT0/1#

+VCC_HDA_IO

PCH_SPI_SI

GPIO33_E31

R569 *1K_4

PCI_GNT3# 8

R389 330K_4

R680 *0_4

1 2

R613 *1K_4

R390 *1K_4

R684 *1K_4

ACZ_SDOUT

R621 *1K_4

R571 *1K_4

R374 *1K_4

R564 *1K_4

3

ODD (SATA2 3Gb/s)

HDD0 (SATA3 6.0Gb/s)

BIT_CLK_AUDIO

EMI

9/21 Install for Intel DG

+3V

+3V_RTC

+3V

10/18: SI Modify

BBS_BIT0

BBS_BIT1 8

ACZ_SYNC

R693 *1K_4

BT_OFF# 9,34

PLL_ODVR_EN 9

+3V

PCH_SUSCLK 6,31

3

2

+1.05V 2,4,9,10,11,31,34,37

+3V_RTC 6,10,11

+3VPCU 4,9,11,25,31,32,34,35,36

+3V 2,6,8,9,10,12,13,14,23,24,25,26,27,28,29,30,31,32,33,34,39,40,42,44

+3V_DEEP_SUS 6,8,9,10,39

+3VS5 2,6,9,10,34,36,38,39,42,44

+5V 23,26,28,29,32,33,34,39

+3V_RTC_0 11

RTC Circuitry(RTC)

10/11: SI change footprint

+3VPCU

12

ACZ_RST#_AUDIO28

ACZ_SDOUT_AUDIO28

+3V_RTC_0

BIT_CLK_AUDIO28

+5V

C855

*33P/50V_4

+3V_RTC_0

ACZ_SYNC_AUDIO28

12/13: PV modify

PCH SPI ROM(CLG)

1

2/13: PV modify

+VCC_HDA_IO

PCH_SPI_CS1#

PCH_SPI_CS0#

10/18: Del R350 , R344

R562 *0_4

R561 0_4

2

10/18: SI Modify

+3V_RTC_2

R735 *1K_4

CN20

BAT_CONN

DFHD02MS119

85204-0200-2p-l

RTC Power trace width 20mils.

+3V_RTC_1

HDA Bus(CLG)

R697 33_4

R688 33_4

R691 33_4

+SPI_PWR

R407 *10K_4

R398 33_4

R401

*1M_4

PCH_SPI_CLK

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_IO2

PCH_SPI_IO3

2

1

R811 0_4

If EC support embedded flash , SPI

p

ower must be used S5_0N power rail

for EC load code.

TP103R563 *1K_4

TP106

TP104

PCH_SPI_CS0#R

R548 3.3K_4

R592 0_4

R591 0_4

Vender

EON

Socket

1

RTC Clock 32.768KHz

C530 *18P/50V_4

C536 *18P/50V_4

30mils

+3V_RTC

D13

*BAT54C

23

RTC_X1_1

Y3

*32.768KHZ

4 1

R739 20K/F_4

R736 20K/F_4

C904

1U/6.3V_4

R382

*10M_4

RTC_X2_1

C905

1U/6.3V_4

C903

1U/6.3V_4

PCH JTAG Debug(CLG)

ACZ_BCLK

ACZ_RST#

ACZ_SDOUT

3

ACZ_SYNC

Q23

*2N7002K

C792

TP102

*22P/50V_4

R544 33_4

R542 0_4

R554 0_4

BIOS_WP#

TP105

Size

4MB

AKE39ZN0Q03 EON EN25QH32-104HIP

4MB

A

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

+3VS5

R654

R596

*210/F_4

*210/F_4

R595

R617

*100/F_4

*100/F_4

+SPI_PWR

C788

*22P/50V_4

U31

1

CE#

VDD

6

SCK

5

SI

2

SO

HOLD#

3

WP#

VSS

EN25QH32-104HIP

P/N

KE39ZN0800 AMIC A25QE32M-F (QE)AMIC

DFHS08FS023

PROJECT : R63

PROJECT : R63

PROJECT : R63

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PCH 2/6 (SATA/HDA/SPI)

PCH 2/6 (SATA/HDA/SPI)

PCH 2/6 (SATA/HDA/SPI)

1

R778 *0_4

R779 *0_4

12

J2

*SOLDERJUMPER-2

12

J1

*SOLDERJUMPER-2

R656

*210/F_4

PCH_JTAG_TMS

PCH_JTAG_TDI_R

PCH_JTAG_TDO_R

PCH_JTAG_TCK_R

R619

*100/F_4

R552 *0_4

R556 *0_4/S

8

7

R550 3.3K_4

4

7 44Monday, December 24, 2012

7 44Monday, December 24, 2012

7 44Monday, December 24, 2012

07

RTC_X1

RTC_X2

RTC_RST#

SRTC_RST#

R657

*51_4

C793

0.1U/10V_4

+3VS5

+3V

1A

1A

1A

5

PCI/USBOC# Pull-up(CLG)

PCI_PIRQA#

R695 8.2K_4

PCI_PIRQB#

R698 8.2K_4

PCI_PIRQC#

R689 8.2K_4

PCI_PIRQD#

R699 8.2K_4

+3V

RP5

10

9

for DS3

8

7 4

+3V_DEEP_SUS

RP3

10

9

8

7 4

10K_10P8R_6

BT_COMBO_EN#34

10K_10P8R_6

USB30_RX1-29

USB30_RX2-29

USB30_RX1+29

USB30_RX2+29

USB30_TX1-29

USB30_TX2-29

USB30_TX1+29

USB30_TX2+29

BBS_BIT17

ACC_LED#32

PCI_GNT3#7

PM_EXTTS#012,13

EXTTS#113

D D

EDID_SELECT#

LCD_BK

USB_OC4#

USB_OC1#

USB_OC3#

USB3.0

C C

LCD_BK25

ACCEL_INTH#34

B B

+3V

1

ACC_LED#

2

ACCEL_INTH#MPC_PWR_CTRL#

3

BT_COMBO_EN#

DGPU_SELECT#

56

4/30: CRB 1.0 =>rename PCH_TP26

1

USB_OC6#

2

USB_OC0#

3

PCH_AOCS#

USB_OC5#USB_OC2#

56

R810 *0_4

R809 0_4

TP76

check

MPC Switch Control

MPC_PWR_CTRL#

MPC_PWR_CTRL#

Low = MPC ON

High = MPC OFF (Default)

R396 *1K_4

PLTRST#(CLG)

7/26 DB modify

PLTRST#

A A

PLTRST# 2,14,27,30,31,34

PEG Clock detect (SG only)

7/26 DB modify

5

Lynx Point (PCI,USB,NVRAM)

U33E

BA45

TP1

BC45

TP2

BE44

TP3

BE43

TP4

AY43

PCH_TP26

R7108.2K_4

PCI_PIRQA#

PCI_PIRQB#

PCI_PIRQC#

PCI_PIRQD#

BT_COMBO_EN#

DGPU_SELECT#

EDID_SELECT#

BBS_BIT1

ACC_LED#

PCI_GNT3#

MPC_PWR_CTRL#

PCI_PME#

PLTRST#

PLTRST#

R349

100K_4

TD_IREF

AR26

USB3RXN1

AW26

USB3RXN2

AW29

USB3RXN5

AR29

USB3RXN6

AP26

USB3RXP1

AV26

USB3RXP2

AV29

USB3RXP5

AP29

USB3RXP6

BE24

USB3TXN1

BD25

USB3TXN2

BE26

USB3TXN5

BD27

USB3TXN6

BD23

USB3TXP1

BC24

USB3TXP2

BC26

USB3TXP5

BE28

USB3TXP6

H20

PIRQA#

L20

PIRQB#

K17

PIRQC#

M20

PIRQD#

A12

GPIO50

B13

GPIO52

C12

GPIO54

C10

GPIO51

A10

GPIO53

AL6

GPIO55

G17

PIRQE# / GPIO2

F17

PIRQF# / GPIO3

L15

PIRQG# / GPIO4

M15

PIRQH# / GPIO5

AD10

PME#

Y11

PLTRST#

LPT_PCH_M_EDS/BGA

12/18 PV modify

MBCLK213,24,31

MBDATA213,24,31

+3V

SMB_PCH_DAT

SMB_PCH_CLK

Thermal

(+3V)

(+3V)

(+3

V)

(+3V)

PCI

(+3V)

(+3V)

USB

(+3V)

(+3V)

(+3V)

(+3V)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

SMBus/Pull-up(CLG)

Q20

2N7002DW

2N7002DW

5

2

6

Q22

43

1

4 3

1

5

2

6

C- Link

CL_CLK1

CL_DATA1

CL_RST1#

USBP0N

USBP0P

USBP1N

USBP1P

USBP2N

USBP2P

USBP3N

USBP3P

USBP4N

USBP4P

USBP5N

USBP5P

USBP6N

USBP6P

USBP7N

USBP7P

USBP8N

USBP8P

USBP9N

USBP9P

USBP10N

USBP10P

USBP11N

USBP11P

USBP12N

USBP12P

USBP13N

USBP13P

USBRBIAS#

USBRBIAS

TP24

TP23

OC0# / GPIO59

OC1# / GPIO40

OC2# / GPIO41

OC3# / GPIO42

OC4# / GPIO43

OC5# / GPIO9

OC6# / GPIO10

OC7# / GPIO14

+3V

R352 2.2K_4

SMB_ME1_CLK

+3V_DEEP_SUS

SMB_ME1_DAT

R346 2.2K_4

SMB_RUN_DAT 12,13,24

R356 4.7K_4

R355 4.7K_4

SMB_RUN_CLK 12,13,24

4

4

AF11

AF10

AF7

B37

D37

A38

C38

A36

C36

A34

C34

B33

D33

F31

G31

K31

L31

G29

H29

A32

C32

A30

C30

B29

D29

A28

C28

G26

F26

F24

G24

K24

K26

M33

L33

P3

V1

U2

P1

M3

T1

N2

M1

for DS3

WLAN

LAN

C

ardreader

USBP0- 29

USBP0+ 29

USBP1- 29

USBP1+ 29

USBP4- 25

USBP4+ 25

USBP5- 29

USBP5+ 29

PCIE_RXN3_CARD27

PCIE_RXP3_CARD27

PCIE_TXN3_CARD27

PCIE_TXP3_CARD27

USB2.0

USB2.0

Web

Touch screen

12/11: PV modify

USBP9- 30

Right_USB

USBP9+ 30

USBP10- 34

WLAN

USBP10+ 34

USB_BIAS

R400

22.6/F_4

USB_OC0#

USB_OC1#

USB_OC2#

USB_OC3#

USB_OC4#

USB_OC5#

USB_OC6#

PCH_AOCS#

PCH_AOCS# 34

CLK_REQ/Strap Pin(CLG)

CLK_PCIE_REQ1#

CLK_PCIE_REQ2#

CLK_PCIE_REQ0#

CLK_PCIE_REQ3#

CLK_PCIE_REQ4#

CLK_PEGB_REQ#

CLK_PEGA_REQ#

CLK_PEGA_REQ#

7/26 DB modify

CLK_BUF_BCLK_N

CLK_BUF_BCLK_P

CLK_BUF_PCIE_3GPLL#

CLK_BUF_PCIE_3GPLL

+3V

CLK_BUF_DREFCLK#

CLK_BUF_DREFCLK

CLK_BUF_DREFSSCLK#

CLK_BUF_DREFSSCLK

CLK_PCH_14M

CLOCK TERMINATION for FCIM

PCIE_RXN134

PCIE_RXP134

PCIE_TXN134

PCIE_TXP134

PCIE_RXN2_LAN30

PCIE_RXP2_LAN30

PCIE_TXN2_LAN30

PCIE_TXP2_LAN30

USB2.0/USB3.0 COMBO 1st

2.0/USB3.0 COMBO 2nd

USB

+1.5V

cam

R370 10K_4

R378 10K_4

R658 10K_4

R623 10K_4

R659 10K_4

R602 10K_4

R598 *10K_4

Ra

R597 10K_4

Rb

SG : Rb ; UMA : Ra

R406 10K_4

R405 10K_4

R399 10K_4

R402 10K_4

R409 10K_4

R408 10K_4

R669 10K_4

R670 10K_4

R708 10K_4

C850 0.1U/10V_4

C846 0.1U/10V_4

C851 0.1U/10V_4

C857 0.1U/10V_4

C864 0.1U/10V_4

C865 0.1U/10V_4

CLK_PCIE_CARDN27

CLK_PCIE_CARDP27

CLK_PCIE_REQ2#27

CLK_PEGA_REQ#15

+3V

+3V_DEEP_SUS

3

Lynx Point (PCI-E,SMBUS,CLK)

PCIE_TXN1_C

PCIE_TXP1_C

PCIE_TXN2_LAN_C

PCIE_TXP2_LAN_C

PCIE_TXN3_CARD_C

PCIE_TXP3_CARD_C

R692 *0_4/S

R687 7.5K/F_4

PCIE_IREF

PCIE_RCOMP

CLK_PCH_SRC0N

CLK_PCH_SRC0P

CLK_PCIE_REQ0#

CLK_PCH_SRC2N

CLK_PCH_SRC2P

CLK_PCIE_REQ1#

CLK_PCH_CARD2N

CLK_PCH_CARD2P

CLK_PCIE_REQ2#

CLK_PCIE_REQ3#

CLK_PCIE_REQ4#

BOARD_ID09

BOARD_ID19

BOARD_ID29

CLK_PCH_PEGAN

CLK_PCH_PEGAP

CLK_PEGA_REQ#

DS3

for

PCIE Clock

N

WLA

LAN

GPU

3

CLK_PCIE_WLAN#34

CLK_PCIE_WLAN34

PCIE_CLKREQ_WLAN#34

CLK_PCIE_LANP30

CLK_PCIE_LANN30

PCIE_CLKREQ_LAN#30

CLK_PCIE_VGA#14

CLK_PCIE_VGA14

U33B

AW31

PERN1 / USB3RN3

AY31

PERP1 / USB3RP3

BE32

PETN1 / USB3TN3

BC32

PETP1 / USB3TP3

AT31

PERN2/ USB3RN4

AR31

PERP2/ USB3RP4

BD33

PETN2/ USB3TN4

BB33

PETP2/ USB3TP4

AW33

PERN3

AY33

PERP3

BE34

PETN3

BC34

PETP3

AT33

PERN4

AR33

PERP4

BE36

PETN4

BC36

PETP4

AW36

PERN5

AV36

PERP5

BD37

PETN5

BB37

PETP5

AY38

PERN6

AW38

PERP6

BC38

PETN6

BE38

PETP6

AT40

PERN7

AT39

PERP7

BE40

PETN7

BC40

PETP7

AN38

PERN8

AN39

PERP8

BD42

PETN8

BD41

PETP8

BE30

PCIE_IREF

BD29

PCIE_RCOMP

BC30

TP11

BB29

TP6

Y43

CLKOUT_PCIE0N

Y45

CLKOUT_PCIE0P

AB1

PCIECLKRQ0# / GPIO73

AA44

CLKOUT_PCIE1N

AA42

CLKOUT_PCIE1P

AF1

PCIECLKRQ1# / GPIO18

AB43

CLKOUT_PCIE2N

AB45

CLKOUT_PCIE2P

AF3

PCIECLKRQ2# / GPIO20/ SMI#

AD43

CLKOUT_PCIE3N

AD45

CLKOUT_PCIE3P

T3

PCIECLKRQ3# / GPIO25

AF43

CLKOUT_PCIE4N

AF45

CLKOUT_PCIE4P

V3

PCIECLKRQ4# / GPIO26

AE44

CLKOUT_PCIE5N

AE42

CLKOUT_PCIE5P

AA2

PCIECLKRQ5# / GPIO44

AB40

CLKOUT_PCIE6N

AB39

CLKOUT_PCIE6P

AE4

PCIECLKRQ6# / GPIO45

AJ44

CLKOUT_PCIE7N

AJ42

CLKOUT_PCIE7P

Y3

PCIECLKRQ7# / GPIO46

AB35

CLKOUT_PEG_A_N

AB36

CLKOUT_PEG_A_P

AF6

PEG_A_CLKRQ# / GPIO47

AD39

TP19

AD38

TP18

LPT_PCH_M_EDS/BGA

R620 *0_4/S

R361 *0_4/S

2

RP4

4

0_4P2R_4

Remove for UMA only.

PCI-E*

(+3VS5)

(+3V)

(+3V)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

SMBUS

CLK_PCH_SRC0N

CLK_PCH_SRC0P

CLK_PCH_SRC2P

CLK_PCH_SRC2N

1

CLK_PCH_PEGAN

3

CLK_PCH_PEGAP

2

(+3VS5)

SMBALERT# / GPIO11

SMBCLK

SMBDATA

(+3VS5)

SML0ALERT# / GPIO60

SML0CLK

SML0DATA

SML1ALERT# / PCHHOT# / GPIO74

CLOCKS

(+3VS5)

(+3VS5)

SML1CLK / GPIO58

(+3VS5)

SML1DATA / GPIO75

CLKOUT_PEG_B_N

CLKOUT_PEG_B_P

PEG_B_CLKRQ# / GPIO56

(+3

VS5)

CLKOUT_ITPXDP_N

CLKOUT_ITPXDP_P

CLKOUT_DPNS_N

CLKOUT_DPNS_P

CLKOUT_DP_N

CLKOUT_DP_P

CLKOUT_DMI_N

CLKOUT_DMI_P

CLKIN_DMI_N

CLKIN_DMI_P

CLKIN_GND1_N

CLKIN_GND1_P

CLKIN_DOT_96N

CLKIN_DOT_96P

CLKIN_SATA_N

CLKIN_SATA_P

REFCLK14IN

CLKIN_PCILOOPBACK

XTAL25_IN

XTAL25_OUT

ICLK_IREF

DIFFCLK_BIASREF

CLKOUT_33MHZ0

CLKOUT_33MHZ1

CLKOUT_33MHZ2

CLKOUT_33MHZ3

CLKOUT_33MHZ4

(+3V)

CLKOUTFLEX0 / GPIO64

(+3V)

CLKOUTFLEX1 / GPIO65

CLKOUTFLEX2 / GPIO66

(+3V)

CLKOUTFLEX3 / GPIO67

(+3V)

FLEX CLOCKS

CLK_PCIE_REQ0#

CLK_PCIE_REQ1#

2

N7

SMBALERT#

R10

SMB_PCH_CLK

U11

SMB_PCH_DAT

N8

DRAMRST_CNTRL_PCH

U8

SMB_ME0_CLK

R7

SMB_ME0_DAT

H6

SML1ALERT#_R

K6

SMB_ME1_CLK

N11

SMB_ME1_DAT

Y39

Y38

U4

CLK_PEGB_REQ#

AH43

CLK_PCH_ITPN

AH45

CLK_PCH_ITPP

AF35

AF36

AJ40

AJ39

AF39

AF40

AY24

CLK_BUF_PCIE_3GPLL#

AW24

CLK_BUF_PCIE_3GPLL

AR24

CLK_BUF_BCLK_N

AT24

CLK_BUF_BCLK_P

H33

CLK_BUF_DREFCLK#

G33

CLK_BUF_DREFCLK

BE6

CLK_BUF_DREFSSCLK#

BC6

CLK_BUF_DREFSSCLK

F45

CLK_PCH_14M

D17

CLK_PCI_FB

AM43

XTAL25_IN

AL44

XTAL25_OUT XTAL25_OUT_1

AM45

ICLK_IREF

AN44

ICLK_BIAS

D44

CLK_PCI_TPM_R

E44

CLK_PCI_CARD_R

B42

CLK_PCH_PCI2

F41

CLK_PCH_PCI3

A40

CLK_PCH_PCI4

C40

CLK_FLEX0

F38

CLK_FLEX1

F36

CLK_FLEX2

F39

CLK_FLEX3

for DS3

TP67

TP85

TP84

TP64

TP118

CLK_DPLL_NSCCLKN 2

CLK_DPLL_NSCCLKP 2