Page 1

5

4

3

2

1

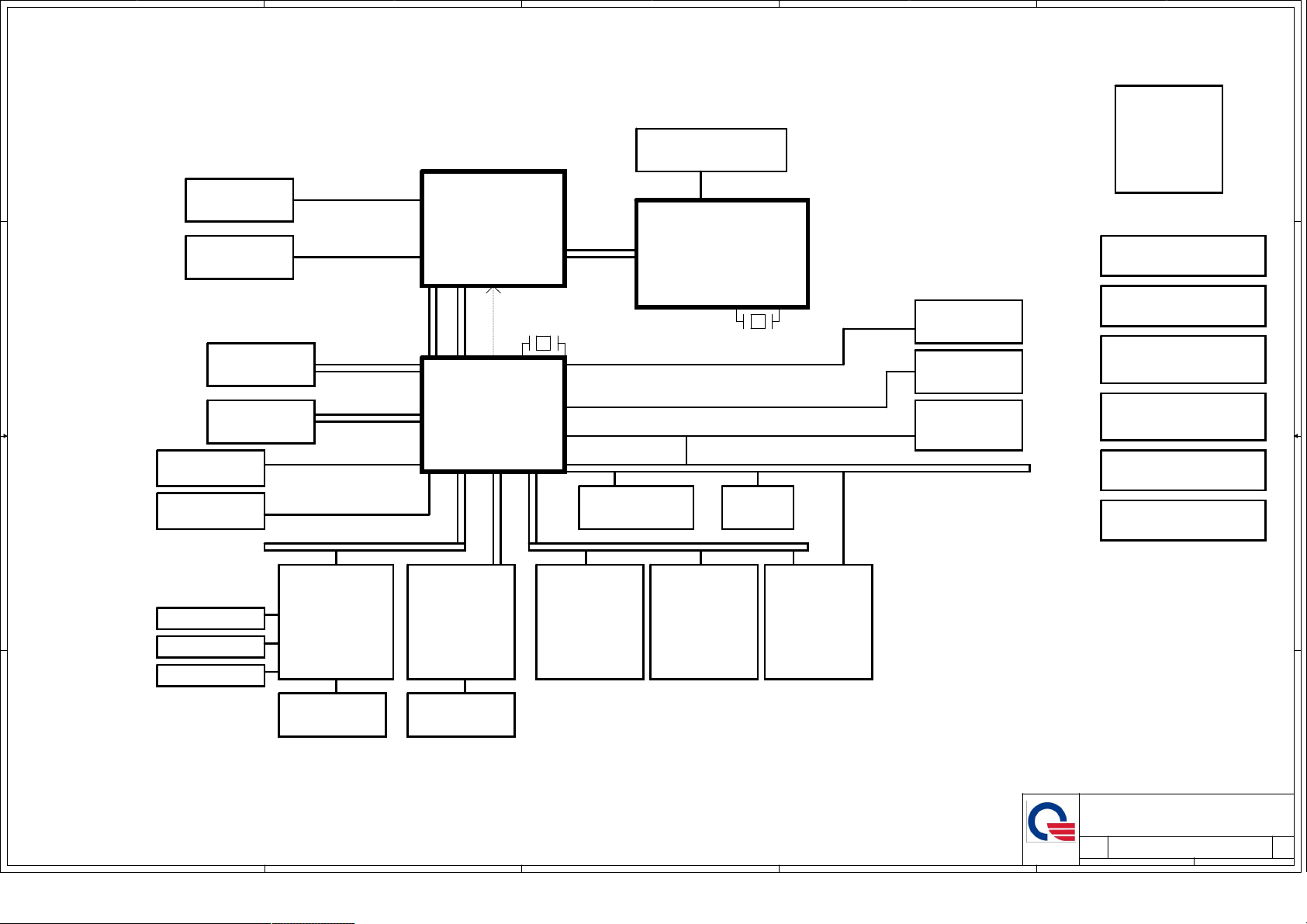

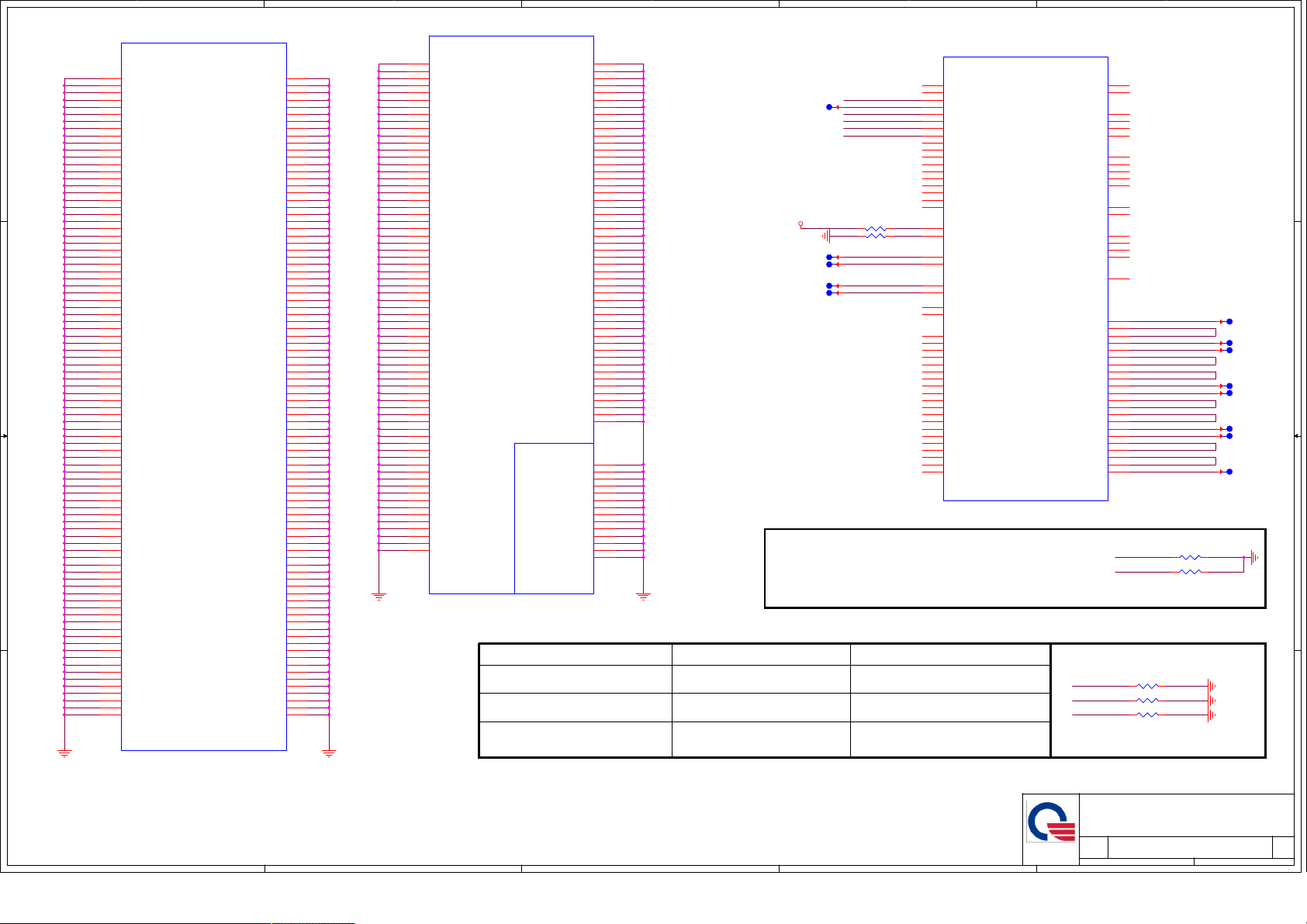

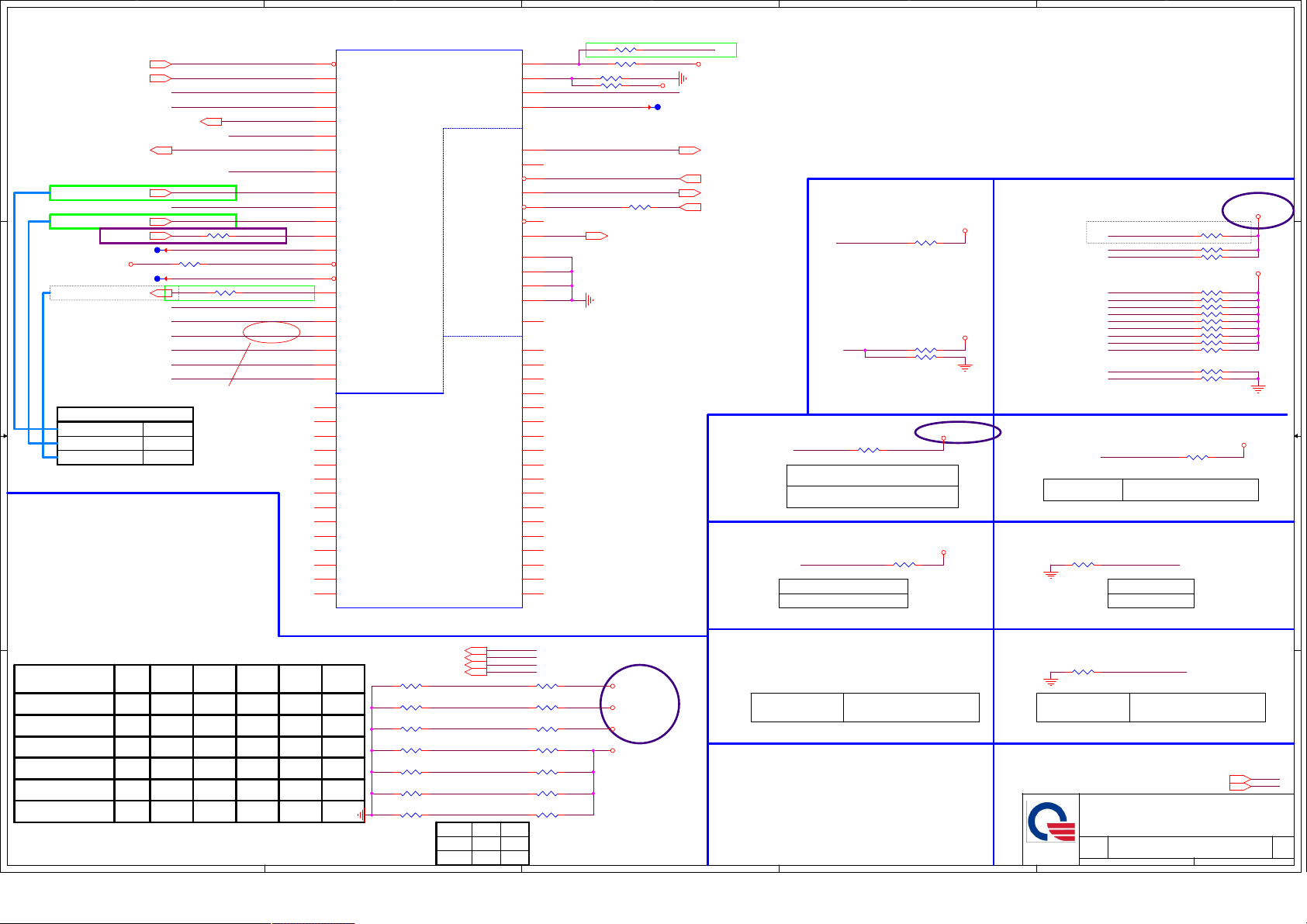

Volks DIS/UMA (14"/15.6")

D D

C C

G-Sensor

System BIOS

SPI ROM

B B

Intel Chief River Platform Block Diagram

DDR3 SODIMM1

Maxima 4GBs

PAGE 12

DDR3 SO-DIMM2

Maxima 4GBs

PAGE 13

SATA - 1st HDD

Package : 9.5 (mm)

Power :

mSATA

Package : 12.7 (mm)

Power :

PAGE 22

PAGE 7

DDR3 800 ~ 1600 MT/s

DDR3 800 ~ 1600 MT/s

SATA0 6GB/s

PAGE 24

SATA1 6GB/s

PAGE 24

SM BUS

SPI Interface

Intel Ivy Bridge

Sandy Bridge

Processor : Daul Core

Power : 35/17 (Watt)

Package : BGA1023

Size : 31x 27 (mm)

PAGE 2~5

DMI x 4

FDI x 8

BCLK133M

Intel Cougar/Panther Point

Platform Controller Hub

Power : 3.5 Watt

Package : FCBG989

Size : 25 x 25 (mm)

PAGE 6~11

Azalia

ph

Green CLK

32.768KHz

PAGE 25

PCIE Gen 1 x 1 LaneLPC Interface

PCI-E Gen3

x 8 Lane

LVDS Interface

HDMI Interface

USB3.0 Interface

USB2.0 Interface

USB2.0 Port x 1(Left side)

Port9 Port2

PAGE 19

Ultra/Slim

VRAM DDR3 x 4

Max 1GBs/2GBs

900Mhz

NVIDIA N13 P-GV2

S3 Pack age 23*23 mm

27.5W

DP PortB

USB 3.0 Port1(USB 2.0 Port0)

Port0,1

PAGE 18

64bit

PAGE 14~17

27MHz

PAGE 16

Camera

PAGE 26

LCD Conn (14")

PAGE 26

HDMI Conn

PAGE 26

USB3.0 Port x 1

PAGE 22

PCB 6L STACK UP

LAYER 1 : TOP

LAYER 2 : SGND

LAYER 3 : IN1(High)

LAYER 4 : IN2(Low)

LAYER 5 : SVCC

LAYER 6 : BOT

Power Source

BQ24738

System Charge Power (+BATCHG)

Ricktek RT8223P

System Power (+3VPCU/+5VPCU/

+3VS5/+5VS5)

NCP6132/NCP5911/RT8240P/

TPS51462RGER

Processor Power (+VCC_CORE/

+1.05_VTT/+VCCSA)

SLG55448V

System Discharge Power

(+1.5V/+3V/+5V)

Richtek RT8207

System Memory Power (+1.5VSUS/

+0.75V_DDR_VTT)

NCP3218G

GPU core power(+VGACORE)

01

Realtek RTL8105

LAN Controller

Power :

Package : OFN48

Size : 6 x 6 (mm)

PAGE 20

Intel Rambo Peak

Halt Mini Card

WLAN / BT Combo

PAGE 23

EC SPI ROM

Keyboard

Touch Pad

PAGE 25

PAGE 22

PAGE 24

EnE KB3940QF A1

Embedded Controller

Power :

Package : LQPF128

Size : 14 x 14 (mm)

PAGE 25

FAN Controller

IDT

92HD99

Power :

Package : LQPF48

Size : 7 x 7 (mm)

PAGE 19

Combo Jack

RTS5229-GR

Card Reader

Power :

Package : LQPF48

Size : 7 x 7 (mm)

PAGE 21

iPHONE type

PAGE 24

A A

5

4

PAGE 19

PROJECT : VOLKS

PROJECT : VOLKS

PROJECT : VOLKS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Block Diagram

Block Diagram

NB5

NB5

3

2

NB5

Block Diagram

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1A

1A

1A

1 37Wednesday, May 2 3, 2012

1 37Wednesday, May 2 3, 2012

1 37Wednesday, May 2 3, 2012

Page 2

5

4

3

2

1

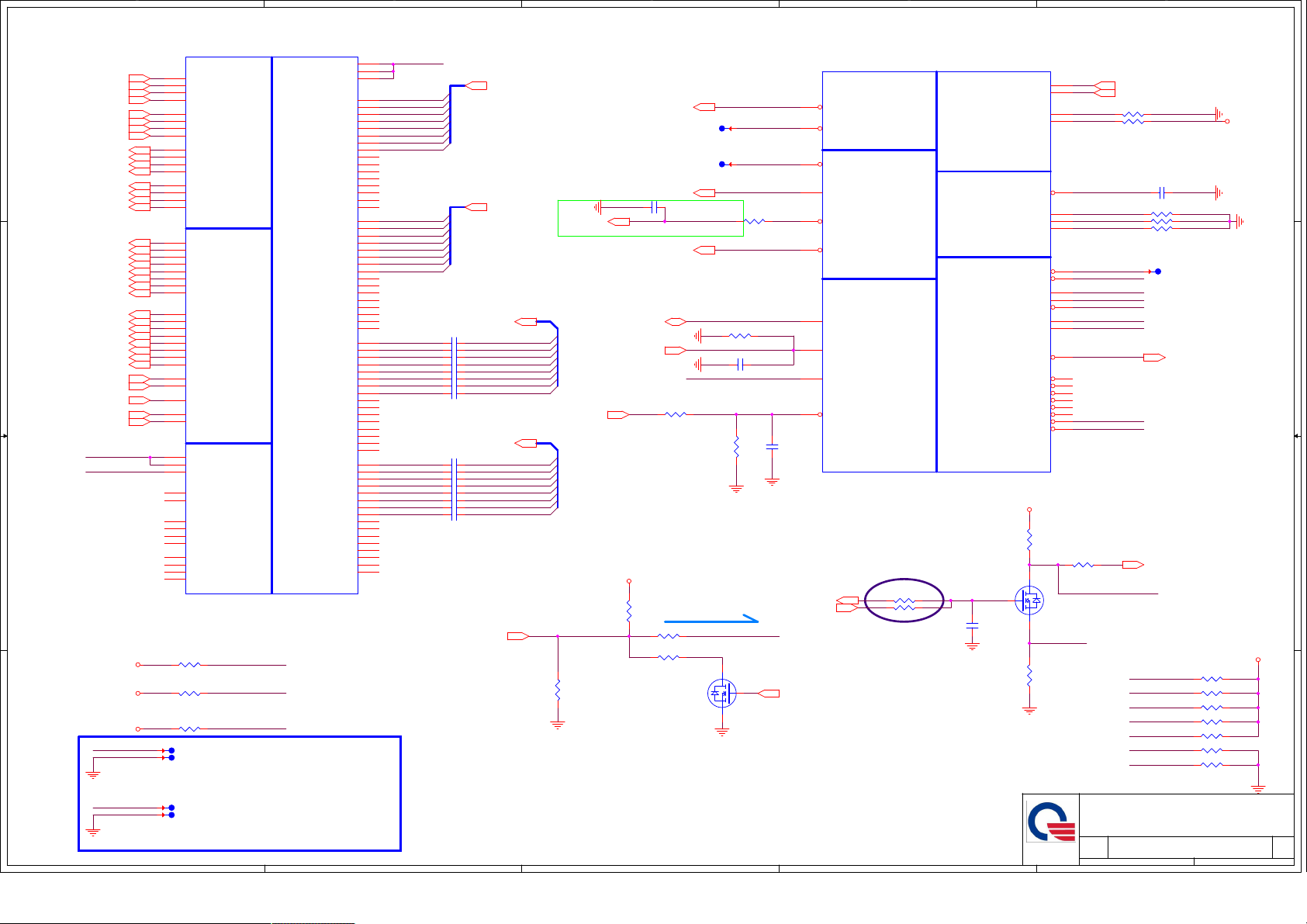

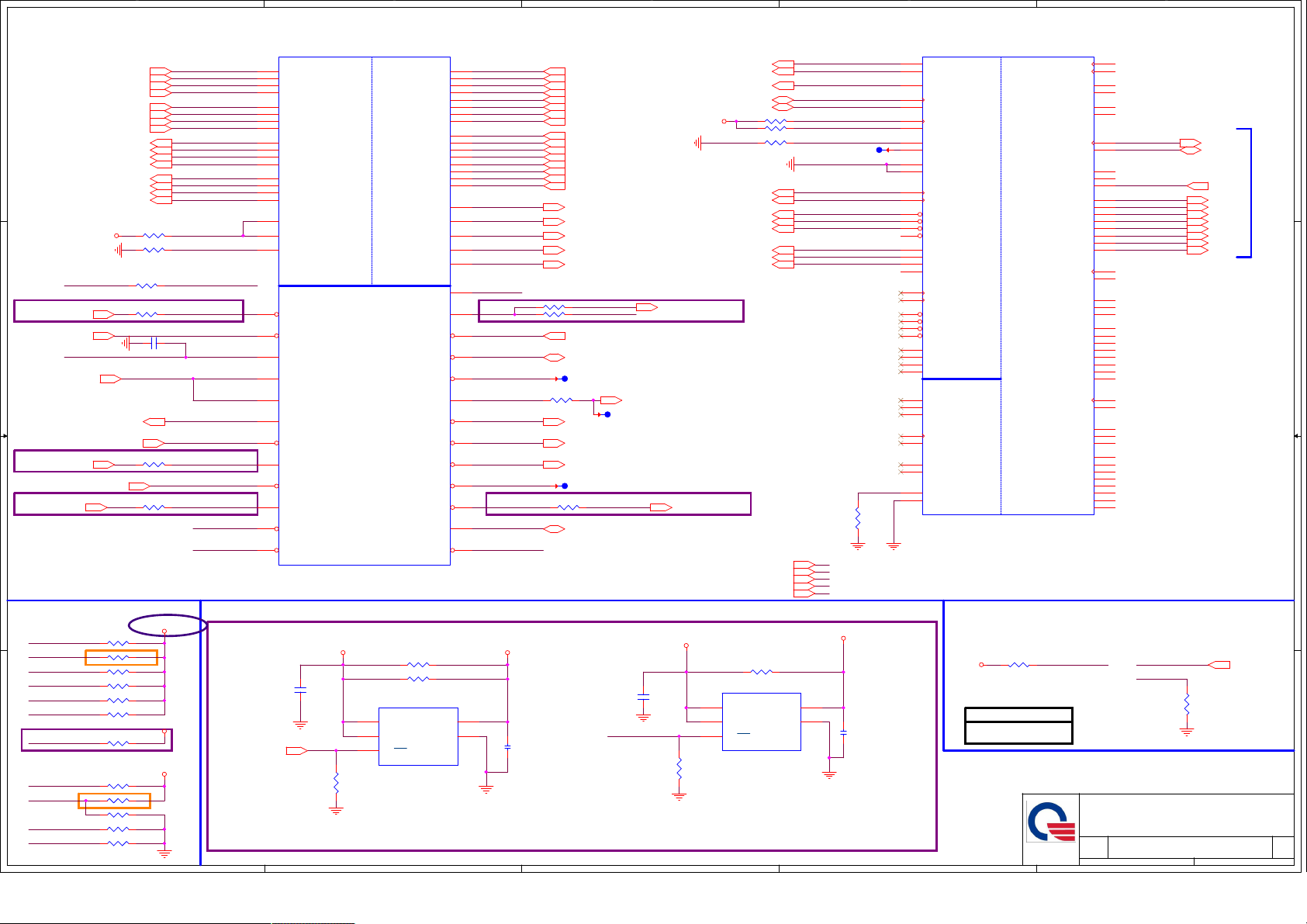

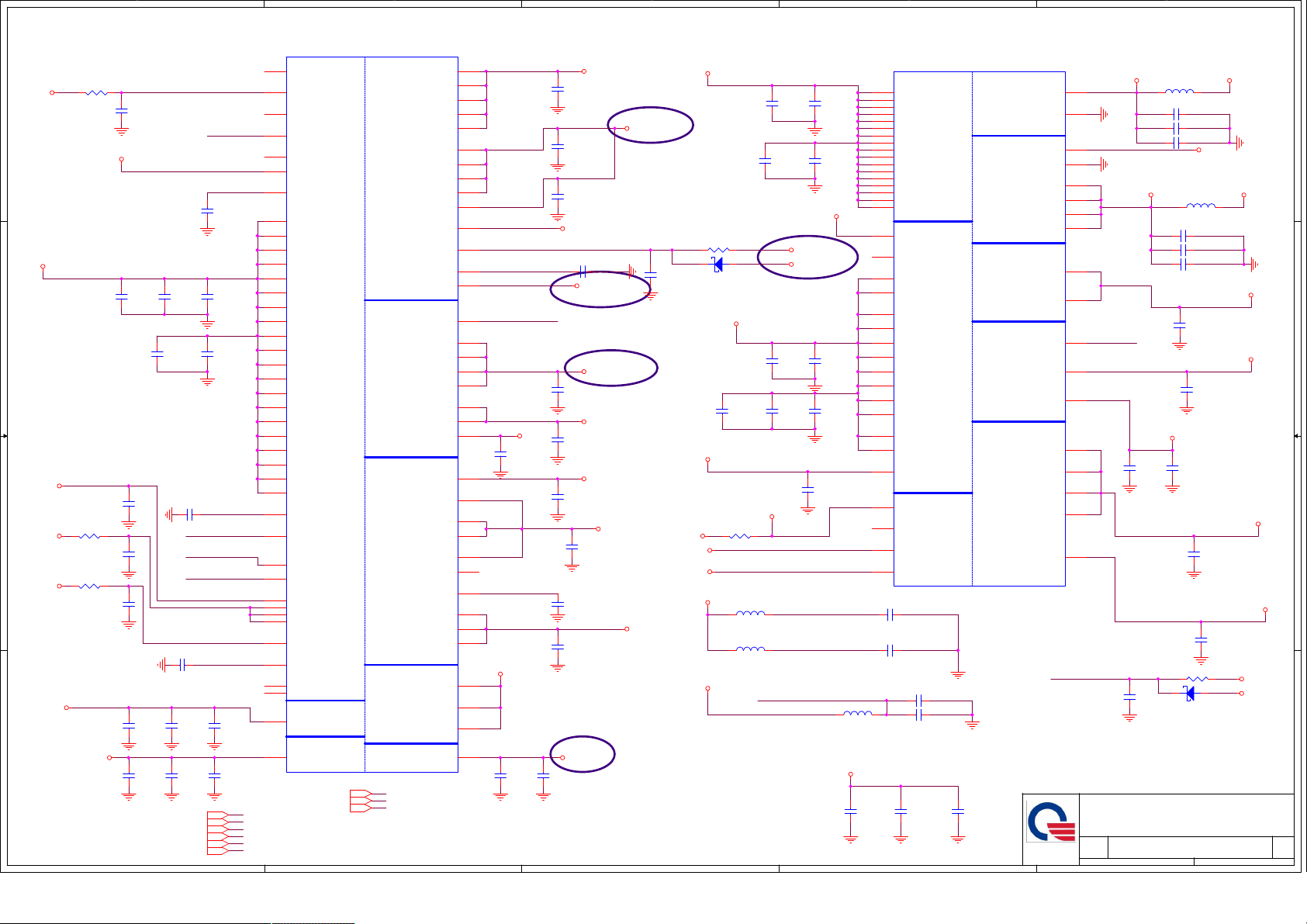

Ivy Bridge Processor (DMI,PEG,FDI)

PEG_COM P connect to PI N G3&G4 W:4mils/ S:15mils/L : 500mils.

U20A

DMI_TXN 06

DMI_TXN 16

DMI_TXN 26

DMI_TXN 36

D D

C C

B B

A A

DMI_TXP 06

DMI_TXP 16

DMI_TXP 26

DMI_TXP 36

DMI_RX N06

DMI_RX N16

DMI_RX N26

DMI_RX N36

DMI_RX P06

DMI_RX P16

DMI_RX P26

DMI_RX P36

FDI_TXN 06

FDI_TXN 16

FDI_TXN 26

FDI_TXN 36

FDI_TXN 46

FDI_TXN 56

FDI_TXN 66

FDI_TXN 76

FDI_TXP 06

FDI_TXP 16

FDI_TXP 26

FDI_TXP 36

FDI_TXP 46

FDI_TXP 56

FDI_TXP 66

FDI_TXP 76

FDI_FSYNC 06

FDI_FSYNC 16

FDI_INT6

FDI_LSYNC 06

FDI_LSYNC 16

eDP_COM P

INT_eDP_H PD_Q

eDP_CO MPIO an d ICOMPO signals should be sh orted

near b alls and routed with ty pical imp edance <25 m ohms

+1.05V

+1.05V

+1.05V

XDP_BP M6

M2

DMI_RX #[0]

P6

DMI_RX #[1]

P1

DMI_RX #[2]

P10

DMI_RX #[3]

N3

DMI_RX [0]

P7

DMI_RX [1]

P3

DMI_RX [2]

P11

DMI_RX [3]

K1

DMI_TX #[0]

M8

DMI_TX #[1]

N4

DMI_TX #[2]

R2

DMI_TX #[3]

K3

DMI_TX [0]

M7

DMI_TX [1]

P4

DMI_TX [2]

T3

DMI_TX [3]

U7

FDI0_TX #[0]

W1 1

FDI0_TX #[1]

W1

FDI0_TX #[2]

AA6

FDI0_TX #[3]

W6

FDI1_TX #[0]

V4

FDI1_TX #[1]

Y2

FDI1_TX #[2]

AC9

FDI1_TX #[3]

U6

FDI0_TX [0]

W1 0

FDI0_TX [1]

W3

FDI0_TX [2]

AA7

FDI0_TX [3]

W7

FDI1_TX [0]

T4

FDI1_TX [1]

AA3

FDI1_TX [2]

AC8

FDI1_TX [3]

AA11

FDI0_FS YNC

AC12

FDI1_FS YNC

U11

FDI_INT

AA10

FDI0_LSY NC

AG8

FDI1_LSY NC

AF3

eDP_CO MPIO

AD2

eDP_ICOM PO

AG11

eDP_HPD #

AG4

eDP_AUX #

AF4

eDP_AUX

AC3

eDP_TX# [0]

AC4

eDP_TX# [1]

AE11

eDP_TX# [2]

AE7

eDP_TX# [3]

AC1

eDP_TX[ 0]

AA4

eDP_TX[ 1]

AE10

eDP_TX[ 2]

AE6

eDP_TX[ 3]

IC,IVB_2C BGA,0P7

R407 24.9/F_4

R396 24.9/F_4

R405 *10K/F_4

TP8

TP26

DMI Intel(R) FDI

4mils

12mils

eDP

ph

eDP_COM P

PEG_COM P

INT_eDP_H PD_Q

For iFDIM

XDP_BP M7

5

Trigger Point

TP1

TP41

PEG_COM P connect to PI N G1 W:12mils/S:15 mils/L: 5 00mils.

PEG_ICO MPI

PEG_ICO MPO

PEG_R COMPO

PEG_R X#[10]

PEG_R X#[11]

PEG_R X#[12]

PEG_R X#[13]

PEG_R X#[14]

PEG_R X#[15]

PEG_TX #[10]

PEG_TX #[11]

PEG_TX #[12]

PEG_TX #[13]

PEG_TX #[14]

PCI EXPRESS -- GRAPHICS

PEG_TX #[15]

Connect a Test Point on

BPM# 6 signal, very close

to processor.

Connect a Test Point on

BPM# 7 signal, very close

to processor.

PEG_R X#[0]

PEG_R X#[1]

PEG_R X#[2]

PEG_R X#[3]

PEG_R X#[4]

PEG_R X#[5]

PEG_R X#[6]

PEG_R X#[7]

PEG_R X#[8]

PEG_R X#[9]

PEG_R X[0]

PEG_R X[1]

PEG_R X[2]

PEG_R X[3]

PEG_R X[4]

PEG_R X[5]

PEG_R X[6]

PEG_R X[7]

PEG_R X[8]

PEG_R X[9]

PEG_R X[10]

PEG_R X[11]

PEG_R X[12]

PEG_R X[13]

PEG_R X[14]

PEG_R X[15]

PEG_TX #[0]

PEG_TX #[1]

PEG_TX #[2]

PEG_TX #[3]

PEG_TX #[4]

PEG_TX #[5]

PEG_TX #[6]

PEG_TX #[7]

PEG_TX #[8]

PEG_TX #[9]

PEG_TX [0]

PEG_TX [1]

PEG_TX [2]

PEG_TX [3]

PEG_TX [4]

PEG_TX [5]

PEG_TX [6]

PEG_TX [7]

PEG_TX [8]

PEG_TX [9]

PEG_TX [10]

PEG_TX [11]

PEG_TX [12]

PEG_TX [13]

PEG_TX [14]

PEG_TX [15]

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

PEG_COM P

PEG_RX# 0

PEG_RX# 1

PEG_RX# 2

PEG_RX# 3

PEG_RX# 4

PEG_RX# 5

PEG_RX# 6

PEG_RX# 7

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

C_PEG_T X#0

C_PEG_T X#1

C_PEG_T X#2

C_PEG_T X#3

C_PEG_T X#4

C_PEG_T X#5

C_PEG_T X#6

C_PEG_T X#7

C_PEG_T X0

C_PEG_T X1

C_PEG_T X2

C_PEG_T X3

C_PEG_T X4

C_PEG_T X5

C_PEG_T X6

C_PEG_T X7

4

C183 0.22U/10V_4

C180 0.22U/10V_4

C182 0.22U/10V_4

C173 0.22U/10V_4

C169 0.22U/10V_4

C171 0.22U/10V_4

C158 0.22U/10V_4

C166 0.22U/10V_4

PEG x8

C178 0.22U/10V_4

C179 0.22U/10V_4

C181 0.22U/10V_4

C172 0.22U/10V_4

C167 0.22U/10V_4

C170 0.22U/10V_4

C164 0.22U/10V_4

C165 0.22U/10V_4

PM_DR AM_PWRG D6

PEG_RX# [0..7] 14

PEG_RX[0 ..7] 14

PEG_TX# [0..7]14

PEG_TX# 0

PEG_TX# 1

PEG_TX# 2

PEG_TX# 3

PEG_TX# 4

PEG_TX# 5

PEG_TX# 6

PEG_TX# 7

PEG_TX[0 ..7]14

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

SM_DRAMPWROK

Processor Input.

H_SNB_ IVB#7

SKTOCC #

TP3

TP_CAT ERR#

TP7

Placement close to EC.

H_PECI25

C58947P/50V_4

H_PROC HOT#25,34

SI modify on 4/2

PLTRST #8,14,20,21,23 ,25

H_PROC HOT#_R

PM_THR MTRIP#9,21

PM_SYNC6

H_PW RGOOD9

R376 1.5K/F_4

CPU RESET#

+1.5V_CP U

R458

PM_DR AM_PWRG D PM_DR AM_PWRG D_R

R459

*3K/F_4

200/F_4

R460 130/F_4

R461

*39_4

3

H_PECI

R375 56.2/F_4

R373 10K/F_4

C588 *43P/50V_4

PM_DR AM_PWRG D_R

Intel DG request

CPU_RE SET#

R393

750/F_4

3

2

Q33

*2N7002K

1

C590

*43P/50V_ 4

DRAMR ST_CNTRL_ PCH8,12,13

DRAMR ST_CNTRL_ EC2 5

MAIN_ON G 4,36

U20B

F49

PROC_ SELECT#

C57

PROC_ DETECT#

C49

CATER R#

A48

PECI

C45

PROCH OT#

D45

THERM TRIP#

C48

PM_SY NC

B46

UNCOR EPWRG OOD

BE45

SM_DR AMPWR OK

D44

RESET#

IC,IVB_2C BGA,0P7

for DS3

MISC THERMAL PWR MANAGEMENT

CLOCKS

DDR3

MISC

JTAG & BPM

DDR3 DRAM RESET

R532 0_4

R533 *0_4

C618

0.047U/10V _4

2

BCLK

BCLK#

DPLL_R EF_CLK

DPLL_R EF_CLK#

SM_DR AMRST#

SM_RC OMP[0]

SM_RC OMP[1]

SM_RC OMP[2]

PRDY#

PREQ#

TRST#

DBR#

BPM#[0 ]

BPM#[1 ]

BPM#[2 ]

BPM#[3 ]

BPM#[4 ]

BPM#[5 ]

BPM#[6 ]

BPM#[7 ]

+1.5VSUS

3

Q30

2N7002K

2

1

CPU_DR AMRST#

J3

H2

AG3

AG1

AT30

BF44

BE43

BG43

SM_RCOM P[0] W:20mils/S:20mi ls/L: 500mils,

SM_RCOM P[1] W:20mils/S:20mi ls/L: 500mils,

SM_RCOM P[2] W:15mils/S:20mi ls/L: 500mils,

N53

N55

L56

TCK

L55

TMS

J58

M60

TDI

L59

TDO

K58

G58

E55

E59

G55

G59

H60

J59

J61

R447

1K/F_4

CPU_DR AMRST#_R

CLK_CP U_BCLKP 8

CLK_CP U_BCLKN 8

R410 1K/F_4

R408 1K/F_4

CPU_DR AMRST#

SM_RC OMP_0

SM_RC OMP_1

SM_RC OMP_2

XDP_PR DY#

XDP_PR EQ#

XDP_TC LK

XDP_TM S

XDP_TR ST#

XDP_TD I_R

XDP_TD O

XDP_DB RST#

XDP_BP M6

XDP_BP M7

R4481K/F_4

C616 *43P/50V_4

R175 140/F_4

R176 25.5/F_4

R177 200/F_4

TP2

DDR3_D RAMRST# 12 ,13

Processor pull-up (CPU)

R444

4.99K/F_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

NB5

NB5

NB5

Date: Sheet of

Date: Sheet of

Date: Sheet of

H_PROC HOT#

XDP_TD O

XDP_TM S

XDP_TD I_R

XDP_PR EQ#

XDP_TC LK

XDP_TR ST#

PROJECT : VOLKS

PROJECT : VOLKS

PROJECT : VOLKS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Processor 1/4 (Host/GPU)

Processor 1/4 (Host/GPU)

Processor 1/4 (Host/GPU)

1

XDP_DB RST# 6

02

+1.05V

CPU XDP

R374 62_4

R384 51_4

R387 51_4

R383 51_4

R388 *51_4

R386 51_4

R385 51_4

+1.05V

1A

1A

1A

2 37Wednesday, May 2 3, 2012

2 37Wednesday, May 2 3, 2012

2 37Wednesday, May 2 3, 2012

Page 3

5

4

3

2

1

07

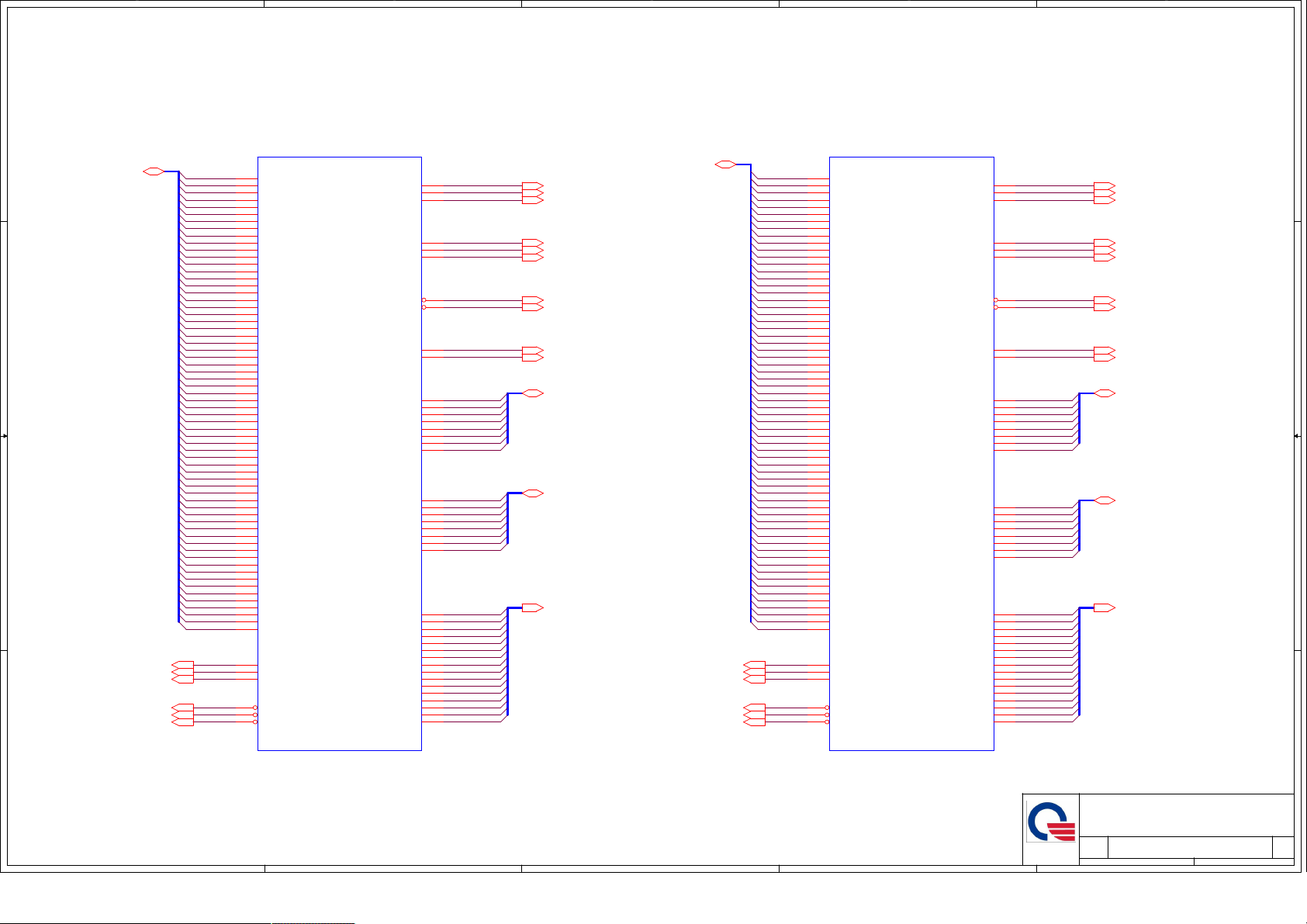

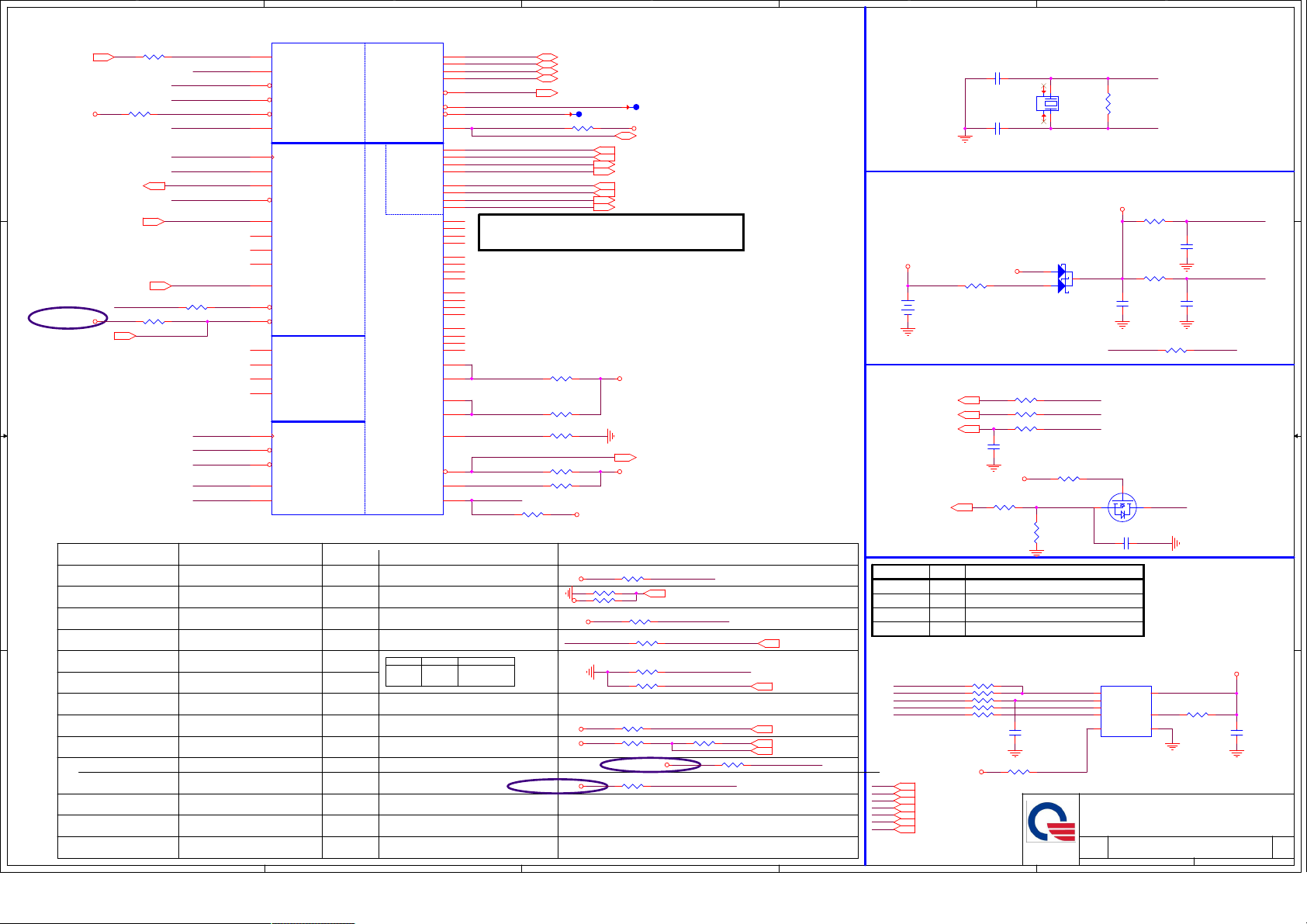

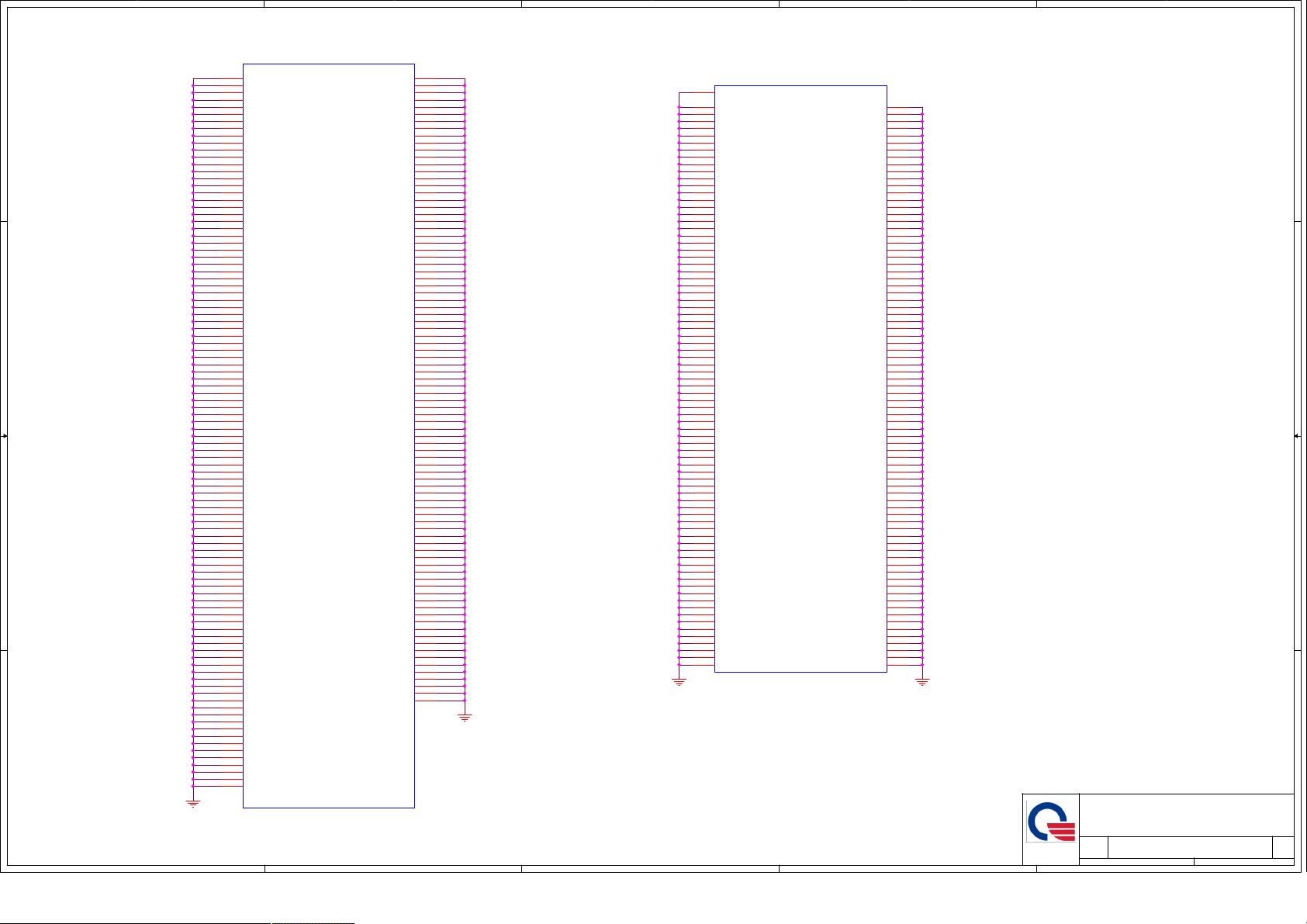

Ivy Bridge Processor (DDR3)

D D

U20C IC,IVB_2C BGA,0P7

M_A_DQ [63:0]12

C C

B B

M_A_BS #012

M_A_BS #112

M_A_BS #212

M_A_CA S#12

M_A_RA S#12

M_A_W E#12

M_A_DQ 0

M_A_DQ 1

M_A_DQ 2

M_A_DQ 3

M_A_DQ 4

M_A_DQ 5

M_A_DQ 6

M_A_DQ 7

M_A_DQ 8

M_A_DQ 9

M_A_DQ 10

M_A_DQ 11

M_A_DQ 12

M_A_DQ 13

M_A_DQ 14

M_A_DQ 15

M_A_DQ 16

M_A_DQ 17

M_A_DQ 18

M_A_DQ 19

M_A_DQ 20

M_A_DQ 21

M_A_DQ 22

M_A_DQ 23

M_A_DQ 24

M_A_DQ 25

M_A_DQ 26

M_A_DQ 27

M_A_DQ 28

M_A_DQ 29

M_A_DQ 30

M_A_DQ 31

M_A_DQ 32

M_A_DQ 33

M_A_DQ 34

M_A_DQ 35

M_A_DQ 36

M_A_DQ 37

M_A_DQ 38

M_A_DQ 39

M_A_DQ 40

M_A_DQ 41

M_A_DQ 42

M_A_DQ 43

M_A_DQ 44

M_A_DQ 45

M_A_DQ 46

M_A_DQ 47

M_A_DQ 48

M_A_DQ 49

M_A_DQ 50

M_A_DQ 51

M_A_DQ 52

M_A_DQ 53

M_A_DQ 54

M_A_DQ 55

M_A_DQ 56

M_A_DQ 57

M_A_DQ 58

M_A_DQ 59

M_A_DQ 60

M_A_DQ 61

M_A_DQ 62

M_A_DQ 63

AG6

AP11

AJ10

AR11

AP6

AU6

AV9

AR6

AP8

AT13

AU13

BC7

BB7

BA13

BB11

BA7

BA9

BB9

AY13

AV14

AR14

AY17

AR19

BA14

AU14

BB14

BB17

BA45

AR43

AW 48

BC48

BC45

AR45

AT48

AY48

BA49

AV49

BB51

AY53

BB49

AU49

BA53

BB55

BA55

AV56

AP50

AP53

AV54

AT54

AP56

AP52

AN57

AN53

AG56

AG53

AN55

AN52

AG55

AK56

BD37

BF36

BA28

BE39

BD39

AT41

AJ6

AL6

AJ8

AL8

AL7

SA_DQ [0]

SA_DQ [1]

SA_DQ [2]

SA_DQ [3]

SA_DQ [4]

SA_DQ [5]

SA_DQ [6]

SA_DQ [7]

SA_DQ [8]

SA_DQ [9]

SA_DQ [10]

SA_DQ [11]

SA_DQ [12]

SA_DQ [13]

SA_DQ [14]

SA_DQ [15]

SA_DQ [16]

SA_DQ [17]

SA_DQ [18]

SA_DQ [19]

SA_DQ [20]

SA_DQ [21]

SA_DQ [22]

SA_DQ [23]

SA_DQ [24]

SA_DQ [25]

SA_DQ [26]

SA_DQ [27]

SA_DQ [28]

SA_DQ [29]

SA_DQ [30]

SA_DQ [31]

SA_DQ [32]

SA_DQ [33]

SA_DQ [34]

SA_DQ [35]

SA_DQ [36]

SA_DQ [37]

SA_DQ [38]

SA_DQ [39]

SA_DQ [40]

SA_DQ [41]

SA_DQ [42]

SA_DQ [43]

SA_DQ [44]

SA_DQ [45]

SA_DQ [46]

SA_DQ [47]

SA_DQ [48]

SA_DQ [49]

SA_DQ [50]

SA_DQ [51]

SA_DQ [52]

SA_DQ [53]

SA_DQ [54]

SA_DQ [55]

SA_DQ [56]

SA_DQ [57]

SA_DQ [58]

SA_DQ [59]

SA_DQ [60]

SA_DQ [61]

SA_DQ [62]

SA_DQ [63]

SA_BS[ 0]

SA_BS[ 1]

SA_BS[ 2]

SA_CAS #

SA_RAS #

SA_W E#

SA_CK[ 0]

SA_CK# [0]

SA_CKE [0]

SA_CK[ 1]

SA_CK# [1]

SA_CKE [1]

SA_CS# [0]

SA_CS# [1]

SA_OD T[0]

SA_OD T[1]

SA_DQ S#[0]

SA_DQ S#[1]

SA_DQ S#[2]

SA_DQ S#[3]

SA_DQ S#[4]

SA_DQ S#[5]

SA_DQ S#[6]

SA_DQ S#[7]

SA_DQ S[0]

SA_DQ S[1]

SA_DQ S[2]

SA_DQ S[3]

SA_DQ S[4]

SA_DQ S[5]

SA_DQ S[6]

SA_DQ S[7]

AU36

AV36

AY26

AT40

AU40

BB26

BB40

BC41

AY40

BA41

AL11

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW 45

AV51

AT56

AK54

M_A_DQ SN0

M_A_DQ SN1

M_A_DQ SN2

M_A_DQ SN3

M_A_DQ SN4

M_A_DQ SN5

M_A_DQ SN6

M_A_DQ SN7

M_A_DQ SP0

M_A_DQ SP1

M_A_DQ SP2

M_A_DQ SP3

M_A_DQ SP4

M_A_DQ SP5

M_A_DQ SP6

M_A_DQ SP7

M_A_CL KP0 12

M_A_CL KN0 12

M_A_CK E0 12

M_A_CL KP1 12

M_A_CL KN1 12

M_A_CK E1 12

M_A_CS #0 12

M_A_CS #1 12

M_A_OD T0 12

M_A_OD T1 12

M_A_DQ SN[7:0] 12

M_A_DQ SP[7:0] 12

DDR SYSTEM MEMORY A

SA_MA [0]

SA_MA [1]

SA_MA [2]

SA_MA [3]

SA_MA [4]

SA_MA [5]

SA_MA [6]

SA_MA [7]

SA_MA [8]

SA_MA [9]

SA_MA [10]

SA_MA [11]

SA_MA [12]

SA_MA [13]

SA_MA [14]

SA_MA [15]

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW 41

AY28

AU26

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A1 0

M_A_A1 1

M_A_A1 2

M_A_A1 3

M_A_A1 4

M_A_A1 5

M_A_A[1 5:0] 12

M_B_DQ [63:0]13

M_B_BS #013

M_B_BS #113

M_B_BS #213

M_B_CA S#13

M_B_RA S#13

M_B_W E#13

M_B_DQ 0

M_B_DQ 1

M_B_DQ 2

M_B_DQ 3

M_B_DQ 4

M_B_DQ 5

M_B_DQ 6

M_B_DQ 7

M_B_DQ 8

M_B_DQ 9

M_B_DQ 10

M_B_DQ 11

M_B_DQ 12

M_B_DQ 13

M_B_DQ 14

M_B_DQ 15

M_B_DQ 16

M_B_DQ 17

M_B_DQ 18

M_B_DQ 19

M_B_DQ 20

M_B_DQ 21

M_B_DQ 22

M_B_DQ 23

M_B_DQ 24

M_B_DQ 25

M_B_DQ 26

M_B_DQ 27

M_B_DQ 28

M_B_DQ 29

M_B_DQ 30

M_B_DQ 31

M_B_DQ 32

M_B_DQ 33

M_B_DQ 34

M_B_DQ 35

M_B_DQ 36

M_B_DQ 37

M_B_DQ 38

M_B_DQ 39

M_B_DQ 40

M_B_DQ 41

M_B_DQ 42

M_B_DQ 43

M_B_DQ 44

M_B_DQ 45

M_B_DQ 46

M_B_DQ 47

M_B_DQ 48

M_B_DQ 49

M_B_DQ 50

M_B_DQ 51

M_B_DQ 52

M_B_DQ 53

M_B_DQ 54

M_B_DQ 55

M_B_DQ 56

M_B_DQ 57

M_B_DQ 58

M_B_DQ 59

M_B_DQ 60

M_B_DQ 61

M_B_DQ 62

M_B_DQ 63

U20D IC,IVB_2C BGA,0P7

AL4

SB_DQ [0]

AL1

SB_DQ [1]

AN3

SB_DQ [2]

AR4

SB_DQ [3]

AK4

SB_DQ [4]

AK3

SB_DQ [5]

AN4

SB_DQ [6]

AR1

SB_DQ [7]

AU4

SB_DQ [8]

AT2

SB_DQ [9]

AV4

SB_DQ [10]

BA4

SB_DQ [11]

AU3

SB_DQ [12]

AR3

SB_DQ [13]

AY2

SB_DQ [14]

BA3

SB_DQ [15]

BE9

SB_DQ [16]

BD9

SB_DQ [17]

BD13

SB_DQ [18]

BF12

SB_DQ [19]

BF8

SB_DQ [20]

BD10

SB_DQ [21]

BD14

SB_DQ [22]

BE13

SB_DQ [23]

BF16

SB_DQ [24]

BE17

SB_DQ [25]

BE18

SB_DQ [26]

BE21

SB_DQ [27]

BE14

SB_DQ [28]

BG14

SB_DQ [29]

BG18

SB_DQ [30]

BF19

SB_DQ [31]

BD50

SB_DQ [32]

BF48

SB_DQ [33]

BD53

SB_DQ [34]

BF52

SB_DQ [35]

BD49

SB_DQ [36]

BE49

SB_DQ [37]

BD54

SB_DQ [38]

BE53

SB_DQ [39]

BF56

SB_DQ [40]

BE57

SB_DQ [41]

BC59

SB_DQ [42]

AY60

SB_DQ [43]

BE54

SB_DQ [44]

BG54

SB_DQ [45]

BA58

SB_DQ [46]

AW 59

SB_DQ [47]

AW 58

SB_DQ [48]

AU58

SB_DQ [49]

AN61

SB_DQ [50]

AN59

SB_DQ [51]

AU59

SB_DQ [52]

AU61

SB_DQ [53]

AN58

SB_DQ [54]

AR58

SB_DQ [55]

AK58

SB_DQ [56]

AL58

SB_DQ [57]

AG58

SB_DQ [58]

AG59

SB_DQ [59]

AM60

SB_DQ [60]

AL59

SB_DQ [61]

AF61

SB_DQ [62]

AH60

SB_DQ [63]

BG39

SB_BS[ 0]

BD42

SB_BS[ 1]

AT22

SB_BS[ 2]

AV43

SB_CAS #

BF40

SB_RAS #

BD45

SB_W E#

SB_CK[ 0]

SB_CK# [0]

SB_CKE [0]

SB_CK[ 1]

SB_CK# [1]

SB_CKE [1]

SB_CS# [0]

SB_CS# [1]

SB_OD T[0]

SB_OD T[1]

SB_DQ S#[0]

SB_DQ S#[1]

SB_DQ S#[2]

SB_DQ S#[3]

SB_DQ S#[4]

SB_DQ S#[5]

SB_DQ S#[6]

SB_DQ S#[7]

SB_DQ S[0]

SB_DQ S[1]

SB_DQ S[2]

SB_DQ S[3]

SB_DQ S[4]

SB_DQ S[5]

SB_DQ S[6]

SB_DQ S[7]

BA34

AY34

AR22

BA36

BB36

BF27

BE41

BE47

AT43

BG47

AL3

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

M_B_DQ SN0

M_B_DQ SN1

M_B_DQ SN2

M_B_DQ SN3

M_B_DQ SN4

M_B_DQ SN5

M_B_DQ SN6

M_B_DQ SN7

M_B_DQ SP0

M_B_DQ SP1

M_B_DQ SP2

M_B_DQ SP3

M_B_DQ SP4

M_B_DQ SP5

M_B_DQ SP6

M_B_DQ SP7

M_B_CL KP0 13

M_B_CL KN0 13

M_B_CK E0 13

M_B_CL KP1 13

M_B_CL KN1 13

M_B_CK E1 13

M_B_CS #0 13

M_B_CS #1 13

M_B_OD T0 13

M_B_OD T1 13

M_B_DQ SN[7:0] 13

M_B_DQ SP[7:0] 13

DDR SYSTEM MEMORY B

SB_MA [0]

SB_MA [1]

SB_MA [2]

SB_MA [3]

SB_MA [4]

SB_MA [5]

SB_MA [6]

SB_MA [7]

SB_MA [8]

SB_MA [9]

SB_MA [10]

SB_MA [11]

SB_MA [12]

SB_MA [13]

SB_MA [14]

SB_MA [15]

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A1 0

M_B_A1 1

M_B_A1 2

M_B_A1 3

M_B_A1 4

M_B_A1 5

M_B_A[1 5:0] 13

A A

PROJECT : VOLKS

PROJECT : VOLKS

PROJECT : VOLKS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Processor 2/5 (DDR3 I/F)

Processor 2/5 (DDR3 I/F)

NB5

NB5

5

4

3

2

NB5

Processor 2/5 (DDR3 I/F)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1A

1A

1A

3 37Wednesday, May 2 3, 2012

3 37Wednesday, May 2 3, 2012

3 37Wednesday, May 2 3, 2012

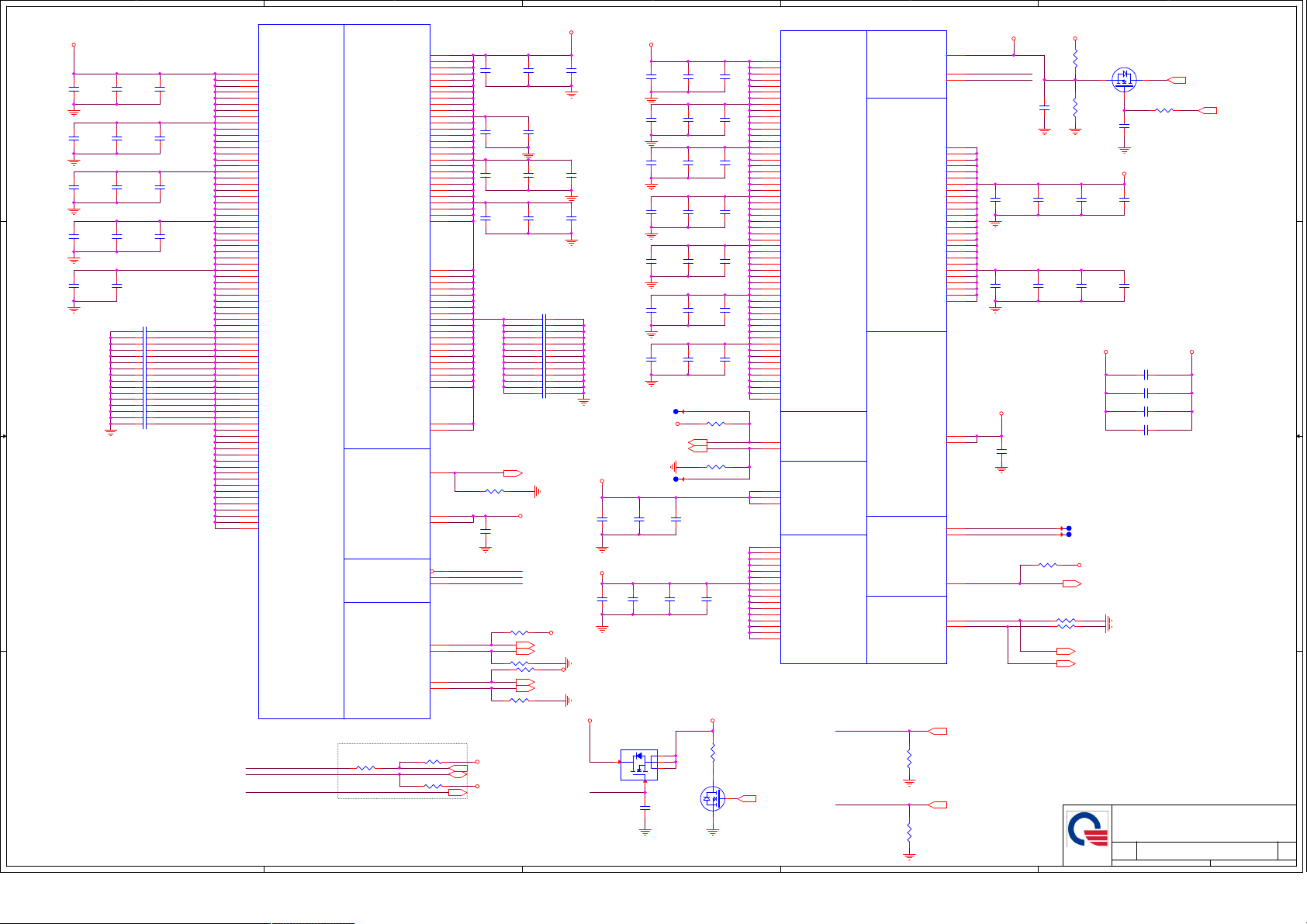

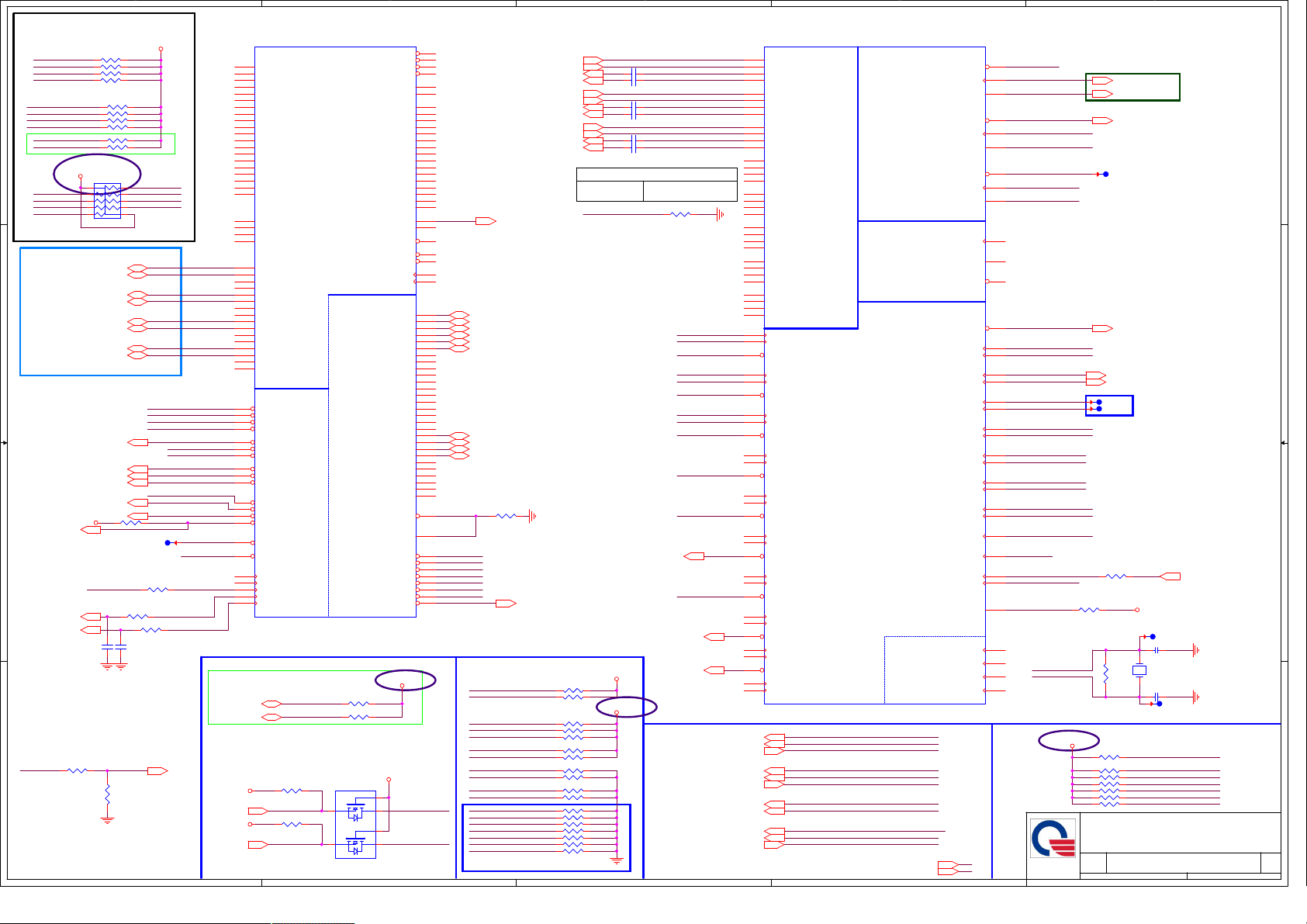

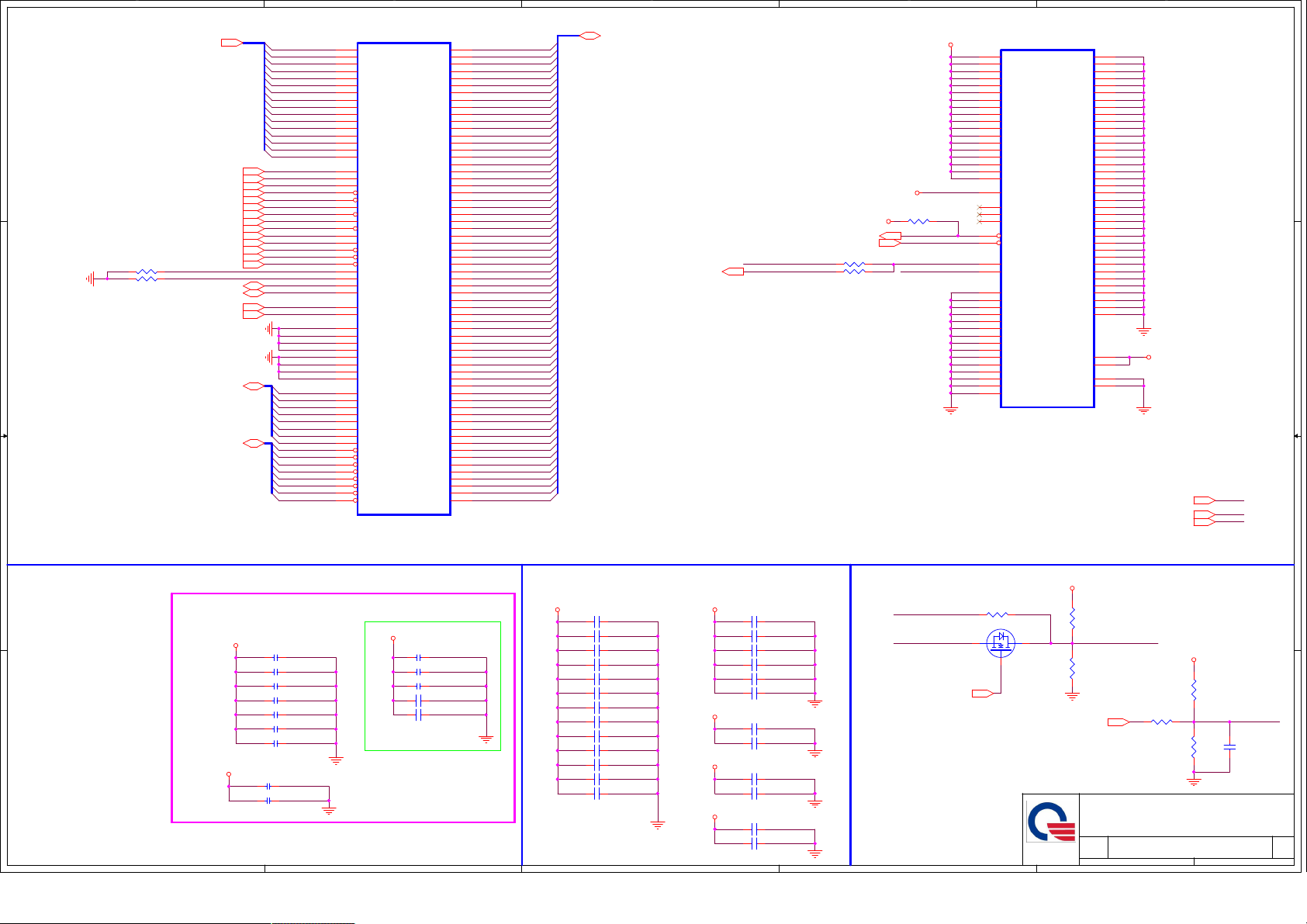

Page 4

5

U20F

+VCC_CORE

A26

VCC[1]

A29

VCC[2]

A31

VCC[3]

C585

22U/6.3VS_6

D D

C569

22U/6.3VS_6

C578

22U/6.3VS_6

C583

22U/6.3VS_6

C576

22U/6.3VS_6

C C

330uFx3pcs bulk B OT

22uFx14pcs ca vity BOT

2.2uFx16pcs B GA TOP

B B

A A

22U/6.3VS_6

22U/6.3VS_6

C586

22U/6.3VS_6

22U/6.3VS_6

C582

C587

22U/6.3VS_6

22U/6.3VS_6

C579

C581

22U/6.3VS_6

22U/6.3VS_6

C580

22U/6.3VS_6

C244 2.2U/6.3VS_4

C236 2.2U/6.3VS_4

C248 2.2U/6.3VS_4

C272 2.2U/6.3VS_4

C259 2.2U/6.3VS_4

C268 2.2U/6.3VS_4

C269 2.2U/6.3VS_4

C270 2.2U/6.3VS_4

C271 2.2U/6.3VS_4

C265 2.2U/6.3VS_4

C266 2.2U/6.3VS_4

C267 2.2U/6.3VS_4

C234 2.2U/6.3VS_4

C246 2.2U/6.3VS_4

C249 2.2U/6.3VS_4

C237 2.2U/6.3VS_4

5

C577

C584

A34

VCC[4]

A35

VCC[5]

A38

VCC[6]

A39

VCC[7]

A42

VCC[8]

C26

VCC[9]

C27

VCC[10]

C32

VCC[11]

C34

VCC[12]

C37

VCC[13]

C39

VCC[14]

C42

VCC[15]

D27

VCC[16]

D32

VCC[17]

D34

VCC[18]

D37

VCC[19]

D39

VCC[20]

D42

VCC[21]

E26

VCC[22]

E28

VCC[23]

E32

VCC[24]

E34

VCC[25]

E37

VCC[26]

E38

VCC[27]

F25

VCC[28]

F26

VCC[29]

F28

VCC[30]

F32

VCC[31]

F34

VCC[32]

F37

VCC[33]

F38

VCC[34]

F42

VCC[35]

G42

VCC[36]

H25

VCC[37]

H26

VCC[38]

H28

VCC[39]

H29

VCC[40]

H32

VCC[41]

H34

VCC[42]

H35

VCC[43]

H37

VCC[44]

H38

VCC[45]

H40

VCC[46]

J25

VCC[47]

J26

VCC[48]

J28

VCC[49]

J29

VCC[50]

J32

VCC[51]

J34

VCC[52]

J35

VCC[53]

J37

VCC[54]

J38

VCC[55]

J40

VCC[56]

J42

VCC[57]

K26

VCC[58]

K27

VCC[59]

K29

VCC[60]

K32

VCC[61]

K34

VCC[62]

K35

VCC[63]

K37

VCC[64]

K39

VCC[66]

K42

VCC[67]

L25

VCC[68]

L28

VCC[69]

L33

VCC[70]

L36

VCC[71]

L40

VCC[72]

N26

VCC[73]

N30

VCC[74]

N34

VCC[75]

N38

VCC[76]

IC,IVB_2CBGA,0P7

H_CPU_SVIDALRT#

VR_SVID_DATA

VR_SVID_CLK

POWER

CORE SUP PLY

R close to CPU

R394 43_4

4

VCCIO[1]

VCCIO[3]

VCCIO[4]

VCCIO[5]

VCCIO[6]

VCCIO[7]

VCCIO[8]

VCCIO[9]

VCCIO[10]

VCCIO[11]

VCCIO[12]

VCCIO[13]

VCCIO[14]

VCCIO[15]

VCCIO[16]

VCCIO[17]

VCCIO[18]

VCCIO[19]

VCCIO[20]

VCCIO[21]

VCCIO[22]

VCCIO[23]

VCCIO[24]

VCCIO[25]

VCCIO[26]

VCCIO[27]

VCCIO[28]

VCCIO[29]

VCCIO[30]

VCCIO[31]

VCCIO[32]

PEG IO AND D DR IO

VCCIO[33]

VCCIO[34]

VCCIO[35]

VCCIO[36]

VCCIO[37]

VCCIO[38]

VCCIO[39]

VCCIO[40]

VCCIO[41]

VCCIO[42]

VCCIO[43]

VCCIO[44]

VCCIO[45]

VCCIO[46]

VCCIO[47]

VCCIO[48]

VCCIO[49]

VCCIO50

VCCIO51

VCCIO_SE L

VCCPQE [1]

VCCPQE [2]

RAILS

VIDALERT #

VIDSCLK

VIDSOUT

VCC_SE NSE

VSS_SEN SE

VCCIO_SE NSE

VSS_SEN SE_VCCIO

SENSE L INES SVID QUIET

4

IVB:8.5A

AF46

AG48

AG50

AG51

AJ17

AJ21

AJ25

AJ43

AJ47

AK50

AK51

AL14

AL15

AL16

AL20

AL22

AL26

AL45

AL48

AM16

AM17

AM21

AM43

AM47

AN20

AN42

AN45

AN48

AA14

AA15

AB17

AB20

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

AM25

AN22

A44

B43

C44

100- ±1% pull-up to VCC near processor.

F43

G43

AN16

AN17

R378 75/F_4

R377 130/F_4

C311

1U/6.3V_4

C601

22U/6.3VS_6C573

C603

22U/6.3VS_6

C604

22U/6.3VS_6

330uFx2pcs bulk B OT

22uFx10pcs ca vity BOT

2.2uFx13pcs B GA TOP

R178 *1K/F_4

C300

1U/6.3V_4

H_CPU_SVIDALRT#

VR_SVID_CLK

VR_SVID_DATA

VCCP_SENSE

VSSP_SENSE

+1.05V

VR_SVID_ALERT# 34

VR_SVID_DATA 34

+1.05V

VR_SVID_CLK 34

R381 100/F_4

R380 100/F_4

R180 10/F_4

R179 10/F_4

+1.05V

C302

1U/6.3V_4

C602

22U/6.3VS_6

C313

22U/6.3VS_6

C597

22U/6.3VS_6

C295 1U/6.3V_4

C287 1U/6.3V_4

C288 1U/6.3V_4

C289 1U/6.3V_4

C290 1U/6.3V_4

C291 1U/6.3V_4

C293 1U/6.3V_4

C316 1U/6.3V_4

C315 1U/6.3V_4

C321 1U/6.3V_4

C312 1U/6.3V_4

C292 1U/6.3V_4

C322 1U/6.3V_4

H_VTTVID1 30

+1.05V

+VCC_CORE

VCC_SENSE 34

VSS_SENSE 34

+1.05V

VCCP_SENSE 30

VSSP_SENSE 30

3

+VCC_GFX

C303

1U/6.3V_4

C317

22U/6.3VS_6

C599

22U/6.3VS_6

+1.8V

22U/6.3VS_6

22U/6.3VS_6

22U/6.3VS_6

22U/6.3VS_6

1U/6.3V_4

1U/6.3V_4

1U/6.3V_4

C283

C256

C207

C206

C280

C262

C210

+VCC_GFX

VCC_AXG_SENSE34

VSS_AXG_SENSE34

C285

22U/6.3VS_6

C284

22U/6.3VS_6

C257

22U/6.3VS_6

C208

22U/6.3VS_6

C209

1U/6.3V_4

C299

1U/6.3V_4

C260

1U/6.3V_4

TP39

TP40

IVB: 1.5A

C609

C610

1U/6.3V_4

1U/6.3V_4

330uF x1, 10 uF_8 x1, 1uF_4 x2

+VCCSA

C238

10U/6.3V_6

C278

10U/6.3V_6

IVB: 6A

10U/6.3V_6

330uFx1, 10uF x4

Zo imp edance: 27.4ohm

Zo imp edance: 27.4ohm

Q11

AON7410

4

C620

*470P/50V_4

1

3

5 2

MAIND

CPU VDDQ

3

330uFx2pcs bulk B OT

22uFx12pcs ca vity BOT

1uFx12pcs BG A TOP

C205

22U/6.3VS_6

C304

22U/6.3VS_6

C286

22U/6.3VS_6

C258

22U/6.3VS_6

C281

1U/6.3V_4

C282

1U/6.3V_4

C261

1U/6.3V_4

C611

10U/6.3V_6

C276

C294

10U/6.3V_6

+1.5V_CPU+1.5VSUS

R462

220_8

3

2

Q32

2N7002K

1

R38210/F_4

R37910/F_4

U20G

AA46

VAXG[1]

AB47

VAXG[2]

AB50

VAXG[3]

AB51

VAXG[4]

AB52

VAXG[5]

AB53

VAXG[6]

AB55

VAXG[7]

AB56

VAXG[8]

AB58

VAXG[9]

AB59

VAXG[10]

AC61

VAXG[11]

AD47

VAXG[12]

AD48

VAXG[13]

AD50

VAXG[14]

AD51

VAXG[15]

AD52

VAXG[16]

AD53

VAXG[17]

AD55

VAXG[18]

AD56

VAXG[19]

AD58

VAXG[20]

AD59

VAXG[21]

AE46

VAXG[22]

N45

VAXG[23]

P47

VAXG[24]

P48

VAXG[25]

P50

VAXG[26]

P51

VAXG[27]

P52

VAXG[28]

P53

VAXG[29]

P55

VAXG[30]

P56

VAXG[31]

P61

VAXG[32]

T48

VAXG[33]

T58

VAXG[34]

T59

VAXG[35]

T61

VAXG[36]

U46

VAXG[37]

V47

VAXG[38]

V48

VAXG[39]

V50

VAXG[40]

V51

VAXG[41]

V52

VAXG[42]

V53

VAXG[43]

V55

VAXG[44]

V56

VAXG[45]

V58

VAXG[46]

V59

VAXG[47]

W50

VAXG[48]

W51

VAXG[49]

W52

VAXG[50]

W53

VAXG[51]

W55

VAXG[52]

W56

VAXG[53]

W61

VAXG[54]

Y48

VAXG[55]

Y61

VAXG[56]

F45

VAXG_SENS E

G45

VSSAXG_SE NSE

BB3

VCCPLL [1]

BC1

VCCPLL [2]

BC4

VCCPLL [3]

L17

VCCSA[1]

L21

VCCSA[2]

N16

VCCSA[3]

N20

VCCSA[4]

N22

VCCSA[5]

P17

VCCSA[6]

P20

VCCSA[7]

R16

VCCSA[8]

R18

VCCSA[9]

R21

VCCSA[10 ]

U15

VCCSA[11 ]

V16

VCCSA[12 ]

V17

VCCSA[13 ]

V18

VCCSA[14 ]

V21

VCCSA[15 ]

W20

VCCSA[16 ]

IC,IVB_2CBGA,0P7

MAIN_ONG 2,36

POWER

VREF

DDR3 - 1.5V RAILS

GRAPHI CS

SENSE

LINES

1.8V R AIL

SA RAI L

VCCSA V ID

SMDDR_VREF_DQ0_M3

SMDDR_VREF_DQ1_M3

2

SM_VRE F

SA_DIMM_ VREFDQ

SB_DIMM _VREFDQ

VDDQ[10 ]

VDDQ[11 ]

VDDQ[12 ]

VDDQ[13 ]

VDDQ[14 ]

VDDQ[15 ]

VDDQ[16 ]

VDDQ[17 ]

VDDQ[18 ]

VDDQ[19 ]

VDDQ[20 ]

VDDQ[21 ]

VDDQ[22 ]

VDDQ[23 ]

VDDQ[24 ]

VDDQ[25 ]

VDDQ[26 ]

VCCDQ[1 ]

VCCDQ[2 ]

QUIET R AILS

VDDQ_S ENSE

VSS_SEN SE_VDDQ

VCCSA_S ENSE

SENSE L INES

VCCSA_VID[ 0]

VCCSA_VID[ 1]

lines

R445

*1K/F_4

R446

*1K/F_4

2

AY43

BE7

BG7

AJ28

VDDQ[1]

AJ33

VDDQ[2]

AJ36

VDDQ[3]

AJ40

VDDQ[4]

AL30

VDDQ[5]

AL34

VDDQ[6]

AL38

VDDQ[7]

AL42

VDDQ[8]

AM33

VDDQ[9]

AM36

AM40

AN30

AN34

AN38

AR26

AR28

AR30

AR32

AR34

AR36

AR40

AV41

AW26

BA40

BB28

BG33

AM28

AN26

BC43

BA43

U10

D48

D49

SMDDR_VREF_DQ0_M3 12

SMDDR_VREF_DQ1_M3 13

+VDDR_REF_CPU +1.5V_CPU

SMDDR_VREF_DQ0_M3

SMDDR_VREF_DQ1_M3

20mils width

C619

0.1U/10V_4

IVB: 5A

C318

10U/6.3V_6

C320

10U/6.3V_6

CPU center

CRB: 1uf*1

+1.5V_CPU

C314

1U/6.3V_4

R127 *100/F_4

VCCSA_SEL0

VCCSA_SEL

C307

10U/6.3V_6

C308

10U/6.3V_6

TP28

TP27

R392 1K/F_4

R372 1K/F_4

VCCSA_SEL0 29

VCCSA_SEL 29

NB5

NB5

NB5

1

CAD Note: +VDDR_REF_CPU should

have 10 mil tra ce width

R454

1K/F_4

1

R449

1K/F_4

+VDDR_REF_CPU and DDR_VTTREF must use 10mils width

C305

10U/6.3V_6

C319

10U/6.3V_6

+VCCSA

VCCUSA_SENSE 29

2

C621

470P/50V_4

+1.5V_CPU

C309

10U/6.3V_6

C306

10U/6.3V_6

C332 0.1U/10V_4

C333 0.1U/10V_4

C331 0.1U/10V_4

C330 0.1U/10V_4

3

Q31

2N7002K

R455 3.3K/F_4

DDR_VTTREF 12,13,31

+1.5VSUS+1.5V_CPU

09

MAIND 36

Zo:55 ohm

PROJECT : VOLKS

PROJECT : VOLKS

PROJECT : VOLKS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Processor 3/4 (POWER)

Processor 3/4 (POWER)

Processor 3/4 (POWER)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

4 37Wednesday, May 23, 2012

4 37Wednesday, May 23, 2012

4 37Wednesday, May 23, 2012

1A

1A

1A

Page 5

5

4

3

2

1

U20H

A13

VSS[1]

A17

VSS[2]

A21

VSS[3]

A25

VSS[4]

A28

VSS[5]

A33

D D

C C

B B

A A

A37

A40

A45

A49

A53

A9

AA1

AA13

AA50

AA51

AA52

AA53

AA55

AA56

AA8

AB16

AB18

AB21

AB48

AB61

AC10

AC14

AC46

AC6

AD17

AD20

AD4

AD61

AE13

AE8

AF1

AF17

AF21

AF47

AF48

AF50

AF51

AF52

AF53

AF55

AF56

AF58

AF59

AG10

AG14

AG18

AG47

AG52

AG61

AG7

AH4

AH58

AJ13

AJ16

AJ20

AJ22

AJ26

AJ30

AJ34

AJ38

AJ42

AJ45

AJ48

AJ7

AK1

AK52

AL10

AL13

AL17

AL21

AL25

AL28

AL33

AL36

AL40

AL43

AL47

AL61

AM13

AM20

AM22

AM26

AM30

AM34

IC,IVB_2C BGA,0P7

VSS[6]

VSS[7]

VSS[8]

VSS[9]

VSS[10 ]

VSS[11 ]

VSS[12 ]

VSS[13 ]

VSS[14 ]

VSS[15 ]

VSS[16 ]

VSS[17 ]

VSS[18 ]

VSS[19 ]

VSS[20 ]

VSS[21 ]

VSS[22 ]

VSS[23 ]

VSS[24 ]

VSS[25 ]

VSS[26 ]

VSS[27 ]

VSS[28 ]

VSS[29 ]

VSS[30 ]

VSS[31 ]

VSS[32 ]

VSS[33 ]

VSS[34 ]

VSS[35 ]

VSS[36 ]

VSS[37 ]

VSS[38 ]

VSS[39 ]

VSS[40 ]

VSS[41 ]

VSS[42 ]

VSS[43 ]

VSS[44 ]

VSS[45 ]

VSS[46 ]

VSS[47 ]

VSS[48 ]

VSS[49 ]

VSS[50 ]

VSS[51 ]

VSS[52 ]

VSS[53 ]

VSS[54 ]

VSS[55 ]

VSS[56 ]

VSS[57 ]

VSS[58 ]

VSS[59 ]

VSS[60 ]

VSS[61 ]

VSS[62 ]

VSS[63 ]

VSS[64 ]

VSS[65 ]

VSS[66 ]

VSS[67 ]

VSS[68 ]

VSS[69 ]

VSS[70 ]

VSS[71 ]

VSS[72 ]

VSS[73 ]

VSS[74 ]

VSS[75 ]

VSS[76 ]

VSS[77 ]

VSS[78 ]

VSS[79 ]

VSS[80 ]

VSS[81 ]

VSS[82 ]

VSS[83 ]

VSS[84 ]

VSS[85 ]

VSS[86 ]

VSS[87 ]

VSS[88 ]

VSS[89 ]

VSS[90 ]

VSS

VSS[91 ]

VSS[92 ]

VSS[93 ]

VSS[94 ]

VSS[95 ]

VSS[96 ]

VSS[97 ]

VSS[98 ]

VSS[99 ]

VSS[10 0]

VSS[10 1]

VSS[10 2]

VSS[10 3]

VSS[10 4]

VSS[10 5]

VSS[10 6]

VSS[10 7]

VSS[10 8]

VSS[10 9]

VSS[11 0]

VSS[11 1]

VSS[11 2]

VSS[11 3]

VSS[11 4]

VSS[11 5]

VSS[11 6]

VSS[11 7]

VSS[11 8]

VSS[11 9]

VSS[12 0]

VSS[12 1]

VSS[12 2]

VSS[12 3]

VSS[12 4]

VSS[12 5]

VSS[12 6]

VSS[12 7]

VSS[12 8]

VSS[12 9]

VSS[13 0]

VSS[13 1]

VSS[13 2]

VSS[13 3]

VSS[13 4]

VSS[13 5]

VSS[13 6]

VSS[13 7]

VSS[13 8]

VSS[13 9]

VSS[14 0]

VSS[14 1]

VSS[14 2]

VSS[14 3]

VSS[14 4]

VSS[14 5]

VSS[14 6]

VSS[14 7]

VSS[14 8]

VSS[14 9]

VSS[15 0]

VSS[15 1]

VSS[15 2]

VSS[15 3]

VSS[15 4]

VSS[15 5]

VSS[15 6]

VSS[15 7]

VSS[15 8]

VSS[15 9]

VSS[16 0]

VSS[16 1]

VSS[16 2]

VSS[16 3]

VSS[16 4]

VSS[16 5]

VSS[16 6]

VSS[16 7]

VSS[16 8]

VSS[16 9]

VSS[17 0]

VSS[17 1]

VSS[17 2]

VSS[17 3]

VSS[17 4]

VSS[17 5]

VSS[17 6]

VSS[17 7]

VSS[17 8]

VSS[17 9]

VSS[18 0]

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP10

AP51

AP55

AP7

AR13

AR17

AR21

AR41

AR48

AR61

AR7

AT14

AT19

AT36

AT4

AT45

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW 13

AW 43

AW 61

AW 7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

U20I

BG17

BG21

BG24

BG28

BG37

BG41

BG45

BG49

BG53

BG9

C29

C35

C40

D10

D14

D18

D22

D26

D29

D35

D4

D40

D43

D46

D50

D54

D58

D6

E25

E29

E3

E35

E40

F13

F15

F19

F29

F35

F40

F55

G51

G6

G61

H10

H14

H17

H21

H4

H53

H58

J1

J49

J55

K11

K21

K51

K8

L16

L20

L22

L26

L30

L34

L38

L43

L48

L61

M11

M15

IC,IVB_2C BGA,0P7

VSS[18 1]

VSS[18 2]

VSS[18 3]

VSS[18 4]

VSS[18 5]

VSS[18 6]

VSS[18 7]

VSS[18 8]

VSS[18 9]

VSS[19 0]

VSS[19 1]

VSS[19 2]

VSS[19 3]

VSS[19 4]

VSS[19 5]

VSS[19 6]

VSS[19 7]

VSS[19 8]

VSS[19 9]

VSS[20 0]

VSS[20 1]

VSS[20 2]

VSS[20 3]

VSS[20 4]

VSS[20 5]

VSS[20 6]

VSS[20 7]

VSS[20 8]

VSS[20 9]

VSS[21 0]

VSS[21 1]

VSS[21 2]

VSS[21 3]

VSS[21 4]

VSS[21 5]

VSS[21 6]

VSS[21 7]

VSS[21 8]

VSS[21 9]

VSS[22 0]

VSS[22 1]

VSS[22 2]

VSS[22 3]

VSS[22 4]

VSS[22 5]

VSS[22 6]

VSS[22 7]

VSS[22 8]

VSS[22 9]

VSS[23 0]

VSS[23 1]

VSS[23 2]

VSS[23 3]

VSS[23 4]

VSS[23 5]

VSS[23 6]

VSS[23 7]

VSS[23 8]

VSS[23 9]

VSS[24 0]

VSS[24 1]

VSS[24 2]

VSS[24 3]

VSS[24 4]

VSS[24 5]

VSS[24 6]

VSS[24 7]

VSS[24 8]

VSS[24 9]

M4

VSS[25 0]

M58

VSS[25 1]

M6

VSS[25 2]

N1

VSS[25 3]

N17

VSS[25 4]

N21

VSS[25 5]

N25

VSS[25 6]

N28

VSS[25 7]

N33

VSS[25 8]

N36

VSS[25 9]

N40

VSS[26 0]

N43

VSS[26 1]

N47

VSS[26 2]

N48

VSS[26 3]

N51

VSS[26 4]

N52

VSS[26 5]

N56

VSS[26 6]

N61

VSS[26 7]

P14

VSS[26 8]

P16

VSS[26 9]

P18

CDPTR

VSS

VSS[27 0]

VSS[27 1]

VSS[27 2]

VSS[27 3]

VSS[27 4]

VSS[27 5]

VSS[27 6]

VSS[27 7]

VSS[27 8]

VSS[27 9]

VSS[28 0]

VSS[28 1]

VSS[28 2]

VSS[28 3]

VSS[28 4]

VSS[28 5]

VSS[28 6]

VSS[28 7]

VSS[28 8]

VSS[28 9]

VSS[29 0]

VSS[29 1]

VSS[29 2]

VSS[29 3]

VSS[29 4]

VSS[29 5]

VSS[29 6]

VSS[29 7]

VSS[29 8]

VSS[29 9]

VSS[30 0]

VSS_NC TF_1

VSS_NC TF_2

VSS_NC TF_3

VSS_NC TF_4

VSS_NC TF_5

VSS_NC TF_6

VSS_NC TF_7

VSS_NC TF_8

VSS_NC TF_9

VSS_NC TF_10

VSS_NC TF_11

NCTF

VSS_NC TF_12

VSS_NC TF_13

VSS_NC TF_14

P21

P58

P59

P9

R17

R20

R4

R46

T1

T47

T50

T51

T52

T53

T55

T56

U13

U8

V20

V61

W1 3

W1 5

W1 8

W2 1

W4 6

W8

Y4

Y47

Y58

Y59

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

Processor Strapping

CFG2

(PCIe Sta tic x16 Lane Numbering Rev ersal.)

CFG4

(DP Pres ence Strap)

CFG7

(PEG Defer Training)

CFG2

TP4

+VCC_C ORE

TP14

TP15

TP6

TP5

CFG3

CFG4

CFG5

CFG6

CFG7

R119*49.9/F_4

R120*49.9/F_4

CFG[6:5] (PCIE P ort Bifurcation S traps)

11: ( Defau lt) x 16 - Devi ce 1 funct ions 1 and 2 di sabled

10: x 8, x8 - De vice 1 fu nctio n 1 e nable d ; f uncti on 2 disab led

01: R eserv ed - (Dev ice 1 func tion 1 dis abled ; fu nction 2 e nable d)

00: x 8,x4, x4 - Devi ce 1 funct ions 1 and 2 en abled

The CFG signals hav e a default v alue of '1 ' if not ter minated on the board.

1 0

Normal O peration (Default) Lane Reversed

Disable ; No phys ical DP attached to eDP

PEG train immediately following

xxRESE TB de assertion

Enable; An ext DP device is connecte d to eDP

PEG wa it for BIO S training

U20E

B50

CFG[0]

C51

CFG[1]

B54

CFG[2]

D53

CFG[3]

A51

CFG[4]

C53

CFG[5]

C55

CFG[6]

H49

CFG[7]

A55

CFG[8]

H51

CFG[9]

K49

CFG[10 ]

K53

CFG[11 ]

F53

CFG[12 ]

G53

CFG[13 ]

L51

CFG[14 ]

F51

CFG[15 ]

D52

CFG[16 ]

L53

CFG[17 ]

H43

VCC_VA L_SENSE

K43

VSS_VA L_SENSE

H45

VAXG_V AL_SENSE

K45

VSSAXG _VAL_SENS E

F48

VCC_D IE_SENSE

G48

RSVD47

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

IC,IVB_2C BGA,0P7

RESERVED

BCLK_IT P

BCLK_IT P#

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

DC_TES T_A4

DC_TES T_C4

DC_TES T_D3

DC_TES T_D1

DC_TES T_A58

DC_TES T_A59

DC_TES T_C59

DC_TES T_A61

DC_TES T_C61

DC_TES T_D61

DC_TES T_BD61

DC_TES T_BE61

DC_TES T_BE59

DC_TES T_BG61

DC_TES T_BG59

DC_TES T_BG58

DC_TES T_BG4

DC_TES T_BG3

DC_TES T_BE3

DC_TES T_BG1

DC_TES T_BE1

DC_TES T_BD1

CFG2

CFG4

CFG7

N59

N58

N42

L42

L45

L47

M13

M14

U14

W1 4

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

CFG5

R390 1K/F_4

CFG6

R389 *1K/F_4

R370 *1K/F_4

R391 *1K/F_4

R371 *1K/F_4

11

TP12

TP13

TP37

TP38

TP45

TP44

TP42

TP43

PROJECT : VOLKS

PROJECT : VOLKS

PROJECT : VOLKS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Processor 4/4 (RSV,Ground)

Processor 4/4 (RSV,Ground)

NB5

NB5

5

4

3

2

NB5

Processor 4/4 (RSV,Ground)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

1A

1A

1A

5 37Wednesday, May 2 3, 2012

5 37Wednesday, May 2 3, 2012

5 37Wednesday, May 2 3, 2012

Page 6

5

4

3

2

1

Cougar Point/Panther Point (DMI,FDI,PM)

U18C

CPT_PP T_Rev_0p7

DMI_RX N02

DMI_RX N12

DMI_RX N22

DMI_RX N32

DMI_RX P02

D D

for DS3

SUSAC K#_EC25

C C

XDP_DB RST#2

IMVP_PW RGD

EC_PW ROK21,25

for DS3

SUSW ARN#_EC25

for DS3

B B

PCH Pull-high/low(CLG)

PM_RI#

PM_BAT LOW#

PCIE_W AKE#

SLP_LAN #

SUSW ARN#

SUS_PW R_ACK

AC_PRE SENT_R

A A

CLKRUN #

XDP_DB RST#

RSMRS T#

IMVP_PW RGD

DMI_RX P12

DMI_RX P22

DMI_RX P32

DMI_TXN 02

DMI_TXN 12

DMI_TXN 22

DMI_TXN 32

DMI_TXP 02

DMI_TXP 12

DMI_TXP 22

DMI_TXP 32

+1.05V

R536 *0_4

R521 0_4

PM_DR AM_PWRG D2

RSMRS T#25

DNBSW ON#25

for DS3

R411 10K/F_4

R155 8.2K_4

R412 10K/F_4

R142 *10K/F_4

R528 *10K/F_4

R404 *10K/F_4

R421 8.2K_4

R435 1K/F_4

R436 *1K/F_4

R123 10K/F_4

R170 *100K/F_4

R399 49.9/F_4

R401 750/F_4

SUS_PW R_ACKSUSW ARN#

SUS_PW R_ACK

C323 *1U/6.3V_4

R522 0_4

R523 0_4

+3V_DE EP_SUS

INTEL DG

+3VS5

+3V

INTEL DG

5

DMI_COM P

DMI_RB IAS

XDP_DB RST#

EC_PW ROK

EC_PW ROK

RSMRS T#

SUSW ARN#

DNBSW ON#

AC_PRE SENT_R

PM_BAT LOW#

PM_RI#

BC24

BE20

BG18

BG20

BE24

BC20

BJ18

BJ20

AW 24

AW 20

BB18

AV18

AY24

AY20

AY18

AU18

BJ24

BG25

BH21

C12

K3

P12

L22

L10

B13

C21

K16

E20

H20

E10

A10

for DS3

SLP_SU S#_OFF25

DMI0RX N

DMI1RX N

DMI2RX N

DMI3RX N

DMI0RX P

DMI1RX P

DMI2RX P

DMI3RX P

DMI0TX N

DMI1TX N

DMI2TX N

DMI3TX N

DMI0TX P

DMI1TX P

DMI2TX P

DMI3TX P

DMI_ZC OMP

DMI_IRC OMP

DMI2RB IAS

SUSAC K#

SYS_RE SET#

SYS_PW ROK

PW ROK

APW ROK

DRAMP WROK

RSMRS T#

(+3VS5)

SUSW ARN#/SU SPWRD NACK/GPIO 30

PW RBTN#

(DSW)

ACPRE SENT / GP IO31

(+3VS5)

BATLOW # / G PIO72

RI#

C702

1U/6.3V_4

SLP_SU S#_OFF

R530

100K/F_4

DMI

CLKRU N# / GPIO32

SUS_ST AT# / GPIO 61

System Powe r Management

SLP_LAN # / GPIO29

U25

5

IN

4

IN

3

ON/OF F

IC(5P) G5243 AT11U

FDI

FDI_FSY NC0

FDI_FSY NC1

FDI_LSY NC0

FDI_LSY NC1

DSW VRMEN

SUSCLK / GPIO62

SLP_S5# / GPIO63

R525 *0_6

R527 *0_6

4

FDI_RXN 0

FDI_RXN 1

FDI_RXN 2

FDI_RXN 3

FDI_RXN 4

FDI_RXN 5

FDI_RXN 6

FDI_RXN 7

FDI_RXP 0

FDI_RXP 1

FDI_RXP 2

FDI_RXP 3

FDI_RXP 4

FDI_RXP 5

FDI_RXP 6

FDI_RXP 7

FDI_INT

DPW ROK

WA KE#

(+3V)

(+3VS5)

(+3VS5)

(+3VS5)

SLP_S4#

SLP_S3#

SLP_A#

SLP_SU S#

PMSYN CH

(+3VS5)

BJ14

AY14

BE14

BH13

BC12

BJ12

BG10

BG9

BG14

BB14

BF14

BG13

BE12

BG12

BJ10

BH9

AW 16

AV12

BC10

AV14

BB10

A18

DSWV REN

E22

DPWR OK RSMRS T#

B9

PCIE_W AKE#

N3

CLKRUN #

G8

SUS_SA TA#

N14

PCH_SU SCLK_L

D10

H4

F4

G10

G16

SLP_SU S#

AP14

K14

SLP_LAN #

+3V_DE EP_SUS+3VS5

1

OUT

2

GND

C704

0.1U/10V_ 4

R535 0_4

R534 *0_4

PCIE_W AKE# 2 0,23,25

CLKRUN # 25

R151 *0_4/S

SLP_S5 25

SUSC# 25

SUSB# 2 5

R524 0_4

PM_SYNC 2

FDI_TXN 0 2

FDI_TXN 1 2

FDI_TXN 2 2

FDI_TXN 3 2

FDI_TXN 4 2

FDI_TXN 5 2

FDI_TXN 6 2

FDI_TXN 7 2

FDI_TXP 0 2

FDI_TXP 1 2

FDI_TXP 2 2

FDI_TXP 3 2

FDI_TXP 4 2

FDI_TXP 5 2

FDI_TXP 6 2

FDI_TXP 7 2

FDI_INT 2

FDI_FSYNC 0 2

FDI_FSYNC 1 2

FDI_LSYNC 0 2

FDI_LSYNC 1 2

DPWR OK_EC

TP21

TP25

TP23

SLP_SU S#_EC

DPWR OK_EC 25

PCH_SU SCLK 25

for DS3

C701

1U/6.3V_4

SLP_SU S#_OFF

3

SLP_SU S#_EC 25AC_PRE SENT_EC25

+5VS5

R529

*100K/F_4

PCH_LV DS_BLON26

PCH_DIS P_ON26

PCH_DP ST_PWM26

PCH_ED IDCLK26

PCH_ED IDDATA26

+3V

PCH_LA _CLK#26

PCH_LA _CLK26

PCH_LA _DATAN026

PCH_LA _DATAN126

PCH_LA _DATAN226

PCH_LA _DATAP026

PCH_LA _DATAP126

PCH_LA _DATAP226

for DS3

U26

5

IN

4

IN

3

ON/OF F

IC(5P) G5243 AT11U

Cougar Point/Panther Point (LVDS,DDI)

U18D

CPT_PP T_Rev_0p7

J47

R98 2.2K_4

R101 2.2K_4

R103 2.37K/F_4

+3VS510,23,28,30,3 3,36

+1.05V2,4,7,8,10,21,2 3,30,33,34

+3VPCU7,21,22,23,24 ,25,26,27,28

+3V_RTC7,10,23

R526 *0_4

PCH_LA _CLK#

PCH_LA _CLK

PCH_LA _DATAN0

PCH_LA _DATAN1

PCH_LA _DATAN2

PCH_LA _DATAP0

PCH_LA _DATAP1

PCH_LA _DATAP2

+3V7,8,9,10,12,13 ,14,16,19,20,21,22,23,2 4,25,26,30,32,34,36

OUT

GND

PCH_ED IDCLK

PCH_ED IDDATA

CTRL_C LK

CTRL_D ATA

LVD_IBG

1

2

TP11

+5V_DE EP_SUS

C703

0.1U/10V_ 4R126 *10K/F_4

DAC_IRE F

R100

1K/F_4

M45

AF37

AF36

AE48

AE47

AK39

AK40

AN48

AM47

AK47

AJ48

AN47

AM49

AK49

AJ47

AF40

AF39

AH45

AH47

AF49

AF45

AH43

AH49

AF47

AF43

N48

M40

M47

M49

P45

T40

K47

T45

P39

P49

T49

T39

T43

T42

2

L_BKLTE N

L_VDD_ EN

L_BKLTC TL

L_DDC_ CLK

L_DDC_ DATA

L_CTRL _CLK

L_CTRL _DATA

LVD_IBG

LVD_VB G

LVD_VR EFH

LVD_VR EFL

LVDSA_ CLK#

LVDSA_ CLK

LVDSA_ DATA#0

LVDSA_ DATA#1

LVDSA_ DATA#2

LVDSA_ DATA#3

LVDSA_ DATA0

LVDSA_ DATA1

LVDSA_ DATA2

LVDSA_ DATA3

LVDSB_ CLK#

LVDSB_ CLK

LVDSB_ DATA#0

LVDSB_ DATA#1

LVDSB_ DATA#2

LVDSB_ DATA#3

LVDSB_ DATA0

LVDSB_ DATA1

LVDSB_ DATA2

LVDSB_ DATA3

CRT_BL UE

CRT_G REEN

CRT_RE D

CRT_DD C_CLK

CRT_DD C_DATA

CRT_HS YNC

CRT_VS YNC

DAC_IRE F

CRT_IRT N

+3V_RTC

LVDS

CRT

On Die DSW VR En able

High = Enable ( Default)

Low = Disabl e

SDVO_ TVCLKINN

SDVO_ TVCLKINP

SDVO_ CTRLCLK

SDVO_ CTRLDATA

DDPC_ CTRLCLK

DDPC_ CTRLDATA

Digital Dis play Interface

DDPD_ CTRLCLK

DDPD_ CTRLDATA

R131 330K_4

NB5

NB5

NB5

SDVO_ STALLN

SDVO_ STALLP

SDVO_ INTN

SDVO_ INTP

DDPB_A UXN

DDPB_A UXP

DDPB_H PD

DDPB_0 N

DDPB_0 P

DDPB_1 N

DDPB_1 P

DDPB_2 N

DDPB_2 P

DDPB_3 N

DDPB_3 P

DDPC_ AUXN

DDPC_ AUXP

DDPC_ HPD

DDPC_ 0N

DDPC_ 0P

DDPC_ 1N

DDPC_ 1P

DDPC_ 2N

DDPC_ 2P

DDPC_ 3N

DDPC_ 3P

DDPD_ AUXN

DDPD_ AUXP

DDPD_ HPD

DDPD_ 0N

DDPD_ 0P

DDPD_ 1N

DDPD_ 1P

DDPD_ 2N

DDPD_ 2P

DDPD_ 3N

DDPD_ 3P

DSWV REN

AP43

AP45

AM42

AM40

AP39

AP40

P38

M39

AT49

AT47

AT40

AV42

AV40

AV45

AV46

AU48

AU47

AV47

AV49

P46

P42

AP47

AP49

AT38

AY47

AY49

AY43

AY45

BA47

BA48

BB47

BB49

M43

M36

AT45

AT43

BH41

BB43

BB45

BF44

BE44

BF42

BE42

BJ42

BG42

SDVO_C LK

SDVO_D ATA

HDMI_H PD_CON

IN_D2#

IN_D2

IN_D1#

IN_D1

IN_D0#

IN_D0

IN_CLK#

IN_CLK

06

SDVO_C LK 26

SDVO_D ATA 26

INT. HDMI

HDMI_H PD_CON 26

IN_D2# 26

IN_D2 26

IN_D1# 26

IN_D1 26

IN_D0# 26

IN_D0 26

IN_CLK# 26

IN_CLK 26

System PWR_OK(CLG)

IMVP_PW RGD

EC_PW ROK

PROJECT : VOLKS

PROJECT : VOLKS

PROJECT : VOLKS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

PCH 1/6 (Host/Display)

PCH 1/6 (Host/Display)

PCH 1/6 (Host/Display)

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

R165

100K/F_4

IMVP_PW RGD 34

6 37Wednesday, May 2 3, 2012

6 37Wednesday, May 2 3, 2012

6 37Wednesday, May 2 3, 2012

1A

1A

1A

Page 7

5

Cougar Point/Panther Point (HDA,JTAG,SATA)

RTC_RS T#

SRTC_R ST#

SM_INTR UDER#

PCH_INV RMEN

ACZ_BC LK

ACZ_SYNC

SPKR

ACZ_RS T#

ACZ_SD OUT

R116 0_4

PCH_SP I_CS0#

PCH_SP I_CS1#

RTC_X1

RTC_X2

GPIO33

PCH_SP I_SI

PCH_SP I_SO

CLKGEN _RTC_X123

D D

+3V_RTC

for DS3

+3V_DE EP_SUS

C C

SIO_EXT_ SCI#25

R99 0_4

R121 1 M_4

SPKR19

ACZ_SD IN019

GPIO33_E25

BIOS_W P#

R110 10K/F_4

SIO_EXT_ SCI#

U18A

CPT_PP T_Rev_0p7

A20

RTCX1

C20

RTCX2

D20

RTCRS T#

G22

SRTCR ST#

K22

INTRUD ER#

C17

INTVRM EN

N34

HDA_BC LK

L34

HDA_SY NC

T10

SPKR

K34

HDA_R ST#

E34

HDA_SD IN0

G34

HDA_SD IN1

C34

HDA_SD IN2

A34

HDA_SD IN3

A36

HDA_SD O

(+3V)

C36

HDA_D OCK_EN# / GPIO33

(+3VS5)

N32

HDA_D OCK_RST# / GPIO13

J3

JTAG_ TCK

H7

JTAG_ TMS

K5

JTAG_ TDI

H1

JTAG_ TDO

T3

SPI_CLK

Y14

SPI_CS0 #

T1

SPI_CS1 #

V4

SPI_MO SI

U3

SPI_MISO

JTAG

ph

B B

PCH Strap Table

Pin Nam e Strap de scription Sampled Configuration

SPKR

GNT3# / GPIO55 Top-Block Swap Ov erride

No reboot mode set ting PWRO K

PWRO K

INTVRME N Integrated 1.05V VRM ena ble ALWA YS Should be always pull-up

HDA_DOCK _EN#/GP IO33

GNT1# / GPIO51

GPIO19

Different f rom

Calpella

GNT2# / GPIO53

NV_ALE

NV_CLE

A A

HDA_SYN C On-Die P LL VR Voltage Select RSMRST

Flash Des criptor Security

Only for Int erposer

Boot BI OS Selection 1 [ bit-1]

Boot BI OS Selec tion 0 [bit-0]

ESI st rap (Serv er only)

Intel Ant i-Theft HDD protect ion

Only for Int erposer

DMI Termination volta ge weak pull-down 20kohm

PWRO K

PWRO K

PWRO K

PWRO K

PWRO K 0 = Dis able (Intern al pull-down 20kohm)

PWRO K

HDA_SDO PWRO KFlash Descriptor Security

GPIO8

GPIO28

Different f rom

Calpella

Integrated Clock Chip Enable Should be pull-down (weak pull-up 20K)RSMRST#

On-die PLL Voltage Regulator RSMRST#

SPI_MOSI iTPM function D isable APW ROK

5

4

FW H0 / LAD0

FW H1 / LAD1

FW H2 / LAD2

FW H3 / LAD3

LPC

FW H4 / LFRAM E#

LDRQ0#

LDRQ1# / GPIO23

RTCIHDA

SPI

(+3V)

SERIRQ

SATA0R XN

SATA0R XP

SATA0T XN

SATA0T XP

SATA1R XN

SATA1R XP

SATA 6 G

SATA1T XN

SATA1T XP

SATA2R XN

SATA2R XP

SATA2T XN

SATA2T XP

SATA3R XN

SATA3R XP

SATA3T XN

SATA3T XP

SATA4R XN

SATA4R XP

SATA4T XN

SATA

SATA4T XP

SATA5R XN

SATA5R XP

SATA5T XN

SATA5T XP

SATAICO MPO

SATAICO MPI

SATA3R COMPO

SATA3C OMPI

SATA3R BIAS

SATALE D#

(+3V)

SATA0G P / GPIO21

(+3V)

SATA1G P / GPIO19

0 = Default (weak pull-down 20K)

1 = Set ting to No -Reboot mo de

0 = "top-block swap" mode

1 = Default (weak pull-up 20K)

0 = Ov erride

1 = Default (weak pull-up 20K)

GNT0#GNT1#

11

00

Should not be pull-down

(weak pull-up 20K)

0 = Support b y 1.8V (weak pull-down)

1 = Support b y 1.5V

0 = Ov erride

1 = Default (weak pull-up 20K)

0 = Disable

1 = Ena ble (Default)

0 = Default (weak pull-down 20K)

1 = Ena ble

4

C38

A38

B37

C37

D36

E36

PCH_DR Q#0

K36

PCH_DR Q#1

V5

SERIRQ

AM3

SATA_R XN0

AM1

SATA_R XP0

AP7

SATA_T XN0

AP5

SATA_T XP0

AM10

SATA_R XN1

AM8

SATA_R XP1

AP11

SATA_T XN1

AP10

SATA_T XP1

AD7

AD5

DG recom mended that SATA AC coupling capacitors s hould be

AH5

close to the connector (< 100 mils) fo r optimal signal quality.

AH4

AB8

AB10

AF3

AF1

Y7

Y5

AD3

AD1

Y3

Y1

AB3

AB1

Y11

Y10

SATA_C OMP

AB12

AB13

SATA3_C OMP

AH1

SATA3_R BIASPCH_SP I_CLK

P3

V14

P1

BBS_BIT 0

R433 *10K/F_4

LAD0 23,2 5

LAD1 23,2 5

LAD2 23,2 5

LAD3 23,2 5

LFRAME # 23,25

TP10

R168 8.2K_4

R139 37.4/F_4

R136 49.9/F_4

R417 750/F_4

R432 10K/F_4

R143 10K/F_4

+3V

SATA_R XN0 24

SATA_R XP0 24

SATA_T XN0 24

SATA_T XP0 24

SATA_R XN1 24

SATA_R XP1 24

SATA_T XN1 24

SATA_T XP1 24

Circuit

R152 *1K/F_4

+3V

R363 *1K/F_4

R364 10K/F_4

+3V

R122 330K_4

GPIO33

[Need ext ernal pull -down for LP C BIOS]

Default weak pull-up on GNT0/1#

R419 * 1K/F_4

R354 * 1K/F_4

Boot Locat ion

SPI

LPC

+3V_RTC

USE GPIO PIN

R416 *1K/F_4

+1.8V

R415 2.2K_4

+1.8V

for DS3

+3V_DE EP_SUS

+3V_DE EP_SUS

R105 *1K/F_4

3

TP9

+3V

SERIRQ 25

HDD0 (SATA3 6.0Gb/s)

mSATA (SATA4 3Gb/s)

+1.05V

SATA_LE D# 24

+3V

PCI_GNT3 # 8

PCH_INV RMEN

R104 *1K/F_4

R414 1K/F_4

ACZ_SD OUT

3

SPKR

ACZ_SD OUT

BBS_BIT 0

R135 1 K/F_4

ACZ_SD OUT 25

BBS_BIT 1 8

NV_ALE 8

NV_CLE 9

H_SNB_ IVB# 2

ACZ_SYNC

2

RTC Clock 32.768KHz

C592 * 18P/50V_4

C593 * 18P/50V_4

23

Y6

*32.768KH Z

4 1

no stuff If use green Clock

RTC Circuitry(RTC)

+3V_RTC _0

+3V_RTC _0

12

CN18

BAT_CON N

RTC Pow er trace width 20mils.

+3VPCU

R473 *1K/F_4

+3V_RTC _1

D20

*BAT54C

HDA Bus(CLG)

R133 10K/F_4

1M_4

PCH_SP I_CS0#_R

PCH_SP I1_CLK_R

PCH_SP I1_SO_R

C622

22P/50V_4

NB5

NB5

NB5

ACZ_RS T#

ACZ_SD OUT

ACZ_BC LK

1

C310

U22

1

6

5

2

3

EN25Q32 B-104HIP

AKE39ZN 0Q02

BIOS_W P#

PROJECT : VOLKS

PROJECT : VOLKS

PROJECT : VOLKS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

R106 33_4

R109 33_4

R107 33_4

C219

+5V

R148 33_4

R140

P/N

AKE39ZN0Q02 (EN25Q32B-104 HIP)

AKE39FP 0Z02 (MX25L3206EM2I-12G)MX

ACZ_SD OUT_AUDIO19

ACZ_SYNC _AUDIO19

Vender

EON

ACZ_RS T#_AUDIO19

BIT_CLK _AUDIO19

*10P/50V_ 4

Size

4MB

4MB

AMIC 4MB AKE39 F-0800 (A2 5LQ32AM -F/Q)

Socket

PCH_SP I_CS1#

PCH_SP I_CS0#

PCH_SP I_CLK

PCH_SP I_SI P CH_SPI1_SI_R

PCH_SP I_SO

+3V 6,8,9,10,12,13,1 4,16,19,20,21,22,23,2 4,25,26,30,32,34,36

+5V 10,19,21,22,23 ,24,26,36

+1.8V 4,10,3 1

+1.05V 2,4,6 ,8,10,21,23,30,33,34

+3VS5 6,10,23,28 ,30,33,36

+3VPCU 21,22,23,2 4,25,26,27,28

+3V_RTC 6,10,23

2

DFHS08F S023

R452 *0_4

R457 0_4

R453 0_4

R450 0_4

R451 0_4

R456 3 .3K_4

+3V

1

RTC_X1

R400

*10M_4

RTC_X2

30mils

+3V_RTC

2

R472

20K/F_4

R471

20K/F_4

C625

1U/6.3V_4

Q9

2N7002K

10P/50V_4

R115 *0_6

3

ACZ_SYNCACZ_SYNC _R1

C627

1U/6.3V_4

C626

1U/6.3V_4

SRTC_R ST#RTC_RS T#

RTC_RS T#

SRTC_R ST#

PCH SPI ROM(CLG)

+3V

CE#

SCK

SI

SO

WP #

8

VDD

7

R474 3.3K_4

HOLD#

4

VSS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PCH 2/6 (HDA/RTC/SATA/SPI)

PCH 2/6 (HDA/RTC/SATA/SPI)

PCH 2/6 (HDA/RTC/SATA/SPI)

C629

0.1U/10V_ 4

1

07

7 37Wednesday, May 2 3, 2012

7 37Wednesday, May 2 3, 2012

7 37Wednesday, May 2 3, 2012

1A

1A

1A

Page 8

5

PCI/USBOC# Pull-up(CLG)

1

2

3

56

+3V

USB_OC6 #

USB_OC0 #

PCH_AOC S#

USB_OC5 #USB_OC2 #

PCI_PIRQ A#

R94 8.2K_4

PCI_PIRQ B#

R76 8.2K_4

PCI_PIRQ C#

R83 8.2K_4

PCI_PIRQ D#

R77 8.2K_4

MPC_PW R_CTRL#

ACC_LED#

BT_COMB O_EN#

D D

LCD_BK

SI modify on 4/2

for D S3

USB_OC4 #

USB_OC1 #

USB_OC3 #

USB3.0

C C

GPIO52

GPIO54

R74 10K/F_ 4

R82 10K/F_ 4

R362 10K/F_4

R80 10K/F_ 4

R502 10K/F_4

R503 10K/F_4

+3V_DEEP _SUS

RP5

10

9

8

7 4

10K_10P 8R_6

USB30_RX 1-22

USB30_RX 2-22

USB30_RX 1+22

USB30_RX 2+22

USB30_TX1 -2 2

USB30_TX2 -2 2

USB30_TX1 +22

USB30_TX2 +22

Cougar Point-M/Panther Point (PCI,USB,NVRAM)

BG26

BJ26

BH25

BJ16

BG16

AH38

AH37

AK43

AK45

AH12

AM4

AM5

AB46

AB45

M20

AY16

BG46

BE28

BC30

BE32

BJ32

BC28

BE30

BF32

BG32

AV26

BB26

AU28

AY30

AU26

AY26

AV28

AW30

C18

N30

H3

Y13

K24

L24

B21

U18E

CPT_PPT_R ev_0p7

TP1

TP2

TP3

TP4

TP5

TP6

TP7

TP8

TP9

TP10

TP11

TP12

TP13

TP14

TP15

TP16

TP17

TP18

TP19

TP20

TP21

TP22

TP23

TP24

USB3Rn1

USB3Rn2

USB3Rn3

USB3Rn4

USB3Rp1

USB3Rp2

USB3Rp3

USB3Rp4

USB3Tn1

USB3Tn2

USB3Tn3

USB3Tn4

USB3Tp1

USB3Tp2

USB3Tp3

USB3Tp4

RSVD

20111 130 Mod ify USB3.0 for HM70

PCI_PIRQ A#

PCI_PIRQ B#

PCI_PIRQ C#

PCI_PIRQ D#

BT_COMB O_EN#23

BBS_BIT17

ACC_LED#2 4

PCI_GNT3 #7

LCD_BK26

BOARD_ID 39

R81 8.2K_4

ACCEL_IN TH#22

B B

CLK_33M _DEBUG23

CLK_33M _KBC25

+3V

CLK_PCI_ FB

C176

18P/50V_ 4

R96 22_4

BT_COMB O_EN#

BBS_BIT1

ACC_LED#

PCI_GNT3 #

MPC_PW R_CTRL#

LCD_BK

TP24

R93 22_4

R108 22_4

C211

18P/50V_ 4

GPIO52

GPIO54

ACCEL_IN TH#

PCI_PME#

PCI_PLTRS T#

CLK_PCI_ FB_R

CLK_PCI_ LPC_R

CLK_PCI_ EC_R

EMI(nea r PCH)

K40

PIRQA#

K38

PIRQB#

H38

PIRQC#

G38

PIRQD#

C46

REQ1# / GPIO50

C44

REQ2# / GPIO52

E40

REQ3# / GPIO54

D47

GNT1# / G PIO51

E42

GNT2# / G PIO53

F46

GNT3# / G PIO55

G42

PIRQE# / GPIO2

G40

PIRQF# / GPIO3

C42

PIRQG# / GPIO4

D44

PIRQH# / GPIO5

K10

PME#

C6

PLTRST#

H49

CLKOUT_P CI0

H43

CLKOUT_P CI1

J48

CLKOUT_P CI2

K42

CLKOUT_P CI3

H40

CLKOUT_P CI4

SMBus/Pull-up(CLG)

SI modify on 4/2

SMB_ME1 _CLK22

SMB_ME1 _DAT22

SMB_ME1 _CLK

SMB_ME1 _DAT

PCI

(+3V)

(+3V)

(+3V)

(+3V)

(+3V)

(+3V)

(+3V)

(+3V)

(+3V)

(+3V)

for D S3

R429 2.2K_4

R442 2.2K_4

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

(+3VS5)

PLTRST#(CLG)

R427

*0_4/S

PCI_PLTRS T#

A A

PLTRST#

R440

100K/F_ 4

PLTRST# 2,14,20,2 1,23,25

5

R248 4.7K_4

+3V

SMB_RUN _DAT12, 13

SMB_RUN _DAT

+3V

SMB_RUN _CLK SMB_ PCH_CLK

Q29

4 3

1

2N7002 DW

USB

4

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

USBP0N

USBP0P

USBP1N

USBP1P

USBP2N

USBP2P

USBP3N

USBP3P

USBP4N

USBP4P

USBP5N

USBP5P

USBP6N

USBP6P

USBP7N

USBP7P

USBP8N

USBP8P

USBP9N

USBP9P

USBP10N

USBP10P

USBP11N

USBP11P

USBP12N

USBP12P

USBP13N

USBP13P

USBRBIAS#

USBRBIAS

OC0# / G PIO59

OC1# / G PIO40

OC2# / G PIO41

OC3# / G PIO42

OC4# / G PIO43

OC5# / G PIO9

OC6# / G PIO10

OC7# / G PIO14

+3V_DEEP _SUS

+3V

5

SMB_PCH _DAT

2

6

4

AY7

AV7

AU3

BG4

AT10

BC8

AU2

AT4

AT3

AT1

AY3

AT5

AV3

AV1

BB1

BA3

BB5

BB3

BB7

BE8

BD4

BF6

AV5

AV10

AT8

AY5

BA2

AT12

BF3

C24

A24

C25

B25

C26

A26

K28

H28

E28

D28

C28

A28

C29

B29

N28

M28

L30

K30

G30

E30

C30

A30

L32

K32

G32

E32

C32

A32

C33

B33

A14

K20

B17

C16

L16

A16

D14

C14

WLAN

PCIE_RXN2 _LAN20

NV_ALE 7

USB2.0

USB2.0

Camera

USB2.0 Right

WLAN

R395

22.6/F_ 4

PCH_AOC S# 23

PCIE_RXP2 _LAN20

PCIE_TXN2 _LAN20

PCIE_TXP2_ LAN20

PCIE_RXN3 _CR21

PCIE_RXP3 _CR21

PCIE_TXN3 _CR21

PCIE_TXP3_ CR21

Cardreader

NV_ALE

USB_BIAS

USB_OC0 #

USB_OC1 #

USB_OC2 #

USB_OC3 #

USB_OC4 #

USB_OC5 #

USB_OC6 #

PCH_AOC S#

LAN

USBP0- 22

USBP0+ 22

USBP1- 22

USBP1+ 22

USBP2- 26

USBP2+ 26

USBP9- 19

USBP9+ 19

USBP10- 23

USBP10+ 23

CLK_REQ/Strap Pin(CLG)

PCIE_CLK REQ_LAN#

PCIE_CLK REQ_CR#

PCIE_CLK REQ_WLAN #

CLK_PCIE _REQ3#

CLK_PCIE _REQ4#

Intel DG r equest

CLK_PEGB _REQ#

CLK_PEGA _REQ#

CLK_PEGA _REQ#

CLK_PEGB _REQ#

CLK_BUF _BCLK_N

CLK_BUF _BCLK_P

CLK_BUF _PCIE_3GPLL #

CLK_BUF _PCIE_3GPLL

CLK_BUF _DREFCLK#

CLK_BUF _DREFCLK

CLK_BUF _DREFSSCLK#

CLK_BUF _DREFSSCLK

CLK_PCH_ 14M

CLOCK TE RMINATIO N for FC IM

PCIE_RXN123

PCIE_RXP123

PCIE_TXN123

PCIE_TXP12 3

C194 0.1U/1 0V_4

C193 0.1U/1 0V_4

C213 0.1U/1 0V_4

C203 0.1U/1 0V_4

C187 0.1U/1 0V_4

C184 0.1U/1 0V_4

MPC Sw itch Control

MPC_PW R_CTRL#

MPC_PW R_CTRL#

USB2.0/U SB3.0 COMBO 1s t

USB2.0/U SB3.0 COMBO 2n d

Cardreader

R434 10K/F_4

R150 10K/F_4

for D S3

R424 10K/F_4

R441 10K/F_4

R159 10K/F_4

R438 10K/F_4

R172 10K/F_4

R164 *10K/F_4

R426 *10K/F_4

R398 10K/F_4

R397 10K/F_4

R130 10K/F_4

R134 10K/F_4

R117 10K/F_4R430 4.7K_4

R118 10K/F_4

R153 10K/F_4

R154 10K/F_4

R95 10 K/F_4

+3V

+3V_DEEP _SUS

3

PCIE_TXN1 _C

PCIE_TXP1_ C

PCIE_TXN2 _LAN_C

PCIE_TXP2_ LAN_C

PCIE_TXN3 _CR_C

PCIE_TXP3_ CR_C

Low = MPC ON

High = M PC OFF (Defa ult)

R75 *1K/F_4

CLK_PCIE _WLANN

CLK_PCIE _WLANP

WLAN

LAN

PCIE_CLK REQ_WLAN #

CLK_PCIE _LANN

CLK_PCIE _LANP

PCIE_CLK REQ_LAN#

CLK_PCIE _CRN

CLK_PCIE _CRP

PCIE_CLK REQ_CR#

CLK_PCIE _REQ3#

CLK_PCIE _REQ4#

BOARD_ID 09

CLK_PEGB _REQ#

BOARD_ID 19

BOARD_ID 29

PCIE Clock

WLAN

PCIE_CLK REQ_WLAN #23

LAN

GPU

Cardrea der

3

2

Cougar Point-M/Panther Point (PCI-E,SMBUS,CLK)

CLK_PCIE _WLANN23

CLK_PCIE _WLANP23

CLK_PCIE _LANN20

CLK_PCIE _LANP20

PCIE_CLK REQ_LAN#20

CLK_PCIE _VGA#14

CLK_PCIE _CRN21

CLK_PCIE _CRP21

PCIE_CLK REQ_CR#21SMB_RUN _CLK1 2,13

U18B

CPT_PPT_R ev_0p7

BG34

PERN1

BJ34

PERP1

AV32

PETN1

AU32

PETP1

BE34

PERN2

BF34

PERP2

BB32

PETN2

AY32

PETP2

BG36

PERN3

BJ36

PERP3

AV34

PETN3

AU34

PETP3

BF36

PERN4

BE36