7-54

Silicon Bipolar RFIC 100 MHz

Vector Modulator

Technical Data

Features

• 25 - 250 MHz Output

Frequency

• -5 dBm Peak P

out

• Unbalanced 50 Ω Ouptut

Match

• Internal 90° Phase Shifter

• 5 V, 15 mA Bias

• SO-16 Surface Mount

Package

Applications

• Dual Conversion Cellular

Telephone and PCS

Handsets

• Dual Conversion ISM Band

Transmitters and LANs

• Direct Conversion Digital

Transmitters for 25- 250␣ MHz

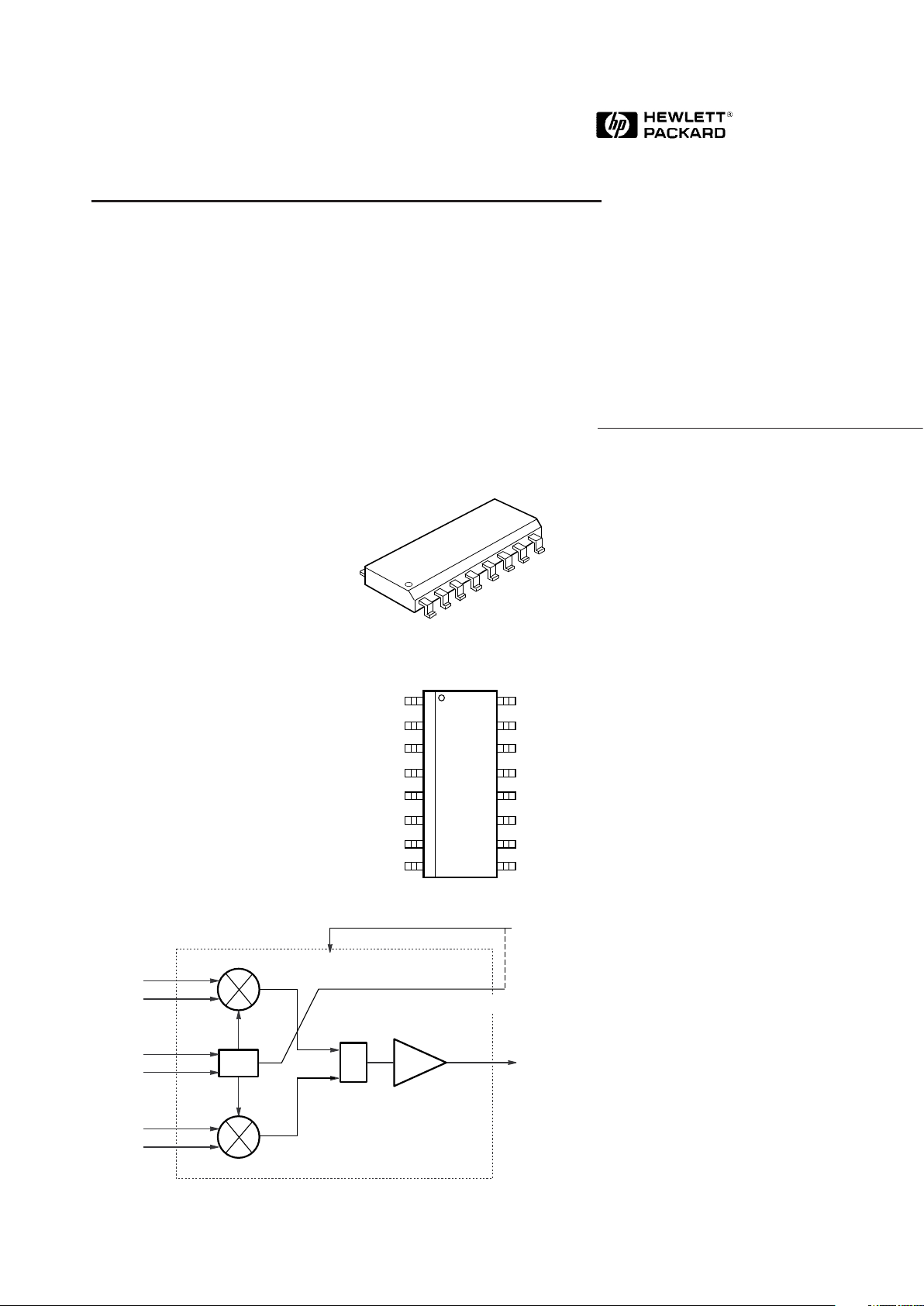

Functional Block Diagram

Plastic SO-16 Package

Pin Configuration

Description

Hewlett Packard’s HPMX-2005 is a

silicon RFIC vector modulator

housed in a SO-16 surface mount

plastic package. This IC can be

used for direct modulation at output frequencies from 25 to

250␣ MHz, or, in combination with

an up-converting mixer, for dual

or multiple conversion modulation to higher frequencies. The IC

contains two matched Gilbert cell

mixers, an RC phase shifter, a

summer, and an output amplifier.

This RFIC is well suited to portable and mobile cellular telephone applications such as North

American Digital Cellular, GSM,

and Japan Digital Cellular, and to

Personal Communications Systems such as DCS-1800 or

handyphones. It is also useful for

applications in 900 MHz, 2.4 GHz

and 5.7 GHz ISM (Industrial-Scientific-Medical) bands requiring digital modulation, such as Local Area

Networks (LANs).

The HPMX-2005 is fabricated with

Hewlett-Packard’s 25 GHz

ISOSAT-II process, which combines stepper lithography, selfalignment, ion-implantation

techniques, and gold metallization

to produce state of the art RFICs.

HPMX-2005

OUTPUT

AMPLIFIER

I

ref

Q MIXER

0°

V

CC

RF

out

50 Ω Z

o

(UNBALANCED)

I MIXER

I

mod

LO +

Q

mod

Q

ref

90°

LO –

φ ADJUST

(OPTIONAL CONNECTION FOR

OPERATION AT 140-250 MHz)

φ

SUMMER

Σ

PHASE

SHIFTER

16 V

CC

15 RF

out

14 GROUND

13 GROUND

12 I

ref

11 I

mod

10 GROUND

9 φ ADJUST

V

CC

1

V

CC

2

GROUND 3

GROUND 4

Q

mod

6

LO +

7

LO –

8

Q

ref

5

5965-9104E

7-55

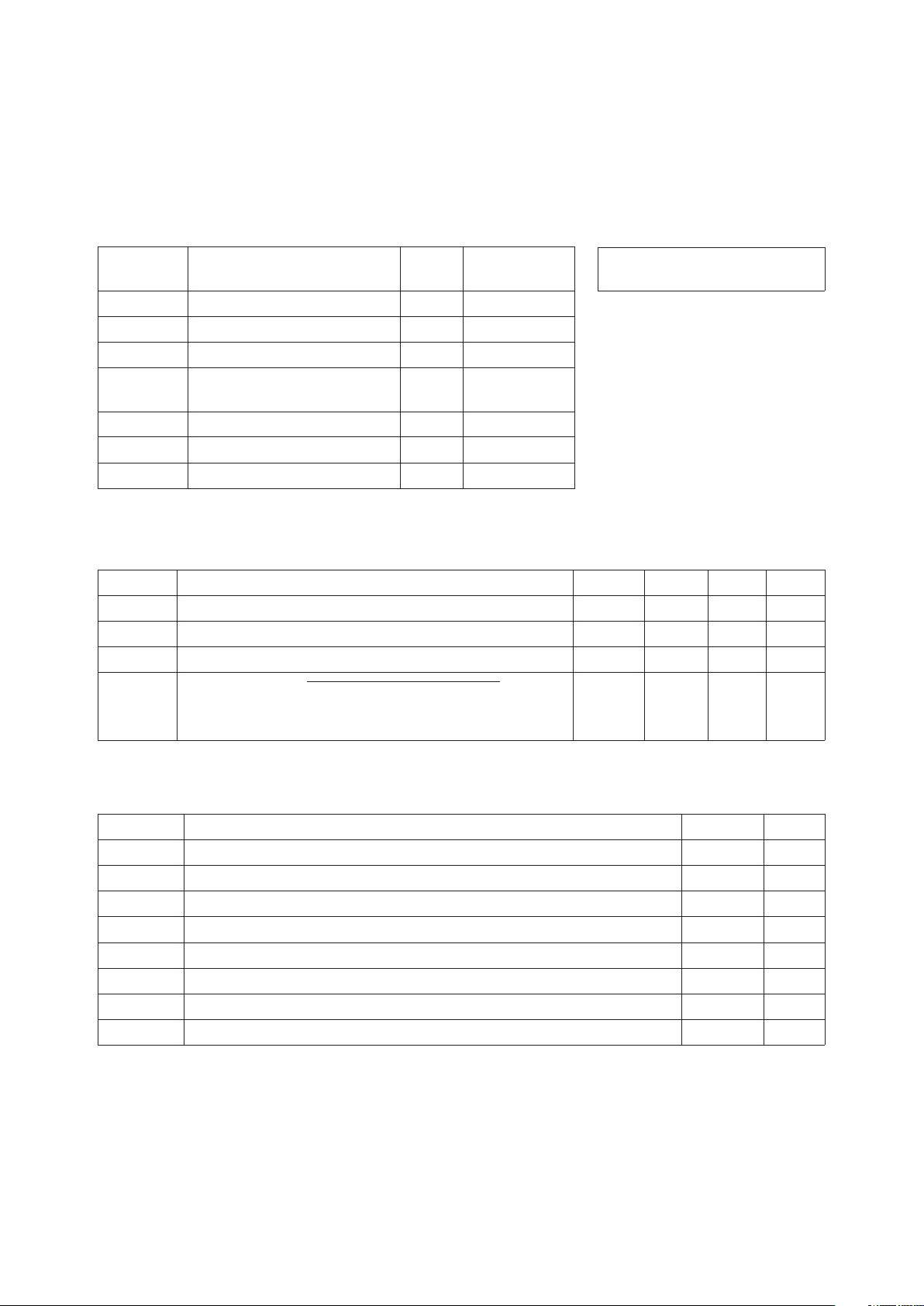

HPMX-2005 Guaranteed Electrical Specifications, T

A

= 25° C, ZO = 50 Ω

VCC = 5 V, LO = -12 dBm @ 100 MHz (Unbalanced Input), V

Iref

= V

Qref

= 2.5 V (unless otherwise noted).

Symbol Parameters and Test Conditions Units Min. Typ. Max.

I

d

Device Current mA 14 17

P

out

Output Power V

Imod

= V

Qmod

= 3.25 V dBm -7 -5

LO

leak

P

out

- LO at Output V

Imod

= V

Qmod

= 2.5 V dBc 30 36

ε

mod

Average % 2.5 5

Modulation

Error

HPMX-2005 Absolute Maximum Ratings, T

A

= 25° C

Absolute

Symbol Parameter Units Maximum

[1]

P

diss

Power Dissipation

[2,3]

mW 500

LO

in

LO Input Power dBm 15

V

CC

Supply Voltage V 10

[4]

∆V

Imod

, Swing of V

Imod

about V

Iref

or V

p-p

5

[4]

∆V

Qmod

V

Qmod

about V

Qref

V

Iref

, V

Qref

Reference Input Levels V 5

T

STG

Storage Temperature °C -65 to 150

T

j

Junction Temperature °C 150

Thermal Resistance

[2]

:

θjc = 125°C/W

Notes:

1. Operation of this device above any one

of these parameters may cause

permanent damage.

2. TC = 25°C (TC is defined to be the

temperature at the ends of pin 3 where

it contacts the circuit board).

3. Derate at 8 mW/°C for TC > 87°C.

4. This voltage must not exceed V

CC

by

more than 0.8 V.

HPMX-2005 Summary Characterization Information. T

A

= 25° C, ZO = 50 Ω

VCC = 5 V, LO = -12 dBm @ 100 MHz (Unbalanced Input), V

Iref

= V

Qref

= 2.5 V (unless otherwise noted).

Symbol Parameters and Test Conditions Units Typ.

R

in

Input Resistance (I

mod

to I

ref

or Q

mod

to Q

ref

) Ω 10 k

R

in-gnd

Input Resistance to Ground (Any I, Q Input to Ground) Ω 10 k

VSWR

LO

LO VSWR (50 Ω) 25 - 200 MHz Bandwidth 1.5:1

VSWR

O

Output VSWR (50 Ω) 25 - 200 MHz Bandwidth 2.5:1

- Output Noise Floor V

Imod

= V

Qmod

= 3.25 V dBm/Hz -134

IM

3

DSB Third Order Intermodulation Products dBc 33

A

i

RMS Amplitude Error dB 0.15

P

i

RMS Phase Error degrees 1.0

√(V

Imod

- 2.5)2 + (V

Qmod

- 2.5)2 = 0.75 V

7-56

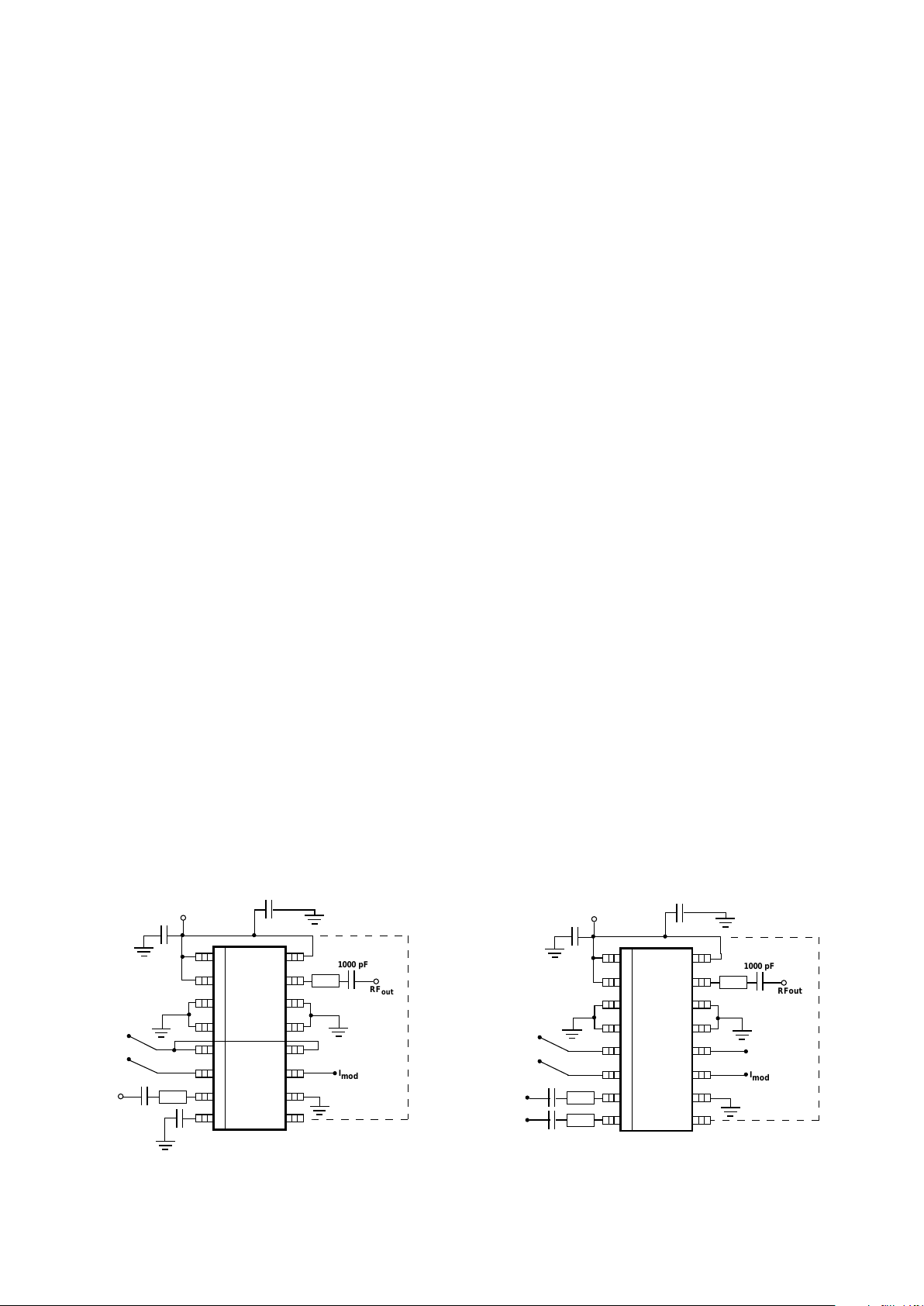

Figure 1. HPMX-2005 Connections Showing Unbalanced

LO and I/Q Inputs.

Figure 2. HPMX-2005 Connections Showing Differential

LO and I/Q Inputs.

HPMX-2005 Pin

Descriptions

VCC (pins 1, 2 & 16)

These three pins provide DC

power to the RFIC, and are connected together internal to the

package. They should be connected to a 5 V supply, with appropriate AC bypassing (1000 pF

typ.) used near the pins, as shown

in figures 1 and 2.The voltage on

these pins should always be

kept at least 0.8 V more posi-

tive than the DC level on any

of pins 5, 6, 11, or 12. Failure to

do so may result in the modulator

drawing sufficient current

through the data or reference inputs to damage the IC (see also

Figure 5).

Ground (pins 3, 4, 10, 13 & 14)

These pins should connect with

minimal inductance to a solid

ground plane (usually the backside of the PC board). Recommended assembly employs

multiple plated through via holes

where these leads contact the PC

board.

I

ref

(pin 12) and Q

ref

(pin 5)

I

mod

(pin 11) and Q

mod

(pin 6)

Inputs

The I and Q inputs are designed

for unbalanced operation but can

be driven differentially with similar performance. The recommended level of unbalanced I and

Q signals is 1.5 V

p-p

with an average level of 2.5 V above ground.

The reference pins should be DC

biased to this average data signal

level (VCC/2 or 2.5 V typ.). For

single ended drive, pins 5 and 12

can be tied together. For differential operation, 0.75 V

p-p

signals

may be applied across the I

mod/Iref

and the Q

mod/Qref

pairs. The average level of all four signals should

be about 2.5 V above ground. The

impedance between Iin or Qin and

ground is typically 10 kΩ and the

impedance between I

mod

and I

ref

or Q

mod

and Q

ref

is typically

10␣ k Ω. The input bandwidth typically exceeds 40 MHz. It is possible to reduce LO leakage

through the IC by applying slight

DC imbalances between I

mod

and

I

ref

and/or Q

mod

and Q

ref

(see page

9). All performance data shown

on this data sheet was taken with

unbalanced I/Q inputs.

LO Input (pins 7 and 8)

The LO input of the HPMX-2005 is

balanced (differential) and

matched to 50 Ω. For drive from a

unbalanced LO, pin 7 should be

AC coupled to the LO using a 50 Ω

transmission line and a blocking

capacitor (1000 pF typ.), and pin 8

should be AC grounded (1000 pF

capactitor typ.), as shown in figure 1. For drive from a differential

LO source, 50 Ω transmission

lines and blocking capacitors

(1000 pF typ.) are used on both

pins 7 and 8, as shown in figure 2.

The internal phase shifter allows

operation from 25 to 200 MHz (or

to 250 MHz by using pin 9 — see

below). The recommended LO

input level is -12 dBm. All performance data shown on this data

sheet was taken with unbalanced

LO operation.

Phase Adjust (pin 9)

Applying a DC bias to this pin alters the frequency range of the internal RC phase shifter. In normal

operation, this pin is not connected. (Do not ground this pin!)

For operation at LO frequencies

above 140 MHz, superior modulation error can be achieved by connecting pin 9 to VCC (5 V). The

resulting changes in performance

are shown in figures 13 through

18. Use of pin 9 extends the

operating range to beyond

250␣ MHz.

RF Output (pin 15)

The RF output of the HPMX-2005

is configured for unbalanced operation, and connects directly to

an emitter follower in the output

stage of the IC. The output impedance is appropriate for connection

without further impedance matching to transmission lines of

characteristic impedance between

50 Ω and 150 Ω. The reflection

coefficients are given in figure 11.

A DC blocking capacitor (1000 pF

typ.) is required on this pin.

OPTIONAL FOR

OPERATION TO 250 MHz

LO

in

1000 pF

1000 pF

VCC = +5 V

1000 pF

RF

out

1000 pF

Q

ref

Q

mod

I

mod

1 16

215

314

413

512

611

710

89

1000 pF

OPTIONAL FOR

OPERATION TO 250 MHz

1000 pF

1000 pF

VCC = +5 V

1000 pF

RFout

Q

ref

Q

mod

I

mod

LO

+

LO

–

1000 pF

1000 pF

I

ref

1 16

2

15

314

413

512

611

710

89

7-57

by applying 1.75 V to the I and/or

Q inputs.

Amplitude and phase are measured by setting the network analyzer for an S21 measurement at

the center frequency of choice.

Set the port 1 stimulus level to the

LO level you intend to use in your

circuit (-12 dBm for the data

sheet).

By adjusting the Vi and Vq settings

you can step around the I/Q vector circle, reading magnitude and

phase at each point. The relative

values of phase and gain (amplitude) at the various points will

indicate the accuracy of the

modulator. Note: you must use

very low ripple power supplies for

the reference, V

Imod

, and V

Qmod

supplies. Ripple or noise of only a

few millivolts will appear as wob-

bling phase readings on the network analyzer.

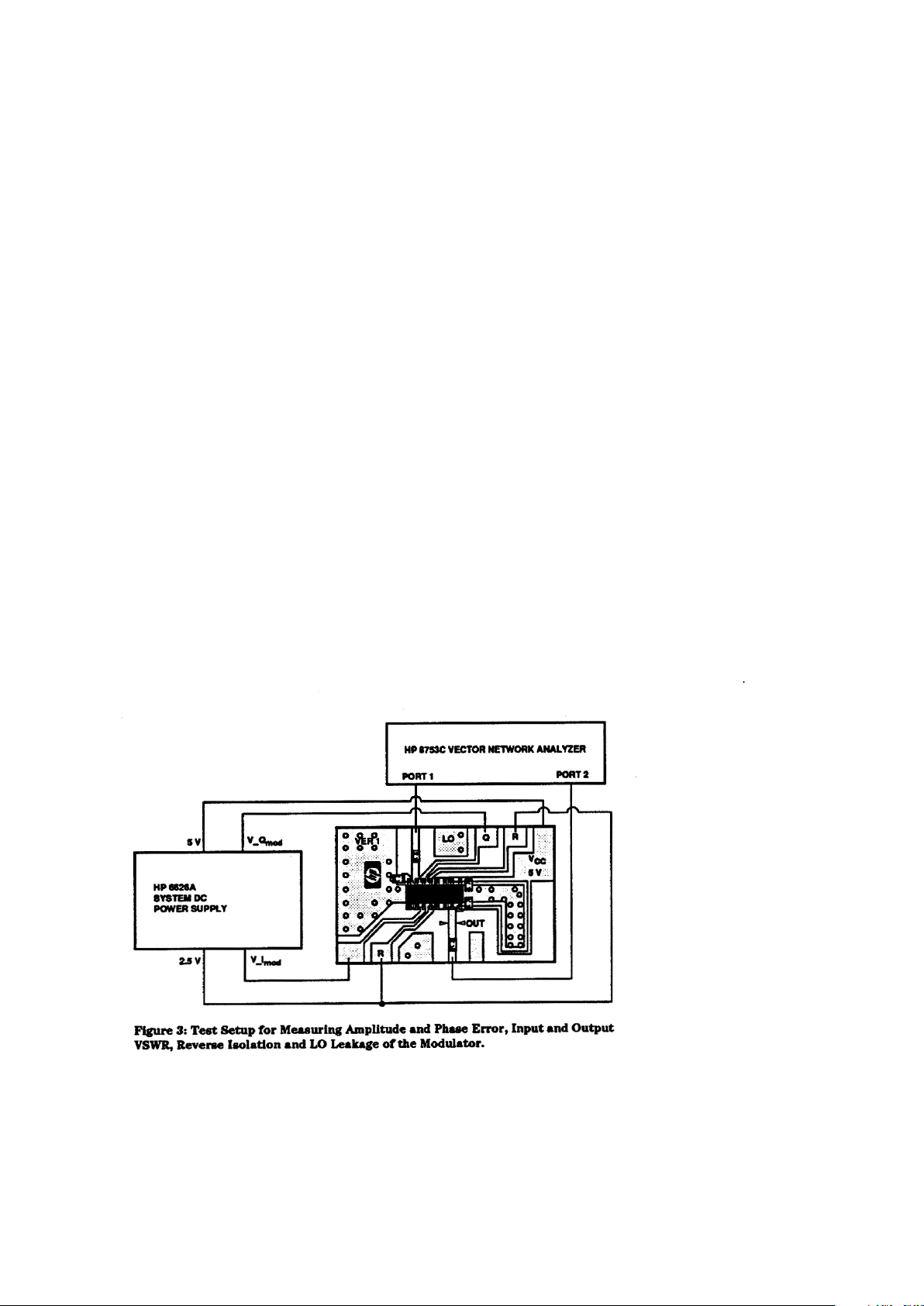

The same test setup shown below

is used to measure input and output VSWR, reverse isolation, and

power vs. frequency. V

Imod

and

V

Qmod

are set to 3.25 V and the

appropriate frequency ranges are

swept. S11 provides input VSWR

data, S22 provides output VSWR

data and S12 provides reverse

isolation data. S21 provides power

output (add the source power to

the S21 derived gain).

LO leakage data shown in figure

17 is generated by setting V

Imod

=

V

Qmod

= V

Iref

= V

Qref

= 2.5 volts then

performing an S21 sweep. Since

phase is not important for these

measurements, a scalar network

analyzer or a signal generator and

spectrum analyzer could be used.

HPMX-2005 Typical Data

Measurement

Direct measurement of the amplitude and phase error at the output

is the most accurate way to evaluate modulator performance. By

measuring the error directly, all

the harmonics, LO leakage, etc.

that show up in the output signal

are accounted for. Figure 3 below

shows the test setup that was

used to create the amplitude and

phase error plots (figures 19 and

21).

Amplitude and phase error are

measured by using the four channel power supply to simulate I and

Q input signals. Real 1.5 V

p-p

I and

Q signals would swing 0.75 volts

above and below an average 2.5 V

level, therefore, a logic “high”

level input is simulated by applying 3.25 V, and a logic “low” level

Loading...

Loading...