Page 1

A

1 1

2 2

B

C

D

E

Compal confidential

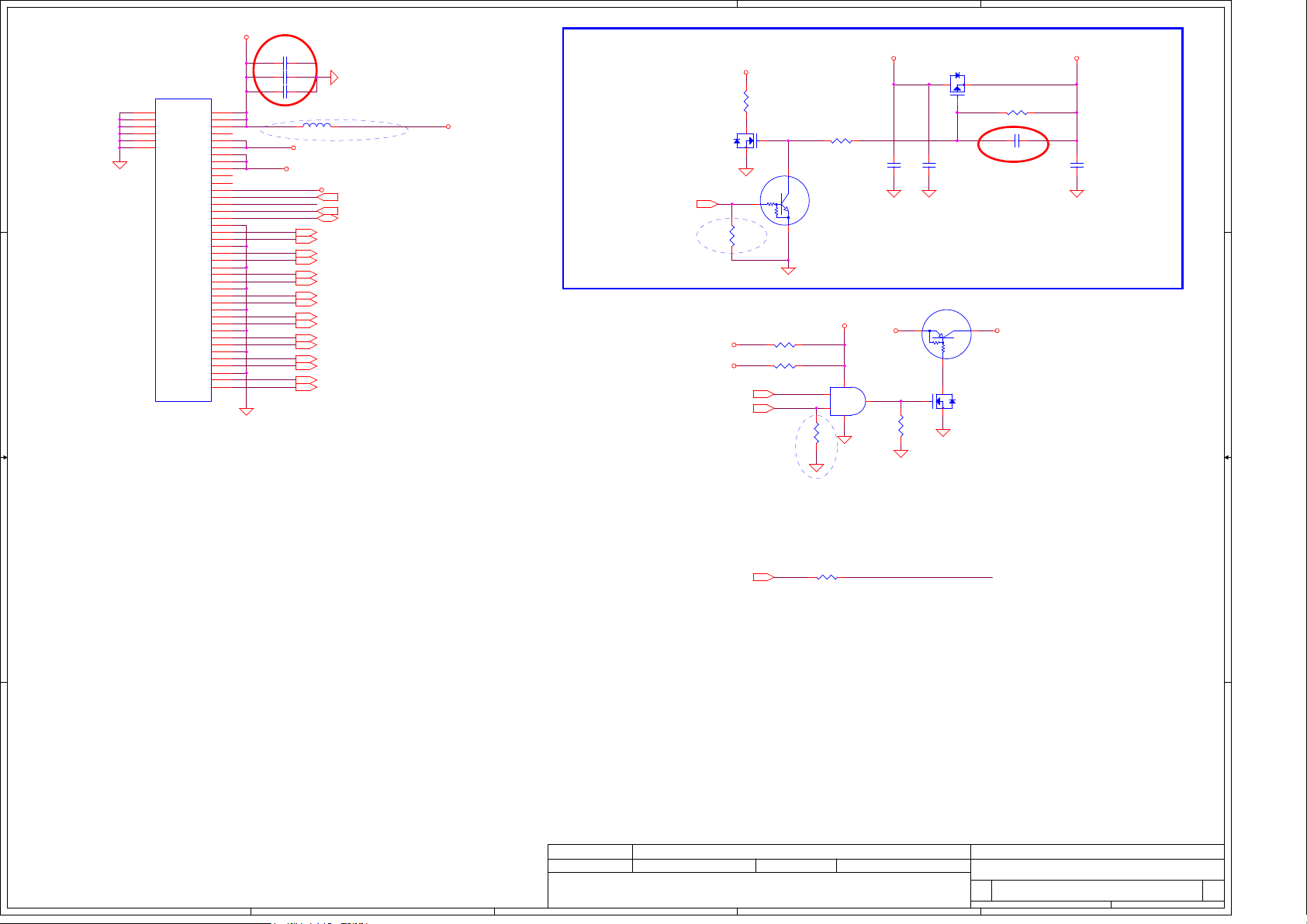

Schematics Document

Mobile Merom uFCPGA with Intel

Crestline_PM+ICH8-M core logic

3 3

IBT00 LA-3261P UMA

2007-03-28

4 4

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2006/02/13 2006/03/10

REV:1A (MV2)

Compal Secret Data

Deciphered Date

D

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

Compal Electronics, Inc.

Cover Sheet

LA -3 26 1P U MA

E

1 55Wednesday, March 28, 2007

0.4

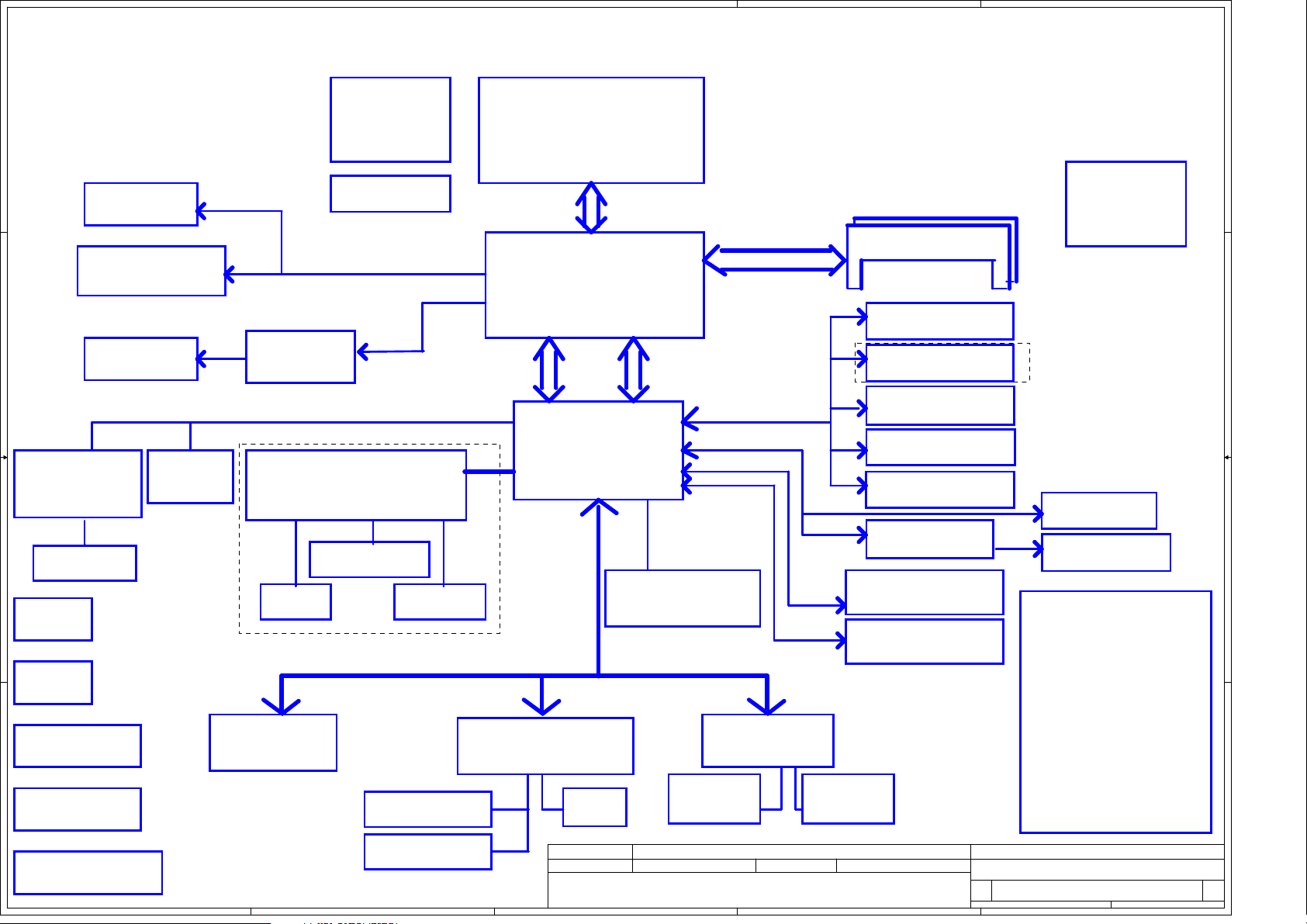

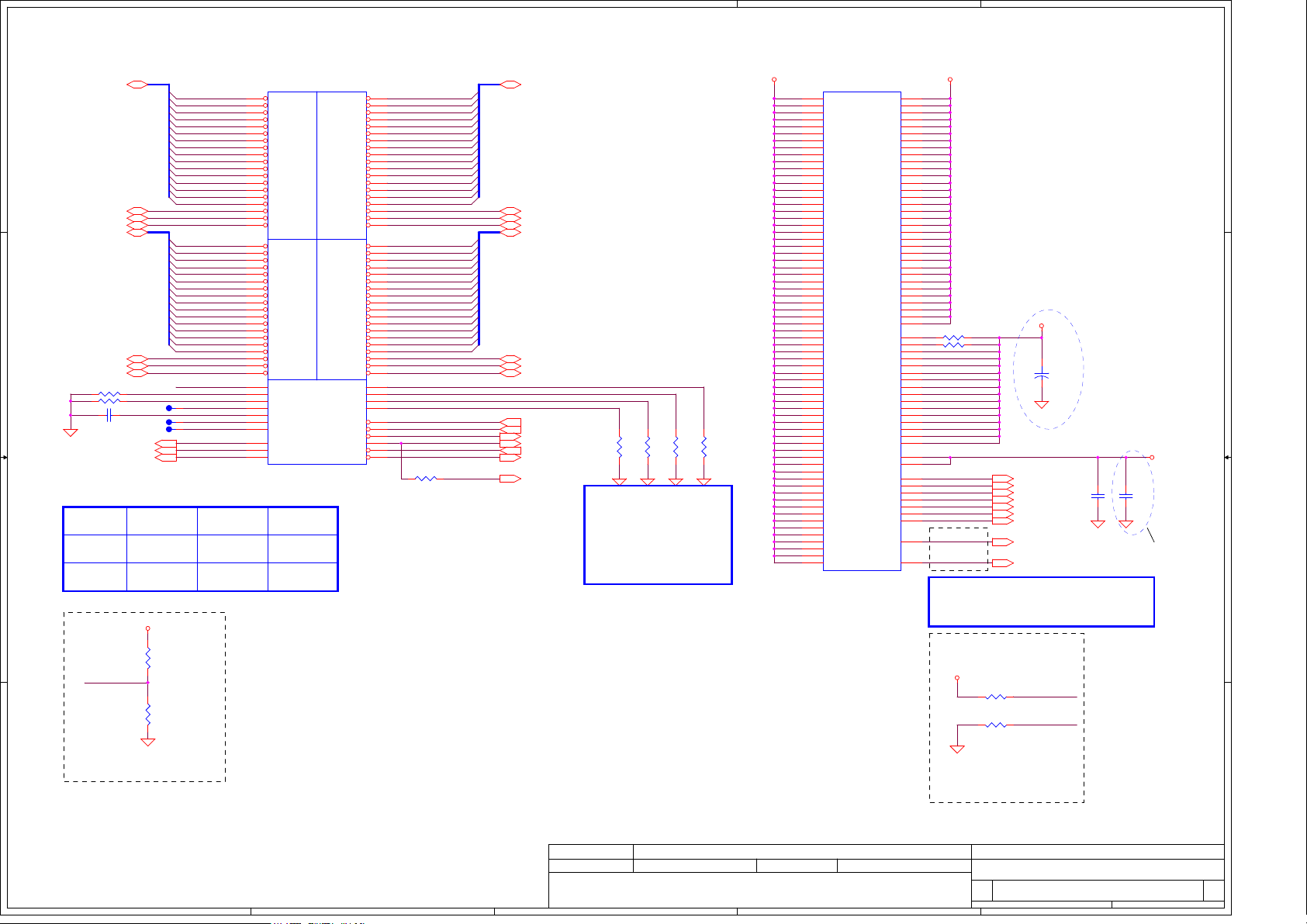

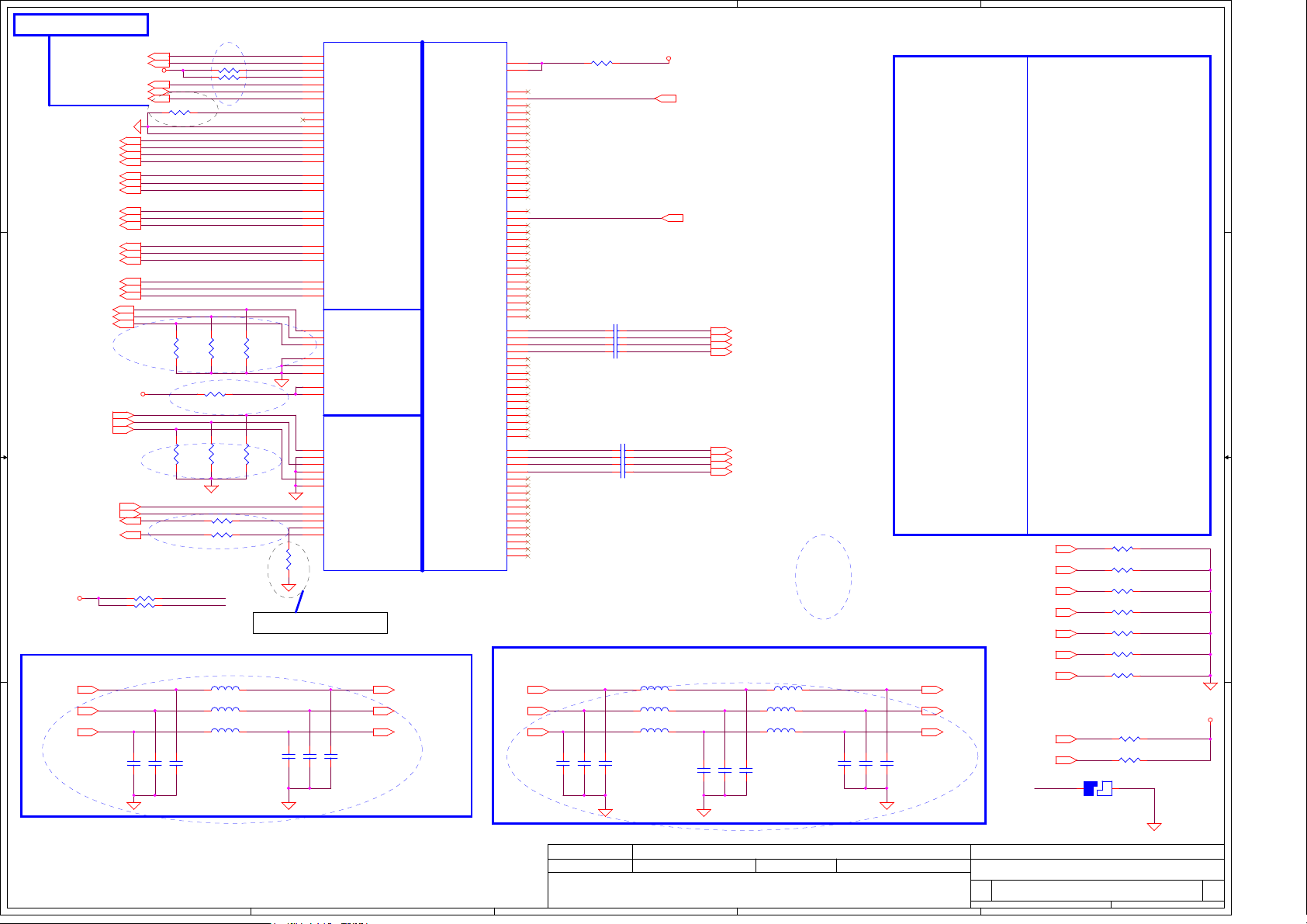

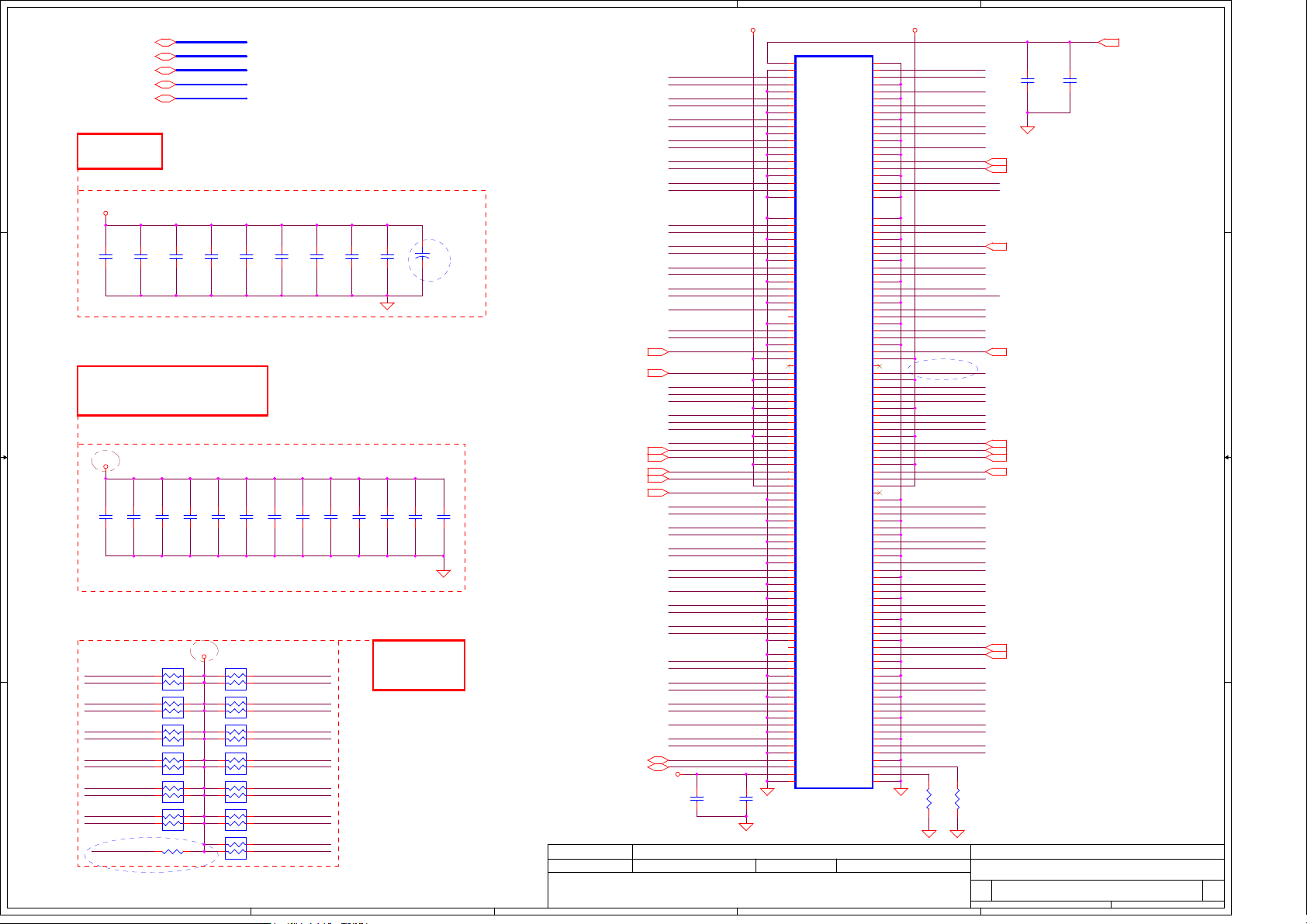

Page 2

A

Compal confidential

File Name : LA-3261P

B

C

Chimay UMA

D

E

1 1

CRT & TV OUT

P16

LVDS Panel Interface

P17

Thermal Sensor

AD M1032ARMZ

P4

Fan c onn

P4

Intel Crestline MCH

SDV O

2 2

DVI (Docking)

P33

CH 7307 C

P16

DM I X4

PCI-E BUS

10/100/1000 LAN

Mini-Card

Intel 82566MM

P23

RJ 45/11 CONN

3 3

P24

LED

P30

CardBus Controller & PCMCIA conn

Ri coh R5C853 & R5C851

P25

Slot 0/Smart Card

1394 port

P28

6in1 Slot

PCI

daug hte r board

RTC CKT.

P19

Mo bile Merom

uFCPGA-478 CPU

H_ A#( 3.. 35)

H_ D#( 0..6 3)

FSB

667/800MH z 1.05V

FC BGA 1299

P7, 8, 9, 10, 11, 12

Intel ICH8-M

mB GA-676

P18, 19, 20, 21

SPI ROM & Debug port

16Mb*2 or 32Mb*1

P4, 5, 6

C- Link

SPI

LPC BUS

DDR2 667MHz 1. 8V

Dual Channel

USB2.0

Azalia

SATA Master

PATA Slave

P30

DDR2- SO-DIMM X2

BANK 0, 1, 2, 3

P13, 14

USB conn x2

(Docking)

FingerPrint er 2501B

USBx1

USB conn x3

BT Co nn

Mini-Card WWAN

P25P25

Audio CKT

AD1981HD

P26

SATA HDD Connector

P22

Multi-bay II Connector

P22

P33

P30

P28

P28

CK505

TSSOP- 64

Clock Generator

IC S 9LPR S355

P15

daug hte r board

MDC

P32

AMP & Audio Jack

MAX9710

P33

Docking CONN.

*RJ-45(LED*2)

*RJ-11(Pass Through)

*CRT

*COMPOSITE Video Out

*TVOUT

*DVI

*LINE IN

P27

*LINE OUT

Power OK CKT.

P35

4 4

Power On/Off CKT.

P32

TPM1.2

SLB9635TT

P30

Touch P ad CON N.

SMSC KBC 1070

SMSC KBC 1021-NU

P31

Int.KBD

P32 P32

SMSC Super I/O

LPC47N217

COM1 LPT

( Docking ) ( Docking )

P33 P33

P29

*PCI-E x2

*Serial Port

*Parallel Port

*PS/2 x2

*USB x2

*DC JACK

DC/DC Interface CKT.

P34

A

TrackPoint CONN.

B

P32

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2006/02/13 2006/03/10

Compal Secret Data

Deciphered Date

D

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

Compal Electronics, Inc.

Block Diagram

LA -3 26 1P U MA

E

2 55Tuesday, March 27, 2 007

0.4

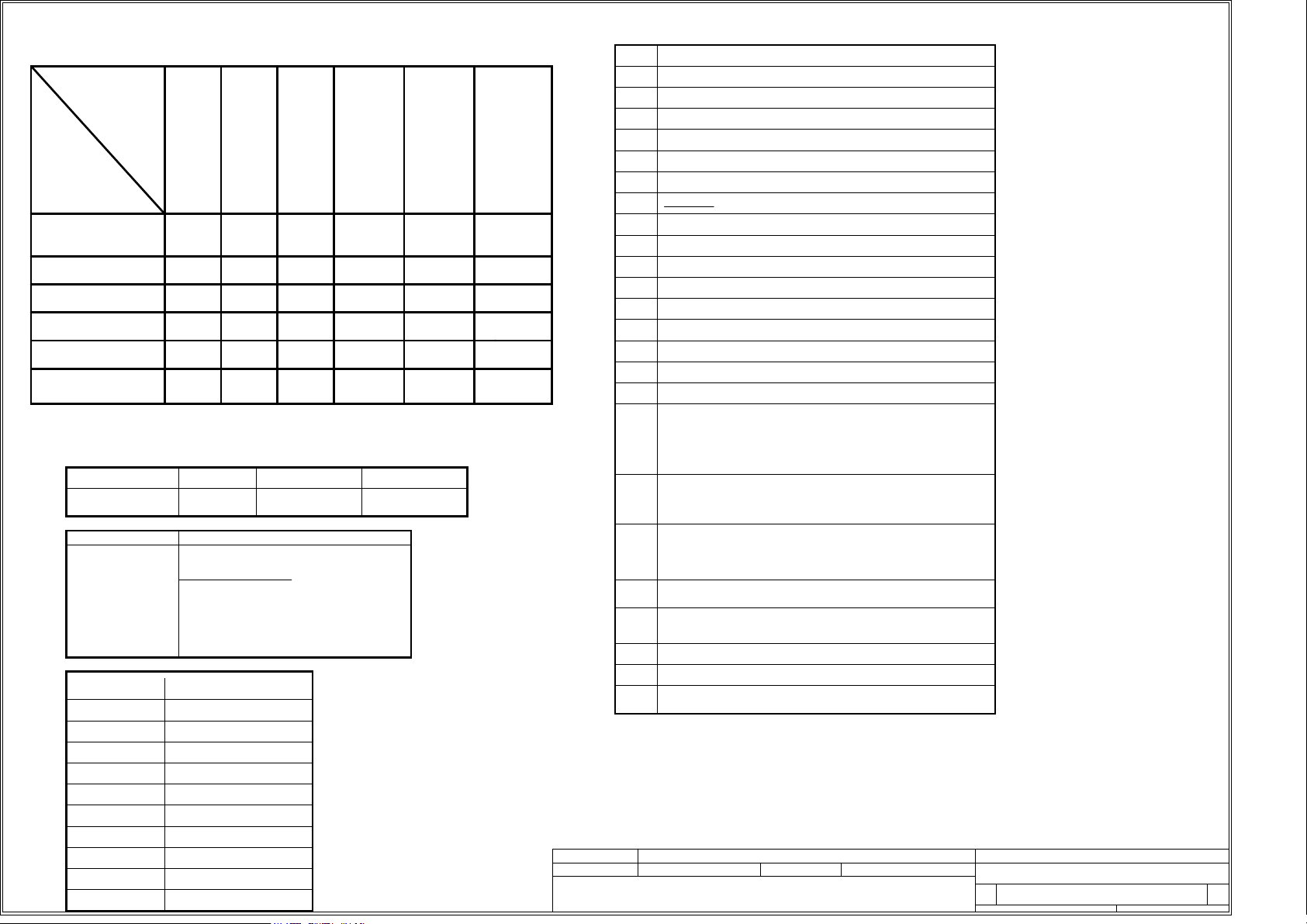

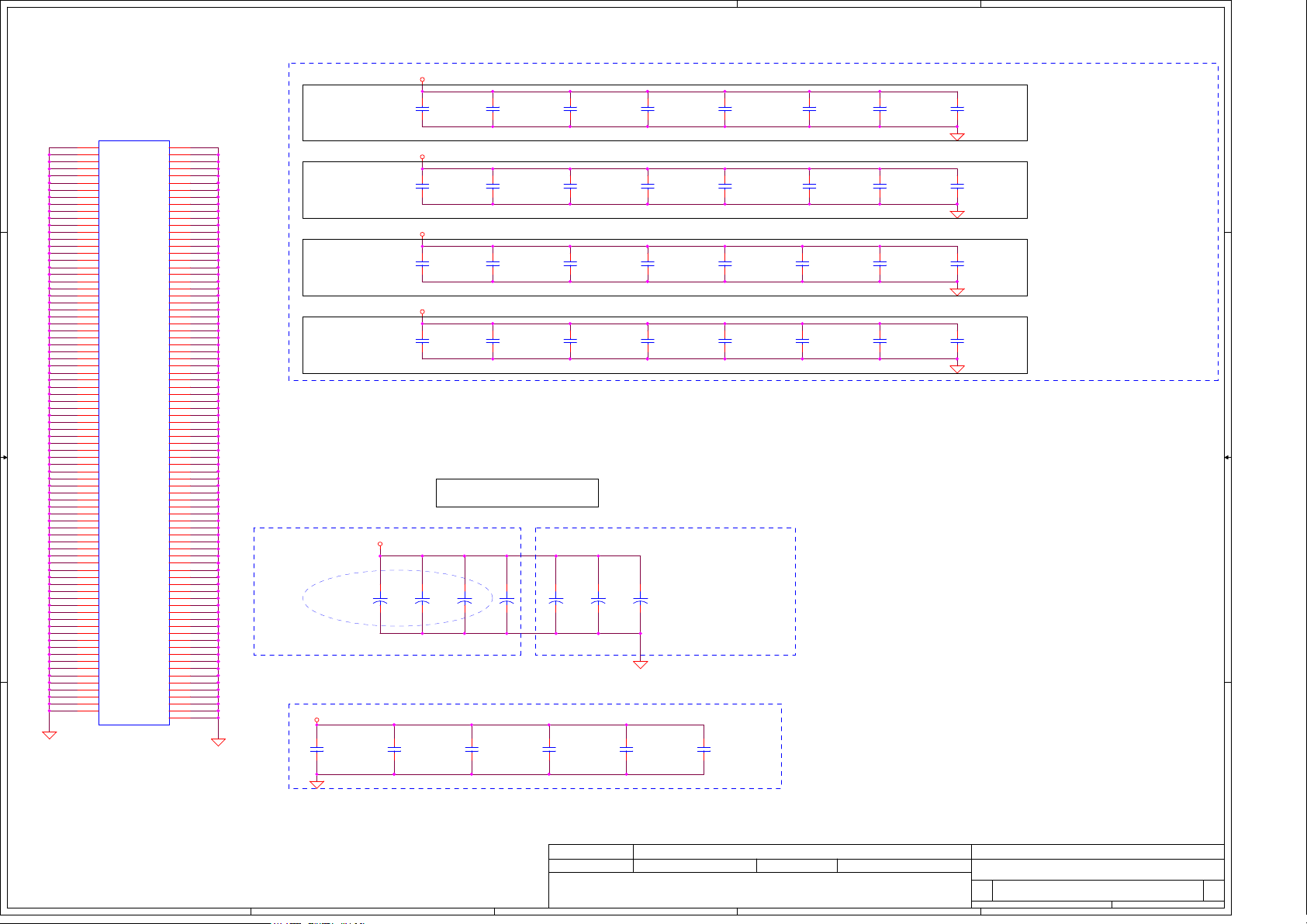

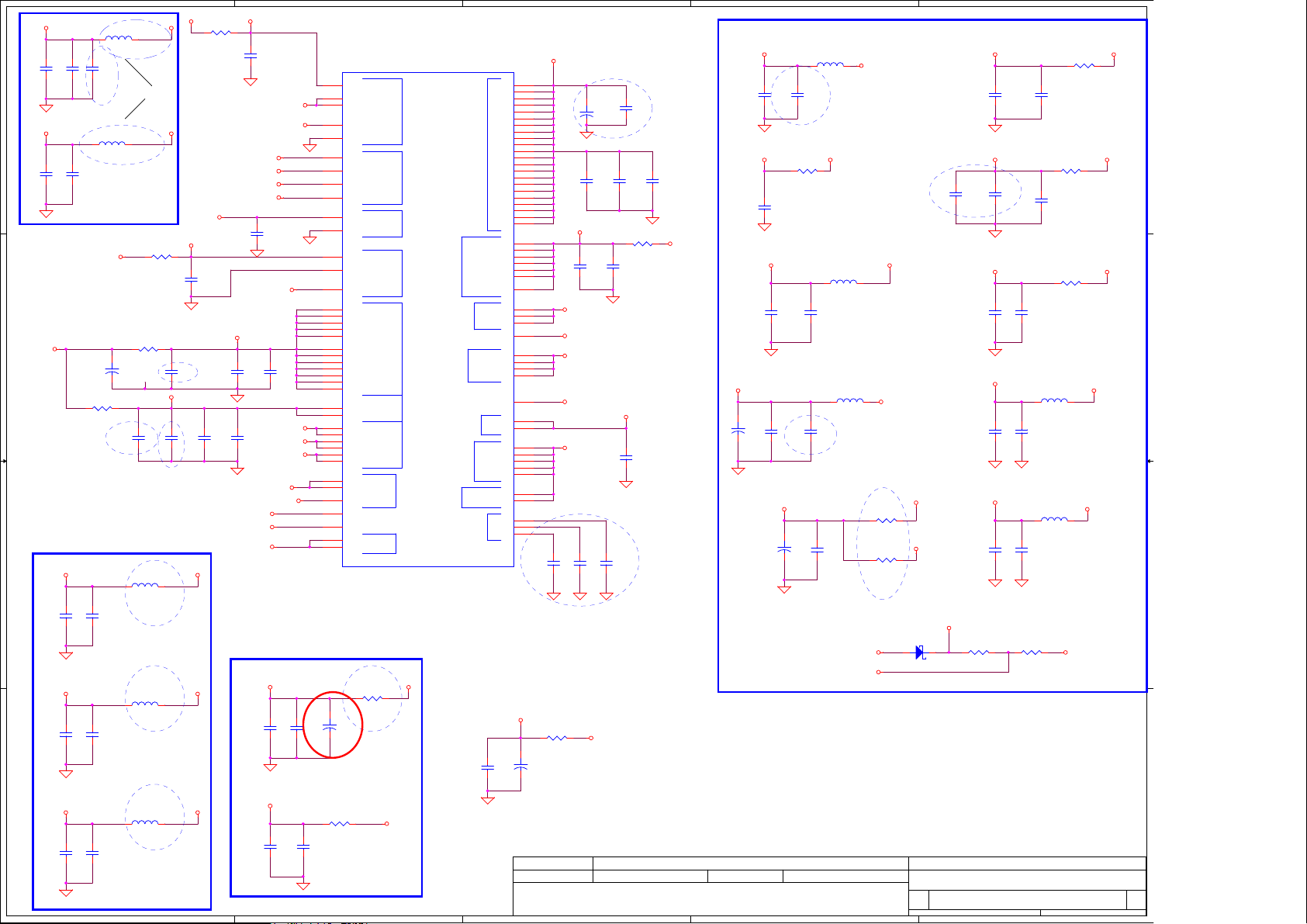

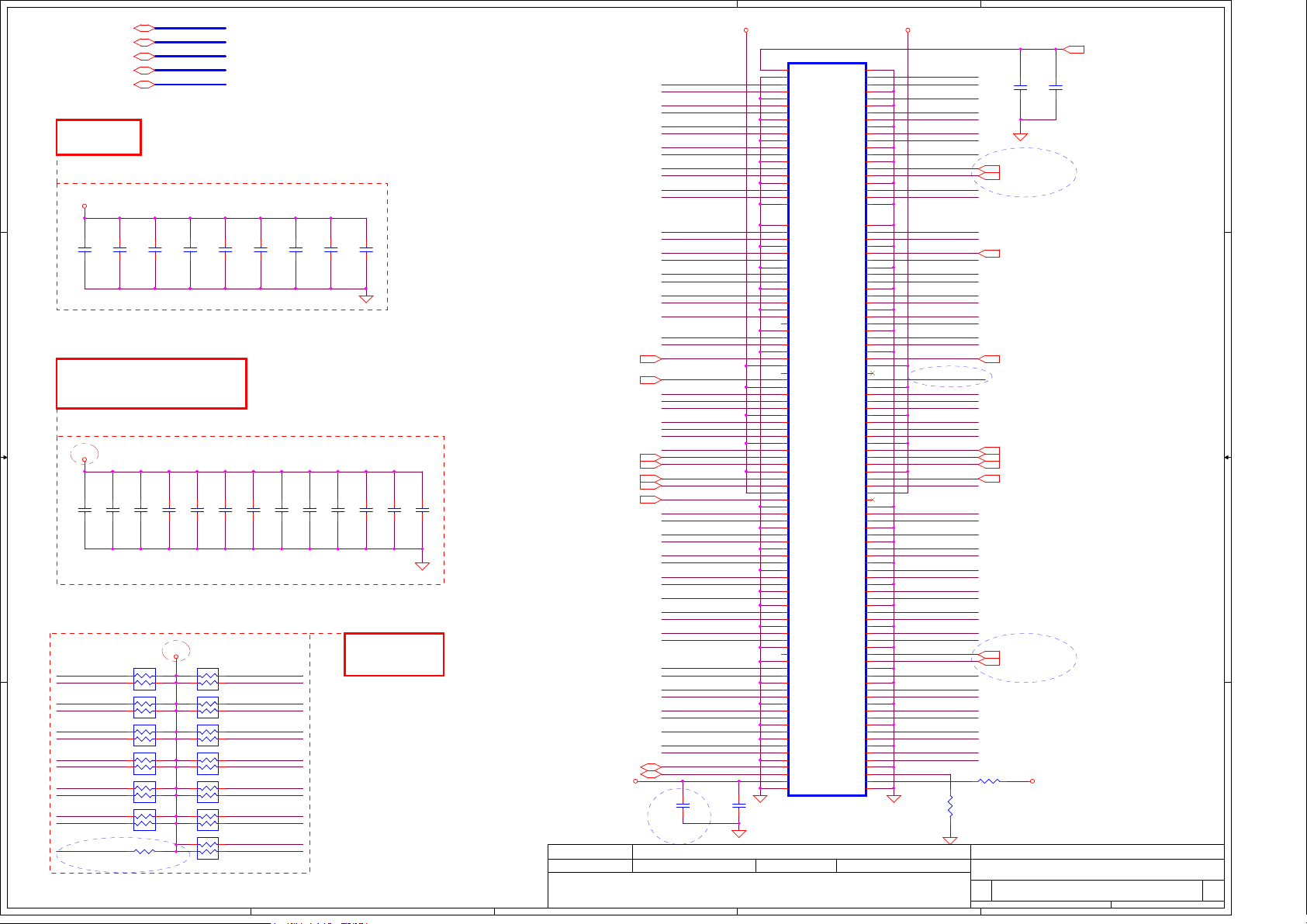

Page 3

A

Voltage Rails

power

plane

State

S0

S3/M1

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

1 1

PCI Devices

EXTERNAL

CA RD B US & 139 4

DMA Channel

DM A0

DM A1

DM A2

DM A3

DM A4

DM A5

DM A6

DM A7

USB PORT#

O MEANS ON X MEANS OFF

+B

LDO3

LDO5

O

O

O

O

O

X

De st in at ion

0

1

2

3

4

5

6

7

8

9

Walk -up0 (R ight side)

Finge rprint

Reserv e

WWAN

Walk -up1 (Le ft Side)

Walk -up2 (Le ft Side)

Bluet ooth

Reserv e

Dockin g

Dockin g

+5VS

+3VS

+2.5VS

+1.8VS

+5VALW

+3VALW

O

O

O

O

X

+1.8V

+5V

+0.9V

+1.5VS

+1.25VS

+VGA_CORE

+CPU_CORE

+VCCP

O

O

X X

X

OO

X

X

X

X X X

ID SE L# RE Q/G NT# PI RQ

AD 22 2 C, D, E, G

Device

MODEM / LAN

ECP

FL OPP Y DISK

AUDIO

(Cascade)

Unused

Unused

Unused

+3VM

+1.05VM

+1.25VM

O

O

O

O

X

X

CLOCK

O

O

O

O

X

X

IRQ

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

De vic e

Syste m Timer

Keyboa rd

N/A

Seri al po rt (COM2),L AN/Modem

Seri al port (COM1)

Audio /VGA

Floppy

Para llel port

Syst em CM OS/Real-tim e clock

Micr osoft ACPI

N/A, Momem,LAN

Mass str orag e contr ol/ PCI sim ple communi cation cont rol

syna ctic PS2 port Gl idePAD

Nume ric Data Process

Prim ary I DE interfac e,HDD

Seco ndar y IDE innt erface,CD-R OM

Mobi le I ntel Crestline E xpress Chip set Family

Micr osof t UA A Bus Dri ver for Hig h Definitio n Audio

Inte l 82 801H (ICH8 Fa mily) PCI E xpress Root Port -27D0

Broa dcom NetXtrem e Gigabit E thernet

Inte l 82 801H (ICH8 Fa mily)PCI Ex press Root Port - 27D2

Broa dcom 80 2.11b/g WLA N

Inte l 82 801H (ICH8 Fa mily)USB Un iversal Hos t Controll

Inte l 82 801H (ICH8 Fa mily)USB Un iversal Hos t Controll

Rico h R5C 853 Cardbus Control

Rico h R5 C853 Integrates FlashMedia Control

Rico h R5 C853 Gemcore bas ed SmartCar d Control

Inte l 82 801H (ICH8 Fa mily)PCI Ex press Root Port - 27D6

Inte l 82 801H (ICH8 Fa mily)USB Un iversal Hos t Controll

Inte l 82 801H (ICH8 Fa mily)USB Un iversal Hos t Controll

Inte l 82 801H (ICH8 Fa mily)USB2 E nhanced Hos t Controll

Inte l 82 801H (ICH8 Fa mily)USB Un iversal Hos t Controll

SDA Stan dard Co mpliant SD Host Contro ller

HP M obil e Data Pro tection Sen sor

2005/03/10 2006/03/10

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

Compal Electronics, Inc.

Notes List

LA -3 26 1P U MA

3 55Tuesday, March 27, 2 007

0.4

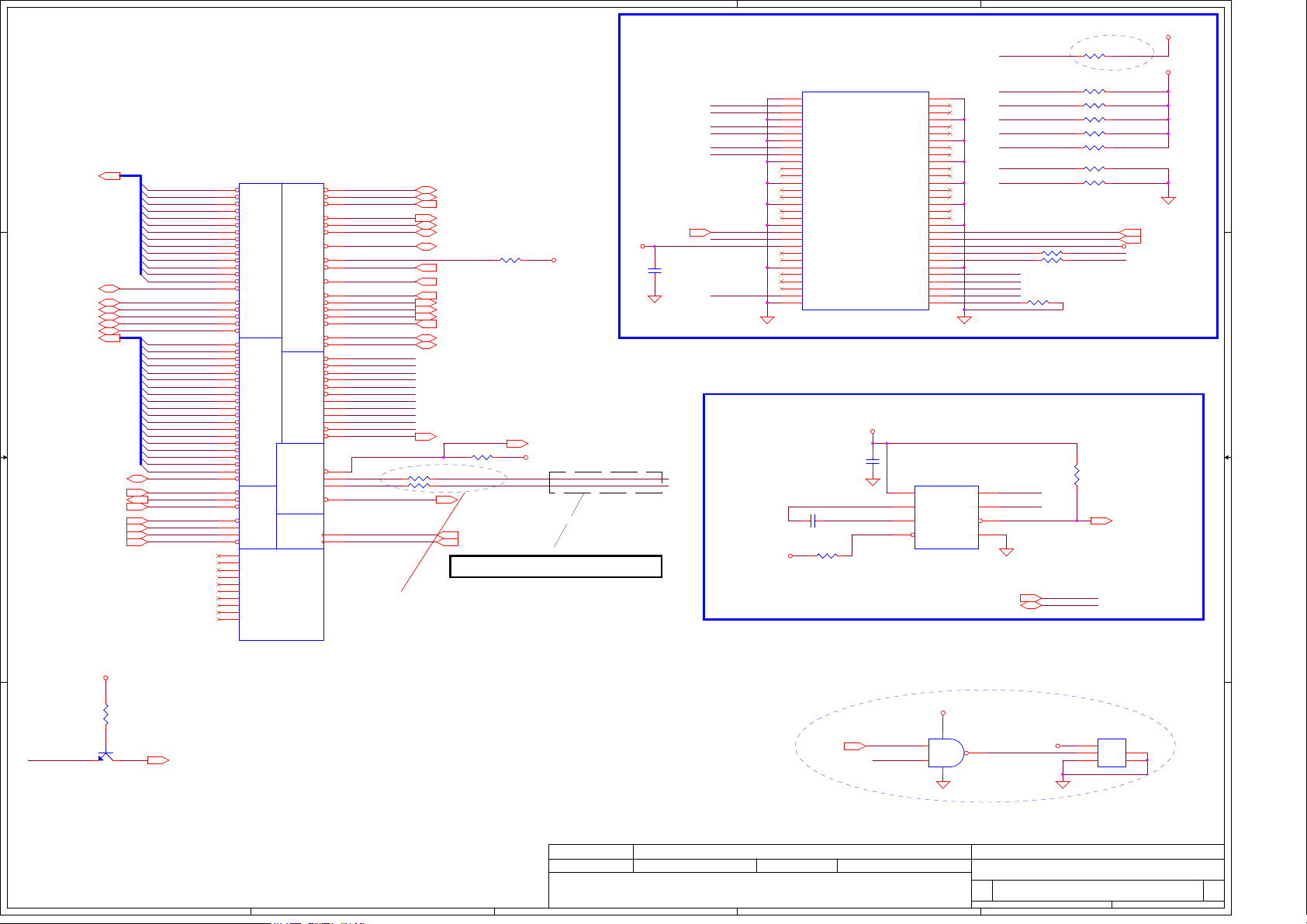

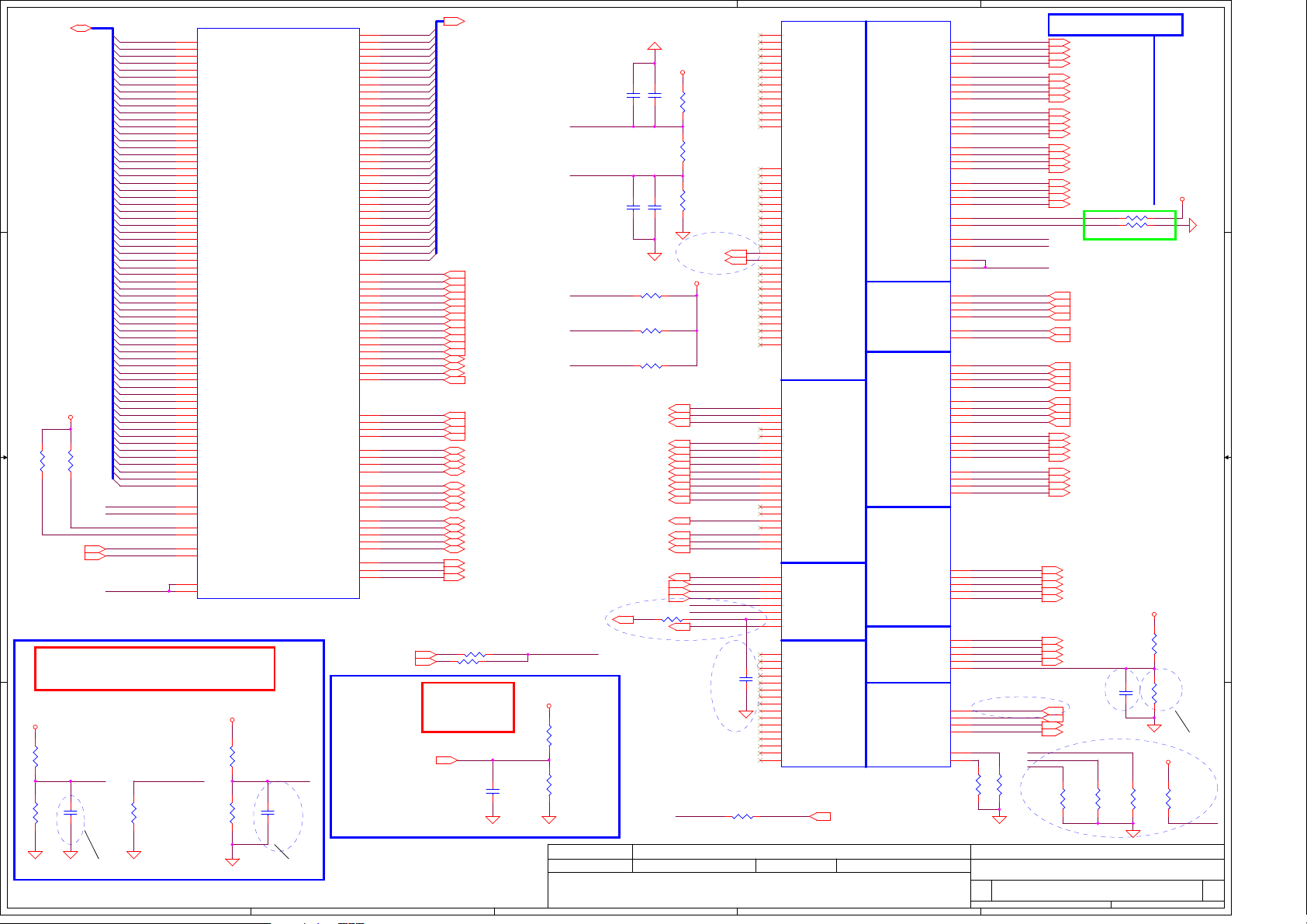

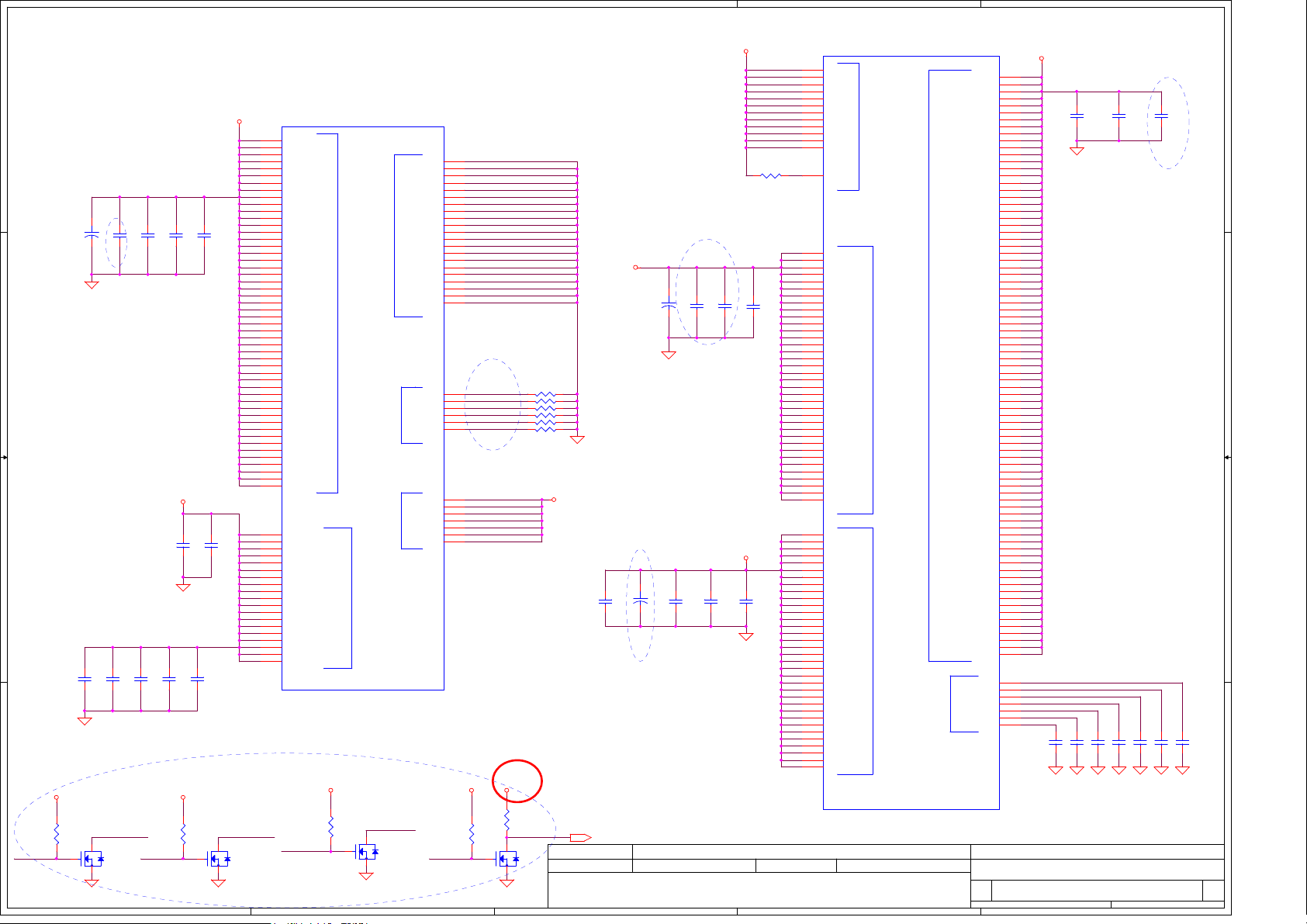

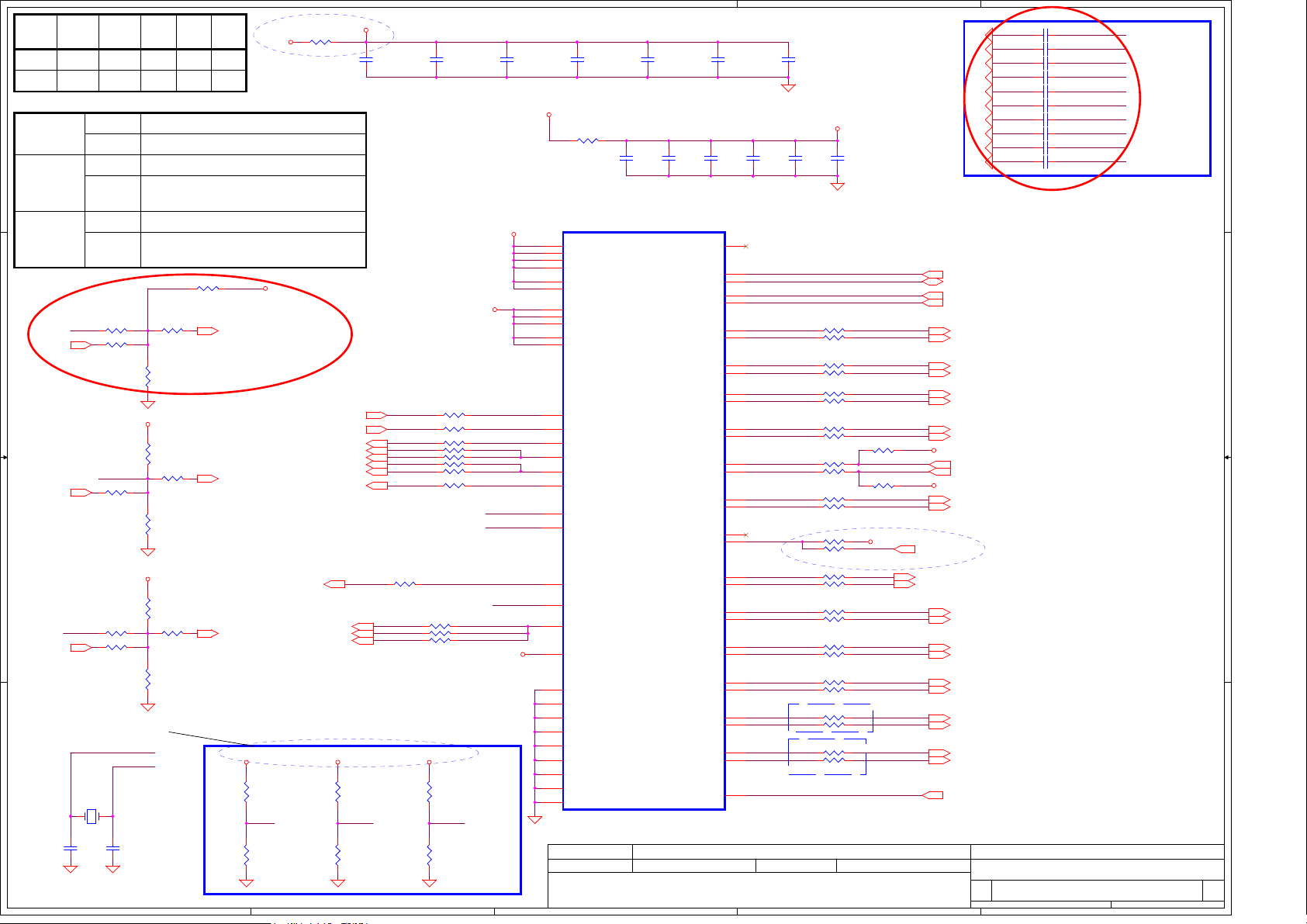

Page 4

5

D D

H_A#[ 3..16]7

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_NMI19

H_SMI#19

12

R1255

56_0402_5%@

B

2

C

Q85

MMBT3904_SOT23

H_ADSTB#0

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADSTB#1

H_A20M#

H_FER R#

H_IGNN E#

H_STPCLK#

H_INT R

H_NMI

H_SMI#

OCP# 20,44

H_ADSTB#07

H_REQ#07

H_REQ#17

H_REQ#27

H_REQ#37

H_REQ#47

C C

B B

A A

H_A#[ 17..35]7

H_ADSTB#17

H_A20M#19

H_FER R#19

H_IGNN E#19

H_STPCLK#19

H_INT R19

+VCCP

H_PROCH OT# OCP#

E

3 1

@

JP12A

J4

A[3]#

L5

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10]#

P5

A[11]#

P2

A[12]#

L2

A[13]#

P4

A[14]#

P1

A[15]#

R1

A[16]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17]#

U5

A[18]#

R3

A[19]#

W6

A[20]#

U4

A[21]#

Y5

A[22]#

U1

A[23]#

R4

A[24]#

T5

A[25]#

T3

A[26]#

W2

A[27]#

W5

A[28]#

Y4

A[29]#

U2

A[30]#

V4

A[31]#

W3

A[32]#

AA4

A[33]#

AB2

A[34]#

AA3

A[35]#

V1

ADSTB[1]#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD[01]

N5

RSVD[02]

T2

RSVD[03]

V3

RSVD[04]

B2

RSVD[05]

C3

RSVD[06]

D2

RSVD[07]

D22

RSVD[08]

D3

RSVD[09]

F6

RSVD[10]

Mero m Ball-out Rev 1a

ADDR GROUP 0 ADDR GROUP 1

ICH

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

XDP/ITP SIGNALS

DBR#

TH ERMAL

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

H CLK

BCLK[0]

BCLK[1]

RESERVED

conn@

TDI

4

3

XDP Connector

H_ADS#H_A#3

H1

H_BNR #

E2

H_BPR I#

G5

H_DEF ER#

H5

H_D RDY#

F21

H_ DBSY#

E1

H_BR0#

F1

H_IER R#

D20

H_INIT#

B3

H_LOCK#

H4

H_RESET#

C1

H_RS#0

F3

H_RS#1

F4

H_RS#2

G3

H_ TRDY#H_REQ#3

G2

H_HIT#

G6

H_HITM#

E4

XDP_BPM#0

AD4

XDP_BPM#1

AD3

XDP_BPM#2

AD1

XDP_BPM#3

AC4

XDP_BPM#4

AC2

XDP_BPM#5

AC1

XDP_TCK

AC5

XDP_TDI

AA6

XDP_TDO

AB3

XDP_TMS

AB5

XDP_TRST#

AB6

XDP_DBRESET#

C20

H_PROCH OT#

D21

H_THERMDA_R

A24

H_THE RMDC_R

B25

H_THERMTRIP#

C7

CLK_CP U_BCLK

A22

CLK_CP U_BCLK#

A21

1113 Add res isto rs in ser ies with th e diode sig nals going to ADM1032.

For Mero m, R1798 and R1799 a re 0ohm

For Penr yn, R17 98 and R179 9 are 100oh m.

H_ADS# 7

H_BNR # 7

H_BPR I# 7

H_DEF ER# 7

H_D RDY# 7

H_D BSY# 7

H_BR0# 7

H_INIT# 19

H_LOCK# 7

H_RESET# 7

H_RS#0 7

H_RS#1 7

H_RS#2 7

H_T RDY# 7

H_HIT# 7

H_HITM# 7

XDP_DBRESET# 20

R1798 0_0402_5%

1 2

R1799 0_0402_5%

1 2

R172

56_0402_5%

12

+VCCP

12

H_THERMDA

H_THERMDC

H_PROCH OT# 43

+VCCP

R410

68_0402_5%

H_THERMTRIP# 7,19

CLK_CP U_BCLK 15

CLK_CP U_BCLK# 15

H_THERMDA, H_THERMDC routing together,

Trace width / Spacing = 10 / 10 mil

H_PW RGOOD_R5

+VCCP +VCCP

0.1U_0402_16V4Z

1

C1099

2

2

layo ut n ote: Cha nge R237 to 649 ohm if using XTP to ITP adap ter

JP51

1

XDP_BPM#5

XDP_BPM#4

XDP_BPM#3

XDP_BPM#2

XDP_BPM#1

XDP_BPM#0

H_PW RGOOD_R

XDP_HOOK1

XDP_TCK

Thermal Sensor ADM1032ARMZ

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

conn@

1 2

2200P_0402_50V7K

+3VS

GND0

OBSFN_A0

OBSFN_A1

GND2

OBSDATA_A0

OBSDATA_A1

GND4

OBSDATA_A2

OBSDATA_A3

GND6

OBSFN_B0

OBSFN_B1

GND8

OBSDATA_B0

OBSDATA_B1

GND10

OBSDATA_B2

OBSDATA_B3

GND12

PWRGOOD/HOOK0

HOOK1

VCC_OBS_AB

HOOK2

HOOK3

GND14

SDA

SCL

TCK1

TCK0

GND16

SAMTE_BSH-030-01-L-D-A

C273

0.1U_0402_16V4Z

H_THERMDA

C264

H_THERMDC

R228

1 2

10K_0402_5%

ITPCLK/HOOK4

ITPCLK#/HOOK5

RESET#/HOOK6

+3VS

2

1

THERM#

OBSDATA_C0

OBSDATA_C1

OBSDATA_C2

OBSDATA_C3

OBSDATA_D0

OBSDATA_D1

OBSDATA_D2

OBSDATA_D3

VCC_OBS_CD

DBR#/HOOK7

2

GND1

4

OBSFN_C0

6

OBSFN_C1

8

GND3

10

12

14

GND5

16

18

20

GND7

22

OBSFN_D0

24

OBSFN_D1

26

GND9

28

30

32

GND11

34

36

38

GND13

40

42

44

46

48

50

GND15

52

TD0

54

TRST#

56

TDI

58

TMS

60

GND17

U16

1

VDD

2

D+

3

D-

THERM#4GND

ADM1032ARMZ-2REEL_MSOP8

Addres s:100_1100

PWM Fan Control circuit

+3VS

FAN_PWM31

THERM#

1

INB

2

INA

XDP_DBRESET#_R

R243

1 2

04/ 10 no stuff

XDP_TDI

XDP_TMS

XDP_TDO

XDP_BPM#5

XDP_HOOK1

XDP_TRST#

XDP_TCK

CLK_CPU_XDP

CLK_CPU_XDP#

XDP_TDO

XDP_TRST#

XDP_TDI

XDP_TMS

XDP_PRE

R143 54.9_0402_1%

1 2

R236 54.9_0402_1%

1 2

R1670 54.9_0402_1%

1 2

R241 54.9_0402_1%

1 2

R1430 54.9_0402_1%@

1 2

R237 51_0402_1%

1 2

R239 54.9_0402_1%

1 2

1K_0402_1%

H_RESET#H_RESET#_R

R1431

1 2

XDP_DBRESET#XDP_DBRESET#_R

12

200_0402_1%

R1432

R1433 0_0402_5%

1 2

Plac e R1 431 withi n 200ps (~1 ") to CPU

R227

8

SCLK

7

SDATA

6

ALERT#

5

ICH_SM _CLK20,25

ICH_SM_DA20,25

0308 change desig n

5

U24

P

4

O

G

TC7SH00FU_ SSOP5

3

ICH_SM_CLK

ICH_SM_DA

THERM_SCI#

+5VS

1 2

ICH_SM_CLK

ICH_SM_DA

ACES_85204-03001

10K_0402_5%

1

2

3

1

THERM_SCI# 20

conn@

JP8

1

2

G1

3

G2

+3VS

1K_0402_5%@

+VCCP

CLK_CPU_XDP 15

CLK_CPU_XDP# 15

4

5

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/02/13 2006/03/10

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

2

Date: Sheet of

Compal Electronics, Inc.

Merom(1/3)-AGTL+/XDP

LA -3 26 1P U MA

1

4 55Tuesday, March 27, 2007

0.4

Page 5

5

4

3

2

1

H_D #[0..15]7

D D

H_DSTBN#07

H_DSTBP#07

H_DIN V#07

H_D# [16..31]7

C C

H_DSTBN#17

H_DSTBP#17

H_DIN V#17

R1264 1K_0402_5%@

1 2

R1265 1K_0402_5%@

1 2

C1101 0.1U_0402_16V4Z@

1 2

CPU_BSEL015

CPU_BSEL115

CPU_BSEL215

T1

T2

T3

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DIN V#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DIN V#1 H_DIN V#3

V_CPU_GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

CPU_BSEL0 H_PW RGOOD

CPU_BSEL1

CPU_BSEL2

JP12B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H22

D[12]#

F26

D[13]#

K22

D[14]#

H23

D[15]#

J26

DSTBN[0]#

H26

DSTBP[0]#

H25

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L23

D[20]#

M24

D[21]#

L22

D[22]#

M23

D[23]#

P25

D[24]#

P23

D[25]#

P22

D[26]#

T24

D[27]#

R24

D[28]#

L25

D[29]#

T25

D[30]#

N25

D[31]#

L26

DSTBN[1]#

M26

DSTBP[1]#

N24

DINV[1]#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

TEST3

AF26

TEST4

AF1

TEST5

A26

TEST6

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

Mero m Ball-out Rev 1 a

conn@

DATA GRP 1

MISC

DATA GRP 0

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

DATA GRP 2DATA GRP 3

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DIN V#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#3

H_DSTBP#3

COMP0

COMP1

COMP2

COMP3

H_DPRSTP#

H_DPSLP#

H_DPW R#

H_CPUSLP #

H_PSI#

R1436

1K_0402_5%

H_PW RGOOD_R

12

layo ut n ote: Rou te TES T3 & TEST5 traces on g round refer enced layer to the TPs

CPU_BSEL CPU_BSEL2 CPU_BSEL1

166

B B

200

0 1

0

1

CPU_BSEL0

1

0

H_D# [32..47] 7

H_DSTBN#2 7

H_DSTBP#2 7

H_DIN V#2 7

H_D# [48..63] 7

H_DSTBN#3 7

H_DSTBP#3 7

H_DIN V#3 7

H_DPRSTP# 7,19,43

H_DPSLP# 19

H_DPW R# 7

H_PW RGOOD 19

H_CPUSLP # 7

H_PSI# 43

H_PW RGOOD_R 4

12

R355

R1220

27.4_0402_1%

54.9_0402_1%

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

mils away from any other

toggling signal.

COMP[0,2] trace width is

18 mils. COMP[1,3] trace

width is 4 mils.

12

R245

R244

54.9_0402_1%

27.4_0402_1%

12

12

+VCC_C ORE +VCC_C ORE

JP12C

A7

VCC[001]

A9

VCC[002]

A10

VCC[003]

A12

VCC[004]

A13

VCC[005]

A15

VCC[006]

A17

VCC[007]

A18

VCC[008]

A20

VCC[009]

B7

VCC[010]

B9

VCC[011]

B10

VCC[012]

B12

VCC[013]

B14

VCC[014]

B15

VCC[015]

B17

VCC[016]

B18

VCC[017]

B20

VCC[018]

C9

VCC[019]

C10

VCC[020]

C12

VCC[021]

C13

VCC[022]

C15

VCC[023]

C17

VCC[024]

C18

VCC[025]

D9

VCC[026]

D10

VCC[027]

D12

VCC[028]

D14

VCC[029]

D15

VCC[030]

D17

VCC[031]

D18

VCC[032]

E7

VCC[033]

E9

VCC[034]

E10

VCC[035]

E12

VCC[036]

E13

VCC[037]

E15

VCC[038]

E17

VCC[039]

E18

VCC[040]

E20

VCC[041]

F7

VCC[042]

F9

VCC[043]

F10

VCC[044]

F12

VCC[045]

F14

VCC[046]

F15

VCC[047]

F17

VCC[048]

F18

VCC[049]

F20

VCC[050]

AA7

VCC[051]

AA9

VCC[052]

AA10

VCC[053]

AA12

VCC[054]

AA13

VCC[055]

AA15

VCC[056]

AA17

VCC[057]

AA18

VCC[058]

AA20

VCC[059]

AB9

VCC[060]

AC10

VCC[061]

AB10

VCC[062]

AB12

VCC[063]

AB14

VCC[064]

AB15

VCC[065]

AB17

VCC[066]

AB18

VCC[067]

Mero m Ball-out Rev 1a

conn@

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA[01]

VCCA[02]

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

R1434 0_0402_5%

G21

V6

R1435 0_0402_5%

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

VCCSENS E

AF7

VSSSENSE

AE7

.

Length match within 25 mils.

+VCCP

12

12

C1100

CPU_V ID0 43

CPU_V ID1 43

CPU_V ID2 43

CPU_V ID3 43

CPU_V ID4 43

CPU_V ID5 43

CPU_V ID6 43

VCCSENSE 43

VSSSENSE 4 3

1

+

330U_D2E_2.5VM _R7

2

0228 change value

1

1

C531

C520

2

2

10U_0805_6.3V6M

Near pin B26

+1.5VS

0.01U_0402_16V7K

The trace width/space/other is

20/7/25.

+VCC_ CORE

1 2

1 2

R1269

100_0402_1%

R1270

100_0402_1%

VCCSENS E

VSSSENSE

V_CPU_GTLREF

+VCCP

12

R1268

1K_0402_1%

12

R1271

2K_0402_1%

Close to CPU pin AD26

within 500mils.

A A

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/02/13 2006/03/10

Compal Secret Data

Deciphered Date

2

Close to CPU pin

within 500mils.

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet of

Compal Electronics, Inc.

Merom(2/3)-AGTL+/PWR

LA -3 26 1P U MA

1

5 55Tuesday, March 27, 2007

0.4

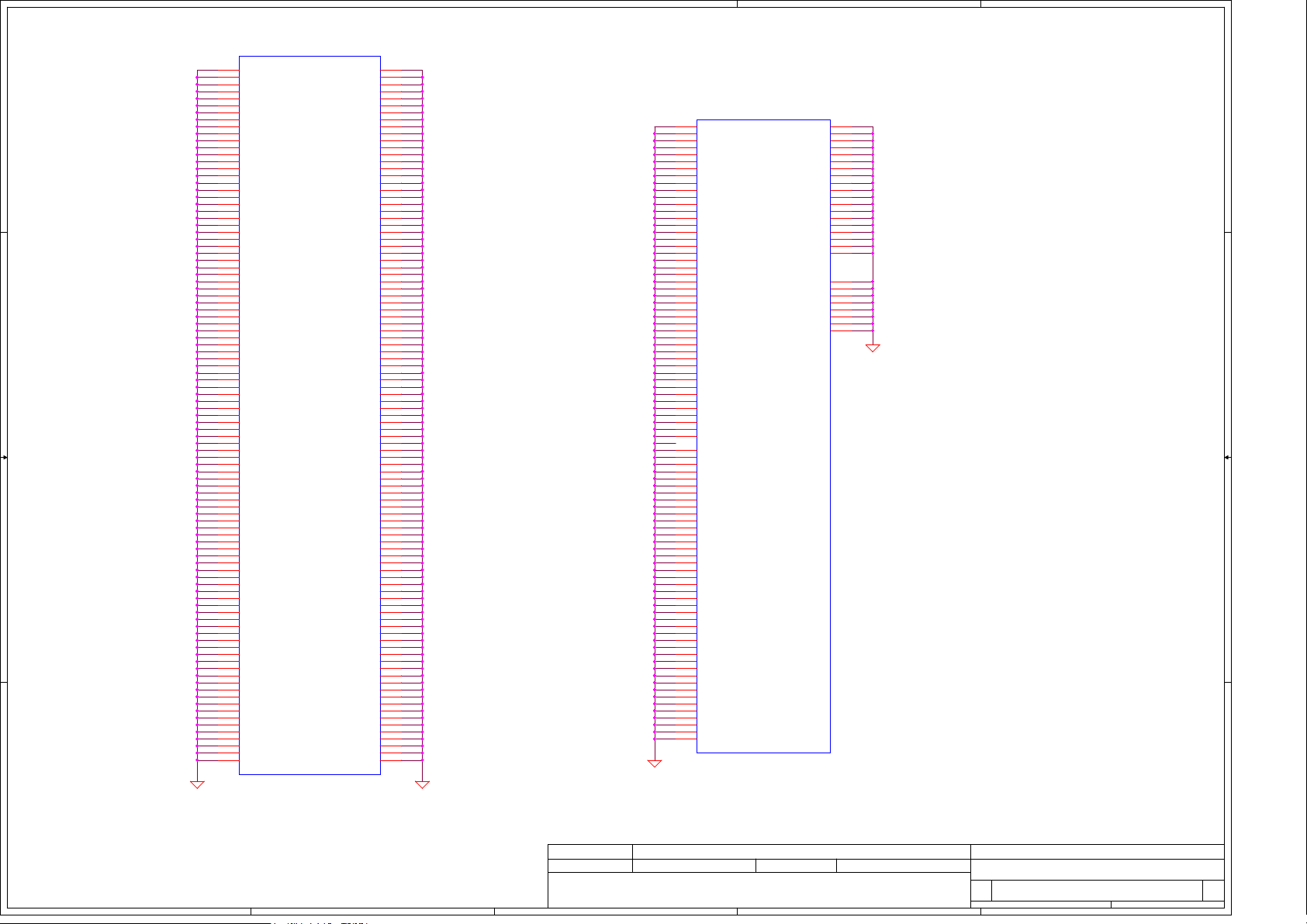

Page 6

5

Place these capac itors on L8

D D

JP12D

A4

VSS[001]

A8

VSS[002]

A11

VSS[003]

A14

VSS[004]

A16

VSS[005]

A19

VSS[006]

A23

VSS[007]

AF2

VSS[008]

B6

VSS[009]

B8

VSS[010]

B11

VSS[011]

B13

VSS[012]

B16

VSS[013]

B19

VSS[014]

B21

VSS[015]

B24

VSS[016]

C5

VSS[017]

C8

VSS[018]

C11

VSS[019]

C14

VSS[020]

C16

VSS[021]

C19

VSS[022]

C2

VSS[023]

C22

VSS[024]

C25

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

D11

C C

B B

VSS[029]

D13

VSS[030]

D16

VSS[031]

D19

VSS[032]

D23

VSS[033]

D26

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

E11

VSS[038]

E14

VSS[039]

E16

VSS[040]

E19

VSS[041]

E21

VSS[042]

E24

VSS[043]

F5

VSS[044]

F8

VSS[045]

F11

VSS[046]

F13

VSS[047]

F16

VSS[048]

F19

VSS[049]

F2

VSS[050]

F22

VSS[051]

F25

VSS[052]

G4

VSS[053]

G1

VSS[054]

G23

VSS[055]

G26

VSS[056]

H3

VSS[057]

H6

VSS[058]

H21

VSS[059]

H24

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

K23

VSS[067]

K26

VSS[068]

L3

VSS[069]

L6

VSS[070]

L21

VSS[071]

L24

VSS[072]

M2

VSS[073]

M5

VSS[074]

M22

VSS[075]

M25

VSS[076]

N1

VSS[077]

N4

VSS[078]

N23

VSS[079]

N26

VSS[080]

VSS[081]P3VSS[162]

Mero m Ball-out Rev 1a

conn@

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[163]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

.

(Nort h side ,Secon dary L ayer)

Place these capac itors on L8

(Nort h side ,Secon dary L ayer)

Place these capac itors on L8

(Sort h side ,Secon dary L ayer)

Place these capac itors on L8

(Sort h side ,Secon dary L ayer)

0314 change to mo unt

330U_D2E_2.5VM _R7

+VCCP

1

C940

0.1U_0402_10V6K

2

4

+VCC_ CORE

1

+

C931

2

+VCC_ CORE

1

C899

10U_0805_6.3V6M

2

+VCC_ CORE

1

C907

10U_0805_6.3V6M

2

+VCC_ CORE

1

C915

10U_0805_6.3V6M

2

+VCC_ CORE

1

C923

10U_0805_6.3V6M

2

Near CPU CORE regulator

330U_D2E_2.5VM_R7

1

+

C932

C933

2

330U_D2E_2.5VM _R7

1

C941

0.1U_0402_10V6K

2

1

C900

10U_0805_6.3V6M

2

1

C908

10U_0805_6.3V6M

2

1

C916

10U_0805_6.3V6M

2

1

C924

10U_0805_6.3V6M

2

1

+

C935

2

330U_D2E_2.5VM_R7

1

C942

0.1U_0402_10V6K

2

1

+

2

1

C901

10U_0805_6.3V6M

2

1

C909

10U_0805_6.3V6M

2

1

C917

10U_0805_6.3V6M

2

1

C925

10U_0805_6.3V6M

2

330U_D2E_2.5VM _R7

1

+

C937

C936

2

330U_D2E_2.5VM _R7

1

C943

0.1U_0402_10V6K

2

3

1

C902

10U_0805_6.3V6M

2

1

C910

10U_0805_6.3V6M

2

1

C918

10U_0805_6.3V6M

2

1

C926

10U_0805_6.3V6M

2

ESR <= 1.5m ohm

Capacitor > 1980uF

1

1

+

+

C934

@

2

820U_E9_2_5V_M_R7

2

1

C944

0.1U_0402_10V6K

2

1

C903

10U_0805_6.3V6M

2

1

C911

10U_0805_6.3V6M

2

1

C919

10U_0805_6.3V6M

2

1

C927

10U_0805_6.3V6M

2

Plac e these inside

sock et cavity o n L8

(North side

Seco ndary)

1

C945

0.1U_0402_10V6K

2

1

C904

10U_0805_6.3V6M

2

1

C912

10U_0805_6.3V6M

2

1

C920

10U_0805_6.3V6M

2

1

C928

10U_0805_6.3V6M

2

2

1

C905

10U_0805_6.3V6M

2

1

C913

10U_0805_6.3V6M

2

1

C921

10U_0805_6.3V6M

2

1

C929

10U_0805_6.3V6M

2

1

C906

10U_0805_6.3V6M

2

1

C914

10U_0805_6.3V6M

2

1

C922

10U_0805_6.3V6M

2

1

C930

10U_0805_6.3V6M

2

1

Mid Frequence Decoupling

A A

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/02/13 2006/03/10

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

2

Date: Sheet of

Compal Electronics, Inc.

Merom(3/3)-GND&Bypass

LA -3 26 1P U MA

1

6 55Tuesday, March 27, 2007

0.4

Page 7

5

W10

AD12

AC14

AD11

AC11

AG3

AJ14

AE11

AH12

AH13

M10

N12

AE3

AD9

AC9

AC7

AB2

AD7

AB1

AC6

AE2

AC5

AH8

AE9

AH5

AE7

AE5

AH2

E2

G2

G7

M6

H7

H3

G4

F3

N8

H2

N9

H5

P13

K9

M2

Y8

V4

M3

J1

N5

N3

W6

W9

N2

Y7

Y9

P4

W3

N1

Y3

AJ9

AJ5

AJ6

AJ7

AJ2

AJ3

B3

C2

W1

W2

B6

E5

B9

A9

U15A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_CPURST#

H_CPUSLP#

H_AVREF

H_DVREF

CRES TLINE_1p0

H_ADSTB#_0

H_ADSTB#_1

H_DEFER#

HOST

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_D #[0..63]5

D D

C C

+VCCP

12

12

R1197

R1196

54.9_0402_1%

54.9_0402_1%

H_RESET#4

H_CPUSLP #5

B B

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SW NG

H_RCOMP

H_SCOMP

H_SCOMP#

H_RESET#

H_CPUSLP #

H_VRE F

layo ut note:

Rout e H_ SCOM P an d H_ SCOMP # with trac e width, sp acing and i mpedance (5 5 ohm) same as FSB dat a traces

Layout Note:

H_RCOM P / H_VREF / H_SWNG

trace width and spacing is 10/20

+VCCP

12

1K_0402_1%

R1208

0.1U_0402_16V4Z

H_VRE F

12

A A

1

C60

2

R1212

2K_0402_1%

H_RCOMP

12

R1199

24.9_0402_1%

12

R1206

221_0603_1%

H_SW NG

12

1

R1210

C896

2

100_0402_1%

0.1U_0402_16V4Z

Near B3 pinwith in 100 mils from N B

5

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_BNR#

H_BPRI#

H_BREQ#

H_DBSY#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_RS#_0

H_RS#_1

H_RS#_2

J13

B11

C11

M11

C15

F16

L13

G17

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D17

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

G12

H17

G20

C8

E8

F12

D6

C10

AM5

AM7

H8

K7

E4

C6

G10

B7

K5

L2

AD13

AE13

M7

K3

AD2

AH11

L7

K2

AC2

AJ10

M14

E13

A11

H13

B12

E12

D7

D8

4

PM_PWROK20,31,45

V_DDR _MCH_REF13,14,42

4

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR #

H_BPR I#

H_BR0#

H_DEF ER#

H_ DBSY#

CLK_MCH_BCLK

CLK_MCH_BCLK#

H_DPW R#

H_D RDY#

H_HIT#

H_HITM#

H_LOCK#

H_ TRDY#

H_DIN V#0

H_DIN V#1

H_DIN V#2

H_DIN V#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

VGATE20,31

Layout Note:

V_DDR_MCH_REF

trace width and

spacin g is 20/20.

H_A#[ 3..35] 4

H_ADS# 4

H_ADSTB#0 4

H_ADSTB#1 4

H_BNR# 4

H_BPR I# 4

H_BR0# 4

H_DEF ER# 4

H_DB SY# 4

CLK_MCH_BCLK 15

CLK_MCH_BCLK# 15

H_DPW R# 5

H_D RDY# 4

H_HIT# 4

H_HITM# 4

H_LOCK# 4

H_TR DY# 4

H_DIN V#0 5

H_DIN V#1 5

H_DIN V#2 5

H_DIN V#3 5

H_DSTBN#0 5

H_DSTBN#1 5

H_DSTBN#2 5

H_DSTBN#3 5

H_DSTBP#0 5

H_DSTBP#1 5

H_DSTBP#2 5

H_DSTBP#3 5

H_REQ#0 4

H_REQ#1 4

H_REQ#2 4

H_REQ#3 4

H_REQ#4 4

H_RS#0 4

H_RS#1 4

H_RS#2 4

R1483 0_0402_5%@

12

12

R1484 0_0402_5%

V_DDR _MCH_REF

1

C895

2

0.1U_0402_16V4Z

3

2.2U_0 603_6.3V4Z

2.2U_0 603_6.3V4Z

PM_EXTTS#0

PM_EXTTS#1

CLKREQ#_B DMI_TXN0

MCH_CLKSEL015

MCH_CLKSEL115

MCH_CLKSEL215

PM_BMBUSY#20

0612 a dd

1128 Install R1739

1226 Add C

0309 add

+1.8V

12

12

SMRCOMP_VOH

SMRCOMP_VOL

H_THERMTRIP#4,19

PM_POK_R

R1201

1K_0402_1%@

R1204

1K_0402_1%

@

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

+1.8V

2

2

12

C1103

C1105

CFG59

CFG6

CFG79

CFG89

CFG99

R1437

1

1K_0402_1%

0.01U_0402_25V7K

12

R31

3.01K_0402_1%

NA le ad free

12

R1438

1

1K_0402_1%

2

0612 a dd

0.01U_0402_25V7K

DDR_A_MA1413

DDR_B_MA1414

+3VS

12

12

12

MCH_CLKSEL0

MCH_CLKSEL1

MCH_CLKSEL2

CFG5

CFG6

CFG7

CFG9

CFG10

CFG11

CFG12

CFG13

CFG16

CFG18

CFG19

CFG20

PM_BMBUSY#

H_DPRSTP#

PM_EXTTS#0

PM_EXTTS#1

PM_POK_R

PLT_RST#_R

THERMTRIP#

12

DPRSLPVR

C1370

R1446

100_0402_5%

1

C1102

1

2

C1104

R1439

10K_0402_5%

R1440

10K_0402_5%

R1441

<>

10K_0402_5%

CFG10

CFG11

CFG129

CFG139

CFG169

CFG18

CFG199

CFG209

H_DPRSTP#5,19,43

PM_EXTTS#013

PM_EXTTS#114

R1739 0_0402_5%

DPRSLPVR20,43

2006/02/13 2006/03/10

U15B

P36

RSVD1

P37

RSVD2

R35

RSVD3

N35

RSVD4

AR12

RSVD5

AR13

RSVD6

AM12

RSVD7

AN13

RSVD8

J12

RSVD9

AR37

RSVD10

AM36

RSVD11

AL36

RSVD12

AM37

RSVD13

D20

RSVD14

H10

RSVD20

B51

RSVD21

BJ20

RSVD22

BK22

RSVD23

BF19

RSVD24

BH20

RSVD25

BK18

RSVD26

BJ18

RSVD27

BF23

RSVD28

BG23

RSVD29

BC23

RSVD30

BD24

RSVD31

BJ29

RSVD32

BE24

RSVD33

BH39

RSVD34

AW20

RSVD35

BK20

RSVD36

C48

RSVD37

D47

RSVD38

B44

RSVD39

C44

RSVD40

A35

RSVD41

B37

RSVD42

B36

RSVD43

B34

RSVD44

C34

RSVD45

P27

CFG_0

N27

CFG_1

N24

CFG_2

C21

CFG_3

C23

CFG_4

F23

CFG_5

N23

CFG_6

G23

CFG_7

J20

CFG_8

C20

CFG_9

R24

CFG_10

L23

CFG_11

J23

CFG_12

E23

CFG_13

E20

CFG_14

K23

CFG_15

M20

CFG_16

M24

CFG_17

L32

CFG_18

N33

CFG_19

L35

CFG_20

G41

PM_BM_BUSY#

L39

PM_DPRSTP#

L36

PM_EXT_TS#_0

J36

PM_EXT_TS#_1

AW49

PWROK

AV20

RSTIN#

N20

THERMTRIP#

G36

DPRSLPVR

BJ51

NC_1

BK51

NC_2

BK50

1

NC_3

BL50

NC_4

BL49

NC_5

BL3

NC_6

2

BL2

NC_7

0.1U_0402_16V4Z

BK1

NC_8

BJ1

NC_9

E1

NC_10

A5

NC_11

C51

NC_12

B50

NC_13

A50

NC_14

A49

NC_15

BK2

NC_16

CRES TLINE_1p0

PLT_RST#PLT_RST#_R

12

Compal Secret Data

Deciphered Date

2

SM_CK_0

SM_CK_1

SM_CK_3

SM_CK_4

SM_CK#_0

SM_CK#_1

SM_CK#_3

SM_CK#_4

SM_CKE_0

SM_CKE_1

SM_CKE_3

SM_CKE_4

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF_0

DDR M UXIN GCLK

SM_VREF_1

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

CFGRS VD

PM

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VR_EN

GRA PHI CS V ID

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

ME

NC

SDVO_CTRL_CLK

SDVO_CTRL_DATA

CLK_REQ#

ICH_SYNC#

MI SC

PLT_RST# 16,18 ,22,30

083 0 A dd pu ll- up an d pul l-dow n re sisto r.

2

M_CLK_DD R0

AV29

M_CLK_DD R1

BB23

M_CLK_DD R2

BA25

M_CLK_DD R3

AV23

M_CLK_DDR#0

AW30

M_CLK_DDR#1

BA23

M_CLK_DDR#2

AW25

M_CLK_DDR#3

AW23

DDR_CKE 0_DIMMA

BE29

DDR_CKE 1_DIMMA

AY32

DDR_CKE 2_DIMMB

BD39

DDR_CKE 3_DIMMB

BG37

DDR_C S0_DIMMA#

BG20

DDR_C S1_DIMMA#

BK16

DDR_C S2_DIMMB#

BG16

DDR_C S3_DIMMB#

BE13

M_ODT0

BH18

M_ODT1

BJ15

M_ODT2

BJ14

M_ODT3

BE16

SMRCOMP

BL15

SMRCOMP#

BK14

SMRCOMP_VOH

BK31

SMRCOMP_VOL

BL31

AR49

V_DDR _MCH_REF

AW4

CLK_M CH_DREFCLK

B42

CLK_M CH_DREFCLK#

C42

MCH_ SSCDREFCLK

H48

MCH_ SSCDREFCLK#

H47

CLK_MCH_3GPLL

K44

CLK_MCH_3GPLL#

K45

AN47

DMI_TXN1

AJ38

DMI_TXN2

AN42

DMI_TXN3

AN46

DMI_TXP0

AM47

DMI_TXP1

AJ39

DMI_TXP2

AN41

DMI_TXP3

AN45

DMI_RXN0

AJ46

DMI_RXN1

AJ41

DMI_RXN2

AM40

DMI_RXN3

AM44

DMI_RXP0

AJ47

DMI_RXP1

AJ42

DMI_RXP2

AM39

DMI_RXP3

AM43

DFGT_ VID_0

E35

DFGT_ VID_1

A39

DFGT_ VID_2

C38

DFGT_ VID_3

B39

DFGT_VR_E N

E36

CL_CLK0

AM49

CL_CLK

CL_DATA0

AK50

M_PWROK

AT43

CL_RST#

AN49

CL_VRE F CL_VRE F

AM50

062 1 a dd CL K a nd DA T fo r DVI

SDVO_SCLK

H35

SDVO_SDAT

K36

CLKREQ#_B

G39

MCH _ICH_SYNC #

G40

A37

TEST_1

R32

TEST_2

12

R1444

20K_0402_5%

12

R1445

0_0402_5%

Title

CRESTLINE(1/6)-AGTL+/DMI/DDR2

Size Doc ument Number Re v

Cus tom

LA -3 26 1P U MA

Date: Sheet of

1

For Crestli ne: 20ohm

For Calero: 80.6ohm

M_CLK_DD R0 13

M_CLK_DD R1 13

M_CLK_DD R2 14

M_CLK_DD R3 14

M_CLK_DD R#0 13

M_CLK_DD R#1 13

M_CLK_DD R#2 14

M_CLK_DD R#3 14

DDR_CKE 0_DIMMA 13

DDR_CKE 1_DIMMA 13

DDR_CKE 2_DIMMB 14

DDR_CKE 3_DIMMB 14

DDR_CS0_D IMMA# 13

DDR_CS1_D IMMA# 13

DDR_CS2_D IMMB# 14

DDR_CS3_D IMMB# 14

M_ODT0 13

M_ODT1 13

M_ODT2 14

DFGT_ VID_0

DFGT_ VID_1

DFGT_ VID_3

R1786

M_ODT3 14

CLK_M CH_DREFCLK 15

CLK_M CH_DREFCLK# 1 5

MCH_ SSCDREFCLK 1 5

MCH_ SSCDREFCLK# 15

CLK_MCH_3GPLL 15

CLK_MCH_3GPLL# 15

DMI_TXN0 20

DMI_TXN1 20

DMI_TXN2 20

DMI_TXN3 20

DMI_TXP0 20

DMI_TXP1 20

DMI_TXP2 20

DMI_TXP3 20

DMI_RXN0 20

DMI_RXN1 20

DMI_RXN2 20

DMI_RXN3 20

DMI_RXP0 20

DMI_RXP1 20

DMI_RXP2 20

DMI_RXP3 20

DFGT_ VID_0 45

DFGT_ VID_1 45

DFGT_ VID_2 45

DFGT_ VID_3 45

DFGT_VR_E N 45

CL_CLK0 20

CL_DATA0 20

M_PWROK 20,35

CL_RST# 20

0.1U_0402_16V4Z

SDVO_SCLK 16

SDVO_SDAT 16+VCCP

CLKREQ#_B 15

MCH _ICH_SYNC # 20

12

22K_0402_5%

20_0402_1%

R1194

R1195 20_0402_1%

C1106

+1.25VM_AXD

1

2

12

12

12

R1442

1K_0402_1%

12

R1443

392_0402_1%

04/ 10 ch ange size

+3VS

12

12

22K_0402_5%

R1787

22K_0402_5%

R1789

R1788

Compal Electronics, Inc.

7 55Tuesday, March 27, 2 007

1

+1.8V

12

22K_0402_5%

DFGT_ VID_2

0.4

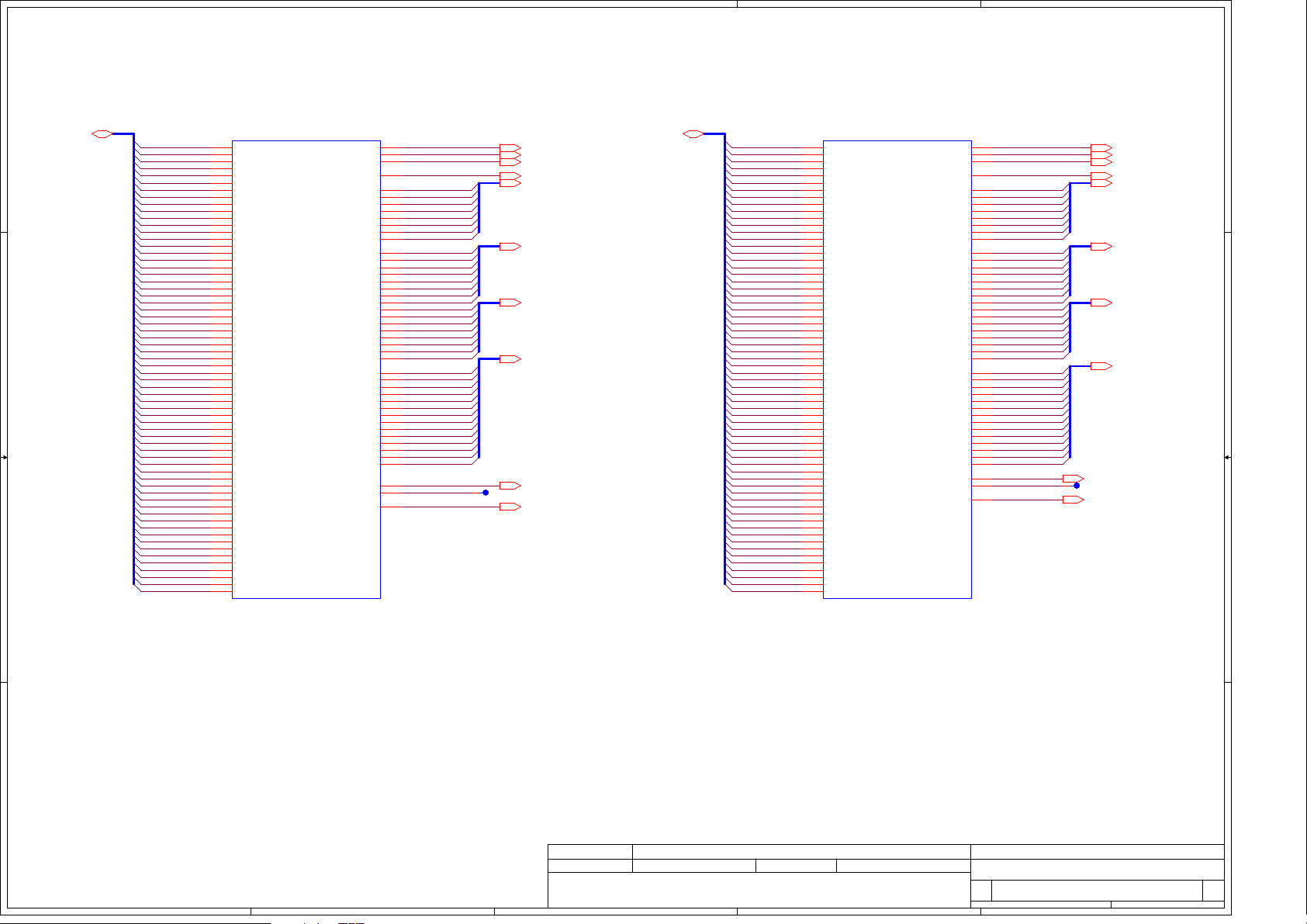

Page 8

5

D D

DDR_ A_D[0..63 ]13

C C

B B

DDR_A _D0

DDR_A _D1

DDR_A _D2

DDR_A _D3

DDR_A _D4

DDR_A _D5

DDR_A _D6

DDR_A _D7

DDR_A _D8

DDR_A _D9

DDR_A _D10

DDR_A _D11

DDR_A _D12

DDR_A _D13

DDR_A _D14

DDR_A _D15

DDR_A _D16

DDR_A _D17

DDR_A _D18

DDR_A _D19

DDR_A _D20

DDR_A _D21

DDR_A _D22

DDR_A _D23

DDR_A _D24

DDR_A _D25

DDR_A _D26

DDR_A _D27

DDR_A _D28

DDR_A _D29

DDR_A _D30

DDR_A _D31

DDR_A _D32

DDR_A _D33

DDR_A _D34

DDR_A _D35

DDR_A _D36

DDR_A _D37

DDR_A _D38

DDR_A _D39

DDR_A _D40

DDR_A _D41

DDR_A _D42

DDR_A _D43

DDR_A _D44

DDR_A _D45

DDR_A _D46

DDR_A _D47

DDR_A _D48

DDR_A _D49

DDR_A _D50

DDR_A _D51

DDR_A _D52

DDR_A _D53

DDR_A _D54

DDR_A _D55

DDR_A _D56

DDR_A _D57

DDR_A _D58

DDR_A _D59

DDR_A _D60

DDR_A _D61

DDR_A _D62

DDR_A _D63

AR43

AW44

BA45

AY46

AR41

AR45

AT42

AW47

BB45

BF48

BG47

BJ45

BB47

BG50

BH49

BE45

AW43

BE44

BG42

BE40

BF44

BH45

BG40

BF40

AR40

AW40

AT39

AW36

AW41

AY41

AV38

AT38

AV13

AT13

AW11

AV11

AU15

AT11

BA13

BA11

BE10

BD10

BD8

AY9

BG10

AW9

BD7

BB9

BB5

AY7

AT5

AT7

AY6

BB7

AR5

AR8

AR9

AN3

AM8

AN10

AT9

AN9

AM9

AN11

U15D

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

CRES TLINE_1p0

DDR SYSTEM MEMORY A

SA_BS_0

SA_BS_1

SA_BS_2

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVEN#

SA_WE#

4

DDR_A_BS 0

BB19

BK19

BF29

BL17

AT45

BD44

BD42

AW38

AW13

BG8

AY5

AN6

AT46

BE48

BB43

BC37

BB16

BH6

BB2

AP3

AT47

BD47

BC41

BA37

BA16

BH7

BC1

AP2

BJ19

BD20

BK27

BH28

BL24

BK28

BJ27

BJ25

BL28

BA28

BC19

BE28

BG30

BJ16

BE18

AY20

BA19

DDR_A_BS 1

DDR_A_BS 2

DDR_A _CAS#

DDR_A_DM 0

DDR_A_DM 1

DDR_A_DM 2

DDR_A_DM 3

DDR_A_DM 4

DDR_A_DM 5

DDR_A_DM 6

DDR_A_DM 7

DDR_A _DQS0

DDR_A _DQS1

DDR_A _DQS2

DDR_A _DQS4

DDR_A _DQS5

DDR_A _DQS6

DDR_A _DQS7

DDR_A _DQS#0

DDR_A _DQS#1

DDR_A _DQS#2

DDR_A _DQS#3

DDR_A _DQS#4

DDR_A _DQS#5

DDR_A _DQS#6

DDR_A _DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A _RAS#

SA_RCVEN #

DDR_A_W E#

DDR_A_BS 0 13

DDR_A_BS 1 13

DDR_A_BS 2 13

DDR_A _CAS# 13 DDR_B _CAS# 14

DDR_A _DM[0..7] 13

DDR_ A_DQS[0.. 7] 13

DDR_A _DQS#[0.. 7] 13

DDR_A _MA[0..13] 13

DDR_A _RAS# 13

T5

DDR_A_W E# 13

3

DDR_ B_D[0..63 ]14

DDR_B _D0

DDR_B _D1

DDR_B _D2

DDR_B _D3

DDR_B _D4

DDR_B _D5

DDR_B _D6

DDR_B _D7

DDR_B _D8

DDR_B _D9

DDR_B _D10

DDR_B _D11

DDR_B _D12

DDR_B _D13

DDR_B _D14

DDR_B _D15

DDR_B _D16

DDR_B _D17

DDR_B _D18DDR_A _DQS3

DDR_B _D19

DDR_B _D20

DDR_B _D21

DDR_B _D22

DDR_B _D23

DDR_B _D24

DDR_B _D25

DDR_B _D26

DDR_B _D27

DDR_B _D28

DDR_B _D29

DDR_B _D30

DDR_B _D31

DDR_B _D32

DDR_B _D33

DDR_B _D34

DDR_B _D35

DDR_B _D36

DDR_B _D37

DDR_B _D38

DDR_B _D39

DDR_B _D40

DDR_B _D41

DDR_B _D43

DDR_B _D44

DDR_B _D45

DDR_B _D46

DDR_B _D47

DDR_B _D48

DDR_B _D49

DDR_B _D50

DDR_B _D51

DDR_B _D52

DDR_B _D53

DDR_B _D54

DDR_B _D55

DDR_B _D56

DDR_B _D57

DDR_B _D58

DDR_B _D59

DDR_B _D60

DDR_B _D61

DDR_B _D62

DDR_B _D63

AP49

AR51

AW50

AW51

AN51

AN50

AV50

AV49

BA50

BB50

BA49

BE50

BA51

AY49

BF50

BF49

BJ50

BJ44

BJ43

BL43

BK47

BK49

BK43

BK42

BJ41

BL41

BJ37

BJ36

BK41

BJ40

BL35

BK37

BK13

BE11

BK11

BC11

BC13

BE12

BC12

BG12

BJ10

BK5

BK9

BK10

BH5

BG1

BC2

BK3

BE4

BD3

BA3

BB3

AR1

AU2

BL9

BL5

BJ8

BJ6

BF4

BJ2

AT3

AY2

AY3

AT2

2

U15E

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

CRES TLINE_1p0

1

DDR_B_BS0

AY17

SB_BS_0

SB_BS_1

SB_BS_2

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVEN#

SB_WE#

DDR SYSTEM MEMORY B

BG18

BG36

BE17

AR50

BD49

BK45

BL39

BH12

BJ7

BF3

AW2

AT50

BD50

BK46

BK39

BJ12

BL7

BE2

AV2

AU50

BC50

BL45

BK38

BK12

BK7

BF2

AV3

BC18

BG28

BG25

AW17

BF25

BE25

BA29

BC28

AY28

BD37

BG17

BE37

BA39

BG13

AV16

AY18

BC17

DDR_B_BS 1

DDR_B_BS 2

DDR_B _CAS#

DDR_B_DM 0

DDR_B_DM 1

DDR_B_DM 2

DDR_B_DM 3

DDR_B_DM 4

DDR_B_DM 5

DDR_B_DM 6

DDR_B_DM 7

DDR_B _DQS0

DDR_B _DQS1

DDR_B _DQS2

DDR_B _DQS3

DDR_B _DQS4

DDR_B _DQS5

DDR_B _DQS6

DDR_B _DQS7

DDR_B _DQS#0

DDR_B _DQS#1

DDR_B _DQS#2

DDR_B _DQS#3

DDR_B _DQS#4

DDR_B _DQS#5

DDR_B _DQS#6

DDR_B _DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10DDR_B _D42

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B _RAS#

SB_RCVEN #

DDR_B_W E#

DDR_B _RAS# 14

T4

DDR_B_W E# 14

DDR_B_BS 0 14

DDR_B_BS 1 14

DDR_B_BS 2 14

DDR_B _DM[0..7] 14

DDR_ B_DQS[0.. 7] 14

DDR_B _DQS#[0.. 7] 14

DDR_B _MA[0..13] 14

A A

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2006/02/13 2006/03/10

Compal Secret Data

Deciphered Date

Title

Size Doc ument Number Re v

Cus tom

2

Date: Sheet of

Compal Electronics, Inc.

CRESTLINE((2/6)-DDR2 A/B CH

LA -3 26 1P U MA

8 55Tuesday, March 27, 2 007

1

0.4

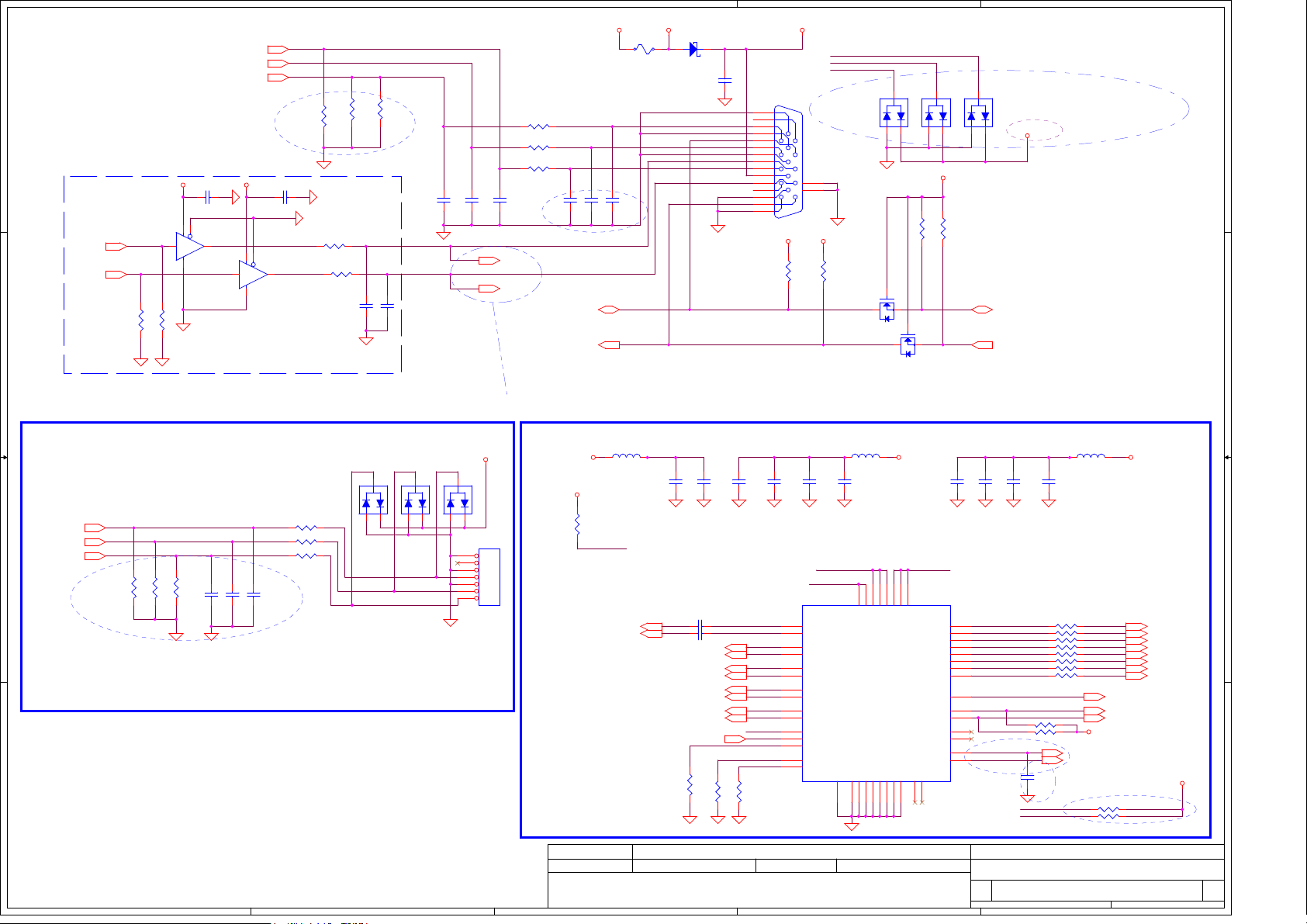

Page 9

5

For Crestli ne:2.4kohm

For Calero: 1.5Kohm

+3VS

M_COMP

M_LUMA

M_CRMA

R175

M_BLUE

M_GREEN

M_RED

R180

BLON_PWM

ENABLT

DDC2_ CLK

DDC2_DAT A

ENAVDD

2.4K_0402_1%

R1447

TXCLK_LTXCLK_L+

TXCLK_UTXCLK_U+

TXOUT_L0TXOUT_L1TXOUT_L2-

TXOUT_L0+

TXOUT_L1+

TXOUT_L2+

TXOUT_U0TXOUT_U1TXOUT_U2-

TXOUT_U0+

TXOUT_U1+

TXOUT_U2+

75_0402_1%

12

R94

12

75_0402_1%

BLON_PWM17

ENABLT17

DDC2_ CLK17

DDC2_DAT A17

ENAVDD17

D D

TXCLK_L-17

TXCLK_L+17

TXCLK_U-17

TXCLK_U+17

TXOUT_L0-17

TXOUT_L1-17

TXOUT_L2-17

TXOUT_L0+17

TXOUT_L1+17

TXOUT_L2+17

TXOUT_U0-17

TXOUT_U1-17

TXOUT_U2-17

TXOUT_U0+17

TXOUT_U1+17

TXOUT_U2+17

M_COMP

M_LUMA

0622 change value

C C

M_CRMA

M_BLUE

M_GREEN

M_RED

0314 change desig n

+3VS

0821

1013 change value

DDC1_ CLK16

DDC1_DAT A16

M_HS YNC1 6

M_VSYNC16

DDC1_ CLK

DDC1_DAT A

M_H SYNC

M_VSYNC

R165

R166

0821

B B

+3VS

1013 change value

2.2K_0402_5%

2.2K_0402_5%

DDC2_ CLK

DDC2_DAT A

R92

R158

1 2

1 2

TV-Out Termination/EMI Filter

M_COMP

M_LUMA

A A

M_COMP

M_LUMA

M_CRMA

1

2

C238

5.6P_0402_50V8D

C7

5.6P_0402_50V8D

1

1

2

2

0314 add

R95 10K_0402_5%

1 2

R160 10K_0402_5%

1 2

12

75_0402_1%

75_0402_1%

12

12

R177

R176

2.2K_0402_5%

1 2

75_0402_1%

1 2

30.1_0402_1%

1 2

30.1_0402_1%

L38

1 2

CHB1608U301_ 0603

L37

1 2

CHB1608U301_ 0603

L17

1 2

CHB1608U301_ 0603

C251

5.6P_0402_50V8D

0314 add

75_0402_1%

12

12

R182

R181

HS YNC

VSYN C

1.15K_0402_1%

For Crestli ne:1.3kohm

For Calero: 255ohm

5.6P_0402_50V8D

U15C

J40

H39

E39

E40

C37

D35

K40

L41

L43

N41

N40

D46

C45

D44

E42

G51

E51

F49

G50

E50

F48

G44

B47

B45

E44

A47

A45

E27

G27

K27

F27

J27

L27

M35

P33

H32

G32

K29

J29

F29

E29

K33

G35

F33

C32

E33

12

R1449

CRES TLINE_1p0

Pl a c e c l o

Pl a c e c l o s e t o U 15

Pl a c e c l oPl ace c lo

1

1

2

2

C243

C8

5.6P_0402_50V8D

Note: C RT / TV-out s hould rout e to JP30 fir st then to the JP1 & JP2 on system side.

5

L_BKLT_CTRL

L_BKLT_EN

L_CTRL_CLK

L_CTRL_DATA

L_DDC_CLK

L_DDC_DATA

L_VDD_EN

LVDS_IBG

LVDS_VBG

LVDS_VREFH

LVDS_VREFL

LVDSA_CLK#

LVDSA_CLK

LVDSB_CLK#

LVDSB_CLK

LVDSA_DATA#_0

LVDSA_DATA#_1

LVDSA_DATA#_2

LVDSA_DATA_0

LVDSA_DATA_1

LVDSA_DATA_2

LVDSB_DATA#_0

LVDSB_DATA#_1

LVDSB_DATA#_2

LVDSB_DATA_0

LVDSB_DATA_1

LVDSB_DATA_2

TVA_DAC

TVB_DAC

TVC_DAC

TVA_RTN

TVB_RTN

TVC_RTN

TV_DCONSEL_0

TV_DCONSEL_1

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_TVO_IREF

CRT_VSYNC

1

C253

2

5.6P_0402_50V8D

4

LVDS

TV VGA

se to U1 5

se to U1 5s e t o U 15

COMP 16,33

LUMA 16,33

CRMA 16,33

0314 change desig n

4

PCI-EXPRESS GRAPHICS

PEG_COMPI

PEG_COMPO

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

PEG_RX#_7

PEG_RX#_8

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PEG_TX#_11

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

3

N43

M43

J51

L51

N47

T45

T50

U40

Y44

Y40

AB51

W49

AD44

AD40

AG46

AH49

AG45

AG41

J50

L50

M47

U44

T49

T41

W45

W41

AB50

Y48

AC45

AC41

AH47

AG49

AH45

AG42

N45

U39

U47

N51

R50

T42

Y43

W46

W38

AD39

AC46

AC49

AC42

AH39

AE49

AH44

M45

T38

T46

N50

R51

U43

W42

Y47

Y39

AC38

AD47

AC50

AD43

AG39

AE50

AH43

PEGCOMP

PEG_RXP1

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

R1176

24.9_0402_1%

1 2

PEG_RXN1

C1058 0.1U_0402_16V4Z

1 2

C1059 0.1U_0402_16V4Z

1 2

C1060 0.1U_0402_16V4Z

1 2

C1061 0.1U_0402_16V4Z

1 2

C1062 0.1U_0402_16V4Z

C1063 0.1U_0402_16V4Z

C1066 0.1U_0402_16V4Z

C1067 0.1U_0402_16V4Z

+VCCP

1 2

1 2

1 2

1 2

0809 Ad d M AX9511

PEG_RXN1 16

PEG_RXP1 16

1013 Re mov e MAX9511

CRT Termination/EMI Filter

M_RED

M_GREEN

M_BLUEM_CRMA

1

C194

@

1

2

2

10P_0402_50V8J

10P_0402_50V8J

C240

@

Secur ity Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

L28

1 2

HLC06 03CSCC39NJT_0603

L35

1 2

HLC06 03CSCC39NJT_0603

L27

1 2

HLC06 03CSCC39NJT_0603

1

C233

@

2

10P_0402_50V8J

3

C_RED _L

C_GRN _L

C_BLU_L

1

C193

22P_0402_50V8J

2

0314 change desig n

2006/02/13 2006/03/10

PE GC OMP tr ace w idth

and sp acing is 2 0/25 mils .

SDVOB_R- 16

SDVOB_G- 16

SDVOB_B- 16

SDVOB_CLK- 16

SDVOB_R+ 16

SDVOB_G+ 16

SDVOB_B+ 16

SDVOB_CLK+ 16

Pl a c e C

Pl a c e C lo sed to U1 5

Pl a c e CPl ace C

L31

1 2

HLC06 03CSCCR11JT_0603

L34

1 2

HLC06 03CSCCR11JT_0603

L26

1 2

HLC06 03CSCCR11JT_0603

1

1

C237

2

2

22P_0402_50V8J

C232

22P_0402_50V8J

@

Compal Secret Data

Deciphered Date

2

lo sed to U1 5

lo sed to U1 5lo sed to U1 5

1

C195

1

2

2

10P_0402_50V8J

10P_0402_50V8J

C244

@

2

10P_0402_50V8J

@

CFG[2:0] FSB Freq select

CFG5 (DMI select)

CFG6

CFG7 (CPU Strap)

CFG8 (Low power PCIE)

CFG9

(PCIE Graphics Lane Reversal)

CFG[11:10]

CFG[13:12] (XOR/ALLZ)

CFG16 (FSB Dynamic ODT)

SDVO_CTRLDATA

CFG19 (DMI Lane Reversal)

CFG20 (PCIE/SDVO concurrent)

RED

GREEN

BLUE

1

2

C245

RED 33

GREEN 33

BLUE 33

Title

Size Doc ument Number Re v

Cus tom

Date: Sheet

1

Strap Pin Table

010 = FSB 800MHz

011 = FSB 667MHz

Others = Reserved

0 = DMI x 2

1 = DMI x 4

*

Reserved

0 = Reserved

1 = Mobile CPU

*

0 = Normal mode

1 = Low Power mode

*

0 = Reverse Lane

1 = Normal Operation

*

Reserved

00 = Reserved

01 = XOR Mode Enabled

10 = All Z Mode Enabled

11 = Normal Operation

(Default)

ReservedCFG[15:14]

0 = Disabled

1 = Enabled

*

ReservedCFG[18:17]

0 = No SDVO Device Present

1 = SDVO Device Present

0 = Normal Operation

(Lane number in Order)

*

1 = Reverse Lane

0 = Only PCIE or SDVO is operational.

1 = PCIE/SDVO are operating simu.

R1151 4.02K_0402_1%@

CFG57

CFG77

CFG87

CFG97

CFG127

CFG137

CFG167

1 2

R1152 4.02K_0402_1%@

1 2

R1451 4.02K_0402_1%@

1 2

R1153 4.02K_0402_1%@

1 2

R1155 4.02K_0402_1%@

1 2

R1156 4.02K_0402_1%@

1 2

R1157 4.02K_0402_1%@

1 2

CFG[17 :3] ha ve internal pull up

CFG[19 :18] h ave internal pull down

R1159 4.02K_0402_1%@

CFG197

CFG207

CFG5

1 2

R1160 4.02K_0402_1%@

1 2

J37

2 1

PAD-N O SHORT 2 x2m

Compal Electronics, Inc.

CRESTLINE((3/6)-VGA/LVDS/TV

LA -3 26 1P U MA

9 55Tuesday, March 27, 2 007

1

*

*

*

+3VS

0.4

of

Page 10

5

+3VS_DAC_BG

0.022U_0402_16V7K

D D

+3VS_DAC_CRT

0.022U_0402_16V7K

+1.25VM

C C

1

C1108

2

1

C1113

2

MBK1608102Y ZF 0603

22U_0805_6.3V

0.1U_0402 _16V4Z

C1375

1

1

C1109

2

2

0621 Chan ge R to BLM18PG1 SN1D

BLM18PG181SN1D_0603

R1456

0.1U_0402_16V4Z

1

C1114

2

+3VS

1

+

C1126

150U_D_6.3V M

R1462

0_0603_5%

0316 add

2

+1.25VM_A_SM_CK

12

R1453

12

R1459

0_0603_5%

0.1U_0402_16V 4Z

R1461

1 2

0_0805_5%

C1127

22U_0805_6.3VAM

12

1U_0402_6 .3V4Z

C1226

1

2

0317 c hange value

+3VS

+3VS

+1.8V_TXLVDS

+3VS_PEG_BG

12

C1121

0317 c hange value

1

4.7U_0805_10 V4Z

2

22U_0805_6.3VAM

C1130

1

2

1116 Change to BLM18PG181SN1D_0603

+3VS_TVDACC

B B

0.022U_0402_16V7K

C1144

+3VS_TVDACA

0.022U_0402_16V7K

C1148

A A

+3VS_TVDACB

0.022U_0402_16V7K

C1152

1

C1145

2

1

C1149

2

1

C1153

2

BLM18PG181SN1D_0603

0.1U_0402_16V4Z

1

2

BLM18PG181SN1D_0603

0.1U_0402_16V4Z

1

2

BLM18PG181SN1D_0603

0.1U_0402 _16V4Z

1

2

5

R1468

R1472

R1473

12

12

12

+3VS

1

2

C1131

+3VS

+3VS

+3VS

R1452

0_0603_5%

+1.25VM_A_SM

C1128

1U_0603_10V4Z

1

2

+1.25VS_PEGPLL

VCC SYNC

12

1

C1107

2

+3VS_DA C_CRT

+1.25VS_DPLLA

+1.25VS_DPLLB

+1.25VM_HPLL

+1.25VM_MPLL

1000P_0402_50V7K

C1118

+1.25VS_PEGPLL

1

2

1U_0603_10V4Z

0.1U_0402 _16V4Z

C1132

1

2

+1.5VS_TV DAC

+1.5VS_Q DAC

+1.25VM_HPLL

+1.8V_LVDS

+1.5VS_QDA C

0.022U_0402_16V7K

10U_0805_10V4Z

0.1U_0402 _16V4Z

+3VS_DAC_BG

1

2

20 mils

1

C1129

2

+3VS_TVDACA

+3VS_TVDACB

+3VS_TVDACC

1

1

C1147

C1146

2

2

0119 Add C1374

20070301 Install C1374

+1.8V_LVDS

1U_0603_10V4Z

C1151

C1150

1

2

4

U15 H

J32

VCCSYNC

A33

VCCA_CRT_DAC_1

B33

VCCA_CRT_DAC_2

A30

VCCA_DAC_BG

B32

VSSA_DAC_BG

B49

VCCA_DPLLA

H49

VCCA_DPLLB

AL2

VCCA_HPLL

AM2

VCCA_MPLL

A41

VCCA_LVDS

B41

VSSA_LVDS

K50

VCCA_PEG_BG

K49

VSSA_PEG_BG

U51

VCCA_PEG_PLL

AW18

VCCA_SM_1

AV19

VCCA_SM_2

AU19

VCCA_SM_3

AU18

VCCA_SM_4

AU17

VCCA_SM_5

AT22

VCCA_SM_7

AT21

VCCA_SM_8

AT19

VCCA_SM_9

AT18

VCCA_SM_10

AT17

VCCA_SM_11

AR17