HITACHI C32WF727N Service Manual

SERVICE MANUAL

MANUEL D'ENTRETIEN

WARTUNGSHANDBUCH

CAUTION:

Before servicing this chassis, it is important that the service technician read the “Safety

Precautions” and “Product Safety Notices” in this service manual.

SM00025

C28WF523N

C32WF523N

C32WF720N

C32WF727N

C32WF810N

C36WF810N

C36WF830N

CL28WF720AN

CL32WF720AN

CL32WF720AND

CL32WF727N

CL32WF810AN

CL36WF810AN

CL36WF830AN

D36WF840N

ATTENTION:

Avant d’effectuer l’entretien du châassis, le technicien doit lire les «Précautions de sécurité»

et les «Notices de sécurité du produit» présentés dans le présent manuel.

VORSICHT:

Vor Öffnen des Gehäuses hat der Service-Ingenieur die „Sicherheitshinweise“ und „Hinweise

zur Produktsicherheit“ in diesem Wartungshandbuch zu lesen.

Data contained within this Service

manual is subject to alteration for

improvement.

Les données fournies dans le présent

manuel d’entretien peuvent faire l’objet

de modifications en vue de perfectionner

le produit.

Die in diesem Wartungshandbuch

enthaltenen Spezifikationen können sich

zwecks Verbesserungen ändern.

SPECIFICATIONS AND PARTS ARE SUBJECT TO CHANGE FOR IMPROVEMENT

COLOUR TELEVISION

DECEMBER 1999

SAFETY PRECAUTIONS

WARNING: The following precautions must be observed.

ALL PRODUCTS

Before any service is performed on the chassis an isolation transformer should be inserted between the power line and the

product.

When replacing the chassis in the cabinet, ensure all the protective devices are put back in place.

When service is required, observe the original lead dressing. Extra precaution should be taken to ensure correct lead dressing

in any high voltage circuitry area.

Many electrical and mechanical parts in HITACHI products have special safety related characteristics. These characteristics

are often not evident from visual inspection, nor can the protection afforded by them necessarily be obtained by using

replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety

characteristics are identified by marking with a on the schematics and the replacement parts list.

The use of a substitute replacement component that does not have the same safety characteristics as the HITACHI

recommended replacement one, shown in the parts list, may create electrical shock, fire, X-radiation, or other hazards.

Always replace original spacers and maintain lead lengths. Furthermore, where a short circuit has occurred, replace those

components that indicate evidence of overheating.

Insulation resistance should not be less than 2MΩ at 500V DC between the main poles and any accessible metal parts.

No flashover or breakdown should occur during the dielectric strength test, applying 3KV AC or 4.25KV DC for two seconds

between the main poles and accessible metal parts.

Before returning a serviced product to the customer, the service technician must thoroughly test the unit to be certain that it is

completely safe to operate without danger of electrical shock. The service technician must make sure that no protective device

built into the instrument by the manufacturer has become defective, or inadvertently damaged during servicing.

CE MARK

HITACHI products may contain the CE mark on the rating plate indicating that the product contains parts that have been

specifically approved to provide electromagnetic compatibility to designated levels.

When replacing any part in this product, please use only the correct part itemised in the parts list to ensure this standard is

maintained, and take care to replace lead dressing to its original state, as this can have a bearing on the electromagnetic

radiation/immunity.

PICTURE TUBE

The line output stage can develop voltages in excess of 25KV; if the E.H.T. cap is required to be removed, discharge the

anode to chassis via a high value resistor, prior to its removal from the picture tube.

High voltage should always be kept at the rated value of the chassis and no higher. Operating at higher voltages may cause a

failure of the picture tube or high voltage supply, and also, under certain circumstances could produce X-radiation levels

moderately in excess of design levels. The high voltage must not, under any circumstances, exceed 29KV on the chassis

(except for projection Televisions).

The primary source of X-radiation in the product is the picture tube. The picture tube utilised for the above mentioned function

in this chassis is specially constructed to limit X-radiation. For continued X-radiation protection, replace tube with the same

type as the original HITACHI approved type.

Keep the picture tube away from the body while handling. Do not install, remove, or handle the picture tube in any manner

unless shatterproof goggles are worn. People not so equipped should be kept away while picture tubes are handled.

SM00025 Service Manual

TABLE OF CONTENTS

DESCRIPTION ................................................................................................................................................... 1

1

1.1 A8/D8 MKII MAIN PSU ................................................................................................................................ 1

1.2 DTI PSU....................................................................................................................................................... 2

1.3 SCAN VELOCITY MODULATION ............................................................................................................... 3

1.4 DIGITAL DOUBLE-SCAN CONVERSION UNIT (FEATURE BOX) ............................................................ 3

1.5 INPUT PROCESSOR (TDA 9320) .............................................................................................................. 4

1.6 PICTURE IMPROVEMENT (TDA9178) ...................................................................................................... 5

1.7 TUNER......................................................................................................................................................... 5

1.8 RGB PROCESSOR (TDA9330) .................................................................................................................. 6

1.9 SIGNAL PATH DESCRIPTION ................................................................................................................... 7

1.10 AUDIO CIRCUIT ...................................................................................................................................... 7

1.11 DOLBY DECODER (Prologic Models)..................................................................................................... 8

1.12 DIGITAL AUDIO ....................................................................................................................................... 8

1.13 AUDIO AMPLIFIER ................................................................................................................................ 10

1.14 DEFLECTION ........................................................................................................................................ 14

1.15 MICRO-CONTROLLER SECTION ........................................................................................................14

1.16 MULTIPICTURE FUNCTION ................................................................................................................. 22

1.17 AUTOWIDESCREEN ............................................................................................................................. 23

2 SERVICE .......................................................................................................................................................... 24

2.1 BOARD ADJUSTMEMT ............................................................................................................................ 24

2.2 FINAL ALIGNMENT (by Software) ............................................................................................................ 27

2.3 AUDIO SUB BOARDS ............................................................................................................................... 29

2.4 SHIPPING SPEC DATA SHEETS............................................................................................................. 32

3 SCHEMATIC DIAGRAMS................................................................................................................................. 37

4 PCB LAYOUT DIAGRAMS............................................................................................................................... 47

5 PARTS LIST...................................................................................................................................................... 57

SM00025 Service Manual

1 DESCRIPTION

1.1 A8/D8 MKII MAIN PSU

From switch on the AC voltage is rectified by the

bridge D900 which produces approximately 300V

across C918. This is then applied to the collector of

Q903 via the primary winding of T900. Initially the

voltage on pin 7 of I900 will rise to approximately

16V via R901, D929 and Q905. This allows the

internal circuitry of IC900 to generate a sawtooth

waveform at pin 4, from which a square wave output

is obtained at pin 6. This output is applied to the gate

of Q901 which turns on and off, this alters the

voltage on the emitter of Q903 causing this device to

turn on and off, generating the outputs in the

secondary windings of T900.

After initial power up of I900 pin 7 is supplied from

the bias winding (pin 18) of T900 via D911 for

continued operation. The bias winding voltage is also

rectified by D922 which is then supplied to the base

of Q905 low via R908/Q906/R924 turning Q905 off,

this is done to reduce the power dissipated by R901

once the power supply is running.

A current sense circuit consisting of R910, R939,

R922 and R980 feeds back a voltage to pin 3 of

I900, MAX voltage approximately 0.8V. Should the

applied voltage exceed the reference the pulse width

is limited from output pin 6. In this way Q903 is

offered protection from changes in primary current.

R909 and C914 act as a soft start circuit, this limits

the pulse width output from pin 6 during the initial

start up period, allowing a gradual rise to full power.

Q909, R918 and associated circuitry are for reducing

the frequency of the power supply when the set is in

standby. A sense voltage rectified by D922

consisting of R905 and R906, supplied pin 2 of I900,

this is then compared to an internal reference

voltage. If it exceeds the internal reference the

output from pin 6 will be limited by the internal error

amp. The secondary voltage induced in T900

winding 7/9 is rectified by D950, producing the HT

voltage which is smoothed by C977. In standby the

HT rises slightly.

Winding 5/10 produces approximately 10V via D951,

which is smoothed by C957. This is then applied to

dual DC-DC converters (+8V, +5V out). A control

ramp is found on pin 2/6 I900. This ramp is formed

by R944/C935, and terminated by Z913, D902, R934

network. Ramp frequency is clamped to the main

PSU frequency by the winding on pin 5 T900. This

ramp is compared with the feedback level from I902

(+5V) I904 (+8V). The reference device monitors the

output and changes the DC level to pin 5. The ramp

crosses the DC feedback level, and the output at

pins 1/7 goes low. The output at pins 1/7 starts high

at the beginning of the ramp, goes low at ramp cross

level. This action via Q912, Q911 controls the pulse

width and so the regulation of the +8V/ +5V rails.

The output pulse width changes with load to

maintain the correct regulating voltage.

The output of I910 pins 1,7 are buffered to improve

switching losses using a push - pull transistor

network Q918, Q917 (for +5V). This transistor

network gives fast edge switching of Q912 (+5V) and

Q911 (+8V). Over current protection is provided with

the current sense resistor RP03. Network Q956

RP04/C966 pull pin 10 of I903 high if high load

current is flowing through RP03.

Winding 2/11 produces approximately 16V via D952,

which is smoothed by C955 and then applied to

Q921 through R974, which is used as a current

sense. The output from Q921 supplies 16V for the

audio amplifier I401.

HT regulation is controlled by Q954 stage. The base

of Q954 is set at a pre-determined level by the

resistor network R950, R982 and R953. The emitter

of Q954 is held at approximately 6.2V by Z950.

Should the HT rise, the base voltage becomes more

positive than the emitter, and this difference is

amplified by the transistor and applied to optocoupler

I901. The output from I901 is then applied to pin 1 of

I900 which regulates the HT by altering the duty

cycle of the waveform output from pin 6 of I900.

1.1.1 STANDBY SWITCHING

The low voltage supplies are switched off in standby,

this is controlled by the micro processor which

outputs a high in standby and a low when the set is

out of standby. This is then applied to resistors R923

and R940/R977. This ‘high’ is also applied to the

base of Q915, Q916, Q910 which in turn terminate

operation of the +8V, +5V DC-DC converters, and

pull the gate of Q921 low so switching the +16V

audio supply to low state. In standby the +B voltage

rises slightly to maintain bias winding voltage to pin 7

of I900. To switch the set out of standby the on/off

line is switched high by the micro, and Q916, Q915,

Q910 are deactivated, causing the +8V, +5V, +16V

rails to return to normal operation.

1.1.2 POWER GOOD AND PROTECTION

I903 is made up of 4 comparators, the power good

line uses comparator 2. Pin 5 is used as the

reference which is held at 2.5V by I905 supplied by

pull up resistor R968. Pin 4 uses R961/R962 and

R955/R959 as a potential divider which is connected

between the +10V and T900 winding through D959

which is in forward converter mode. In operation this

1

SM00025 Service Manual

means pin 4 is held below the reference level of pin

5 until the mains supply is interrupted or the set is

switched off at which time pin 4 rises above pin 5

and the output pin 2 is pulled low. This low is sensed

by the micro. In normal operation pin 2 is held high

by pull up resistor R990 from the 5V supply.

The protection line (pin 14) is held high under normal

running conditions by R971 from the 5V supply, this

high is applied to the protection line to the micro.

When the protection line is pulled low the set goes

into standby mode, the set can be restarted by the

usual methods of bringing the set out of standby, but

until the cause of the protection circuit operation is

removed the set will return to its standby state.

The over current for the 16V audio supply uses

comparator 1, a reference voltage is set up on pin 6

by resistors R967, and R964. The voltage being

compared is fed to pin 7 using the potential divider

R968 and R966 which is supplied from the output

side of the current sense resistor R974. Should the

voltage on pin 7 fall below that of pin 6, pin 1 will be

pulled low, thus pulling the protection line low via

D958 putting the set into standby.

Comparator 3 is used to protect against a layer short

within the FBT, it will also act as protection for a

short on the secondary outputs of the FBT. I903 is

supplied with approximately 16V via D960 to pin 3,

from this supply a reference voltage is fed to pin 9

using potential divider R972/R969, fed via Z948

supply. Pin 8 is supplied by another potential divider

this time made up of three resistors R973/R970 and

R760 samples the current flowing through Q752,

should this increase, the voltage drop across R760

will increase and raise the voltage of pin 8, when it

exceeds pin 9, pin 14 will be pulled low, putting the

set into standby.

I952. The +16V phono out has a diode back to I903

pin 5 in case of short.

If the +B or audio supply lines become short circuit

to ground before the protection on the secondary of

the power supply, the primary over current protection

(I900 pin 3) will operate, turning off the drive output

from I900 pin 6. A latch circuit

Q955/R998/RP01/C964, will operate to turn the

power supply into standby (under fault condition) if

the software fails to act on I903 pin 14 low. Delay

before latch set by C964/R994. The +B is given

protection from overvoltage via Z907, Z907 goes

short circuit if the +B voltage rises above 180V DC.

1.2 DTI PSU

1.2.1 CIRCUIT DESCRIPTION

The mains is switched on via the {TV on}. At this

point the AC mains is rectified by D9019, D9001,

D9002, D9003 which produces approximately 340v

DC across C9026. This is then applied to the

collector of Q9000 via the primary winding of T9000.

Initially the voltage on pin 7 of I9000 will rise to

approximately 16v via R9001, D9000, this allows the

internal circuitry of I9000 to generate a sawtooth

waveform at pin 4 from which a square wave output

is obtained at pin 6. This output is applied to the gate

of Q9005 turning the MOSFET on and off, pulling the

base/emitter high and low accordingly reducing

cross over, generating the outputs in the secondary

windings of T9000.

After initial power up pin 7 of I9000 is supplied from

the bias winding pin 3 of T9000 via D9010 for

continued operation hence R9001 unable to provide

running current demand for I9000 [200mA approx].

Comparator 4 is used for EHT/over voltage

protection, as all the FBT secondary voltages are

proportional, the 200V supply to the CRT base is

used to generate the voltage to be used in

comparison, this is done by using a potential divider

made up of R718, R749 and R719. Z708 monitors

the voltage at the junction of R718 and R749, if this

exceeds 36V, the Zener diode conducts, applying a

high on pin 10 of I903, this is compared with the

reference voltage on pin 11, which also uses the

2.5V set up by I905. When pin 10 is higher than

2.5V, pin 13 is pulled low, in turn pulling the

protection line low via D957, putting the set into

standby.

The LT lines are given protection using diodes D931,

D932 and D930, these are connected in reverse bias

from the prot sense line to the 8V and 5V. The +5V

standby link is protected by D986, pulling the

reference Z950 low if a short is seen on the output of

A current sense circuit consisting of R9057, R9013

and R9015 feeds back a voltage to pin 3 of I9000,

this voltage is compared with an internal reference

voltage of approximately 0.8V, should the applied

exceed the reference, the pulse width is limited from

output pin 6 [chip in over current mode]. In this way

Q9005 is offered protection from changes in primary

current. Secondary overvoltage protection is offered

also by R9009, should the feedback be disabled

then the secondary voltage will be limited to safe

levels, the output from pin 6 will be limited by the

internal error amplifier and internal reference.

R9006 and C9010 act as a soft start circuit, this

limits the pulse width output from pin 6 during the

initial start up period, allowing a gradual rise to full

power. ZD9000 and ZD9001, ZD9006 will go short if

Q9000 should go short, protecting I9000 and Q9005.

2

SM00025 Service Manual

The secondary voltage induced in T9000 winding

10/14 is rectified by D9031 producing 30V which is

smoothed by C9041.

Winding 12/14 produces 5V at 1.5A then rectified by

D9026 and smoothed by C9037 and C9036. This

voltage rail, being the highest current rail is used for

regulation via I9002, providing feedback to pin 1 of

I9000. From the 5V rail, a 3V3 rail is extracted at

2.7A. The current output is controlled by a PWM

circuit consisting of switching MOSFET Q9003, gate

drive is provided by Q9002 and Q9004 and pin 1 of

I9004, pin 2 of I9004 is supplied by a sawtooth

waveform shaping circuit consisting of D9022,

Z9003, R9036, C9032. Pin 3 is supplied by varying

DC levels via I9003. The 3V3 voltage rail is

regulated by I9003.

Winding 13/15 provides 16V from D9018 and

smoothing caps C9046 and C9024, also a 9V rail is

provided by I9005 regulator. –16V rail is provided by

D9017 and smoothing caps C9022 and C9045.

SECONDARY PROTECTION: Provided via I9004

pin 7. Pin 6 of I9004 is set to a steady voltage level

around 3V, pin 5 is used as the over current sense

point, D9023, D9034, D9029 is used to pull down pin

5 below pin 6 during over current, in this state pin 7

is low which in turn disables the feedback point pin 1

of IC9000 shutting down the power supply.

The velocity modulation circuit produces a

compensation signal by adding the RGB

components then differentiating. The compensation

signal is given some current gain, applied to the

auxiliary coil (connector E806) on the neck of the

cathode ray tube (CRT).

The VM circuit is located on the CRT base along

with the final RGB amplifiers. The RGB signals

derive from PL803 pins 2-4 and into emitter of Q861,

through the differentiator C865, R892 and R893

arriving at the base of Q862 for voltage amplification

and latter stages power gain. Final VM pulses arrive

at E806 to VM coil around tube neck.

1.4 DIGITAL DOUBLE-SCAN

CONVERSION UNIT

(FEATURE BOX)

The main feature of this unit is double scan

frequency conversion, 100/120Hz interlaced and

50/60Hz progressive scan. Other features of this unit

are CTI (Colour Transient Improvement), horizontal

compression, noise reduction, sharpness and

vertical zoom & freeze. These functions are

controlled by I

the picture improvement IC, TDA9178 (IE01) for

50Hz models without a Feature Box.

2

C bus and are provided elsewhere by

1.2.2 FEEDBACK OPERATION

Increase in load demand by secondary rails results

in higher voltage feedback on the cathode of I9002

in turn rising the voltage on pin 1 of I9000 this

voltage is compared to the sawtooth generated on

pin 4 via R9011 and C9013, this produces the gate

drive square pulse with larger off time, therefore the

larger the load demand the larger the duty cycle and

vice versa.

1.3 SCAN VELOCITY MODULATION

During transmission the signal suffers from

degradation and also due to the frequency

characteristics of the television circuitry. This

normally results in a gentle rise or fall in the

luminance change areas when black-to-white-toblack patterns are received.

The picture sharpness quality can be assessed by

how steep the leading and trailing edges are. The

scan velocity modulation circuit has been designed

to improve picture quality, i.e. make the video signal

edges steeper, by controlling the horizontal scanning

velocity of the electron beam in the CRT.

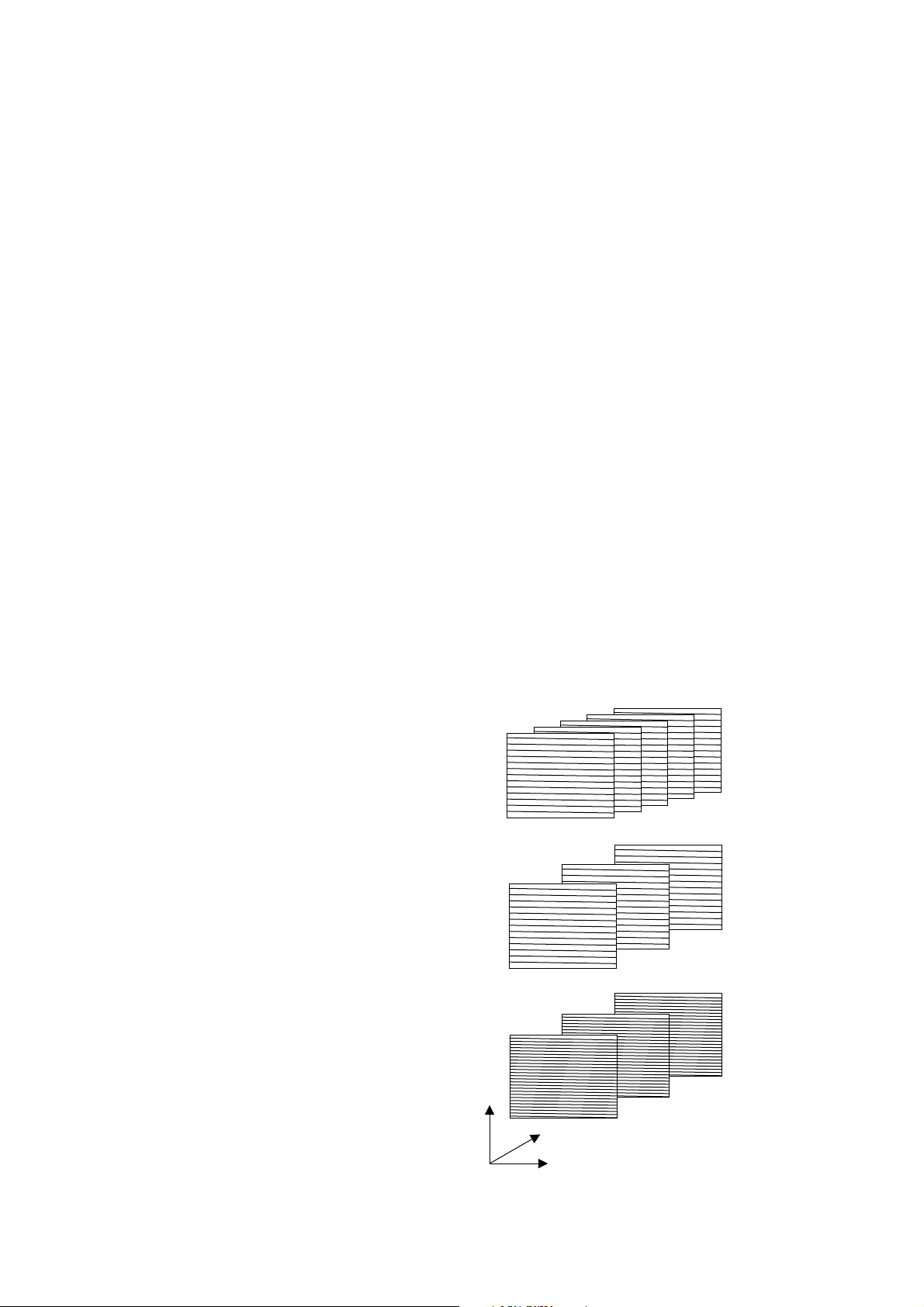

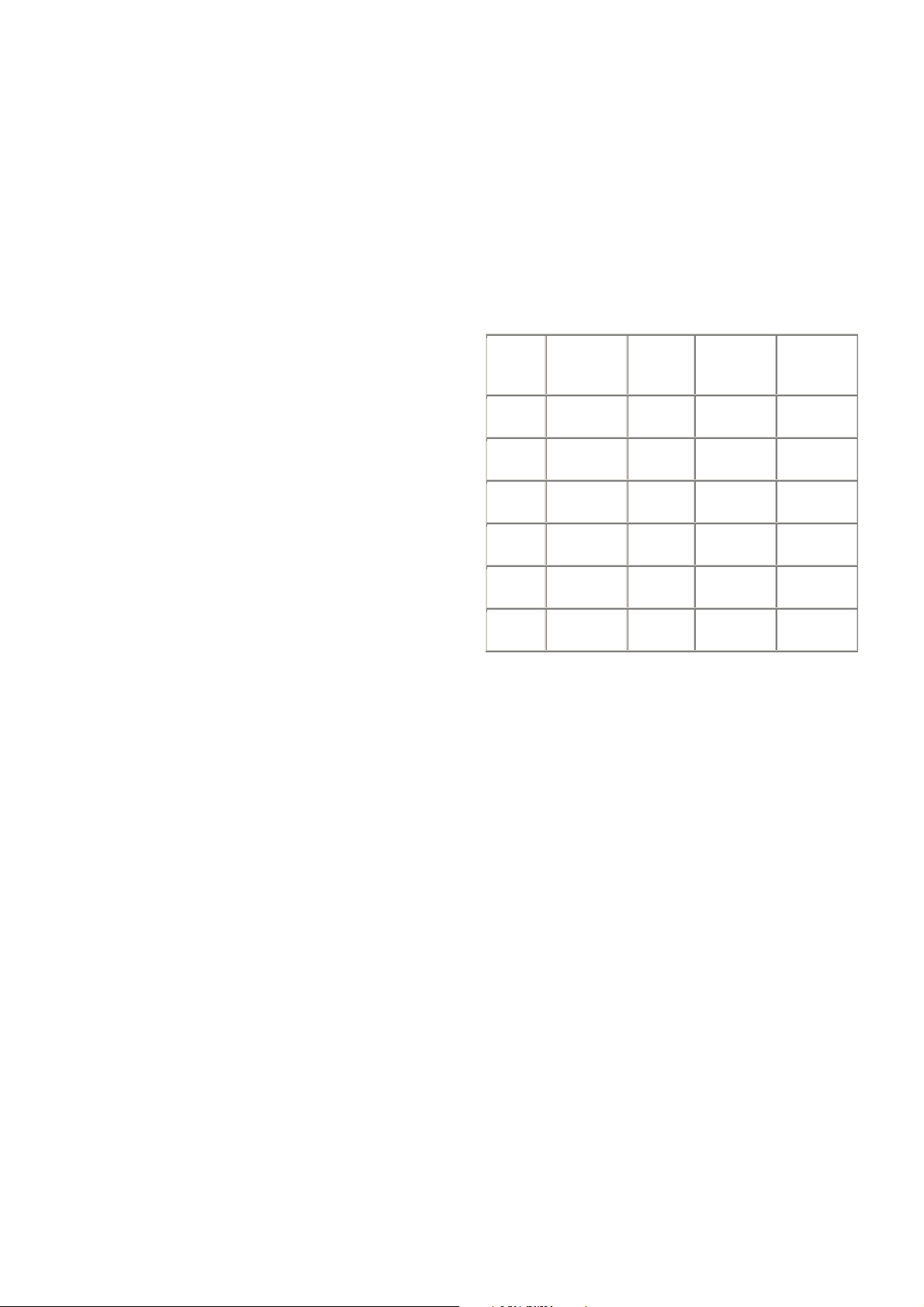

100/120 Hz

100/120 Hz

INTERLACED

INTERLACED

(2:1)

(2:1)

AA

BB

B*B*

A*A*

AA

50/60 Hz

50/60 Hz

INTERLACED

INTERLACED

(2:1)

(2:1)

AA

BB

AA

50/60 Hz

50/60 Hz

PPOSCAN

PPOSCAN

(1:1)

(1:1)

YY

TT

XX

A/A*A/A*

B*/BB*/B

A/A*A/A*

3

SM00025 Service Manual

As the diagram shows, A/B are the Odd/Even

original 50Hz signal fields which are used to create

extra picture information, while A*/B* are the

predicted/manipulated extra picture information,

created by the feature box. The diagram shows the

differences between 100/120Hz interlaced and

50/60Hz progressive scan. The biggest advantage of

progressive scan is "non-interlaced" scanning;

keeping the field frequency at 50/60Hz. This means

the line construction is double per field, compared

with 100/120Hz interlaced. It will make very fine pitch

scan lines and will eliminate line flicker. The

advantage of selecting 100Hz operation will be the

reduction of large area flicker and reduce line flicker

(except 523 50Hz models).

This unit is powered from +5V and +8V supplies,

feeding into pins 21, 22 and 26 of E10 respectively.

The three input 50Hz video signals Y, U, V are sent

to this unit at pins 8, 10 and 12 of E11. The Y, U, V

video output signals (double frequency video) are

taken from pins 5, 3 and 1 of E11. Horizontal and

vertical input sync signals are taken from composite

signal at pin 24 of E10, the double frequency

horizontal and vertical sync signals outputs are from

pins 30 and 31 of E10.

coincidence detector. This coincidence detector is

used to detect whether the line oscillator is

synchronized and can also be used for transmitter

identification. The PLL has a very high statical

steepness so that the phase of the picture is

independent of the line frequency.

For the horizontal output pulse, two conditions are

possible:

1. An HA pulse which has a phase and width which

is identical to the incoming horizontal sync pulse.

2. A clamp pulse CLP which has a phase and width

which is identical to the clamp pulse in the

sandcastle pulse.

The HA/CLP signal is generated by means of an

oscillator which is running at a frequency of 440 x

FH. Its frequency is divided by 440 to lock the first

loop to the incoming signal. The free running

frequency of the oscillator is determined by a digital

control circuit which is locked to the reference signal

of the colour decoder. When the coincidence

detector indicates an out of lock situation the

calibration procedure is repeated.

1.5 INPUT PROCESSOR (TDA 9320)

The TDA 9320 (I200) is a multi-standard input

processor.

Features include:

1.5.1 VIDEO OUTPUTS/EXTERNAL INPUTS

The input processor has provision for three CVBS

inputs (1 internal & 2 external) and 2 Y/C inputs. The

external CVBS inputs are used for the SCART

sockets. The Y/C inputs are used for S-VHS and a

third CVBS input. The circuit can detect whether

CVBS or a Y/C signal is presented to AV3, or AV1

inputs. The IC has 2 RGB inputs with fast switching.

The switching of the various sources is controlled by

2

I

C and detection of a Comb filter can be made.

Only one RGB input is used for connection of eternal

RGB equipment. These are pins 36, 37, 38 (RGB) &

pin 39 (blanking).

1.5.2 SYNCHRONISATION

The sync separator is preceded by a controlled

amplifier which adjusts the sync pulse amplitude to a

fixed level. These pulses are fed to the slicing stage

which is operating at 50% of the amplitude. The sync

pulses are fed to the phase detector and to the

The vertical pulse is obtained via a vertical count

down circuit. The countdown circuit has various

windows depending on the incoming signal

(50/60Hz).

1.5.3 VISION IF AMPLIFIER

The video signal is demodulated by means of a PLL

carrier regenerator. This circuit contains a frequency

detector and a phase detector. During acquisition the

frequency detector will tune the VCO to the right

frequency. After lock-in, the phase detector controls

the VCO so that a stable phase relation between

VCO and the input signal is achieved. The VCO is

running at double the IF frequency with the reference

signal for the demodulator obtained by means of a

frequency divider circuit.

The AFC output is obtained by using the VCO

control voltage of the PLL and can be read via the

2

I

C bus. The AGC detector operates on top sync and

top white level. The time constant on the AGC

system during positive modulation is long to avoid

visible variations of the signal amplitude. To improve

the speed of the AGC system a circuit has been

included which detects whether the AGC detector is

activated every frame period. When during 3 field

periods no action is detected the speed of the

system is increased. For signals without peak white

information the system switches automatically to a

gated black level AGC. Because a black level clamp

pulse is required for this way of operation the circuit

4

SM00025 Service Manual

will only switch to black level AGC in the internal

mode.

The circuit contains a video identification circuit

which is independent of the synchronisation circuit.

Therefore search tuning is possible when the display

section of the receiver is used as a monitor.

1.5.4 CHROMA & LUMA PROCESSING

The IC contains a chrominance bandpass filter, the

SECAM cloche and chrominance traps. The filters

are calibrated using the tuning frequency and the

crystal frequency of the colour decoder. The

luminance output signal which is derived from the

incoming CVBS or Y/C signal can be varied in

amplitude by means of a separate gain control.

1.5.5 COLOUR DECODING

The colour decoder can decode PAL, NTSC and

SECAM signals. The PAL/NTSC decoder contains

an alignment free crystal oscillator with 4 separate

pins, a killer circuit and two colour difference

demodulators. The 90o phase shift for the reference

signal is made internally. Because it is possible to

connect 4 different crystals to the colour decoder, all

colour standards can be decoded without external

switching circuits. Crystals not used must be left

open. The horizontal oscillator is calibrated by

means of the crystal frequency of the PLL.

The IC contains an automatic colour limiting circuit

which is switchable which prevents over saturation

when signals with a high chroma-to-burst ratio are

received. The ACL circuit is designed such that it

only reduces the chroma signal and not the burst.

This has the advantage that the colour sensitivity is

not affected by this function.

The SECAM decoder contains an auto-calibrating

PLL demodulator which has two references, the

4.43MHz sub-carrier frequency which is obtained

from the crystal oscillator which is used to tune the

PLL to the desired free running frequency and the

bandgap reference to obtain the correct absolute

value of the output signal. The VCO of the PLL is

calibrated during each vertical blanking period, when

the IC is in search or SECAM mode. The base-band

delay line is integrated into the package.

CVBS outputs for Teletext, Comb Filter and monitor

outputs are available.

1.6 PICTURE IMPROVEMENT

(TDA9178)

The picture improvement IC is an analogue video

processor offering three main processing functions;

luminance vector, colour vector and spectral

processing. Features presently being implemented

are; luminance transient improvement (LTI), colour

transient improvement (CTI), variable gamma control

and picture dependant non-linear Y and U, V

processing by luminance histogram analysis.

The spectral processor provides luminance transient

improvement, luminance detail enhancement by

smart peaking and colour step improvement (CTI).

The line width control may be user defined. The

luminance vector processor, the transfer function is

controlled in a non-linear manner by histogram

analysis of measured luminance values measured in

a picture. As a result the contrast ratio of the most

important parts of the scene will be improved. A

variable gamma function after the conversion offers

the possibility of alternative brightness control or

factory adjustment of the picture tube.

The following functions sharpness, noise reduction

and colour transient improvement (CTI) are provided

by the picture improvement IC for 50Hz models,

while 100Hz/progressive scan models provide these

functions within the double scan module (feature

box). All functions described are

switchable/adjustable via I

2

C control using the

options in the service menu.

Y, U and V signals are taken from I200 pins 49, 50

and 51 and go straight into Yin U

and Vin (pins 6, 8

in

and 9 of IE01). The enhanced Y, U and V outputs

originate from IE01 (pins 19, 17 and 16 respectively)

and are directed to IZ04 (pins 28, 27 and 26

respectively).

1.7 TUNER

The tuner U100, is a frequency synthesis type with

an unbalanced input and IF of 38.9MHz, powered

from the +5V rail while the tuning voltage is supplied

by the +33V rail, supplied from the horizontal

deflection circuit. Direct frequency access, channel

selection, AGC and AFC functions are controlled via

2

the I

C bus. AGC, AFC and Offset controls may be

selected by entering the service menu and selecting

the ‘tuner’ option.

Pin 1, AGC is taken from pin 62 of TDA9320/9321

(I200). The balanced IF output is taken from pins 10

and 11 arriving at both inputs of the vision and sound

SAW filters (pins 1 and 2). The outputs from X200

5

SM00025 Service Manual

and X202 (pins 4 and 5 respectively) pass through to

pins 2 and 3 and pins 63 and 64 of I200, where they

are demodulated.

1.8 RGB PROCESSOR (TDA9330)

1.8.1 VERTICAL DEFLECTION AND

GEOMETRY CONTROLS

The drive circuit for the vertical and E-W deflection

circuits are generated by means of a vertical divider

which gets its clock from the line oscillator. The

divider is synchronised by the incoming vertical

pulse generated by the input processor (50Hz

models) or the feature box.

The vertical drive is realised by means of a

differential output current. The outputs

(100Hz/progressive scan models) must be DC

coupled to the vertical output stage. The vertical

geometry can be adjusted by I

service menu.

1.8.2 HORIZONTAL SYNCHRONISATION AND

DRIVE CIRCUIT

2

C control via the

An additional function of the IC is the low-power

start-up feature. This mode is activated when a

supply voltage of 5V is supplied to the start-up pin.

The required current for this function is 3mA typical.

In this condition the horizontal drive signal has the

normal T

and Ton grows gradually from zero to

off

about 30% of the normal value. This results in a line

frequency of about 50KHz or 25KHz. The output

signal remains unchanged until the mains voltage is

switched-on. Then the horizontal drive signal will

gradually change to the normal frequency and duty

cycle via the soft-start procedure.

The IC has a general purpose bus controlled DAC

output with a resolution of 6 bits and with an output

voltage range between 0.2V to 4V.

1.8.3 INPUT SIGNALS

The RGB control circuit of the TDA9330 (IZ04)

contains three sets of input signals.

Y, U, V, input signals which are supplied by the input

processor or feature box. The nominal input signals

for u and V are 1.33 V

Peak-to-Peak

and 1.05V

Peak-to-Peak

respectively. These input signals are controlled by

brightness, contrast and saturation.

The horizontal drive signal is obtained from an

internal VCO which is running at a frequency of

13.75MHz. This oscillator is stabilised to this

frequency by means of a resonant oscillator 12MHz.

The internal VCO is synchronised to the incoming

horizontal HD pulse by means of a PLL with an

internal time constant. The horizontal drive signal

generated by means of a second control loop which

compares the phase of the reference signal from the

internal VCO with the flyback pulse. The time

constant loop is internal. The IC has a dynamic

horizontal phase correction input which can be used

to compensate phase shifts which are caused by

beam current variations. Additional settings of the

horizontal deflection which are realised via the

second loop are the horizontal shift and the

parallelogram correction.

The horizontal drive signal is switched on and off via

the so called soft-start/soft-stop procedure. This

function is realised by means of a variation to the

Ton of the horizontal drive pulse. For EHT

generators without bleeder the IC can be set in a

fixed beam current mode. In that case the picture

tube capacitance is discharged with a current of

about 1mA which is determined by the black current

feedback loop. With the fixed beam current option

activated it is still possible to have a black screen

during switch-off. This can be realised by placing the

vertical deflection in an overscan position.

Two RGB sources are intended for use by the

SCART, while the second is used for the OSD and

Teletext. The required input signal has an amplitude

of 0.7V

Peak-to-Peak

. The switching between the internal

signal and the OSD signal can be realised via a fast

blanking . this input is only controlled by brightness.

Switching between various sources can be realised

via the I

2

C bus and by fast insertion switches. The

circuit contains switchable matrix circuits for the

colour difference signal so that the colour

reproduction can be adapted for PAL/SECAM and

NTSC.

1.8.4 OUTPUT AMPLIFIER

The output signal has an amplitude of around 2V

black-to-white at nominal settings. The required

white point setting of the picture tube is implemented

by 3 separate gain settings for the RGB channels.

To obtain an accurate biasing of the tube, a

continuous cathode calibration circuit is implemented

by means of a two point black level stabilisation

circuit. By inserting 2 test levels for each gun and

comparing the resulting cathode currents with two

different reference currents, the influence of the

picture tube parameters like the spread in cut-off

voltage can be eliminated.

6

1.9 SIGNAL PATH DESCRIPTION

The IF signal is obtained from SAW filters X200

(vision) and X202 (Sound) pins 4 and 5 and are fed

into pins 2 and 3 vision and 63 and 64 sound of I200.

A composite video signal is available at pin 10 from

the vision demodulator. IF sound out from pin 6. The

video is taken from pin 10 via C304 into pin 12 and

out at pin 13. This is the selectable Group Delay via

software input output. The composite video gets

taken through buffer and filtering stages where the

desired video returns to I200 at pin 14.

SM00025 Service Manual

2

I

C is present at pins 10 and 11 (IZ04) and +8V

supply rails at pins 7 and 17. Two sets of RGB inputs

are available, only one set is used for the OSD, pins

35-37, the other is for a VGA board which is not

fitted.

A CVBS monitor output is taken from pin 28 of I200

and is sent to pin 61 of I001 (Microprocessor) where

the text is decoded. CVBS monitor output is also

sent to SCART 1 pin 19 to monitor what is being

displayed. Pin 19 of SCART 2 outputs signal from

RF.

The AV switching matrix supports two SCART

sockets, phono CVBS and S-VHS inputs. SCART

CVBS inputs are at pins 20 (AV1 E301) and 16 (AV2

E302), CVBS outputs to SCART pins 19 from emitter

of Q301 (AV1) and emitter of Q303 (AV2). The RGB

input (Digital models) to I200 from the Digital

Terrestrial Tuner (DTT) comes to pins 36-38, from

P301 pins 9, 7 and 5, respectively. S-VHS input is

via E300 to pin 23 and 24 of I200, detection of CVBS

input is detected within I200. For models with

progressive scan feature, detection for a Comb filter

has been fitted via Y/C input pins 28 and 29. Colour

sub-carrier output for the Comb filter is from pin 30.

Y, U and V signals are taken from I200 pins 49, 50

and 51 and go straight into Yin Uin and Vin (pins 6, 8

and 9 of IE01) for 50Hz operation, while 100Hz

operation, Y, U, V signals are directed to pins 9, 10

and 12 of the double scan module (UQ01).

Other miscellaneous pins such as the sandcastle pin

59 is independent of the sandcastle pulse generated

by I200, they do not drive each other. The Vertical

and Horizontal output pulses generated by I200 drive

the double scan module, pins 18 and 19 respectively

(100Hz operation) or the IE02 (50Hz operation) pins

23 and 24. I

2

C control lines are pins 46 and 47, and

tuner AGC control voltage is present at pin 62.

1.10 AUDIO CIRCUIT

The output from the Tuner T1 is fed via a gain and

buffer stage formed by Q200 and Q201 to the Saw

Filter X202. The saw filter has two separate

characteristics depending on which of the two inputs

(on pin 1 and 2 of the Saw Filter) the signal is

applied to. Selection is achieved by the combination

of Q204 and Q203. For most standards, pin 1 is

selected. However, when an L’ Signal has been

selected, the micro (I001) instructs I200 via an I

command to take pin 19 high. When this happens

Q204 conducts taking pin 1 low and switching Q203

and D203 off. This means that the collector of Q203

goes high allowing D202 to conduct and hence the

signal to be applied to pin 2. To return to other

broadcast standards, pin 19 of I200 is obviously

returned to the low condition.

The output of the Saw is applied to pins 63 and 64 of

I200. Here the signal is transformed from the 1st IF

(30 – 40MHz depending on transmission standard)

to the sound IF (5.5MHz to 6.5MHz depending on

the transmission standard ).

I200 also provides AM demodulation for the L’ and L

standards. The demodulated signal appears

superimposed on the Sound IF on pin 5 of I200.

2

C

As already previously described Y, U, V signals in

either 50Hz/100Hz/Progressive scan mode are sent

to pins 26-28 of the TDA 9330/31 (IZ04). Once

inside the RGB processor, geometry and

synchronisation functions can be implemented

before being sent to the CRT base (pins 40-42 of

IZ04 and 3-5 of PZ02) for final video amplification

and to the velocity modulation circuit.

The vertical drive output is provided by pin 1 and 2 of

IZ04 directly to I601 Vertical Output IC (pins 11 and

12). Horizontal output is from pin 8 of IZ04 and feeds

the base of Q701 Bipolar (50Hz), Q701B MOSFET

(100Hz). East-West drive output can be obtained at

pin 3 and is driving the gate of the East-West

MOSFET Q700.

This signal then takes two paths, the first takes it

through a Low pass filter formed by R426 and C427

and coupling capacitor C426. This is then applied to

pin 55 of I400 and forms the AM Sound Input. The

second path takes the signal through an amplifier

and buffer stage formed by Q400 and Q401.

After these stages some high pass filtering is applied

by C464 and R477 before the sound IF is applied to

pin 60 of I400 via C431.

I400 is The MSP3410D. This IC provides NICAM,

FM Mono and FM Stereo Demodulation as well as

matrixing of the SCART/digital receiver signals (If

fitted).

7

SM00025 Service Manual

The AV1 input is applied on pins 52 and 53, the AV2

input on pins 49 and 50, the AV3 input on pins 46

and 47. The Digital input (DTT) is applied to pins 43

and 44 (when fitted). In each case a 100R resistor

and 330nF capacitor is used.

The SCART outputs on I400 use the following

protocol.

SCART

Output

Output Signal

Non Digital Models Digital Models

AV1 RF Digital

AV2 Selectable or Auto* Selectable or Auto*

*If auto is selected in the on screen menus, AV2

follows the audio of what is being watched.

2

The device is I

C controlled via pins 10 and 11 and

receives a reset from the micro at power-up on pin

24. The clock is provided by X406 on pins 62 and

63. The device has three supply rails, 5V Digital (Pin

18), 5v Analogue (Pin 57) and 8v Analogue (Pin 39).

1.11 DOLBY DECODER (Prologic

Models)

Pre-C and Pre-S respectively. These are then

amplified by 3dB by op-amp IF03 to become AmpL,

AmpR, Centre and Surround. These then pass

through a buffer and filter network to the four way

phono plug JF01. The AmpL and AmpR signals split

off before the buffers to the amplifier I401 via

dividing resistors R443/R439 and R446/R447 and

are decoupled by C443 and C445. The operation of

the amplifier is explained elsewhere in this manual.

1.12 DIGITAL AUDIO

1.12.1 SUPPLY RAILS

The Digital Audio decoder board consists of a 4 layer

PCB and is situated above the Audio amp board.

The 8v supply for the Digital Audio decoder arrives

at pin 4 of PS06. It is then passed to the 5v regulator

IS16 via LS02. It then reappears at the output of the

regulator as 5VM. This rail is split into 5VA and 5VD

via inductors LS05 and LS06 and is decoupled by

CS63, CS64, CS65 and CS66 respectively. The two

rails then supply the DAC’s IS06, IS07 and IS08, the

SPDIF Receiver IS05, the clock generator IS15 and

the DAC output buffers QS05, QS06, QS07, QS08,

QS09 and QS10. 5VD is also made available for the

optical receiver on the amplifier board via the

connector PS07.

The Dolby decoding is provided by IF01 (YSS241).

The signals which are sent to this device from I400

in the I2S format are:

SD0 (Pin 13 Of I400) - the Left and Right channel

data (before Dolby decoding)

SCK (Pin 11 Of I400) - the system or bit clock

WS (Pin 12 Of I400) - the word select line, provides

selection between the Left and Right samples on the

SDO Line.

IFO1 is provided with an 18.432MHz clock via pin 1

of I400 (SYSCLK), a reset line from pin 4 and is I

2

C

controlled. The Pro-logic signals that the device

decodes are provided in I2S form at pins 40 and 41

(DACS1 and DALR). These signals are in a 32bit per

channel format (The MSP4310D uses 16 bit) and

must therefore pass through a conversion IC IF02.

This IC also takes a Bit clock DABC from pin 36 of

IF01. IF02 then provides the 16 bit pro-logic I2S

channels as SDI1 and SDI2 on pins 14 and 20 of

I400.

I400 then passes these signals through DAC’s so

that the Left, Right, Centre and Surround signals

appear at pins 29, 28, 26 and 25 as Pre-L, Pre-R,

5VM goes to the 3V3 regulator IS13. This rail then

supplies the main decoding IC IS01, the SRAM IS02,

IS03 and IS04, the EEPROM IS12, the I

2

C level

translator IS09 and the signal multiplex IS10. Finally,

there is an option for a 1V8/2V5 rail via regulator

IS14, which can be fed either by the 3V3 or 5VM rail.

This will supply certain pins of The DSP processor

IS01 should the device change over to this style.

1.12.2 I

2

C CONVERSION, DSP MAIN CLOCK

AND RESET

The DSP56362 (IS01) is controlled by the I

2

C lines

(SDA and SCL) from the micro, which come from the

header E304 on the main board. The signal travels

via a nine way lead arriving at pins 8 and 9 of PS04

on the decoder board.

Since the DSP56362 is a 3V3 device and the Micro

is 5V, some level translation of the I

2

C is required.

This is achieved by IS09. This device also acts as a

buffer for the Main Clock for the DSP, which also

travels on the 9 way lead described above before

arriving at pin 5 of PS04. It then goes to pin 5 of IS09

as MSP12SCLK and leaves pin 6 as DSP Extal. This

1.024MHz signal is then up-converted within the

DSP to the various clocks required. IS01 is reset on

pin 44 via a line from the 9 way lead at pin 7 of

PS04.

8

SM00025 Service Manual

1.12.3 MUTING

The DACs IS06, IS07 and IS08 are muted via pin 34

of IS01 going low. Additional mute lines are provided

for the Amplifier board on pins 41, 42 and 43 via the

three way header PS08. In either case, the mute

lines are activated via I

2

C commands.

1.12.4 MODES OF OPERATION

Although described as the Digital Audio Decoder

board, this board in fact provides audio in both the

Analogue and Digital Audio modes. The following is

a description of this board operation in the two

different modes.

ANALOGUE MODE

This mode is used when either a SCART, Phono or

RF signal provides the Audio source.

In analogue mode, the analogue signal, be it RF or

from a SCART/Phono source, is first processed by

I400, the MSP3410D on the main board.

This device converts the signal to 16 bit I2S format

consisting of a Word Select (pin 12), Data (pin 13)

and Bit Clock line (pin11). The signals arrive at PS04

on the decoder board via the 9 way lead described

above.

it redirects the centre to the Left and Right

channels).

The DAC signals then emerge (depending on mode)

for the Front Left and Right, Rear Left and Right, and

Centre and Subwoofer on pins 4, 5 and 6

respectively of the DSP56362. They are then

converted by the DACs to Analogue form after which

they are buffered by QS05, QS06, QS07, QS08,

QS09 and QS10 before being passed to the Audio

Amplifier board via header PS03. Here, 6dB is

added to the main channels and 9.5dB to the

Subwoofer channel by Op Amps I408, I409 and I410

before being passed to the output buffers (phono

outputs) and power amplifiers (speaker outputs).

This operation is described more thoroughly in the

description of the Audio amplifier board itself.

DIGITAL MODE

This mode is used when either a coaxial or optical

digital audio signal is the selected source

The operation in Digital Mode is similar to the

Analogue mode except in this case the signals are

not derived from the MSP3410D but instead come

from the SPDIF receiver CS8414 (IS05). This device

takes signals on pins 9 and 10 from either the

coaxial socket or optical receiver on the amplifier

board via a 4 way shielded lead connected to PS07.

If both sources are connected, the optical receiver

takes priority.

The 18.432MHz clock signal from pin 1 of the

MSP3410D is connected to a two way header E28.

From here it is passed via a shielded lead to PS01

on the decoder board. The signal is then passed

through a buffer amplifier stage formed by QS11 and

QS12 before being transformed to a 8.192MHz

Clock by IS15.

On the Decoder Board, Analogue mode is selected

by instructing IS01 via an I

2

C command to take pin

28 of IS01 (the SPDIF select line) high. This signal is

then inverted by QS01 thus pulling pin 1 of IS10 low.

This Multiplexer then switches the Word Select,

Data, Bit Clock and 8.192MHz clock mentioned

earlier to the DSP56362 (IS01). The 8.192MHz clock

is also passed to the DACs IS06, IS07 and IS08.

The output of QS01 is also fed to pin 23 of the

DACs, thus switching the devices to 16 bit. (leaving

the device in 24 bit results in distorted sound).

The DSP carries out either Stereo or Pro Logic

decoding of the signal, setting the volume and

Graphic Equaliser to the level selected by the user

and also the channel outputs to their desired settings

(i.e. if no centre has been selected in the speaker

setup menu and the device is in the Pro Logic mode,

IS01 (the DSP56362) provides the device with

6.144MHz clock on pin 13 in order that status and

error information can be returned on pins 2, 3, 25

and 27. IS01 also provides a reset for the SPDIF by

taking pins 17, 18, 23 and 24 high via pin 32 of IS01

applied at switch on, this reset is sometimes reapplied by the DSP if invalid data is received.

The SPDIF Receiver converts the PCM or Digital

Audio bit-stream to I2S format which appears as

SPDIFWS, SPDIFSCK, SPDIFMSTRCLK and

SPDIFI2SDATA, on pins 11, 12, 19 and 26 of the

device respectively. This is passed to the DSP and

DACs via the multiplexer, which is switched via pin

28 of IS01 going low and thus the output of QS01

going high. This also switches the DACs to 24 bit

mode.

Three of the I2S signals (SPDIFW S, SPDIFSCK and

SPDIFI2SDATA) are passed to the DSP where they

are processed according to the user settings and

there format into either a Dolby Digital, DTS, MPEG

Multi-channel, PCM Prologic or PCM Stereo signals

before being passed out to the DACs (which have

the SPDIFMSTRCLK provided to them via the

multiplexing IC). The Audio signals then pass to the

9

SM00025 Service Manual

amplifier board in the same manner described

above.

In DTS Mode extensive use is made of the EEPROM

IS12 as this holds the decoder coefficients.

The SRAM, IS02, IS03 and IS04 is made use of

extensively in both Dolby Digital, DTS and MPEG

Multi-channel modes. The SRAM integrity can be

confirmed by looking for a code in the fault

diagnostics software. A fault here will normally

manifest itself as a distortion in the Surround

channels.

NOTE: Due to the nature of Digital Audio and in

particular Dolby Digital, DTS and MPEG Multichannel, it may sometimes appear that channels

aren’t working when either the user has disabled

them in the speaker setup menu or the software they

are using doesn’t support that channel (i.e. no centre

from a Dolby Digital 2/2.1 source)

For this reason, before carrying out tests for missing

audio on individual channels, please use a DVD

player to check that:

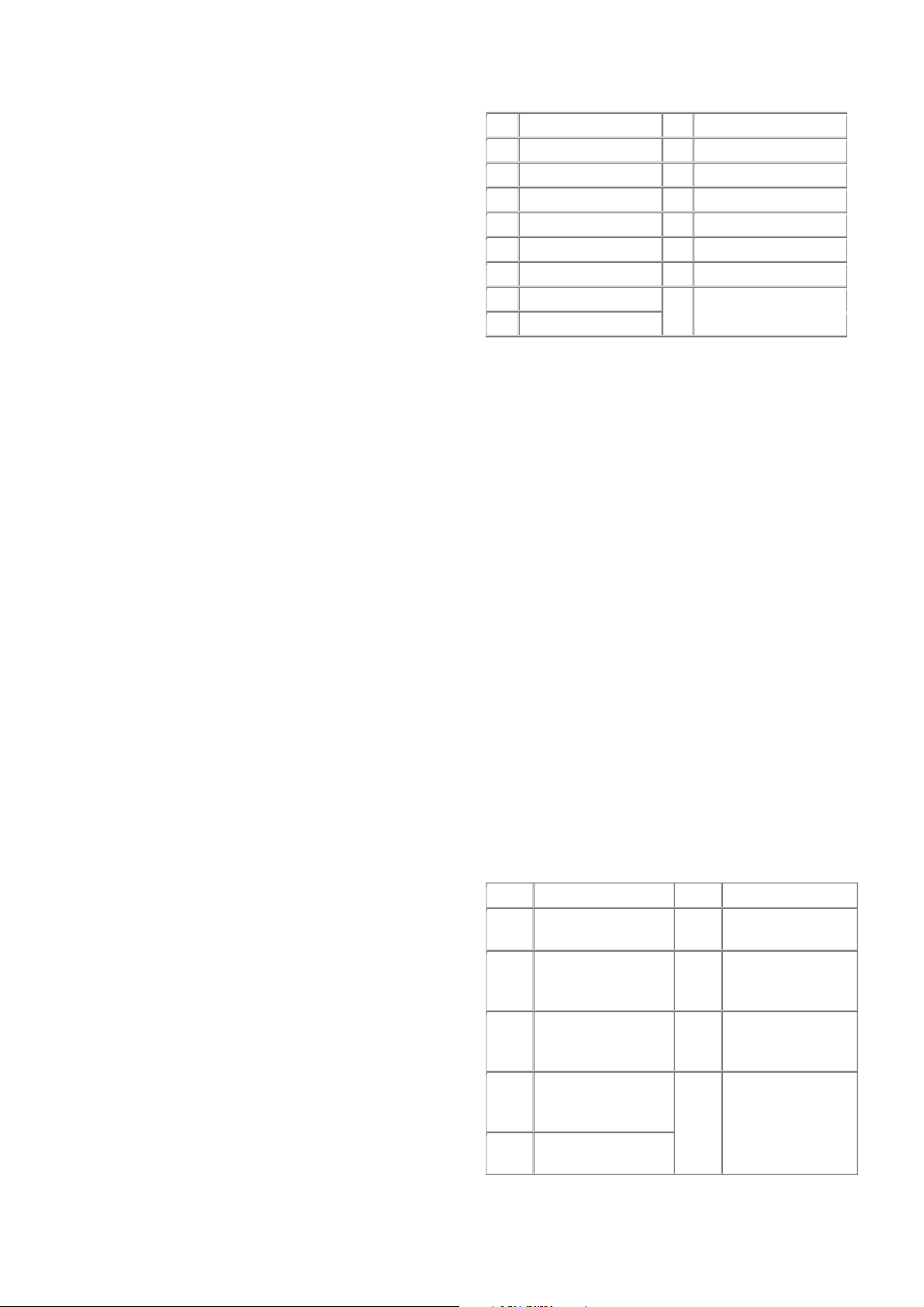

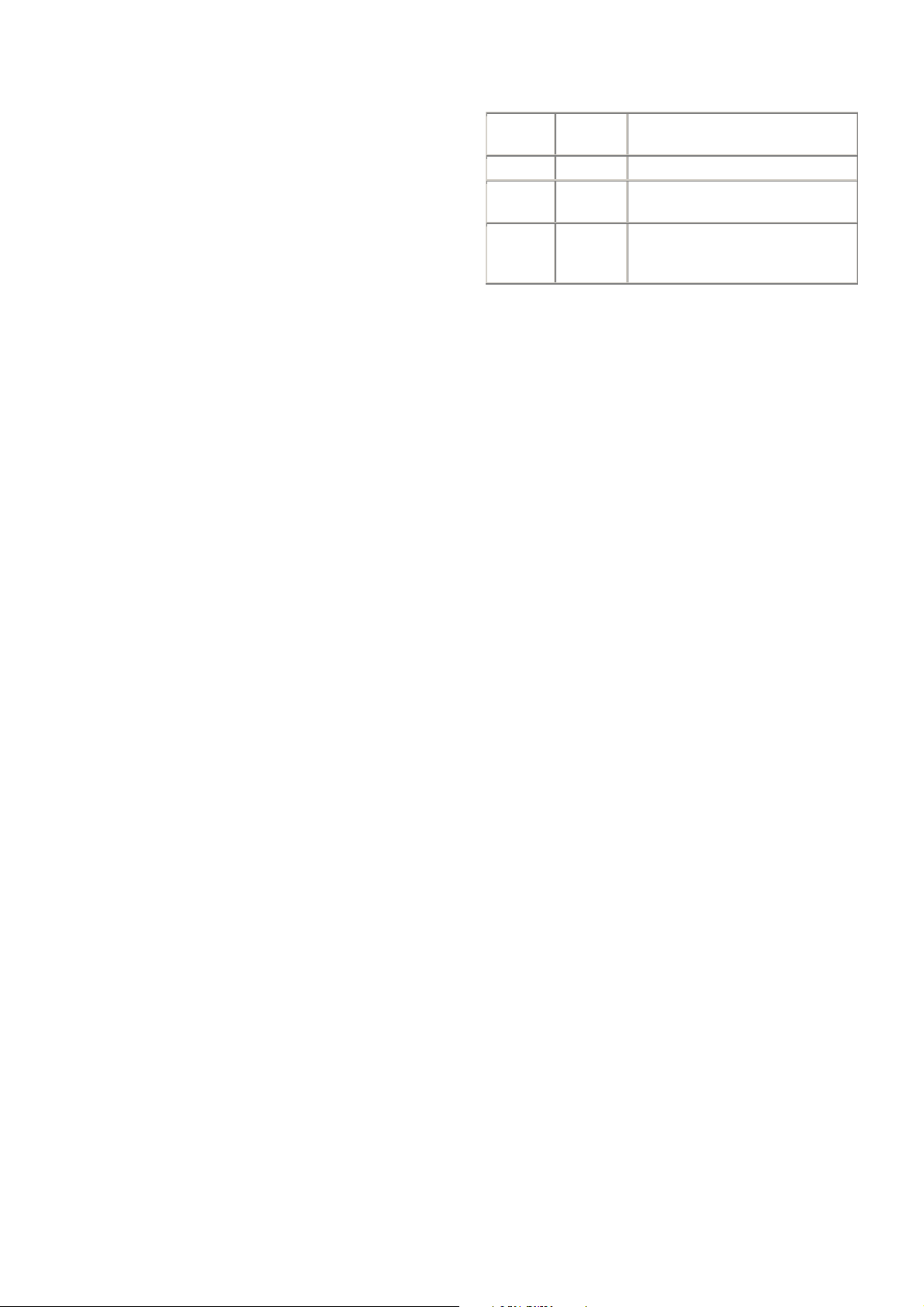

Pin Function Pin Function

1 Left output positive 9 Signal ground

2 Left output negative 10 Not connected

3 +18V supply 11 Not connected

4 Left signal input 12 Right input

5 Not connected 13 +18V supply

6 Mute control 14 Right output negative

7 St-by control

8 Power ground

At turn ON and OFF, I001 turns Q403 on, holding

pins 6 and 7 low keeping the amplifier turned off

stopping pops through the speakers.

When the front amplifier is turned off using the

software option in the installation/speaker set up

menu the amplifier is turned off by I001 controlling

Q402 which holds pins 6 and 7 low.

The left and right signals are supplied from the Audio

Amplifier panel via P303 pins 2 and 3.

15 Right output positive

The Sound mode is Dolby Digital, DTS or MPEG

Multi-channel (or Pro Logic if your disc isn’t playing

yet)

The speakers are set to either small or large (and

not none!) in the speaker setup menu

The power amplifiers are set to ON in the speaker

setup menu.

The disc you are playing is encoded in the 3/2.1

format, (This can be confirmed by pressing the

info/recall button on the handset when the disc is

playing)

You can then check for the signals at the DAC

outputs with an oscilloscope.

1.13 AUDIO AMPLIFIER

1.13.1 AUDIO AMPLIFIERS MAIN BOARD

The amplifier for the left and right channels on the

main board is a ST Microelectronics TDA7297, a

dual bridge 2x 15W IC. It requires an 18V supply to

achieve 15W into 8W speakers.

Table below shows IC pin connections:

The left signal is input through the potential divider

network of R443/R439, capacitor C442 into pin 4 of

I401. The right signal is input through the potential

divider network of R446/R447 capacitor C444 into

pin 12 of I401.

On Dolby models a DIN board containing 2 switched

speaker sockets is connected into the speaker leads

connected to P400. On non-Dolby models the

speaker leads connect directly into P400.

For the 32" the outputs from pins 1 and 15 of I401

are input to pins 6 and 4 of J400 the headphone

socket respectively these are then output from pins 7

E17 Connection E18 Connection

1 Headphone right

signal output.

2 Right speaker

output return from

front panel.

3 Right speaker

output to front

panel.

4 +18V supply to

headphone socket

switch.

5 Headphone left

signal output.

1 +18V return from

headphone switch

2 Left speaker

output to front

panel.

3 Left speaker

output return from

front panel.

4 Ground.

10

SM00025 Service Manual

and 5 and applied to pins 1 and 4 of P400.

The return paths from pins 2 and 3 of P400 go

directly to pins 2 and 15 of I401.

For the 36" the headphone socket is on the front

control panel and is connected via E17 and E18.

Headphone Circuit

When a 3.5mm jack plug is inserted into the

headphone socket the connections between pins 6

and 7 (left channel), pins 4 and 5 (right channel) and

pins 8 and 9 (headphone inserted indicator) are

broken. The signals for the headphone outputs are

taken from one half of each of the left and right

power amplifiers (pins 1 and 15 of I401) via

C438/R438 and C437/R437 which are input to pins 2

and 3 of J400 respectively. The headphone return is

through pin 1 of J400 to ground, this method is used

to restrict the maximum power available at the

headphones.

The 18V output from pin 8 of J400 is used in 2 ways.

The first is to supply the single phono output at the

rear of the chassis to power the IR surround speaker

transmitter. The second the 18V is sampled by the

potential divider made up of R474 and R473 with the

midpoint being fed to the microprocessor pin 19 via

R045, when this pin is low the software goes into

"headphone mode".

WARNING - Neither output for either channel is

connected to the chassis ground so caution must be

taken if an oscilloscope and other mains operated

equipment with a common earth is used

simultaneously when checking the amplifier outputs.

1.13.2 AUDIO AMPLIFIER PANEL (CTV)

The Audio Amplifier panel has four distinct functions:

Optical and phono inputs for the digital decoder.

Amplification of the analogue signals.

Phono outputs for the analogue signals to be

amplified externally of the set.

Power amplification of the centre, sub woofer, rear

left and right channels.

The single phono socket E408 marked coaxial is for

inputting digital signals (electrical) and the socket

directly above it, I407 marked optical is for inputting

digital signals (using laser light and optical link). I407

converts the optical signal into electrical pulses.

These are outputted from the Amplifier board to the

Digital Decoder panel via E419.

The Analogue signals output from the Digital

Decoder are input to the Amplifier panel at E414,

these are applied to operational amplifiers I408, I409

and I410. These Op Amps are powered from the

+17V supply used by the Audio Power Amps.

Because of the gain required these devices are quad

Op Amps with half of each IC (two Op Amp stages)

being used for each channel.

First

Stage

Input

Front

I410 Pin 5 I410 Pin

Left

Front

I409 Pin 3 I409 Pin

Right

Centre I410 Pin 3 I410 Pin

Sub-

I408 Pin 5 I408 Pin

Woofer

Rear

I409 Pin 5 I409 Pin

Left

Rear

I408 Pin 3 I408 Pin

Right

First

Stage

Output

7

1

1

7

7

1

Second

Stage

Input

I410 Pin

10

I409 Pin

12

I410 Pin

12

I408 Pin

10

I409 Pin

10

I408 Pin

12

The outputs of the Op Amps are then connected to

two different paths, one goes to the phono outputs

via a single transistor buffer stage, the other to the

power amplifiers. The 12V supply for the buffer stage

is derived from the +17V via Z415, a 4V7 zener

diode.

All the phono output stages are the same so the

centre will be used as an example. The signal from

I410 pin 14 passes through R493 to the base of

Q415, the output from the emitter then passes

through R473 and C483. R466 gives the required

output impedance, C484, L424 and C485 are a filter

network to reduce the EMC emissions. Transistor

Q431 is used to mute the phono output and is

controlled by the microprocessor via the lines

marked MUTE. The signal is then output from the

phono socket block E401.

The Audio Amplifiers uses are ST Microelectronics

TDA7482 25W mono class D IC’s, they are powered

by 2 rails one positive, the other negative, in this

application +/- 17V are used.

Audio power output requirement for the CTV is 15W

for front left and right (amplifier on the main board),

centre, rear left and right. 25W is required for the

bass/sub woofer/LFE channel, this is achieved by

connecting the output of I401 to 2x 7W internal bass

11

Second

Stage

Output

I410 Pin 8

I409 Pin

14

I410 Pin

14

I408 Pin 8

I409 Pin 8

I408 Pin

14

SM00025 Service Manual

speakers in parallel or 1x 3.5W external bass

speaker fitted via E405.

The 32" sets have internal centre and bass

speakers. SW401 is fitted so the outputs of

amplifiers I401 and I402 can be switched between

the internal speakers and external speakers

connected to E405.

The 36" sets have no facility for internal centre and

bass speakers so SW 401 is not fitted and the

outputs of I401 and I402 are permanently connected

to E405.

I401 is for the bass output.

I402 is for the centre channel.

I403 is for the rear right output.

I404 is for the rear left output.

Pin connection for TDA7482 (I401-404)

Pin 1 is the output which is a PWM (pulse width

modulated) square wave with a peak to peak voltage

that of the supply rails.

Pins 2 and 12 are connected together and are for the

internal voltage regulators.

Pin 3 is the bootstrap connection.

Pin 4 is not connected.

Pin 5 is the feedback integration capacitor.

Pin 6 the resistor connected to this pin is used for

setting the frequency at which the IC operates.

Voltage Condition Output at Pin1 (using

oscilloscope)

0 to 1V Standby None

1.7V to

2.5V

Mute Switching frequency square

wave 50% duty cycle only

4V to 5V Play Switching frequency square

wave with variable duty cycle

(audio heard from speaker)

Pin 11 is the signal positive supply.

Pin 13 is the power output positive supply.

Pins 14 and 15 are the power output negative

supply.

The front, centre, rear and bass channel amplifiers

can be turned off independently by the user with

software in the installation / speaker set up menu.

As the control of the amplifiers is the same for all the

channels the centre channel will be used as an

example:

When the set is turned on, the amplifiers are held in

hardware mute by the microprocessor, by making

the MUTE line high. This is applied to the base of

Q412 via D406 and R426, which in turn holds the

base of Q404 low. Q404 turns on pulling pin 10 of

I402 low via D402, R420 (D402 and R420 are used

to speed up the discharge of C419 at switch off) and

R421.

When the hardware mute is released pin 10 is pulled

high (turning the amplifier on), via R419 clamped to

5.6V by Z402, R414 and R411. C419 is used to

create a time constant to stop any pops when the

amplifier is turned on.

Pin 7 is ground.

Pin 8 is the signal negative supply.

Caution is required when checks are made as the

metal tab of the IC is connected to pin 8, so the heat

sinks are not connected to ground.

Pin 9 is the signal input.

Pin 10 controls the mute/standby functions, this pin

controls the output state of the IC:

When the centre channel is turned off using the

software option the CENTRE OFF line is held low,

turning off Q434, which in turn allows the base of

Q403 to rise pulled high from the +17V via R447.

Q403 turns on pulling pin 10 of I402 low via D402,

R420 and R411.

Because internal centre and bass speakers are fitted

to the 32" models and not the 36", SW401 is only

fitted to the 32" so that external centre and bass

speakers can be connected.

The 36" models have to have external speakers

fitted.

12

Denotes Main Board

SM00025 Service Manual

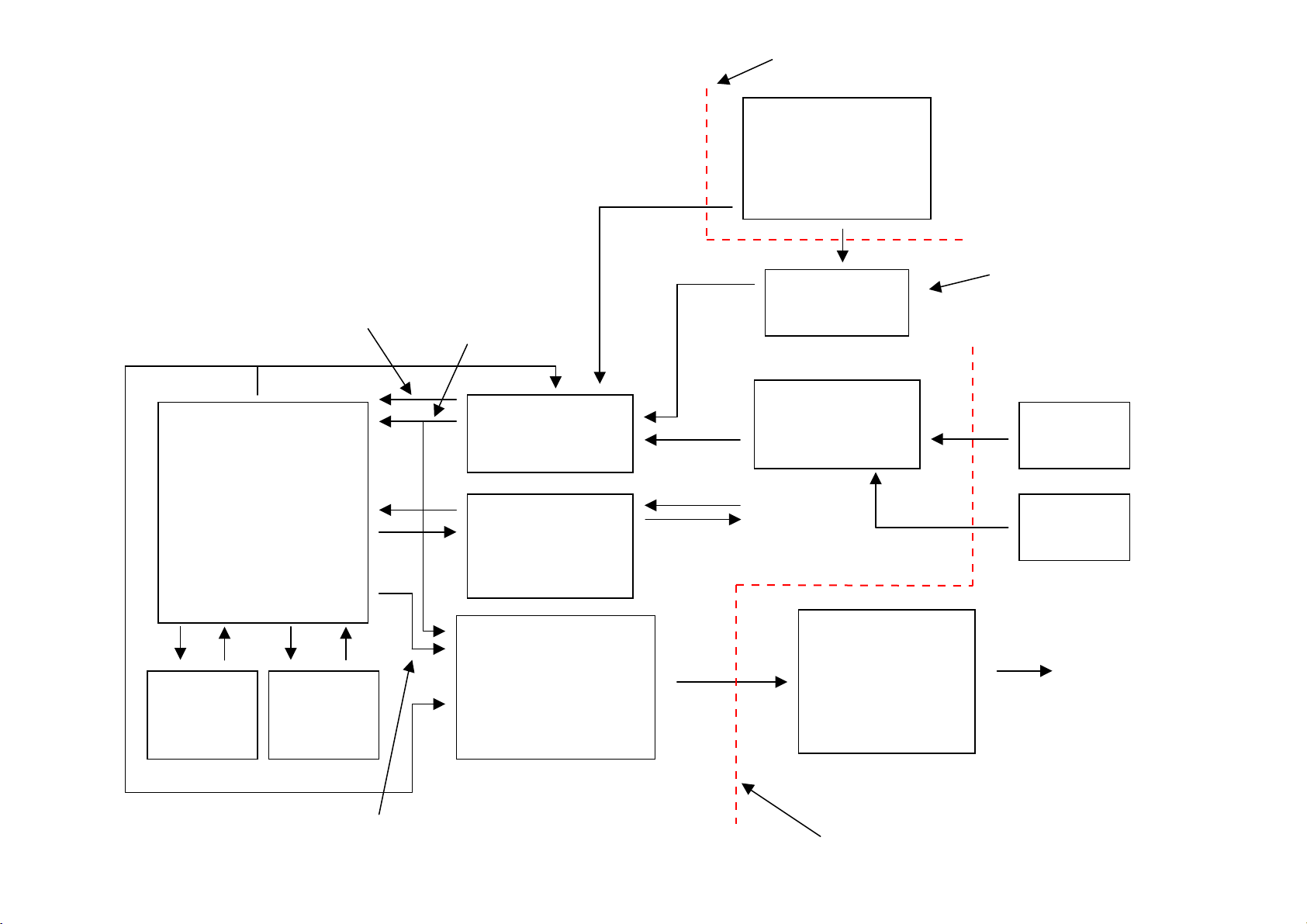

DIGITAL AUDIO DECODER BLOCK DIAGRAM

IS2 Data

Bit and word

Data Format

Select Line

IS01

DSP56362

Digital Audio Decoding IC

Clock

IS10

Analogue/Digital

Format Select

IS09

12C 3v3/5v

Level translator

And 1.024 MHz

Clock buffer

I400

12C 5v side

(Main Board)

MSP3410D,

Provides source in

Analogue Mode

IS15

ICS525 Clock

Translator

IS05

SPDIF Receiver.

Provides source in

Digital Mode

Translates 18.432 MHz

Clock into 8.192 MHz

Bit Clock for MSP data

I407

Optical

Receiver

E408

Coaxial

input

IS02, IS03,

I2S Data for Centre, Front Left and Right,

And rear Left and Right channels.

IS04

SRAM

IS12

EEPROM

(Holds DTS

Coefficient

s)

IS06, IS07, IS08

Digital to Analogue

Converters

Format line selects

whether 16 or 24 bit.

13

I408, I409, I410

Operational Amplifiers

= 6dB gain Main

Channels

= 9.5dB gain LFE

Channel

Denotes

Amplifier

Board

To read Phono sockets

and power amplifiers

SM00025 Service Manual

1.14 DEFLECTION

1.14.1 100HZ HORIZONTAL DEFLECTION

STAGE

The 2H output from UQ01 (the feature box) from pin

30 is fed via RZB7 to pin 24 of IZ04 TDA9330 the

"HOP".

The horizontal drive is then output from pin 8 is

passed through an emitter follower stage (QZ18) to

the gate of Q701B. A MOSFET is used to sharpen

the switching edges and reduce the temperature of

the power transistor Q751. The drain of Q701B is fed

from the +B via R701 and the primary of the drive

transformer T702. The secondary of the transformer

drives the base of the power transistor Q751, the

collector of which is supplied from the +B via R751,

L700 and the primary of the FBT. The emitter is

connected to ground via R760 a 1Ohm 10W resistor

(R760 should be kept away from Q751 heatsink to

reduce heat transfer) which is a sense resistor for

the protection circuit.

The capacitive divider network C717 and C708

produce a line pulse which is sampled by Z704 and

clamped by D713 and D714 this is then returned to

pin 13 of IZ04.

1.14.2 50HZ HORIZONTAL DEFLECTION STAGE

The HA OUT from pin 60 of I200 TDA9320 the "HIP"

is fed via RZB7 to pin 24 of IZ04 TDA9330 the

"HOP".

The horizontal drive is then output from pin 8 is fed

to the base of Q701. The collector of Q701 is

supplied from the +B via R701 and the primary of the

drive transformer T702. The secondary of T702

drives the base of the power transistor Q751. The

collector of Q751 is supplied from the +B via R751,

L700 and the primary of the FBT. The emitter is

connected to ground via R760 which is a sense

resistor for the protection circuit.

The capacitive divider network C717 and C708

produce a line pulse which is sampled by Z704 and

clamped by D713 and D714 this is then returned to

pin 13 of IZ04.

1.14.3 VERTICAL DEFLECTION

On the 50Hz the vertical drive pulse come from pin

61 (VA OUT) of I200 and on the 100Hz it comes

from pin 31 of UQ01. This is fed via RZB8 to pin 23

of IZ04. The vertical sawtooth waveforms are output

from pins 1 and 2 of IZ04 and fed to pins 11 and 12

of I601 via RZ92 and RZ93. I601 (TDA8354) is the

vertical output amplifier, it requires 2 supply

voltages, approximately 14V to pins 4 and 10 to

operate the IC and approximately 48V to pin 7 for

the flyback pulse generator. The outputs are from

pins 2 and 9 with the gain setting feedback resistors

R602 and R603 connected to pin 5.

Z615 samples the flyback pulse which is then

clamped by Z606 this generates the frame pulse

used by the micro I001.

If vertical failure is detected I001 switches off to

prevent damage to the tube.

1.14.4 EAST WEST CORRECTION

The east west parabola is output from pin 3 of IZ04

and fed to the gate of Q700 via RZ94. The drain of

Q700 is connected to the centre of the diode

modulator D706 and D707 via the east west injection

coil L751.

1.15 MICRO-CONTROLLER SECTION

The main microcontroller on the A8/D8 chassis is

located at I001 (ST92R195B). This is an 80-pin QFP

(quad-flat package) that is surface mounted for

compactness. This highly complex device controls

many of the other integrated circuits via dedicated

input/output lines or the I

generates the RGB signals for the on-screen display

(OSD) menus and the Teletext. The device can

acquire, decode and display the Teletext without the

need for a separate IC. This microcontroller is ROMless which results in the need of a separate memory

device to store the program code necessary for

operating the television. This memory device is

located at I002 and is a multi-time programmable

(MTP) or FLASH device. This allows the device to be

re-programmed and in the future can even be reprogrammed in the board without having to remove

the back cabinet of the TV. The television stores all

the necessary customer preferences and operating

settings in an on-board EEPROM (E2). This device

can hold 2Kb of information for storing the program

information (frequency, name, AV setting, etc.),

factory alignment settings (geometry, white balance,

tuner AFC/AGC, etc.), service diagnostic errors and

customer control settings (volume, brightness,

contrast, etc.). This device communicates with the

main microcontroller via the I

standby mode.

2

C bus. This device also

2

C bus, even in the

14

SM00025 Service Manual

1.15.1 MAIN MICRO-CONTROLLER (I001)

The ST92R195B is an enhanced micro-controller

based on the ST9+ instruction set from ST

Microelectronics. It is capable of displaying menus

and Teletext for 50Hz and 100Hz televisions. This

device can acquire/decode and display pages of

Teletext information in FLOF (FastText) and TOP

(only in Germany/Switzerland/Austria) modes. The

device operates from a single 4MHz crystal and a

+5V supply. Dedicated address/data lines enable it

to access 4Mbytes of address space, even though in

this television it is accessing 128Kbytes (1Mbit).

These address/data lines are connected to the

EPROM/MTP/FLASH device which holds the

instructions necessary for controlling the television,

and on certain models to a 128K SRAM device used

for 100 pages of Teletext storage.

External Memory Interface MMU Address Lines

Pins 1 (MMU0), 15 (MMU1) and 16 (MMU2) are

used to access addresses above 64Kbytes.

Normally pins 15 and 16 are not used when using a

128Kbyte EPROM/MTP device (MX26C1000APC) in

position I002.

Pin 2 (MMU3) is used to select between either the

EPROM/MTP/FLASH in position I002, or a future

device that can be fitted in position I003. When this

line is low, the device in position I002 is enabled

(chip enable).

case, this line should be changing state very

frequently.

External Memory Interface Data Lines

Pins 63 to 70 are the 8 data lines needed for

receiving data from the EPROM/MTP (I002) or I003.

Under normal circumstances these lines change

from LOW (0V) to HIGH (approx. +5V).

Ground Connections

Pin 9 (GNDM) is the ground connection (0V) for the

external memory interface. This should be free of

noise to enable successful communications between

the microcontroller and the EPROM/MTP (or SRAM).

Pin 35 (GND) is the digital ground connection (0V)

for normal operation of the device.

Pin 62 (GNDA) is the analogue ground connection

for the DAC and phase lock loops (PLL’s).

Supply Connections

Pin 10 (VDDM) is the +5V supply for the external

memory interface. Without this supply, the

microcontroller cannot communicate with the

EPROM/MTP (or SRAM).

Pin 34 (VDD) is the main digital supply voltage to the

IC (5V 10% tolerance).

Pin 17 (MMU4) not used.

Pin 18 (MMU5) is not used.

External Memory Interface Control Lines

Pin 4 is the Data strobe line which is connected to

the output enable input of the EPROM/MTP/FLASH

(I002). When data is read from the

EPROM/MTP/FLASH, this line is temporarily low.

Pin 8 is the Read/Write line for I002 and I003.

Normally, this line is high and is low when writing

data to the SRAM or FLASH device.

External Memory Interface Address Lines

Pins 3, 5, 6, 7, 13, 14 and 71 to 80 are the address

lines needed to specify which location in a 64Kbyte

page is needed to be accessed from the

EPROM/MTP (I002) or SRAM (I003). Normally these

lines will be changing state (0V to approx. +5V). By

placing an oscilloscope on pin 12 of the

EPROM/MTP (I002) it can be confirmed that the

microcontroller is operating successfully. In this

Pin 52 (VDDA) is the analogue supply voltage for the

DAC’s and PLL’s (+5V). These connections are all

joined together to the +5V standby rail of the

television, ensuring that the microcontroller operates

even in the standby state.

Crystal Oscillator Connections

Pin 11 is the 4MHz crystal oscillator input (OSCIN).

Pin 12 is the 4MHz crystal oscillator output

(OSCOUT). By connecting a x100 scope probe to

pin 11, it can be seen if a 4MHz sine wave is present

at the oscillator input to the microcontroller.

Reset Connection

Pin 54 is the active low RESET input of the

microcontroller. This input is normally high (approx.

+5V) under operating conditions, but changes state

when the standby +5V power supply is typically

below +4.5V. In this circumstance, the reset IC

(I021) pulls pin 54 low until the input of it is above

+4.5V. The diode (D001) ensures that the capacitor

(C015) discharges quickly when the standby supply

15

SM00025 Service Manual

falls, so that the reset operates quickly. The

capacitor (C015) charges up slowly when the

standby +5V supply is restored, ensuring that there

is some hysteresis.

Infra-red (IR) Receiver Input

Pin 25 is the IR receiver’s filtered output. This input

from the IR receiver consists of PWM pulses

between 0V and +5V which are decoded by the