Page 1

harman/kardon

AVR 145/230 service manual

Page 1 of 135

harman/kardon

AVR145

5 X 40W 5.1 CHANNEL A/V RECEIVER

SERVICE MANUAL

CONTENTS

ESD WARNING........................ 2 ELECTRICAL PARTS LIST.... 12

LEAKAGE TESTING.................. 3 SEMICONDUCTOR PINOUTS 48

BASIC SPECIFICATIONS.......... 4 PCB DRAWINGS.................. 119

TROUBLESHOOTING GUIDE..... 5 BLOCK DIAGRAM................. 126

PROCESSOR RESET............... 5 WIRING DIAGRAM................ 127

PACKAGE LIST AND PARTS....... 6 AMP BIAS ADJUSTMENT 128

DISASSEMBLY 7 SCHEMATIC DIAGRAMS....... 129

UNIT EXPLODED VIEW AND PARTS 11

Released 2007

Discontinued XXXX Rev 0, 10/2007

harman/kardon, Inc.

250 Crossways Park Dr.

Woodbury, New York, 11797

Page 2

harman/kardon

AVR 145/230 service manual

Page 2 of 135

2

ELECTROSTATICALLY SENSITIVE DEVICES

AVR145

harman/kardon

Some semiconductor (solid state) devices can be damaged easily by static electricity. Such components commonly are called

Electrostatically Sensitive (ES) Devices. Examples of typical ES devices are integrated circuits and some field effect transistors and

semiconductor "chip" components.

The following techniques should be used to help reduce the incidence of component damage caused by static electricity.

1. Immediately before handling any semiconductor component or semiconductor-equipped assembly, drain off any electrostatic charge on

your body by touching a known earth ground. Alternatively, obtain and wear a commercially available discharging wrist strap device,

which should be removed for potential shock reasons prior to applying power to the unit under test.

2. After removing an electrical assembly equipped with ES devices, place the assembly on a conductive surface such as aluminum foil, to

prevent electrostatic charge build-up or exposure of the assembly.

3. Use only a grounded-tip soldering iron to solder or unsolder ES devices.

4. Use only an anti-static solder removal device. Some solder removal devices not classified as "anti-static" can generate electrical charges

sufficient to damage ES devices.

5. Do not use freon-propelled chemicals. These can generate electrical change sufficient to damage ES devices.

6. Do not remove a replacement ES device from its protective package until immediately before you are ready to install it. (Most replacement

ES devices are packaged with leads electrically shorted together by conductive foam, aluminum foil or comparable conductive material.)

7. Immediately before removing the protective material from the leads of a replacement ES device, touch the protective material to the

chassis or circuit assembly into which the device will be installed.

CAUTION :

8. Minimize bodily motions when handling unpackaged replacement ES devices. (Otherwise harmless motion such as the brushing together

or your clothes fabric or the lifting of your foot from a carpeted floor can generate static electricity sufficient to damage an ES devices.

Be sure no power is applied to the chassis or circuit, and observe all other safety precautions.

Each precaution in this manual should be followed during servicing.

Components identified with the IEC symbol in the parts list are special significance to safety. When replacing a component identified with

, use only the replacement parts designated, or parts with the same ratings or resistance, wattage, or voltage that are designated in the

parts list in this manual. Leakage-current or resistance measurements must be made to determine that exposed parts are acceptably

insulated from the supply circuit before retuming the product to the customer.

Page 3

SAFETY PRECAUTIONS

The following check should be performed for the continued

protection of the customer and service technician.

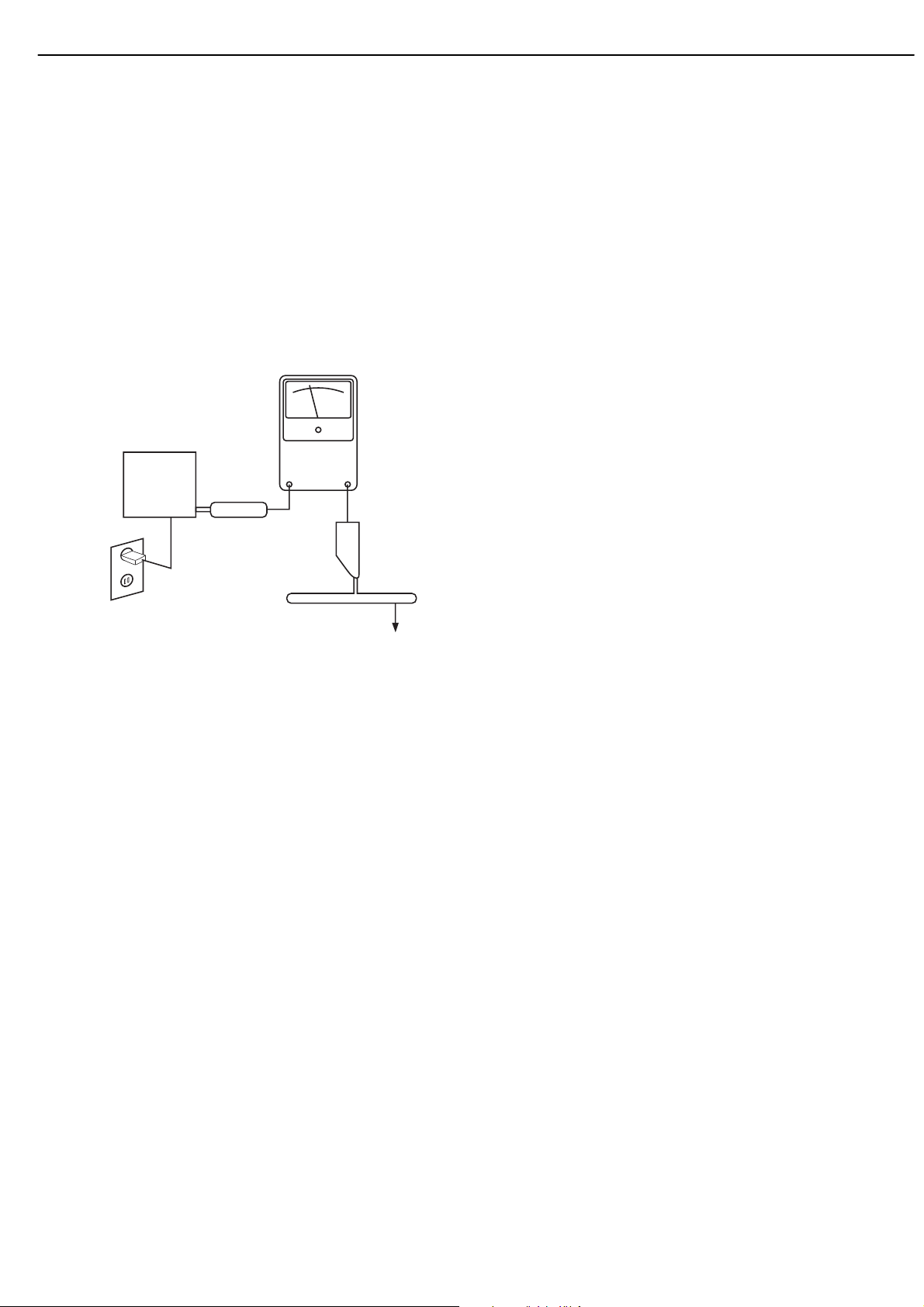

LEAKAGE CURRENT CHECK

Measure leakage current to a known earth ground (water

pipe, conduit, etc.) by connecting a leakage current tester

between the earth ground and all exposed metal parts of the

appliance (input/output terminals, screwheads, metal

overlays, control shaft, etc.). Plug the AC line cord of the

appliance directly into a 120V AC 60Hz outlet and turn the

AC power switch on. Any current measured must not exceed

o.5mA.

ANY MEASUREMENTS NOT WITHIN THE LIMITS

OUTLINED ABOVE ARE INDICATIVE OF A

POTENTIAL SHOCK HAZARD AND MUST BE

CORRECTED BEFORE RETURNING THE APPLIANCE

TO THE CUSTOMER.

harman/kardon

AVR 145/230 service manual

Page 3 of 135

Reading should

not be above

0.5mA

Earth

ground

Device

under

test

Test all

exposed metal

surfaces

Also test with

plug reversed

(Using AC adapter

plug as required)

Leakage

current

tester

AC Leakage Test

Page 4

Technical Specifications AVR145/230

harman/kardon

AVR 145/230 service manual

Page 4 of 135

Audio Section

Stereo Mode

Continuous Average Power (FTC)

50 Watts per channel, 20Hz–20kHz,

@ < 0.07% THD, both channels driven into 8 ohms

5 Channel Surround Modes

Power Per Individual Channel

Front L&R channels:

40 Watts per channel,

@ < 0.07% THD, 20Hz–20kHz into 8 ohms

Center channel:

40 Watts, @ < 0.07% THD, 20Hz–20kHz into 8 ohms

Surround channels:

40 Watts per channel,

@ < 0.07% THD, 20Hz–20kHz into 8 ohms

Input Sensitivity/Impedance

Linear (High Level) 200mV/47kohms

Signal-to-Noise Ratio (IHF-A) 100dB

Surround System Adjacent Channel Separation

Analog Decoding 40dB

(Pro Logic, etc.)

Dolby Digital (AC-3) 55dB

DTS 55dB

FM Tuner Section

Frequency Range 87.5–108MHz

Usable Sensitivity IHF 1.3 µV/13.2dBf

Signal-to-Noise Ratio Mono/Stereo: 70/68dB (DIN)

Distortion Mono/Stereo: 0.2/0.3%

Stereo Separation 40dB @ 1kHz

Selectivity ±400kHz: 70dB

Image Rejection 80dB

IF Rejection 90dB

AM Tuner Section

Frequency Range 522–1620kHz

Signal-to-Noise Ratio 45dB

Usable Sensitivity Loop: 500µV

Distortion 1kHz, 50% Mod: 0.8%

Selectivity ±10kHz: 30dB

Video Section

Video Format PAL/NTSC

Input Level/Impedance 1Vp-p/75 ohms

Output Level/Impedance 1Vp-p/75 ohms

Video Frequency Response

(Composite and S-Video) 10Hz–8MHz (-3dB)

Video Frequency

Response (Component) 10Hz–100MHz (-3dB)

Frequency Response

@ 1W (+0dB, –3dB) 10Hz–130kHz

High Instantaneous

Current Capability (HCC) ±25 Amps

Transient Intermodulation

Distortion (TIM) Unmeasurable

Rise Time 16 µsec

Slew Rate 40V/µsec**

General

Power Requirement AC 220–240V/50Hz

Power Consumption 65W idle, 540W maximum

(5 channels driven)

Dimensions (Max)

Width 440mm

Height 165mm

Depth 382mm

Weight 9.7 kg

Depth measurement includes knobs, buttons and terminal connections.

Height measurement includes feet and chassis.

All features and specifications are subject to change without notice.

Harman Kardon, The Bridge and Logic 7 are

registered trademarks of Harman International Industries, Incorporated.

*Manufactured under license from Dolby Laboratories.

“Dolby,”“Pro Logic” and the Double-D symbol are trademarks of Dolby Laboratories.

"DTS" and "DTS Neo:6" are registered trademarks of DTS,

Inc. "96/24" is a trademark of DTS,Inc.

SA-CD is a trademark of Sony Electronics, Inc.

Apple and iPod are registered trademarks of Apple Computer,Inc.

Cirrus is a registered trademark of Cirrus Logic Corp.

**Without input anti slewing and output isolation networks.

TM

is a trademark of Harman International Industries, Inc.

Page 5

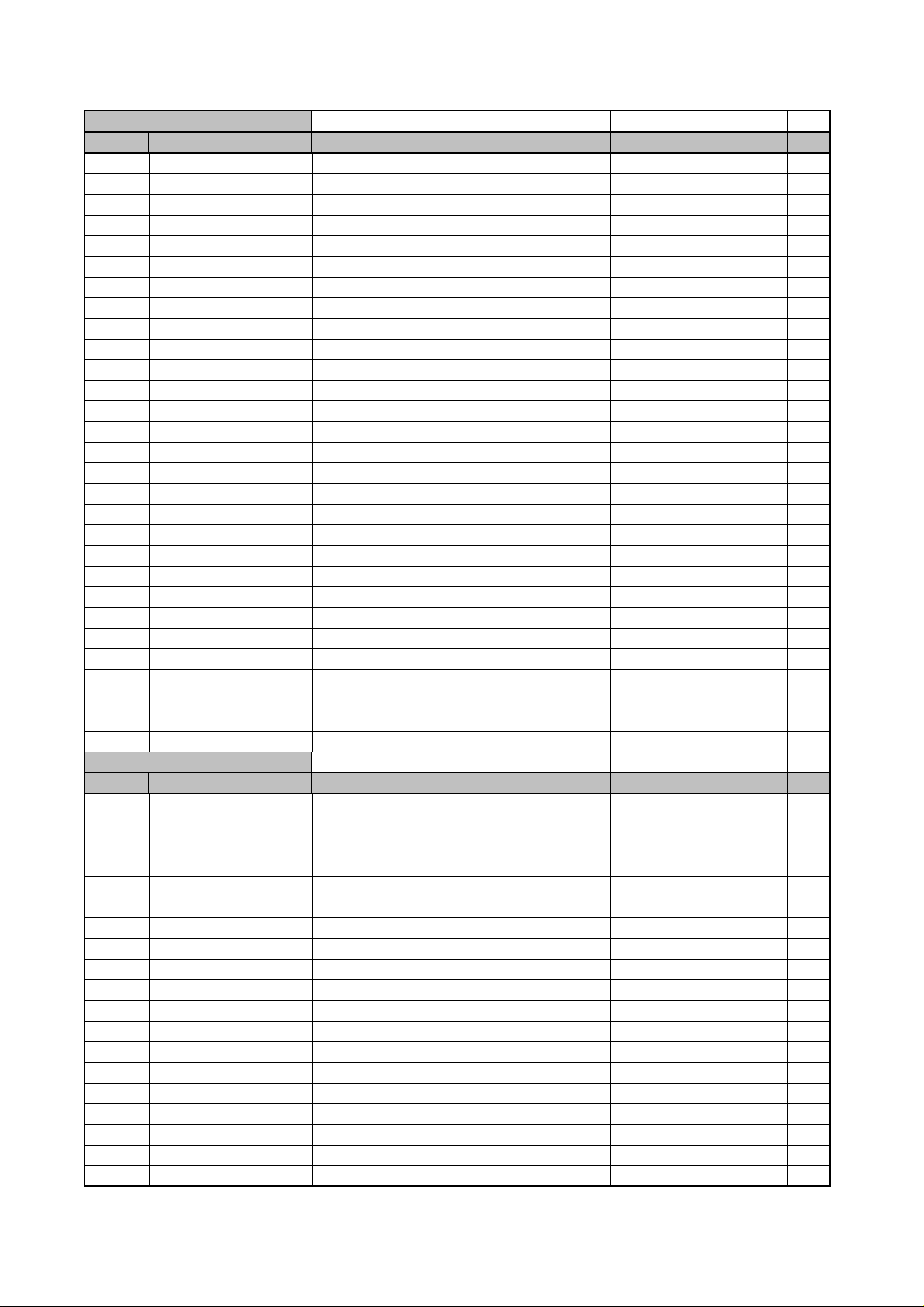

45

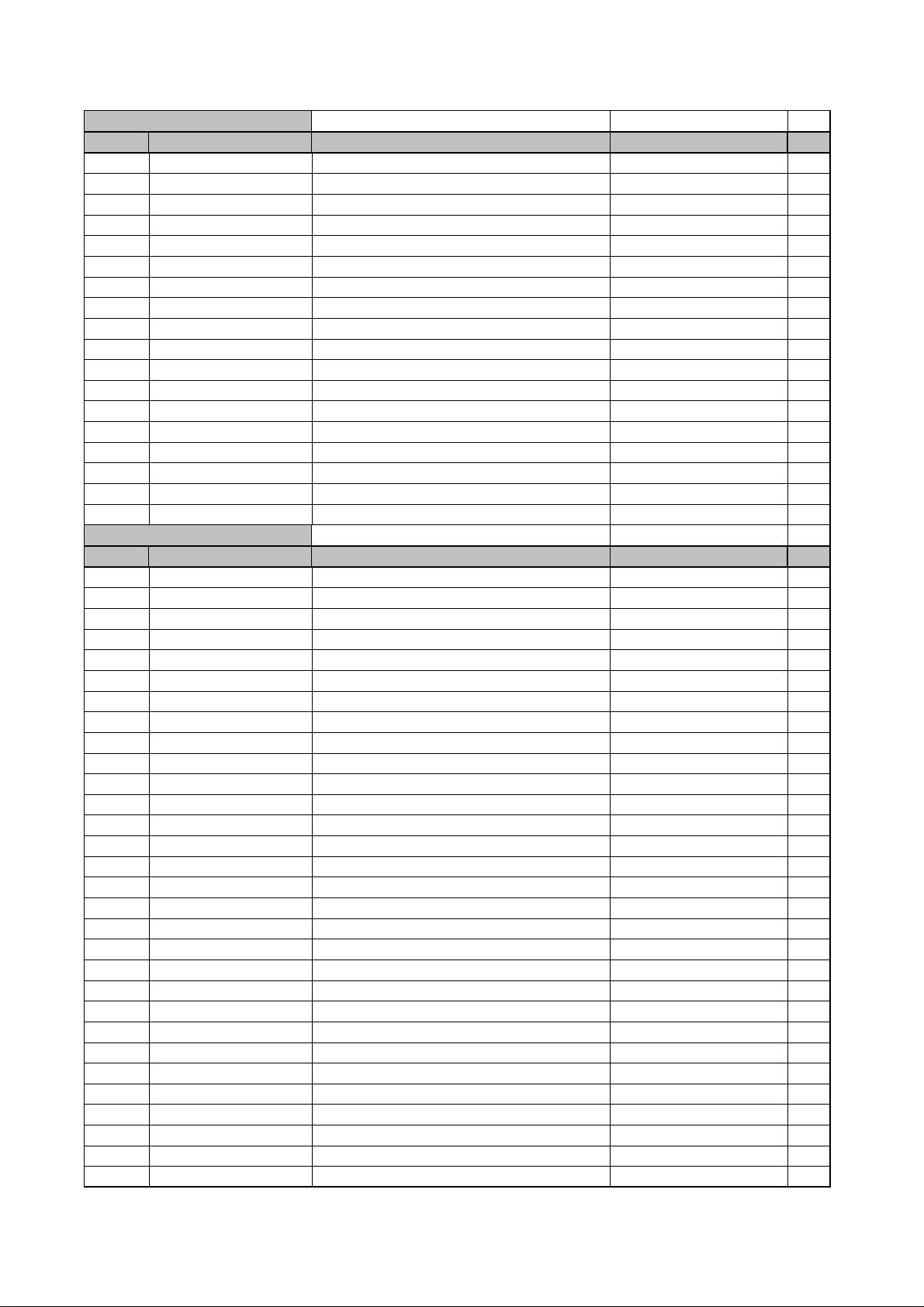

TROUBLESHOOTING GUIDE

SYMPTOM CAUSE SOLUTION

Unit does not function when Main • No AC Power • Make certain AC power cord is plugged into

Power Switch is pushed a live outlet

• Check to see whether outlet is switch-controlled

Display lights,but no sound • Intermittent input connections • Make certain that all input and speaker connections

or picture are secure

• Mute is on • Press Mute Button

• Volume control is down • Turn up volume control

No sound from any speaker; • Amplifier is in protection mode • Check speaker wire connections for shorts at receiver and

light around power switch is red due to possible short speaker ends

• Amplifier is in protection mode • Contact your local Harman Kardon service center

due to internal problems

No sound from surround or • Incorrect surround mode • Select a mode other than Stereo

center speakers • Input is monaural • There is no surround information from mono sources

• Incorrect configuration • Check speaker mode configuration

• Stereo or Mono program material • The surround decoder may not create center- or rear-channel

information from nonencoded programs

Unit does not respond to • Weak batteries in remote • Change remote batteries

remote commands • Wrong device selected • Press the AVR selector

• Remote sensor is obscured • Make certain front panel sensor is visible to remote

or connect an optional remote sensor

Intermittent buzzing in tuner • Local interference • Move unit or antenna away from computers,fluorescent

lights,motors or other electrical appliances

Letters flash in the channel indicator • Digital audio feed paused • Resume play for DVD

display and digital audio stops • Check that Digital Input is selected

In addition to the items shown above,additional information on troubleshooting possible problems with your AVR 145,or installation-related issues, may

be found in the list of "Frequently Asked Questions" which is located in the Product Support section of our Web site at www.harmankardon.com.

harman/kardon

AVR 145/230 service manual

Page 5 of 135

Page 6

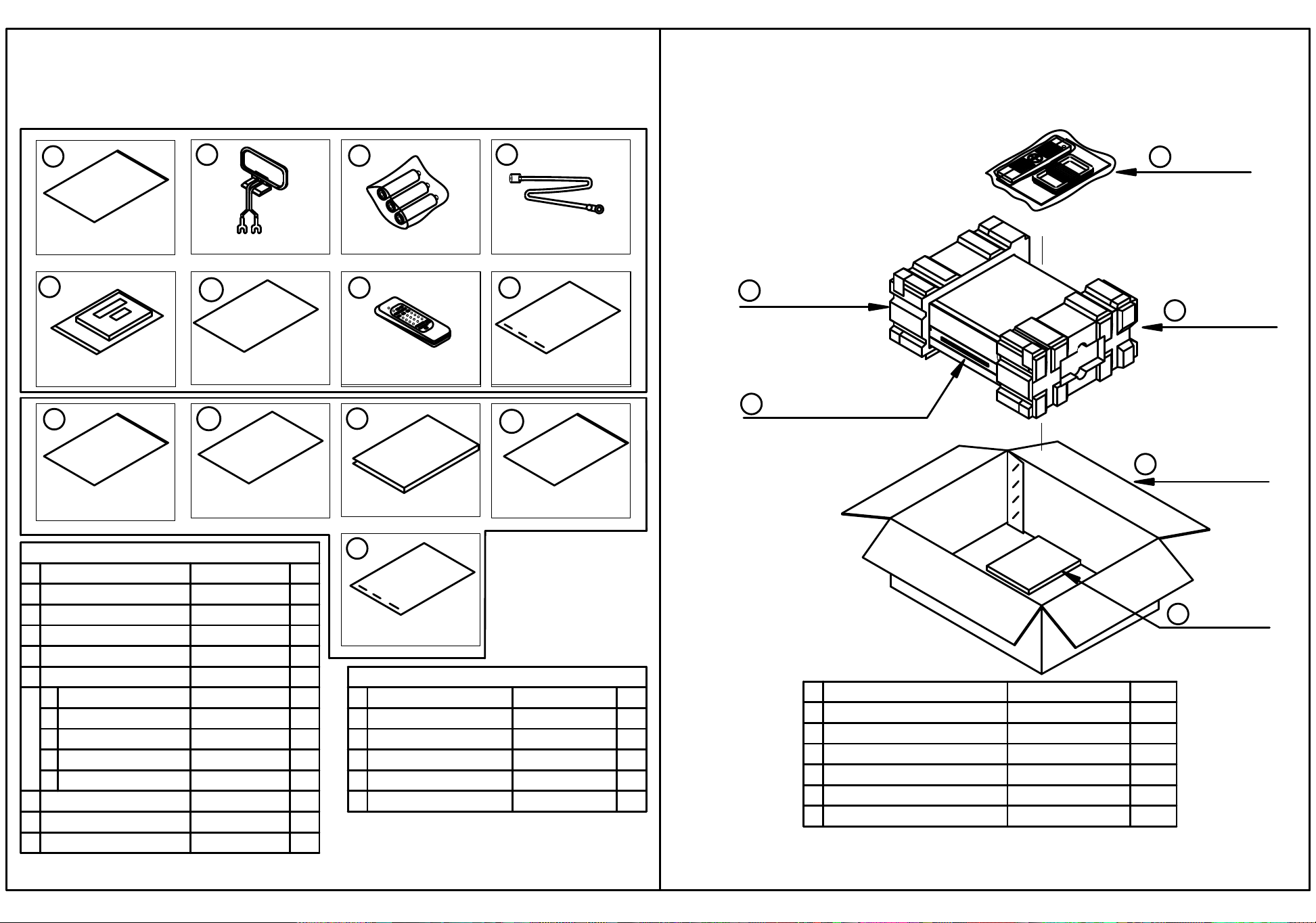

1. Instruction manual ass'y - Accessories

harman/kardon

AVR 145/230 service manual

Page 6 of 135

2. Package Drawing

AVR145/230

1

5

9

POLY BAG

COVER ASS'Y

POLY BAG

2

AM LOOP ANTENNA ASS'Y

6

IMAGE BROCHURES

10

BOOKLET,INFORMATION

3

BATTERY ASS'Y

7

REMOCON

TRANSMITTER ASS'Y

11

MANUAL INSTRUCTION

4

FM 1 POLE ANT

8

STAPLE

12

MANUAL SETUP CODE

2

SNOW PAD (L)

SET

4

ACCESSORY-1

1

SNOW PAD (R)

3

BOX ,OUT CARTON

5

ACCESSORY-1

NO

1

2

3

4

5

6

7

8 STAPLE CPL0905 3

DESCRIPTION

POLY BAG

AM LOOP ANTENNA ASS'Y

BATTERY 3

FM 1 POL ANT

COVER ASS'Y

1

COVER A

2

COVER B

SHEET,FRONT COVER

3

PAD , COVER

4

5

BAG , POLY

IMAGE BROCHURES

REMOCON ASS'Y CARTAVR145/230 1

PARTS NO. Q,ty

CPB1061Y

CSA1A027Z

CABR03P3

CSA1A018Z 1

CGRAVR130/230ZA

CGR1A331M7H43 1

CQE1A220Z

CPS1A676 1

CPB1A176Z 1

HQE1A273Z

13

1

1

STAPLE

1

1

NO

1CGR1A332M7H43

1

1

9

BOOKLET,INFORMATION

10

11

12

MANUAL ,SETUP GUIDE

13

STAPLE CPL0905 3

ACCESSORY-2

DESCRIPTION

PARTS NO. Q,ty

CQE1A180Z 1

CQX1A1135YMANUAL,INSTRUCTION

CQX1A1138X

DESCRIPTIONNO

ACCESSORY-1

1CPB1061YPOLY BAG

1

1

1

SNOW,PAD(L)

2

3

SNOW,PAD(R)

4

SET

BOX,OUT CARTON5

6

ACCESSORY-2 CQXAVR145/230

CQXAVR145/230

CPS4A564

CPS4A565

AVR145/230SET

CPG1A820W

Q,tyPARTS NO.

1

1

1

1

6

1

1

ACCESSORY-2

Page 7

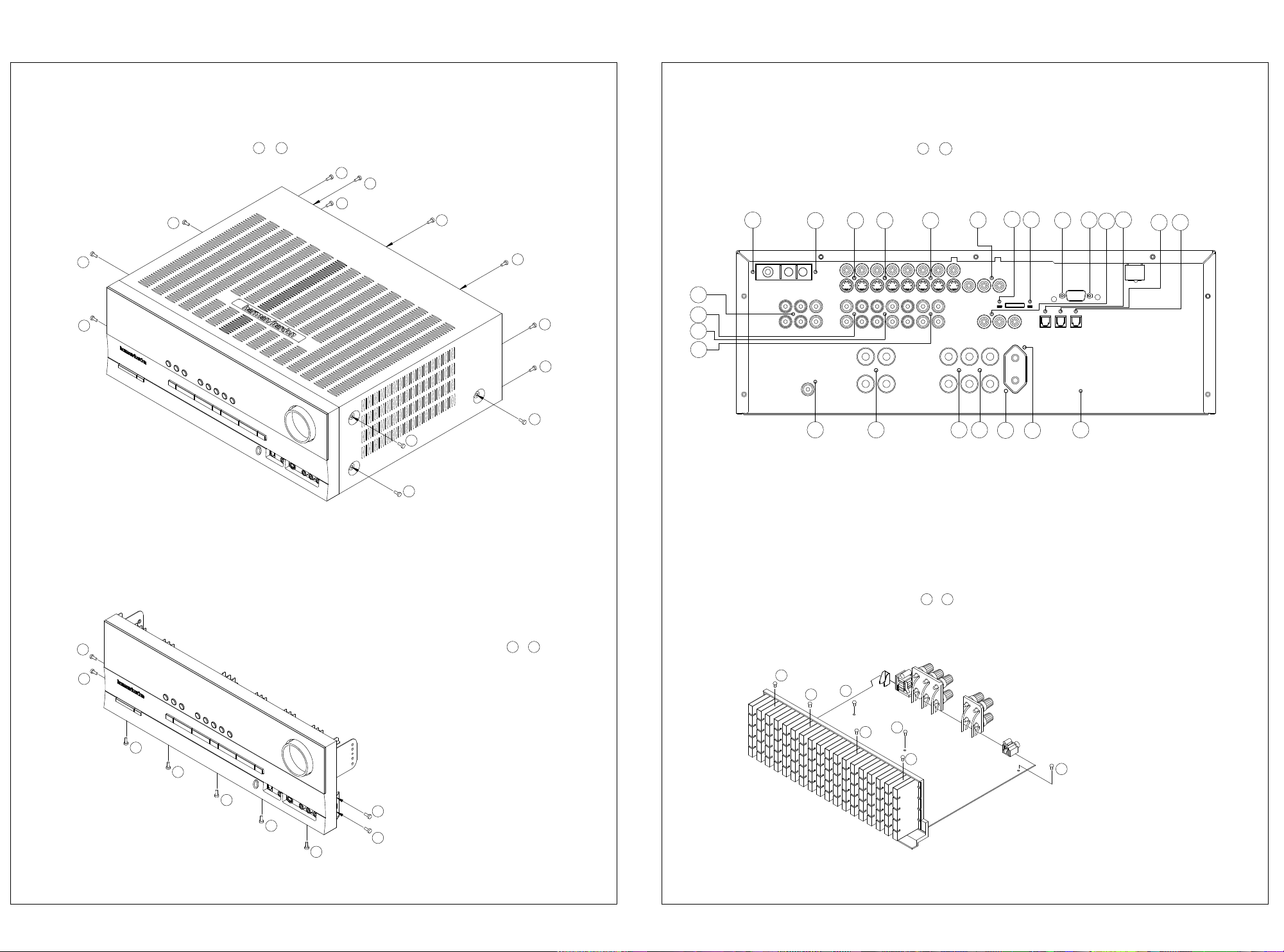

DISASSEMBLY

harman/kardon

AVR 145/230 service manual

Page 7 of 135

AVR145/230

1. Removing the Top Cabinet

Remove the Screws

6

4

5

3. Removing the Rear Panel

13

1

~

10

9

11

7

8

12

13

3

1

2

Remove the Screws

6

7

8

9

10

19

5

4 3 2

20 21 22

25

1

~

11

23

12

24

13

25

1

14

15

16

17 18

9

8

7

4. Removing the Main PCB

1 7

Remove the Screws

~

2. Removing the Front Panel

Remove the Screws

6

5

1

4

2

3

1 9

~

1

5

2

6

3

4

7

Page 8

Page 8 of 135

AVR145

harman/kardon

AVR145 DISASSEMBLY PROCEDURE

1 TOP-CABINET (21) REMOVAL

1. Remove 13 screws (S1,S7) and then remove the Top-cabinet.

2 FRONT PANEL ASS’Y REMOVAL

1. Remove the Top-cabinet, referring to the previous step 1.

2. Disconnect the card cable between connector (CN72-17p) on the FIP PCB (37-1) and connector (CN72) on the Input PCB (39-1).

3. Disconnect the lead wire (BN81-8P) on the FIP PCB (37-1) from connector (CN81) on the Trans PCB (40-4).

4. Disconnect the lead wire (BN22-6P) on the Phone PCB (37-5) from connector (CN22) on the Input PCB (39-1).

5. Disconnect the lead wire (BN18-5P) on the Phone PCB (37-5) from connector (CN18) on the Input PCB (39-1)

6. Disconnect the lead wire (BN10-4P) on the Volume PCB (37-6) from connector (CN10) on the Input PCB (39-1)

7. Disconnect the lead wire (BN41-6P) on the Volume PCB (37-6) from connector (CN41) on the Video PCB (41)

8. Remove 1 screw (S10) and then lead wire (JW82-1P,JW83-1P) on the Phone PCB (37-5).

9 .Remove 1screw (S10) and then lead wire (JW84-1P) on the Volume PCB (37-3).

10. Remove 10 screws (S1) and then remove the Front Panel ASS’Y.

3 VOLUME PCB (37-6) REMOVAL

1. Remo ve the Top-cabinet, r eferring to t he prev iou s step 1.

2. Remove the Front Panel ASS’Y, referring to the previous step 2.

3. Pull out the Volume Knob ASS’Y.

4. Disconnect connector (CN84) on the Volume PCB (37-6) from the lead wire (BN84-5P) on the FIP PCB (37-1).

5. Remove 8 screws (S2,S14), and then remove the Volume PCB (37-6).

4 PHONE PCB (37-5) REMOVAL

1. Remo ve the Top-cabinet, r eferring to t he prev iou s step 1.

2. Remove the Front Panel ASS’Y, referring to the previous step 2.

3.. Disconnect connector (CN85)on the Phone PCB (37-5) from the lead wire (BN85-2P) on the FIP PCB (37-1).

4. Remove 2 screws (S2) and then remove the Phone PCB (37-5).

5 POWER LED PCB (37-3) REMOVAL

1. Remo ve the Top-cabinet, r eferring to t he prev iou s step 1.

2. Remove the Front Panel ASS’Y, referring to the previous step 2.

3. Disconnect connector (CN88) on the Power Led PCB (37-3) from the lead wire (BN88-4P) on the FIP PCB (37-1) .

4. Remove 2 screws (S2) and then remove the Power led PCB (37-3).

6 FIP PCB (37-1) REMOVAL

1. Remo ve the Top-cabinet, r eferring to t he prev iou s step 1.

2. Remove the Front Panel ASS’Y, referring to the previous step 2.

3. Disconnect the lead wire (BN84-5P) on the FIP PCB (37-1) from connector (CN84) on the Volume PCB (37-6).

4. Disconnect the lead wire (BN85-2P) on the FIP PCB (37-1) from connector (CN85) on the Phone PCB (37-5).

5. Disconnect the lead wire (BN88-4P) on the FIP PCB (37-1) from connector (CN88) on the Power Led PCB (37-3).

6. Disconnect the connector (CN89) on the FIP PCB (37-1) from lead wire (BN89-4P) on the Key PCB (37-2).

7. Remove 3 screws (S2) and then remove the Guide PCB (37-8) & the FIP PCB (37-1).

7 KEY PCB (37-2) REMOVAL

1. Remo ve the Top-cabinet, r eferring to t he prev iou s step 1.

2. Remove the Front Panel ASS’Y, referring to the previous step 2.

3. Remove the FIP PCB (37-1), referring to the previous step6.

4. Remove 10 screws (S2) and then remove the Key PCB (37-2).

Page 9

Page 9 of 135

AVR145

harman/kardon

8 TUNER MODULE (42) REMOVAL

1. Remove the Top-cabinet, referring to the previous step 1.

2. Disconnect the card cable between connector (CON1-13p) on the Tuner module (42) and connector (CN13) on Input PCB (39-1).

3. Remove 2 screws (S8) and then remove the Tuner Module (42).

9 VIDEO PCB (41) REMOVAL

1. Remove the Top-cabinet, referring to the previous step 1.

2. Disconnect the card cable between connector (BN14-13p) on the Video PCB (41) and connector (CN14) on the Input PCB (39-1).

3. Disconnect connector (CN43 ) on the Vide o PCB (41 ) from the lead wire (BN43-4P ) on the Re gulator PCB (A)(40 -2) .

4. Disconnect the card cable between connector (CN42) on the Video PCB (41) and connector (BN44-7p) on the I-Pod PCB (39-2).

5. Disconnect connector (CN41) on the Video PCB (41) from the lead wire (BN41-6P) on the Volume PCB (37-6).

6. Remove 6 screws (S8) and then remove the Video PCB (41).

10 I-POD PCB (39-2) REMOVAL

1. Remove the Top-cabinet, referring to the previous step 1.

2. Remove the Video PCB (41), referring to the previous step9

3. Disconnect connector (CN46) on the I-Pod PCB (39-2) from the lead wire (BN46-3P) on the Input PCB (39-1).

4. Disconnect the card cable between connector (BN19-9p)) on the I-Pod PCB (39-2) and connector (CN19) on the Input PCB (39-1).

5. Disconnect the card cable between connector (BN44-7p)) on the I-Pod PCB (39-2) and connector (CN42) on the Video PCB (41).

6. Disconnect the card cable between connector (CN47-7p)) on the I-Pod PCB (39-2) and connector (CN47) on the RS232 PCB (37-7).

7. Remove 2 screws (S13) and then remove the I-Pod PCB (39-2).

11 RS232 PCB (37-7) REMOVAL

1. Remove the Top-cabinet, referring to the previous step 1.

2. Remove the Video PCB (41), referring to the previous step9

3. Disconnect the card cable between connector (CN47) on the RS232 PCB (37-7) and connector (CN47-7) on the RS232 PCB (37-7).

4. Remove 2 screws and then remove the RS232 PCB (37-7).

12 INPUT PCB (39-1) REMOVAL

1. Remove the Top-cabinet, referring to the previous step 1.

2. Remove the Tuner module (42), referring to the previous step8

3. Remove the Video PCB (41), referring to the previous step9

4. Disconnect connector (CN20) on the the Input PCB (39-1) from the lead wire (BN20-5P) on the Regulator PCB (B)(40-5).

5. Disconnect connector (CN22) on the Input PCB (39-1) from the lead wire (BN22-6P) on the Phone PCB (37-5).

6. Disconnect connector (CN18) on the Input PCB (39-1) from the lead wire (BN18-5P) on the Phone PCB (37-5)

7. Disconnect connector (CN10) on the Input PCB (39-1) from the lead wire (BN10-4P) on the Volume PCB (37-6).

8. Disconnect the card cable between connector (CN14) on the Input PCB (39-1) and connector (BN14-13p)) on the Video PCB (41).

9. Disconnect the card cable between connector (CN19) on the Input PCB (39-1) and connector (BN19-9p) on the I-Pod PCB (39-2)

10. Disconnect the lead wire (BN46-3P) on the Input PCB (39-1) from connector (CN46) on the I-Pod PCB (39-2).

11. Disconnect the card cable between connector (CN12-21p) on the Input PCB (39-1) and connector (CN12-21p)

on the main PCB (38-1)

12. Disconnect the card cable between connector (CN11-13p) on the Input PCB (39-1) and connector (CN11) on the main PCB (38-1)

13. Disconnect the card cable between connector (CN72) on the Input PCB (39-1) and connector (CN72-17p) on the FIP PCB (37-1)

14. Remove 11 screws (S8,S15) and then remove the Input PCB (39-1).

13 POWER TRANS (36) & POWER PCB ASS’Y(40) REMOVAL

1. Remove the Top-cabinet, referring to the previous step 1.

2. Disconnect lead wire of the Power Trans (36) from connector (CN91-3P) on the Main PCB (38-1)

3. Disconnect connector (CN19-3P,CN20-4P) on TRANS PCB (40-3) from the lead wire (BN19-3P,BN20-4P) on the Main PCB (38-1).

4. Disconnect the lead wire (BN96-8P) on the Power PCB (40-4) from connector (CN96) on the Regulator PCB (B)(40-5).

5. Disconnect the lead wire (BN99-8P) on the Power PCB (40-4) from connector (CN99) on the Regulator PCB (A)(40-2).

6. Disconnect connector (CN81) on the Trans PCB (40-4) from the lead wire (BN81-8P) on the FIP PCB (37-1).

7. Remove 4 Trans screws (S9) and then remove the Power Trans (36)& Power PCB ASS’Y(40) REMOVAL .

Page 10

Page 10 of 135

AVR145

harman/kardon

14 MAIN PCB AS S ’Y (38 -1 ) REMOVA L

1. Remove the Top-cabinet, referring to the previous step 1.

2. Remove the Tuner module (42), referring to the previous step8.

3. Remove the Video PCB (41) referring to the previous step9.

4. Remove the I-Pod PCB (39-2), referring to the previous step 10.

5. Remove the RS232 PCB (37-7), referring to the previous step 11.

6. Remove the Input PCB (39-1), referring to the previous step 12.

7. Remove the AC Cord(35) on the Main PCB (38-1)

8. Disconnect the lead wire (BN90-2P) on the Main PCB (38-1) from connector (CN86) on Moms PCB (37-4).

9. Disconnect connector (CN91-3P) on the Main PCB (38-1) from lead wire of the Power Trans (36)

10. Disconnect the lead wire (BN89-2P) on the Main PCB (38-1) from connector (CN89) on Regulator PCB (A)(40-2).

11. Disconnect the lead wire (BN19-3P,BN20-4P) on the Main PCB (38-1) from connector (CN19-3P,CN20-4P) on TRANS PCB (40-4).

12. Remove 11screws (S13-1EA, S4-2EA, S6-2EA, S8-6EA) and then remove the Main PCB ASS’Y (38-1).

Page 11

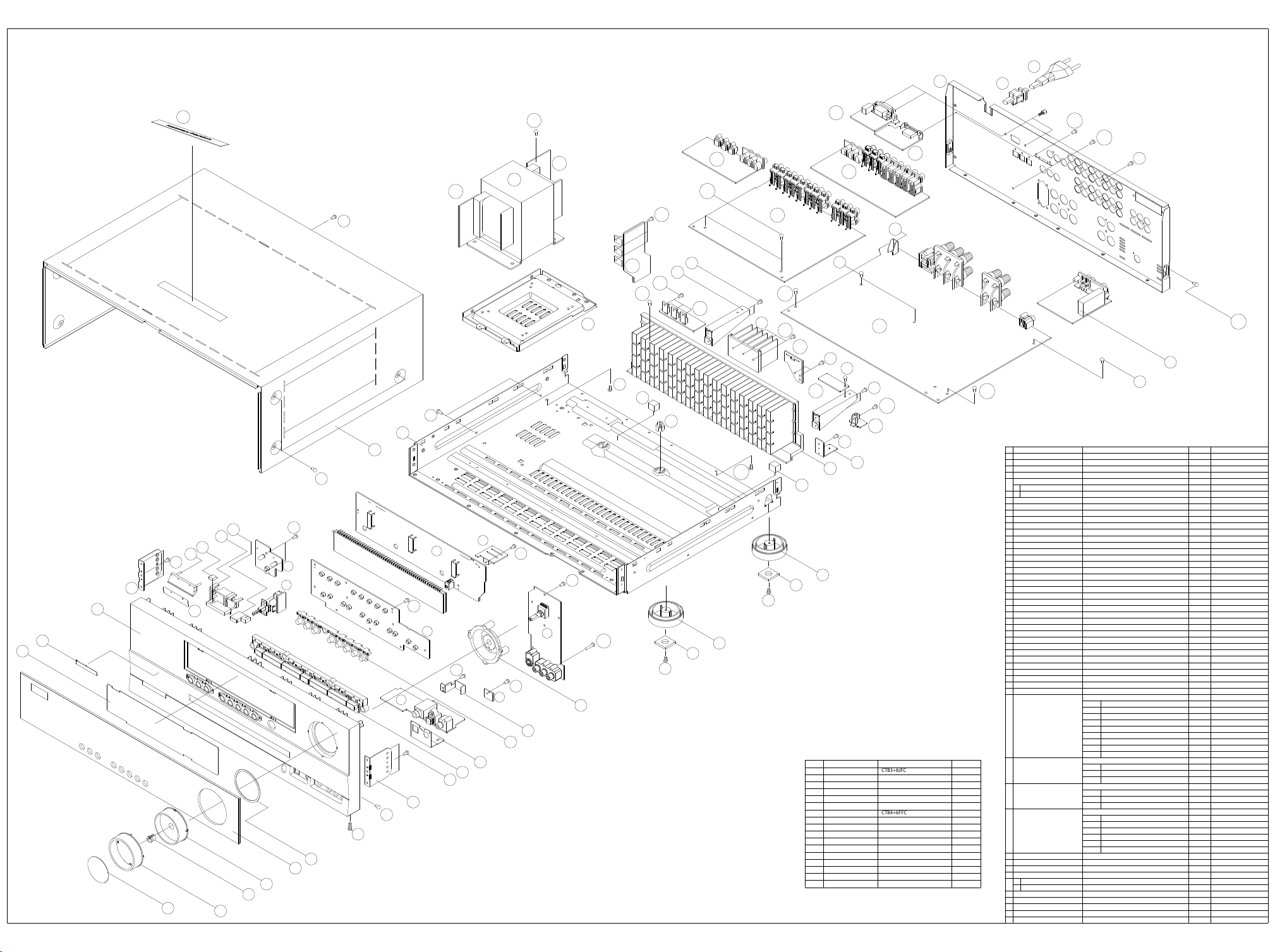

AVR145/230 EXPLODED VIEW

harman/kardon

AVR 145/230 service manual

Page 11 of 135

Only screws marked in yellow are stocked

33

35

34

44

S9

37-7

S13

S13

40-3

36

40-4

40-5

S16

30

S1

40-1

41

S15

39-1

S6

S5

x2

39-2

32

S8

S16

S17

S4

40-2

29

45

S12

38-1

S10

38-2

S4

S4

S5

43

S5

28

39-3

22

21

S7

37-4

37-3

S2

37-1

37-8

S2

S2

S2

37-2

37-6

S11

23

S2

S4

15

13

14-1

14

S2

10

9

18

8

7

S10

S4

24

26

25

24

23

S2

37-5

37-9

19

16

12

17

11

S2

10

S1

S1

6

5

4

DESCRIPTION PARTS NO. Q,ty

NO

S1

SCREW

S2

SCREW

S3

SCREW

S4

SCREW

S5

SCREW

S6

SCREW

S7

SCREW

S8

SCREW,TRANS

S9

SCREW

S10

SCREW

S11

SCREW CTB3+10JR 3

S12

SCREW

S13

SCREW,SPECIAL CHD1A012R 18

S14

SCREW,SPECIAL

S15

SCREW,SPECIAL

S16

SCREW,SPECIAL

S17

3

1

2

S5

S15

S14

40-2

S5

27

CTB3+10GR

CTWS3+10GR

CTW3+8JR

CTB3+8JR

CTW3+12JR

CTB4+6FFC

CTB3+10GFZR

CHD1A023R

CTB3+6JR

CTB3+16GFZR

CTB3+8JFZR

CHD1A012ZR 2

CHD3A012R 6

CHD4A012R 5

17CTB3+8JFCSCREW

35

1

9

10

3

6

19

4

19

2

3

DESCRIPTION

NO

ORNAMENT,VOLUME CGU1A318Z 1

1

CAP,VOLUME

2

HOLDER,VOLUME

3

INDICATOR,VOLUME

4

WINDOW ASS'Y

5

WINDOW,FIP CGU1A399Y

1

BADGE,MODEL

2

6

FILTER,FIP

7

BDAGE,HARMAN/KARDON

8

PANEL,FRONT

9

BRACKET,SIDE

10

KNOB,FUNCTION

11

KNOB,DISPLAY

12

KNOB,POWER

13

INDICATOR,POWER

14

KNOB,MOMS

15

BRACKET,PCB CMK2A010

16

PLATE,SHIELD

17

SHEET , REFLECTION CMZ1A120 1

18

HOLDER,LED

19

BRACKET,FIP

20

CABINET,TOP

21

CHASSIS,BOTTOM

22

RUBBER,CUSHION

23

FOOT

24

SUPPORT,CUSHION

25

HEAT SINK

26

BRACKET,PCB

27

HOLDER,PCB

28

BRACKET,TRANS

29

BRACKET,PCB(H/T)

30

BRACKET,PCB CMD1A570 1

31

BRACKET,PCB

32

PANEL,REAR

33

BUSHING,AC CORD

34

CORD,POWER

35

TRANS,POWER

36

FRONT PCB ASS'Y

37

MAIN PCB ASS'Y COP11911E 1

38

INPUT PCB ASS'Y COP11912E 1

39

POWER PCB ASS'Y

40

VIDEO PCB ASS'Y

41

TUNER MODULE

42

43

BADGE ASS'Y

44

ORNAMENT,BADGE

1

BADGE,H/K(TOP)

2

45

PARTS NO.

CGX1A338MBC63

CMH1A214

CGL1A222

CGUAVR145

CGB1A168Z

CMZ2A090SHEET,VOLUME 1

CMZ1A088

KGB1A158Z

CGW1A427RDZH43

CMD2A443

CBT1A1028MBYG27

CBT1A1027K128

CBT1A1026MMZG27

CGL1A258Z

CBC1A158MBZG27

CMC1A302

CMH1A215

CMD1A209

CKC5B145S46Z

CUA2A229

CHG1A329

CKL2A069H43

CHG1A104Z

CMY2A269

CMD1A417

CHE1A170

CMD1A487

CMD1A398

CMD1A387

CKF4A319Z

KHR1A028

CJA2B043ZA

CLT5V045ZE

COP11910E

FIP PCB

37-1

KEY PCB

37-2

POWER LED PCB

37-3

MOMS PCB

37-4

PHONE PCB

37-5

VOLUME PCB

37-6

RS232 PCB

37-7

GUIDE PCB(CARD CABLE)

37-8

MAIN PCB

38-1

GUIDE PCB(CARD CABLE) 1

38-2

INPUT PCB

39-1

iPOD PCB 1

39-2

RDS PCB 1

39-3

COP11916E 1

DIGITAL IN OUT PCB 1

40-1

REGULATOR PCB(A) 5

40-2

TRANS PCB 1

40-3

TRANS PCB 1

40-4

REGELATOR PCB(B) 1

40-5

COP11917E 1

CNVM9014MS171L

CHG1A160ZCUSHION 1

CGX1A375ZA

CGX1A375M7G32

KGB1A159Z

CMY1A249HEAT SINK 1

42

S4

Q,ty

Weright

1

1

1

1

1

1

1

1

1

2

11

1

1

1

1

1

1

3

1

1

4

4

1

1

2

2

1

2

2

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Page 12

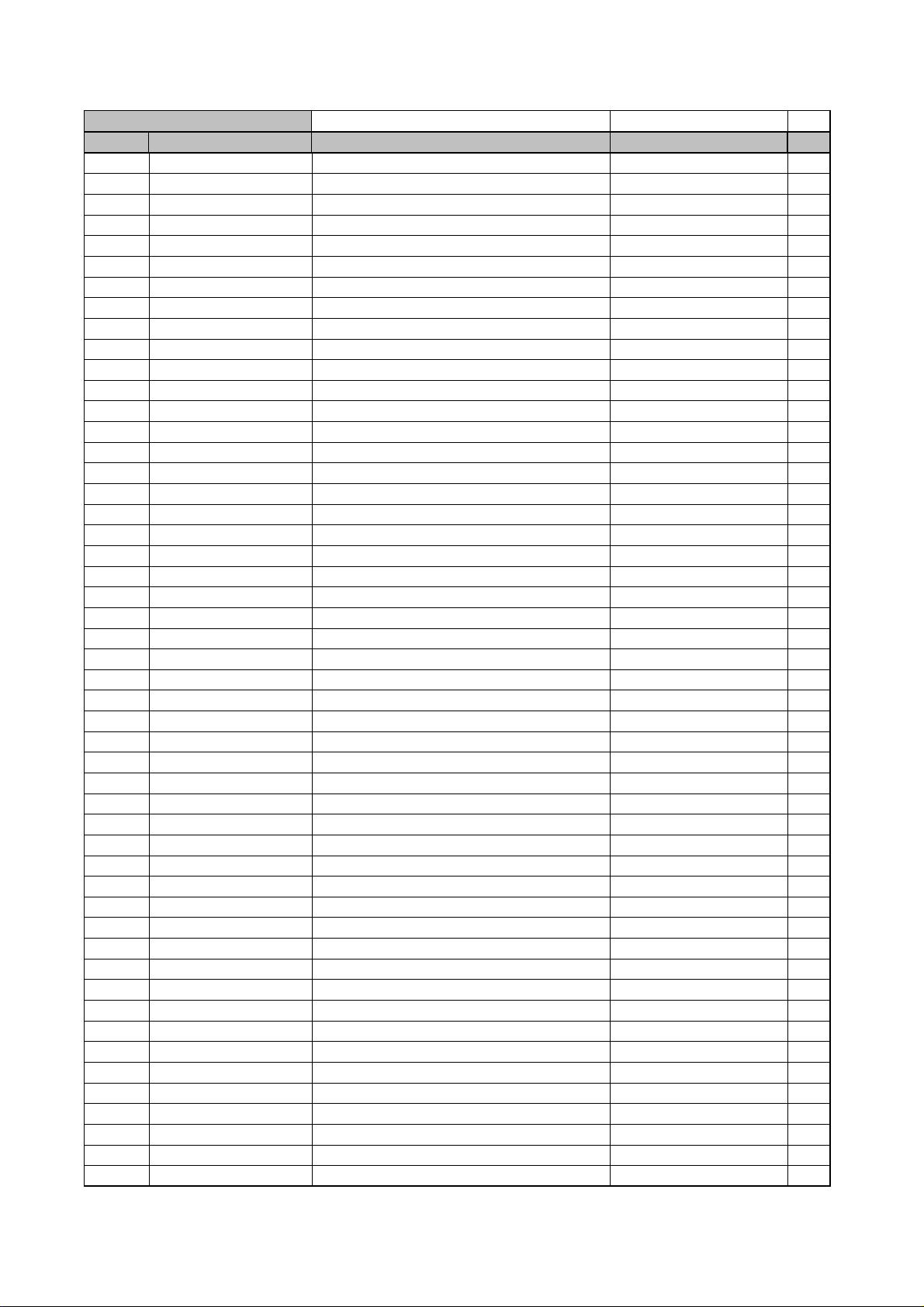

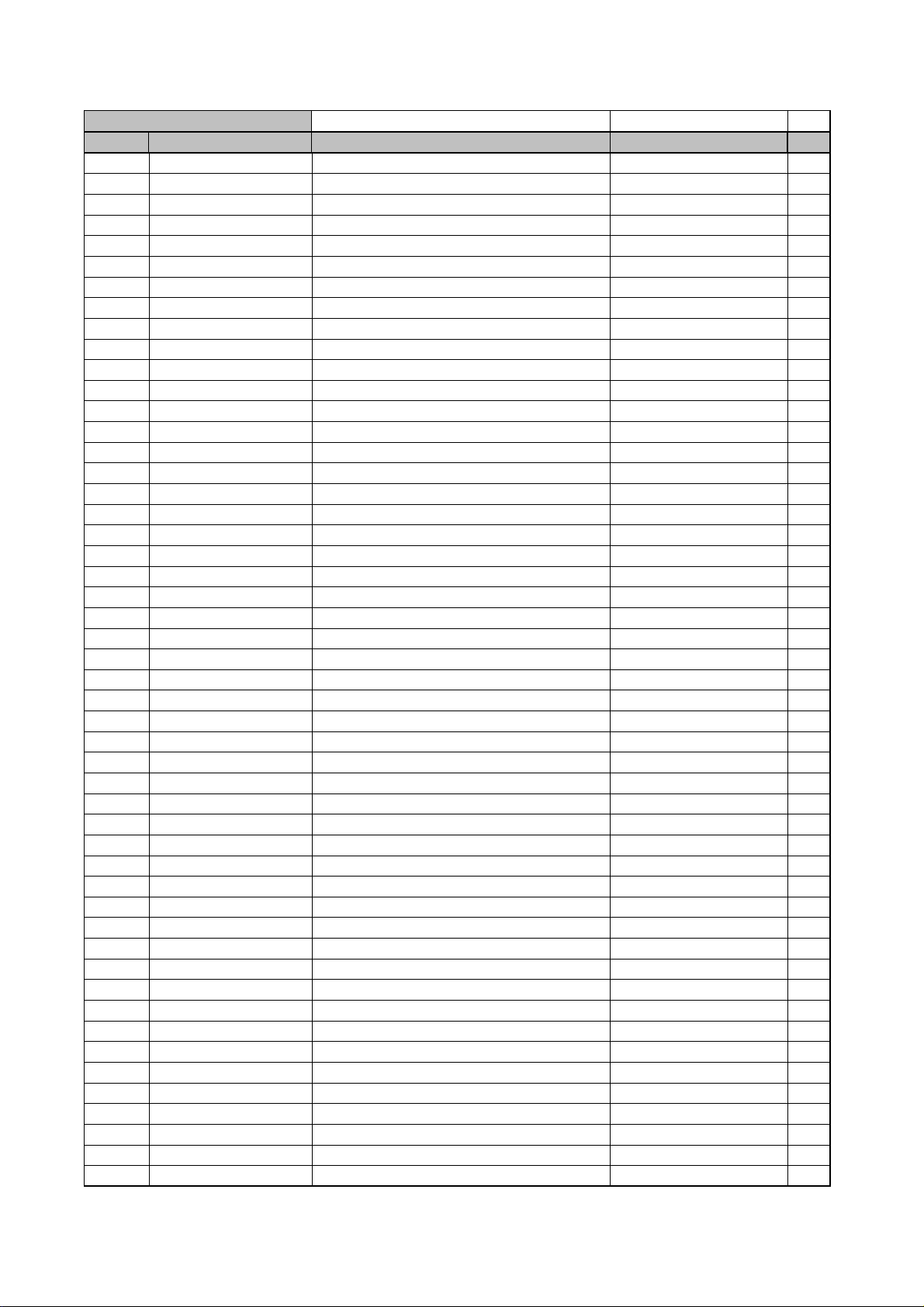

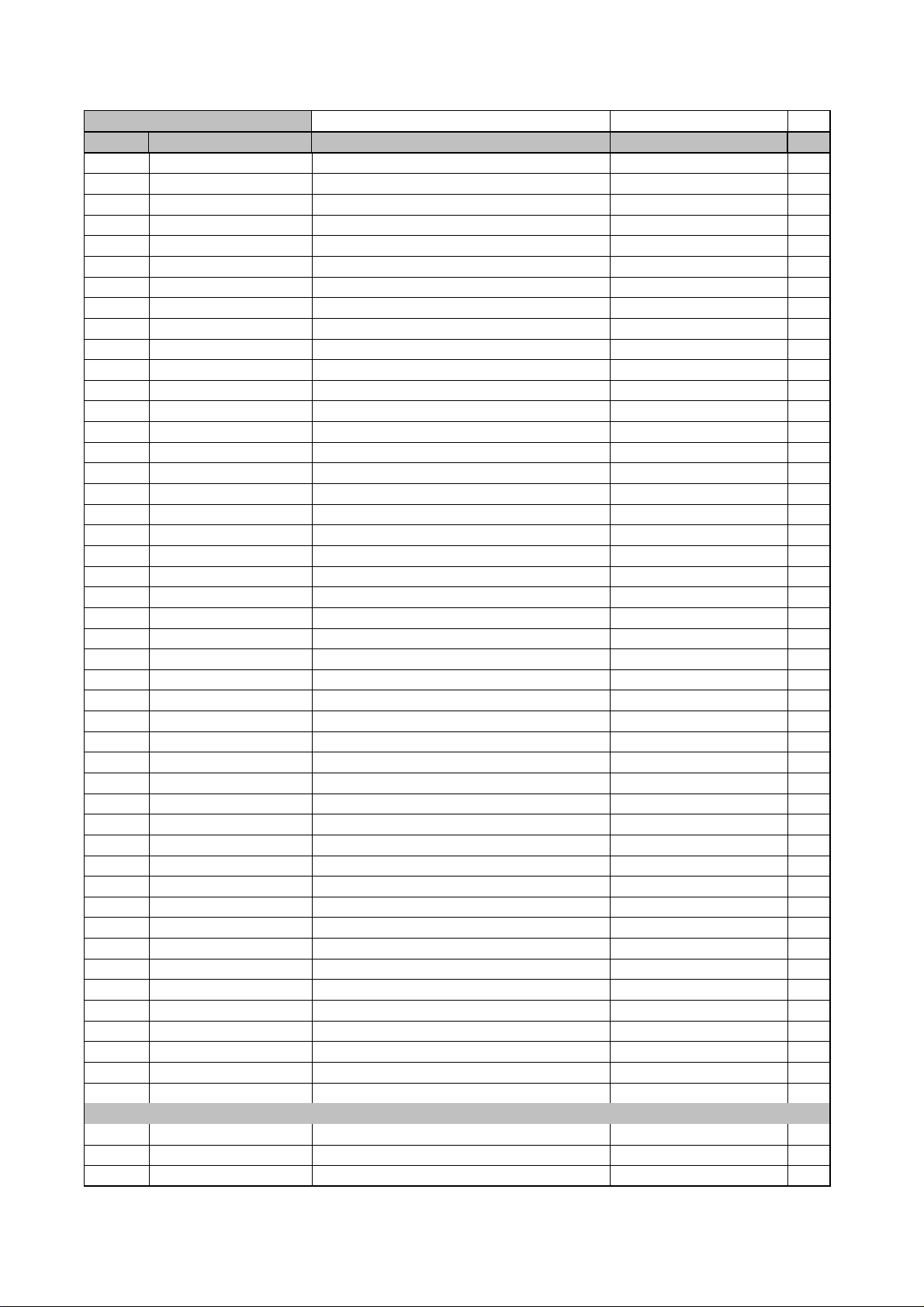

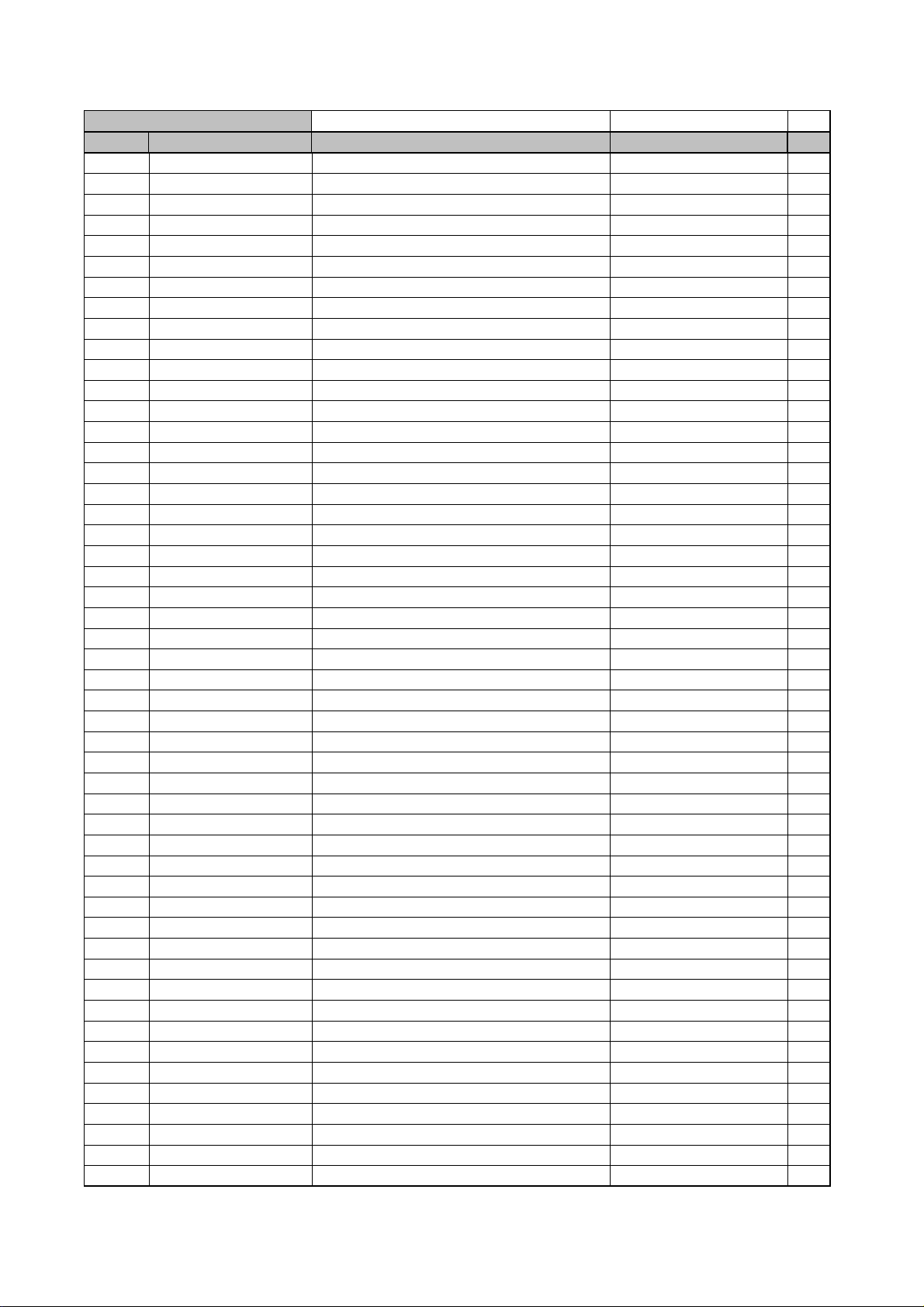

AVR145/230 Electrical Parts List

harman/kardon

AVR 145/230 service manual

Page 12 of 135

Ref. # Part Number

CGL1A222 INDICATOR , VOLUME INDICATOR 1

CGUAVR145 WINDOW ASS'Y ASS'Y 1

CGB1A168Z BADGE , AVR145 BADGE 1

CGU1A399Y WINDOW , FIP FIP WINDOW 1

CGU1A318Z ORNAMENT , VOLUME ORNAMENT 1

CGX1A338MBC63 CAP , VOLUME CAP 1

CGX1A375ZA BADGE ASS'Y ASS'Y 1

CGX1A375M7G32 ORNAMENT , BADGE ORNAMENT 1

KGB1A159Z BADGE , HARMAN/KARDON(TOP) BADGE 1

CKC5B145S46Z CABINET , TOP TOP CABINET 1

BKC5C145S46 TOP CABINET TOP CABINET 1

CMH1A214 HOLDER , VOLUME HOLDER 1

CMZ2A090 SHEET,VOLUME SHEET 1

CQB1A549Z LABEL , ATTENTION LABEL 1

CQB1A551Z LABEL , BAR CODE LABEL 1

CQB1A622 LABEL , SERIAL NO LABEL 1

CTB3+8JFC SCREW SCREW 13

CTB4+6FFC SCREW SCREW 6

CHE154 CLAMPER , ARM CLAMPER 0,12

CPG1A820W BOX , OUT CARTON BOX 1

CPS4A564 PAD , SNOW L PAD 1

CPS4A565 PAD , SNOW R PAD 1

CQB1A551Z LABEL , BAR CODE LABEL 2

CQB1A795Z LABEL , COUNTRY(AVR245/230) LABEL 2

CQS1A001 RIBON , BAR CODE SONY(TR-4070) 0,12

CQXAVR145/230 INSTRUCTION MANUAL ASS'Y ASS'Y 1

CARTAVR145/230 REMOCON ASS'Y ASS'Y 1

CGRAVR130/230ZA COVER ASS'Y ASS'Y 1

CGR1A331M7H43 COVER A COVER 1

CGR1A332M7H43 COVER B COVER 1

CPS1A676 PAD , COVER PAD 1

CQE1A220Z SHEET , FRONT COVER SHEET 1

CPL0905 STAPLE STAPLE 6

CQE1A180Z BOOKLET , IMFORMATIONS BOOKLET 1

CQX1A1135Y MANUAL , INSTRUCTION AVR145/23 MANUAL 1

CQX1A1138X MANUAL , SETUP(AVR145/230) MANUAL 1

CSA1A018Z FM 1 POLE ANT ANT 1

HQE1A273Z HARMAN IMAGE BROCHURES BROCHURES 1

CRE1A037 LOCKER LOCKER 10

KPL6500 STAPLE STAPLE 8

Description

Value Qty

BOTTOM CHASSIS ASS'Y

Ref. # Part Number

CUAAVR145/230 BOTTOM CHASSIS ASS'Y ASS'Y 1

CHD1A012ZR SCREW , SPECIAL Not stocked 2

CHD1A023R SCREW , SPECIAL Not stocked 4

CHD4A012R SCREW , SPECIAL Not stocked 5

CHE170 HOLDER , PCB HOLDER 2

Description

Value Qty

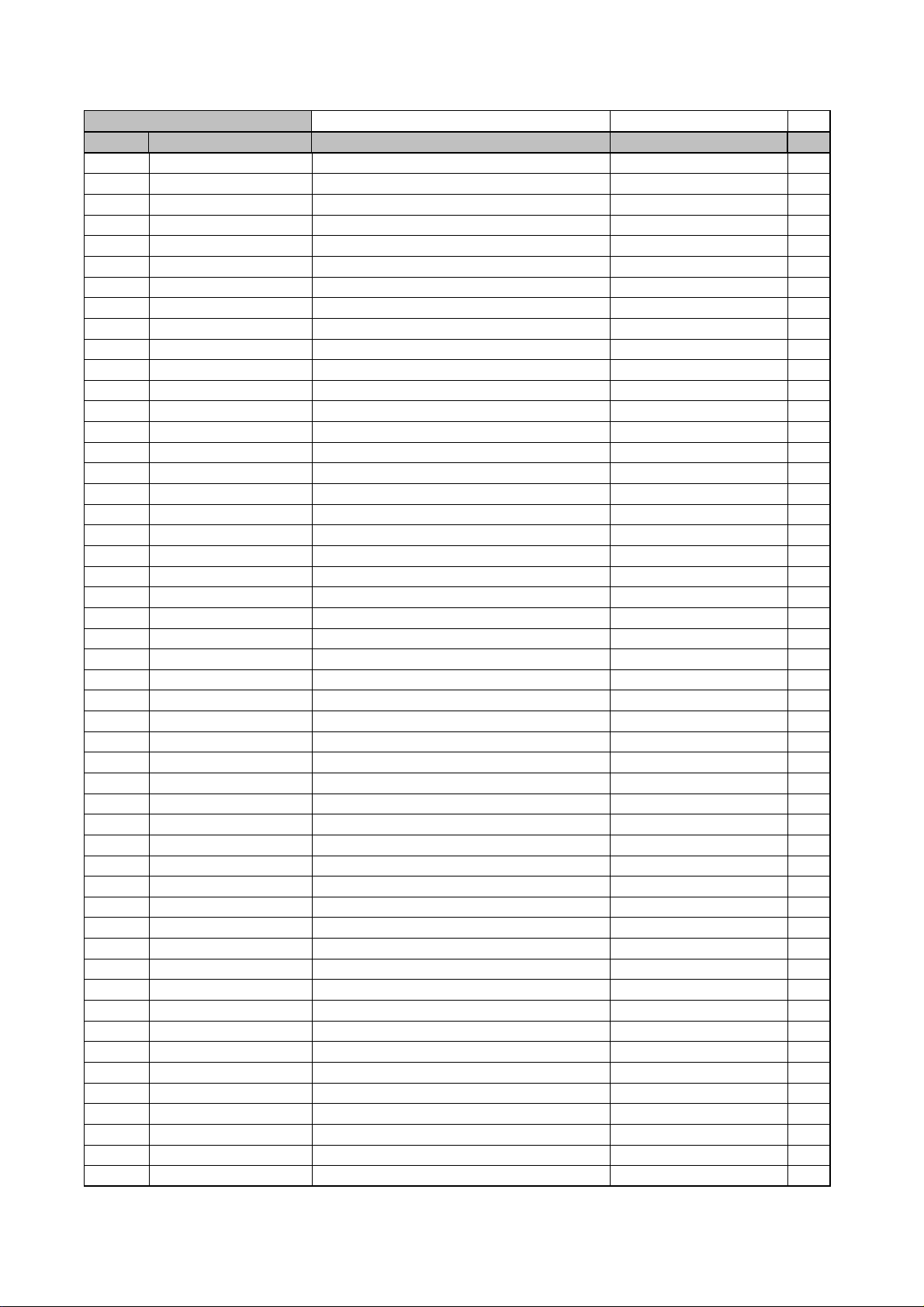

Page 13

BOTTOM CHASSIS ASS'Y

Y

harman/kardon

AVR 145/230 service manual

Page 13 of 135

Ref. # Part Number

CHE36-3 CLAMPER , WIRE CLAMPER 1

CHG1A104Z CUSHION , RUBBER CUSHION 1

CHG1A160Z CUSHION , RUBBER CUSHION 1

CHG1A360 CUSHION , FOOT CUSHION 4

CHS1A032 HEMELON TAPE TAPE 5

CJA2B043ZA CORD , POWER(EUR) QDR-7100CC 1

CKF4A319Z PANEL , REAR PANEL 1

CKL2A069H43 FOOT FOOT 4

CLZ9W003Z FERRITE , RING FERRITE RING 1

CMD1A487 BRACKET , TRANS BARCKET 1

CNVM9014MS171L MODULE , TUNER(EUR) TUNER 1

CQB1A173Y LABEL, FUSE CAUTION LABEL 1

CTB3+10GFZR SCREW Not stocked 20

CTB3+6FFZR SCREW Not stocked 3

CTB3+6JR SCREW Not stocked 13

CTB3+8JR SCREW Not stocked 7

CTW3+12JR SCREW Not stocked 2

CTW3+8JR SCREW Not stocked 8

CUA2A229 CHASSIS , BOTTOM CHASSIS 1

KHR1A028 BUSHING , AC CORD AC CORD 1

CB11 CWC1B2A13A100B CABLE , CARD CARD CABLE 1

CB12 CWC1C4A21B110B CABLE , CARD CARD CABLE 1

CB13 CWC1C4A13B080B CABLE , CARD CARD CABLE 1

CB14 CWC1B2A13A100B CABLE , CARD CARD CABLE 1

CB19 CWC1B2A09A240B CABLE , CARD CARD CABLE 1

CB42 CWC1B2A07A120B CABLE, CARD (1mm PITCH, A-B TY CARD CABLE 1

CB47 CWC1B2A07A060B CABLE , CARD CARD CABLE 1

F901 KBA2C4000TLEZ FUSE(233TPYE,4A,250V) LITTLE FUSE 1

T901 CLT5V045ZE TRANS , POWER MAIN MAIN TRANS 1

Description

Value Qty

FRONT PANEL ASS

Ref. # Part Number

CGWAVR145/230 FRONT PANEL ASS'Y ASS'Y 1

CBC1A158MBZG27 KNOB , MOMS KNOB 1

CBT1A1026MMZG27 KNOB , POWER KNOB 1

CBT1A1027K128 KNOB , DISPLAY KNOB 1

CBT1A1028MBYG27 KNOB , FUNCTION KNOB 1

CGL1A258Z INDICATOR , POWER INDICATOR 1

CGW1A427RDZH43 PANEL , FRONT PANEL 1

CHR301 CLAMPER CLAMPER 12

CMC1A302 PLATE , SHIELD PLATE 1

CMD2A443 BRACKET , SIDE BRACKET 2

CMH1A215 HOLDER , LED HOLDER 1

CMK2A010 BRACKET , PCB BRACKET 1

CMZ1A088 FILTER , FIP FIP 1

CMZ1A120 SHEET , REFLECTION SHEET 1

CTB3+10GR SCREW Not stocked 31

CTB3+16GFZR SCREW Not stocked 2

KGB1A158Z BADGE , HARMAN/KARDON(FRONT) BADGE 1

CB72 CWC1B2A17A230B WAFER, CARD CABLE (1mm PITCH, WAFER 1

Description

Value Qty

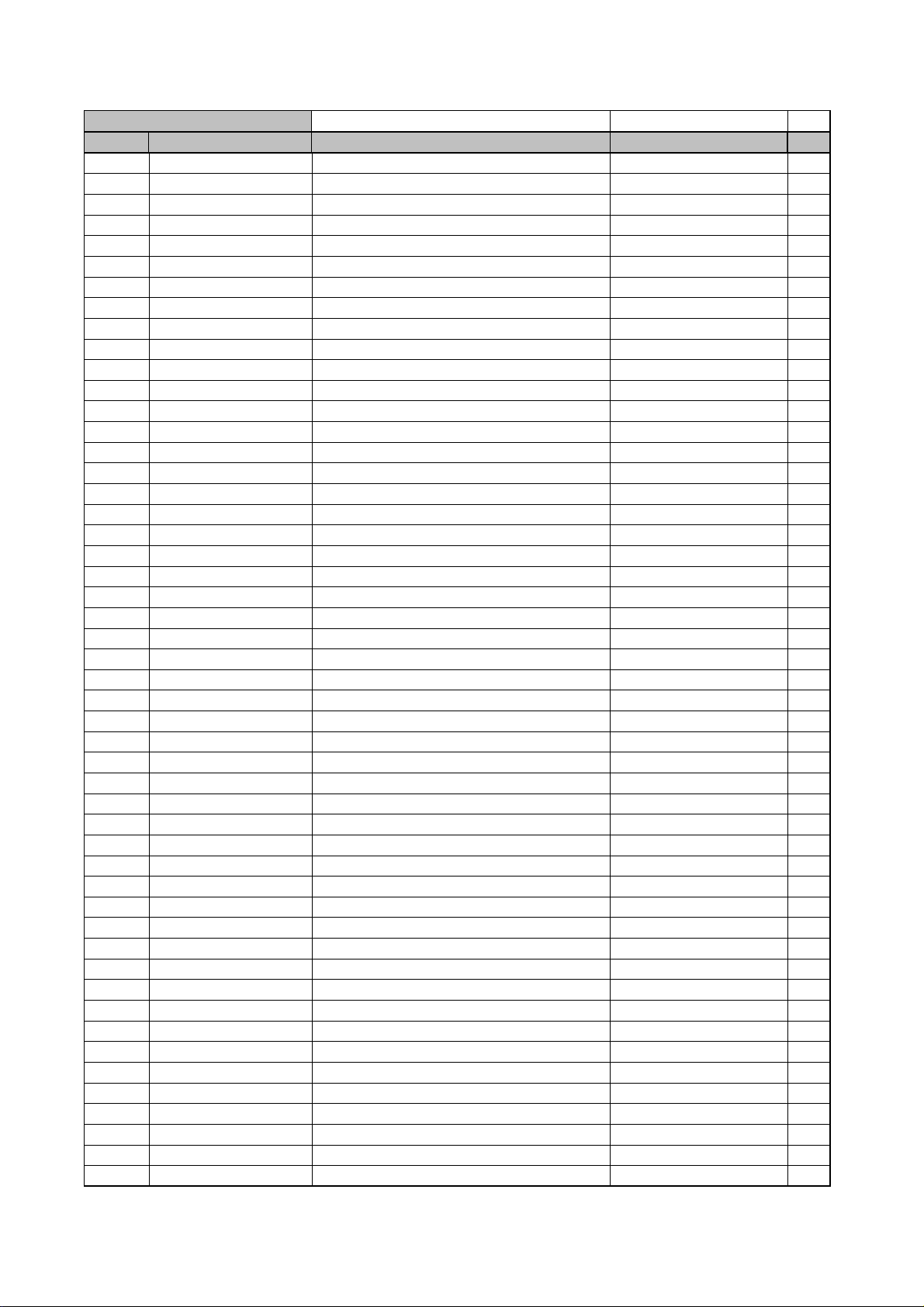

Page 14

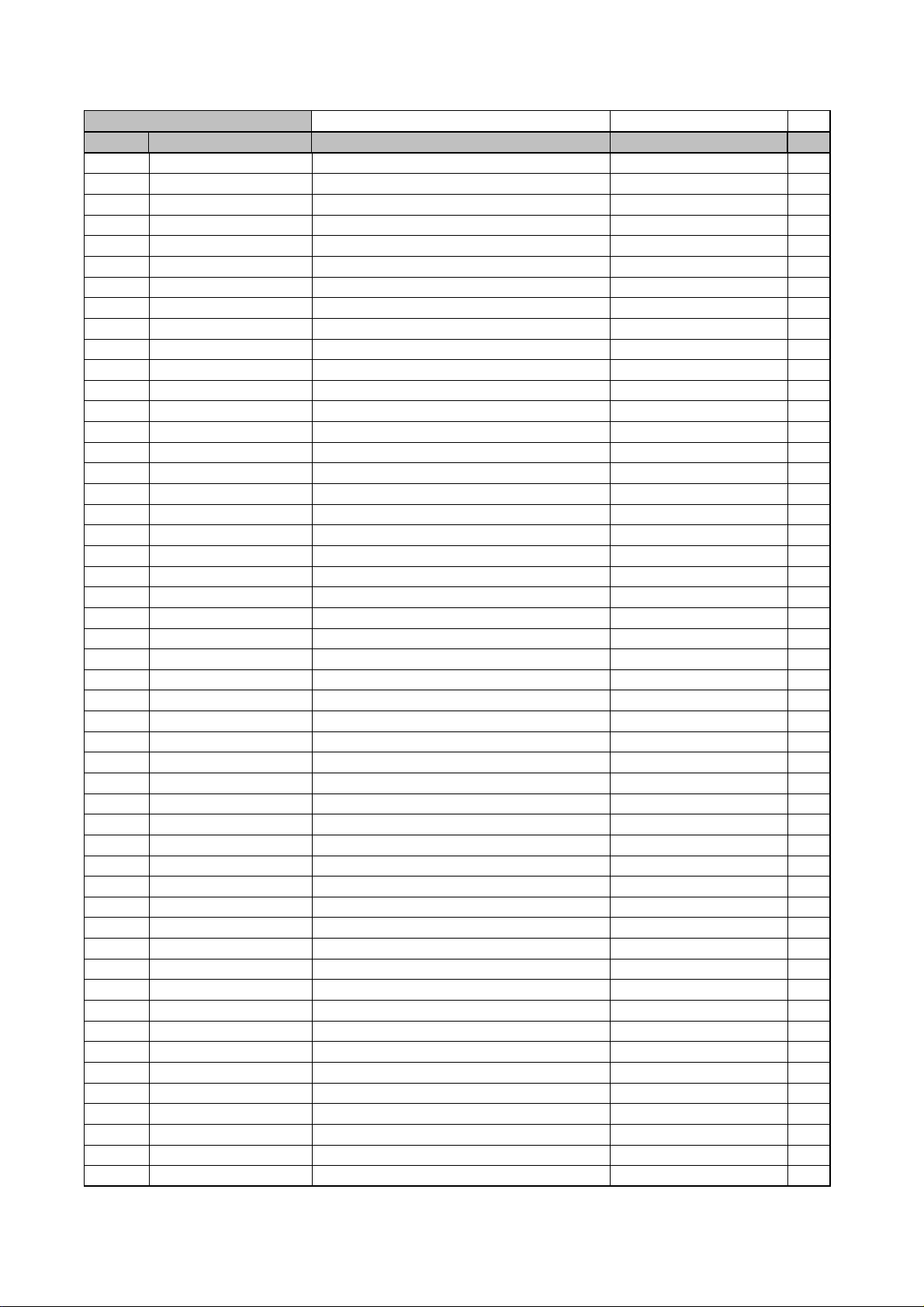

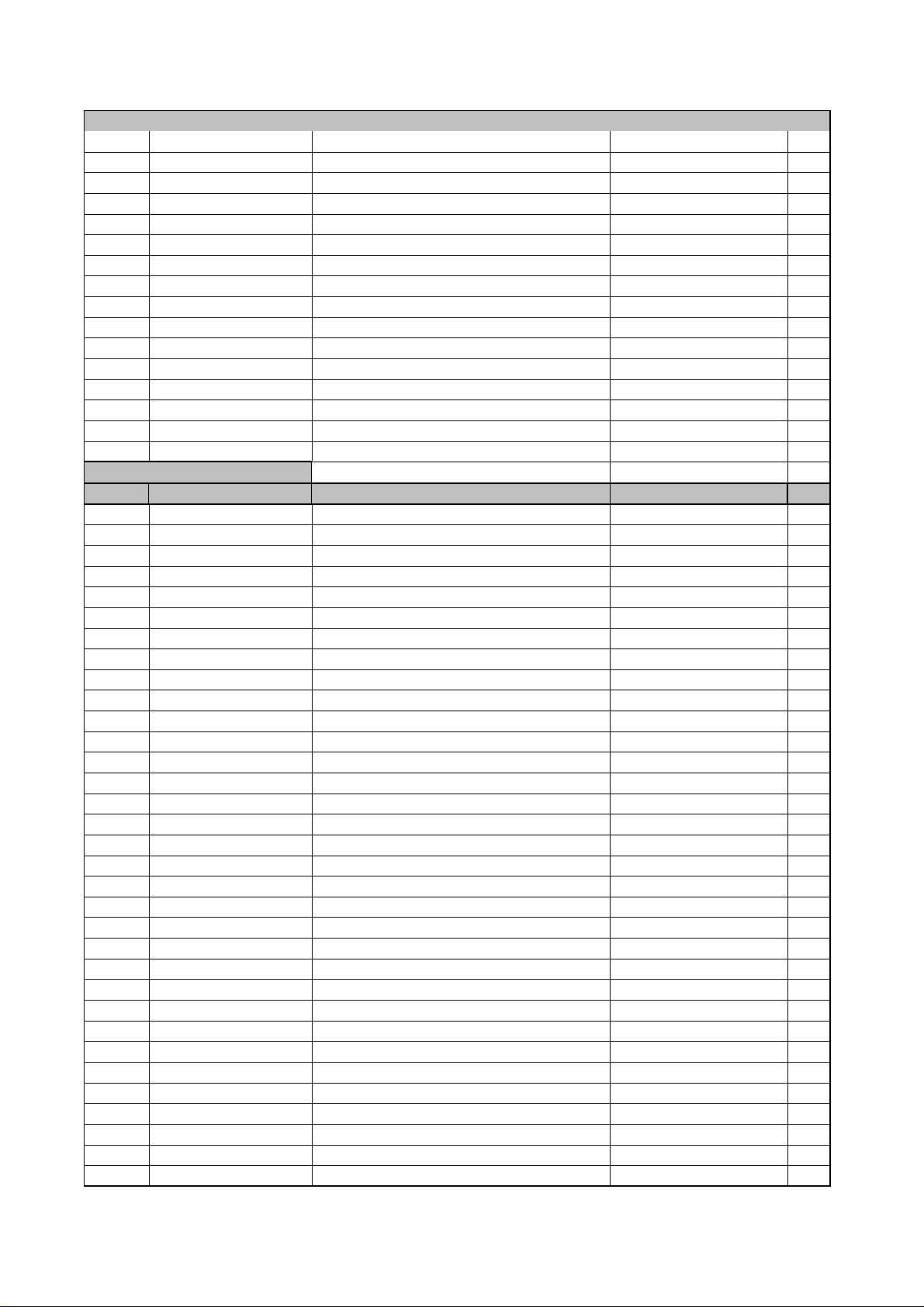

FRONT PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 14 of 135

Ref. # Part Number

COP11910E FRONT PCB ASS'Y(AVR145/230) ASS'Y 1

C714 HCBS1H151KBT CAP , CERAMIC 150UF 50V K 1

C716 CCEA1AH331T CAP , ELECT 330UF 10V 1

C719 HCBS1H102KBT CAP , CERAMIC 1000PF 50V K 1

C720 HCBS1H102KBT CAP , CERAMIC 1000PF 50V K 1

C721 HCBS1H102KBT CAP , CERAMIC 1000PF 50V K 1

C723 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C728 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C729 HCBS1H473ZFT CAP , CERAMIC 0.047UF 50V Z 1

C731 CCEA1HH100T CAP , ELECT 10UF 50V 1

C735 CCEA1CKS100T CAP , ELECT 10UF 16V 1

C742 HCBS1H223ZFT CAP , CERAMIC 0.02UF 50V Z 1

C793 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C794 HCBS1C222MXT CAP , CERAMIC 2200PF 16V 1

C795 HCBS1H102KBT CAP , CERAMIC 1000PF 50V K 1

C796 HCBS1H102KBT CAP , CERAMIC 1000PF 50V K 1

C805 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C806 HCBS1H223ZFT CAP , CERAMIC 0.022UF 50V Z 1

C807 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C808 HCBS1H181KBT CAP , CERAMIC 180PF 50V Z 1

C809 CCEA1AH471T CAP , ELECT 470UF 10V 1

C812 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C817 HCBS1H100JCT CAP , CERAMIC 10PF 50V 1

C841 CCEA1HH100T CAP , ELECT 10UF 50V 1

C842 CCEA1HH100T CAP , ELECT 10UF 50V 1

C843 CCEA1HH100T CAP , ELECT 10UF 50V 1

C850 HCBS1H471KBT CAP , CERAMIC 470PF 50V 1

C851 HCBS1H471KBT CAP , CERAMIC 470PF 50V 1

C852 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C855 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C856 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C857 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C862 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C863 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C866 CCEA1HKS100T CAP , ELECT 10UF 50V SMALL 1

C867 CCEA1HKS100T CAP , ELECT 10UF 50V SMALL 1

C868 CCEA1EKS470T CAP , ELECT 47UF 25V 1

C869 CCEA1EKS470T CAP , ELECT 47UF 25V 1

C870 HCBS1H681KBT CAP , CERAMIC 680PF 50V K 1

C871 HCBS1H681KBT CAP , CERAMIC 680PF 50V K 1

C872 CCEA1CH331T CAP , ELECT 330UF 16V 1

C873 CCEA1CH331T CAP , ELECT 330UF 16V 1

C874 HCBS1H101KBT CAP , CERAMIC 100PF 50V K 1

C882 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C889 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C891 HCBS1H223ZFT CAP , CERAMIC 0.023UF 50V Z 1

C892 HCBS1H223ZFT CAP , CERAMIC 0.023UF 50V Z 1

C893 HCBS1H223ZFT CAP , CERAMIC 0.023UF 50V Z 1

C894 CCEA1CKS100T CAP , ELECT 10UF 16V 1

Description

Value Qty

Page 15

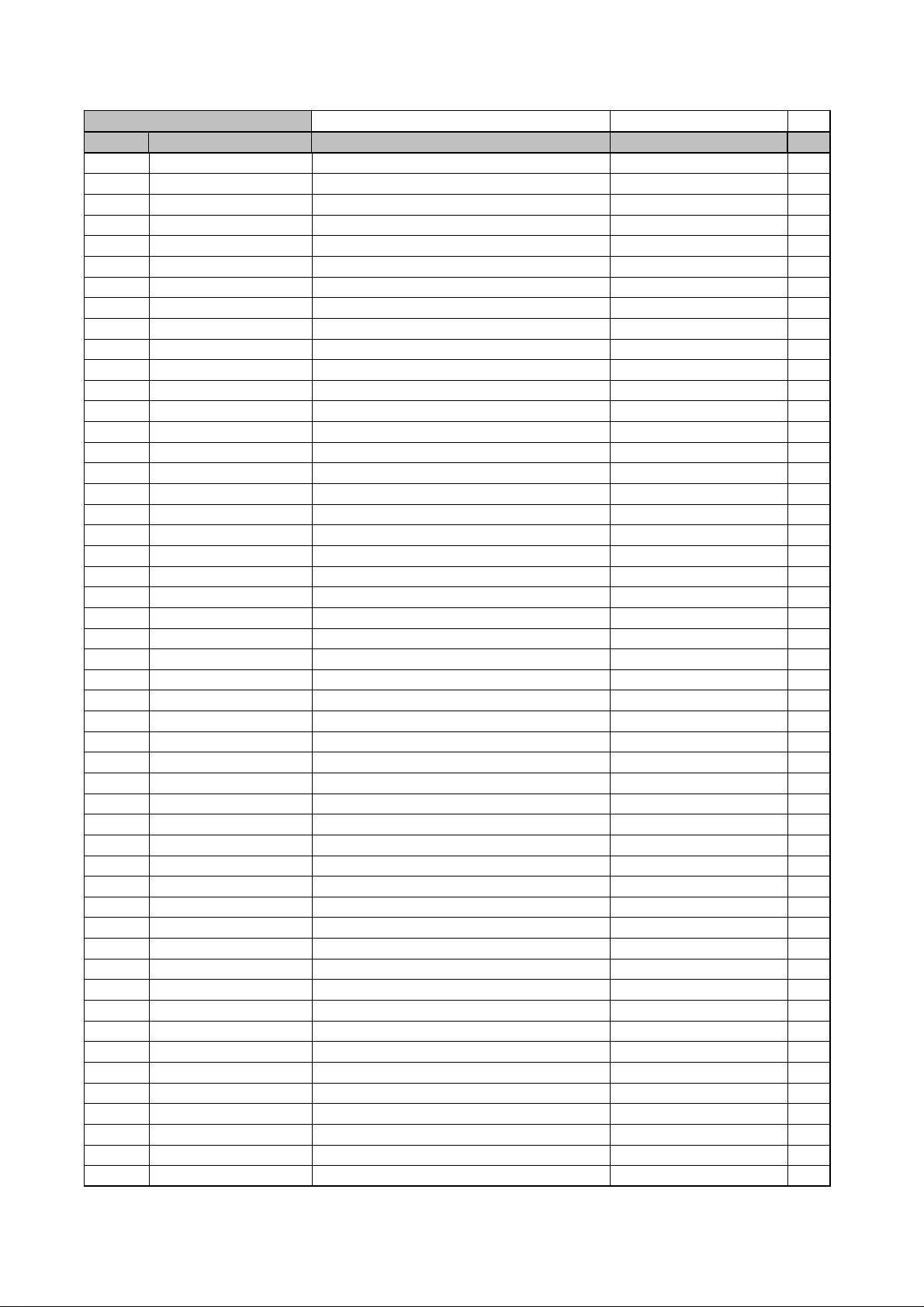

FRONT PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 15 of 135

Ref. # Part Number

C896 HCBS1H223ZFT CAP , CERAMIC 0.023UF 50V Z 1

C897 CCEA1AH471T CAP , ELECT 470UF 10V 1

C901 HCBS1H390JT CAP , CERAMIC 39PF 50V Z 1

C903 CCEA1HKS2R2T CAP , ELECT 2.2UF 50V SMALL SIZE 1

C905 CCEA1HKS2R2T CAP , ELECT 2.2UF 50V SMALL SIZE 1

C953 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C954 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

C957 HCBS1H104ZFT CAP , CERAMIC 0.1UF 50V Z 1

D730 CVD1SS133MT DIODE 1SS133 1

D774 CVD1SS133MT DIODE 1SS133 1

D778 HVD1N5819T DIODE , SCHOTTKY 1N5819 1

D784 CVD1SS133MT DIODE 1SS133 1

D785 CVD1SS133MT DIODE 1SS133 1

L702 HLQ02C100KT COIL , AXAIL 10uH 1

Q701 HVTKRC107MT T.R KRC107M 1

Q722 HVTKRA107MT T.R KRA107M 1

Q724 HVTKRC107MT T.R KRC107M 1

Q725 HVTKRC107MT T.R KRC107M 1

Q734 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q735 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q736 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q737 HVTKTC2874BT T.R , MUTE KTC2874B 1

Q738 HVTKRC107MT T.R KRC107M 1

Q739 HVTKTA1271YT T.R KTA1271Y 1

R701 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R704 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R705 CRD20TJ820T RES , CARBON 82 OHM 1/5W J 1

R706 CRD20TJ820T RES , CARBON 82 OHM 1/5W J 1

R708 CRD20TJ820T RES , CARBON 82 OHM 1/5W J 1

R709 CRD20TJ470T RES , CARBON 47 OHM 1/5W J 1

R710 CRD20TJ470T RES , CARBON 47 OHM 1/5W J 1

R711 CRD20TJ470T RES , CARBON 47 OHM 1/5W J 1

R718 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R737 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R747 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R753 CRD20TF1001T RES , CARBON 1K 1/5W F 1

R754 CRD20TF1501T RES , CARBON 1.5K 1/5W F 1

R755 CRD20TF1801T RES , CARBON 1.8K 1/5W F 1

R756 CRD20TF2701T RES , CARBON 2.7K 1/5W F 1

R757 CRD20TF3301T RES , CARBON 3.3K 1/5W F 1

R758 CRD20TF5601T RES , CARBON 5.6K 1/5W F 1

R759 CRD20TF1001T RES , CARBON 1K 1/5W F 1

R760 CRD20TF1501T RES , CARBON 1.5K 1/5W F 1

R761 CRD20TF1801T RES , CARBON 1.8K 1/5W F 1

R762 CRD20TF2701T RES , CARBON 2.7K 1/5W F 1

R763 CRD20TF3301T RES , CARBON 3.3K 1/5WF 1

R764 CRD20TF5601T RES , CARBON 5.6K 1/5W F 1

R765 CRD20TF7501T RES , CARBON 7.5K 1/5W F 1

R766 CRD20TF1001T RES , CARBON 1K 1/5W F 1

R767 CRD20TF1501T RES , CARBON 1.5K 1/5W F 1

Description

Value Qty

Page 16

FRONT PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 16 of 135

Ref. # Part Number

R768 CRD20TF1801T RES , CARBON 1.8K 1/5W F 1

R769 CRD20TF2701T RES , CARBON 2.7K 1/5W F 1

R781 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R783 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R784 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R786 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R787 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R791 CRD20TJ822T RES , CARBON 8.2K OHM 1/5W J 1

R805 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R806 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R824 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R825 CRD20TJ681T RES , CARBON 680 OHM 1/5W J 1

R828 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R829 CRD20TJ681T RES , CARBON 680 OHM 1/5W J 1

R864 CRD20TJ272T RES , CARBON 2.7K OHM 1/5W J 1

R865 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R866 CRD20TJ272T RES , CARBON 2.7K OHM 1/5W J 1

R869 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R871 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R872 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R873 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R874 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R875 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R876 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R877 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R878 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R892 CRD20TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R893 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R895 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R896 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R897 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R898 CRD20TJ101T RES , CARBON 100 OHM 1/5W J 1

R899 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R900 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R901 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R902 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R903 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R904 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R905 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R906 CRD20TJ104T RES , CARBON 100K OHM 1/5W J 1

R907 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R908 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R909 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R910 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R911 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R912 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R913 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R915 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R918 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R919 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

Description

Value Qty

Page 17

FRONT PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 17 of 135

Ref. # Part Number

R956 CRD20TJ1R0T RES , CARBON 1 OHM 1/5W J 1

S701 HST1A020ZT SW , TACT 1A020 1

S702 HST1A020ZT SW , TACT 1A020 1

S703 HST1A020ZT SW , TACT 1A020 1

S704 HST1A020ZT SW , TACT 1A020 1

S705 HST1A020ZT SW , TACT 1A020 1

S706 HST1A020ZT SW , TACT 1A020 1

S707 HST1A020ZT SW , TACT 1A020 1

S708 HST1A020ZT SW , TACT 1A020 1

S709 HST1A020ZT SW , TACT 1A020 1

S710 HST1A020ZT SW , TACT 1A020 1

S711 HST1A020ZT SW , TACT 1A020 1

S712 HST1A020ZT SW , TACT 1A020 1

S713 HST1A020ZT SW , TACT 1A020 1

S714 HST1A020ZT SW , TACT 1A020 1

S715 HST1A020ZT SW , TACT 1A020 1

S716 HST1A020ZT SW , TACT 1A020 1

S717 HST1A020ZT SW , TACT 1A020 1

S718 HST1A020ZT SW , TACT 1A020 1

S719 HST1A020ZT SW , TACT 1A020 1

S720 HST1A020ZT SW , TACT 1A020 1

CMC3A111 PLATE , EARTH PLATE 1

BK71 CMD1A209 BRACKET , FLT BRACKET 1

BK72 CMD1A209 BRACKET , FLT BRACKET 1

BK73 CMD1A209 BRACKET , FLT BRACKET 1

BN10 CWZAVR230BN10 WIRE ASS'Y (SHIELD) WIRE 1

BN18 CWZAVR125BN18 WIRE ASS'Y (SHIELD) WIRE 1

BN22 CWZAVR145BN22 WIRE ASS'Y (SHIELD) WIRE 1

BN41 CWZAVR130BN41 WIRE ASS'Y (SHIELD) WIRE 1

BN81 CWB2C908200BM WIRE ASS'Y WIRE 1

BN84 CWB2B905080EN WIRE ASS'Y WIRE 1

BN85 CWB2B902100EW WIRE ASS'Y ( ANGLE ) WIRE 1

BN88 CWB2B904100EN WIRE ASS'Y WIRE 1

BN89 CWB2B904100EN WIRE ASS'Y WIRE 1

CN47 CJP07GA117ZY TEMP ITEM WAFER 1

CN72 CJP17GA193ZY WAFER, CARD CABLE (SMD) WAFER 1

CN84 CJP05GB46ZY WAFER WAFER 1

CN85 CJP02GA19ZY WAFER, 2PIN WAFER 1

CN86 CJP02GA89ZM WAFER WAFER 1

CN88 CJP04GB46ZY WAFER WAFER 1

CN89 CJP04GB46ZY WAFER WAFER 1

D701 CVD52CSBBCEAB2 BLUE L.E.D L.E.D 1

D703 CVD52CSBBCEAB2 BLUE L.E.D L.E.D 1

D705 CVD52CSBBCEAB2 BLUE L.E.D L.E.D 1

D723 CVD50BOBBWGA L.E.D , 2 COLOR (ORG , BLUE) L.E.D 1

D727 CVD50BOBBWGA L.E.D , 2 COLOR (ORG , BLUE) L.E.D 1

ET03 CMD1A569 BRACKET , PCB BRACKET 1

FIP1 HFLHCA18ML03 F.I.P FIP 1

IC73 HRVNJL34H380A SENSOR , REMOTE JRC 1

IC75 HVI74ACT04MTR I.C , HEX INVERTER FAIRCHILD 1

Description

Value Qty

Page 18

FRONT PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 18 of 135

Ref. # Part Number

IC76 HVI74HCU04AFNG I.C , INVERTER TOSHIBA 1

IC86 HVINJM4556AL I.C , HEADPHONE JRC 1

IC97 HVIST202EBW IC , RS232C TRANSCEIVER ST 1

JK81 CJJ4M043Y JACK , BOARD BOARD JACK 1

JK82 HJSTORX177L MODULE , OPTICAL(RX) OPT JACK(RX) 1

JK83 CJJ2E026Z JACK , HEADPHONE(SILVER PLATE) JACK 1

JK85 CJJ9M003Z JACK , S-VIDEO JACK 1

JK86 CJJ4S023Y JACK , BOARD JACK 1

JK97 CJJ9W001Z 9P D-SUB FEMALE(RS-232C) SEMCO JACK 1

JW82 CWE8202300RV WIRE ASS'Y WIRE 1

JW83 CWE8202150RV WIRE ASS'Y WIRE 1

JW84 CWE8202110RV WIRE ASS'Y WIRE 1

SW1 CSH1A008ZV SW , PUSH (MOMS) MOMS SWITCH 1

SW95 KST1A010Z SW , TACT SWITCH 1

SW98 HSH2B018Z SW , PUSH SWITCH 1

VR74 CSR2A037Z ENCODER ENCODER 1

Description

Value Qty

MAIN PCB ASSY

Ref. # Part Number

COP11911E MAIN PCB ASS'Y(AVR145/230) ASS'Y 1

CHD3A012R SCREW , SPECIAL Not stocked 3

CHS1A032 HEMELON TAPE TAPE 1

C501 CCEA1HH100T CAP , ELECT 10UF 50V 1

C502 CCEA1HH100T CAP , ELECT 10UF 50V 1

C503 CCEA1HH100T CAP , ELECT 10UF 50V 1

C504 CCEA1HH100T CAP , ELECT 10UF 50V 1

C505 CCEA1HH100T CAP , ELECT 10UF 50V 1

C506 CCKT1H331KB CAP , CERAMIC 330PF 50V 1

C507 HCBS1H331KBT CAP , CERAMIC 330PF 50V 1

C508 HCBS1H331KBT CAP , CERAMIC 330PF 50V 1

C509 CCKT1H331KB CAP , CERAMIC 330PF 50V 1

C510 HCBS1H331KBT CAP , CERAMIC 330PF 50V 1

C561 CCEA1CH101T CAP , ELECT 100UF 16V 1

C562 CCEA1CH101T CAP , ELECT 100UF 16V 1

C563 CCEA1CH101T CAP , ELECT 100UF 16V 1

C564 CCEA1CH101T CAP , ELECT 100UF 16V 1

C565 CCEA1CH101T CAP , ELECT 100UF 16V 1

C566 CCEA1CH101T CAP , ELECT 100UF 16V 1

C567 CCEA1CH101T CAP , ELECT 100UF 16V 1

C568 CCEA1CH101T CAP , ELECT 100UF 16V 1

C569 CCEA1CH101T CAP , ELECT 100UF 16V 1

C570 CCEA1CH101T CAP , ELECT 100UF 16V 1

C571 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C572 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C573 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C574 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C575 HCBS1H681KBT CAP , CERAMIC 680PF 50V 1

C601 CCCT1H120JC CAP , CERAMIC 12PF 50V 1

C602 CCCT1H120JC CAP , CERAMIC 12PF 50V 1

Description

Value Qty

Page 19

MAIN PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 19 of 135

Ref. # Part Number

C603 CCCT1H120JC CAP , CERAMIC 12PF 50V 1

C604 CCCT1H120JC CAP , CERAMIC 12PF 50V 1

C605 CCCT1H120JC CAP , CERAMIC 12PF 50V 1

C606 CCCT1H330JC CAP , CERAMIC 33PF 50V 1

C607 CCCT1H330JC CAP , CERAMIC 33PF 50V 1

C608 CCCT1H330JC CAP , CERAMIC 33PF 50V 1

C609 CCCT1H330JC CAP , CERAMIC 33PF 50V 1

C610 CCCT1H330JC CAP , CERAMIC 33PF 50V 1

C681 CCEA1HH100T CAP , ELECT 10UF 50V 1

C682 CCEA1HH100T CAP , ELECT 10UF 50V 1

C683 CCEA1HH100T CAP , ELECT 10UF 50V 1

C684 CCEA1HH100T CAP , ELECT 10UF 50V 1

C685 CCEA1HH100T CAP , ELECT 10UF 50V 1

C726 CCKT1H221KB CAP , CERAMIC 220PF 50V 1

C900 HCQI1H473JZT CAP , MYLAR 0.047UF 50V 1

C901 HCQI1H473JZT CAP , MYLAR 0.047UF 50V 1

C905 CCFT1H223ZF CAP , CERAMIC 0.022UP 50V 1

C907 CCEA1CH101T CAP , ELECT 100UF 16V 1

C908 CCFT1H223ZF CAP , CERAMIC 0.022UP 50V 1

C910 HCQI1H473JZT CAP , MYLAR 0.047UF 50V 1

C911 CCEA1CH471T CAP , ELECT 470UF 16V 1

C912 CCEA1CH221T CAP , ELECT 220UF 16V 1

C913 CCFT1H104ZF CAP , SEMICONDUCTOR 0.1UF 50V ZF 1

C914 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C917 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C924 CCFT1H104ZF CAP , SEMICONDUCTOR 0.1UF 50V ZF 1

C939 CCEA1HH4R7T CAP , ELECT 4.7UF 50V 1

C940 CCEA1AH471T CAP , ELECT 470UF 10V 1

C948 CCFT1H104ZF CAP , SEMICONDUCTOR 0.1UF 50V ZF 1

C949 CCEA1HH220T CAP , ELECT 22UF 50V 1

C971 HCQI1H562JZT CAP , MYLAR 5600PF 50V 1

C972 HCQI1H562JZT CAP , MYLAR 5600PF 50V 1

C973 HCQI1H562JZT CAP , MYLAR 5600PF 50V 1

C980 HCQI1H562JZT CAP , MYLAR 5600PF 50V 1

C981 HCQI1H562JZT CAP , MYLAR 5600PF 50V 1

C990 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C991 CCEA1HH1R0T CAP , ELECT 1UF 50V 1

C992 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C993 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C995 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C997 HCQI1H473JZT CAP , MYLAR 0.047UF 50V J 1

C999 CCFT1H223ZF CAP , CERAMIC 0.022UP 50V 1

D501 CVD1SS133MT DIODE 1SS133 1

D502 CVD1SS133MT DIODE 1SS133 1

D503 CVD1SS133MT DIODE 1SS133 1

D504 CVD1SS133MT DIODE 1SS133 1

D505 CVD1SS133MT DIODE 1SS133 1

D581 CVD1SS133MT DIODE 1SS133 1

D582 CVD1SS133MT DIODE 1SS133 1

D583 CVD1SS133MT DIODE 1SS133 1

Description

Value Qty

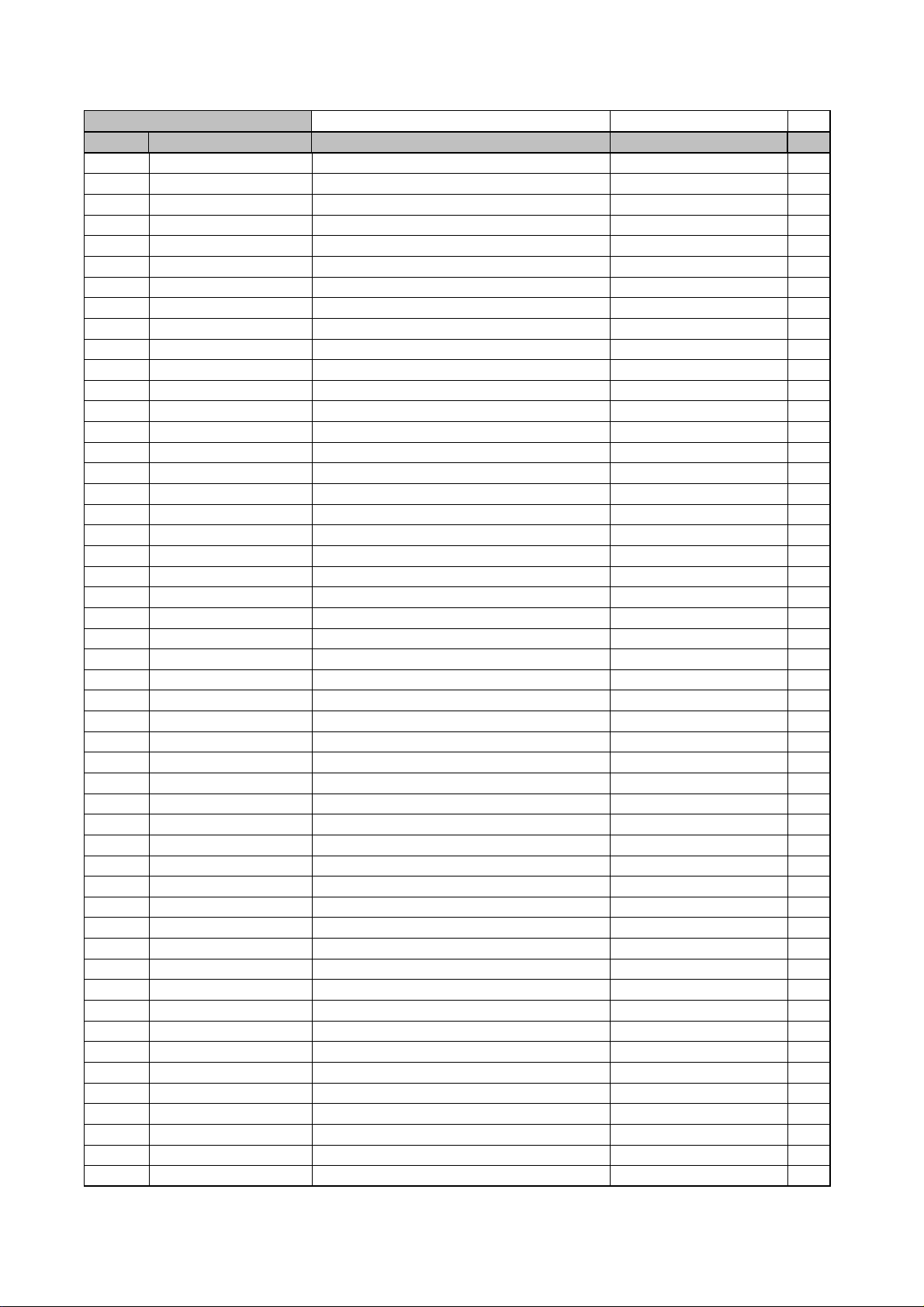

Page 20

MAIN PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 20 of 135

Ref. # Part Number

D584 CVD1SS133MT DIODE 1SS133 1

D585 CVD1SS133MT DIODE 1SS133 1

D901 CVD1N4003SRT RECT , DIODE 1N4003 1

D902 CVD1SS133MT DIODE 1SS133 1

D911 CVD1SS133MT DIODE 1SS133 1

D912 CVD1SS133MT DIODE 1SS133 1

D914 CVD1SS133MT DIODE 1SS133 1

D917 CVD1SS133MT DIODE 1SS133 1

D953 CVD1SS133MT DIODE 1SS133 1

D954 CVD1N4003SRT RECT , DIODE 1N4003 1

D955 CVD1N4003SRT RECT , DIODE 1N4003 1

D956 CVD1N4003SRT RECT , DIODE 1N4003 1

D957 CVD1N4003SRT RECT , DIODE 1N4003 1

D961 CVD1N4003ST RECT , DIODE 1N4003 1

D962 CVD1N4003SRT RECT , DIODE 1N4003 1

D963 CVD1N4003ST RECT , DIODE 1N4003 1

D973 CVD1SS133MT DIODE 1SS133 1

D974 CVD1SS133MT DIODE 1SS133 1

D979 HVDMTZJ6.2BT DIODE , ZENER MTZJ6.2B 1

D980 CVD1SS133MT DIODE 1SS133 1

ET90 HJT1A025 PALTE , EARTH MET37-0002 1

ET91 HJT1A025 PALTE , EARTH MET37-0002 1

F901 KJCFC5S HOLDER , FUSE FUSE HOLDER 2

F902 KBA2D2500TLET FUSE(SR-5, 2.5A, 250V) SAVE FUSETECH 1

Q501 HVTKTA1268GRT T.R KTA1268GR 1

Q502 HVTKTA1268GRT T.R KTA1268GR 1

Q503 HVTKTA1268GRT T.R KTA1268GR 1

Q504 HVTKTA1268GRT T.R KTA1268GR 1

Q505 HVTKTA1268GRT T.R KTA1268GR 1

Q511 HVTKTC3200GRT T.R KTC3200GR 1

Q512 HVTKTC3200GRT T.R KTC3200GR 1

Q513 HVTKTC3200GRT T.R KTC3200GR 1

Q514 HVTKTC3200GRT T.R KTC3200GR 1

Q515 HVTKTC3200GRT T.R KTC3200GR 1

Q516 HVTKTC3200GRT T.R KTC3200GR 1

Q517 HVTKTC3200GRT T.R KTC3200GR 1

Q518 HVTKTC3200GRT T.R KTC3200GR 1

Q519 HVTKTC3200GRT T.R KTC3200GR 1

Q520 HVTKTC3200GRT T.R KTC3200GR 1

Q541 HVTKTC3198YT T.R KTC3198Y 1

Q542 HVTKTC3198YT T.R KTC3198Y 1

Q543 HVTKTC3198YT T.R KTC3198Y 1

Q544 HVTKTC3198YT T.R KTC3198Y 1

Q545 HVTKTC3198YT T.R KTC3198Y 1

Q556 HVTKTC3200GRT T.R KTC3200GR 1

Q557 HVTKTC3200GRT T.R KTC3200GR 1

Q558 HVTKTC3200GRT T.R KTC3200GR 1

Q559 HVTKTC3200GRT T.R KTC3200GR 1

Q560 HVTKTC3200GRT T.R KTC3200GR 1

Q561 HVTKTC3200GRT T.R KTC3200GR 1

Description

Value Qty

Page 21

MAIN PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 21 of 135

Ref. # Part Number

Q562 HVTKTC3200GRT T.R KTC3200GR 1

Q563 HVTKTC3200GRT T.R KTC3200GR 1

Q564 HVTKTC3200GRT T.R KTC3200GR 1

Q565 HVTKTC3200GRT T.R KTC3200GR 1

Q601 HVTKTA1268GRT T.R KTA1268GR 1

Q602 HVTKTA1268GRT T.R KTA1268GR 1

Q603 HVTKTA1268GRT T.R KTA1268GR 1

Q604 HVTKTA1268GRT T.R KTA1268GR 1

Q605 HVTKTA1268GRT T.R KTA1268GR 1

Q681 HVTKSC2785YT T.R KSC2785Y 1

Q682 HVTKSC2785YT T.R KSC2785Y 1

Q683 HVTKSC2785YT T.R KSC2785Y 1

Q684 HVTKSC2785YT T.R KSC2785Y 1

Q685 HVTKSC2785YT T.R KSC2785Y 1

Q901 HVTKSC2785YT T.R KSC2785Y 1

Q938 HVTKRA107MT T.R KRA107M 1

Q939 HVTKRA107MT T.R KRA107M 1

Q942 HVTKSC2785YT T.R KSC2785Y 1

Q943 HVTKSC2785YT T.R KSC2785Y 1

Q951 HVTKRC107MT T.R KRC107M 1

Q952 HVTKRA107MT T.R KRA107M 1

Q960 HVTKRC107MT T.R KRC107M 1

Q961 HVTKTA1024YT T.R KTA1024YT 1

Q991 HVTKRC107MT T.R KRC107M 1

Q992 HVTKRA107MT T.R KRA107M 1

R501 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R502 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R503 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R504 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R505 CRD20TJ433T RES , CARBON 43K OHM 1/5W J 1

R506 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R507 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R508 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R509 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R510 CRD20TJ333T RES , CARBON 33K OHM 1/5W J 1

R511 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R512 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R513 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R514 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R515 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R516 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R517 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R518 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R519 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R520 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R521 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R522 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R523 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R524 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

R525 CRD20TJ471T RES , CARBON 470 OHM 1/5W J 1

Description

Value Qty

Page 22

MAIN PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 22 of 135

Ref. # Part Number

R531 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R532 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R533 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R534 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R535 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R536 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R537 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R538 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R539 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R540 CRD20TJ221T RES , CARBON 220 OHM 1/5W J 1

R541 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R542 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R543 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R544 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R545 CRD20TJ271T RES , CARBON 270 OHM 1/5W J 1

R556 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R557 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R558 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R559 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R560 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R561 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R562 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R563 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R564 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R565 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R566 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R567 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R568 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R569 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R570 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R571 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R572 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R573 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R574 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R575 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R576 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R577 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R578 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R579 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R580 CRD20TJ100T RES , CARBON 10 OHM 1/5W J 1

R581 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R582 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R583 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R584 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R585 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R586 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R587 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R588 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R589 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R590 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

Description

Value Qty

Page 23

MAIN PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 23 of 135

Ref. # Part Number

R591 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R592 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R593 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R594 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R595 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R596 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R597 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R598 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R599 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R600 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R601 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R602 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R603 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R604 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R605 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R606 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R607 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R608 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R609 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R610 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R631 CRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R632 CRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R633 CRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R634 CRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R635 CRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R636 CRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R637 CRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R638 CRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R639 CRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R640 CRD25FJ180T RES , CARBON 18 OHM 1/4W J 1

R646 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R647 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R648 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R649 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R650 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R651 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R652 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R653 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R654 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R655 CRD25FJ3R3T RES , CARBON 3.3 OHM 1/4W J 1

R666 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R667 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R668 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R669 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R670 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R671 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R672 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R673 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R674 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

R675 CRD20TJ911T RES , CARBON 910 OHM 1/5W J 1

Description

Value Qty

Page 24

MAIN PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 24 of 135

Ref. # Part Number

R676 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R677 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R678 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R679 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R680 CRD20TJ182T RES , CARBON 1.8K OHM 1/5W J 1

R681 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R682 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R683 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R684 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R685 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R686 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R687 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R688 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R689 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R690 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R696 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R697 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R698 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R699 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R700 CRD25TJ470T RES , CARBON 47 OHM 1/4W J 1

R771 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R772 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R773 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R774 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R775 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R781 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R782 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R783 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R784 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R785 CRD20TJ750T RES , CARBON 75 OHM 1/5W J 1

R900 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R901 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R902 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R903 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R906 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R907 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R910 CRD20TJ105T RES , CARBON 1M OHM 1/5W J 1

R911 CRD25TJ680T RES , CARBON 68 OHM 1/4W J 1

R912 CRD20TJ332T RES , CARBON 3.3K OHM 1/5W J 1

R917 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R918 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R919 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R920 CRD25TJ393T RES , CARBON 39K OHM 1/4W J 1

R932 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

R939 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R940 CRD20TJ152T RES , CARBON 1.5K OHM 1/5W J 1

R941 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R942 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R944 CRD25TJ223T RES , CARBON 22K OHM 1/4W J 1

R946 CRD25TJ223T RES , CARBON 22K OHM 1/4W J 1

Description

Value Qty

Page 25

MAIN PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 25 of 135

Ref. # Part Number

R947 CRD20TJ223T RES , CARBON 22K OHM 1/5W J 1

R948 CRD25TJ222T RES , CARBON 2.2K OHM 1/5W J 1

R949 CRD20TJ822T RES , CARBON 8.2K OHM 1/5W J 1

R955 CRD20TJ203T RES , CARBON 20K OHM 1/5W J 1

R956 CRD20TJ394T RES , CARBON 390K OHM 1/5W J 1

R957 CRD20TJ153T RES , CARBON 15K OHM 1/5W J 1

R960 CRD20TJ332T RES , CARBON 3.3K OHM 1/5W J 1

R961 CRD20TJ331T RES , CARBON 330 OHM 1/5W J 1

R962 CRD20TJ273T RES , CARBON 27K OHM 1/5W J 1

R963 CRD20TJ105T RES , CARBON 1M OHM 1/5W J 1

R966 CRD20TJ472T RES , CARBON 4.7K OHM 1/5W J 1

R980 CRD20TJ473T RES , CARBON 47K OHM 1/5W J 1

R986 CRD20TJ102T RES , CARBON 1K OHM 1/5W J 1

R987 CRD20TJ561T RES , CARBON 560 OHM 1/5W J 1

R988 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R989 CRD20TJ302T RES , CARBON 3K OHM 1/5W J 1

R991 CRD20TJ822T RES , CARBON 8.2K OHM 1/5W J 1

R992 CRD20TJ562T RES , CARBON 5.6K OHM 1/5W J 1

R998 CRD20TJ103T RES , CARBON 10K OHM 1/5W J 1

CTW3+8JR SCREW Not stocked 2

BN19 CWB3FE03250UP WIRE ASS'Y WIRE 1

BN20 CWB3FC04280UP WIRE ASS'Y WIRE 1

BN82 CWB1C902050EN WIRE ASS'Y WIRE 1

BN83 CWB1C902050EN WIRE ASS'Y WIRE 1

BN84 CWB1C902050EN WIRE ASS'Y WIRE 1

BN85 CWB1C902050EN WIRE ASS'Y WIRE 1

BN86 CWB1C902050EN WIRE ASS'Y WIRE 1

BN89 CWB1C902250BM WIRE ASS'Y WIRE 1

BN90 CWB4F232550PU WIRE ASS'Y WIRE 1

BN98 HJP08GA130ZK WAFER WAFER 1

CN11 CJP13GA117ZY WAFER , CARD CABLE WAFER 1

CN12 CJP21GA115ZY WAFER , CARD CABLE WAFER 1

CN61 CJP02GA01ZY WAFER, STRAIGHT, 2PIN WAFER 1

CN62 CJP02GA01ZY WAFER, STRAIGHT, 2PIN WAFER 1

CN63 CJP02GA01ZY WAFER, STRAIGHT, 2PIN WAFER 1

CN64 CJP02GA01ZY WAFER, STRAIGHT, 2PIN WAFER 1

CN65 CJP02GA01ZY WAFER, STRAIGHT, 2PIN WAFER 1

CN91 CJP02GA89ZY WAFER WAFER 1

CN92 KJP02KA060ZY WAFER WAFER 1

C631 CCEA1JH101E CAP , ELECT 100UF 63V 1

C632 CCEA1JH101E CAP , ELECT 100UF 63V 1

C633 CCEA1JH101E CAP , ELECT 100UF 63V 1

C634 CCEA1JH101E CAP , ELECT 100UF 63V 1

C635 CCEA1JH101E CAP , ELECT 100UF 63V 1

C636 CCEA1JH101E CAP , ELECT 100UF 63V 1

C637 CCEA1JH101E CAP , ELECT 100UF 63V 1

C638 CCEA1JH101E CAP , ELECT 100UF 63V 1

C639 CCEA1JH101E CAP , ELECT 100UF 63V 1

C640 CCEA1JH101E CAP , ELECT 100UF 63V 1

C902 CCET50VKL4682NK CAP , ELECT 6800UF/50V 1

Description

Value Qty

Page 26

MAIN PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 26 of 135

Ref. # Part Number

C904 KCKDKS472ME CAP , CERAMIC(X1/Y2/SC) 0.0047UF/2.5KV 1

C906 CCEA1EH102E CAP , ELECT 1000UF 25V 1

C909 CCET50VKL4682NK CAP , ELECT 6800UF/50V 1

C915 CCET50VKL4682NK CAP , ELECT 6800UF/50V 1

C916 CCET50VKL4682NK CAP , ELECT 6800UF/50V 1

ET01 CMD1A387 BRACKET , PCB BRACKET 1

IC94 HVIMC7805C I.C, REGULATOR FAIRCHILD 1

IC97 HVIS-80842CNY-X I.C RESET SEIKO 1

JK90 CJJ4M040Z JACK , BOARD (SW) JACK 1

JK91 CJJ5R006Z TERMINAL , SPEAKER TERMINAL 1

JK92 CJJ5P020Z TERMINAL , SPEAKER TERMINAL 1

JW90 CWE8212120VV WIRE , RED WIRE 1

JW91 CWE8212180VV WIRE ASS'Y WIRE 1

JW92 CWEE212080VV WIRE ASS'Y WIRE 1

JW93 CWEP202110VV WIRE WIRE 1

L501 CLEY0R5KAK COIL , SPEAKER 0.5UH 1

L502 CLEY0R5KAK COIL , SPEAKER 0.5UH 1

L503 CLEY0R5KAK COIL , SPEAKER 0.5UH 1

L504 CLEY0R5KAK COIL , SPEAKER 0.5UH 1

L505 CLEY0R5KAK COIL , SPEAKER 0.5UH 1

OL91 KJJ7A022Z OUTLET , AC(EUR/1P) A302D0061P 1

Q858 HVT2SA1360O T.R 2SA1360O 1

Q871 HVT2SA1360O T.R 2SA1360O 1

Q872 HVT2SA1360O T.R 2SA1360O 1

Q874 HVT2SA1360O T.R 2SA1360O 1

Q875 HVT2SA1360O T.R 2SA1360O 1

Q881 HVT2SC3423O T.R 2SC3423O 1

Q882 HVT2SC3423O T.R 2SC3423O 1

Q883 HVT2SC3423O T.R 2SC3423O 1

Q884 HVT2SC3423O T.R 2SC3423O 1

Q885 HVT2SC3423O T.R 2SC3423O 1

RY94 HSL1A008ZE RELAY SDT-S-112DMR 1

R656 CRF5EKR27HX2K RES , CEMENT 0.27ohm X 2 1

R657 CRF5EKR27HX2K RES , CEMENT 0.27ohm X 2 1

R658 CRF5EKR27HX2K RES , CEMENT 0.27ohm X 2 1

R659 CRF5EKR27HX2K RES , CEMENT 0.27ohm X 2 1

R660 CRF5EKR27HX2K RES , CEMENT 0.27ohm X 2 1

R905 CRG1ANJ100H RES , METAL OXIDE FILM 10 OHM 1W J 1

R990 CRG1ANJ100H RES , METAL OXIDE FILM 10 OHM 1W J 1

R993 CRG1ANJ100H RES , METAL OXIDE FILM 10 OHM 1W J 1

R995 CRG1ANJ100H RES , METAL OXIDE FILM 10 OHM 1W J 1

R997 CRG1ANJ100H RES , METAL OXIDE FILM 10 OHM 1W J 1

R999 CRG1ANJ100H RES , METAL OXIDE FILM 10 OHM 1W J 1

TH91 KRTP42T7D330B THERMAL SENSOR , POSISTOR P42T7D330BW20 1

T902 CLT5J033YE TRANS , SUB TRANS 1

Description

Value Qty

CMYAVR145 HEAR SINK ASS'Y 1

CHD1A012R SCREW , SPECIAL Not stocked 15

CHD3A012R SCREW , SPECIAL Not stocked 4

CMD1A398 BRACKET , PCB AG-D9320 2

Page 27

CMYAVR145 HEAR SINK ASS'Y 1

harman/kardon

AVR 145/230 service manual

Page 27 of 135

CMD1A417 BRACKET , PCB AG-D8900 2

CMY1A249 HEAT SINK HEAT SINK 1

CMY2A269 HEAT SINK HEAT SINK 1

CTB3+10JR SCREW Not stocked 3

CTB3+8JR SCREW Not stocked 6

Q652 HVT2SB1560-OKM T.R , POWER 2SB1560 1

Q653 HVT2SB1560-OKM T.R , POWER 2SB1560 1

Q654 HVT2SB1560-OKM T.R , POWER 2SB1560 1

Q655 HVT2SB1560-OKM T.R , POWER 2SB1560 1

Q657 HVT2SD2390-OKM T.R , POWER 2SD2390 1

Q658 HVT2SD2390-OKM T.R , POWER 2SD2390 1

Q659 HVT2SD2390-OKM T.R , POWER 2SD2390 1

Q660 HVT2SD2390-OKM T.R , POWER 2SD2390 1

Q661 HVT2SB1560-OKM T.R , POWER 2SB1560 1

Q670 HVT2SD2390-OKM T.R , POWER 2SD2390 1

INPUT PCB ASSY

Ref. # Part Number

COP11912E INPUT PCB ASS'Y(AVR145/230) ASS'Y 1

C201 CCUS1H221JA CAP , CHIP 220PF 1

C202 CCUS1H221JA CAP , CHIP 220PF 1

C203 CCUS1H221JA CAP , CHIP 220PF 1

C204 CCUS1H221JA CAP , CHIP 220PF 1

C205 CCUS1H221JA CAP , CHIP 220PF 1

C206 CCUS1H221JA CAP , CHIP 220PF 1

C209 CCUS1H221JA CAP , CHIP 220PF 1

C210 CCUS1H221JA CAP , CHIP 220PF 1

C211 CCUS1H221JA CAP , CHIP 220PF 1

C212 CCUS1H221JA CAP , CHIP 220PF 1

C213 CCUS1H221JA CAP , CHIP 220PF 1

C214 CCUS1H221JA CAP , CHIP 220PF 1

C215 CCUS1H221JA CAP , CHIP 220PF 1

C216 CCUS1H221JA CAP , CHIP 220PF 1

C219 CCUS1H221JA CAP , CHIP 220PF 1

C220 CCUS1H221JA CAP , CHIP 220PF 1

C221 CCUS1H221JA CAP , CHIP 220PF 1

C222 CCUS1H221JA CAP , CHIP 220PF 1

C223 CCUS1H221JA CAP , CHIP 220PF 1

C224 CCUS1H221JA CAP , CHIP 220PF 1

C260 CCUS1H104KC CAP , CHIP 0.1UF 1

C269 CCUS1A105KC CAP , CHIP 1UF 1

C274 CCUS1A105KC CAP , CHIP 1UF 1

C277 CCUS1H104KC CAP , CHIP 0.1UF 1

C279 CCUS1H104KC CAP , CHIP 0.1UF 1

C280 CCUS1H104KC CAP , CHIP 0.1UF 1

C289 CCUS1H104KC CAP , CHIP 0.1UF 1

C290 CCUS1H104KC CAP , CHIP 0.1UF 1

C291 CCUS1H104KC CAP , CHIP 0.1UF 1

C293 CCUS1H104KC CAP , CHIP 0.1UF 1

C299 CCUS1H104KC CAP , CHIP 0.1UF 1

C301 CCUS1H471JA CAP , CHIP 470PF 1

Description

Value Qty

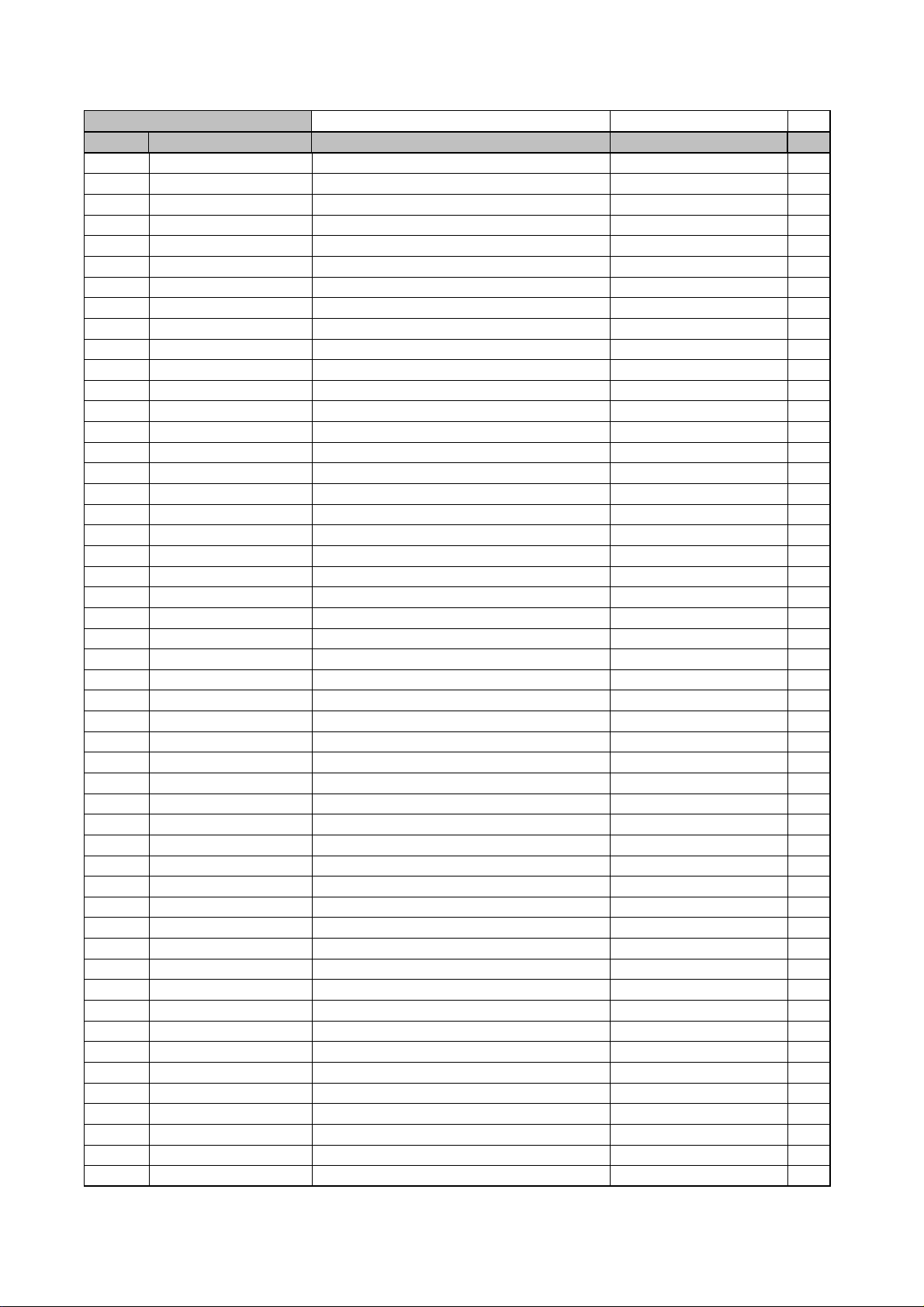

Page 28

INPUT PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 28 of 135

Ref. # Part Number

C302 CCUS1H471JA CAP , CHIP 470PF 1

C303 CCUS1H471JA CAP , CHIP 470PF 1

C304 CCUS1H471JA CAP , CHIP 470PF 1

C305 CCUS1H471JA CAP , CHIP 470PF 1

C306 CCUS1H471JA CAP , CHIP 470PF 1

C309 CCUS1H332KC CAP , CHIP 3300PF 1

C310 CCUS1H332KC CAP , CHIP 3300PF 1

C311 CCUS1H332KC CAP , CHIP 3300PF 1

C312 CCUS1H332KC CAP , CHIP 3300PF 1

C313 CCUS1H332KC CAP , CHIP 3300PF 1

C314 CCUS1H332KC CAP , CHIP 3300PF 1

C317 CCUS1H223KC CAP , CHIP 0.022UF 1

C318 CCUS1H223KC CAP , CHIP 0.022UF 1

C319 CCUS1H223KC CAP , CHIP 0.022UF 1

C321 CCUS1H561JA CAP , CHIP 560PF 1

C322 CCUS1H561JA CAP , CHIP 560PF 1

C323 CCUS1H561JA CAP , CHIP 560PF 1

C324 CCUS1H561JA CAP , CHIP 560PF 1

C325 CCUS1H561JA CAP , CHIP 560PF 1

C326 CCUS1H561JA CAP , CHIP 560PF 1

C327 CCUS1H561JA CAP , CHIP 560PF 1

C328 CCUS1H561JA CAP , CHIP 560PF 1

C329 CCUS1H561JA CAP , CHIP 560PF 1

C330 CCUS1H561JA CAP , CHIP 560PF 1

C331 CCUS1H561JA CAP , CHIP 560PF 1

C332 CCUS1H561JA CAP , CHIP 560PF 1

C337 CCUS1H223KC CAP , CHIP 0.022UF 1

C338 CCUS1H223KC CAP , CHIP 0.022UF 1

C339 CCUS1H223KC CAP , CHIP 0.022UF 1

C350 CCUS1H332KC CAP , CHIP 3300PF 1

C351 CCUS1H332KC CAP , CHIP 3300PF 1

C352 CCUS1H332KC CAP , CHIP 3300PF 1

C353 CCUS1H332KC CAP , CHIP 3300PF 1

C354 CCUS1H332KC CAP , CHIP 3300PF 1

C355 CCUS1H332KC CAP , CHIP 3300PF 1

C369 CCUS1H223KC CAP , CHIP 0.022UF 1

C370 CCUS1H223KC CAP , CHIP 0.022UF 1

C381 CCUS1H223KC CAP , CHIP 0.022UF 1

C382 CCUS1H223KC CAP , CHIP 0.022UF 1

C383 CCUS1H223KC CAP , CHIP 0.022UF 1

C384 CCUS1H223KC CAP , CHIP 0.022UF 1

C385 CCUS1H223KC CAP , CHIP 0.022UF 1

C386 CCUS1H223KC CAP , CHIP 0.022UF 1

C391 CCUS1H151JA CAP , CHIP 150PF 1

C392 CCUS1H151JA CAP , CHIP 150PF 1

C393 CCUS1H151JA CAP , CHIP 150PF 1

C394 CCUS1H102KC CAP , CHIP 1000PF 1

C395 CCUS1H151JA CAP , CHIP 150PF 1

C396 CCUS1H151JA CAP , CHIP 150PF 1

C400 CCUS1H104KC CAP , CHIP 0.1UF 1

Description

Value Qty

Page 29

INPUT PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 29 of 135

Ref. # Part Number

C401 CCUS1H104KC CAP , CHIP 0.1UF 1

C402 CCUS1H471JA CAP , CHIP 470PF 1

C403 CCUS1H471JA CAP , CHIP 470PF 1

C410 CCUS1A105KC CAP , CHIP 1UF 1

C411 CCUS1A105KC CAP , CHIP 1UF 1

C412 CCUC1C225ZF CAP , CHIP(2.2UF/16V/2012/Y5V) 2.2UF 1

C413 CCUC1C225ZF CAP , CHIP(2.2UF/16V/2012/Y5V) 2.2UF 1

C416 CCUS1H473KC CAP , CHIP 0.047UF 1

C420 CCUS1A105KC CAP , CHIP 1UF 1

C421 CCUS1A105KC CAP , CHIP 1UF 1

C422 CCUS1A105KC CAP , CHIP 1UF 1

C423 CCUS1H220JA CAP , CHIP 22PF 1

C424 CCUS1H220JA CAP , CHIP 22PF 1

C425 CCUS1H223KC CAP , CHIP 0.022UF 1

C426 CCUS1H223KC CAP , CHIP 0.022UF 1

C427 CCUS1H223KC CAP , CHIP 0.022UF 1

C432 HCEC1CRV2220T CAP , ELEC (SMD) 22UF/16V 1

C435 CCUS1H070DA CAP , CHIP 7PF 1

C436 CCUS1H120JA CAP, CHIP 12PF/50V/COG/1608 12PF 1

C440 CCUS1H223KC CAP , CHIP 0.022UF 1

C445 HCEC1CRV2220T CAP , ELEC (SMD) 22UF/16V 1

C601 CCUS1H104KC CAP , CHIP 0.1UF 1

C603 CCUS1H104KC CAP , CHIP 0.1UF 1

C605 CCUS1H104KC CAP , CHIP 0.1UF 1

C607 CCUS1H104KC CAP , CHIP 0.1UF 1

C609 CCUS1H104KC CAP , CHIP 0.1UF 1

C611 CCUS1H104KC CAP , CHIP 0.1UF 1

C613 CCUS1H104KC CAP , CHIP 0.1UF 1

C615 CCUS1H104KC CAP , CHIP 0.1UF 1

C617 CCUS1H104KC CAP , CHIP 0.1UF 1

C619 CCUS1H104KC CAP , CHIP 0.1UF 1

C621 CCUS1H104KC CAP , CHIP 0.1UF 1

C623 CCUS1H104KC CAP , CHIP 0.1UF 1

C625 CCUS1H104KC CAP , CHIP 0.1UF 1

C627 CCUS1H104KC CAP , CHIP 0.1UF 1

C629 CCUS1H104KC CAP , CHIP 0.1UF 1

C631 CCUS1H104KC CAP , CHIP 0.1UF 1

C701 CCUS1H150JA CHIP, CAP 15PF/50V/1608 15PF 1

C702 CCUS1H150JA CHIP, CAP 15PF/50V/1608 15PF 1

C704 CCUS1H104KC CAP , CHIP 0.1UF 1

C705 CCUS1H104KC CAP , CHIP 0.1UF 1

C707 CCUS1H102KC CAP , CHIP 1000PF 1

C708 CCUS1H104KC CAP , CHIP 0.1UF 1

C709 CCUS1H102KC CAP , CHIP 1000PF 1

C711 CCUS1H102KC CAP , CHIP 1000PF 1

C712 CCUS1H223KC CAP , CHIP 0.022UF 1

C713 CCUS1H390JA CAP , CHIP 39PF 1

C714 CCUS1H390JA CAP , CHIP 39PF 1

C718 CCUS1H104KC CAP , CHIP 0.1UF 1

C719 CCUS1H104KC CAP , CHIP 0.1UF 1

Description

Value Qty

Page 30

INPUT PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 30 of 135

Ref. # Part Number

C722 CCUS1H104KC CAP , CHIP 0.1UF 1

C723 CCUS1H473KC CAP , CHIP 0.047UF 1

C725 CCUS1H104KC CAP , CHIP 0.1UF 1

C727 CCUS1H104KC CAP , CHIP 0.1UF 1

C729 CCUS1H104KC CAP , CHIP 0.1UF 1

C731 CCUS1H104KC CAP , CHIP 0.1UF 1

C733 CCUS1H104KC CAP , CHIP 0.1UF 1

C734 CCUS1H102KC CAP , CHIP 1000PF 1

C735 CCUS1H470JA CAP , CHIP 0.047UF 1

C738 CCUS1A105KC CAP , CHIP 1UF 1

C739 CCUS1H103KC CAP , CHIP 0.01UF 1

C741 CCUS1H104KC CAP , CHIP 0.1UF 1

C742 CCUS1H180JA CHIP, CAP 18PF/50V/1608 18PF 1

C743 CCUS1H104KC CAP , CHIP 0.1UF 1

C744 CCUS1H180JA CHIP, CAP 18PF/50V/1608 18PF 1

C745 CCUS1H104KC CAP , CHIP 0.1UF 1

C746 CCUS1H104KC CAP , CHIP 0.1UF 1

C747 CCUS1H104KC CAP , CHIP 0.1UF 1

C748 CCUS1H104KC CAP , CHIP 0.1UF 1

C751 CCUS1H104KC CAP , CHIP 0.1UF 1

C755 CCUS1H561JA CAP , CHIP 560PF 1

C757 CCUS1H104KC CAP , CHIP 0.1UF 1

C758 CCUS1H104KC CAP , CHIP 0.1UF 1

C759 CCUS1H104KC CAP , CHIP 0.1UF 1

C760 CCUS1H104KC CAP , CHIP 0.1UF 1

C761 CCUS1H104KC CAP , CHIP 0.1UF 1

C762 CCUS1H104KC CAP , CHIP 0.1UF 1

C763 CCUS1H104KC CAP , CHIP 0.1UF 1

C765 CCUS1H104KC CAP , CHIP 0.1UF 1

C767 HCEC1CRV2100T CAP , ELEC (SMD) 10UF / 16V 1

C768 CCUS1H104KC CAP , CHIP 0.1UF 1

C769 CCUS1H104KC CAP , CHIP 0.1UF 1

C770 CCUS1H104KC CAP , CHIP 0.1UF 1

C771 CCUS1H104KC CAP , CHIP 0.1UF 1

C772 CCUS1H104KC CAP , CHIP 0.1UF 1

C773 CCUS1H104KC CAP , CHIP 0.1UF 1

C774 HCEC1CRV2101T CAP , ELEC (SMD) 100UF / 16V 1

D201 CVD1SS355T CHIP , DIODE 1SS355T 1

D202 CVD1SS355T CHIP , DIODE 1SS355T 1

D203 CVD1SS355T CHIP , DIODE 1SS355T 1

D204 CVD1SS355T CHIP , DIODE 1SS355T 1

D207 CVD1SS355T CHIP , DIODE 1SS355T 1

D208 CVD1SS355T CHIP , DIODE 1SS355T 1

D209 CVD1SS355T CHIP , DIODE 1SS355T 1

D210 CVD1SS355T CHIP , DIODE 1SS355T 1

D211 CVD1SS355T CHIP , DIODE 1SS355T 1

D212 CVD1SS355T CHIP , DIODE 1SS355T 1

D213 CVD1SS355T CHIP , DIODE 1SS355T 1

D214 CVD1SS355T CHIP , DIODE 1SS355T 1

D215 CVD1SS355T CHIP , DIODE 1SS355T 1

Description

Value Qty

Page 31

INPUT PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 31 of 135

Ref. # Part Number

D216 CVD1SS355T CHIP , DIODE 1SS355T 1

D400 CVD1SS355T CHIP , DIODE 1SS355T 1

D401 CVD1SS355T CHIP , DIODE 1SS355T 1

IC20 CVINJW1197FC2 IC , SW(WITH VOLUME) JRC 1

IC21 HVINJM2068MDTE1 I.C , OP AMP JRC 1

IC22 HVINJM2068MDTE1 I.C , OP AMP JRC 1

IC23 HVINJM2068MDTE1 I.C , OP AMP JRC 1

IC25 HVINJM2068MDTE1 I.C , OP AMP JRC 1

IC31 HVINJM2068MDTE1 I.C , OP AMP JRC 1

IC32 HVINJM2068MDTE1 I.C , OP AMP JRC 1

IC33 HVINJM2068MDTE1 I.C , OP AMP JRC 1

IC41 HVINJM2068MDTE1 I.C , OP AMP JRC 1

IC42 HVINJM2068MDTE1 I.C , OP AMP JRC 1

IC43 HVINJM2137MTE1 I.C, OP AMP JRC 1

IC72 HVI74HCU04AFNG I.C , HEX INVERTER TOSHIBA 1

IC73 HVIAK4589VQ-T I.C , CODEC + DIR ASAHI KASEI 1

IC74 HVILC72723M IC , PLL (RDS) SANYO 1

IC75 CVICS49510-CQ I.C , DSP CIRRUS LOGIC 1

IC76 HVIM29W800DT70N I.C, 4M FLASH MEMORY ST 1

IC77 HVI57V161610ET7 SDRAM 16M 7NS HYNIX 1

IC78 HVINJM2391DL133 I.C , CHIP REGULATOR (+3.3V) JRC 1

IC79 HVILM1117S-1V8 I.C , REGULATOR (1.8V) HTC 1

IC88 HVILM1117S-3V3 I.C , REGULATOR (3.3V) HTC 1

IC89 CVIM24C32WMN6TP I.C , EEPROM (32 Kbit) ST 1

IC90 CVIT5CC1 I.C , FLASH U-COM TOSHIBA 1

IC91 HVI74ACT04MTR I.C , HEX INVERTER TOSHIBA 1

JK40 HJJ9L003Z JACK , IPOD IPOD JACK 1

L701 HLZ9Z014Z CHIP , BEAD HU-1H4516-600JT 1

L702 HLZ9Z014Z CHIP , BEAD HU-1H4516-600JT 1

L703 HLZ9Z014Z CHIP , BEAD HU-1H4516-600JT 1

L704 HLZ9R005Z BEAD CHIP 60(1608 SIZE) HH-1M1608-600 1

L705 HLZ9R005Z BEAD CHIP 60(1608 SIZE) HH-1M1608-600 1

Q402 HVTKRC102S TR , CHIP KRC102S 1

Q729 HVTKRC107S TR , CHIP KRC107S 1

Q730 HVTKRC107S TR , CHIP KRC107S 1

RN61 CRJ104DJ103T RES , 4ARRAY (1608*4) 10K OHM/1608*4 1

RN62 CRJ104DJ103T RES , 4ARRAY (1608*4) 10K OHM/1608*4 1

RN63 CRJ104DJ103T RES , 4ARRAY (1608*4) 10K OHM/1608*4 1

RN64 CRJ104DJ101T RES , 4ARRAY (1608*4) 100 OHM/1608*4 1

RN65 CRJ104DJ101T RES , 4ARRAY (1608*4) 100 OHM/1608*4 1

RN66 CRJ104DJ101T RES , 4ARRAY (1608*4) 100 OHM/1608*4 1

RN71 CRJ104DJ103T RES , 4ARRAY (1608*4) 10K OHM/1608*4 1

RN72 CRJ104DJ103T RES , 4ARRAY (1608*4) 10K OHM/1608*4 1

RN73 CRJ104DJ103T RES , 4ARRAY (1608*4) 10K OHM/1608*4 1

RN74 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN75 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN76 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN77 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN78 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN79 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

Description

Value Qty

Page 32

INPUT PCB ASSY

harman/kardon

AVR 145/230 service manual

Page 32 of 135

Ref. # Part Number

RN80 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN81 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN82 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN83 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN84 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN85 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN86 CRJ104DJ103T RES , 4ARRAY (1608*4) 10K OHM/1608*4 1

RN87 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN88 CRJ104DJ103T RES , 4ARRAY (1608*4) 10K OHM/1608*4 1

RN89 CRJ104DJ103T RES , 4ARRAY (1608*4) 10K OHM/1608*4 1

RN90 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN91 CRJ104DJ330T RES , 4ARRAY (1608*4) 33 OHM/1608*4 1

RN92 CRJ104DJ101T RES , 4ARRAY (1608*4) 100 OHM/1608*4 1

R201 CRJ10DJ101T RES , CHIP 100 OHM 1

R202 CRJ10DJ101T RES , CHIP 100 OHM 1

R203 CRJ10DJ101T RES , CHIP 100 OHM 1

R204 CRJ10DJ101T RES , CHIP 100 OHM 1

R205 CRJ10DJ101T RES , CHIP 100 OHM 1

R206 CRJ10DJ101T RES , CHIP 100 OHM 1