Page 1

- 33 -

INTERNAL BLOCK DIAGRAM OF ICs

■ LA1837

FM SD

ADJ

3 rd 5 th

DECODER

ANTI-BIRDIE

FM

BLOCK DIAGRAM

Pin Functions

Page 2

- 34 -- 34 -

Page 3

- 35 -

Page 4

- 36 -

Pre Out

Ch2

3.3µF

3.3µF

3.3µF

3.3µF

3.3µF

1000µF

1000µF

47µF

47µF

47µF

0.018µF

1000µF

3.3µF

47µF

1.2µF

100

µF

R . R

Vcc

1000

µF

47µF

0.018µF

10kΩ

10kΩ

150kΩ

150kΩ

1MΩ

2.2kΩ

2.2kΩ

Rec IN

Ch2

Rec

IN

Rec IN

Ch1

ALC

Rec Out

Ch2

180kΩ

180kΩ

Gv

Gvo

180kΩ

180kΩ

1kΩ

1kΩ

1kΩ

1kΩ

100kΩ

100Ω

10kΩ

10kΩ

10Ω

300kΩ

9.1kΩ

100Ω

Pre IN

Ch2/B

(Play Rec)

Pre IN

Ch2/A

(Play only)

Pre IN

Ch1/B

(Play Rec)

Pre Out

Ch1

Pre IN

Ch1/A

Ch1/B

NF

Ch2/A

Ch1/A

Ch1/B

Gvo

Gv

Gvo

Gv

Vcc

M

N

NF

NF

Ch1

Ch1

Ch2

Gvc

GV

Ch2

ALC

GND

Rec

15

14

13

12

11

23

24

1

2

161718192122

IN

Vref1

Vref

Vref2

A/B

Metal

Out

Pre

Out

REC

Out

Rec Out

Ch1

Mix

Out

GND1 M/N

6.8kΩ

A

B

1000pF

1000pF

6.8kΩ

9.1kΩ

20

10 9876435

M/N

■ KIA6289N

■ KA8301

DRIVER

PRE

LOGIC

23456789101

GND

Vout1

Vz1VrFin

Rin

Vcc1

Vcc2

Vz2

Vout2

Page 5

- 37 -

■ KIA7805 P/PI ~ KIA7824P/PI

3

1

2

4

R

12

R

1

C

21

R

12

Q

1

Q

7

Q

13

Q

10

Q

6

Q

5

Q

4

Q

3

Q

11

Q

15

Q

14

Q

9

Q

8

Q

16

Q

17

Q

INPUT

OUTPUT

GND

2

Q

1

Z

18

R

8

R

9

R

13

R

11

R

17

R

5

R

6

R

1

R

2

RR

16

R

20

R

19

R

14

R

10

R

7

R

Page 6

- 38 -

■ KB9224

Page 7

- 39 -

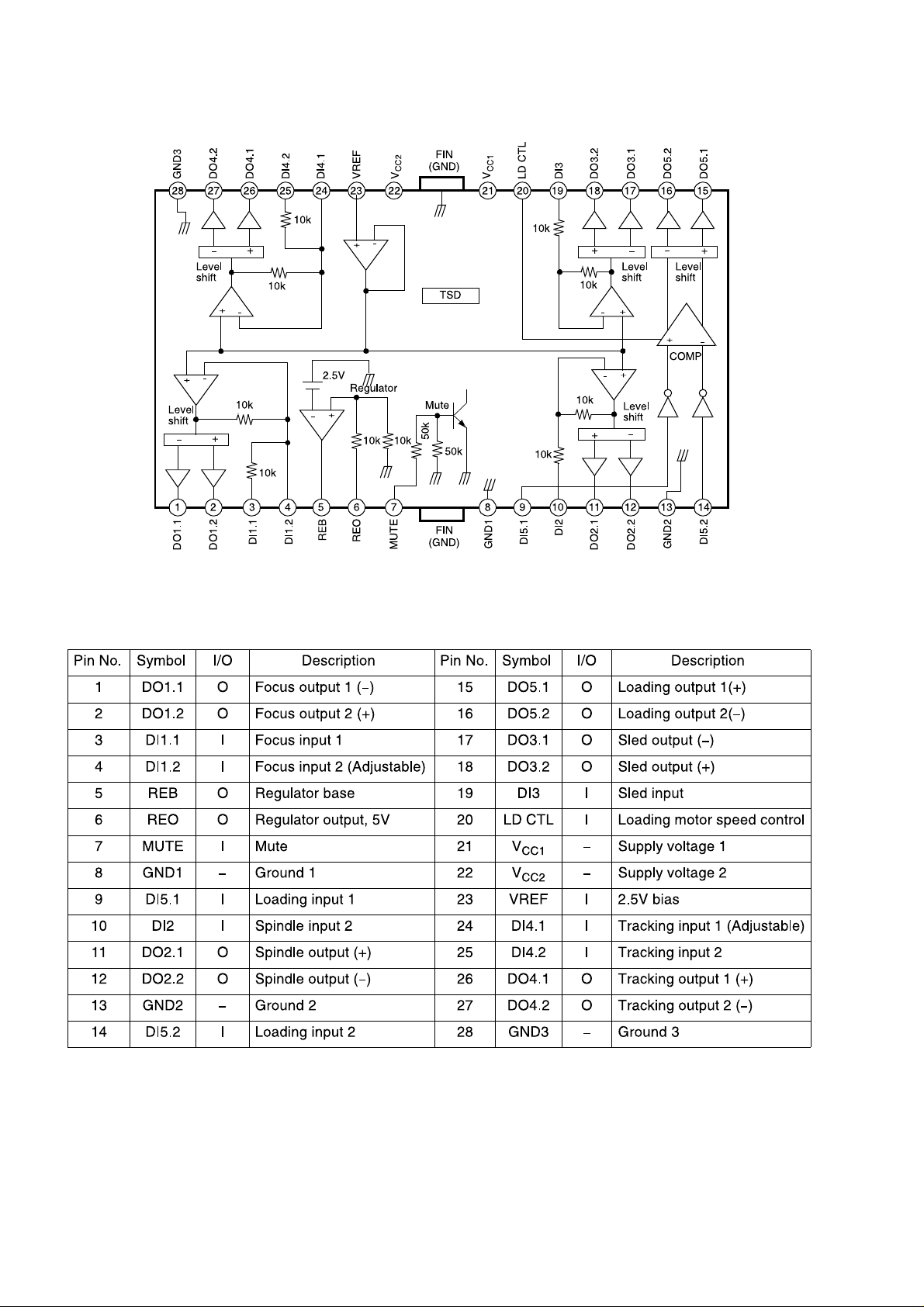

PIN DESCRIPTION

Page 8

- 40 -

PIN DESCRIPTION (Continued)

Page 9

- 41 -

■ TDA7440D

L-IN1

100K

100K

100K

100K

100K

100K

100K

100K

48918

27

21

22

20

26

24

25

LOUT

SCL

SDA

DIG_GND

ROUT

V

S

AGND

R

B

R

B

14 15

10 11 19 12 13 23

5

G

G

6

7

3

2

INPUT MULTIPLEXER

+GAIN

MUXOUTR INR TREBLE(R) BIN(R) BOUT(R) CREF D98AU883

0/30dB

2dB STEP

MUXOUTL

VOLUME TREBLE

I CBUS DECODER + LATCHES

BASS

SPKR ATT

LEFT

VOLUME TREBLE BASS

SUPPLY

V

REF

SPKR ATT

RIGHT

INL TREBLE(L) BOUT(L)BIN(L)

1

28

L-IN2

L-IN3

L-IN4

R-IN1

R-IN2

R-IN3

R-IN4

2

PIN DESCRIPTION (Continued)

Page 10

- 42 -

■ KS9287

BLOCK DIAGRAM

Page 11

- 43 -

PIN DESCRIPTION

Page 12

- 44 -

PIN DESCRIPTION (Continued)

Page 13

- 45 -

PIN DESCRIPTION (Continued)

Page 14

- 46 -

■ KA9259

BLOCK DIAGRAM

PIN DESCRIPTION

Page 15

- 47 -

■ LC72131, 72131M

B01 B02 B03 B04 I01 I02

XIN

PD

AIN

AOUT

IFIN

XOUT

FMIN

AMIN

CE

DI

CL

D0

VDD

VSS

REFERENCE

DIVIDER

PHASE DETECTOR

CHARGE PUMP

UNLOCK

DETECTOR

UNIVERSAL

COUNTER

DATA SHIFT REGISTER

LATCH

12bits PROGRAMMABLE

DIVIDER

SWALLOW COUNTER

1/16. 1/17 4bits

POWER

ON

RESET

CCB

I/F

1

2

■ TDA7296

C2

22

µF

R2

680

Ω

IN-

IN+

2

3

4

10

9

C4 10

µF

1

STBY-GND

C3 10

µF

R4 22K

R5 10K MUTE

STBY

VM

VSTBY

IN+MUTE

R1 22K

C1 470nF

R3 22K

C7 100nF

+Vs

7

8

-Vs

C9 100n

F

15

-PWVs

-Vs

C8 1000

µF

MUTE

THERMAL

SHUTDOWN

S/C

PROTECTION

STBY

+Vs

C6 1000

µF

+PWVs

13

14

6

OUT

C5

22

µF

BOOTSTRAP

D93AU011

Page 16

- 48 -

■ MSGEQ7

■ UDA1330T

Audio

In

Anti-Alias

Filter

Clock

Oscillator

Output

Multiplexor

CKIN

Reset

63Hz

Bandpass

160Hz

Bandpass

400Hz

Bandpass

1kHz

Bandpass

2.5kHz

Bandpass

6.25kHz

Bandpass

16kHz

Bandpass

Peak

Detector

Peak

Detector

Peak

Detector

Peak

Detector

Peak

Detector

Peak

Detector

Peak

Detector

Strobe

DC Out

DIGITAL INTERFACE

UDA1330ATS

VOLUME/MUTE/DE-EMPHASIS

INTERPOLATION FILTER

NOISE SHAPER

DAC

13 15 12

1614

6

BCK

WS

DATAI

SYSCLK

V

O(L)

V

DDA

V

SSA

V

O(R)

APPSEL

APPL0

APPL1

APPL2

APPL3

V

DDD

V

SSD

V

ref(DAC)

3

45

7

11

10

9

8

2

1

DAC

CONTROL

INTERFACE

Page 17

- 49 -

■ GD74HC00D

■ GD74HC04D

■ GD74HC32D

1

2

3

4

5

6

7

D

oa

D

oa

D

ob

1

2

3

D

ob

Q

0

Q

0

D

1a

D

1b

Q

1

GND

TOP VIEW

PIN CONFIGURATION LOGIC DIAGRAM FUNCTION TABLE

8

9

10

11

12

13

14

V

cc

D

3b

D

3a

Q

3

D

2b

D

2a

Q

2

D

1a

D

1b

4

5

6

Q

1

D

2a

D

2b

9

10

8

Q

2

D

3a

D

3b

Vcc = Pin14

GND=Pin7

H=High voltage level

L=Low voltage level

12

13

11

INPUTS OUTPUT

Q

3

DnaD

nb

Q

n

LL

H

LH

H

HL

H

HH

L

1

2

3

4

5

6

7

1A

1Y

2A

2Y

3A

3Y

TOP VIEW

PIN CONFIGURATION

14

13

12

11

10

9

8

V

cc

6A

6Y

5A

5Y

4A

4Y

Vcc = Pin14

GND=Pin7

1A 1Y

21

2A 2Y

43

3A 3Y

65

4A 4Y

89

5A 5Y

1011

6A 6Y

1213

LOGIC DIAGRAM FUNCTION TABLE

H=High voltage level

L=Low voltage level

INPUTS OUTPUT

YA

L

H

H

L

GND

1

2

3

4

5

6

7

D

oa

D

oa

D

ob

1

2

3

D

ob

Q

0

Q

0

D

1a

D

1b

Q

1

GND

TOP VIEW

PIN CONFIGURATION LOGIC DIAGRAM FUNCTION TABLE

14

13

12

11

10

9

8

V

cc

D

3b

D

3a

Q

3

D

2b

D

2a

Q

2

D

1a

D

1b

4

5

6

Q

1

D

2a

D

2b

9

10

8

Q

2

D

3a

D

3b

Vcc = Pin14

GND=Pin7

H=High voltage level

L=Low voltage level

12

13

11

INPUTS OUTPUT

Q

3

D

naDnb

Q

n

LL

L

LH

H

HL

H

HH

H

■ 74HC08D

1

2

3

4

5

6

7

D

oa

D

oa

D

ob

1

2

3

D

ob

Q

0

Q

0

D

1a

D

1b

Q

1

GND

TOP VIEW

PIN CONFIGURATION LOGIC DIAGRAM FUNCTION TABLE

14

13

12

11

10

9

8

V

cc

D

3b

D

3a

Q

3

D

2b

D

2a

Q

2

D

1a

D

1b

4

5

6

Q

1

D

2a

D

2b

9

10

8

Q

2

D

3a

D

3b

Vcc = Pin14

GND=Pin7

H=High voltage level

L=Low voltage level

12

13

11

INPUTS OUTPUT

Q

3

D

naDnb

Q

n

LL

L

LH

L

HL

L

HH

H

Page 18

- 50 -

■ BU1427AK

Pin Description

Pin Name Function pin Name Function

1 BOSD OSD BLUE DATA INPUT

*

33 SLABEB SET MODE MASTER/SLABE

*

2 GD0 GREEN DATA Bit0(LSB)

*

34 ADDH ADD ONE LINE AT NON-HNTER

*

3 GD1 GREEN DATA Bit1

*

35 VREF REFERENCE VOLTAGE (1.29V)

4 GD2 GREEN DATA Bit2

*

36 CGND CHROMA OUTPUT GROUND

5 GD3 GREEN DATA Bit3

*

37 COUT CHROMA OUTPUT

6 GD4 GREEN DATA Bit4 38 VGND COMPOSITE OUTPUT GROUND

7 GD5 GREEN DATA Bit5 39 VOUT COMPOSITE OUTPUT

8 GD6 GREEN DATA Bit6 40 AVSS ANALOG(DAC, VREF) GROUND

9 GND DIGITAL GROUND 41 NC -

10 GD7 GREEN DATA Bit7(MSB) 42 IR REFERENCE RESISTOR (1.2K)

11 BD0 BLUE DATA Bit0(LSB)

*

43 AVDD ANALOG (DAC, REF) VDD

12 BD1 BLUE DATA Bit1

*

44 YGND LUMINANCE OUTPUT GROUND

13 BD2 BLUE DATA Bit2

*

45 YOUT LUMINANCE OUTPUT

14 BD3 BLUE DATA Bit3

*

46 G4FSC PULLDOWN TO GND

15 OSDSW OSD INPUT ENABLE

*

47 GCLK VIDEO CLOCK INPUT FOR CD-G

16 CDGSWB SELECT Video-CD/CD-G 48 YCOFF DAC(YOUT, COUT) OFF

*

17 BD4 BLUE DATA Bit4 49 YFILON PULLDOWN TO GND

*

18 BD5 BLUE DATA Bit5 50 PAL60B PAL60 ON AT NTB=HIGH $

19 BD6 BLUE DATA Bit6 51 VCLK VIDEO CLOCK INPUT FOR VCD

20 BD7 BLUE DATA Bit7(MSB) 52 RSTB LOGIC PART INITIAL RESET $

21 GND DIGITAL GROUND 53 CLKSW DIVIDE INPUT CLK ENABLE

22 NTB SELECT NTSC/PAL MODE 54 RD0 RED DATA Bit0 (LSB)

*

23 IM0 INPUT MODE SET Bit0

*

55 RD1 RED DATA Bit1

*

24 IM1 INPUT MODE SET Bit1

*

56 RD2 RED DATA Bit2

*

25 TEST1

NORMALLY PULLDOWN TO GND*57 ROSD OSD RED DATA INPUT

*

26 TEST2

NORMALLY PULLDOWN TO GND

*

58 RD3 RED DATA Bit3

*

27 CVSY C-SYNC OR V-SYNC INPUT 59 RD4 RED DATA Bit4

*

28 HSY H-SYNC INPUT 60 RD5 RED DATA Bit5

*

29 PIXCLX 1/2 FREQ. OF INTERNAL CL 61 VDD DIGITAL VDD

30 BLKB DATA BLANKING ENABLE

*

62 RD6 RED DATA Bit6

*

31 VDD DIGITAL VDD 63 RD7 RED DATA Bit7

*

32 INT

INTERLACE/NON-INTERLACE

64 GDSD OSD GREEN DATA INPUT

*

*

• • • Internal Pulldown register

$ • • • Internal Pullup register

Page 19

- 51 -

BLOCK DIAGRM

Loading...

Loading...