Page 1

GE Healthcare

MAC™ 3500

Resting ECG Analysis System

Product Code SCA

Service Manual

2021337-036 Revision D

g

Page 2

The information in this manual applies only to MAC 3500 Resting ECG Analysis Systems with product code SCA. It does not

apply to earlier software versions. Due to continuing product innovation, specifications in this manual are subject to change

without notice.

MUSE, CASE, MAC, MARS, MULTI-LINK, and 12SL are trademarks owned by GE Medical Systems Information

Technologies, a General Electric Company going to market as GE Healthcare. All other trademarks are owned by their

respective owners.

© 2005-2008 General Electric Company. All rights reserved.

T-2 MAC™ 3500 Resting ECG Analysis System Revision D

2021337-036 10 October 2008

Page 3

Contents

1 Introduction

Manual Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-3

Manual Purpose . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-3

Intended Audience . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-3

Warnings, Cautions, and Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

Safety Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Responsibility of the Manufacturer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-5

General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-6

Equipment Symbols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

Service Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

Service Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-8

Equipment Identification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-8

Serial Number Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-9

Label Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-9

2 Equipment Overview

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Side View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

Back View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

Connector Identification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

Detailed Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Overview / Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

Power Supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

+3V-C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

+3V-M . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

+3V-EMI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

+5V-M . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

+5V-EMI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

+18V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

+1.8V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

Revision D MAC™ 3500 resting ECG analysis system i

2021337-036

Page 4

+12V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

REF2V5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

VAna+, VAna- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

Super I/O and FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

CPU ATMEL AT91RM9200 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

CPU (Stooges) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

RTC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

External Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

Boot Loader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-15

FPGA Internal Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-16

Board ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-17

XBus Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-17

Video Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-17

Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-23

System Interrupt Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-24

Acquisition Module Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-24

Thermal Printhead Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-25

Serial EEPROM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26

BBus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26

PWM Analog Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-26

Beep Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-27

PC Card Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-27

SDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-27

NAND Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-27

Secure Digital Card Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-28

Serial EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-28

Daughter Board Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-28

VGA LCD/CRT Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-28

LCD Panel EMI Reduction Components . . . . . . . . . . . . . . . . . . .2-29

CRT Video DAC / Sync / Buffers . . . . . . . . . . . . . . . . . . . . . . . . .2-29

Acquisition Module Transceiver / Power Switch . . . . . . . . . . . . . . . . . . . . . .2-29

Transceiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-29

Acquisition Power Regulator / Switch . . . . . . . . . . . . . . . . . . . . . .2-30

COMM Port Power Switch / Current Limiter / KISS Power . . . . . . . . . . . . .2-30

Thermal Printhead Power / Pixel Test Hardware . . . . . . . . . . . . . . . . . . . . .2-31

Super I/O Peripheral Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-31

RS-232 Serial Ports (One Dual Mode RS-232 / IrDA) . . . . . . . . .2-31

Clock/Calendar . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-31

PS2 Keyboard Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-32

The Three Stooges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-32

Startup Self Identification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-32

BBus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-33

Shemp . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-33

Larry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-33

Moe . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-35

ii MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 5

3 Installation

Preparation for Use . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-3

Trolley Height Adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-4

Installing the MAC™ 3500 resting ECG analysis system . . . . . . . . . . . . . . .3-6

Installing the Optional External Modem Kit . . . . . . . . . . . . . . . . . . . . . . . . . .3-8

Magnetic Card Reader Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

Barcode Reader Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12

4 Maintenance

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

Recommended Maintenance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

Required Tools and Supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

Inspection and Cleaning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

Visual Inspection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

Exterior Cleaning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

Interior Cleaning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

Thermal Printhead Cleaning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

FRU Replacement Procedures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Disassembly Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-6

Battery Replacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-6

Remove MAC 3500 System From Trolley . . . . . . . . . . . . . . . . . . . . . . . . . . .4-7

Power Supply Replacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Keypad Replacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

Keyboard/Top Cover Assembly Removal & Reassembly . . . . . . . . . . . . . . . . . . 4-13

Removal of Keyboard/Top Cover Assembly . . . . . . . . . . . . . . . . . . . . . . . .4-13

Keyboard/Top Cover Assembly Reassembly . . . . . . . . . . . . . . . . . . . . . . . .4-15

Printhead Assembly Replacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

Acquisition Board Replacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17

Display Assembly Replacement Procedures . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-18

KISS Pump Replacement Procedures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19

Main CPU Board Replacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-20

Removal of CPU Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-20

Reassembly of CPU Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-21

Software, System Setups, and Option Activation . . . . . . . . . . . . . . . . . . . . .4-22

Revision D MAC™ 3500 resting ECG analysis system iii

2021337-036

Page 6

Software Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-22

Service Only Setups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-23

Restore System Setups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-24

Restore Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-24

Disable Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-25

COMM Board Replacement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-26

Writer Roller/Carriage Assembly Replacement . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28

Leakage Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-29

Functional Checkout Procedures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-30

Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-31

Visual Inspection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-31

Checkout Procedures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-32

Operational Checks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-32

Diagnostic Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-32

Electrical Safety Checks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-33

5 Troubleshooting

Assembly Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-3

Assembly Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-3

Main PCB Board Interconnect Detail . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-4

General Fault Isolation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

Power-up Self-test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-5

Power-up Flow Chart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-6

Poor Quality ECGs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-7

Visual Inspection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-8

Diagnostic Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

Loading the System Diagnostics Menu . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-9

Display Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-10

Speaker Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-11

Keyboard Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-11

Trim Pad Control Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-12

Writer Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-12

Battery Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-14

Communication Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-16

Acq. Module Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-19

Analog I/O Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-20

Floppy Drive Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-22

Internal Memory Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23

SD Card Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-23

Substitute Master Password . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-24

iv MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 7

Equipment Problems . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

ECG Data Noise . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-25

System Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26

Frequently Asked Questions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27

Maintenance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-27

Save Setups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-27

Storing ECGs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-27

Format an SD Card . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-27

Cleaning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-27

Battery Capacity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-28

System Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-28

Location Number . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-28

Patient Questions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-28

Passwords . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-29

Clinical . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-29

Report Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-29

Editing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-29

Entering Patient Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-30

Transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-30

Losing Fields When Transmitting . . . . . . . . . . . . . . . . . . . . . . . . .5-30

Input and Output Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-31

A Pins (J1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-31

COM1 (COM3/4) Pins (J3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-31

COM2 Pins (J5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-32

Analog Pins (J6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-32

EXT. VID. Pins (J7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-33

CPU PCB Input/Output Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-34

Battery Pack/Monitor, J2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-34

LCD Backlight, J4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-34

Keyboard, J8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-34

LCD, J10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-35

Power Supply/Motor, J11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-36

Thermal Printer, J12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-37

Floppy Disk Drive, J13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-38

Acquisition Module, J14 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-39

6 Parts Lists

Ordering Parts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

General Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3

Field Replaceable Units (FRUs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

Upper Level Assembly Drawings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4

Sub-Assemblies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-11

Revision D MAC™ 3500 resting ECG analysis system v

2021337-036

Page 8

MAC 3500 Display Assembly, pn 2026799-001 . . . . . . . . . . . . . .6-11

MAC 3500 KISS Pump Assembly, pn 2022882-001 . . . . . . . . . . 6 -13

Universal Writer Kit, pn 2031810-001 . . . . . . . . . . . . . . . . . . . . . .6-14

Thermal Writer Assembly . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-15

Keyboards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-17

Model 3800 Barcode Scanners . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-18

Model 4600 Barcode Scanners . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-19

Card Readers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-20

Modems . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-21

Wireless Option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-21

Power Cords . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-21

Trolley . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-22

Field Replaceable Unit Kits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-23

Hardware Kit for MAC 3500, pn 2030869-001 . . . . . . . . . . . . . . .6-23

MAC 3500 Plastics Kit, pn 2030898-001 . . . . . . . . . . . . . . . . . . .6-24

MAC 3500 Top Cover Kit, pn 2030899-001 . . . . . . . . . . . . . . . . .6-26

Harness Kit for MAC 3500, pn 2030871-001 . . . . . . . . . . . . . . . .6-27

MAC 3500 KISS Pump Hardware Kit, pn 2030872-001 . . . . . . . .6-28

Appendix A – Technical Specifications

Instrument Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

Communications with MUSE System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

Display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

Writer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

Keyboard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

Electrical . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

Physical . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

Environmental . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

Trolley . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-6

Magnetic Card Reader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-6

Standard Barcode Scanner . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-6

Advanced Barcode Scanner . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-7

vi MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 9

Appendix B – Electromagnetic Compatibility

Electromagnetic Compatibility (EMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-3

Guidance and Manufacturer’s Declaration - Electromagnetic Emissions . . .B-3

Guidance and Manufacturer’s Declaration - Electromagnetic Immunity . . . .B-4

Guidance and Manufacturer's Declaration - Electromagnetic Immunity . . . .B-5

Recommended Separation Distances . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-6

EMC-Compliant Cables and Accessories . . . . . . . . . . . . . . . . . . . . . . . . . . .B-7

Index

Revision D MAC™ 3500 resting ECG analysis system vii

2021337-036

Page 10

viii MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 11

1 Introduction

Revision D MAC™ 3500 resting ECG analysis system 1-1

2021337-036

Page 12

For your notes

1-2 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 13

Manual Information

Revision History

Each page of the document has the document part number and revision

letter at the bottom of the page. The revision letter identifies the

document’s update level. The revision history of this document is

summarized in the table below.

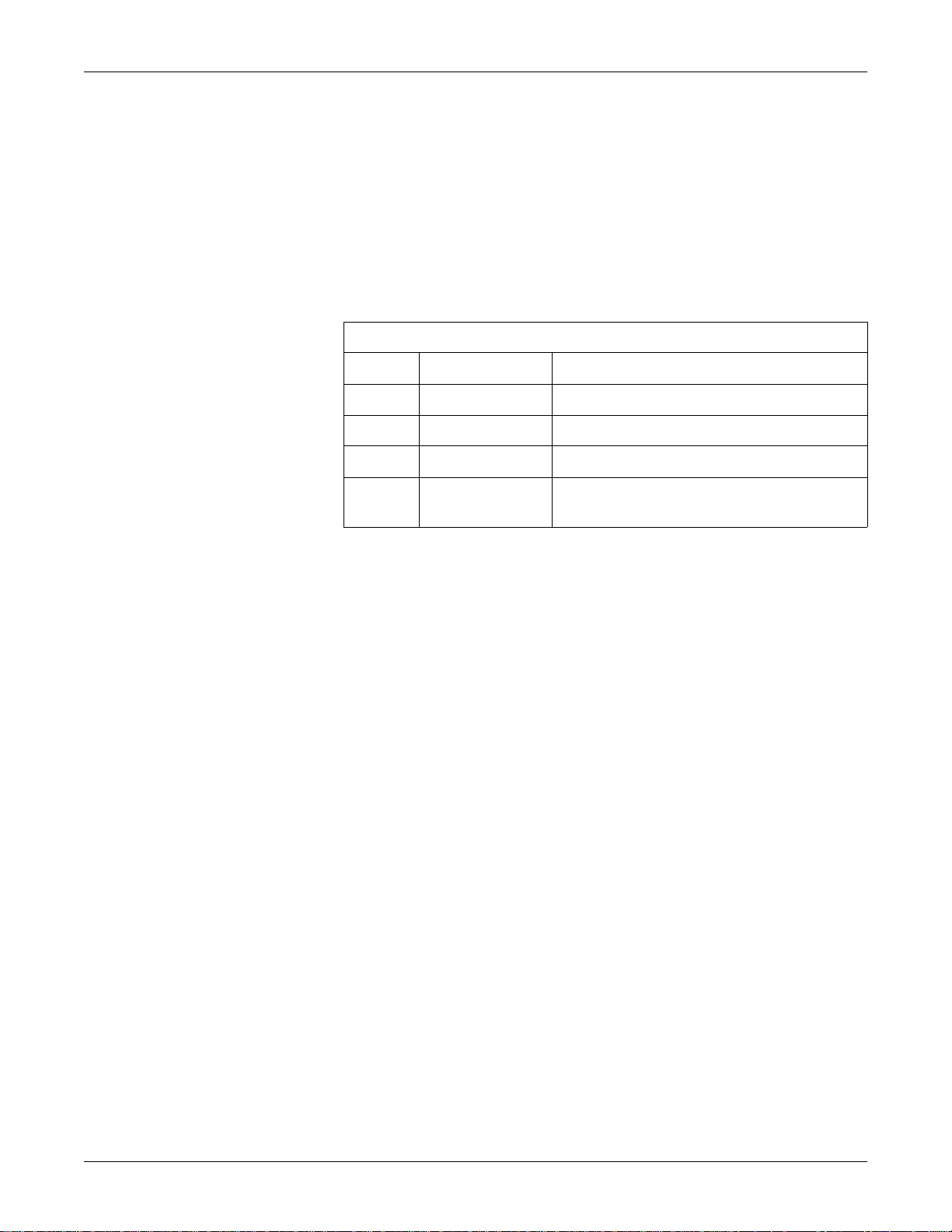

Revision Date Comment

Introduction: Manual Information

Table 1. Revision History, PN 2021337-036

A 1 August 2006 Initial release of document.

B 14 December 2006 Added FRUs for MobileLink Silex serial server.

C 1 February 2007 Edited EMC section for IEC 60601-2-51 compliance.

D 10 October 2008 Added -007 board, 009C SD Card and -002 Comm

PC board. Included Functional Checkout Procedure.

Manual Purpose

Intended Audience

This manual supplies technical information for service representative

and technical personnel so they can maintain the equipment to the

assembly level. Use it as a guide for maintenance and electrical repairs

considered field repairable. Where necessary the manual identifies

additional sources of relevant information and or technical assistance.

See the operator’s manual for the instructions necessary to operate the

equipment safely in accordance with its function and intended use.

This manual is intended for the person who uses, maintains, or

troubleshoots this equipment.

Revision D MAC™ 3500 resting ECG analysis system 1-3

2021337-036

Page 14

Introduction: Warnings, Cautions, and Notes

Warnings, Cautions, and Notes

The terms danger, warning, and caution are used throughout this

manual to point out hazards and to designate a degree or level or

seriousness. Familiarize yourself with their definitions and significance.

Hazard is defined as a source of potential injury to a person.

Term Definition

DANGER Indicates an imminent hazard which, if not avoided, will result in death or

serious injury.

WARNING Indicates a potential hazard or unsafe practice which, if not avoided, could

result in death or serious injury.

CAUTION Indicates a potential hazard or unsafe practice which, if not avoided, could

result in minor personal injury or product/property damage.

NOTE Provides application tips or other useful information to assure that you get

the most from your equipment.

1-4 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 15

Safety Messages

Introduction: Safety Messages

Additional safety messages may be found throughout this manual that

provide appropriate safe operation information.

DANGER

Do not use in the presence of flammable anesthetics.

WARNINGS

This is Class 1 equipment. The mains plug must be

connected to an appropriate power supply.

Operate the unit from its battery if the integrity of the

protective earth conductor is in doubt.

CAUTIONS

This equipment contains no serviceable parts. Refer

servicing to qualified service personnel.

U.S. Federal law restricts this device to the sale by or on

the order of a physician.

Responsibility of the Manufacturer

GE Medical Systems Information Technologies is responsible for the

effects of safety, reliability, and performance only if:

Assembly operations, extensions, readjustments, modifications,

or repairs are carried out by persons authorized by us.

The electrical installation of the relevant room complies with the

requirements of the appropriate regulations.

The equipment is used in accordance with the instructions for

use.

Revision D MAC™ 3500 resting ECG analysis system 1-5

2021337-036

Page 16

General

Introduction: Safety Messages

The intended use of this device is to record ECG signals from surface

ECG electrodes. This device can analyze, record, and store

electrocardiographic information from adult and pediatric populations.

This data can then be computer analyzed with various algorithms such

as interpretive ECG and signal averaging for presentation to the user.

This device is intended for use under the direct supervision of a licensed

health care practitioner.

Failure on the part of the responsible individual, hospital, or institution

using this equipment to implement a satisfactory maintenance schedule

may cause undue equipment failure and possible health hazards.

To ensure patient safety, use only parts and accessories manufactured or

recommended by GE Healthcare.

Contact GE Healthcare for information before connecting any devices to

this equipment that are not recommended in this manual.

If the installation of this equipment, in the USA, will use 240 V rather

than 120 V, the source must be a center-tapped, 240 V, single-phase

circuit.

Parts and accessories used must meet the requirements of the applicable

IEC 60601 series safety standards, and/or the system configuration must

meet the requirements of the IEC 60601-1-1 medical electrical systems

standard.

The use of ACCESSORY equipment not complying with the equivalent

safety requirements of this equipment may lead to a reduced level of

safety of the resulting system. Consideration relating to the choice shall

include:

use of the accessory in the PATIENT VICINITY; and

evidence that the safety certification of the ACCESSORY has

been performed in accordance to the appropriate IEC 60601-1

and/or IEC 60601-1-1 harmonized national standard.

1-6 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 17

Equipment Symbols

For a list and examples of the symbols that appear on the equipment and

packaging, refer to the MAC™ 3500 Resting ECG System Operator

Manual (PN

Introduction: Equipment Symbols

2021337-035).

Revision D MAC™ 3500 resting ECG analysis system 1-7

2021337-036

Page 18

Service Information

Service Requirements

Refer equipment servicing to GE authorized service personnel only. Any

unauthorized attempt to repair equipment under warranty voids that

warranty.

It is the user’s responsibility to report the need for service to GE or to one

of their authorized agents.

Equipment Identification

The serial number label is located inside the device as shown in the

following illustration.

Introduction: Service Information

SERIAL NUMBER

SERIAL NUMBER

LABEL

LABEL

Every GE Healthcare device has a unique serial number for

identification. The serial number is formatted as shown in

Number Format” on page 1-9.

NOTE

The examples shown are representative only. Your product label

may

differ.

“Serial

9A

1-8 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 19

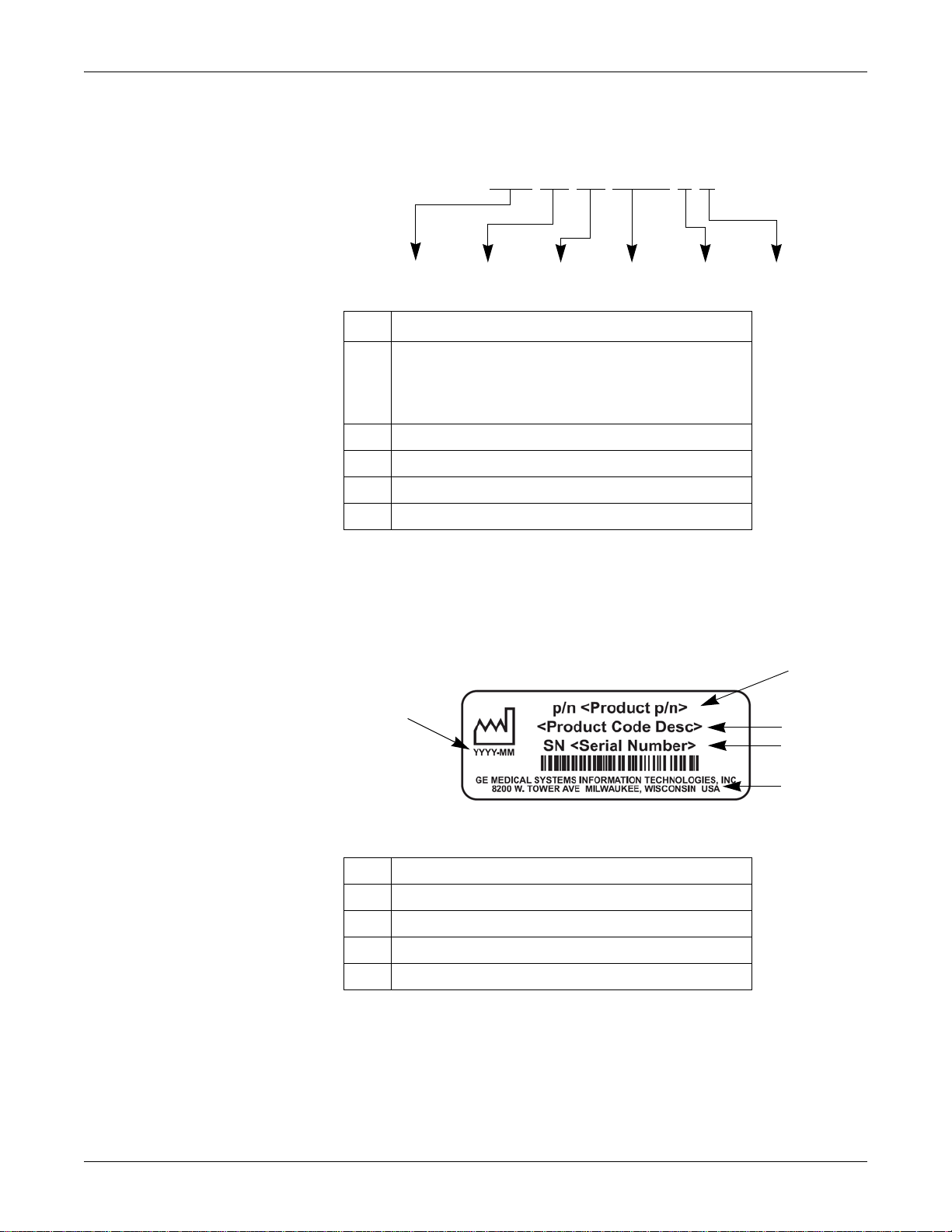

Serial Number Format

Introduction: Service Information

### ## ## #### # #

ABCDEF

Table 2. Serial Number Format

1

A

Product code

B Year manufactured (00-99)

06 = 2006

07 = 2007

(and so on)

C Fiscal week manufactured

D Production sequence number

E Manufacturing site

F Miscellaneous characteristic

Label Format

1. The product code for the MAC 3500 described in th is

manual is SCA.

B

A

C

D

E

Table 3. Equipment Identification Label

A Date of manufacture in YYYY-MM format

B Part number of product

C Product code description

D Serial number (described above)

E Manufacturing site

Revision D MAC™ 3500 resting ECG analysis system 1-9

2021337-036

Page 20

Introduction: Service Information

1-10 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 21

2 Equipment Overview

Revision D MAC™ 3500 resting ECG analysis system 2-1

2021337-036

Page 22

For your notes

2-2 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 23

Equipment Overview: General Description

General Description

The MAC™ 3500 resting ECG analysis system is a 12-lead, 12-channel

system with a 6.5 inch (165 mm) diagonal display, active patient cable,

and battery operation. There are also options for communication

capabilities.

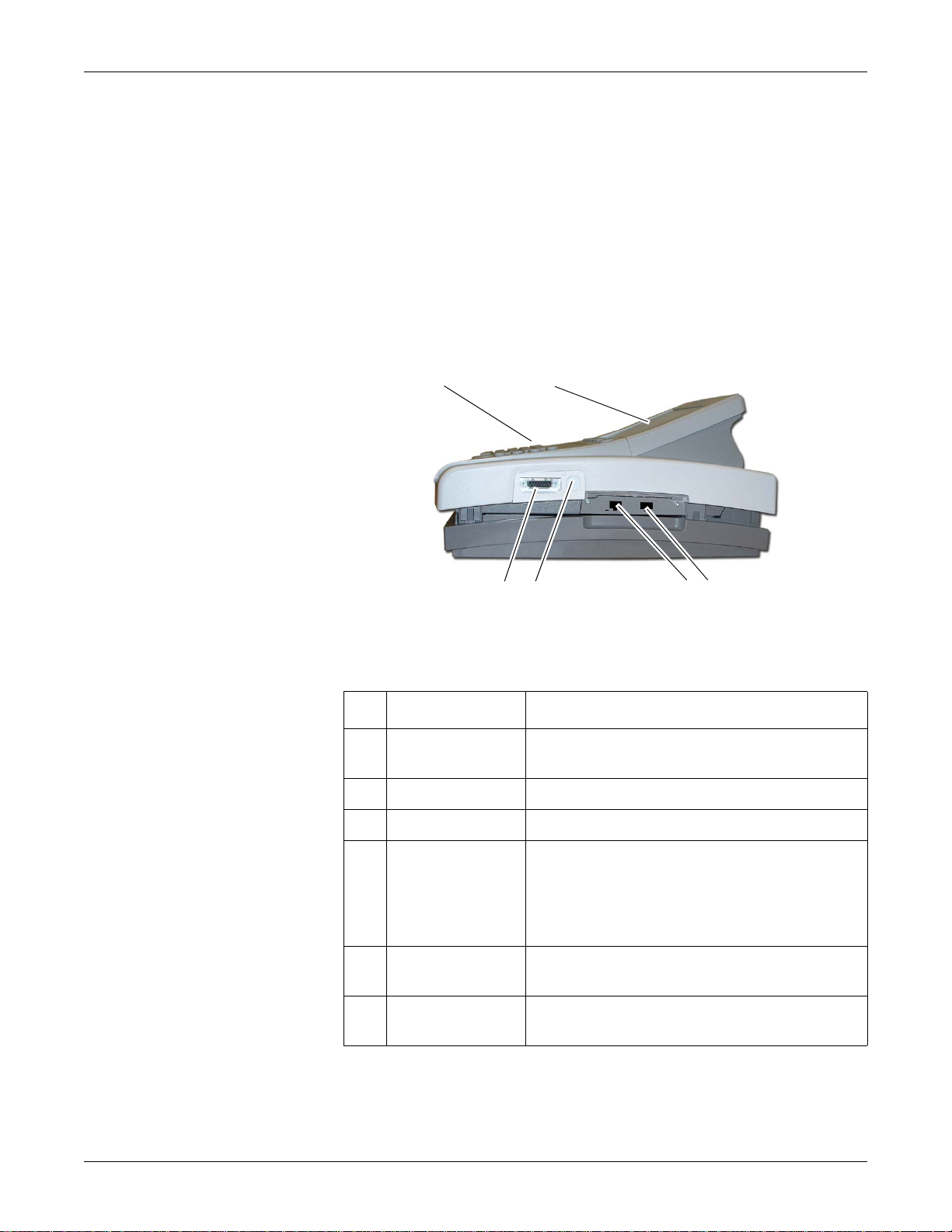

Side View

A

F

Name Description

A keyboard Press the keyboard keys to control the system or to enter

B display screen View the waveform and text data.

C modem port Connect the telephone cable here (optional feature)

E

data.

B

CD

104A

D LAN port Connect to the LAN here (optional feature)

The green LED on the right side of this port indicates

a

good ethernet link.

The amber LED on the left side of this port flashes to

indicate network traffic.

E KISS pump

connector

F ECG signal input

connector

Revision D MAC™ 3500 resting ECG analysis system 2-3

2021337-036

Connect the KISS pump here (optional feature).

Connect the patient cable here.

Page 24

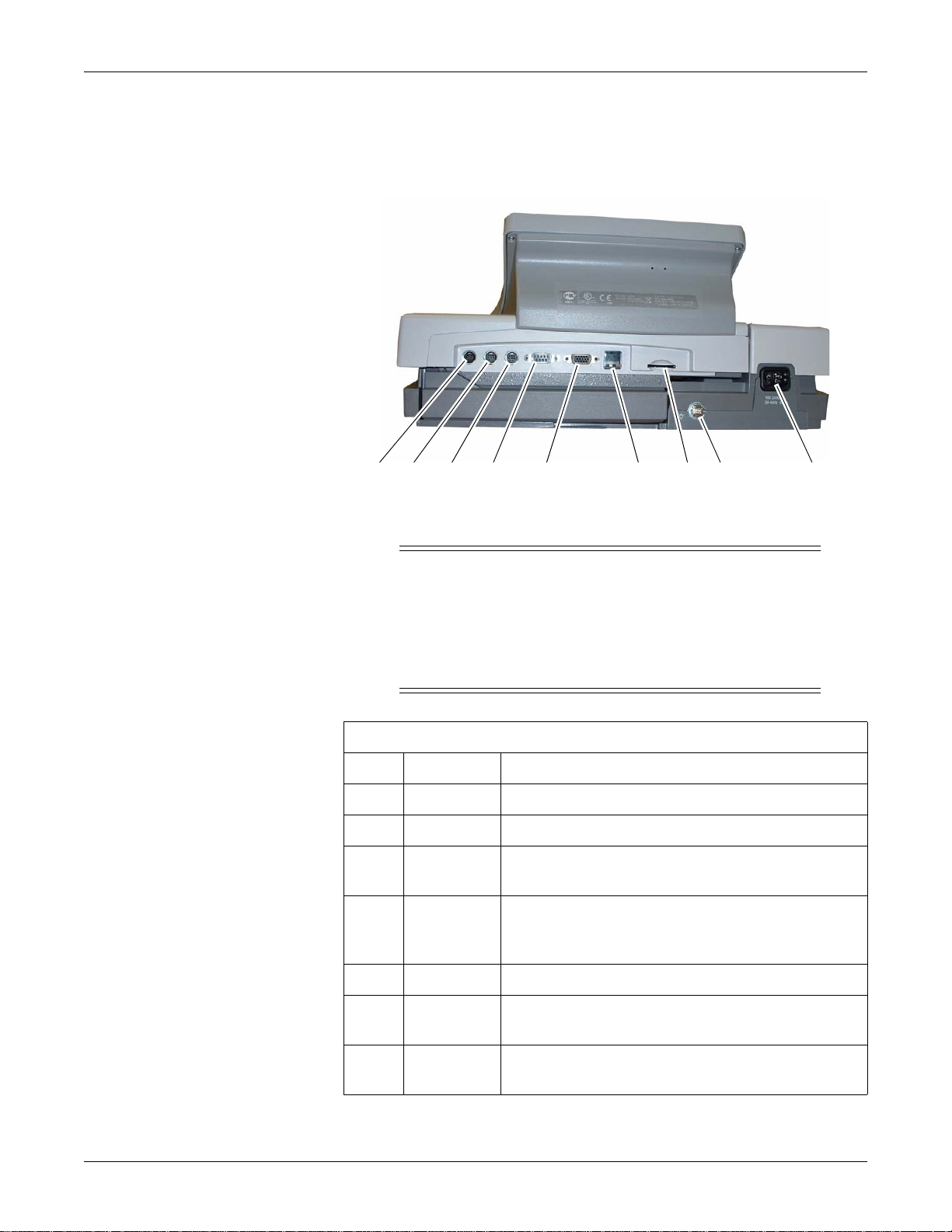

Back View

Equipment Overview: General Description

105A

A BCD

Name Description

A back panel connectors Connect peripheral devices here.

B Secure Digital card slot Insert Secure Digital card for external storage here.

C ground lug Connect non-grounded peripheral devices to ensure

equipotential.

D main AC power Insert the main AC power cable.

2-4 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 25

Equipment Overview: Connector Identification

Connector Identification

A BC D E F GH I

WARNING

LEAKAGE CURRENT – Keep leakage current within

acceptable limits when connecting auxiliary equipment

to this device.

Total system leakage must not exceed 300 microamperes

(United States) or 500 microamperes (international).

Table 4. Back Panel Connectors

Item Name Description

A A Connect an optional card reader or optional bar code reader

B 1 External GE KISS pump connection.

C 2 Connect a local transmission cable, serial line, modem, or client

bridge (wireless option).

D ANA/TTL Connect a device requiring analog data or TTL trigger

(ultrasound, stress echo, ergometer, analog treadmill, blood

pressure units, etc.).

106A

E EXT.VID. Connect an external video display.

F IR Point at a MAC 5000, MAC 5500, MAC 3500, or MUSE

system’s IR transceiver to transmit or receive ECG data.

G card slot Insert the system card into this slot to archive or restore data

from external media or to update software.

Revision D MAC™ 3500 resting ECG analysis system 2-5

2021337-036

Page 26

Equipment Overview: Connector Identification

Table 4. Back Panel Connectors (Continued)

H ground lug Connect non-grounded peripheral devices to ensure

equipotential.

I main AC power Insert the main AC power cable.

2-6 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 27

Equipment Overview: Detailed Description

Detailed Description

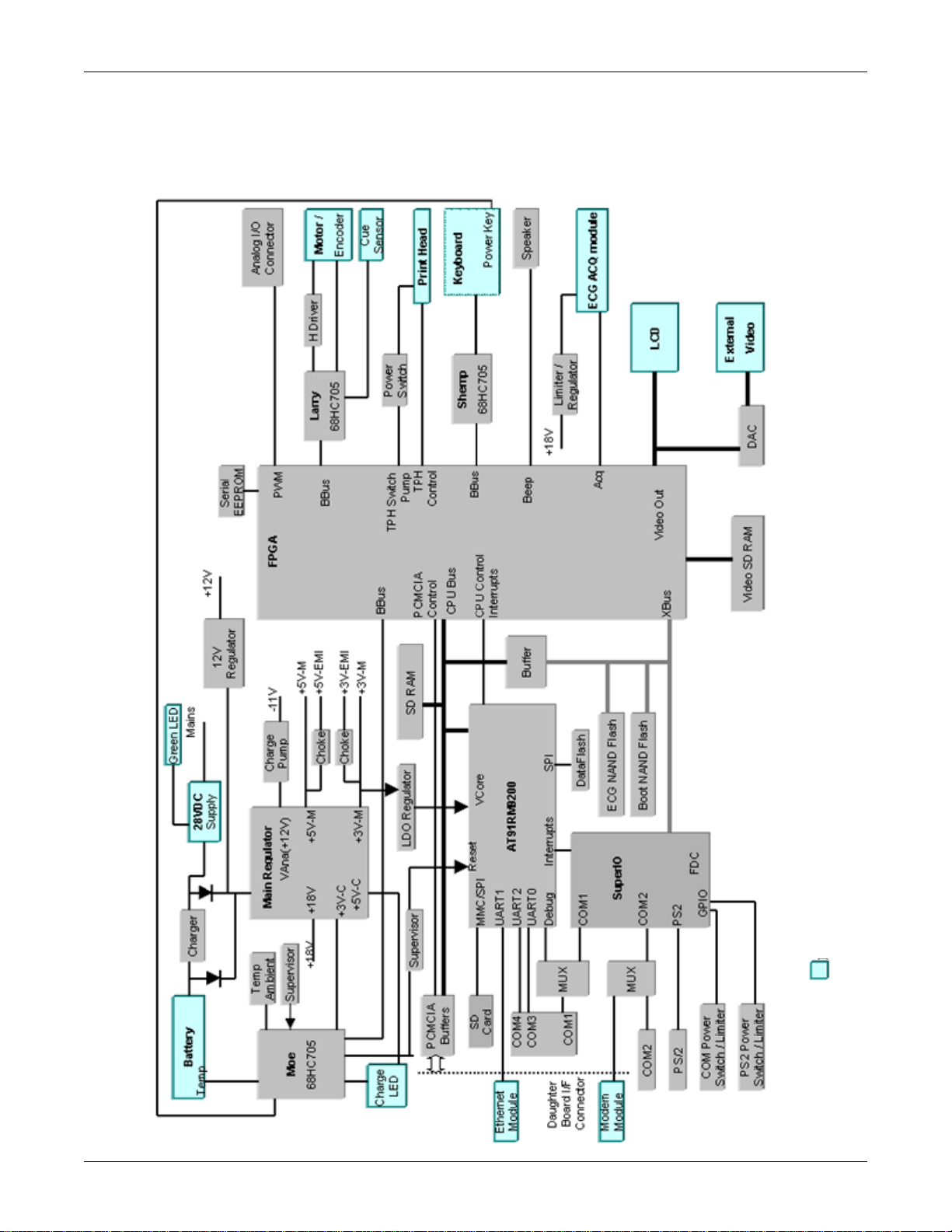

Block Diagram

MAC 3500 Basic Block Diagram

Not part of motherboard

79A

Revision D MAC™ 3500 resting ECG analysis system 2-7

2021337-036

Page 28

Equipment Overview: Theory of Operation

Theory of Operation

Overview / Block Diagram

The MAC 3500 CPU board contains all of the circuitry for the MAC™

3500 resting ECG analysis system except for the line power supply,

acquisition module, keyboard and display. Although the MAC 3500 runs

software derived from products based on the Max-1 architecture

(running on the C-Exec operating system), it has almost nothing in

common with that hardware family. Components listed in this section

refer to the 801212-007 CPU board assembly.

The CPU board contains the following:

64 MB SDRAM (holds both code and data)

32 MB SDRAM acts as video frame memory

32 MB NAND Flash (holds FPGA configuration and system code)

32 MB NAND Flash for ECG Record storage

128 KB Boot Data Flash (holds primary boot image)

CRT video DACs

External 12 Volt Power Switch

Acquisition Module Transceiver / Power Switch

Printhead Power Switches and Pixel Test Circuit

Daughter Board Interface which support LAN and modem

Switch Mode Power Supplies

3.3 Volt for Logic, LCD

5 Volt for Logic, Printer,

12 Volt for LCD backlight, External Com Port Power

Battery Charger

-12 Charge Pump for Analog Circuits

Linear Power Supplies

1.8 Volt (AT91RM9200 Core and FPGA Core)

2.5 Volt Reference

3.3 Volt for System Supervisor (Moe Stooge)

12 Volt for Analog Circuits

Crystals / Clocks

24 MHz Oscillator for FPGA

32.768 Khz Real Time Clock for Super IO chip.

32.768 Khz (AT91RM9200)

18.432 Mhz (AT91RM9200)

4 Mhz (3 devices, 1 for each Stooge)

2-8 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 29

Equipment Overview: Theory of Operation

Atmel AT91RM9200 CPU Containing:

Incorporates the ARM920T™ ARM® Thumb™ Processor

- 200 MIPS at 180 MHz, Memory Management Unit

- 16-KByte Data Cache, 16-KByte Instruction Cache,

Write

Buffer

- In-circuit Emulator including Debug Communication

Channel

- Mid-level Implementation Embedded Trace Macrocell

(256-ball BGA Package Only)

Low Power: 30.4 mA on VDDCORE, 3.1 mA in Standby Mode

Additional Embedded Memories

- 16K Bytes of SRAM and 128K Bytes of ROM

External Bus Interface (EBI)

- Supports SDRAM, Static Memory, Burst Flash, Glueless

Connection to CompactFlash®, SmartMedia

NAND

System Peripherals for Enhanced Performance:

Flash

™ and

- Enhanced Clock Generator and Power Management

Controller

- Two On-chip Oscillators with Two PLLs

- Very Slow Clock Operating Mode and Software Power

Optimization Capabilities

- Four Programmable External Clock Signals

- System Timer Including Periodic Interrupt, Watchdog and

Second Counter

- Real-time Clock with Alarm Interrupt

- Debug Unit, Two-wire UART and Support for Debug

Communication Channel

- Advanced Interrupt Controller with 8-level Priority,

Individually Maskable Vectored Interrupt Sources, Spurious

Interrupt Protected

- Seven External Interrupt Sources and One Fast Interrupt

Source

- Four 32-bit PIO Controllers with Up to 122 Programmable

I/O Lines, Input Change Interrupt and Open-drain

Capability on Each Line

- 20-channel Peripheral Data Controller (DMA)

Multimedia Card Interface (MCI)

- Automatic Protocol Control and Fast Automatic Data

Transfers

- MMC and SD Memory Card-compliant, Supports Up to Two

SD Memory Cards

Three Synchronous Serial Controllers (SSC)

- Independent Clock and Frame Sync Signals for Each

Receiver and Transmitter

- I 2 S Analog Interface Support, Time Division Multiplex

Support

- High-speed Continuous Data Stream Capabilities with 32-bit

Data Transfer

Revision D MAC™ 3500 resting ECG analysis system 2-9

2021337-036

Page 30

Equipment Overview: Theory of Operation

Four Universal Synchronous/Asynchronous Receiver/

Transmitters (USART)

- Support for ISO7816 T0/T1 Smart Card

- Hardware and Software Handshaking

- RS485 Support, IrDA Up To 115 Kbps

- Full Modem Control Lines on USART1

Master/Slave Serial Peripheral Interface (SPI)

- 8- to 16-bit Programmable Data Length, 4 External

Peripheral Chip Selects

Two 3-channel, 16-bit Timer/Counters (TC)

- Three External Clock Inputs, Two Multi-purpose I/O Pins per

Channel

- Double PWM Generation, Capture/Waveform Mode, Up/

Down Capability

FPGA Containing:

XBus Controller

LCD Controller with SDRAM Frame Buffer.

Video Waveform Scroller

Interrupt Controller

System Interrupt Generator

Acquisition Module Interface

Thermal Printhead Interface

Serial EEPROM Interface

BBus Controller

Four PWM Analog Outputs

Beep Generator

PC Card Interface

A PC Super I/O controller containing:

Two Serial Ports (one dual mode RS-232 / IrDA)

Clock/Calendar (Y2K compliant)

PS-2 Keyboard Port (for card and barcode readers)

Floppy Disk Controller

Three Peripheral Microcontrollers (The Three Stooges):

System Supervisor / Battery Charger-Gauge (Moe)

Printer Motor Controller / Analog Input (Larry)

Keyboard Interface (Shemp)

2-10 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 31

Power Supplies

+3V-C

Equipment Overview: Theory of Operation

The MAC™ 3500 resting ECG analysis system requires several regulated

voltages for operation of its various components. The Main Regulator

provides most of the supply rails. The supply rails are:

MAC™ 3500 resting ECG analysis system is never truly “off.” The system

supervisor microcontroller (MOE) must constantly monitor the power

key and perform battery charging/gauging. The clock/calendar in the

Super I/O chip must also maintain time/date when the machine is off.

These functions are powered from the +3V-C rail, which provides power

continuously from the battery pack regardless of the state of the rest of

the system. The Main Regulator produces +3V-C directly from the

battery rail via an internal low current linear regulator. Only 5mA are

available from +3V-C, so it must be used sparingly.

NOTE

The MAX782’s low current regulator is dreadfully inefficient.

Regulator Q current appears to be about 3x the load current. This

makes conservation of load on +3V-C crucial.

+3V-M

+3V-EMI

+5V-M

+5V-EMI

Most of the MAC 3500 hardware runs from +3V-M. The MAX782

provides this rail from the battery via a PWM synchronous switching

regulator. Moe controls +3V-M in tandem with +5V-M.

This is simply an RF blocked feed from +3V-M. +3V-M load is contained

within the CPU board. Power for devices for external functions is

supplied by +3V-EMI. The isolation of +3V-EMI from +3V-M may be

unnecessary as the concept has never been tested for its effect.

The MAC™ 3500 resting ECG analysis system is not fully in the 3V age.

The Super I/O and thermal printhead require 5V power. The MAX782

provides this rail via another PWM synchronous switching regulator.

Moe controls +5V-M in tandem with +3V-M.

Similar to +3V-EMI, this rail is an RF blocked feed from +5V-M, used to

power devices for external functions. The isolation of +5V-EMI from

+5V-M may be unnecessary as the concept has never been tested for its

effect.

Revision D MAC™ 3500 resting ECG analysis system 2-11

2021337-036

Page 32

+18V

+1.8V

+12V

Equipment Overview: Theory of Operation

The Main Regulator’s 5V switching output also supports generation of a

non-regulated 18V rail, which is used to provide power for the acquisition

module. By providing the acquisition module with 11.5V linearly

regulated power from the +18V rail of the main regulator rather than the

main 12V regulator (U17), acquisition is not affected by excessive current

draw from the printer motor or external loads on the COM ports

(especially the KISS pump). The acquisition module's power

requirements are modest, so efficiency is not a pressing concern and the

lower efficiency of this approach is acceptable.

The Atmel CPU and FPGA (Xilinx Spartan 2) operates their internal

core logic at 1.8V, while their I/O ring runs at the system standard 3.3V.

The 1.8 Volt regulator, a low dropout linear regulator, drops +3V-M to

1.8V for use as a core supply.

REF2V5

The paper motor drive circuit, LCD backlight and external COM ports all

require 12V. The Main Regulator’s 18V output cannot provide sufficient

current for all of the systems 12V loads, so a secondary 12V regulator is

required. The Main 12V Regulator (U17), a switching buck regulator,

provides the higher currents needed by these loads. A P-channel

MOSFET (Q1) switch precedes the regulator to provide on/off control.

Gate capacitor C12 slows the turn on/off time of the MOSFET switch to

eliminate switching transients. The voltage divider created by R133,134

prevents the full supply rail from being impressed across Q1’s gate when

on. This protection is necessary, as the maximum Vgs of the MOSFET is

less than the peak supply voltage.

The high power rails are neither precise nor quiet enough to be used as

the reference for analog input/output or internal measurement circuits.

The Analog Reference Regulator (U50), a 2.5V shunt regulator, provides

a quiet and stable reference voltage for such purposes. VREF is derived

from +5V-EMI rather than +3V-EMI to minimize the change in reference

current with changes in input rail voltage. The difference between 5V

and 2.5V is three times greater than the difference between 3.3V and

2.5V. If the absolute ripple on both supplies is the same, the modulation

of reference current will be 3 times less if power is derived from +5V.

2-12 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 33

VAna+, VAna-

Clocks

Super I/O and FPGA

Equipment Overview: Theory of Operation

The analog output circuitry is powered by a low current switched 12V

rail, provided by the Main Regulator. VAna+ provides the positive supply

for the output op-amps. A charge pump voltage inverter is provided to

produce an approximate -11V rail for the op-amps. Although only the

ECG output is bipolar, all output amplifiers are driven from VAna-.

A

short circuit on either of the unipolar DC outputs could load VAnasufficiently to affect the negative peak swing of the ECG output. The

ECG and DC outputs are not required to operate correctly in the

presence of abnormal loads.

Both of these devices use the 24 Mhz clock oscillator Y5 to drive their

internal requirements for various clock frequencies. The main function of

the Super I/O IC is for serial port communication and real time clock; all

the needed timing comes from this oscillator. The FPGA provides many

functions including the acquisition interface, the printer interface, and

the Stooges interface (Bbus) to name a few. The FPGA uses a built-in

frequency doubler to raise this 24 Mhz clock to 48 Mhz for internal use.

All functions inside the FPGA use the clocks derived from 48MHz. The

main derived clocks are:

1 MHz for acquisition interface

4 MHz for printer data shift clock interface.

4 MHz for EEPROM data shift clock

24MHz for VGA LCD panel clock.

The VGA LCD controller, that include the SDRAM frame buffer

controller use 59.904 MHz external memory clock from ATMEL CPU in

addition to the 48MHz FPGA clock

CPU ATMEL AT91RM9200

The ATMEL AT91RM9200 has two oscillators. Slow Clock oscillator and

Main Oscillator. The Slow Clock Oscillator uses 32,768 KHz crystal for

clock generation. The CPU runs in Slow Clock mode (@48MHz) after

system reset. Slow Clock is also used by the built-in RTC. But the -006

and -007 boards do not use the ATMEL RTC for the system timing

requirements. The Main oscillator uses 18.432 MHz crystal. Processor

clock (179.712 MHz), Master clock (59.904) for external Bus Interface

and Peripheral Clocks are derived from the main oscillator by the Master

Clock Controller.

Revision D MAC™ 3500 resting ECG analysis system 2-13

2021337-036

Page 34

CPU (Stooges)

RTC

CPU

Equipment Overview: Theory of Operation

Each of the three Stooges has its own 4 Mhz ceramic resonator for use in

generating their respective clocks.

The Real Time Clock of the system is provided as a part of the Super I/O

controller. The timing for this function is derived from its own 32.768

Khz crystal.

The ATMEL AT91RM9200 replaces the Strong ARM SA1110 used in

-005 board. The AT91RM9200 uses high performance, low power

consumption and high code density ARM920T processor core. One of the

major difference between SA1110 and AT91RM9200 is the absence of

built in LCD controller and 16-bit static memory controller. StrongARM

support 32 bit memory interface. The Processor Clock and External Bus

speed is limited to 180 and 80 MHz when compare with the 206 and 103

MHz of StrongARM. But having an external LCD controller with a

separate video memory interface compensates overall performance of the

-006 board.

External Bus Interface

The external bus interface width is limited to 16bit in ATMEL CPU

when compare with the 32 bit interface of StrongARM. All the non VGA

FPGA registers are either 8 bit or 16 bit wide. However all these were

accessed using 32 bit access in -005 board and aligned to 32 bit word. To

port the applications that was written for the 32 bit access, all the Non

VGA memory space within the FPGA are accessed in 32 bit mode in -006

board. When the ATMEL static memory controller see a 32 bit memory

access, it perform two consecutive 16 bit access. To avoid over writing of

FPGA register with upper 16-Byte data, The FPGA register access logic

is designed in such a way that, the FPGA ignores upper 16 byte access.

However for access to the pixel data FIFO, the upper 16 bit contains

valid data and the this will be loaded into the next 16 bit word.

The VGA registers are accessed using 32 bit access. The Frame Buffer

area can be accessed either in 32 bit word mode or byte mode.

2-14 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 35

Boot Loader

Equipment Overview: Theory of Operation

In the -005 board, after power ON, the FPGA gets configured using the

micro controller Curly. The FPGA emulate the boot ROM and the start

up code was placed in the Boot ROM from the smart media card by the

micro controller Curly.

The ATMEL AT91RM9200 has built in boot program in the internal

ROM. The -006 and -007 boards utilize the ATMEL CPU itself for

bringing up the board. Since the service of Curly is no longer required, it

is removed from the board. At power ON if the BMS pin is high, ATMEL

starts executing boot code in the internal ROM. The boot program looks

for valid code in SPI data flash (U66) and if found, downloads the

program into SRAM and starts executing from SRAM after remap. The

-006 and -007 boot program loads primary boot code into the SDRAM

after initializing it. The primary boot program reads the PCB ID code

from three port pins and then searches the NAND Flash for a matching

FPGA configuration image (pages with ID “Xn” where n is the 3-bit PCB

ID code 1-8 plus one). Once located, the configuration image is loaded

into the FPGA in fly by fashion. Blinking of LED DS3 at 1 Hz indicates

successful completion of FPGA configuration. The primary boot program

then loads the secondary boot code from NAND to SDRAM and transfers

the control to the secondary boot program. Buffer U55 is used to get the

direct CPU access to NAND Flash. To configure the FPGA in fly-by

mode, the data needs to be present at the Xbus while toggling CCLK.

This is achieved by toggling the NAND_RE* alternately with CCLK. The

NAND_RE* needs to be under the GPIO control instead of static memory

controller to do this. The ALE and CLE are also controlled in GPIO mode

and tied to low level during read cycle while configuring the FPGA. The

CLE and ALE acts as address line A23 and A25, respectively, during

Address and command cycle as well as access other than FPGA

configuration. The reason for omitting A24 is because of AT91RM9200

silicon bug. The A24 does not work like an address pin. It can work only

as GPIO line.

The primary boot code also contains the application for software update.

If there is no valid code in the NAND FLASH, the primary boot code

looks for SD Card and if detected it down load the code from the SD Card

to NAND Flash and reset the system. If the primary boot code can not

detect a valid code within 2 minutes 6 seconds, ‘Moe’ shuts down the

system. The status of software update is indicated on DS1 and DS2. The

DS1 and DS2 are not visible once the top cover is in place. The ‘Moe’

flashes amber charge LED at 1Hz to indicate that software update is in

progress. But it can not provide the completion status. Refer the table

below for the status messages from LEDs DS1 and DS2 during primary

boot software update.

DS1 Red DS2 (Green) Status

Off Flashing No SD card detected for software updated

Off‘ On Copying image files from SD card to SDRAM

Revision D MAC™ 3500 resting ECG analysis system 2-15

2021337-036

Page 36

Equipment Overview: Theory of Operation

DS1 Red DS2 (Green) Status

Off Off Erasing and / or formatting the NAND Flash.

Applicable only during the software update

process.

On Off Programming the NAND Flash

Flashing Flashing Successful completion of programming

Flashing Off Error - Could program all the image files. But

error in programming the status page 'Z0'.

On On Error - Could not program all the image files

as well as the status page 'Z0'.

On Flashing Error - Could not program all the image files.

But the status page 'Z0' updated successfully

A copy of primary boot program (pages with ID “Bn” where n is the 3-bit

PCB ID code 1-8) is kept in NAND flash. This is updated whenever

software update happens. For -006 and -007 boards, the FPGA image

and Primary boot code image IDs are X3 and B3 respectively.

FPGA Internal Logic

The primary boot program can do a forceful software update, even if a

valid program is present in the NAND Flash, by using a special SD Card,

which has a file, update.com, in the root directory. The service menu

provides a provision to update the SPI data flash with the primary boot

program copy residing the NAND Flash.

All of the MAC™ 3500 resting ECG analysis system’s proprietary

hardware is contained in a single Xilinx FPGA that contains:

XBus Controller

Video Interface

LCD Controller with SDRAM frame buffer

Video Waveform Scroller

Interrupt Controller

System Interrupt Generator

Acquisition Module Interface

Thermal Printhead Interface

Serial EEPROM Interface

BBus Interface

Four PWM Analog Outputs

Beep Generator

2-16 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 37

Board ID Register

Equipment Overview: Theory of Operation

The following descriptions give an overview of the FPGA’s functionality.

For detailed information on the internal circuitry, refer to the schematic.

For a programmer’s eye view of the FPGA, see the source file

“hardware.h”. Where appropriate, circuitry external to the FPGA is

also

described.

It is necessary to identify versions/revisions of the CPU board

automatically in the field. The ATMEL primary boot code read the boot

ID port pins to identify the FPGA image and startup code required for

the board. The board ID register contains a hardwired three bit code

that tracks the FPGA image number, indicating to the ATMEL just

which FPGA image has been loaded. Three additional FPGA inputs are

reflected in this register to allow further refinement of the board

identity. Resistors (R98 and R99 through R129) are used to program the

board ID.

Board ID Code Versions of the 801212 CPU Board assembly

000h -001, -002

XBus Controller

Video Interface

001h -003

002h -004 (not used)

003h -005

004h not used

005h -006

006h -007

To reduce loading on the high speed processor address and data busses,

a

slow speed byte bus is provided for peripheral interface. The Super I/O

controller and NAND Flash ICs are both located on this bus. Unlike the

3.3V only main data/address busses, XBus is compatible with both 5V

and 3.3V logic. To maintain software compatibility with previous board

versions, the low order address byte is not used by XBus. Starting XBus

addressing with A8 also produces Super I/O addresses that easily map to

their standard PC equivalents (simply append 0x00 to a datasheet Super

I/O address offset to get a MAC 3500 Super I/O address offset).

LCD Controller with SDRAM Frame Buffer

Continuing problems with LCD controller part obsolescence have made

implementation of a controller design in the FPGA attractive. The MAC

3500 GUI software does not depend on sophisticated video functionality,

so an FPGA implementation of a suitable display controller can be

reasonably compact. By implementing the controller in the FPGA (using

Revision D MAC™ 3500 resting ECG analysis system 2-17

2021337-036

Page 38

Equipment Overview: Theory of Operation

the VHDL hardware description language) obsolescence is avoided, and

future upgrades are easily implemented.

The LCD controller is comprised of these functional blocks:

Video Timing Generator (See “Video Timing” on page 2-18)

SDRAM Frame Buffer Controller (See “SDRAM Frame Buffer

Controller” on page 2-18)

Format pack/unpack logic (See “Format pack/unpack logic” on

page 2-19)

Line buffer (See “Line Buffer” on page 2-20)

Fill Engine (See “Fill Engine” on page 2-20)

Main State Machine (See “Main State Machine” on page 2-21)

Interrupt management (See “Interrupt Management” on page 2-22)

Video Timing – The LCD controller generates video pixel and line

timing from a 60Mhz clock inside the FPGA. The timing generator

consists of one counter for timing pixels within a line (including

generation of horizontal sync, horizontal front and back porches, and

LCD data enable timing) and another for timing lines with a frame

(including generation of vertical sync, vertical front and back porches

and generation of Line FIFO fill requests). In addition, the timing

generator increments a memory address register by the line pitch (640)

at the beginning of each video line, so the Line FIFO knows where to get

the next line of pixels. The controller produces fixed timing for a 640x480

LCD, and requires no initialization to produce that timing. Support for

future, higher resolution displays, can be obtained by modifying the

source code for the controller itself, providing the most efficient hardware

implementation possible.

SDRAM Frame Buffer Controller – The LCD obtains pixel data from

a 1Mbyte region of a 32Mbyte, 16-bit wide synchronous DRAM

(SDRAM). The SDRAM buffer is shared by the display controller and the

CPU, allowing system software to directly manipulate screen pixels.

At power-up, SDRAMs must be configured for proper operation.

Properties such as RAS/CAS latency and burst length are written into a

control register in the SDRAM, and an initial burst of refresh cycles are

performed to prepare the memory array for operations. The SDRAM

controller does this all automatically at startup, requiring no

initialization by the CPU.

SDRAMs, being dynamic, require periodic refresh to maintain the

contents of the memory array. The SDRAM controller performs this

refresh automatically between accesses. All details of SDRAM bank

management and page boundary crossing are managed automatically in

the SDRAM controller. In addition, through the use of pipelining, the

SDRAM controller allows burst accesses to and from SDRAM at full

memory speed. All details of burst cycle management, including setup

and page boundary crossings, are handled transparently by the SDRAM

controller. The SDRAM memory clock is derived from the CPU memory

clock, and is passed out of the FPGA and back in to allow one of the

FPGA’s on-board DLLs to “zero out” all internal FPGA delays. This delay

compensation allows the SDRAM controller to operate reliably at very

high speeds (>= 100Mhz).

2-18 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 39

Equipment Overview: Theory of Operation

Format pack/unpack logic – The MAC 3500 display architecture is

based on the division of pixels into static and dynamic planes. As

discussed elsewhere, this technique allows the smooth scrolling of ECG

waveforms across the screen while buttons, annotations and other

graphics remain stationary. Previous generations of MAC 5000 display

controllers packed the five bits of each static plane pixels into the same

byte of memory as the three bits from the corresponding dynamic plane

pixel. In that scheme, pixel manipulations required the CPU to read the

combined pixel, modify either the static or dynamic component, and

write the result back to memory. Such read-modify-write operations are

time consuming.

In contrast, the FPGA implementation of the frame buffer takes

advantage of SDRAMs high speed, large size, individual byte

addressability, and 16-bit width, to access both the static (5 bits) and

dynamic (3 bits) portions of a pixel separately, and simultaneously.

The

SDRAM bus is effectively split into a “dynamic byte lane” and a

“static byte lane”. The resulting improvement in drawing algorithm

speed is substantial.

The 16-bit wide bus of the SDRAM allows each read/write cycle to access

two bytes of data. During writes, upper and lower byte strobes allow

independent writing of either or both bytes. During reads, both bytes are

always presented. Unneeded read data bits are ignored by the CPU. The

LCD controller takes advantage of the individual accessibility of the

bytes to eliminate the need for the CPU to pack and unpack the static

and dynamic pixels. At the expense of unused memory bits (a small

expense as less than 1/16th of the entire SDRAM space is needed at all)

the LCD controller maps the 5 bits of each static pixel into one SDRAM

byte lane (the static lane), and the 3 bits of each static pixel into the

other (the dynamic lane). Unused bits in each lane are written as zeroes,

and ignored on reading.

On the CPU side, the SDRAM frame buffer appears as two regions, the

static and dynamic planes. Each plane is a contiguous array of 480 lines

of 640 pixels each. Within the static plane, the lower 3 bits (the dynamic

bits) of each pixel byte are ignored on writes, and read as zeroes. Within

the dynamic plane, the upper 5 bits of each pixel byte (the static bits)

are

ignored on writes and read as zeroes. The dynamic plane is located

1/2 Mbyte above the static plane and address bit A19 is used to

differentiate between them. The interface from the LCD controller to the

CPU is 16-bits wide, allowing two pixel bytes to be moved in each read/

write cycle.

In the 16-bit wide SDRAM, each word (independently byte addressable)

contains both a static and a dynamic pixel byte, each in their own lanes.

When the CPU writes a pixel to the static plane, the upper five bits of the

byte are routed to the static byte lane (the lower three bits are set to

zero) and the dynamic byte lane is disabled. When the CPU reads a static

pixel, both the static and dynamic byte lanes are accessed, but only the

upper five bits of the static byte lane are passed on to the CPU (the lower

three bits are zeroed). Access to the dynamic plane proceed in much the

same manner, with the appropriate bits being routed to the dynamic byte

lane while the static byte lane is disabled.

Revision D MAC™ 3500 resting ECG analysis system 2-19

2021337-036

Page 40

Equipment Overview: Theory of Operation

Because each 16-bit word of SDRAM contains one pixel, and each 16-bit

access of the CPU into the frame buffer contains two, the LCD controller

must pack/unpack pixels on the fly. During writes, if the CPU signals a

single byte write, the LCD controller writes the byte onto the proper lane

(as determined by A19) of one memory word. If the CPU signals a two

byte write, the LCD controller queues a two cycle burst write into two

consecutive words of SDRAM. On reads, the LCD controller always reads

two pixels from memory and packs them into a single word for access by

the CPU, which may use both pixels, or ignore one.

By design, SDRAMs are faster when data can be moved in sequential

bursts. The Atmel ARM CPU asynchronous bus interface does not

support burst accesses, so the opportunity to burst is limited. The LCD

controller does take advantage of the 16-bit wide nature of the

asynchronous bus to allow bursts of two pixels into and out of memory

when possible. This nearly doubles frame buffer bandwidth over a

byte-at-a-time interface. Finally, as mentioned previously, the CPU is

able to manipulate individual pixels in either plane without resorting to

read-modify-write access cycles. This provides another twofold

improvement in memory bandwidth.

Line Buffer – Within each line of LCD video data, bytes must move

from the frame buffer to the scroller/CLUT in an unbroken stream at

48Mhz. Although the frame buffer is capable of burst transfers of

60Mpixels/sec, it cannot be depended on to maintain that speed for more

than one SDRAM page (256 pixels). At page boundaries, the SDRAM

must initiate a new page access, and potentially satisfy refresh

requirements. Since video lines are longer (640 pixels) than SDRAM

pages, some mechanism is required to smooth the flow of pixels from the

frame buffer to the LCD.

This smoothing is provided by a 1024 byte dual port line buffer,

implemented in a pair of FPGA block RAMs. At the end of each active

LCD line, the video timing generator requests a new line of pixels from

the frame buffer. The memory arbiter services the request by bursting

640 pixels from the frame buffer to the line buffer, using the video

address supplied by the timing controller. The entire line of 640 pixels is

moved at maximum memory speed, taking a little over 11μs to complete

at 60Mhz. The pixels are then clocked out of the line buffer and

presented to the scroller/CLUT at a constant 24Mhz, taking about 30μs

per line. Double buffering is not required, as the burst fill rate far

exceeds the 24Mhz drain rate, and the fill begins during the generation

of horizontal sync, giving the controller plenty of head start on filling the

line buffer before the timing generator begins draining them out.

To keep the control logic simple, and minimize SDRAM access overhead,

each 640 pixel line is transferred from SDRAM in one transaction. This

does hold off the ARM CPU for up to 11μs at a time, but as the ARM CPU

does not access the frame buffer often, this is not thought to be an issue.

Fill Engine – The 3500 routinely draws rectangular regions on screen

for use in dialog boxes and buttons. When drawn by the CPU, frame

buffer bandwidth becomes an issue, as random accesses to the SDRAM

buffer are inefficient, and many of them are required to fill large regions

of the display. To reduce both CPU and frame buffer loading, the LCD

controller provides a simple fill engine which automates the filling of

2-20 MAC™ 3500 resting ECG analysis system Revision D

2021337-036

Page 41

Equipment Overview: Theory of Operation

rectangular regions of the frame buffer, and takes advantage of the burst

capabilities of the SDRAM.

The fill engine interface is simple, consisting of four boundary registers

to define the fill region, and one register to record the fill value, and

planes to be filled. The fill engine can fill any value into any rectangular

region of the display in either or both planes simultaneously. The

bounding values (top, bottom, left, right) define the rectangle to be filled

in screen coordinates, with 0,0 at the upper left, and 639,479 at the

bottom right. The fill value contains both the dynamic (5) and static (3)

pixel bits as well as two plane enable bits.

After loading the boundary control registers, the CPU initiates the fill by

writing the requested fill value and plane enable bits to the fill value

register. The fill is then queued for the next video frame and the fill

engine becomes “busy”.

Fills are implemented synchronous with frame refresh. At the

completion of each line buffer fill request from the video timing generator

the fill engine checks to see if a fill is underway. If so, the current video

line position (from the timing generator) is compared to the top and

bottom boundary registers. If the current line is between the top and

bottom, the fill engine adds the left boundary value to the current line

memory address (as provided by the timing generator) and proceeds to

write the fill value into memory until the address matches the right

boundary. Depending on the width of the filled rectangle, fill bursts can

take anywhere from 100ns to 11μs.

In this way, the fill engine follows the video timing generator down the

screen, replacing pixels in the frame buffer immediately after they are

sent to the LCD. This synchronous operation makes efficient use of the

existing address generation hardware and provides “flicker-free” fills,

regardless of region size. If fills were unsynchronized, they would often

cross two successive display frames and result in visible tearing or

flicker. As a result of this frame synchronous operation, fills always take

one frame time, regardless of their size, and complete coincident with the

end of the frame.

Main State Machine – The SDRAM frame buffer is constantly in

demand by the CPU, the video timing controller and the fill engine. The

CPU manipulates pixels in the frame buffer in real time to construct the

visible display while the video timing controller manages the constant

stream of pixels from the frame buffer into the line buffer, and on to the

scroller/CLUT. At the same time, any requested fills must access the

frame buffer to write the requested fill region. When all three contend for

access to the frame buffer simultaneously, memory bandwidth can

exceed 100Mbytes/sec.

The Main State Machine manages all these competing requests on a

priority basis, with display refresh taking top priority, followed by fills

and finally CPU accesses. The state machine runs at 60Mhz, processing

line buffer fill requests from the video timing generator, fill requests

from the fill engine and read/write requests from the CPU. The 5.3 pack/

unpack logic and fill engine logic are actually various states of the Main

State Machine.

Revision D MAC™ 3500 resting ECG analysis system 2-21

2021337-036

Page 42

Equipment Overview: Theory of Operation

Interrupt Management – The LCD controller produces two interrupts

to notify the CPU of the completion of important tasks. At the end of the

active region of each display frame, the controller can generate an

interrupt to tell the CPU it has uncontested access to the frame buffer for

a short period, and to synchronize display related processes in the CPU

(such as waveform drawing and scrolling control). A similar interrupt is

provided to signal the completion of fills. Both interrupts may be

disabled and/or acknowledged in the system control registers.

Video Waveform Scroller

There are numerous ways of achieving a scrolling waveform, none of

which is supported by standard LCD controllers. The MAC 3500 provides

scrolling through FPGA hardware placed between the LCD controller

output and the LCD panel input.

To produce the scrolling effect it is necessary to maintain two virtual

image planes, one atop the other. Static (stationary) objects are drawn in

the static plane, which appears nearest the viewer and may be either

opaque or transparent. Dynamic (scrolling) objects are drawn in the

dynamic plane, which appears behind the static plane and is always

opaque, though not necessarily visible. The appearance of motion is

achieved by continuously changing the start point for display of the

dynamic plane from one video frame to the next.

Since the LCD controller does not support multiple image planes, it is

necessary to pack two planes of image data into a single frame buffer. On

the software side (during drawing) this is done by bit masking operations

that allow separate manipulation of two virtual pixels in each byte of

frame buffer memory. Each 8-bit byte holds a pair of pixels, one from the

static plane and one from the dynamic plane.

On the hardware side, part of each frame buffer byte (the static plane) is

played directly into the LCD after suitable color mapping. The remainder

of the byte (the dynamic plane) is stored in a 1 line temporal buffer before

being displayed. The amount of delay applied to the line buffer before

merging it with the static image data determines its placement on the

screen. By gradually changing the delay, the dynamic image can be made

to scroll.

Color Lookup Table (CLUT)

Generally the dynamic plane is filled with waveforms and perhaps a few

characters of text. The static plane often contains text messages, icons,

buttons and graphics. The greater variety of object types displayed in the

static plane demands a wider range of colors. For this reason, each video

data byte is split asymmetrically into five bits of static pixel data and

three bits of dynamic pixel data. This has come to be known as 5.3

format.

The 5.3 format provides a palette of 2^3=8 colors for dynamic objects and

(2^5)-1=31 colors for static objects (1 of the colors is transparent, leaving

31 real colors). In practice, to “freeze” dynamic objects in the static plane

requires that the 8 dynamic colors be replicated in the static color map,

leaving only 31-8=23 new colors available for static objects. The FPGA