Page 1

5

4

3

2

1

Foxconn Precision Co.Inc.

Date:2004/03/01

D D

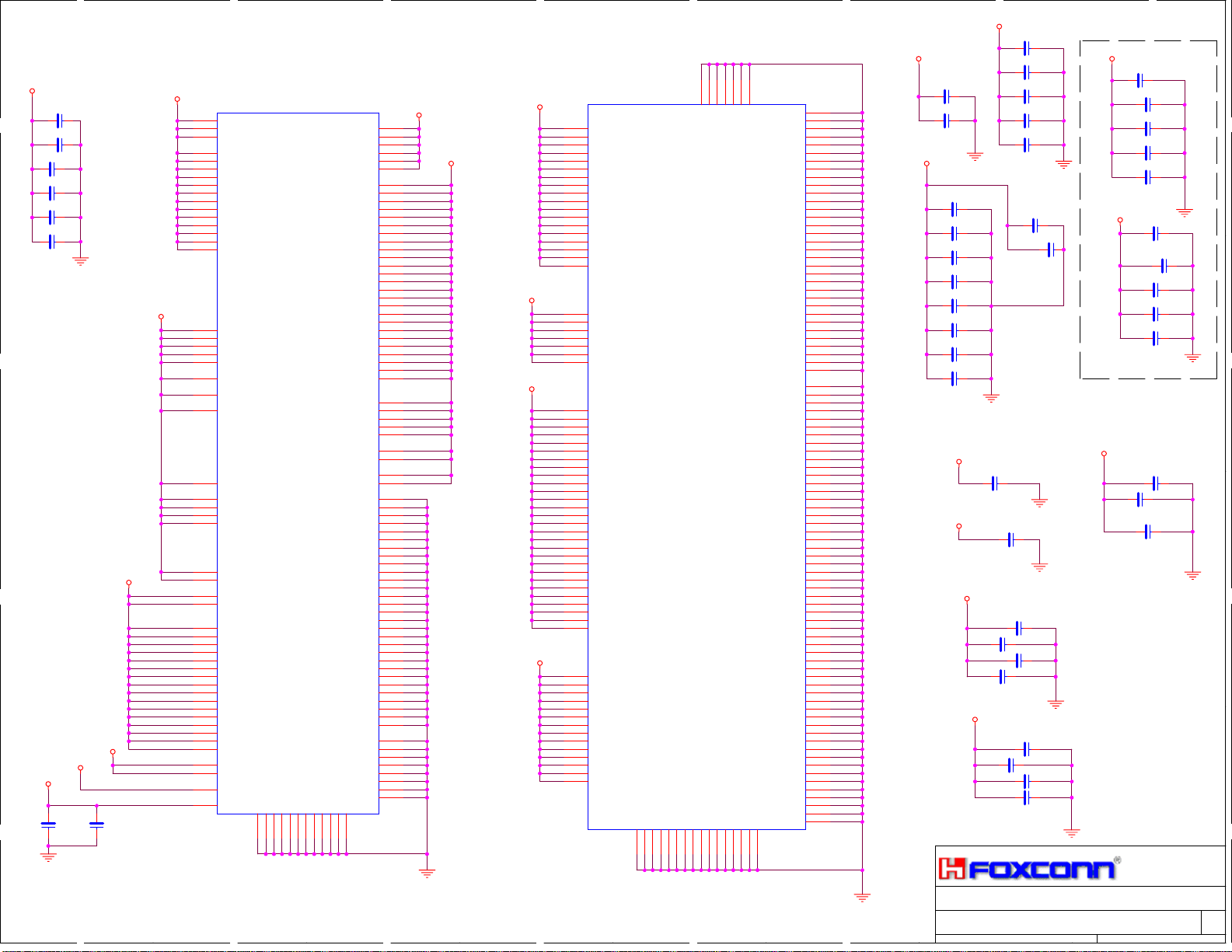

PAGE INDEX

748A01

01. Index Page

02. Topology

03. Reset Map

04. Clock Distribution

05. Power Delivery Map

06. CPU-1

C C

07. CPU-2

08. CPU-3

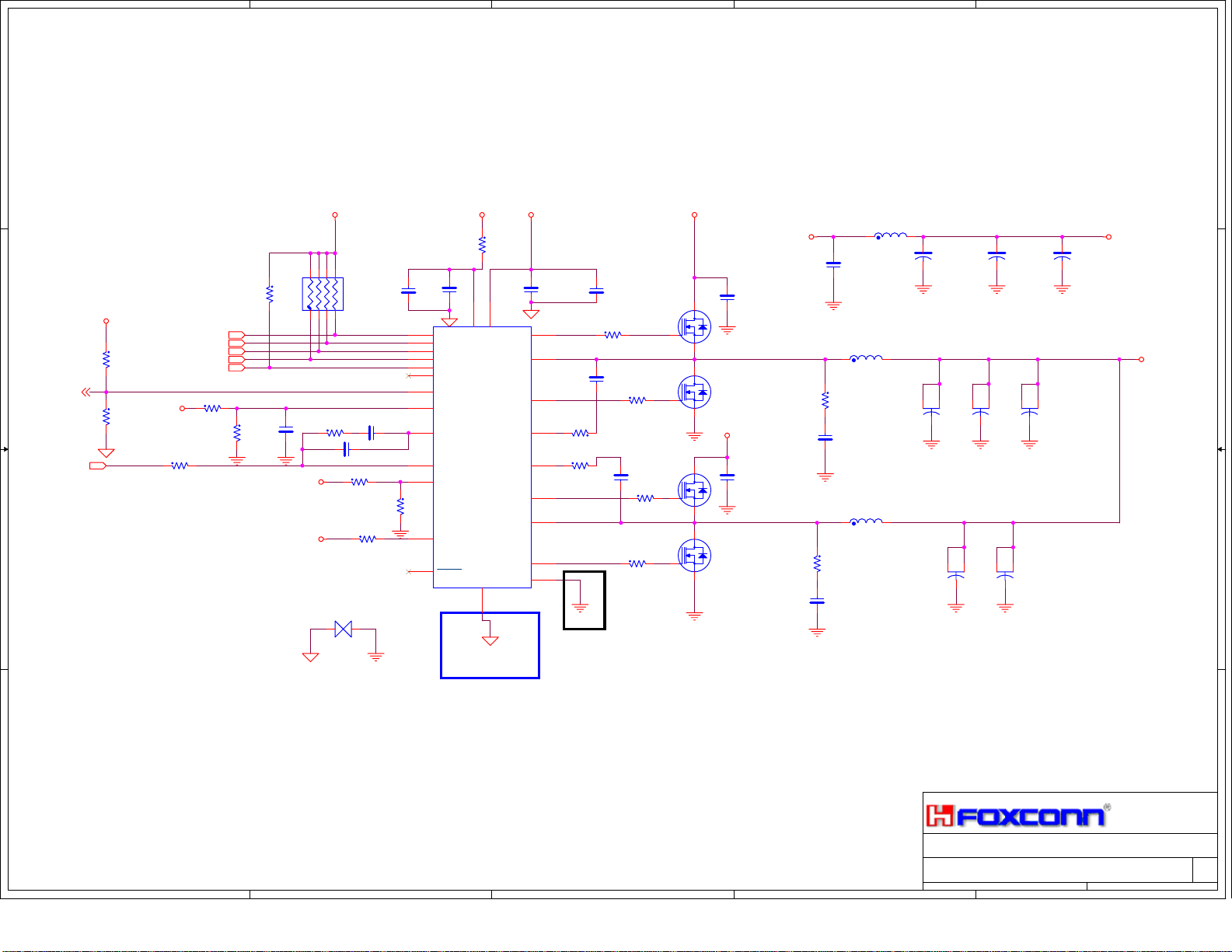

09. ISL6563 VCCP

10. ISL6563 VCCP

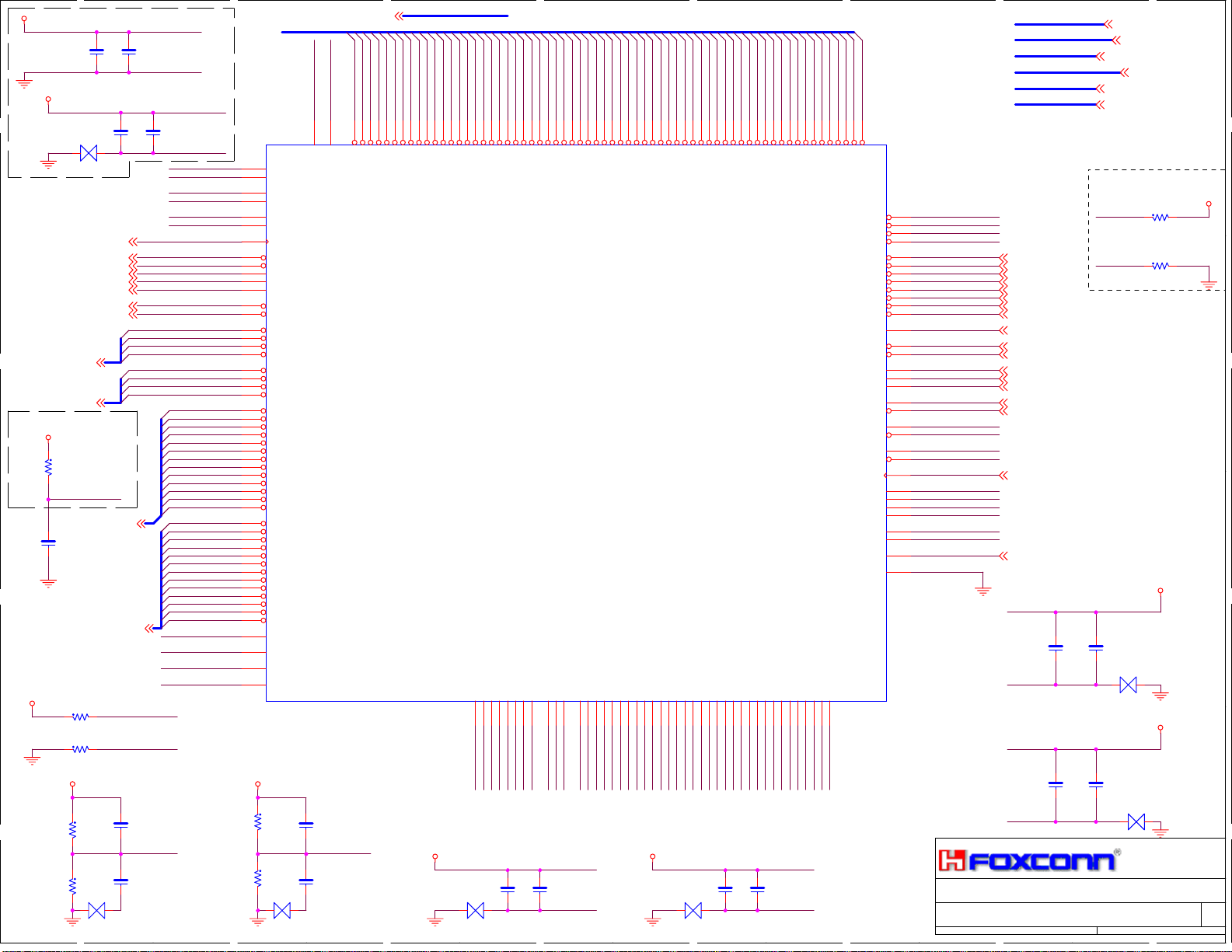

11. 748-1(Host/AGP)

12. 748-2 Memory

13. 748-3 MuTIOL/Other

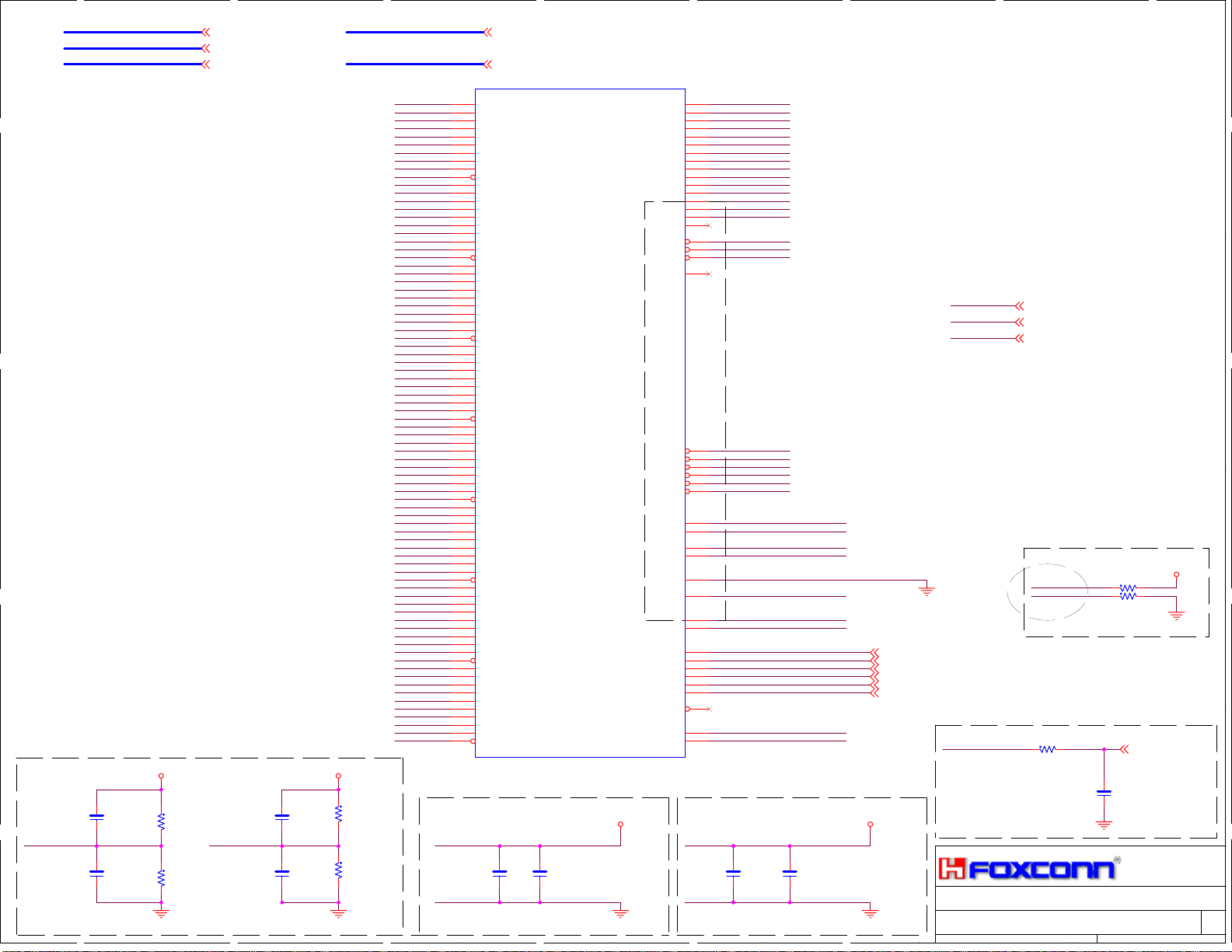

14. 748-4 Power

15. 2.5V_DDR & 1.25V_VTT

B B

16. SB1.8V & SB3V & 5V_DUAL

17. 1D8V_VCC & VDDQ

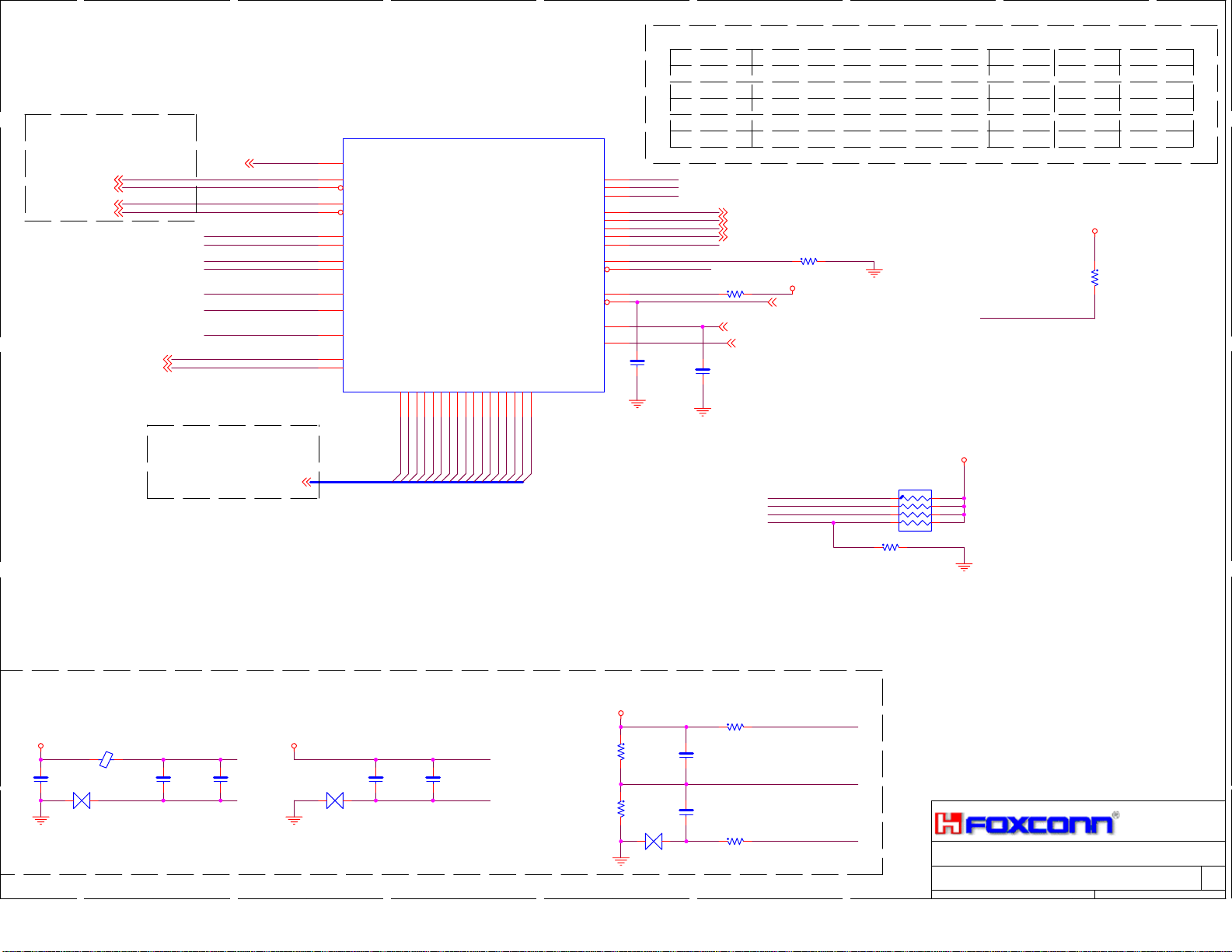

18. Hardware Trap*

19. Main Clock Generator

20. Clock Buffer-1(3DDR/MIX)

21. DDR/MIX DIMM1,2

22. DDR/MIX DIMM3

23. SSTL-2 Termination Res

24. AGP.SCH

25. SIS964-PCI, IDE, MUTIOL

26. SIS964-LPC/MII/GPIO

27. SIS964-USB, SATA

28. SIS964-POWER

29. PCI 1&2.SCH

30. PCI 3&4.SCH

31. PCI5.SCH

32. VT6307

33. USB Header & 1394 Port

34. LAN POWER

35. RTL8110S/RTL8100C

36. LAN & USB PORT

37. IDE.SCH

38. AC97 CODEC.SCH

39. AC97 I/O

40. ITE8705

41. Keyboard Mouse.SCH

42. FAN HW Monitor

43. BIOS/FLOPPY

44. COM/PRT PORT

45. Power BTN/RTC Batt.SCH

46. Power Connector

47. GPIO Setting

48. Change list

A A

Title

Document Number Re v

5

4

3

2

Date: Sheet

Index

748A01

TECHNOLOGY COPR.

148Sunday, September 05, 2004

1

A

of

Page 2

5

4

3

2

1

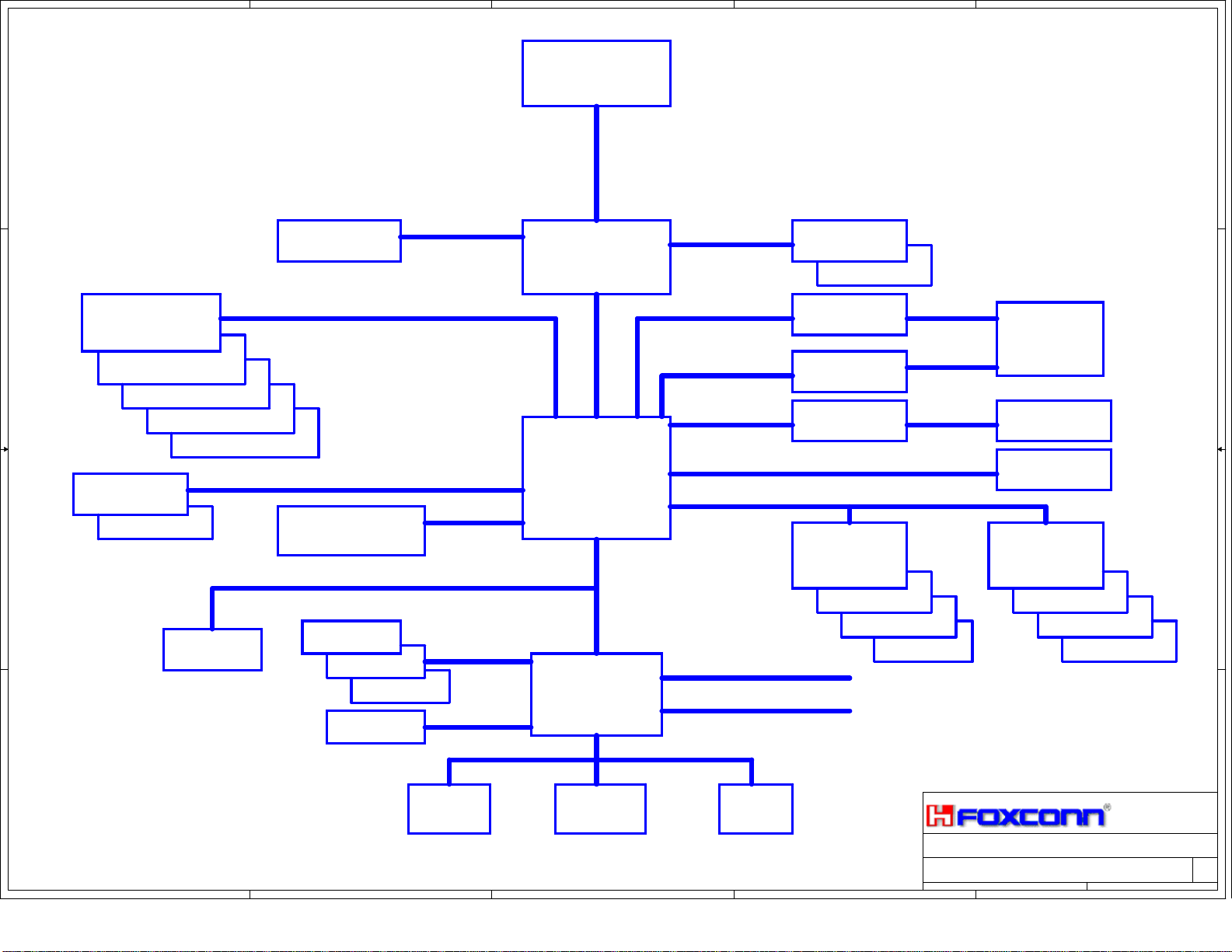

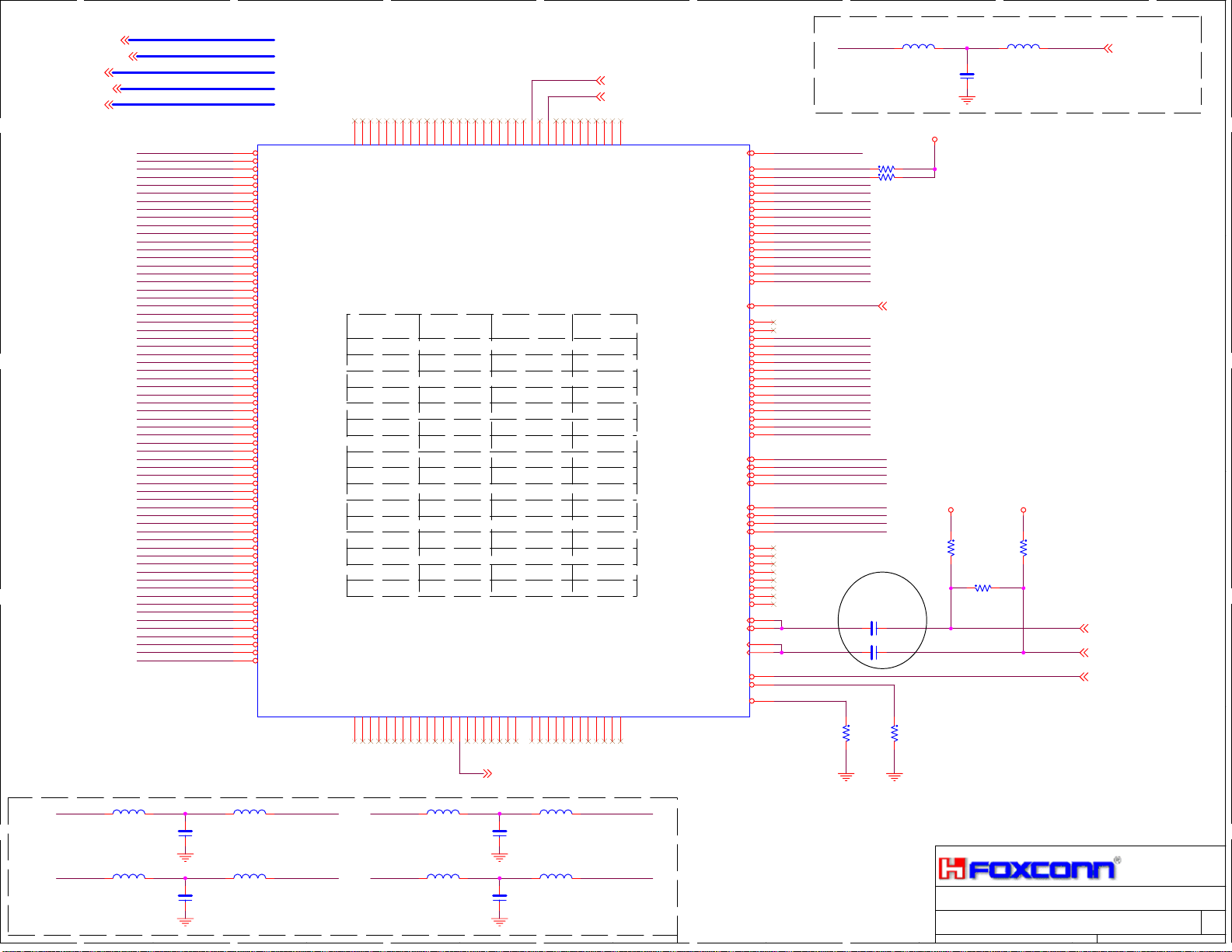

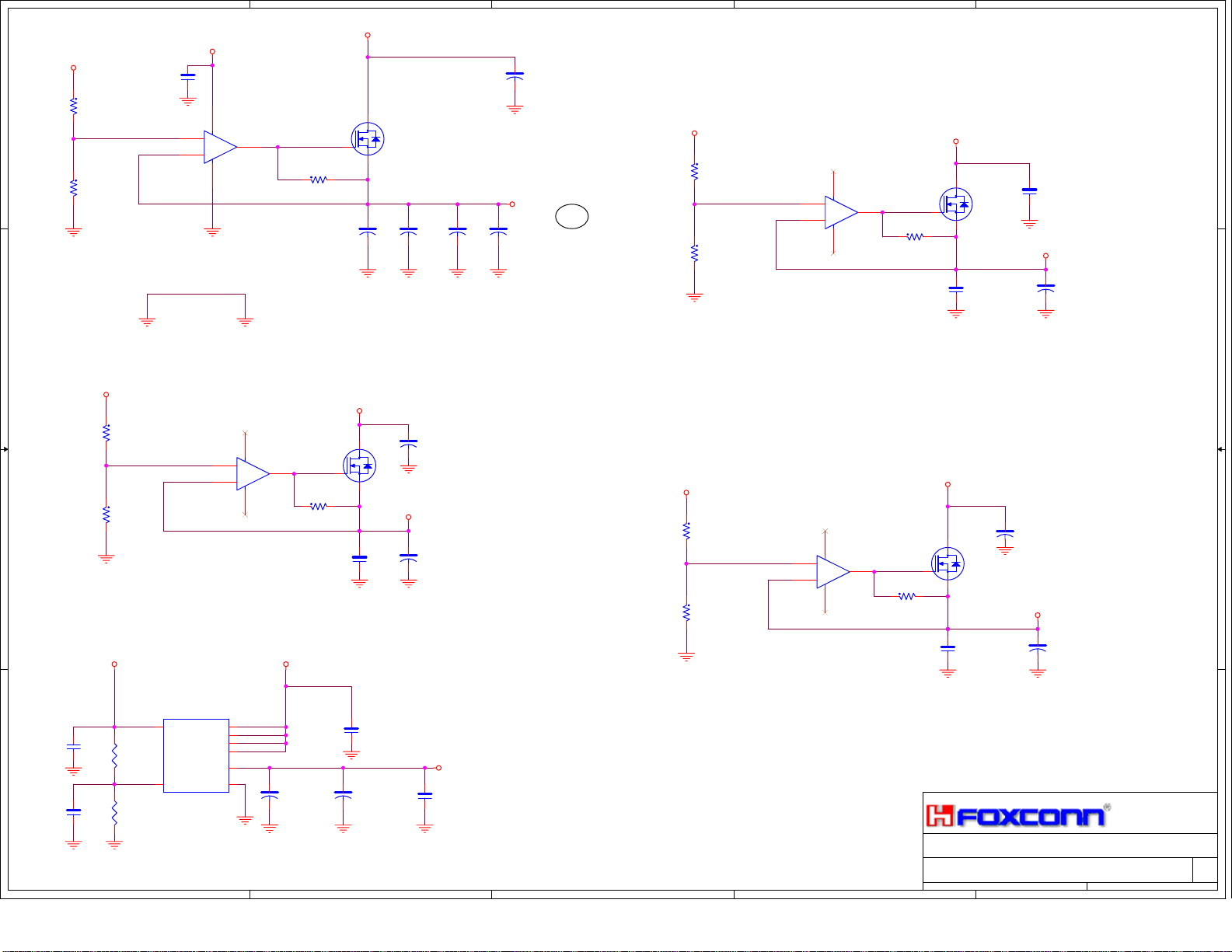

AMD K7

D D

Host Bus

AGP SLOT

DDR SDRAM

CHANNEL A

SiS748

CHANNEL B

PCI Slot 1

C C

PCI Slot 2

PCI Slot 3

MuTIOL 1G

PCI Slot 4

PCI Slot 5

ATA 66/100/133

SiS964

IDE 1

IDE 2

B B

KEYBOARD

/MOUSE

PS/2

LPC Bus

Media

Interface

FAN 1

FAN 2

ISA

FAN 3

ROM

FAN CONTROL

ISA Bus

LPC Super I/O

VOLTAGE MONITOR

TEMPERATURE MONITOR

Gigabit LAN

LAN PHY

AC'97

Audio Codec

Back Panel

USB 0

USB 1

USB 2

USB 3

RJ45

Audio I/O

SATA1,2

Front Panel

USB 4

USB 5

USB 6

USB 7

A A

IR

5

4

PARALLEL

3

FLOPPY

Title

Document Number Re v

2

Date: Sheet

Topology

748A01

TECHNOLOGY COPR.

248Sunday, September 05, 2004

1

A

of

Page 3

5

DCCBB

A

4

3

2

1

D

A

Title

Document Number Re v

5

4

3

2

Date: Sheet

Reset Map

748A01

TECHNOLOGY COPR.

348Sunday, September 05, 2004

1

A

of

Page 4

5

D D

C C

4

3

2

1

B B

A A

TECHNOLOGY COPR.

Title

Document Number Re v

5

4

3

2

Date: Sheet

Clock Distribution

748A01

A

of

448Sunday, September 05, 2004

1

Page 5

5

D D

C C

4

3

2

1

B B

A A

TECHNOLOGY COPR.

Title

Document Number Re v

5

4

3

2

Date: Sheet

Power Delivery Map

748A01

A

of

548Sunday, September 05, 2004

1

Page 6

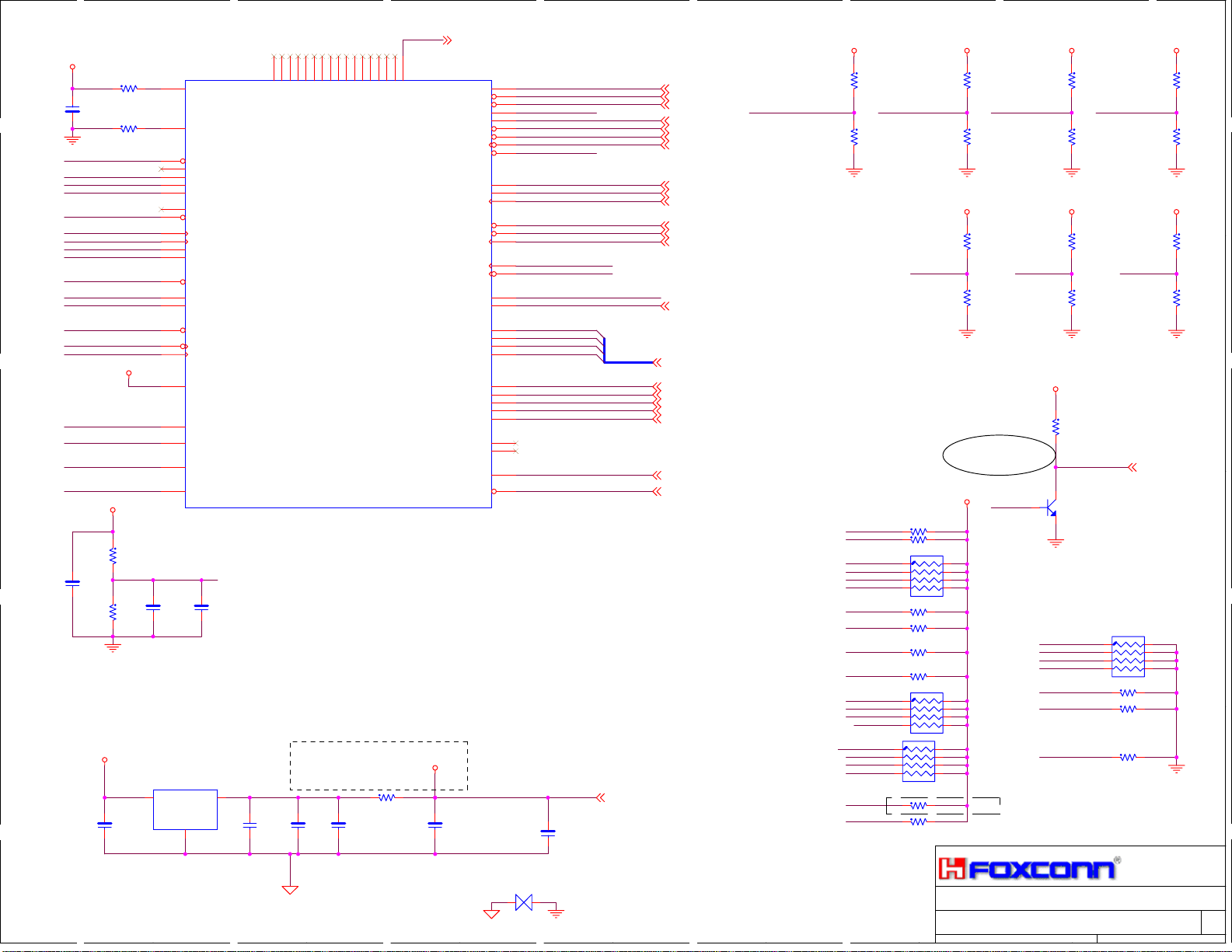

8

DCCBB

A

A

SDATAINCLKJ[0..3]11

SDATAOUTCLKJ[0..3]11

SADDINJ[2..1 4]11

SADDOUTJ[2..14]11

SDATAJ[0..63]11

SDATAINCLKJ[0..3]

SDATAOUTCLKJ[0..3]

SADDOUTJ[2..14]

D

SDATAJ0 ADINCLKJ

SDATAJ1

SDATAJ2 SADDINJ0

SDATAJ3

SDATAJ4

SDATAJ5

SDATAJ6

SDATAJ7

SDATAJ8

SDATAJ9

SDATAJ10

SDATAJ11

SDATAJ12

SDATAJ13

SDATAJ14

SDATAJ15

SDATAJ16

SDATAJ17

SDATAJ18

SDATAJ19 SADDOUTCLKJ

SDATAJ20

SDATAJ21

SDATAJ22

SDATAJ23 SADDOUTJ2

SDATAJ24

SDATAJ25

SDATAJ26

SDATAJ27

SDATAJ28

SDATAJ29

SDATAJ30

SDATAJ31

SDATAJ32

SDATAJ33

SDATAJ34

SDATAJ35

SDATAJ36

SDATAJ37

SDATAJ38

SDATAJ39

SDATAJ40

SDATAJ41

SDATAJ42

SDATAJ43

SDATAJ44

SDATAJ45

SDATAJ46

SDATAJ47

SDATAJ48

SDATAJ49

SDATAJ50

SDATAJ51

SDATAJ52

SDATAJ53

SDATAJ54

SDATAJ55

SDATAJ56

SDATAJ57

SDATAJ58

SDATAJ59

SDATAJ60

SDATAJ61

SDATAJ62

SDATAJ63

Close to S748

L3

DAINCLKJ0 SDATAINCLKJ0 SDATAINCLKJ2

10nH

DAINCLKJ1 M_DAINCLKJ1 SDATAINCLKJ1 SDATAINCLKJ3

L0603 10nH

1 2

L7

L0603 10nH

1 2

M_DAINCLKJ0 DAINCLKJ2

*

*

7

SADDIN J[2..14 ]

SDATAJ[0..63]

AA35

W37

W35

Y35

U35

U33

S37

S33

AA33

AE37

AC33

AC37

Y37

AA37

AC35

S35

Q37

Q35

N37

J33

G33

G37

E37

G35

Q33

N33

L33

N35

L37

J37

A37

E35

E31

E29

A27

A25

E21

C23

C27

A23

A35

C35

C33

C31

A29

C29

E23

C25

E17

E13

E11

C15

A13

C21

A21

E19

C19

C17

A11

A17

A15

L4

1 2

BC4

4.7pF

50V, NPO, +/-0.25pF

C0603

L8

1 2

BC6

4.7pF

50V, NPO, +/-0.25pF

C0603

SYSDATA#0

SYSDATA#1

SYSDATA#2

SYSDATA#3

SYSDATA#4

SYSDATA#5

SYSDATA#6

SYSDATA#7

SYSDATA#8

SYSDATA#9

SYSDATA#10

SYSDATA#11

SYSDATA#12

SYSDATA#13

SYSDATA#14

SYSDATA#15

SYSDATA#16

SYSDATA#17

SYSDATA#18

SYSDATA#19

SYSDATA#20

SYSDATA#21

SYSDATA#22

SYSDATA#23

SYSDATA#24

SYSDATA#25

SYSDATA#26

SYSDATA#27

SYSDATA#28

SYSDATA#29

SYSDATA#30

SYSDATA#31

SYSDATA#32

SYSDATA#33

SYSDATA#34

SYSDATA#35

SYSDATA#36

SYSDATA#37

SYSDATA#38

SYSDATA#39

SYSDATA#40

SYSDATA#41

SYSDATA#42

SYSDATA#43

SYSDATA#44

SYSDATA#45

SYSDATA#46

SYSDATA#47

SYSDATA#48

SYSDATA#49

SYSDATA#50

SYSDATA#51

E9

SYSDATA#52

SYSDATA#53

C9

SYSDATA#54

A9

SYSDATA#55

SYSDATA#56

SYSDATA#57

SYSDATA#58

SYSDATA#59

SYSDATA#60

SYSDATA#61

SYSDATA#62

SYSDATA#63

L0603 10nH

L0603 10nH

6

F30

G11

G13

G19

G21

G27

G29

NC1F8NC2

NC3

NC4

NC5

NC6

NC7

SOCKETA-1

VID[4:0]

00000

00001

00010

00011

00100

00101

00110

00111

01000

01001

01010

01011

01100

01101

01110

01111 1.475

NC35

NC36

NC37

NC38

NC39

NC40

NC41

AF6

AF8

AG5

AF10

AF28

AF30

AE31

AF32

5

THERMDA

THERMDC

G31

H10

H28

H30

H32

J31

K30

L31

N31

Q31

S31

U31

W31

NC8

NC9

NC10H6NC11H8NC12

NC13

NC14

NC15

NC16J5NC17

NC18K8NC19

NC20

NC21

NC22

NC23S7NC24

NC25U7NC26

NC27W7NC28

VCC_CORE VID[4:0] VCC_CORE

1.850

1.825

1.800

1.775

1.750

1.725

1.700

1.675

1.650

1.625

1.600

1.575

1.550

1.525

1.500

NC42

NC43

NC44

NC45

NC46

AG19

AG21

AG23

AG25

L5

L0603 10nH

1 2

L9

L0603 10nH

1 2

AH8

NC47

AH30

NC48

AJ7

FSB1

NC49

NC50

NC51

NC52

NC53

AJ9

AJ11

AJ15

AJ17

AJ19

FSB_Sense[1]

FSB1 19,26

BC5

4.7pF

*

50V, NPO, +/-0.25pF

C0603

M_DAINCLKJ3DAINCLKJ3

BC7

4.7pF

*

50V, NPO, +/-0.25pF

C0603

10000

10001

10010

10011

10100

10101

10110

10111

11000

11001

11010

11011

11100

11101

11110

11111

NC57

NC58

NC54

NC55

AL7

AK8

AJ27

L6

1 2

L10 L0603 10nH

1 2

NC59

NC60

NC61

AL9

AL11

AL25

L0603 10nH

NC62

AL27

10/10

THERMDA 40,42

THERMDC 42

Y31

AA31

AC31

AD8

NC29Y5NC30

NC31

NC32

1.450

1.425

1.400

1.375

1.350

1.325

1.300

1.275

1.250

1.225

1.200

1.175

1.150

1.125

1.100

NO CPU

NC63

NC64

NC65

NC66

AN7

AN9

AM8

AN11

AN25

AD30

NC33

NC67

AN27

NC34

NC68

4

SYSADDINCLK#

SYSADDIN#0

SYSADDIN#1

SYSADDIN#2

SYSADDIN#3

SYSADDIN#4

SYSADDIN#5

SYSADDIN#6

SYSADDIN#7

SYSADDIN#8

SYSADDIN#9

SYSADDIN#10

SYSADDIN#11

SYSADDIN#12

SYSADDIN#13

SYSADDIN#14

SYSADDOUTCLK#

SYSADDOUT#0

SYSADDOUT#1

SYSADDOUT#2

SYSADDOUT#3

SYSADDOUT#4

SYSADDOUT#5

SYSADDOUT#6

SYSADDOUT#7

SYSADDOUT#8

SYSADDOUT#9

SYSADDOUT#10

SYSADDOUT#11

SYSADDOUT#12

SYSADDOUT#13

SYSADDOUT#14

SYSDATAINCLK#0

SYSDATAINCLK#1

SYSDATAINCLK#2

SYSDATAINCLK#3

SYSDATAOUTCLK#0

SYSDATAOUTCLK#1

SYSDATAOUTCLK#2

SYSDATAOUTCLK#3

SYSCHECK#0

SYSCHECK#1

SYSCHECK#2

SYSCHECK#3

SYSCHECK#4

SYSCHECK#5

SYSCHECK#6

SYSCHECK#7

RSTCLK#

CLKIN#

RSTCLK

CLKIN

SDATAIN_VALID#

SDATAOUT_VALID#

SYSFILLVALID#

U1A

AJ33

AJ29

AL29

AG33

AJ37

AL35

AE33

AJ35

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

E3

J1

J3

C7

A7

E5

A5

E7

C1

C5

C3

G1

E1

A3

G5

G3

W33

J35

E27

E15

AE35

C37

A33

C11

U37

Y33

L35

E33

E25

A31

C13

A19

AL19

AL17

AN19

AN17

AN33

AL31

AJ31

SOCKETA

3

L1

ADINCLKJ SADDINCLKJ

L0603 4.7nH

1 2

4.7nH

VCCP

R1 680 +/-5%

SADDINJ1

SADDINJ2

SADDINJ3

SADDINJ4

SADDINJ5

SADDINJ6

SADDINJ7

SADDINJ8

SADDINJ9

SADDINJ10

SADDINJ11

SADDINJ12

SADDINJ13

SADDINJ14

SADDOUTJ3

SADDOUTJ4

SADDOUTJ5

SADDOUTJ6

SADDOUTJ7

SADDOUTJ8

SADDOUTJ9

SADDOUTJ10

SADDOUTJ11

SADDOUTJ12

SADDOUTJ13

SADDOUTJ14

DAINCLKJ0

DAINCLKJ1

DAINCLKJ2

DAINCLKJ3

SDATAOUTCLKJ0

SDATAOUTCLKJ1

SDATAOUTCLKJ2

SDATAOUTCLKJ3

SDATAINVALJ

R2 680 +/-5%

600 0.1uF

*

*

R6

270

+/-5%

R0603

SADDOUTCLKJ 11

BC2

680pF

50V, NPO, +/-5%

BC3

C0603

680pF

50V, NPO, +/-5%

C0603

R7

270

+/-5%

R0603

Title

Document Number R ev

Date: Sheet

2

L2

1 2

BC1

2.7pF

*

50V, NPO, +/-0.25pF

C0603

R3

60.4

+/-1%

R0603

R5

301

+/-1%

R0603

L0603 4.7nH

VCCPVCCP

CPU-1

R4

60.4

+/-1%

R0603

748A01

SADDINCLKJ 11

CK_133M_CPUJ 19

CK_133M_CPU 19

SDATAINVALJ 11

TECHNOLOGY COPR.

648Sunday, September 05, 2004

1

A

of

Page 7

8

DCCBB

A

A

VCCP

*After Model 6,VCC_Z/VSS_Z is NC

R12 0

BC8

*

0.1uF

DUMMY

D

*After Model 6,SYSVERFMODE is NC

R13 0

TRSTJ

TDI

TCK CONNECT

TMS P ROCRDY

DBREQJ

SCANCLK1 PICD0

SCANCLK2 PICCLK0

SCANSHIFTEN

SCANINTEVAL

PLLTESTJ

PLLMON1 COREFBJ

PLLMON2 COREFB

PLLBYPASSJ FID0

PLLBYPASSCLKJ FID2

PLLBYPASSCLK FID3

ZP

ZN

VREFSYS

SYSVREFMODE CPURSTJ

BC9

0.1uF

*

25V, Y5V, +80%/-20%

C0603

3D3V_SYS

*

VCCP

VCCA

R27

100

+/-1%

R0603

R30

100

+/-1%

R0603

BC12

1uF

DUMMY

DUMMY

VREFSYS

*

U2 AME8800

3

AC7

AE7

U3

U5

U1

Q1

Q3

AA1

AA3

S1

S5

Q5

S3

AC3

AN13

AL13

AJ25

AL15

AN15

AJ23

AE5

AC5

W5

AA5

BC10

0.33uF/NC

C0603

V_IN

VCC_Z

VSS_Z

TRST#

TDO

TDI

TCK

TMS

DBRDY

DBREQ#

SCANCLK1

SCANCLK2

SCANSHIFTEN

SCANINTEVAL

PLLTEST#

PLLMON1

PLLMON2

PLLBYPASS#

PLLBYPASSCLK#

PLLBYPASSCLK

VCCA

ZP

ZN

VREFSYS

SYSVREFMODE

U1B

SOCKETA

BC11

47nF

*

C0603

2

V_OUT

GND

1

7

G15

G17

G23

KEY1G7KEY2G9KEY3

KEY4

SOCKETA-2

A individual power

plane, Isolate with

digital power.

12

BC13

*

10uF

C0805

G25

KEY5

BC15

10nF

KEY6

KEY7N7KEY8Q7KEY9

*

Y7

AA7

AG7

KEY10

KEY11

R47 10

BC14

39pF

AG9

KEY12

AG15

KEY13

6

AG17

KEY14

AG27

KEY15

AG29

AG31

KEY16

+/-5%

R0603

KEY17

FSB_Sense[0]

FSB0

FSB0 19,26

IGNNE#

STPCLK#

FLUSH#

CONNECT

PROCRDY

CLKFWDRESET

K7CLKOUT

K7CLKOUT#

COREFB-

COREFB+

AMDPIN

ANALOG

PWROK

RESET#

VCCA

39pF

*

BC16

NMI

SMI#

A20M#

FERR

INTR

INIT#

PIC#1

PIC#0

PICCLK

FID0

FID1

FID2

FID3

VID0

VID1

VID2

VID3

VID4

5

NMI

AN3

SMIJ

AN5

A20MJ

AE1

FERR PLLBYPASSCLKJ PLLBYPASSCLK K7CLKOUT K7CLKOUTJ

AG1

INTR

AL1

INITJ

AJ3

IGNNEJ

AJ1

STPCLKJ

AC1

FLUSHJ

AL3

AL23

AN23

CLKFWDRST

AJ21

PICD1

N5

N3

N1

K7CLKOUT

AL21

K7CLKOUTJ PICD0 PICD1 PICCLK0

AN21

AG13

AG11

W1

W3

Y1

Y3

L1

L3

L5

L7

J7

AH6

AJ13

AE3

AG3

FID1

VID0

VID1

VID2

VID3

VID4

PWRGOOD

BC17

39pF

*

50V, NPO, +/-5%

C0603

15MIL

K7_PLL_PGD 46

4

NMI 26

SMIJ 26

A20MJ 26

INTR 26

INITJ 26

IGNNEJ 26

STPCLKJ 26

CONNECT 11

PROCRDY 11

CLKFWDRST 11

PICD1 26

PICD0 26

PICCLK0 19

COREFB 9

FID[0..3] 18

VID0 9

VID1 9

VID2 9

VID3 9

VID4 9

PWRGOOD 46

CPURSTJ 11

3

VCCP

R8

100

+/-5%

R0603

R14

100

+/-5%

R0603

DBREQJ

PLLTESTJ

TRSTJ

TDI

TCK

TMS

PLLMON1

PLLMON2

PLLBYPASSJ

ZN

SMIJ

INITJ

FLUSHJ

NMI

INTR

IGNNEJ

A20MJ

STPCLKJ

CPURSTJ

COREFB

R28 510

R29 510

RN1 510

1

*

3

5

7 8

CIS

R31 56

R33 56

R35 680

R38 40.2

RN62 680

1

*

3

5

7 8

RN63

+/-5%

1

*

3

5

7 8

680 8P4R0603

+/-5%

R49 100

R50 10K

2

VCCP VCCP VCCP

R9

100

+/-5%

R0603

R15

100

+/-5%

R0603

3D3V_SYS

R18

330

+/-5%

R0603

R21

1K

+/-5%

R0603

VCCP

600 have vccp pull up

VCCP

FERR

B

2

4

6

SCANCLK2

SCANINTEVAL

SCANCLK1

SCANSHIFTEN

2

4

6

8P4R0603

2

4

6

600 NC

ZP

SYSVREFMODE

VREFMODE=Low=No voltage scaling

COREFBJ

1

R10

100

+/-5%

R0603

R16

100

+/-5%

R0603

3D3V_SYS 3D3V_SYS

R19

330

+/-5%

R0603

R22

1K

+/-5%

R0603

R25

150

Change Component

+/-5%

R0603

FERRJ 26

Q1

MMBT3904

E C

RN2

270

1

*

3

5

7 8

2

4

6

R32 56

R34 270DUMMY

R36 10K

R11

100

+/-5%

R0603

R17

100

+/-5%

R0603

R20

330

+/-5%

R0603

R23

1K

+/-5%

R0603

JP18

12

SHORT

Title

Document Number R ev

Date: Sheet

SocketA-2

748A01

of

748Sunday, September 05, 2004

A

TECHNOLOGY COPR.

Page 8

8

DCCBB

A

A

VCCP

D

AB30

AB32

AB34

AB36

AD2

AD4

AD6

AF14

AF18

AF22

AF26

AF34

AF36

AH10

AH14

AH18

AH2

AH22

AH26

AH4

AJ5

AK10

AK14

AK18

AK22

AK26

AK30

AK34

AK36

AL5

AM10

AM14

AM18

AM2

AM22

AM26

AM30

AM34

B12

B16

B20

B24

B28

B32

B36

D12

D16

D20

D24

D28

D32

F12

F16

F20

F24

F28

F32

F34

F36

H12

H16

H20

H24

K32

K34

K36

P30

P32

P34

P36

T30

T32

T34

T36

X30

X32

X34

X36

B4

B8

D2

D4

D8

H2

H4

M2

M4

M6

M8

R2

R4

R6

R8

V2

V4

V6

V8

Z2

Z4

Z6

Z8

7

U1C

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_CORE6

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VCC_CORE61

VCC_CORE62

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

SOCKETA

6

AB2

VSS1

AB4

VSS2

AB6

VSS3

AB8

VSS4

AD32

VSS5

AD34

VSS6

AD36

VSS7

AF12

VSS8

AF16

VSS9

AF2

VSS10

AF20

VSS11

AF24

VSS12

AF4

VSS13

AH12

VSS14

AH16

VSS15

AH20

VSS16

AH24

VSS17

AH28

VSS18

AH32

VSS19

AH34

VSS20

AH36

VSS21

AK12

VSS22

AK16

VSS23

AK2

VSS24

AK20

VSS25

AK24

VSS26

AK28

VSS27

AK32

VSS28

AK4

VSS29

AK6

VSS30

AM12

VSS31

AM16

VSS32

AM20

VSS33

AM24

VSS34

AM28

VSS35

AM32

VSS36

AM36

VSS37

AM4

VSS38

AM6

VSS39

B10

VSS40

B14

SOCKETA-3

VSS41

B18

VSS42

B2

VSS43

B22

VSS44

B26

VSS45

B30

VSS46

B34

VSS47

B6

VSS48

D10

VSS49

D14

VSS50

D18

VSS51

D22

VSS52

D26

VSS53

D30

VSS54

D34

VSS55

D36

VSS56

D6

VSS57

F10

VSS58

F14

VSS59

F18

VSS60

F2

VSS61

F22

VSS62

F26

VSS63

F4

VSS64

F6

VSS65

H14

VSS66

H18

VSS67

H22

VSS68

H26

VSS69

H34

VSS70

H36

VSS71

K2

VSS72

K4

VSS73

K6

VSS74

M30

VSS75

M32

VSS76

M34

VSS77

M36

VSS78

P2

VSS79

P4

VSS80

P6

VSS81

P8

VSS82

R30

VSS83

R32

VSS84

R34

VSS85

R36

VSS86

T2

VSS87

T4

VSS88

T6

VSS89

T8

VSS90

V30

VSS91

V32

VSS92

V34

VSS93

V36

VSS94

X2

VSS95

X4

VSS96

X6

VSS97

X8

VSS98

Z30

VSS99

Z32

VSS100

Z34

VSS101

Z36

VSS102

5

CPR#(AK6): CPU_PRESENCE#

CPR#

is connected to VSS on the

processor package. If

pulled-up on the

motherboard, CPU_PRESENCE#

may be used to detect the

presence or absence of a

processor.

4

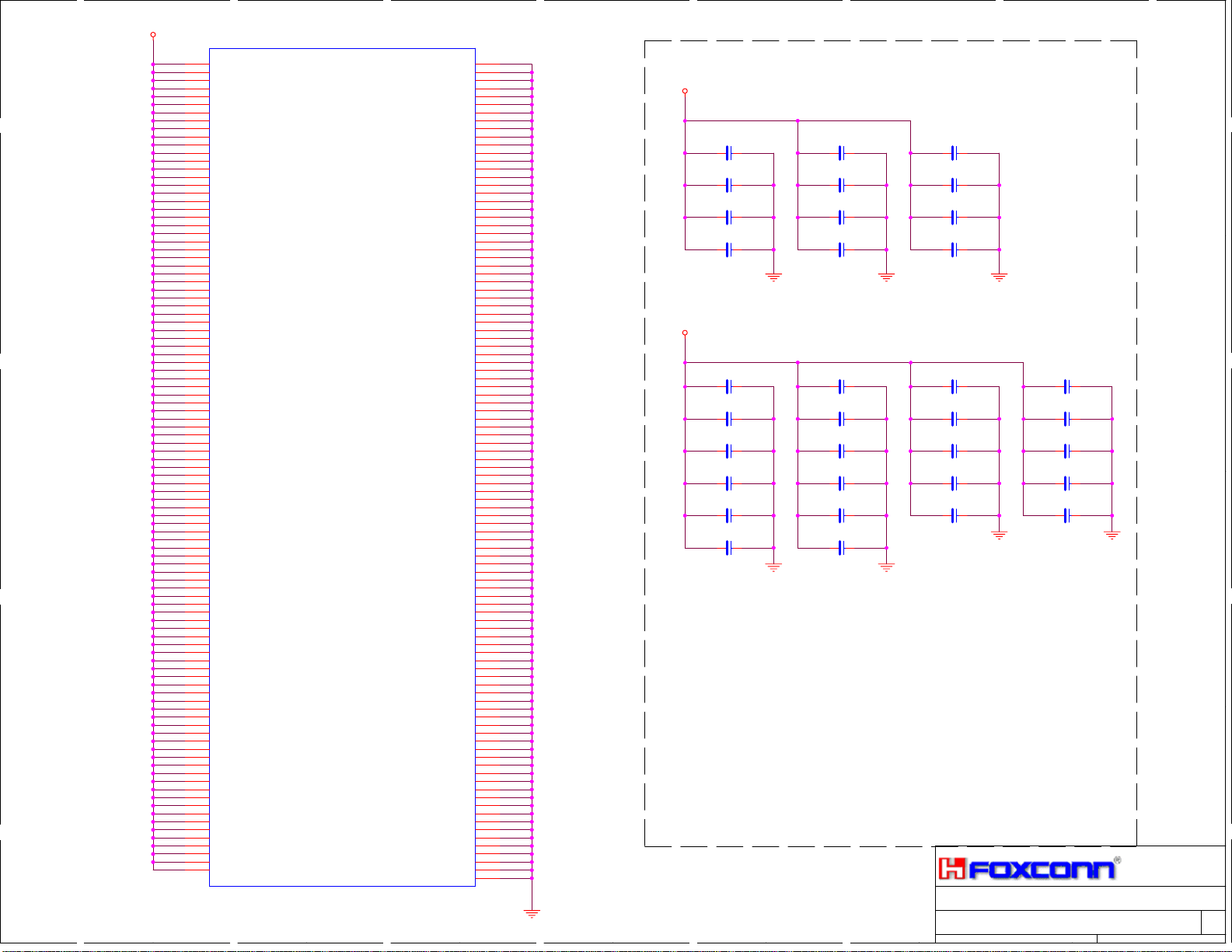

High Frequency Decoupling Capacitors

VCCP

BC18 4.7uF

C1206

*

BC21 4.7uF

C1206

*

BC24 4.7uF/NC

C1206

*

BC27 4.7uF

C1206

*

High Frequency Decoupling Capacitors

VCCP

BC30 0.22uF

*

BC34 0.22uF

*

BC38 0.22uF

*

BC42 0.22uF

*

BC46 0.22uF

*

BC50 0.22uF

*

3

BC19 4.7uF

C1206

*

BC22 4.7uF/NC

C1206

*

BC25 4.7uF/NC

C1206

*

BC28 4.7uF/NC

C1206

*

BC31 0.22uF/NC

*

BC35 0.22uF/NC

*

BC39 0.22uF/NC

*

BC43 0.22uF/NC

*

BC47 0.22uF/NC

*

BC51 0.22uF/NC

*

BC20 10uF

C1206

*

BC23 10uF

C1206

*

BC26 10uF/NC

C1206

*

BC29 10uFNC

C1206

*

BC32 0.22uF/nc

*

BC36 0.22uF/NC

*

BC40 0.22uF/NC

*

BC44 0.22uF/NC

*

BC48 0.22uF/NC

*

2

BC33 0.22uF/NC

*

BC37 0.22uF/NC

*

BC41 0.22uF/NC

*

BC45 0.22uF/NC

*

BC49 0.22uF/NC

*

1

TECHNOLOGY COPR.

Title

Document Number R ev

Date: Sheet

SocketA-3

748A01

of

848Sunday, September 05, 2004

A

Page 9

5

4

3

2

1

D D

R52

1K

+/-5%

R57

10K/NC

+/-5%

R0603

R0603

5V_SYS

5V_SYS

BC72

0.1uF_NC

*

5V_SYS

5V_SYS

VID47

VID37

VID27

VID17

VID07

R59

1K

R0603

+/-5%

R56

10K

R0603

+/-5%

PWMOK

C C

PWMOK46

COREFB7

B B

R536

2K/NC

+/-5%

R0603

R537

3.3K/NC

+/-5%

R0603

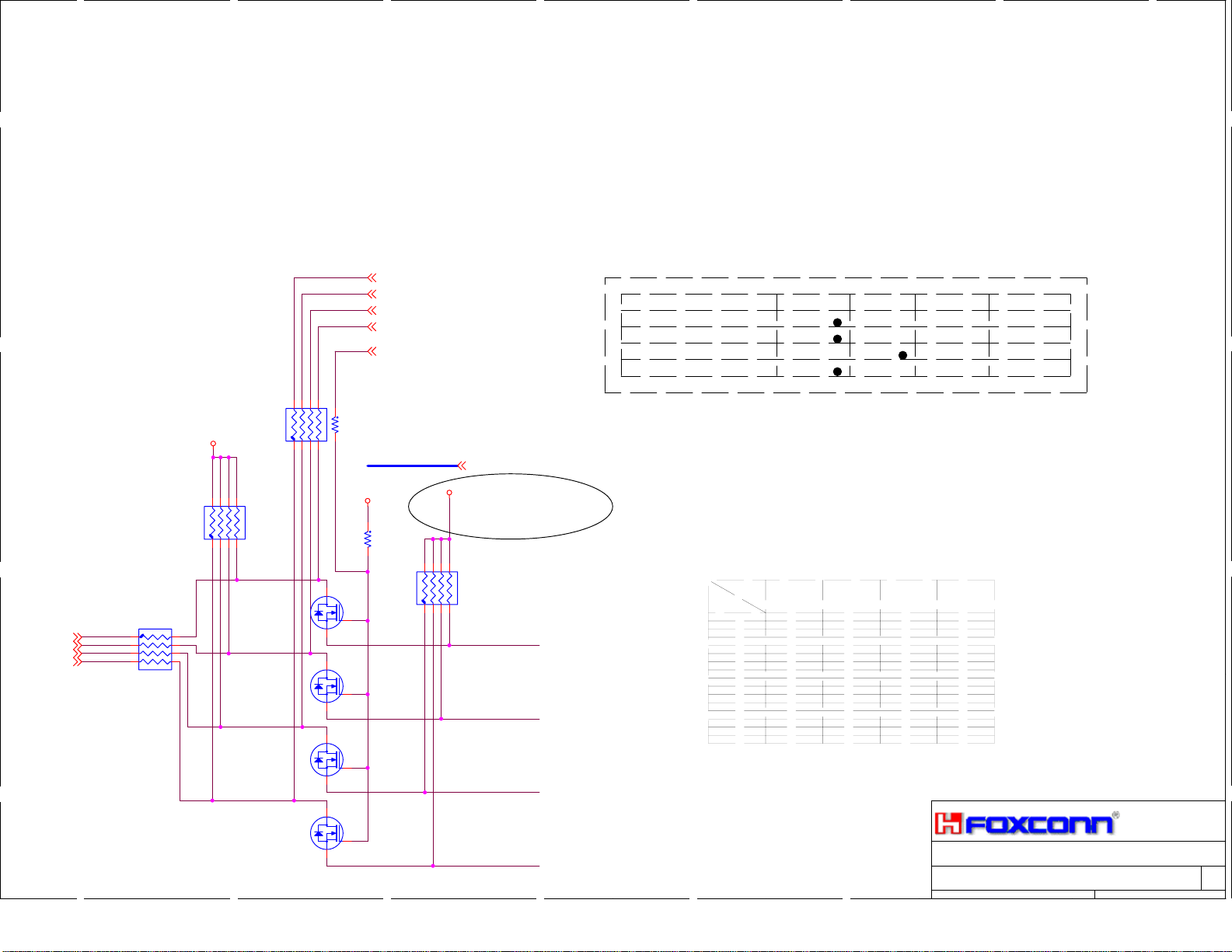

ISL6563CR FOR K7 POWER

R0805

+/-5%

1

VIN

*

DS

Q2AOD412

G

DS

Q3AOD412

G

VIN

DS

*

Q4AOD412

G

DS

Q5AOD412

G

3D3V_SYS

642

RN3

1K

*

135

7 8

R58 2K

BC75 0.1uF_NC

*

R60 150K_NC

R63

10K

R0603

+/-5%

JP17

12

SHORT

*

BC73

0.1uF

BC853

10nF

BC68

10uF

*

*

C1206

22

VID4

23

VID3

24

VID2

1

VID1

2

VID0

3

DACSEL/VID5

10

SSEND

21

ENLL

5

COMP

6

FB

9

OFS

R62

10K

+/-5%

R0603

7

ISEN

4

VRM10

BOTTOM PAD

CONNECT TO GND

5V_SYS

8

VCC

GND

25

R51

2

+/-5%

R0603

16

UGATE1

PVCC

PHASE1

LGATE1

BOOT1

BOOT2

UGATE2

PHASE2

LGATE2

PGND

ISL6563CR

5V_SYS

BC69

10uF

C1206

19

18

17

R1151

20

11

R1152 2.2

12

13

15

14

BC854

0.1uF

R53 1 R0805

BC71

*

0.1uF

2.2

*

U3

Seperated from GND Pad

*

+/-5%

R54 0

BC76

*

0.1uF

R61

R64

0

R0805

+/-5%

5V_SYS

BC70

10uF

6.3V, X5R, +/-20%

C1206

BC77

10uF

6.3V, X5R, +/-20%

C1206

BC834

10uF/NC

*

6.3V, X5R, +/-20%

C1206

Choke COIL 0.7uH

L12

*

R55

2.2

+/-5%

R0805

*

BC74

10nF

Choke COIL 0.7uH

L13

*

R65

2.2

+/-5%

R0805

*

BC78

10nF

Choke COIL 0.7uH

L11

*

*

EC1

1500uF

16V,+/-20%

CE50D100H300

123

EC4

2200uF 6.3V

123

2200uF 6.3V

*

123

2200uF 6.3V

EC8

EC2

1500uF

16V,+/-20%

CE50D100H300

EC5

2200uF 6.3V/NC

123

EC9

2200uF 6.3V

123

EC6

EC3

1500uF

*

16V,+/-20%

CE50D100H300

VIN

VCCP

A A

TECHNOLOGY COPR.

Title

Document Number Re v

5

4

3

2

Date: Sheet

VCCP

748A01

A

of

948Sunday, September 05, 2004

1

Page 10

5

D D

4

3

2

1

H4

Mounting Hole

H1

FMARK

FD40

C C

B B

H2

FMARK

FD40

H3

FMARK

FD40

mh40x80_8

7

8

9

H5

Mounting Hole

mh40x80_8

5

6

4

7

3

8

2

9

1

H6

Mounting Hole

mh40x80_8

5

6

7

4

8

3

9

2

1

H7

Mounting Hole

mh40x80_8

5

6

7

4

8

3

9

2

1

H8

Mounting Hole

mh40x80_8

5

6

4

7

3

8

2

9

1

H9

Mounting Hole

mh40x80_8

5

6

4

3

2

1

5

6

4

7

3

8

2

9

1

A A

TECHNOLOGY COPR.

Title

Document Number Re v

5

4

3

2

Date: Sheet

VRD DRIVER

748A01

A

of

10 48Sunday, September 05, 2004

1

Page 11

DCCBB

A

A

Place near the 748 chip.

3D3V_SYS

3D3V_SYS

D

SDATAINCLKJ[0..3]6

SDATAOUTCLKJ[0..3]6

Put near 748 chip

VCCP

R70

62

+/-1%

R0603

BC859

*

3.3pF/NC

Place near the 748 chip.

VCCP

VCCP

8

BC80

0.1uF

*

C0603

CPUPHYAVDD

JP3

12

SHORT

CK_133M_S74819

SDATAINVALJ6

CPURSTJ7

PROCRDY7

CONNECT7

CLKFWDRST7

SADDINCLKJ6

SADDOUTCLKJ6

CK_133M_S748

SADDINJ[2..14]6

SADDOUTJ[2..14]6

R73

33

+/-5%

R0603

R74

33

+/-5%

R0603

R77

100

+/-1%

R0603

R81

100

+/-1%

R0603

JP6

SHORT

CPUCLKAVDD

BC81

10nF

*

25V, Y5V, +80%/-20%

C0603

CPUCLKAVSS

BC83

0.1uF

*

*

C0603

SDATAOUTCLKJ0

SDATAOUTCLKJ1

SDATAOUTCLKJ2

SDATAOUTCLKJ3

S2KCOMPND

S2KCOMPPD

BC91

10nF/NC

*

C0603

HSTLVREFA

BC95

10nF

*

C0603

12

BC84

10nF

25V, Y5V, +80%/-20%

C0603

CPUPHYAVSS

VDDREFA

VSSREFA

VDDREFB

VSSREFB

HSTLVREFA

HSTLVREFB

SDATAINVALJ

CPURSTJ

PROCRDY

CONNECT

CLKFWDRST

SADDINCLKJ

SADDOUTCLKJ

SDATAINCLKJ0

SDATAINCLKJ1

SDATAINCLKJ2

SDATAINCLKJ3

SADDINJ2

SADDINJ3

SADDINJ4

SADDINJ5

SADDINJ6

SADDINJ7

SADDINJ8

SADDINJ9

SADDINJ10

SADDINJ11

SADDINJ12

SADDINJ13

SADDINJ14

SADDOUTJ2

SADDOUTJ3

SADDOUTJ4

SADDOUTJ5

SADDOUTJ6

SADDOUTJ7

SADDOUTJ8

SADDOUTJ9

SADDOUTJ10

SADDOUTJ11

SADDOUTJ12

SADDOUTJ13

SADDOUTJ14

CPUCLKAVDD

CPUCLKAVSS

CPUPHYAVDD

CPUPHYAVSS

15 mil

trace

7

VCCP

M27

M29

A23

C23

L29

B23

W29

E20

D18

D19

C19

F18

A22

U29

A26

E27

K29

P29

A24

G28

H29

R28

F21

D21

B21

E22

F20

D22

C20

C21

D20

C22

A20

A21

F19

U24

T27

W24

U25

U27

W26

U28

V25

W27

V27

U26

Y25

V29

Y26

Y27

B19

A19

R76

100

+/-1%

R0603

HSTLVREFB

R80

100

+/-1%

R0603

SHORT

SDATAJ[0..63]

S2KCOMPND

E18

VDDREFA

VSSREFA

VDDREFB

VSSREFB

HSTLVREFA

HSTLVREFB

CPUCLK

SDATAINVAL#

CPURST#

PROCRDY

CONNECT

CLKFWDRST

SADDINCLK#

SADDOUTCLK#

SDATAINCLK#0

SDATAINCLK#1

SDATAINCLK#2

SDATAINCLK#3

SDATAOUTCLK#0

SDATAOUTCLK#1

SDATAOUTCLK#2

SDATAOUTCLK#3

SADDIN#2

SADDIN#3

SADDIN#4

SADDIN#5

SADDIN#6

SADDIN#7

SADDIN#8

SADDIN#9

SADDIN#10

SADDIN#11

SADDIN#12

SADDIN#13

SADDIN#14

SADDOUT#2

SADDOUT#3

SADDOUT#4

SADDOUT#5

SADDOUT#6

SADDOUT#7

SADDOUT#8

SADDOUT#9

SADDOUT#10

SADDOUT#11

SADDOUT#12

SADDOUT#13

SADDOUT#14

CPUAVDD

CPUAVSS

CPUPHYAVDD

CPUPHYAVSS

U4A

748

JP7

*

*

12

S2KCOMPND

BC92

10nF/NC

C0603

BC97

10nF

C0603

6

SDATAJ[0..63]6

S2KCOMPPD

SDATAJ0

SDATAJ4

SDATAJ3

SDATAJ1

SDATAJ2

D17

C25

F24

E24

D25

C26

SDATA#0

SDATA#1

SDATA#2

S2KCOMPPD

SDATA#3

HOST

15 mil

trace

SDATAJ5

F23

SDATA#4

SDATA#5

SDATAJ7

SDATAJ6

A27

C27

SDATA#6

SDATAJ[0..63]

SDATAJ9

SDATAJ10

SDATAJ8

SDATAJ11

A25

D23

F22

C24

SDATA#7

SDATA#8

SDATA#9

SDATA#10

1D8V_VCCNB

SDATAJ12

SDATA#11

D26

SDATAJ13

SDATA#12

B25

SDATAJ14

D24

SDATA#13

SDATAJ15

SDATAJ16

B27

F26

SDATA#14

SDATA#15

SBA7

F12

E11

SBAJ6

SBAJ7

JP8

SHORT

5

SDATAJ18

SDATAJ17

SDATAJ19

SDATAJ20

SDATAJ21

SDATAJ22

SDATAJ23

SDATAJ24

SDATAJ25

SDATAJ27

SDATAJ26

SDATAJ28

SDATAJ29

E26

D27

D29

E28

E29

F29

F27

G24

F25

C29

C28

G26

H25

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

748-1

SBA6

SBA5

SBA4

SBA3

SBA2

SBA1

SBA0

ST0

ST1

ST2

AAD0H2AAD1J6AAD2G1AAD3H4AAD4J4AAD5G3AAD6F3AAD7G4AAD8E2AAD9E4AAD10D2AAD11G6AAD12F5AAD13D3AAD14C1AAD15D4AAD16D7AAD17B5AAD18E7AAD19F8AAD20A6AAD21C6AAD22E8AAD23F9AAD24C8AAD25D9AAD26

F14

SBAJ3

C12

D12

SBAJ1

SBAJ2

BC100

0.1uF

C0603

E13

SBAJ0

*

F15

A14

E14

ST1

ST2

ST0

BC101

10nF/NC

C0603

VSSREFB

AAD1

AAD0

A10

C11

SBAJ4

SBAJ5

VDDREFB

*

12

SDATAJ30

SDATA#29

AAD2

G29

SDATAJ31

SDATA#30

AAD3

G27

SDATA#31

SDATAJ32

SDATAJ33

J25

K25

SDATA#32

AAD5

AAD4

SDATAJ34

SDATAJ36

SDATAJ35

L24

K27

M26

SDATA#33

SDATA#34

SDATA#35

AAD7

AAD8

AAD6

1D8V_VCCNB

SDATAJ37

L28

SDATA#36

AAD9

SDATAJ38

SDATA#37

AAD10

L25

SDATAJ39

SDATA#38

AAD11

L27

SDATAJ40

J24

SDATA#39

AAD12

SDATAJ41

J26

SDATA#40

AAD13

4

SDATAJ42

SDATAJ43

H27

J27

SDATA#41

SDATA#42

AAD14

AAD15

JP9

SHORT

SDATAJ45

SDATAJ44

J29

J28

SDATA#43

SDATA#44

SDATA#45

AAD16

AAD17

VDDREFA

*

12

SDATAJ46

M24

AAD18

SDATAJ47

SDATAJ48

SDATAJ49

SDATAJ50

SDATAJ51

SDATAJ52

L26

N26

R25

R26

P27

T26

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

AGP

AAD21

AAD22

AAD23

AAD19

AAD20

AAD24

BC103

BC104

0.1uF

10nF/NC

*

C0603

C0603

VSSREFA

SDATAJ54

SDATAJ53

SDATAJ55

SDATAJ56

SDATAJ57

R27

T24

T29

N27

N24

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

GC_DET#/AGP8XDET#

AAD27C9AAD28

AAD29A9AAD30

F11

E10

AAD28

AAD27

AAD26

AAD25

AAD29

SDATAJ58

SDATAJ59

SDATAJ60

N25

N28

SDATA#58

SDATA#59

PIPE#/DBI_HI

AGPVSSREF

AAD31

B10

D10

AAD30

AAD31

3

SDATAJ61

SDATAJ63

SDATAJ62

P25

R29

N29

R24

SDATA#60

SDATA#61

SDATA#62

SDATA#63

AC/BE3#

AC/BE2#

AC/BE1#

AC/BE0#

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

APAR#

RBF#

WBF#

DBI_LO

SB_STBF

SB_STBS

AD_STBF0

AD_STBS0

AD_STBF1

AD_STBS1

AGPCLK

AGPRCOMP

AGPRCOMN

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

2

AAD[0..31]

SBAJ[0..7]

AC-BE[0..3]

ST[0..2]

ADSTBF[0..1]

ADSTBS[0..1]

AC-BE3

B7

AC-BE2

C5

AC-BE1

C3

AC-BE0

H5

D15

E16

F6

A4

E5

D6

B4

A3

B2

C14

B13

GCDETJ

C15

DBI_HI

A13

DBI_LOW

D13

A12

B11

ADSTBF0

E1

ADSTBS0

F2

ADSTBF1

B8

ADSTBS1

A7

AGPCLK0

C16

AGPRCOMP

J3

AGPRCOMN

J1

A1XAVDD

A16

A1XAVSS

B16

A4XAVDD

B15

A4XAVSS

A15

H1

J2

Title

Document Number R ev

Date: Sheet

AREQ 24

AGNT 24

AFRAME 24

AIRDY 24

ATRDY 24

ADEVSEL 24

ASERR 24

ASTOP 24

APAR 24

RBF 24

WBF 24

GCDETJ 24

DBI_HI 24

DBI_LOW 24

SBSTBF 24

SBSTBS 24

CK_66M_S748 19

AVREFGC 24

A1XAVDD

*

A1XAVSS

A4XAVDD

*

A4XAVSS

HOST & AGP

748A01

BC85

0.1uF

C0603

BC88

0.1uF

C0603

AAD[0..31] 24

AC-BE[0..3] 24

ADSTBF[0..1] 24

ADSTBS[0..1] 24

AGPRCOMN

AGPRCOMP

BC86

10nF

*

C0603

JP4

SHORT

BC89

10nF

*

C0603

1

SBAJ[0..7] 24

ST[0..2] 24

AGP3.0 = 50 ohm

R68

49.9

+/-1%

R0603

R69

43.2

+/-1%

R0603

3D3V_SYS

12

3D3V_SYS

JP5

12

SHORT

TECHNOLOGY COPR.

of

11 48Sunday, September 05, 2004

VDDQ

A

Page 12

8

DCCBB

A

A

MD[0..63] MAA[0..14]

DQM[0..7]

DQS[0..7] CSAJ[0..5]

MD[0..63] 21,22,23

DQM[0..7] 21,22,23

DQS[0..7] 21,22,23

D

2D5V_DDR 2D5V_DDR

BC106

0.1uF/NC

*

C0603

DDRVREFA

( 10-mil trace ) ( 10-mil trace )

25-mil clearance

or shielded by

VSS trace and

VDD trace

BC108

0.1uF

*

C0603

R88

150

+/-1%

R0603

R92

150

+/-1%

R0603

25-mil clearance

or shielded by

VSS trace and

VDD trace

7

DDRVREFB

*

*

BC107

0.1uF/NC

C0603

BC109

0.1uF

C0603

R87

150

+/-1%

R0603

R91

150

+/-1%

R0603

6

AD25

AH28

AD24

AH26

AF27

AG25

AF26

AG27

AJ26

AJ27

AE25

AE23

AG24

AH23

AF24

AH25

AE22

AD21

AD22

AJ24

AH22

AG22

AF20

AH20

AE20

AF21

AE19

AJ20

AG21

AJ21

AE16

AH17

AF15

AJ15

AF17

AD16

AG15

AH16

AG16

AJ17

AJ12

AF12

AG10

AF11

AG12

AD12

AE11

AH10

AH11

AJ11

AJ6

AF6

AE7

AH4

AH7

AG7

AG6

AF5

AJ5

AH5

AD7

AE5

AE4

AF2

AG4

AF3

AG3

AD6

AH2

AG1

AC2

AE1

AB3

AD3

AE2

AC6

AD5

AC4

AB5

AD1

DDRAVDD

DDRAVSS

U4B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

CSB#0/DQS0

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

CSB#1/DQS1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

CSB#2/DQS2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

CSB#3/DQS3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

CSB#4/DQS4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

CSB#5/DQS5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

CSB#6/DQS6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

CSB#7/DQS7

748

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7

5

MAA[0..14] 21,22,23

CSAJ[0..5] 21,22,23

748-2

BC110

BC111

0.1uF

C0603

10nF

*

C0603

*

FWDSDCLKO

3D3V_SYS

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

MAA15

RAMRWA#

SRASA#

SCASA#

Reserved

CS0#

CS1#

CS2#

CS3#

CS4#

CS5#

DDRVREFA

DDRVREFB

DLLAVDD

DLLAVSS

SDRCLKI

DDRAVDD

DDRAVSS

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

S3AUXSW#

DDRCOMP

DDRCOMN

4

AE13

AJ14

AH14

AE14

AD15

AD18

AJ18

AF18

AG18

AH19

AF14

AE10

AD13

AG19

AD19

AF23

AF9

AG9

AJ9

AE17

AD9

AD10

AJ8

AE8

AF8

AH8

AJ23

AJ3

AA29

AA28

AG13

AH13

Y29

Y28

AA6

AB6

AA5

AA3

AB4

AA4

Y6

AB2

AB1

DLLAVDD

DLLAVSS

10 mil wire

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

MWAJ

RASAJ

CASAJ

CSAJ0

CSAJ1

CSAJ2

CSAJ3

CSAJ4

CSAJ5

DDRCOMP

DDRCOMN

BC113

0.1uF

*

C0603

DDRVREFA

DDRVREFB

DLLAVDD

DLLAVSS

FWDSDCLKO

DDRAVDD

DDRAVSS

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

*

BC114

10nF

C0603

3

CKE0 21

CKE1 21

CKE2 21

CKE3 21

CKE4 22

CKE5 22

3D3V_SYS

RASAJ

MWAJ

CASAJ

FWDSDCLKO

2

RASAJ 21,22,23

MWAJ 21,22,23

CASAJ 21,22,23

DDRCOMN

DDRCOMP

Put near 748 chip.

R86 22

+/-5%

R0603

R83 40.2 +/-1%

R84 40.2 +/-1%

*

1

SDCLKO_DDR 20

BC105

10pF

50V, NPO, +/-5%

C0603

2D5V_DDR

TECHNOLOGY COPR.

Title

Document Number R ev

Date: Sheet

748-MEM

748A01

of

12 48Sunday, September 05, 2004

A

Page 13

D

DCCBBAA

The differences between

the traces of MuTIOL

Strobes and Data should

be smaller than 0.05"

8

ZSTB025

ZSTBJ025

ZSTB125

ZSTBJ125

ZUREQ25

ZDREQ25

7

ZCLK0

ZCLK019

ZSTB0

ZSTBJ0

ZSTB1

ZSTBJ1 TRAP0

Z1XAVDD TRAP3

Z1XAVSS

Z4XAVDD

Z4XAVSS

ZCMPJN DRAM_SEL

ZCMPJP

ZVREF

ZUREQ

ZDREQ

AA1

AA2

W1

U1

V2

P2

R1

Y2

Y1

W2

W4

W3

W6

V3

U4C

748

ZCLK

ZSTB0

ZSTB0#

ZSTB1

ZSTB1#

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

ZCMP_N

ZCMP_P

ZVREF

ZUREQ

ZDREQ

6

748-3

MuTIOL

ZAD0V4ZAD1T2ZAD2U5ZAD3T5ZAD4U3ZAD5T4ZAD6R3ZAD7T6ZAD8P6ZAD9P1ZAD10R5ZAD11P4ZAD12N2ZAD13N5ZAD14N3ZAD15N6ZAD16

5

V6

TESTMODE0

TESTMODE1

TESTMODE2

TRAP0

TRAP1

TRAP2

TRAP3

TRAP4

ENTEST

DLLEN#

DRAM_SEL

PCIRST#

PWROK

AUXOK

B18

A18

F17

E17

C17

B17

A17

F16

D16

C18

Y4

W5

Y5

Y3

BC116

1uF

*

C0603

dummy

4

NB Hardware Trap Table

CPUDLLENN

TMODE0

TMODE1

TMODE2

TRAP4 MuTIOL type (verision 1 , 2) Ver. 1 Ver. 2 OFF

TMODE0

TMODE1

TMODE2

*

R94 0

BC117

1uF

C0603

dummy

TRAP0 18

TRAP1 18

TRAP2 18

TRAP3 18

PWRGD_NB 46

AUXOK 26,45

TRAP1

TRAP2

TRAP4

ENTEST

DLLENJ

PWRGD_NB

CPUCLK SDCLK PLL/DLL Circuit Enable

P748 Debug Mode Selection OFF

R1160 0

3D3V_SB

DUMMY

PCIRSTJ2 25,37

3

A0/A1

MuTIOL ( ASL ) DBI Mode

MuTIOL ( ASL ) initialize Mode

2

DLLENJ

ON/1

DISABLE

Packet

ENABLE

OFF/0

ENABLE

ENABLE

Series

DISABLE

3D3V_SYS

R1145

4.7K/NC

+/-5%

R0603

1

Default

OFFDISABLE

OFF

OFF

BC833

10uF

C1206

*

FB52

2 1

FB L0603 47 Ohm

JP14

12

SHORT

8

The differences between

the traces of MuTIOL

Strobes and Data should

be smaller than 0.05"

Z4XAVDD

BC121

0.1uF

*

C0603

Z4XAVSS

BC120

10nF

*

C0603

7

TMODE0

TMODE1

TMODE2

TRAP4

ZCMPJN

ZVREF

ZCMPJP

NB Hardware Trap

1

*

3

5

7 8

R1144 4.7KDUMMY

3

3D3V_SYS

RN75

2

4

6

4.7K DUMMY

TECHNOLOGY COPR.

Title

Document Number Re v

Date: Sheet

MuTIOL

748A01

13 48Sunday, September 05, 2004

2

A

of

1

ZAD16

ZAD11

ZAD14

ZAD13

ZAD12

ZAD10

ZAD0

ZAD[0..16]25

ZAD[0..16]

3D3V_SYS3D3V_SYS

BC123

10nF

*

JP15

SHORT

C0603

12

ZAD6

ZAD3

ZAD4

ZAD2

ZAD1

ZAD8

ZAD9

ZAD5

ZAD7

Z1XAVDD

BC124

0.1uF

*

C0603

Z1XAVSS

6

ZAD15

PULL LOW

NB Hardware Trap has internal pull-low in SiS748 chip

for DRAM_SEL,CPUDLLENN,TMODE0,TMODE1,TMODE2 signals.

Place near 748 chip.

1D8V_VCCNB

JP16

SHORT

BC118

0.1uF

*

C0603

BC126

0.1uF

*

C0603

12

4

R96

150

+/-1%

R0603

R98

49.9

+/-1%

R0603

5

R95

56

+/-5%

R0603

R99

56

+/-5%

R0603

Page 14

D

DCCBB

A

A

VDDQ

BC129

*

BC133

*

BC137 1uF/ NC

*

BC140 1uF

*

BC142 0.1 uF

*

BC144 0.1 uF/NC

*

3D3V_SB

BC673

10uF

*

C1206

8

10uF C1206

10uF/NCC1206

1D8V_SB

*

VCCP

3D3V_SYS

BC188

10nF

C0603

VDDQ

1D8V_VCCNB

U4D

K10

K11

K13

K14

M10

M11

N11

K12

K15

K16

K18

K20

M20

N10

V20

Y12

Y15

Y18

Y19

AB13

AB17

H21

H22

K17

K19

M19

N19

N20

P19

P20

R19

R20

H16

L10

L11

L12

L13

L14

L15

L20

J22

L16

L17

L18

L19

T19

T20

J16

H8

H9

J8

T9

U9

7

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

VDD3.3

VDD3.3

AUX1.8

AUX3.3

748

6

1D8V_VCCNB

T10

VDDZ

R11

VDDZ

R10

VDDZ

P11

VDDZ

P10

VDDZ

W20

IVDD

T11

VDDM

U10

VDDM

U11

VDDM

U19

VDDM

U20

VDDM

V10

VDDM

V11

VDDM

V19

VDDM

W10

VDDM

VSS

M17

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

PVDDM

PVDDM

PVDDM

PVDDM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

M16

W11

W12

W13

W14

W15

W16

W17

W18

W19

Y10

Y13

Y14

Y16

Y17

Y20

AA8

AA22

AB8

AB9

AB21

AB22

W9

Y11

AA13

AA17

P12

P13

P14

P15

P16

R12

R13

R14

R15

R16

T12

T13

T14

T15

T16

U12

U13

U14

U15

U16

U17

U18

V12

V13

V14

V15

V16

V17

V18

M12

M13

M14

M15

N12

N13

N14

N15

748-4

Power(inside)

VSS

VSS

VSS

VSS

VSS

T18

VSS

T17

R18

R17

P18

VSS

P17

VSS

N18

N17

N16

VSS

VSS

M18

2D5V_DDR

5

VDDQ

1D8V_VCCNB

2D5V_DDR

VCCP

U4E

Y24

AA24

AA25

AA26

AA27

AB24

AB25

AB26

AB27

AB28

AB29

AC24

AC25

AC26

AC27

AC28

AC29

AD26

AD27

AD28

AD29

AE26

AE27

AE28

AE29

AF28

AF29

AG29

B20

B22

B24

B26

B28

D28

F28

H28

K28

M28

P28

T28

V28

W28

K1

K2

K3

K4

K5

K6

M1

M2

M3

M4

M5

M6

N1

P3

R2

T1

T3

U2

V1

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

L1

VDDQ

L2

VDDQ

L3

VDDQ

L4

VDDQ

L5

VDDQ

L6

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

S2KOVDD

748

748-5

. Power

(outside)

VSS

VSS

VSS

VSS

VSS

E25

E19

E21

E23

H24

G25

4

VSSZN4VSSZP5VSSZR4VSSZR6VSSZU4VSSZU6VSSZ

VSS

VSS

VSS

VSS

K24

K26

H26

M25

VSS

P24

VSS

P26

VSS

T25

VSS

V24

VSS

V5

V26

VSS

W25

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

VSSM

A5

A8

A11

B3

B6

B9

B12

B14

C2

C4

C7

C10

C13

D1

D5

D8

D11

D14

E3

E6

E9

E12

E15

F1

F4

F7

F10

F13

G2

G5

H3

H6

J5

AC1

AC3

AC5

AD2

AD4

AD8

AD11

AD14

AD17

AD20

AD23

AE3

AE6

AE9

AE12

AE15

AE18

AE21

AE24

AF1

AF4

AF7

AF10

AF13

AF16

AF19

AF22

AF25

AG2

AG5

AG8

AG11

AG14

AG17

AG20

AG23

AG26

AG28

AH3

AH6

AH9

AH12

AH15

AH18

AH21

AH24

AH27

AJ4

AJ7

AJ10

AJ13

AJ16

AJ19

AJ22

AJ25

3

3D3V_SYS

BC131 0.1uF

*

BC135 0.1uF

*

2D5V_DDR

2

1D8V_VCCNB

BC127 10uF C1206

*

BC128 1uF/NC

*

BC132 1uF

*

BC136 0.1uF/NC

*

BC139 0.1uF

*

VCCP

BC130

1

10uF C1206

*

BC134 1uF/NC

*

BC138 0.1uF

*

BC141 0.1uF/NC

*

BC143 0.1uF

*

BC145 1uF/NC

*

BC147 1uF/NC

*

BC150 0.1uF/NC

*

BC153 0.1uF/NC

*

BC156 1uF

*

BC158 1uF

*

BC160 0.1uF

*

BC161 0.1uF

BC146 10uF

*

BC148

10uF/NC

VCCP

C1206

C1206

*

BC149 10uF/NC

*

BC152 1uF/NC

*

BC155 0.1uF

*

BC157 0.1uF/NC

*

BC159 0.1uF

C1206

*

*

Place these capacitors under 748 solder side.

VDDQ

BC164 0.1uF-BOT

*

VDDQ

BC170 0.1uF-BOT

1D8V_VCCNB

BC172 0.1uF-BOT

BC174 0.1uF-BOT

BC176 0.1uF-BOT

BC178

VCCP

BC180 0.1uF-BOT

BC182 0.1uF-BOT

BC184 0.1uF-BOT

BC186 0.1uF-BOT

*

*

0.1uF-BOT

*

*

*

*

*

*

*

2D5V_DDR

BC163 0.1uF-BOT

BC165

*

BC166 0.1uF-BOT

*

0.1uF-BOT

*

Title

Document Number R ev

Date: Sheet

748-POWER

748A01

A

of

14 48Sunday, September 05, 2004

TECHNOLOGY COPR.

Page 15

5

3D3V_SB

R1132

270

+/-1%

D D

R0603

R1134

1K

+/-1%

R0603

12V_SYS

BC778

0.1uF

*

25V, Y5V, +80%/-20%

C0603

411

3

+

2

-

LM324

U26A

1

R1133

R0603 +/-5%

6.3V, +/-20%

CE35D80H200

G

1K

EC79

1000uF

4

3D3V_SYS

DS

*

1000uF

6.3V, +/-20%

CE35D80H200

Q54

SDU3055L2

EC14

*

EC15

1000uF

*

6.3V, +/-20%

CE35D80H200

EC78

1000uF

*

6.3V, +/-20%

EC68

1000uF/NC

*

6.3V, +/-20%

CE35D80H200

CE35D80H200

2D5V_DDR

2.598

3

3D3V_SB

R1135

169

+/-1%

R0603

R1136

205

+/-1%

R0603

2

3D3V_SYS

BC779

0.1uF

*

25V, Y5V, +80%/-20%

C0603

1D8V_VCCSB

*

G

*

DS

Q50

SDU3055L2

BC678

0.1uF

25V, Y5V, +80%/-20%

C0603

U26B

411

5

+

6

7

-

LM324

R522 1K

R0603

EC59

1000uF

6.3V, +/-20%

CE35D80H200

1

C C

3D3V_SB

R1137

340

+/-1%

R0603

R1138

301

+/-1%

R0603

B B

2D5V_DDR

U6

1

12

BC191

1uF/NC

A A

*

12

12

BC193

0.1uF/NC

25V, Y5V, +80%/-20%

C0603

R109

1K

R110

1K

VIN

3

REFEN

RT9173

5

1D5V_AGP POWER FOR NB/AGP

U26C

411

10

+

VCNTL

VCNTL

VCNTL

VCNTL

VOUT

GND

9

8

-

LM324

3D3V_SYS

8

7

6

5

4

EC17

2

470uF

*

6.3V, +/-20%

CE25D60H110

R526

1K

R0603

+/-5%

G

*

*

3D3V_SYS

*

DS

Q51

SDU3055L2

VDDQ

BC679

0.1uF

*

EC18

470uF/NC

6.3V, +/-20%

CE25D60H110

*

BC190

0.1uF

25V, Y5V, +80%/-20%

C0603

4

EC60

1000uF/NC

6.3V, +/-20%

CE35D80H200

EC61

1000uF

6.3V, +/-20%

CE35D80H200

DDR_VTT

BC192

0.1uF

*

25V, Y5V, +80%/-20%

C0603

3D3V_SB

R1139

150

+/-1%

R0603

12

13

R1141

205

+/-1%

R0603

3

U26D

411

+

14

-

LM324

2

G

R1140 1K

R0603

Title

Document Number Re v

Date: Sheet

1.8V--SB

3D3V_SYS

DS

Q55

SDU3055L2

BC780

0.1uF

*

25V, Y5V, +80%/-20%

C0603

1.9V--NB

EC58

1000uF

*

6.3V, +/-20%

CE35D80H200

1D8V_VCCNB

EC80

1000uF

*

6.3V, +/-20%

CE35D80H200

2.5V_DDR & 1.25_VTT

748A01

TECHNOLOGY COPR.

15 48Sunday, September 05, 2004

1

A

of

Page 16

5

4

3

2

1

SB1.8V

D D

C C

3D3V_SB 1D8V_SB

3

1

2

U7

Vin

AME1117

ADJ

4

Vout

4

BC194

10uF

*

10V, Y5V, +80%/-20%

C1206

Vref=1.25V

+

Vref

-

R111

750

+/-1%

R0603

R113

330

+/-1%

R0603

EC21

470uF

*

6.3V, +/-20%

CE25D60H110

BC195

0.1uF

*

25V, Y5V, +80%/-20%

C0603

5V_SB 3D3V_SB

5V_SB 3D3V_SB

B B

EC19

22uF

*

50V, +/-20%

CE20D50H110

A A

*

BC196

10uF/NC

C1206

U36 AIC1086CE/NC

3

VIN

3

1

2

U8

Vin

AME1117

ADJ

Vout

4

4

VOUT

ADJ

1

ADJ

SB3.3V

Vref=1.25V

+

Vref

-

ADJ

2

R112

196

+/-1%

R0603

R114

330

+/-1%

R0603

EC20

470uF

*

6.3V, +/-20%

CE25D60H110

BC197

0.1uF/NC

*

25V, Y5V, +80%/-20%

C0603

TECHNOLOGY COPR.

Title

Document Number Re v

5

4

3

2

Date: Sheet

SB1.8V & SB3V & 5V_DUAL

748A01

1

A

of

16 48Sunday, September 05, 2004

Page 17

5

3D3V_SYS

D D

J9

3

3

2

2

1

1

HEADER_1X3

C C

2-3

1-2

R1165

1K

+/-5%

R0603

PRI_DNJ

B

E C

ENABLE CNR AUDIO

ENABLE PRIMARY AUDIO

R1167

10K

+/-5%

R0603

Q56

MMBT3904

4

ATTACH R1166 FOR NO CNR SKU

R1166

0/NC

D22

21

1N4148W

AC_RESETJ

CODEC_RSTJ 38

3

5V_SB-12V_SYS3D3V_SYS

SMB_CLK_MAIN19,20,21,22,26

SYNC26,38

SDATO26,38

BIT_CLK26,38

R1170

10K

PRI_DNJ

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

CNR1

B1

RESERVED

B2

RESERVED

B3

RESERVED

B4

GND

B5

RESERVED

B6

RESERVED

B7

GND

B8

LAN_TXD1

B9

LAN_RSTSYNC

GND

LAN_RXD2

LAN_RXD0

GND

RESERVED

+5VDUAL

USB_OC#

GND

-12V

+3.3VD

GND

EE_DOUT

EE_SHCLK

GND

SMB_A0

SMB_SCL

PRIMARY_DN#

GND

AC97_SYNC

AC97_SD_OUT

AC97_BITCLK

CNR

5V_SYS

2

RESERVED

RESERVED

GND

RESERVED

RESERVED

GND

LAN_TXD2

LAN_TXD0

GND

LAN_CLK

LAN_RXD1

RESERVED

USB+

GND

USB-

+12V

GND

+3.3VDUAL

+5VD

GND

EE_DIN

EE_CS

SMB_A1

SMB_A2

SMB_SDA

AC97_RESET#

AC97_SD_IN2

AC97_SD_IN1

AC97_SD_IN0

GND

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

R1171

10K/NC

SMA1

SMA2SMA0

R1172

10K

1

5V_SYS12V_SYS 3D3V_SB

SMB_DATA_MAIN 19,20,21,22,26

AC_RESETJ 26

SDATI2 26

SDATI1 26

SDATI0 26,38

R1173

10K/NC

R1175

R1176

10K

R1174

10K

B B

R1177

10K/NC

A A

10K

SMA0

SMA1

SMA2

TECHNOLOGY COPR.

Title

Document Number Re v

5

4

3

2

Date: Sheet

EMPTY

748A01

A

of

17 48Sunday, September 05, 2004

1

Page 18

8

DCCBBAA

7

6

5

4

3

2

1

D

GPIO4 26

GPIO3 26

GPIO1 26

GPIO0 26

GPIO7 26

OC4-( SB debug mode)

SYNC( PCICLK PLL)

0

enable R409 un-stuffdisable

ROM yes

enable

enable

PCI AD R410 un-stuffSDATO( Trap mode)

disable

disable

Default1

R411 un-stuff

NONE

internal pull-low

(30~50K Ohm)

yesSPKR( LPC addr mapping)

NO

yes

*

135

642

R1157

0/NC

+/-5%

R0603

7 8

DS

Q22

G

2N7002

DS

Q23

G

2N7002

DS

Q24

G

2N7002

DS

Q25

G

2N7002

3D3V_SB

FID2

R152

10K

+/-5%

R0603

6

FID[0..3]

FID0

FID1

FID3

2D5V_DDR

642

*

135

FID[0..3] 7

RN71

680

8P4R0603

+/-5%

7 8

max 2.625v

NB Hardware Trap has internal pull-low in SiS748 chip FOR TRAP[0..3].

(FID3)

11.0

11.5

12.0

12.5

5.0

5.5 1

6.0

6.5

7.0

7.5

8.5

9.0

9.5

10.0

10.5

(FID2)

0

0

0

0

0

0

0

0

1

1

1

1

1

(FID1)

0

0

0

1

1

1

0

0

0

0

1

1

1

1

(FID0)

0

0

1

1

0

0

1

1

0

0

11

1

0

0

11

1

00

1

0

1

0

1

0

1

0

1

08.0

11

0

1

0

1

TECHNOLOGY COPR.

Title

Document Number Re v

5

4

3

Date: Sheet

Hardware Trap

2

748A01

A

of

18 48Sunday, September 05, 2004

1

RN76

3D3V_SYS

135

TRAP0

TRAP013

TRAP1

TRAP113

TRAP2

TRAP213

TRAP3

TRAP313

RN72

1

*

3

5

7 8

1K

+/-5%

8P4R0603

2

4

6

8

0/NC

642

RN70

10K

8P4R0603

+/-5%

*

7 8

7

Page 19

8

DCCBBAA

2D5V_DDR

21

FB6

D

FB L0805 60 Ohm

CLK_2.5V

BC686

10uF

*

16V, X5R, +/-10%

C1206

BC225

0.1uF

*

C0603

3D3V_SYS

21

CLK_3V

BC230

0.1uF

*

C0603

7

FB5

FB L0805 60 Ohm

BC215

0.1uF

*

C0603

*

BC231

0.1uF

*

C0603

*

BC220

0.1uF

C0603

3D3V_SYS

FB L0805 60 Ohm

BC216

0.1uF

C0603

FB7

2 1

BC221

0.1uF

*

C0603

6

BC217

0.1uF

*

C0603

*

CLK_2.5V

R53 SATA FOR SRC

BC245

0.1uF

*

C0603

BC222

0.1uF

C0603

*

5

Main Clock Generator

U11

ICS952703

1

VDDREF

11

VDDZ

13

R180

475

+/-1%

R0603

BC246

1nF

25V, NPO, +/-5%

C0603

19

28

29

5

8

18

24

25

32

44

48

39

45

41

34

36

35

VDDPCI

VDDPCI_1

AVDD48

VDDAGP

GNDREF

GNDZ

GNDPCI

GNDPCI_1

GND48

GNDAGP

VDDSRC

VDDAPIC

GNDCPU

GNDAPIC

GNDSRC

IREF

VDDA

GNDA

*(CPU_STOP#)PCICLK4

12_48MHz/SEL12_48#MHz*

24_48MHz/SEL24_48#MHz**~

SRCCLKT

SRCCLKC

CPUCLK_0T

CPUCLK_0C

CPUCLK_1T

IOAPIC1

IOAPIC0

AGPCLK0

AGPCLK1

ZCLK0

ZCLK1

*FS2/PCICLK_F0

*FS3/PCICLK_F1

PCICLK0

PCICLK1

*(PCI_STOP#)PCICLK3

PCICLK2

*(PD#)PCICLK5

**FS0/REF0

**FS1/REF1

**Mode/REF2

SDATA

SCLK

4

SATA FOR SRC

43

42

38

37

40

47

46

31

30

9

10

FS2

14

FS3

15

16

17

20

21

22

23

FS0

2

FS1

3

4

27

26

12

33

R186

10K

+/-5%

R0603

DUMMY

Damping Resistors

Place near to the

Clock Outputs

R161 22

R162 22

R163 10

R164 10

R165 0

R166 10

R167 10

R168 22

R169 22

R170 22

R171 22

RN64

7 8

5

3

*

1

33 8P4R0603

+/-5%

R181 33

R182 33

R183 33/NC

R187 22

R185 22

Frequency Selection

R188

10K

+/-5%

R0603

DUMMY

6

4

2

3

CPUCLK0

CPUCLK-0

748CCLK

PICCLK0

PICCLK1

AGPCLK0

AGPCLK1

ZCLK0

ZCLK1

OSCI

VOSCI

REFCLK2

USB12M

SIO48M

7 8

5

33

3

*

1

RN65

SMB_CLK_MAIN

SMB_DATA_MAIN

R1164

10K

+/-5%

R0603

DUMMY

2

CK_133M_CPU 6

CK_133M_CPUJ 6

CK_133M_S748 11

PICCLK0 7

PICCLK1 26

CK_66M_S748 11

ZCLK0 13

ZCLK1 25

CK_33M_SIO 40

CK_33M_1394 32

CK_33M_PCI5 31

CK_33M_PCI2 29

6

4

2

CK_14M_S964 26

CK_14M_AUDIO 38

CK_48M_SIO 40

SMB_CLK_MAIN 17,20,21,22,26

SMB_DATA_MAIN 17,20,21,22,26

REFCLK2

CPU

SB

NB&SB

3D3V_SYS

BC684 10pFC0603 DUMMY

*

R1161

49.9

+/-1%

R0603

CK_33M_PCI1 29

CK_33M_PCI3 30

CK_33M_PCI4 30

CK_33M_S964 25

*

BC860

10pF

C0603

DUMMY

1

CK_100M_SATA 27

CK_100M_SATAJ 27

R1162

49.9

+/-1%

R0603

CK_66M_AGP 24

*

BC856

10pF

C0603

DUMMY

CK_12M_USB 27

X1

BC247

33pF

C0603

5

6

1 2

XTAL-14.318MHz

*

3D3V_SYS

R190

10K

+/-5%

R0603

J8

Header_1X2

R193

10K

+/-5%

R0603

FS3FSB0

FS2

3D3V_SYS

FSB1

R191 10K

1

2

R197 10K

7

FSB07,26

SB--GPIO

FSB16,26

SB--GPIO

8

FS1

6

*

3D3V_SYS

FS0

BC861

22pF

50V, NPO, +/-5%

C0603

R189

10K

+/-5%

R0603

R192

10K

+/-5%

R0603

DUMMY

50V,NPO,+/-5%

X2

7

FSB_Sense[1] FSB_Sense[0] Bus Frequency

1 0 RESERVED

X1

BC248

33pF

*

50V,NPO,+/-5%

C0603

1 1 133 MHz

0 1 166 MHz

0 0 200 MHz

FS3 FS2 FS1 FS0 CPU SRC ZCLK AGP PCI

0 0 0 1 200.01 100.00 133.34 66.67 33.33

1 0 0 1 166.65 100.00 133.32 66.66 33.33

1 1 0 1 133.34 100.00 133.34 66.67 33.33

0 1 0 1

4

100.00 100.00 133.34 66.67 33.33

Title

Document Number Re v

Date: Sheet

3

CLK 952703

2

748A01

TECHNOLOGY COPR.

of

19 48Sunday, September 05, 2004

1

A

Page 20

8

DCCBBAA

7

6

5

4

3

2

1

Clock Buffer ( FOR 3 DDR SDRAM DIMMS )

1. Cypress CY28351C

D

CBVDD

CBVDD

2D5V_DDR

21

FB50

FB L0805 60 Ohm

BC754

0.1uF

*

C0603

SMB_CLK_MAIN17,19,21,22,26

SMB_DATA_MAIN17,19,21,22,26

SDCLKO_DDR12

SMB_CLK_MAIN

SMB_DATA_MAIN

SDCLKO_DDR

BC755

10nF

*

25V, Y5V, +80%/-20%

C0603

FB_OUT

2. ICS 93735

3. Hitachi CDCV851

4. Phaselink 102-08

5. Realtek RTM 680-648

U34

ICS 93705

15

VDDI2C

4

VDD

11

VDD

21

VDD

28

VDD

34

VDD

38

VDD

45

VDD

16

AVDD

17

AGND

12

SCLK

37

SDATA

13

CLK_IN

14

CLK_IN#

35

FB_IN

36

FB_IN#

FB_OUT#

GND1GND7GND8GND18GND24GND25GND31GND41GND42GND

CLK0

CLK1

CLK2

CLK3

CLK4

CLK5

CLK6

CLK7

CLK8

CLK9

CLK#0

CLK#1

CLK#2

CLK#3

CLK#4

CLK#5

CLK#6

CLK#7

CLK#8

CLK#9

FB_OUT

48

3

5

10

20

22

46

44

39

29

27

2

6

9

19

23

47

43

40

30

26

BFB_OUT FB_OUT

33

32

DDRCLK[0..8]

DDRCLK3

DDRCLK6

DDRCLK2

DDRCLK5

DDRCLK8

DDRCLK0

DDRCLK4

DDRCLK1

DDRCLK7

DDRCLKJ3

DDRCLKJ6

DDRCLKJ2

DDRCLKJ5

DDRCLKJ8

DDRCLKJ0

DDRCLKJ4

DDRCLKJ1

DDRCLKJ7

R1131 22

DDRCLKJ[0..8]

DDRCLK[0..8] 21,22

DDRCLKJ[0..8] 21,22

By-Pass Capacitors

Place near to the Clock Buffer

DDRCLK8

DDRCLK5

DDRCLK2

DDRCLK6

DDRCLK3

DDRCLK0

DDRCLK7

DDRCLK4

DDRCLK1

DDRCLKJ8

DDRCLKJ5

DDRCLKJ2

DDRCLKJ6

DDRCLKJ3

DDRCLKJ0

DDRCLKJ7

DDRCLKJ4

DDRCLKJ1

BC751 10pFC0603 DUMMY

*

BC753 10pFC0603 DUMMY

*

BC757 10pFC0603 DUMMY

*

BC759 10pFC0603 DUMMY