Fairchild Semiconductor MM74C923WMX, MM74C923N, MM74C923CW, MM74C923WM Datasheet

October 1987

Revised January 1999

MM74C922 • MM74C923 16-Key Encoder • 20-Key Encoder

© 1999 Fairchild Semiconductor Corporation DS006037.prf www.fairchildsemi.com

MM74C922 • MM74C923

16-Key Encoder • 20-Key Encoder

General Description

The MM74C922 and MM74C923 CMOS key encoders provide all the necessary logic to fully encode an array of

SPST switches. The keyboard scan can be imp lemented

by either an external clock or external capacitor. These

encoders also have on-chip pull-up devices which pe rmit

switches with up to 50 kΩ on resistance to be used. No

diodes in the switch array are needed to eliminate ghost

switches. The internal debounce circuit needs only a single

external capacitor and can be defeated by omitting the

capacitor. A Data Available output goes to a high level

when a valid keyboard entry has been m ade. The Data

Available output returns to a low level when the entered

key is released, even if another key is depressed. The Data

Available will return high to indicate acceptan ce of the new

key after a normal debou nce period; this t wo-key roll-over

is provided between any two switches.

An internal regist er remembers the last key pressed even

after the key is released. The 3 -STATE outputs provide for

easy expansion and bus operation and are LPTTL compatible.

Features

■ 50 kΩ maximum switch on resistance

■ On or off chip clock

■ On-chip row pull-up devices

■ 2 key roll-over

■ Keybounce elimination with single capacitor

■ Last key register at outputs

■ 3-STATE output LPTTL compatible

■ Wide supply range: 3V to 15V

■ Low power consumption

Ordering Code:

Device also available in Tape and Reel. Specify by appendin g s uf f ix let t er “X” to the ordering co de.

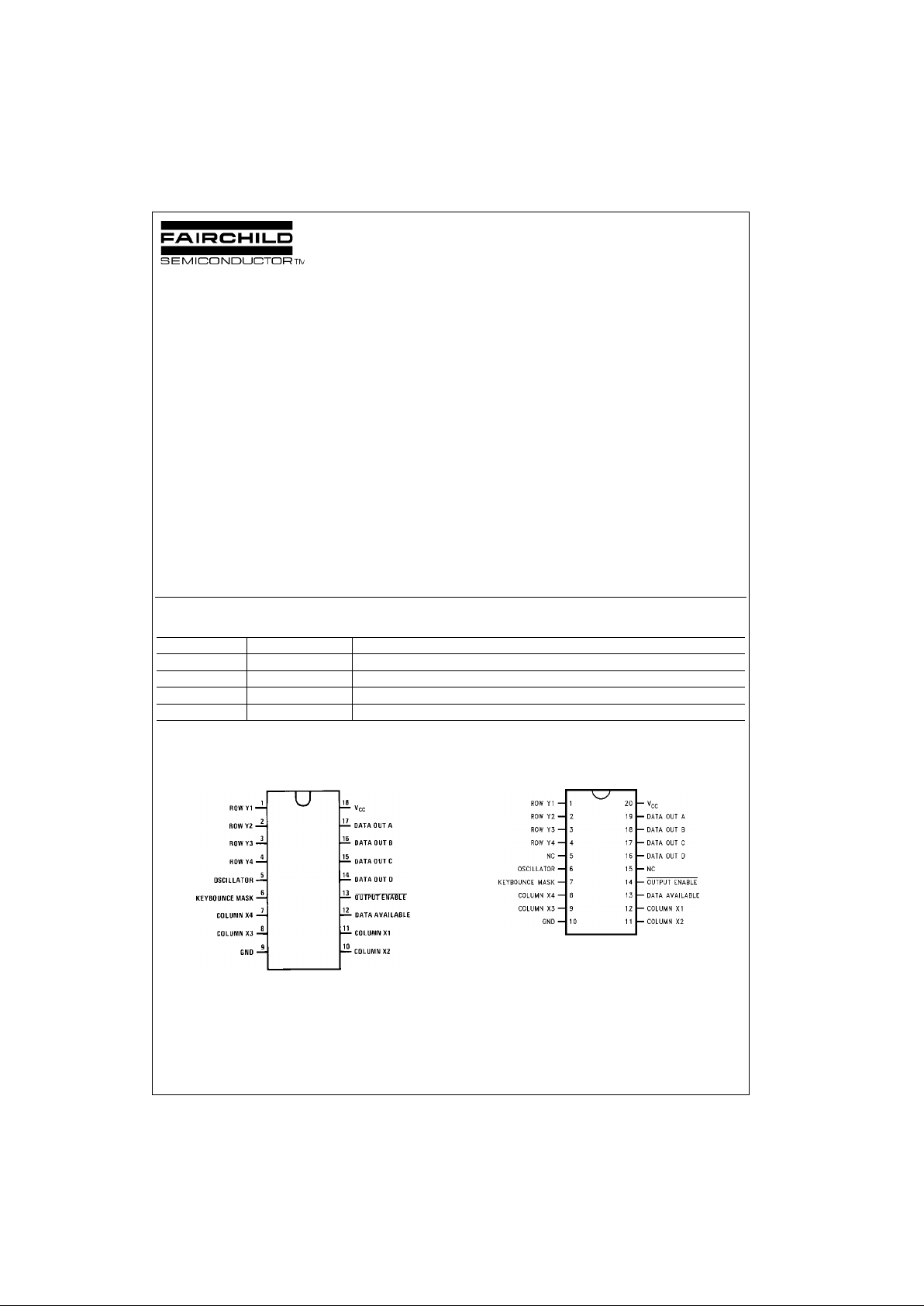

Connection Diagrams

Pin Assignment for DIP

Top View

MM94C922

Pin Assignment for SOIC

Top Vi ew

MM74C922

Order Number Package Number Package Description

MM74C922N N18A 18-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

MM74C922WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide

MM74C923WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide

MM74C923N N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

www.fairchildsemi.com 2

MM74C922 • MM74C923

Connection Diagrams (Continued)

Pin Assignment f or

DIP and SOIC Package

Top View

MM74C923

Truth Tables

(Pins 0 through 11)

(Pins 12 through 19)

Note 1: Omit for MM74C 922

Switch

Position

01234 5678910 11

Y1,X1 Y1,X2 Y1,X3 Y1,X4 Y2,X1 Y2,X2 Y2,X3 Y2,X4 Y3,X1 Y3,X2 Y3,X3 Y3,X4

D

AA 010101010101

TB 001100110011

AC 000011110000

OD 000000001111

UE

(Note 1)000000000000

T

Switch

Position

12 13 14 15 16 17 18 19

Y4,X1 Y4,X2 Y4,X3 Y4,X4 Y5(Note 1),X1Y5 (Note 1),X2Y5 (Note 1),X3 Y5 (Note 1),

X4

D

AA 0101 0 1 0 1

TB 0011 0 0 1 1

AC 1111 0 0 0 0

OD 1111 0 0 0 0

UE

(Note 1) 0 0 0 0 1 1 1 1

T

3 www.fairchildsemi.com

MM74C922 • MM74C923

Block Diagram

Loading...

Loading...