Fairchild Semiconductor KA1M0565R, KA1H0565R Datasheet

KA1M0565R/KA1H0565R

Fairchild Power Switch(FPS)

www.fairchildsemi.com

Features

• Precision fixed operating frequency

• KA1M0565R (67KHz),KA1H0565R (100KHz)

• Pulse by pulse over current limiting

• Over load protection

• Over voltage protection (Min. 23V)

• Internal thermal shutdown function

• Under voltage lock out

• Internal high voltage sense FET

•Auto restart

Description

The Fairchild Power Switch(FPS) product family is specially

designed for an off-line SMPS with minimal external

components. The Fairchild Power Switch(FPS) consist of

high voltage power SenseFET and current mode PWM

controller IC. PWM controller features integrated fixed

oscillator, under voltage lock out, leading edge blanking,

optimized gate turn-on/turn-off driver, thermal shut down

protection, over voltage protection, temperature compensated

precision current sources for loop compensation and fault

protection circuit. compared to discrete MOSFET and

controller or R

Power Switch(FPS) can reduce total component count,

design size, weight and at the same time increase &

efficiency, productivity, and system reliability. It has a basic

platform well suited for cost effective design in either a

flyback converter or a forward converter.

TO-220F-4L

1

1. GND 2. DRAIN 3. V

switching converter solution, a Fairchild

CC

4. FB

CC

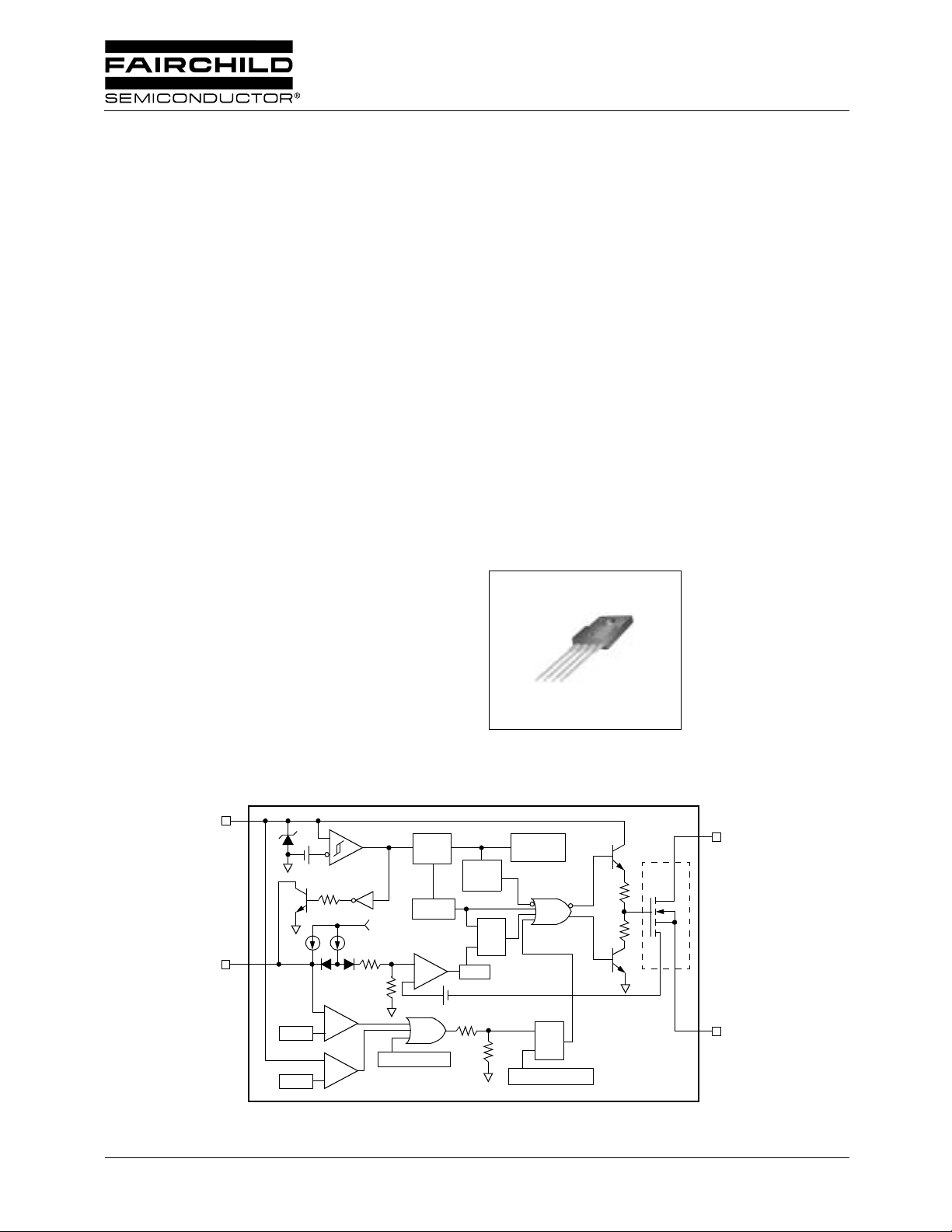

Internal Block Diagram

#3 V

CC

32V

A

µ

5

#4 FB

7.5V

25V

©2001 Fairchild Semiconductor Corporation

9V

1mA

2.5R

1R

+

−

+

−

Thermal S/D

OVER VOLTAGE S/D

OSC

−

+

5V

Vref

L.E.B

0.1V

Good

logic

S

R

Internal

bias

Q

S

R

Power on reset

#2 DRAIN

SFET

Q

#1 GND

Rev.1.0.2

KA1M0565R/KA1H0565R

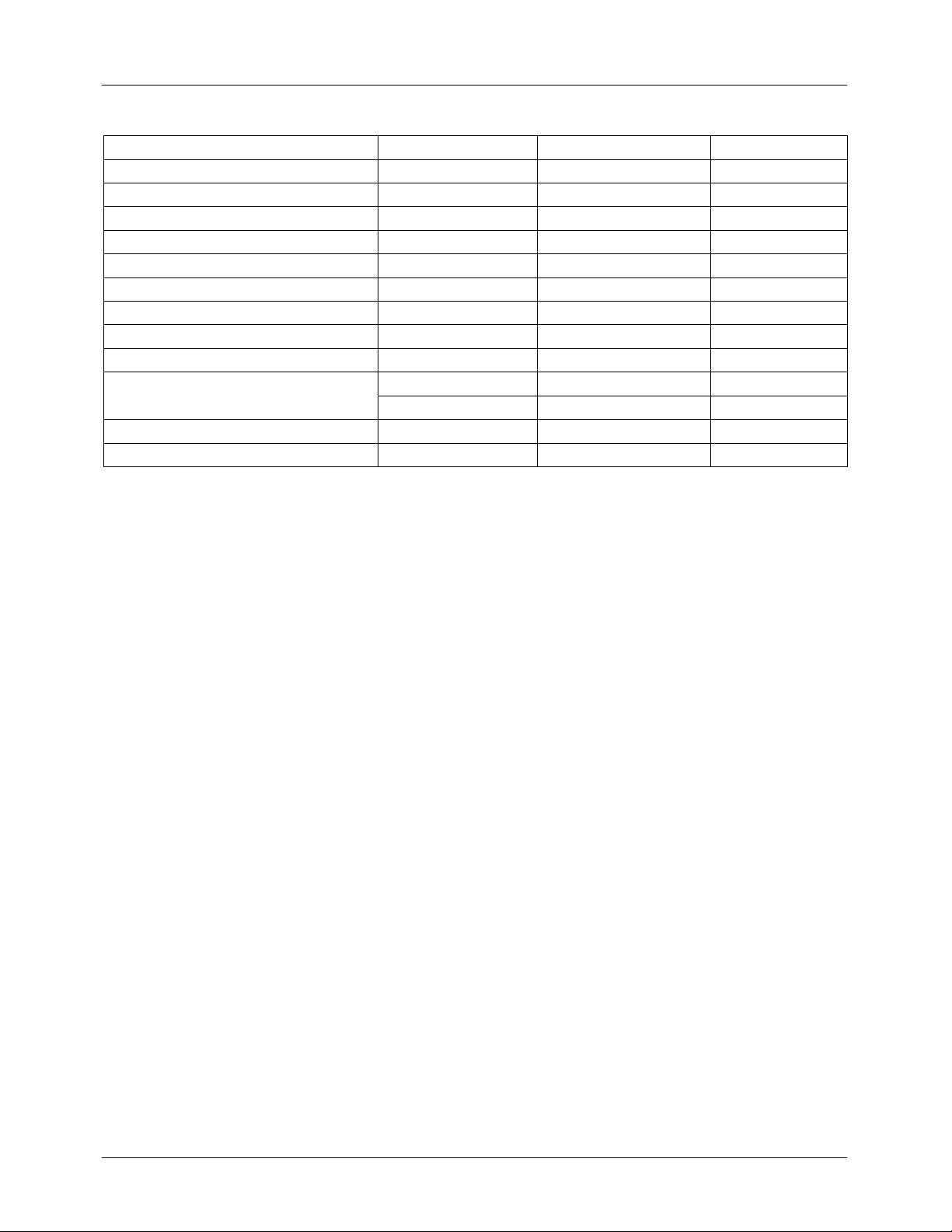

Absolute Maximum Ratings

Parameter Symbol Value Unit

Maximum Drain voltage

Drain Gate voltage (R

(1)

=1MΩ)V

GS

Gate-source (GND) voltage V

Drain current pulsed

Single pulsed avalanche energy

Continuous drain current (T

(2)

(3)

=25°C) I

C

Continuous drain current (TC=100°C) I

Maximum Supply voltage V

Input voltage range V

Total power dissipation

Operating ambient temperature T

Storage temperature T

Notes:

1. Tj=25°C to 150°C

2. Repetitive rating: Pulse width limited by maximum junction temperature

3. L=30mH, V

=50V, RG= 27Ω, starting Tj=25°C

DD

V

D,MAX

DGR

GS

I

DM

E

AS

D

D

CC,MAX

FB

P

D

650 V

650 V

±30 V

20 A

230 mJ

5.0 A

3.5 A

30 V

−0.3 to V

SD

140 W

Derating 1.11 W/°C

A

STG

−25 to +85 °C

−55 to +150 °C

DC

DC

DC

V

2

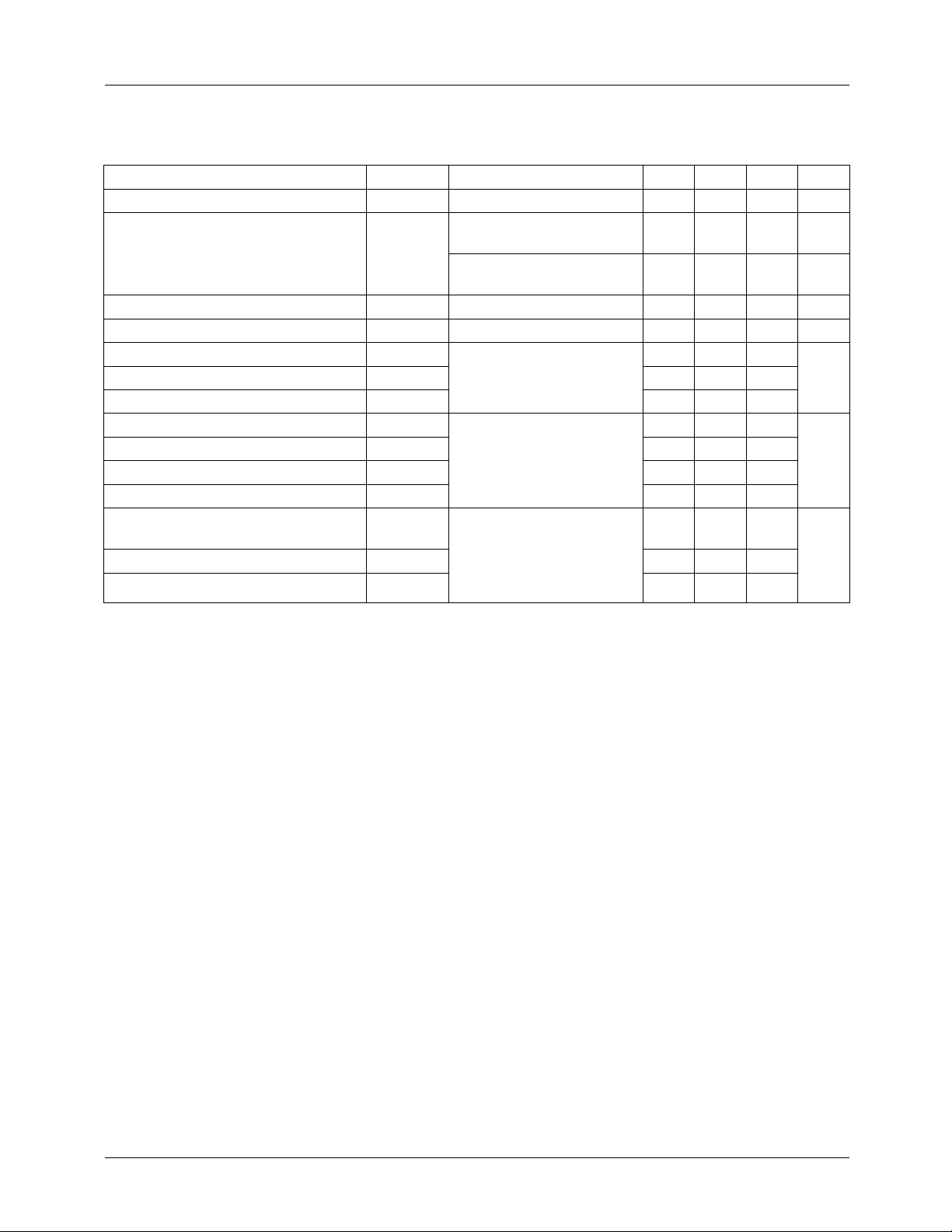

KA1M0565R/KA1H0565R

Electrical Characteristics (SFET part)

(Ta=25°C unless otherwise specified)

Parameter Symbol Condition Min. Typ. Max. Unit

Drain source breakdown voltage BV

Zero gate voltage drain current I

Static drain source on resistance

Forward transconductance

(note)

(note)

DSS

DSS

R

DS(ON)

gfs VDS=50V, ID=2.5A 2.5 - - S

Input capacitance Ciss

Reverse transfer capacitance Crss - 38.8 Turn on delay time t

d(on)

Rise time tr - - 150

Turn off delay time t

d(off)

Fall time tf - - 130

Total gate charge

(gate-source+gate-drain)

Qg

Gate source charge Qgs - 10.3 Gate drain (Miller) charge Qgd - 22.3 -

VGS=0V, ID=50µA 650 - - V

VDS=Max., Rating,

V

=0V

GS

=0.8Max., Rating,

V

DS

V

=0V, TC=125°C

GS

--50µA

- - 200 µA

VGS=10V, ID=2.5A - 1.76 2.2

- 1457 -

=0V, VDS=25V,

V

GS

f=1MHz

VDD=0.5BV

DSS

, ID=5.0A

--60

(MOSFET switching

time are essentially

independent of

- - 300

operating temperature)

V

=10V, ID=5.0A,

V

GS

DS

=0.5BV

(MOSFET

DSS

--56

switching time are

essentially independent of

operating temperature)

Ω

pFOutput capacitance Coss - 130 -

nS

nC

Note:

Pulse test: Pulse width ≤ 300µS, duty cycle ≤ 2%

1

S

--- -=

R

3

Loading...

Loading...