Fairchild Semiconductor DM74LS393N, DM74LS393MX, DM74LS393M, DM74LS393CW Datasheet

© 2000 Fairchild Semiconductor Corporation DS006434 www.fairchildsemi.com

August 1986

Revised March 2000

DM74LS393 Dual 4-Bit Binary Counter

DM74LS393

Dual 4-Bit Binary Counter

General Description

Each of these monolithic circuits contains eight masterslave flip-flops and additional gating to implement two individual four-bit counters in a single package. The

DM74LS393 comprises two independent four-bit binary

counters each having a clear and a clock input. N-bit binary

counters can be implemented with each package providing

the capability of divide-by-256. The DM74LS393 has parallel output s fro m ea c h c ount e r st ag e so th a t an y subm ul t ip l e

of the input count frequency is available for system -timing

signals.

Features

■ Dual version of the popular DM74LS93

■ DM74LS393 dual 4-bit binary counter with individual

clocks

■ Direct clear for each 4-bit counter

■ Dual 4-bit versions can significantly improve system

densities by reducing counter package count by 50%

■ Typical maximum count frequency 35 MHz

■ Buffered outputs reduce possibility of collector commu-

tation

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

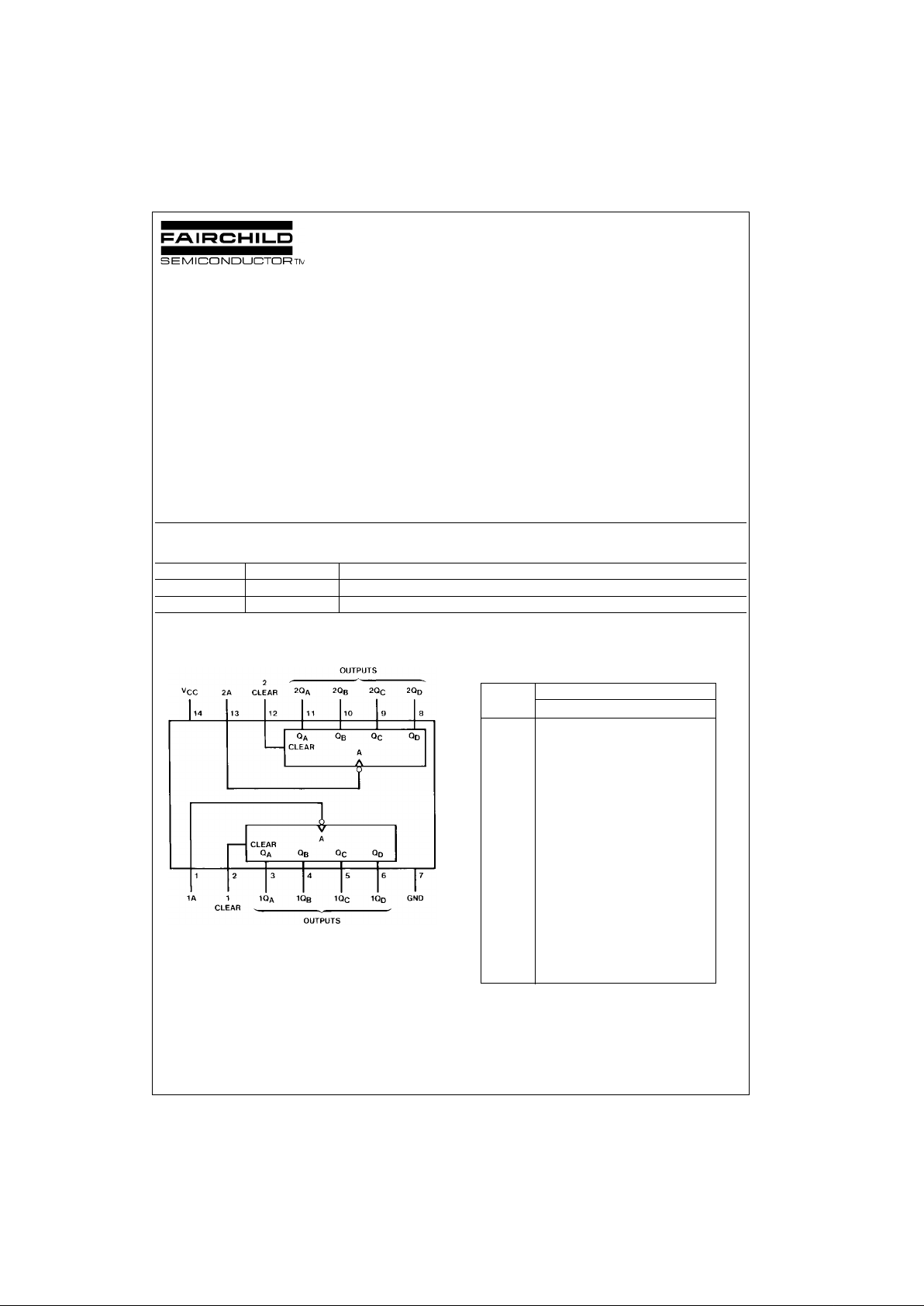

Connection Diagram Function Table

Counter Sequence (Each Counter)

H = HIGH Logic Level

L = LOW Logic Level

Order Number Package Number Package Description

DM74LS393M M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow

DM74LS373N N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Count

Outputs

Q

D

Q

C

Q

B

Q

A

0 LLLL

1 LLLH

2LLHL

3LLHH

4LHLL

5LHLH

6LHHL

7 LHHH

8 HLLL

9HLLH

10HLHL

11 H L H H

12 H H L L

13 H H L H

14 HHHL

15 HHHH

www.fairchildsemi.com 2

DM74LS393

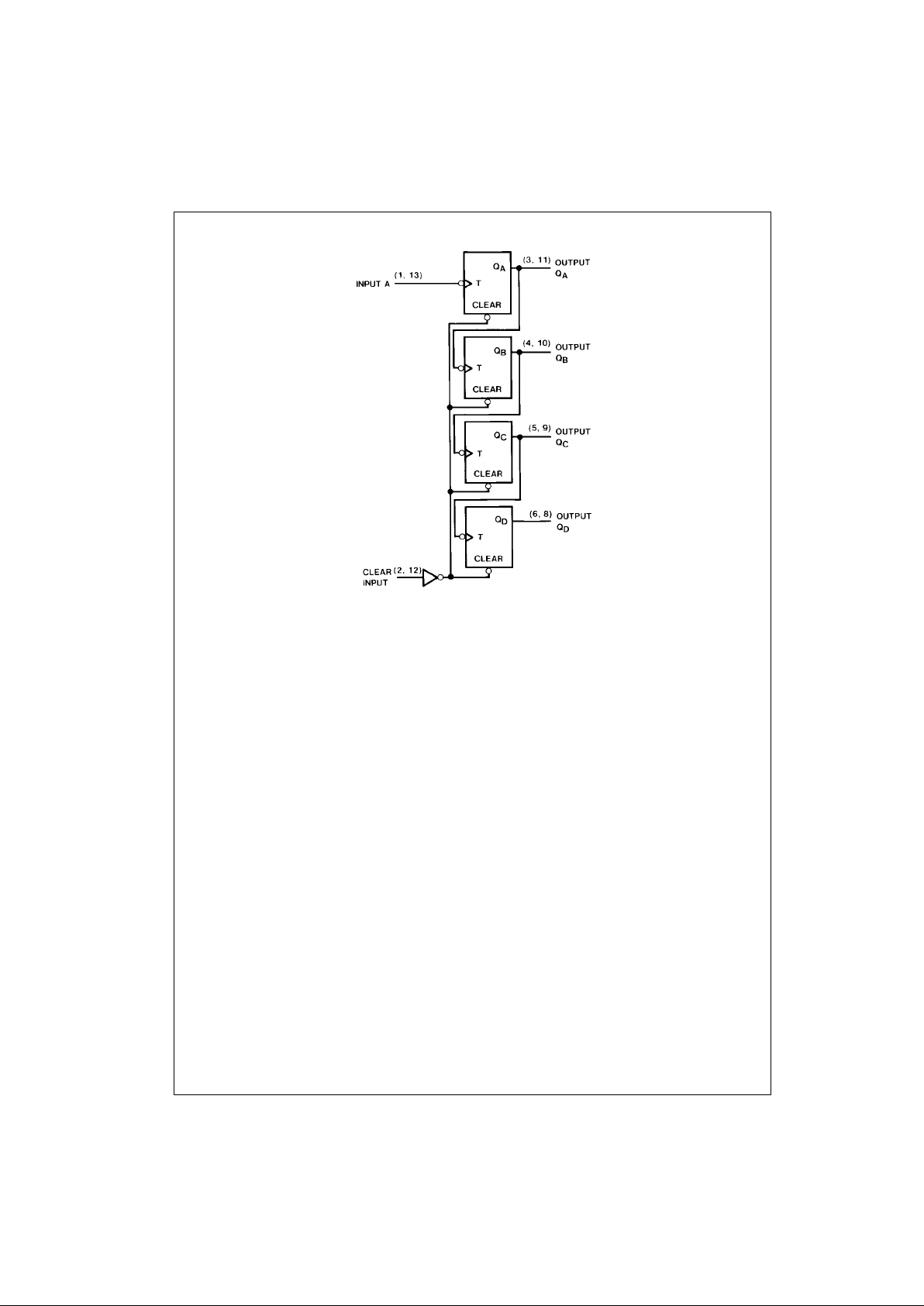

Logic Diagram