Fairchild Semiconductor DM74LS126AN, DM74LS126AMX, DM74LS126AM, DM74LS126ACW Datasheet

© 2000 Fairchild Semiconductor Corporation DS006388 www.fairchildsemi.com

August 1986

Revised March 2000

DM74LS126A Quad 3-STATE Buffer

DM74LS126A

Quad 3-STATE Buffer

General Description

This device contains four independent gates each of which

performs a non-invertin g buffer function . The outpu ts have

the 3-STATE feature. When enabled, the outputs exhibit

the low impedance characte ristics of a sta ndard LS outp ut

with additional drive capability to permit the driving of bus

lines without external r esistors. When disabled, both the

output transistors are turned OFF presenting a high-impedance state to the bus line. Thus the output will act n either

as a significant load n or as a d river. To minimize the possibility that two outputs will attempt to take a co mmon bus to

opposite logic levels, t he disable time is short er than the

enable time of the outputs.

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

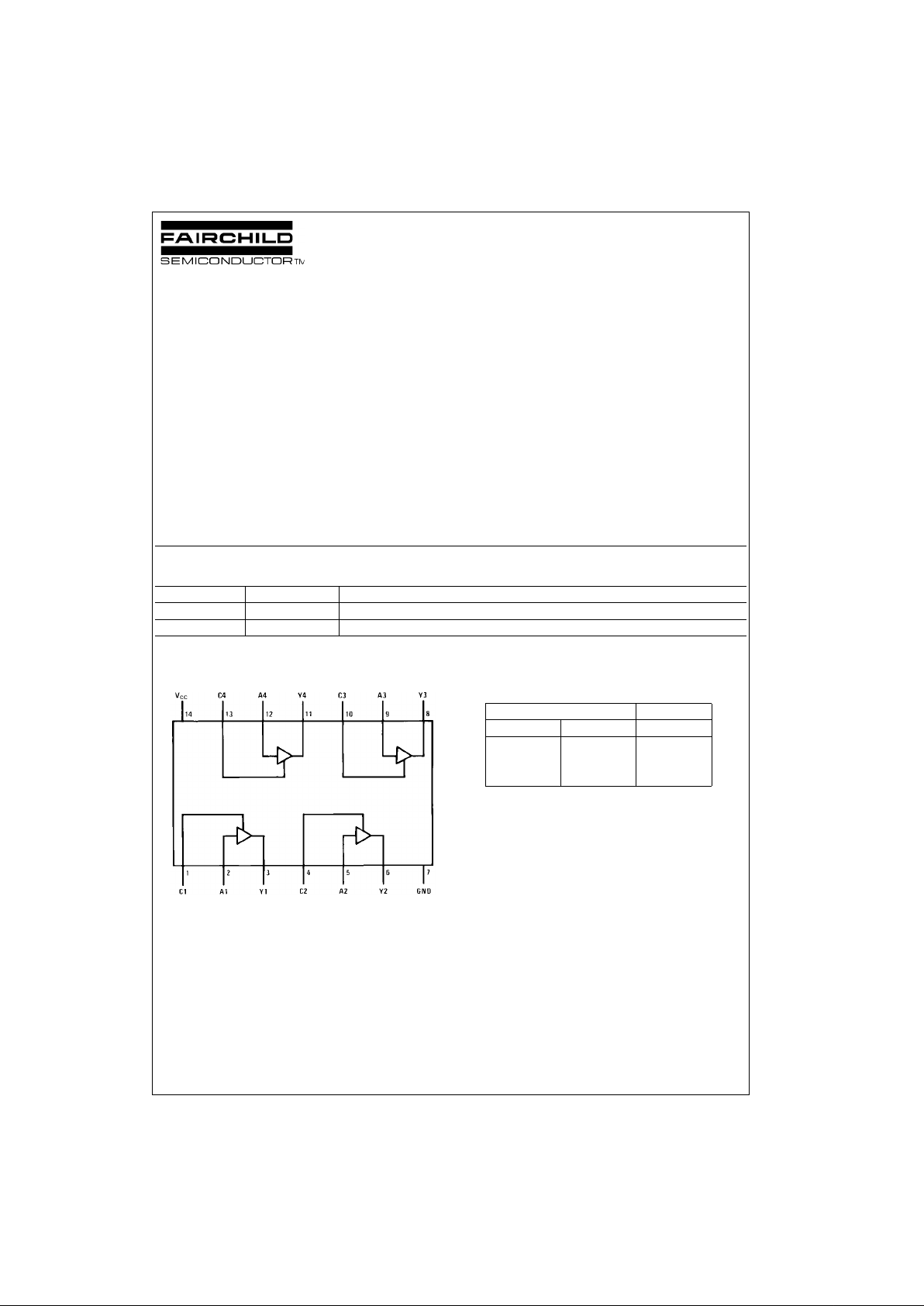

Connection Diagram Function Table

Y = A

H = HIGH Logic Level

L = LOW Logic Level

X = Either LOW or HIGH Logic Level

Hi-Z = 3-STATE (Outputs are disabled)

Order Number Package Number Package Description

DM74LS126AM M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow

DM74LS126AN N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Inputs Output

ACY

LHL

HHH

X L Hi-Z

www.fairchildsemi.com 2

DM74LS126A

Absolute Maximum Ratings(Note 1)

Note 1: The “Absolute Maximum Ratin gs” are those v alues beyon d which

the safety of the dev ice cannot be guaranteed. T he device sh ould not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The “Recommend ed O peratin g Cond itions” t able w ill defin e the co ndition s

for actual device operation.

Recommended Operating Conditions

Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

Note 2: All typicals are at VCC = 5V, TA = 25°C.

Note 3: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Switching Characteristics

VCC = 5V, TA = 25°C

Note 4: CL = 5pF.

Supply Voltage 7V

Input Voltage 7V

Operating Free Air Temperature Range 0°C to +70°C

Storage Temperature Range −65°C to +150°C

Symbol Parameter Min Nom Max Units

V

CC

Supply Voltage 4.75 5 5.25 V

V

IH

HIGH Level Input Voltage V

V

IL

LOW Level Input Voltage 0.8 V

I

OH

HIGH Level Output Current −2.6 mA

I

OL

LOW Level Output Current 24 mA

T

A

Free Air Operating Temperature 0 70 °C

Symbol Parameter Conditions Min

Typ

Max Units

(Note 2)

V

I

Input Clamp Voltage VCC = Min, II = −18 mA −1.5 V

V

OH

HIGH Level VCC = Min, IOH = Max

2.4 V

Output Voltage VIH = Min

V

OL

LOW Level VCC = Min, IOL = Max

0.35 0.5

Output Voltage VIL = Max, VIH = Min V

IOL = 12 mA, VCC = Min 0.25 0.4

I

I

Input Current @ Max Input Voltage VCC = Max, VI = 7V 0.1 mA

I

IH

HIGH Level Input Current VCC = Max, VI = 2.7V 20 µA

IIL LOW Level Input Current VCC = Max, VI = 0.4V −0.4 mA

I

OZH

Off-State Output Current with VCC = Max, VO = 2.4V

20 µA

HIGH Level Output Voltage Applied VIH = Min, VIL = Max

I

OZL

Off-State Output Current with VCC = Max, VO = 0.4V

−20 µA

LOW Level Output Voltage Applied VIH = Min, VIL = Max

I

OS

Short Circuit Output Current VCC = Max (Note 3) −20 −100 mA

I

CC

Supply Current VCC = Max 12 22 mA

RL = 667Ω

Symbol Parameter

CL = 50 pF CL = 150 pF

Units

Min Max Min Max

t

PLH

Propagation Delay Time LOW-to-HIGH Level Output 15 21 ns

t

PHL

Propagation Delay Time HIGH-to-LOW Level Output 18 22 ns

t

PZH

Output Enable Time to HIGH Level Output 30 36 ns

t

PZL

Output Enable Time to LOW Level Output 30 42 ns

t

PHZ

Output Disable Time from HIGH Level Output (Note 4) 25 ns

t

PLZ

Output Disable Time from LOW Level Output (Note 4) 25 ns

Loading...

Loading...