Fairchild Semiconductor DM74AS280M, DM74AS280N, DM74AS280MX Datasheet

© 2000 Fairchild Semiconductor Corporation DS006303 www.fairchildsemi.com

October 1986

Revised March 2000

DM74AS280 9-Bit Parity Generator/Checker

DM74AS280

9-Bit Parity Generator/Checker

General Description

These universal, 9-bit parity generators/checkers utilize

advanced Schottky high perfo rmance circuitry and featu re

odd/even outputs to facilitate operation of either odd or

even parity applications. Th e word leng th capab ility is ea sily expanded by cascading.

The DM74AS280 can be used to upgrade the performance

of most systems utilizing the ’180 parity gene rato r/c heck er.

Although the DM74AS280 is implemented without

expander inputs, the co rre spo ndin g function is provided by

the availability of an input at pin 4 and no internal connection at pin 3. This pe rmits the DM74AS280 to be substituted for the ’180 in existing designs to produce identical

function even if DM74AS280s are mixed with existing

’180s.

Features

■ Generates either odd or even parity for nine data lines

■ Inputs are buffered to lower the drive requirements

■ Can be used to upgrade existing systems using MSI

parity circuits

■ Cascadable for N-bits

■ Advanced oxide-isolated, ion-implanted Schottky

TTL process

■ Switching specifications at 50 pF

■ Switching specifications guaranteed over full

temperat ure and V

CC

range

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

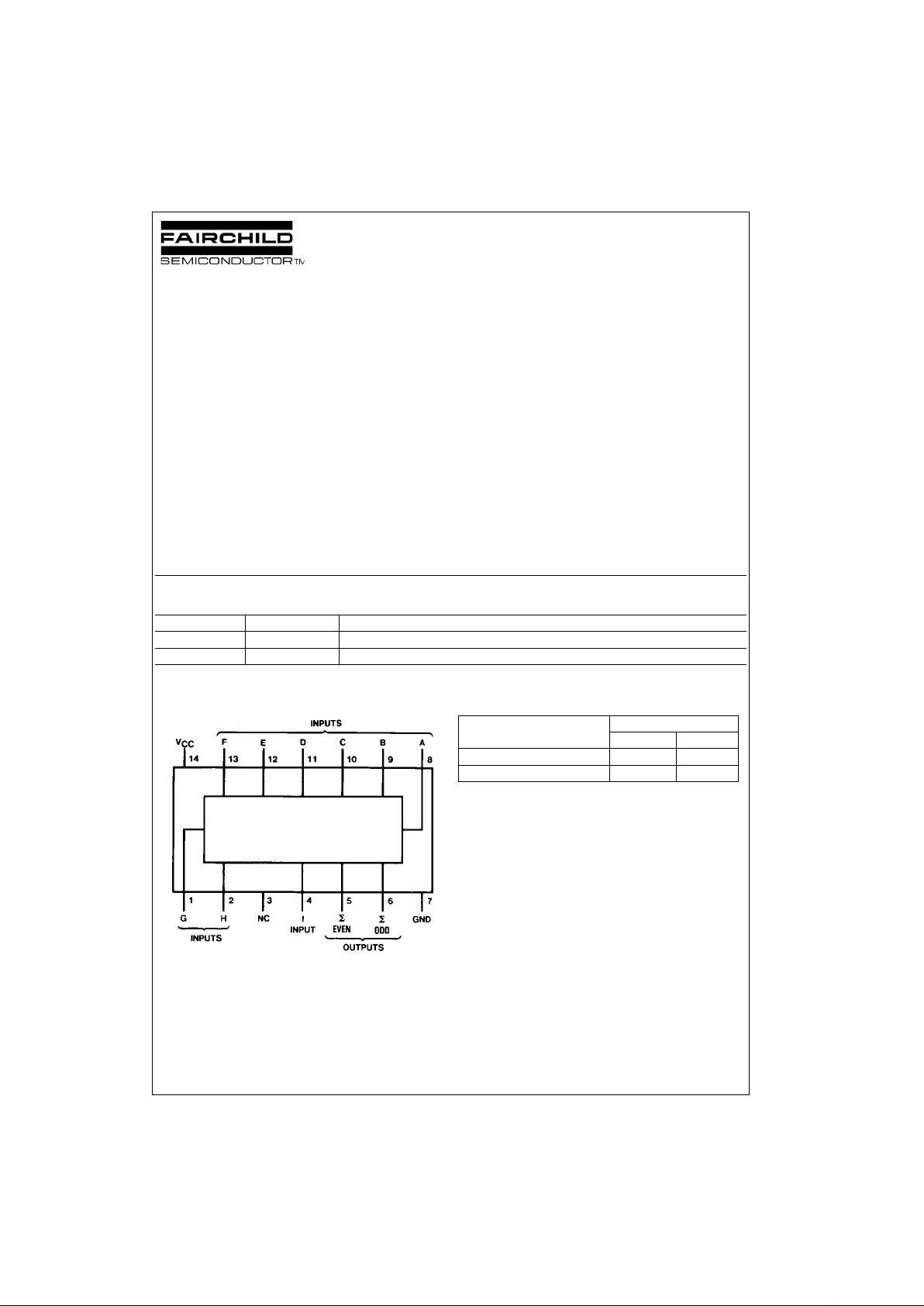

Connection Diagram Function Table

L = LOW State

H = HIGH State

Order Number Package Number Package Description

DM74AS280M M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

DM74AS280N N14A 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Number of Inputs (A thru I) Outputs

that are HIGH ∑Even ∑Odd

0, 2, 4, 6, 8 H L

1, 3, 5, 7, 9 L H

www.fairchildsemi.com 2

DM74AS280

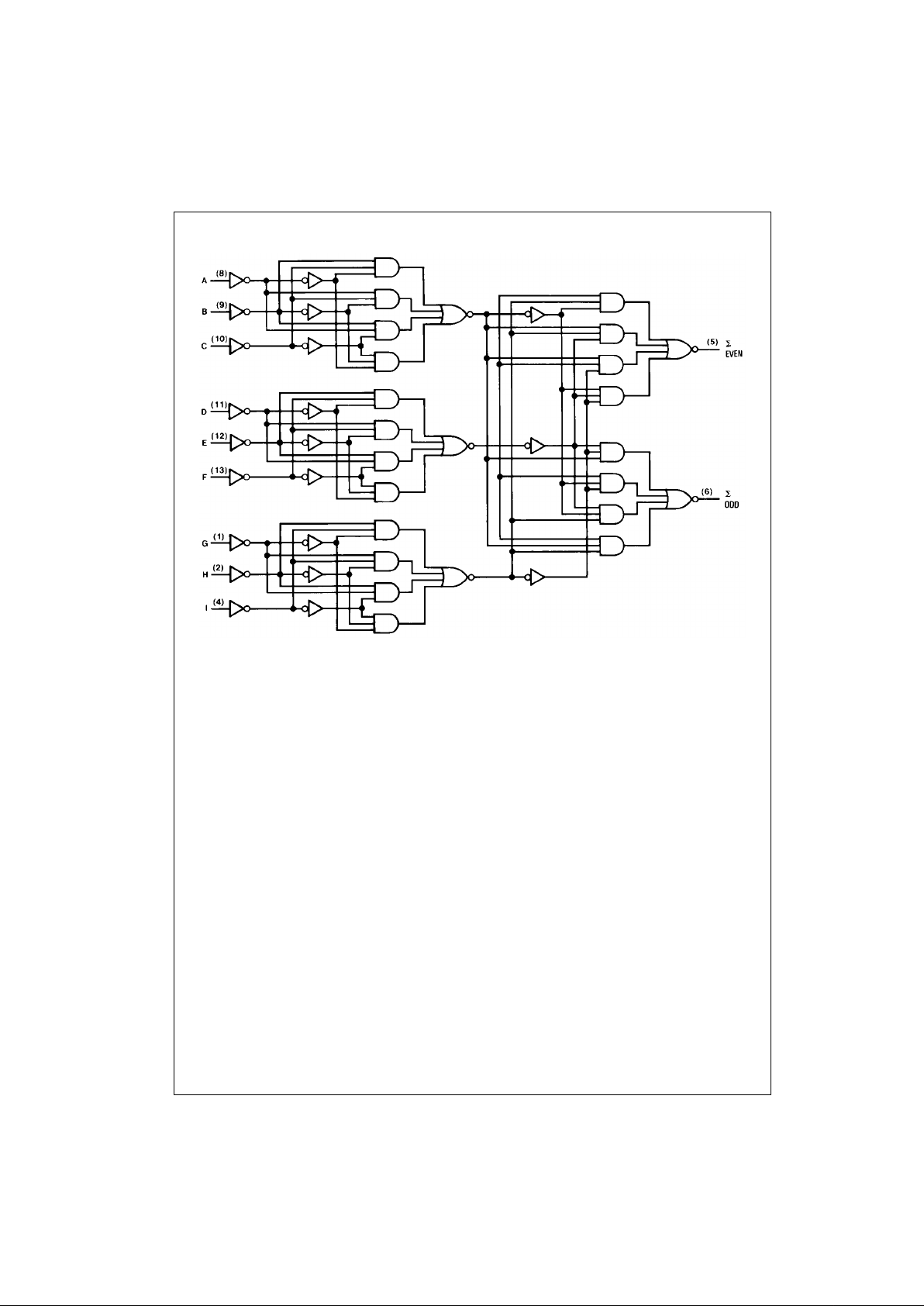

Logic Diagram

Loading...

Loading...