Fairchild Semiconductor DM74ALS174SJX, DM74ALS174SJ, DM74ALS174N, DM74ALS174MX, DM74ALS174M Datasheet

...

DM74ALS174 • DM74ALS175

Hex/Quad D-Type Flip-Flops with Clear

DM74ALS174 • DM74ALS175 Hex/Quad D-Type Flip-Flops with Clear

September 1986

Revised February 2000

General Description

These positive-edge-triggered flip-flops utilize TTL circuitry

to implement D-type flip-flop logic. Both have an asynchronous clear input, and the quad (DM74ALS175) version features complementary outputs from each flip-flop.

Information at the D i n put s m ee ting the se tup tim e req ui r ements is transferred t o the Q output s on the posi tive-go ing

edge of the clock pulse. Clock trigger ing occ urs a t a par ticular voltage level and is not directly related to the transition

time of the positive-goi ng pulse . When the clock in put is at

either the HIGH or LOW le vel, the D input signal has no

effect at the output.

Features

■ Advanced oxide-isolated ion-implanted Schottky TTL

process

■ Pin and functional compatible with LS family counterpart

■ Typical clock frequency maximum is 80 MHz

■ Switching performance guaranteed over full temperature

and V

supply range

CC

Ordering Code:

Ordering Code Package Number Package Description

DM74ALS174M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

DM74ALS174SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

DM74ALS174N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

DM74ALS175M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

DM74ALS175SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

DM74ALS175N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering cod e.

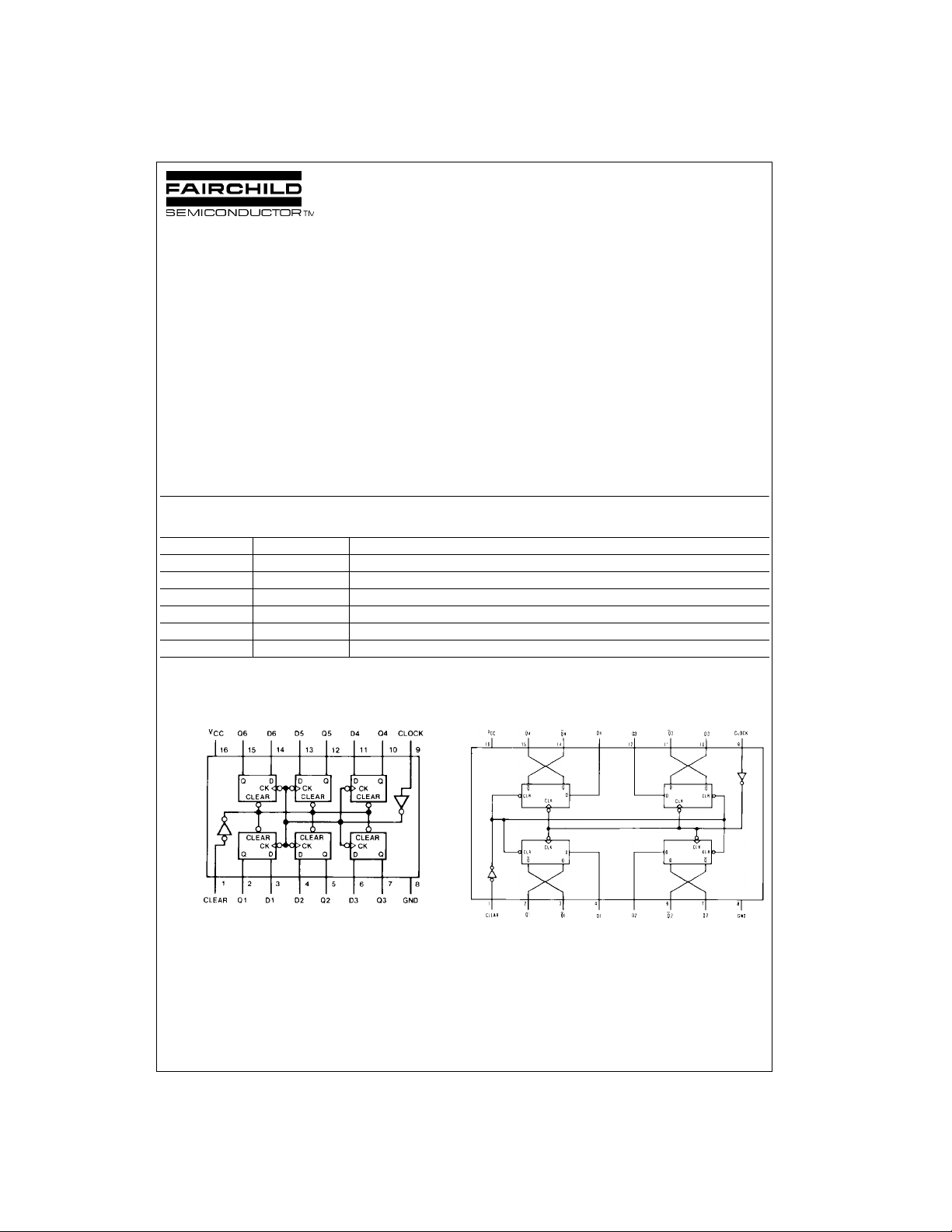

Connection Diagrams

DM74ALS174 DM74ALS175

© 2000 Fairchild Semiconductor Corporation DS006112 www.fairchildsemi.com

Function Table

Inputs Outputs

Clear Clock D Q Q

LXXLH

H ↑ HHL

H ↑ LLH

HLXQ

H = HIGH Level (steady state)

L = LOW Level (steady state)

X = Don’t Care

↑ = Transition from LOW-to-HIGH Level

= the level of Q before the indicated steady-state input conditions were established

Q

0

Note 1: applies to DM 74ALS175 only

DM74ALS174 • DM74ALS175

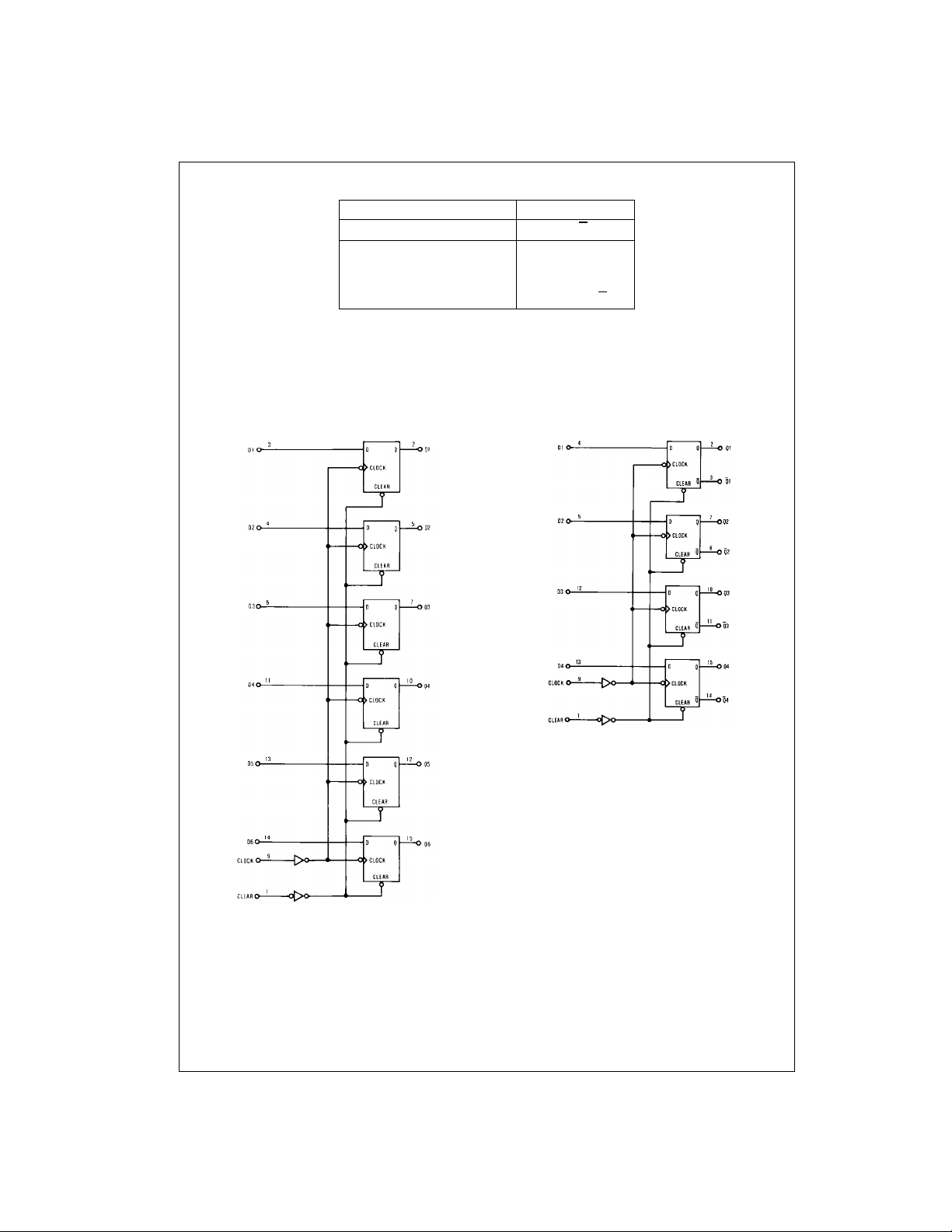

Logic Diagrams

DM74ALS174 DM74ALS175

(Note 1)

0

Q

0

www.fairchildsemi.com 2

Absolute Maximum Ratings(Note 2)

Supply Voltage 7V

Input Voltage 7V

Operating Free Air Temperature Range 0°C to +70°C

Storage Temperature Range −65°C to +150°C

Typical θ

JA

N Package 77.9°C/W

M Package 107.3°C/W

Note 2: The “Absolute M aximu m R atin gs” are t hose valu es b eyo nd w hich

the safety of the device cannot be guaranteed. The device should not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The “Recommend ed O peratin g Cond itions” t able w ill defin e the condit ions

for actual device operation.

Recommended Operating Conditions

Symbol Parameter Min Nom Max Units

V

CC

V

IH

V

IL

I

OH

I

OL

t

W

t

SETUP

t

HOLD

f

CLOCK

T

A

Note 3: The symbol ↑ indicates that the rising edg e of the clock is used as ref erence.

Supply Voltage 4.5 5 5.5 V

HIGH Level Input Voltage 2 V

LOW Level Input Voltage 0.8 V

HIGH Level Output Current −0.4 mA

LOW Level Output Current 8 mA

Pulse Width Clock

HIGH or LOW ns

Clear

LOW 10

10

Setup Time (Note 3) Data Input 10↑

Clear

Inactive State

6↑

Data Hold Time (Note 3) 0↑ ns

Clock Frequency 0 50 MHz

Free Air Operating Temperature 0 70 °C

DM74ALS174 • DM74ALS175

ns

3 www.fairchildsemi.com

Loading...

Loading...