Page 1

MVME2500

Installation and Use

P/N: 6806800L01H

January 2014

Embedded Computing for

Business-Critical Continuity

TM

Page 2

©

2014 Emerson

All rights reserved.

Trademarks

Emerson, Business-Critical Continuity, Emerson Network Power and the Emerson Network Power logo are trademarks and service

marks of Emerson Electric Co. © 2014 Emerson Electric Co. All other product or service names are the property of their respective

owners.

Intel® is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

Java™ and all other Java-based marks are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and other

countries.

Microsoft®, Windows® and Windows Me® are registered trademarks of Microsoft Corporation; and Windows XP™ is a trademark of

Microsoft Corporation.

PICMG®, CompactPCI®, AdvancedTCA™ and the PICMG, CompactPCI and AdvancedTCA logos are registered trademarks of the PCI

Industrial Computer Manufacturers Group.

UNIX® is a registered trademark of The Open Group in the United States and other countries.

Notice

While reasonable efforts have been made to assure the accuracy of this document, Emerson assumes no liability resulting from any

omissions in this document, or from the use of the information obtained therein. Emerson reserves the right to revise this document

and to make changes from time to time in the content hereof without obligation of Emerson to notify any person of such revision or

changes.

Electronic versions of this material may be read online, downloaded for personal use, or referenced in another document as a URL to

a Emerson website. The text itself may not be published commercially in print or electronic form, edited, translated, or otherwise

altered without the permission of Emerson,

It is possible that this publication may contain reference to or information about Emerson products (machines and programs),

programming, or services that are not available in your country. Such references or information must not be construed to mean that

Emerson intends to announce such Emerson products, programming, or services in your country.

Limited and Restricted Rights Legend

If the documentation contained herein is supplied, directly or indirectly, to the U.S. Government, the following notice shall apply

unless otherwise agreed to in writing by Emerson.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (b)(3) of the Rights in

Technical Data clause at DFARS 252.227-7013 (Nov. 1995) and of the Rights in Noncommercial Computer Software and

Documentation clause at DFARS 252.227-7014 (Jun. 1995).

Contact Address

Emerson Network Power - Embedded Computing

2900 South Diablo Way, Suite 190

Tempe, AZ 85282

USA

Page 3

Contents

Contents

About this Manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.2 Standard Compliances . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.3 Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.4 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.5 Product Identification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2 Hardware Preparation and Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2.2 Unpacking and Inspecting the Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.3 Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2.3.1 Environmental Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.3.2 Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.3.3 Equipment Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.4 Configuring the Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.5 Installing Accessories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.5.1 Rear Transition Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.5.2 PMC/XMC Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.6 Installing and Removing the Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.7 Completing the Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3 Controls, LEDs, and Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.1 Board Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.2 Front Panel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.2.1 Reset Switch. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.3 LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.3.1 Front Panel LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.3.2 Onboard LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.4 Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.4.1 Front Panel Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.4.1.1 RJ45 with Integrated Magnetics (J1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.4.1.2 Front Panel Serial Port (J4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

MVME2500 Installation and Use (6806800L01H)

3

Page 4

Contents

Contents

Contents

3.4.1.3 USB Connector (J5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.4.1.4 VMEBus P1 Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.4.1.5 VMEBus P2 Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.4.2 Onboard Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.4.2.1 Flash Program Connector (P7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.4.2.2 SATA Connector (J3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.4.2.3 PMC Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

3.4.2.4 JTAG Connector (P6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

3.4.2.5 COP Connector (P6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

3.4.2.6 SD Connector (J2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

3.4.2.7 XMC Connector (XJ2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.4.2.8 Miscellaneous P2020 Debug Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

3.5 Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.5.1 Geographical Address Switch (S1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

3.5.2 SMT Configuration Switch (S2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

4.1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

4.2 Chipset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

4.2.1 e500 Processor Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

4.2.2 Integrated Memory Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

4.2.3 PCI Express Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

4.2.4 Local Bus Controller (LBC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

4.2.5 Secure Digital Hub Controller (SDHC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

4.2.6 I2C Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

4.2.7 USB Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

4.2.8 DUART. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4.2.9 DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4.2.10 Enhanced Three-Speed Ethernet Controller (eTSEC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4.2.11 General Purpose I/O (GPIO). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4.2.12 Security Engine (SEC) 3.1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4.2.13 Common On-Chip Processor (COP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.2.14 P20x0 Hardware Configuration Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.3 System Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.4 Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4

MVME2500 Installation and Use (6806800L01H)

Page 5

Contents

4.4.1 Real Time Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.4.2 Internal Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

4.4.3 Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

4.4.4 FPGA Tick Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

4.5 Ethernet Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

4.6 SPI Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

4.6.1 SPI Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

4.6.2 SPI Flash Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

4.6.3 Firmware Redundancy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

4.6.4 Crisis Recovery. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

4.7 Front UART Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

4.8 Rear UART Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4.9 PMC/XMC Sites . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4.9.1 PMC Add-on Card . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

4.9.2 XMC Add-on Card . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

4.10 SATA Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

4.11 VME Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

4.11.1 Tsi148 VME Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

4.12 USB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

4.13 I2C Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

4.14 Reset/Control FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

4.15 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

4.15.1 Onboard Voltage Supply Requirement. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

4.15.2 Power Up Sequencing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

4.16 Clock Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

4.17 Reset Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

4.17.1 Reset Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.18 Thermal Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.19 Real-Time Clock Battery . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.20 Debugging Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

4.20.1 POST Code Indicator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

4.20.2 JTAG Chain and Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

4.20.3 Custom Debugging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

4.21 Rear Transition Module (RTM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

MVME2500 Installation and Use (6806800L01H)

5

Page 6

Contents

Contents

Contents

5 Memory Maps and Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

5.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

5.2 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

5.3 Flash Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

5.4 Linux Devices Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

5.5 Programmable Logic Device (PLD) Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.5.1 PLD Revision Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.5.2 PLD Year Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.5.3 PLD Month Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

5.5.4 PLD Day Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

5.5.5 PLD Sequence Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

5.5.6 PLD Power Good Monitor Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

5.5.7 PLD LED Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

5.5.8 PLD PCI/PMC/XMC Monitor Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

5.5.9 PLD U-Boot and TSI Monitor Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.5.10 PLD Boot Bank Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.5.11 PLD Write Protect and I2C Debug Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

5.5.12 PLD Test Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5.5.13 PLD Test Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5.5.14 PLD GPIO2 Interrupt Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.5.15 PLD Shutdown and Reset Control and Reset Reason Register . . . . . . . . . . . . . . . . . . . . . . 95

5.5.16 PLD Watchdog Timer Refresh Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

5.5.17 PLD Watchdog Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

5.5.18 PLD Watchdog Timer Count Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

5.6 External Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.6.1 Prescaler Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.6.2 Control Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

5.6.3 Compare High and Low Word Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

5.6.4 Counter High and Low Word Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

6 Boot System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103

6.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

6.2 Accessing U-Boot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

6.3 Boot Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

6.3.1 Booting from a Network . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

6

MVME2500 Installation and Use (6806800L01H)

Page 7

Contents

6.3.2 Booting from an Optional SATA Drive. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

6.3.3 Booting from a USB Drive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

6.3.4 Booting from an SD Card. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

6.3.5 Booting VxWorks Through the Network. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

6.4 Using the Persistent Memory Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

6.5 MVME2500 Specific U-Boot Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

6.6 Updating U-Boot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

7 Programming Model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

7.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

7.2 Reset Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

7.3 Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

7.4 I2C Bus Device Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

7.5 Ethernet PHY Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

7.6 Other Software Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

7.6.1 MRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

7.6.2 Real Time Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

7.6.3 Quad UART. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

7.6.4 LBC Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

7.7 Clock Distribution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

7.7.1 System Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

7.7.2 Real Time Clock Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

7.7.3 Local Bus Controller Clock Divisor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

A Replacing the Battery . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

A.1 Replacing the Battery . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

B Related Documentation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

B.1 Emerson Network Power - Embedded Computing Documents . . . . . . . . . . . . . . . . . . . . . . . . .129

B.2 Manufacturers’ Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

B.3 Related Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

MVME2500 Installation and Use (6806800L01H)

7

Page 8

Contents

Contents

Contents

Safety Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

Sicherheitshinweise . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

8

MVME2500 Installation and Use (6806800L01H)

Page 9

List of Tables

Table 1-1 Key Features of the MVME2500 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 1-2 Board Standard Compliances . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 1-3 Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 1-4 Available Board Variants . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 1-5 Available Board Accessories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 2-1 Environmental Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 2-2 Power Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 3-1 Front Panel LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 3-2 Onboard LEDs Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 3-3 Front Panel Tri-Speed Ethernet Connector (J1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 3-4 Front Panel Serial Port (J4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 3-5 USB Connector (J5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 3-6 VMEbus P1 Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 3-7 VMEbus P2 Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 3-8 Flash Programming Header (P7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 3-9 Custom SATA Connector (J3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 3-10 PMC J11 Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 3-11 PMC J12 Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 3-12 PMC J13 Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 3-13 PMC J14 Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 3-14 JTAG Connector (P6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 3-15 COP Header (P10) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 3-16 SD Connector (J2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 3-17 XMC Connector (XJ2) Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 3-18 P20x0 Debug Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 3-19 Geographical Address Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 3-20 Geographical Address Switch Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 4-1 Voltage Supply Requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 4-2 Thermal Interrupt Threshold . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 4-3 POST Code Indicator on the LED . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 4-4 Transition Module Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 5-1 Physical Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 5-2 Flash Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 5-3 Linux Devices Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 5-4 PLD Revision Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 5-5 PLD Year Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

MVME2500 Installation and Use (6806800L01H)

9

Page 10

List of Tables

Table 5-6 PLD Month Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

Table 5-7 PLD Day Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 5-8 PLD Sequence Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 5-9 PLD Power Good Monitor Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Table 5-10 PLD LED Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

Table 5-11 PLD PCI/PMC/XMC Monitor Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

Table 5-12 PLD U-Boot and TSI Monitor Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

Table 5-13 PLD Boot Bank Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 5-14 PLD Write Protect and I2C Debug Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Table 5-15 PLD Test Register 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 5-16 PLD Test Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 5-17 PLD GPIO2 Interrupt Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Table 5-18 PLD Shutdown and Reset Control and Reset Reason Register . . . . . . . . . . . . . . . . . . . . . . 95

Table 5-19 PLD Watchdog Timer Refresh Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

Table 5-20 PLD Watchdog Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Table 5-21 PLD Watchdog Timer Count Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

Table 5-22 Prescaler Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98

Table 5-23 Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 5-24 Compare High Word Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

Table 5-25 Compare Low Word Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .100

Table 5-26 Counter High Word Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

Table 5-27 Counter Low Word Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

Table 6-1 MVME2500 Specific U-Boot Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

Table 7-1 POR Configuration Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

Table 7-2 MVME2500 Interrupt List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

Table 7-3 I2C Bus Device Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 7-4 PHY Types and MII Management Bus Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118

Table 7-5 LBC Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Table 7-6 Clock Distribution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

Table 7-7 System Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

Table B-1 Emerson Network Power - Embedded Computing Publications . . . . . . . . . . . . . . . . . .129

Table B-2 Manufacturers’ Publications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

Table B-3 Related Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

10

MVME2500 Installation and Use (6806800L01H)

Page 11

List of Figures

Figure 1-1 Serial Number Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 3-1 Component Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 3-2 Front Panel LEDs, Connectors and Switches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 3-3 Front Panel LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 3-4 Onboard LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 3-5 Geographical Address Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 3-6 SMT Configuration Switch Position . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 4-1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 4-2 SPI Device Multiplexing Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 4-3 Clock Distribution Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure A-1 Battery Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

MVME2500 Installation and Use (6806800L01H)

11

Page 12

List of Figures

12

MVME2500 Installation and Use (6806800L01H)

Page 13

About this Manual

Overview of Contents

This manual is divided into the following chapters and appendices.

Introduction gives an overview of the features of the product, standard compliances,

mechanical data, and ordering information.

Hardware Preparation and Installation outlines the installation requirements, hardware

accessories, switch settings, and installation procedures.

Controls, LEDs, and Connectors describes external interfaces of the board. This includes

connectors and LEDs.

Functional Description includes a block diagram and functional description of major

components of the product.

Memory Maps and Registers contains information on system resources including system

control and status registers and external timers.

Boot System describes the boot loader software.

Programming Model contains additional programming information for the board.

Replacing the Battery contains the procedures for replacing the battery.

Related Documentation provides a listing of related product documentation,

manufacturer’s documents, and industry standard specifications.

Safety Notes summarizes the safety instructions in the manual.

Sicherheitshinweise is a German translation of the Safety Notes chapter.

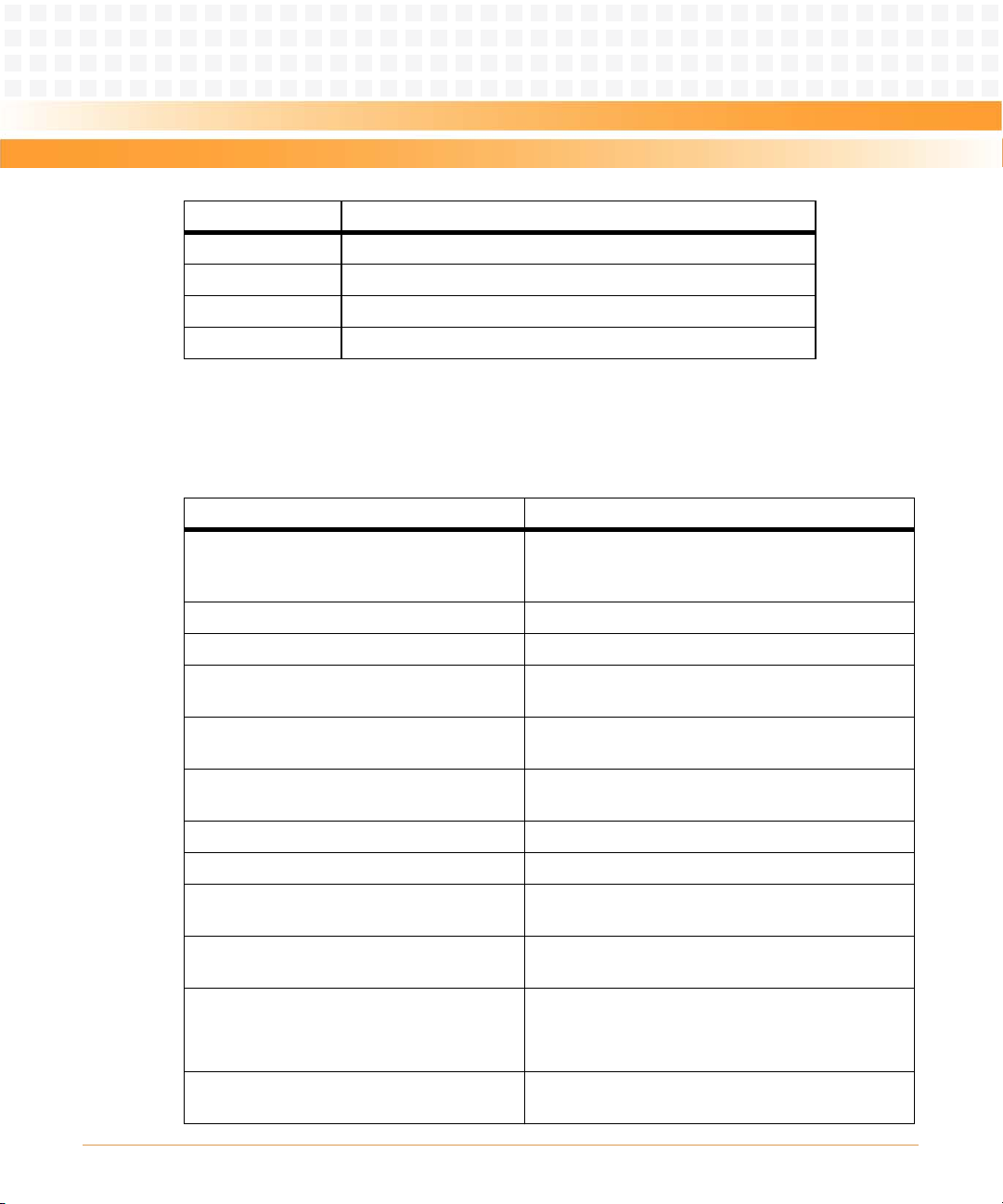

Abbreviations

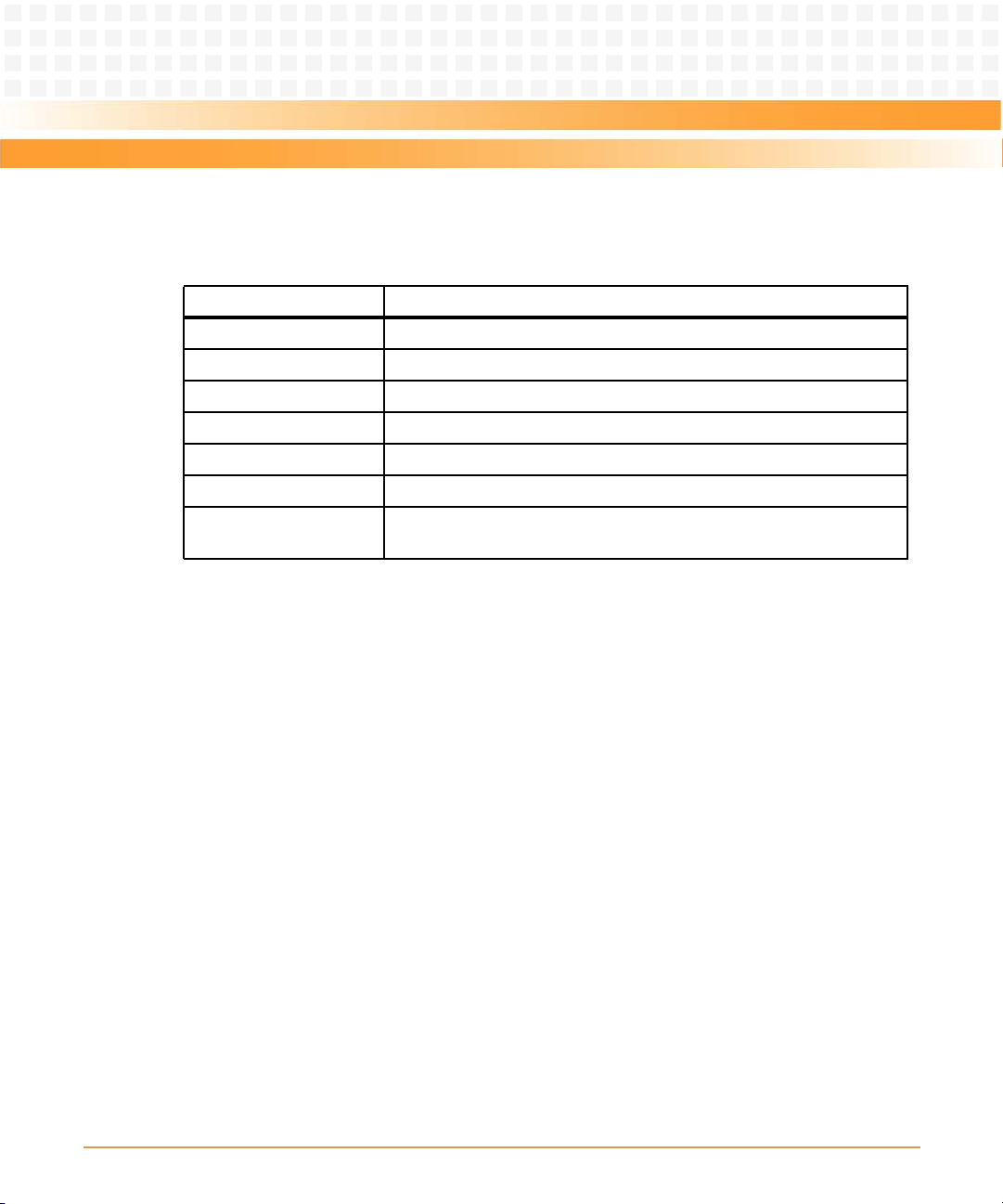

This document uses the following abbreviations:

Term Definition

CPLD Complex Programmable Logic Device

DDR Double Data Rate

DDR3 Double Data Rate 3

DMI Direct Media Interface

MVME2500 Installation and Use (6806800L01H)

13

Page 14

About this Manual

About this Manual

Term Definition

DUART Dual UART

EEPROM Erasable Programmable Read-Only Memory

FCC Federal Communications Commission

GB GigaByte

Gbit Gigabit

Gbps Gigabits per second

I/O Input/Output

IEEE Institute of Electrical and Electronics Engineers

LED Light Emitting Diode

MHz Megahertz

MCP Multi-Chip Package

MRAM Magnetoresistive Random Access Memory

14

OS Operating System

PCB Printed Circuit Board

PCI Peripheral Component Interconnect

PCI-E PCI Express

PCI-X Peripheral Component Interconnect eXtended

PIM PCI Mezzanine Card Input/Output Module

PLD Programmable Logic Device

PMC PCI Mezzanine Card (IEEE P1386.1)

PrPMC Processor PCI Mezzanine Card

RTC Real-Time Clock

RTM Rear Transition Module

SATA Serial AT Attachment

UART Universal Asynchronous Receiver-Transmitter

MVME2500 Installation and Use (6806800L01H)

Page 15

Term Definition

USB Universal Serial Bus

VITA VMEbus International Trade Association

VME Versa Module Eurocard

XMC PCI Express Mezzanine Card

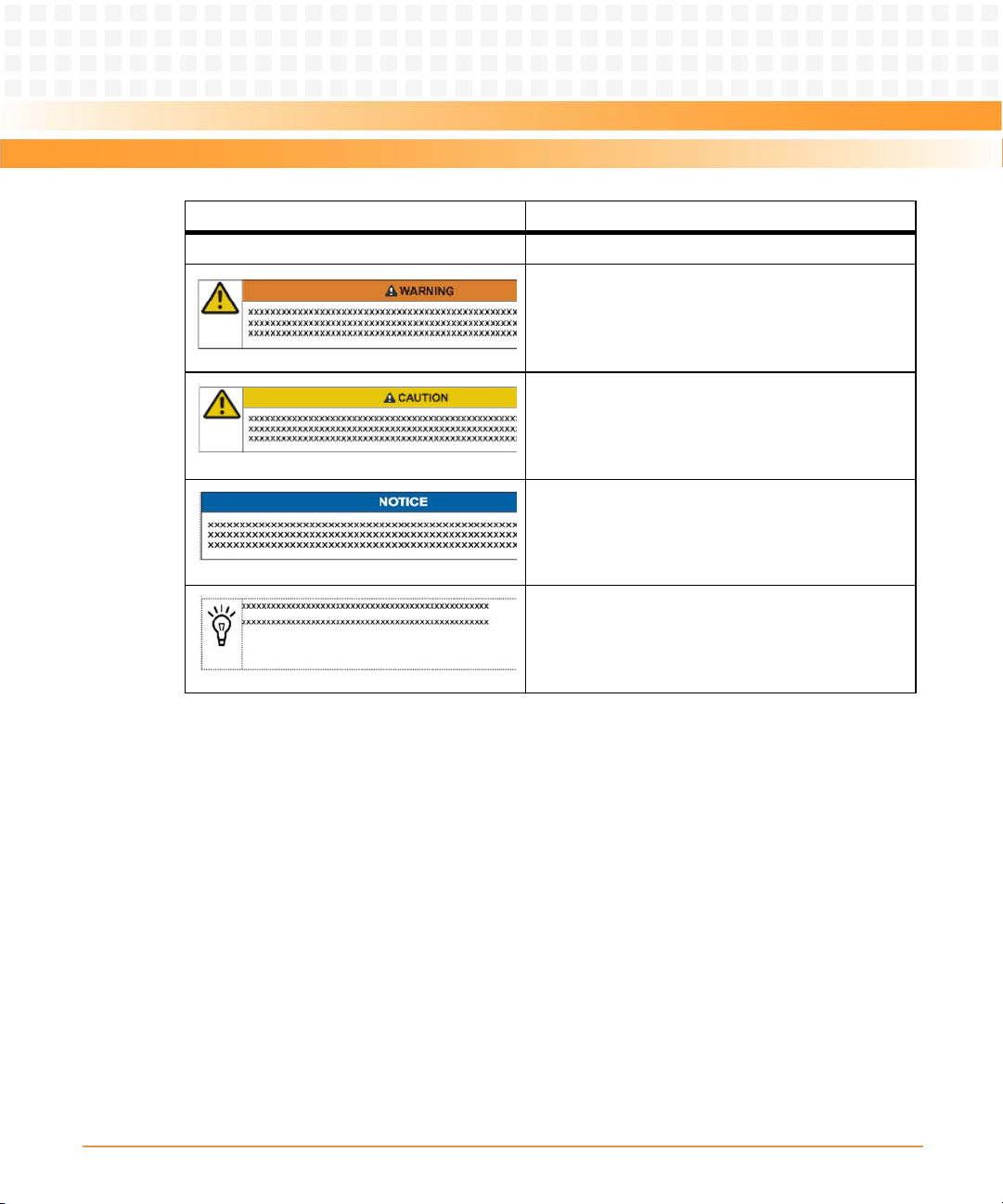

Conventions

The following table describes the conventions used throughout this manual.

Notation Description

0x00000000 Typical notation for hexadecimal numbers (digits are

About this Manual

0 through F), for example used for addresses and

offsets

0b0000 Same for binary numbers (digits are 0 and 1)

bold Used to emphasize a word

Screen Used for on-screen output and code-related

elements or commands in body text

Courier + Bold Used to characterize user input and to separate it

from system output

Reference Used for references and for table and figure

descriptions

File > Exit Notation for selecting a submenu

<text> Notation for variables and keys

[text] Notation for software buttons to click on the screen

and parameter description

... Repeated item for example node 1, node 2, ..., node

12

.

.

.

.. Ranges, for example: 0..4 means one of the integers

Omission of information from example/command

that is not necessary at the time being

0,1,2,3, and 4 (used in registers)

MVME2500 Installation and Use (6806800L01H)

15

Page 16

About this Manual

About this Manual

Notation Description

| Logical OR

Indicates a hazardous situation which, if not avoided,

could result in death or serious injury

Indicates a hazardous situation which, if not avoided,

may result in minor or moderate injury

Indicates a property damage message

No danger encountered. Pay attention to important

information

16

MVME2500 Installation and Use (6806800L01H)

Page 17

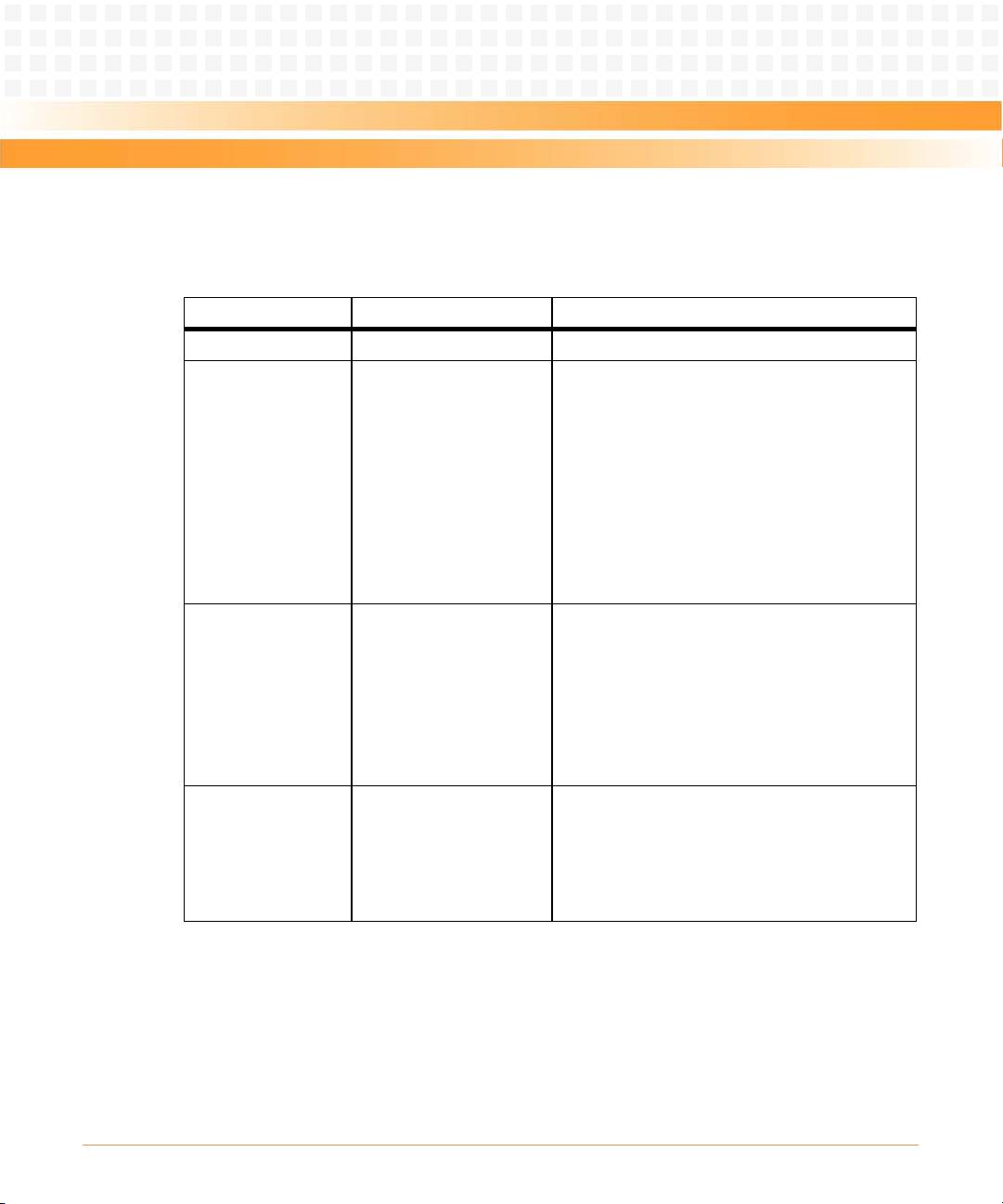

Summary of Changes

This manual has been revised and replaces all prior editions.

Part Number Publication Date Description

6806800L01A June 2010 First edition

6806800L01B October 2010 This version includes updates and revisions

About this Manual

for the EA release of the MVME2500.

Table 1.3. Added mechanical data.

Table 4-3. Removed the following

commands: brd_reset, irqinfo, mac. Added

soft_reset.

Table 4-1. Removed: L2 SRAM, L1 for stack

and Boot Page entries.

Changed all instances of "via" to "through".

Impelemented editorial changes.

6806800L01C May 2011 Updated Controls, LEDs, and Connectors by

adding the following.

– Board Layout

– Front Panel Connectors

– Onboard Connectors

Added Functional Description

Applied editorial edits

6806800L01D May 2011 Edited Memory Maps and Registers

Edited Programming Model

Edited Figure "Component Layout"

Edited Figure "Onboard LEDs"

Added Front Panel Serial Port (J4)

MVME2500 Installation and Use (6806800L01H)

17

Page 18

About this Manual

About this Manual

Part Number Publication Date Description

6806800L01E July 2011 Updated Table "Available Board Variants" on

6806800L01F August 2011 Changed title of Section 3.4.1 to Front Panel

6806800L01G January 2013 Updated Standard Compliances on page 21.

6806800L01H January 2014 Added Flash Memory Map on page 82 and

page 22.

Updated Appendix B, Related

Documentation, on page 129.

Connector s.

Edited Front Panel Serial Port (J4).

Updated Figure "Component Layout" on

page 35 to include proper label for XMC

connectors.

Updated Safety Notes and

Sicherheitshinweise.

updated SPI Flash Memory on page 67.

18

MVME2500 Installation and Use (6806800L01H)

Page 19

Introduction

1.1 Overview

The MVME2500 is a VMEbus board based on the Freescale QorlQ P2010 (single-core) or P2020

(dual-core) processor. It has a 6U form-factor and has an expansion slot for an optional PCI

Mezzanine Card (PMC) or PCI eXpress Mezzanine Card (XMC). It comes with either 1 GB or 2 GB

of DDR3 SDRAM, and is offered with either IEEE 1101.10 compliant or SCANBE ejector handles.

The front panel I/O configuration consists of two RJ45 10/100/1000BASE-T Ethernet ports, a

USB 2.0 port, a Micro DB9 RS-232 serial console port, and a reset/abort switch. It also has an

LED to signal board failure and another LED that can be configured in the LED register.

The rear I/O includes support for VMEbus (Legacy VME, VME 64, VME64x, and 2eSST), rear

PMC/XMC I/O, RTM I/O (through VME P2), two 10/100/1000BASE-T Ethernet, four UART, and

RTM I2C/Presence/Power. See the table below for a summary of the features of the

MVME2500.

Chapter 1

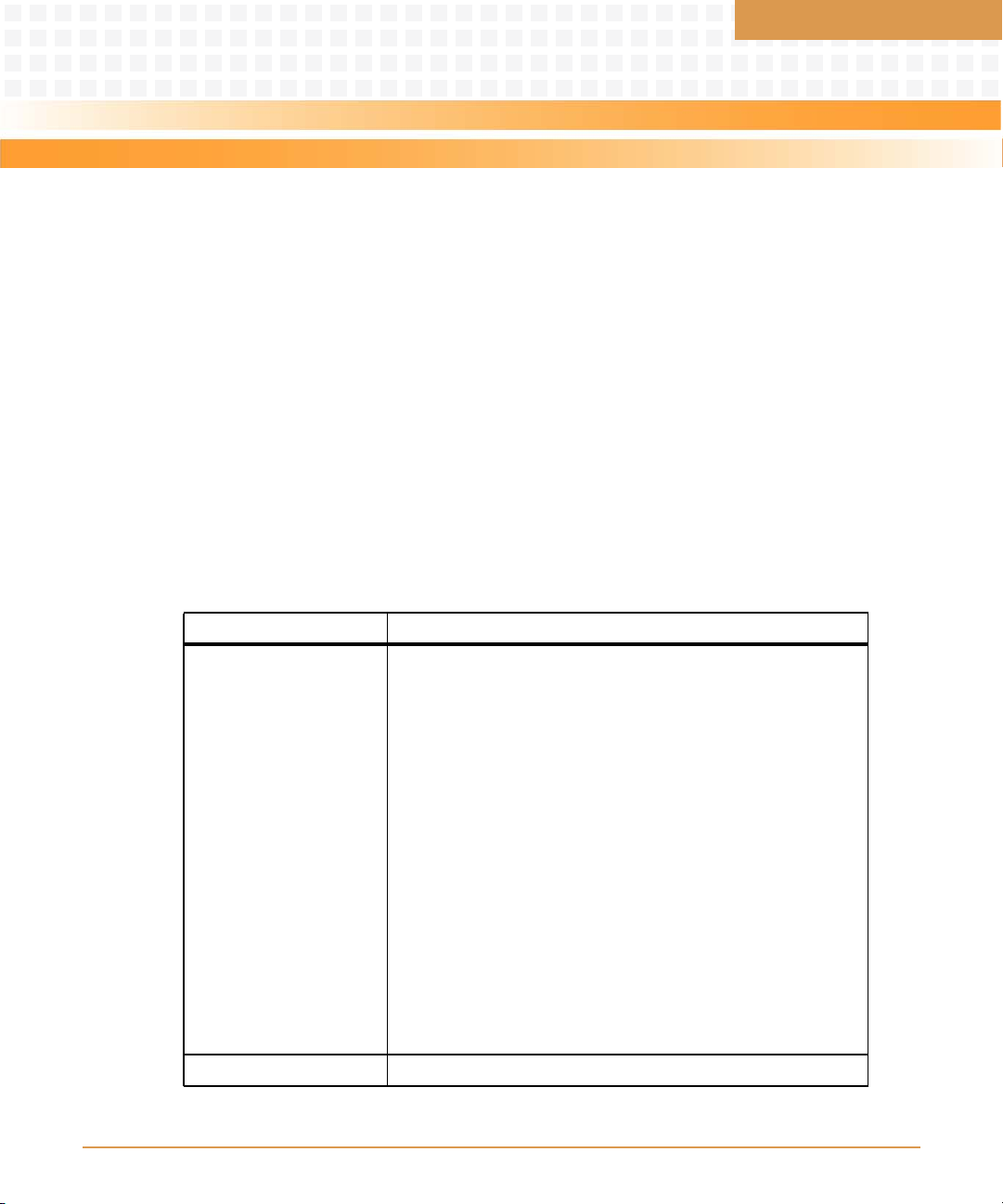

Table 1-1 Key Features of the MVME2500

Function Features

Processor Freescale QorIQ P2010 (single-core) or P2020 (dual-core)

800 MHz or 1000 MHz core frequency

512 KB L2 cache

Three 10/100/1000 Mbps enhanced three-speed Ethernet

controllers (eTSECs)

Two PCI-E 1.0a x1 interface controllers

One PCI-E 1.0a x2 interface controller

USB 2.0 interface

Enhanced secure digital host controller

DDR3 memory controller at 800 MT/s

SPI interface (four chip selects, but only two are used on the

board)

Enhanced local bus controller

UART

Two I2C interfaces

Programmable interrupt controller

Memory 1 GB or 2 GB DDR3 soldered chip memory without ECC

MVME2500 Installation and Use (6806800L01H)

19

Page 20

Introduction

Table 1-1 Key Features of the MVME2500 (continued)

Function Features

Front panel I/O Micro DB9 RS-232 serial console port

Backplane I/O VME Bus

USB 2.0

Two RJ45 10/100/1000BASE-T Ethernet

Reset/Abort switch

Fail LED and User LED

PMC/XMC front panel I/O (optional)

RTM I/O (through VME P2)

PMC/XMC I/O with P4 I/O

Two 10/100/1000BASE-T Ethernet

Four UART

RTM I2C/Presence/Power

Expansion Expansion site 1:

PMC supporting PCI-X 64/33 interface

XMC supporting PCI-E 1.0a x2 interface

Expansion site 2:

SATA drive kit

Boot Flash 16 MB SPI Flash

Persistent Data Storage 512 KB MRAM

User Flash SDHC Socket

I2C Devices Real-Time Clock

Board Temperature Sensor

8 KB VPD EEPROM

Two 64 KB User EEPROM

CPLD Watchdog, timers, and registers

Boot Firmware U-Boot-based firmware image in 16 MB SPI Flash. This flash is split

into two 8 MB chips.

20

MVME2500 Installation and Use (6806800L01H)

Page 21

Table 1-1 Key Features of the MVME2500 (continued)

Function Features

Operating System Based from BSP provided by Freescale which is based from

standard Linux version 2.6.32-rc3

Development tool is ltib 9.1.1 (Linux Target Image Builder)

from Freescale

VxWorks

1.2 Standard Compliances

The product is designed to meet the following standards. Results are pending until testing is

finished.

Table 1-2 Board Standard Compliances

Introduction

Standard Description

EN 60950-1/A11:2009

IEC 60950-1:2005 2nd Edition

CAN/CSA C22.2 No 60950-1

FCC Part 15, Subpart B, Class A (nonresidential)

ICES-003, Class A (non-residential)

EMC Directive 89/336/EEC

EN55022 Class B

EN55024

AS/NZS CISPR 22, Class A

EN300386

ETSI EN 300 019 series Environmental Requirements

Directive 2011/65/EU Directive on the restriction of the use of certain

Safety Requirements (legal)

EMC requirements (legal) on system level

(predefined Emerson system)

hazardous substances in electrical and electronic

equipment (RoHS)

For Declaration of Conformity, refer MVME2500 Series Declaration of Conformity.

MVME2500 Installation and Use (6806800L01H)

21

Page 22

Introduction

1.3 Mechanical Data

The following table provides details about the dimensions and weight of the board.

Table 1-3 Mechanical Data

Feature Value

Height 233.44 mm (9.2 inches)

Depth 160.0 mm (6.3 inches)

Front Panel Height 261.8 mm (10.3 inches)

Width 19.8 mm (0.8 inches)

Max. Component Height 14.8 mm (0.58 inches)

Weight 400 grams (standard variant), 700 grams (ET variants)

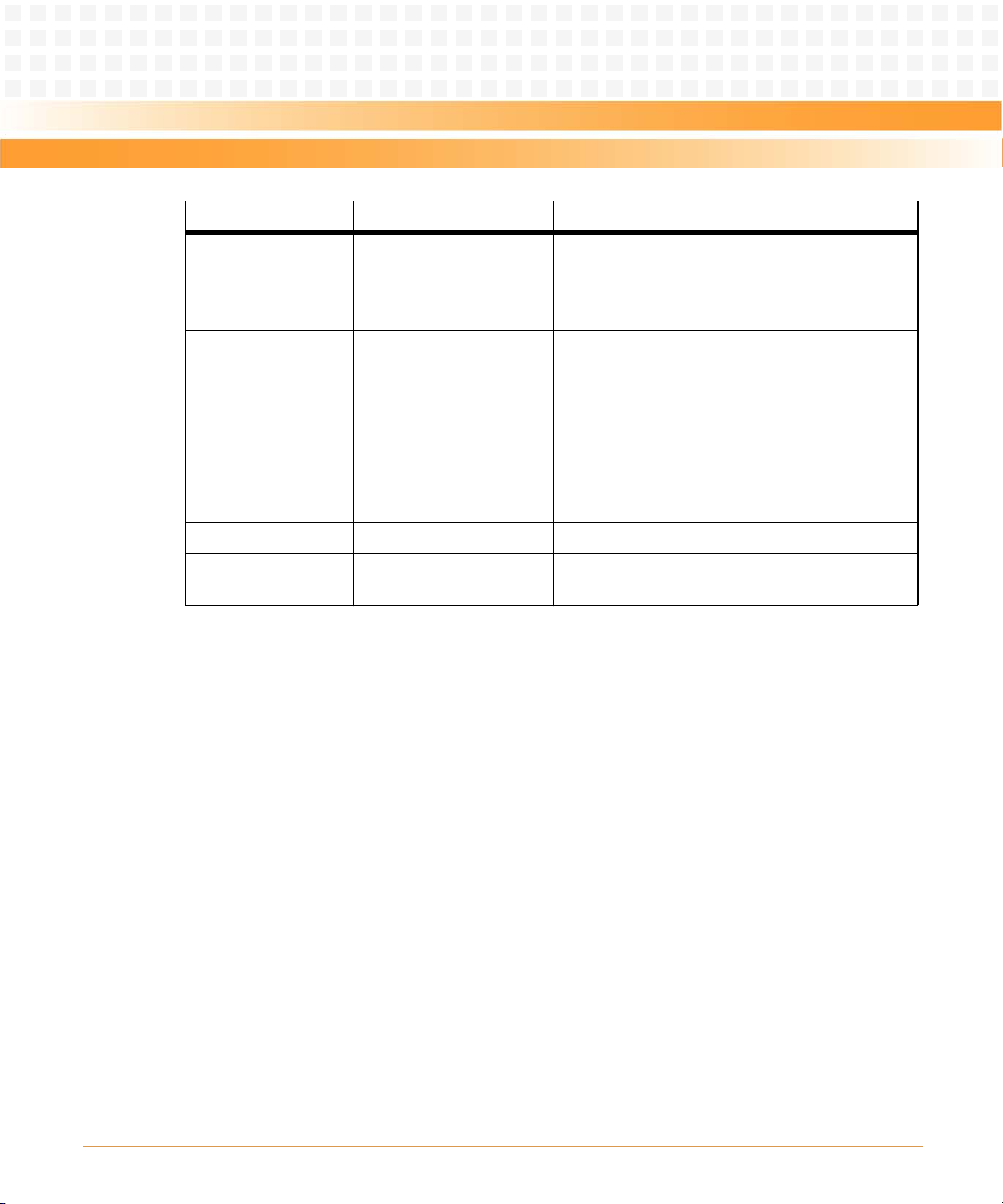

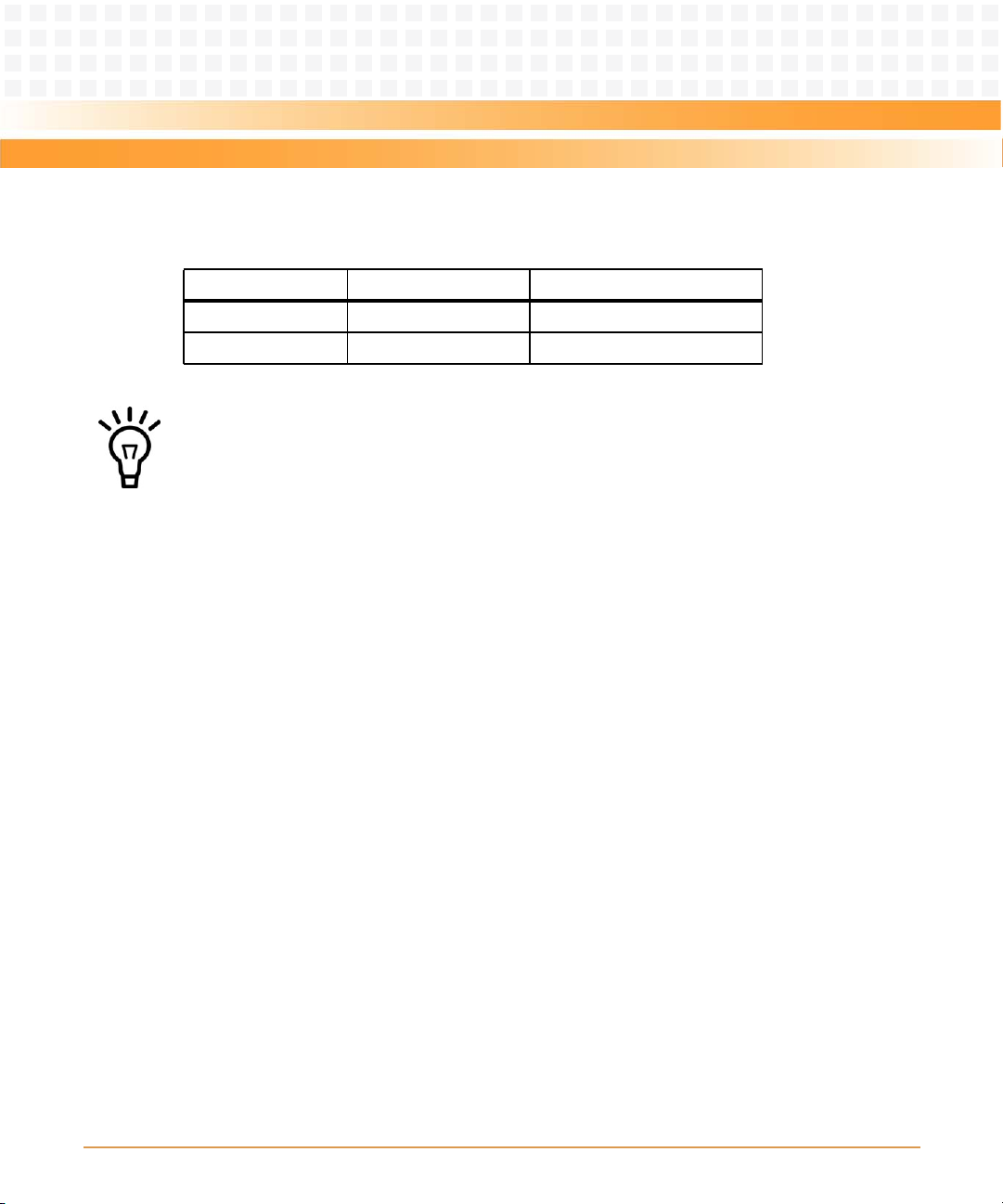

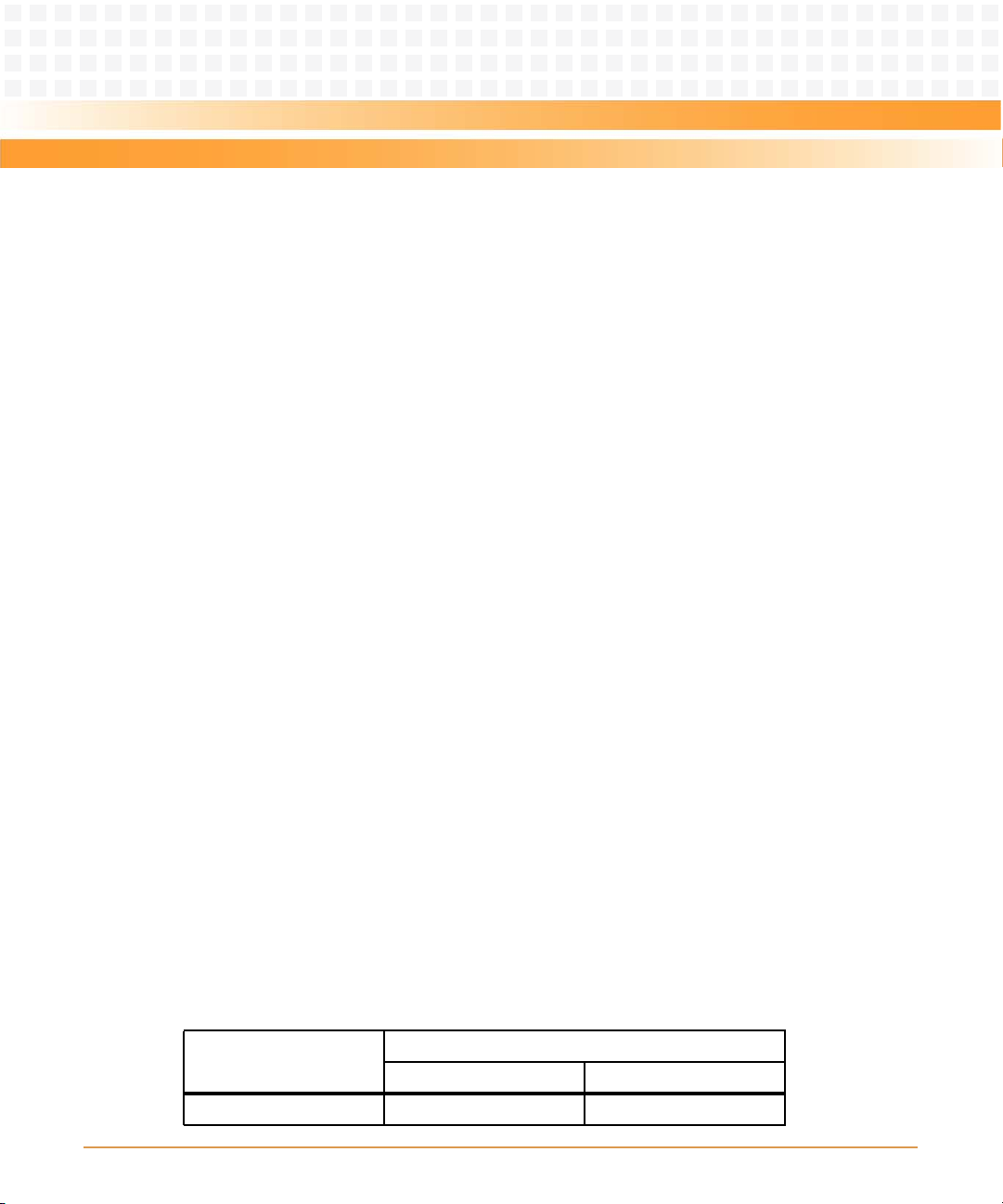

1.4 Ordering Information

As of the printing date of this manual, this guide supports the models listed below.

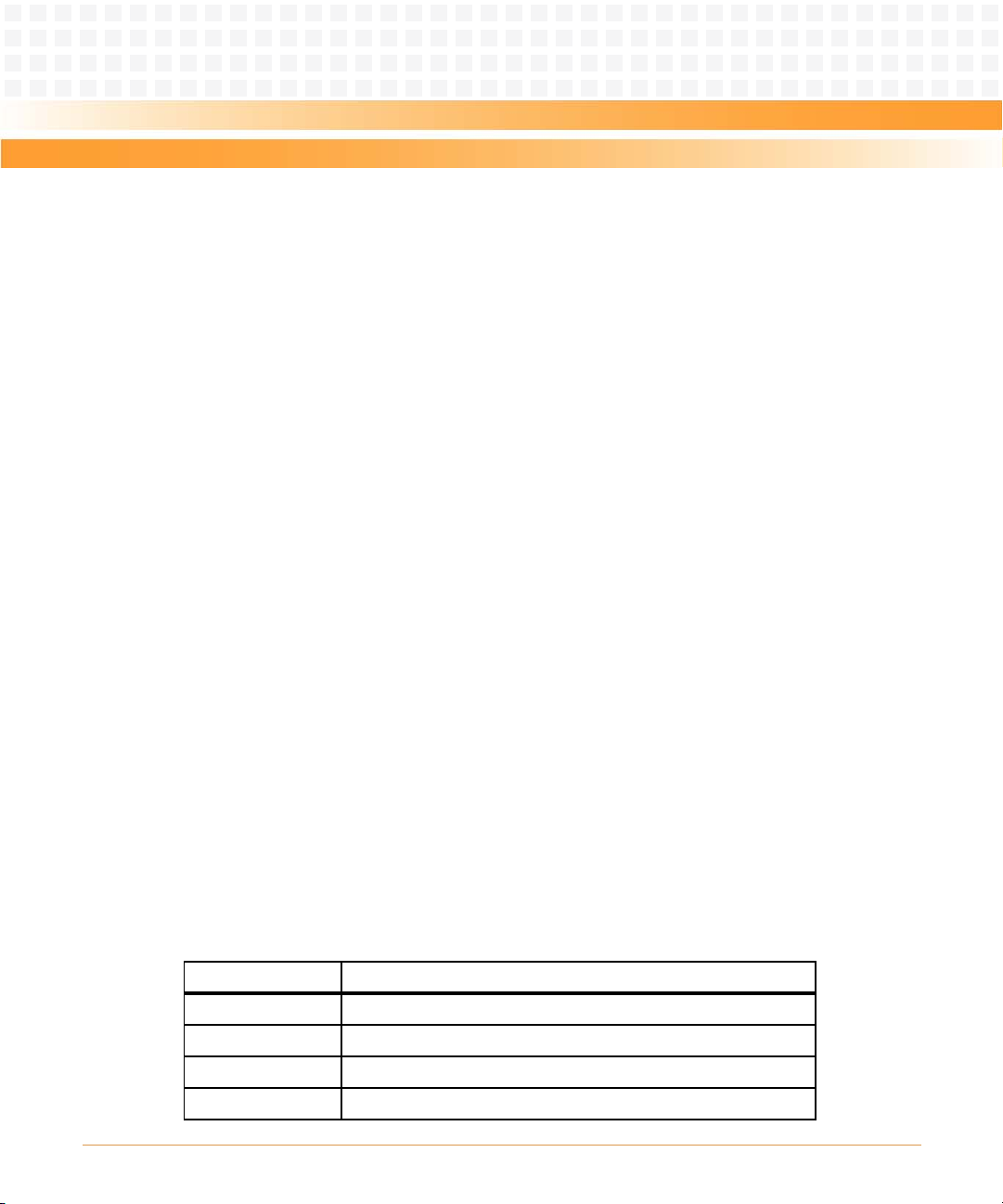

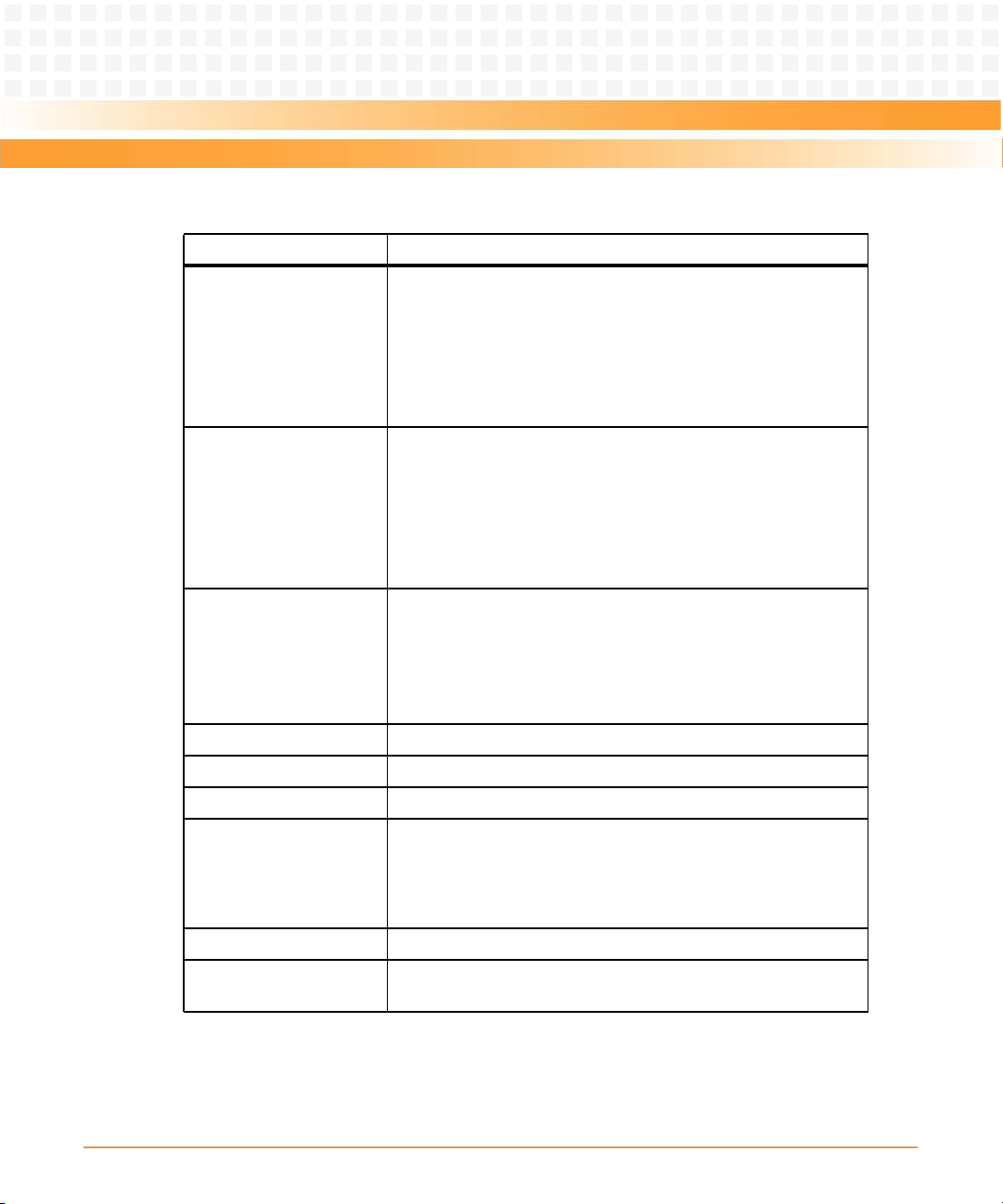

Table 1-4 Available Board Variants

Order Number Processor Speed Memory Ejector

MVME2500-0163 QorIQ P2010 (single-core) 800 MHz 1 GB IEEE

MVME2500-0161 QorIQ P2010 (single-core) 800 MHz 1 GB SCANBE

MVME2500-0173 QorIQ P2020 (dual-core) 1200 MHz 2 GB IEEE

MVME2500-0171 QorIQ P2020 (dual-core) 1200 MHz 2 GB SCANBE

MVME2500ET-0173 QorIQ P2020 (dual-core) 1000 MHz 2 GB IEEE ENP2

MVME2500ET-0171 QorIQ P2020 (dual-core) 1000 MHz 2 GB SCANBE ENP2

22

MVME2500 Installation and Use (6806800L01H)

Page 23

Introduction

As of the printing date of this manual, the following board accessories are available.

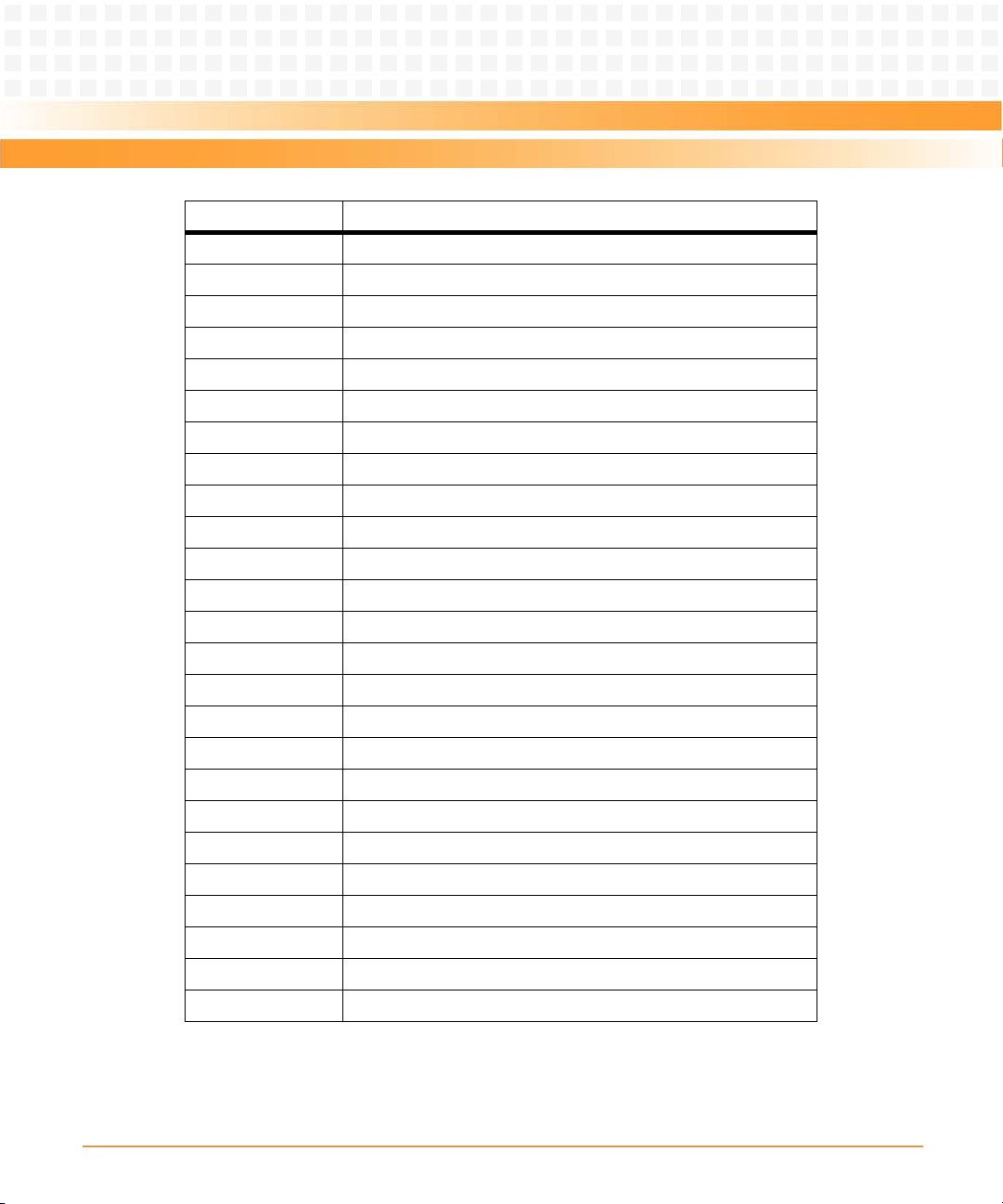

Table 1-5 Available Board Accessories

Order Number Description

VME-HDMNTKIT VME HD mounting kit

VME-64GBSSDKIT VME 64GB SSD and mounting kit

MVME7216E-101 VME RTM (IEEE handle)

MVME7216E-102 VME RTM (SCANBE Handle)

MVME721ET-101 VME RTM Extended Temperature (IEEE handle)

MVME721ET-102 VME RTM Extended Temperature (SCANBE Handle)

SERIAL-MINI-D (30W2400E01A)

Female - to -male micro-mini DB-9 to DB9 adapter cable

MVME2500 Installation and Use (6806800L01H)

23

Page 24

Introduction

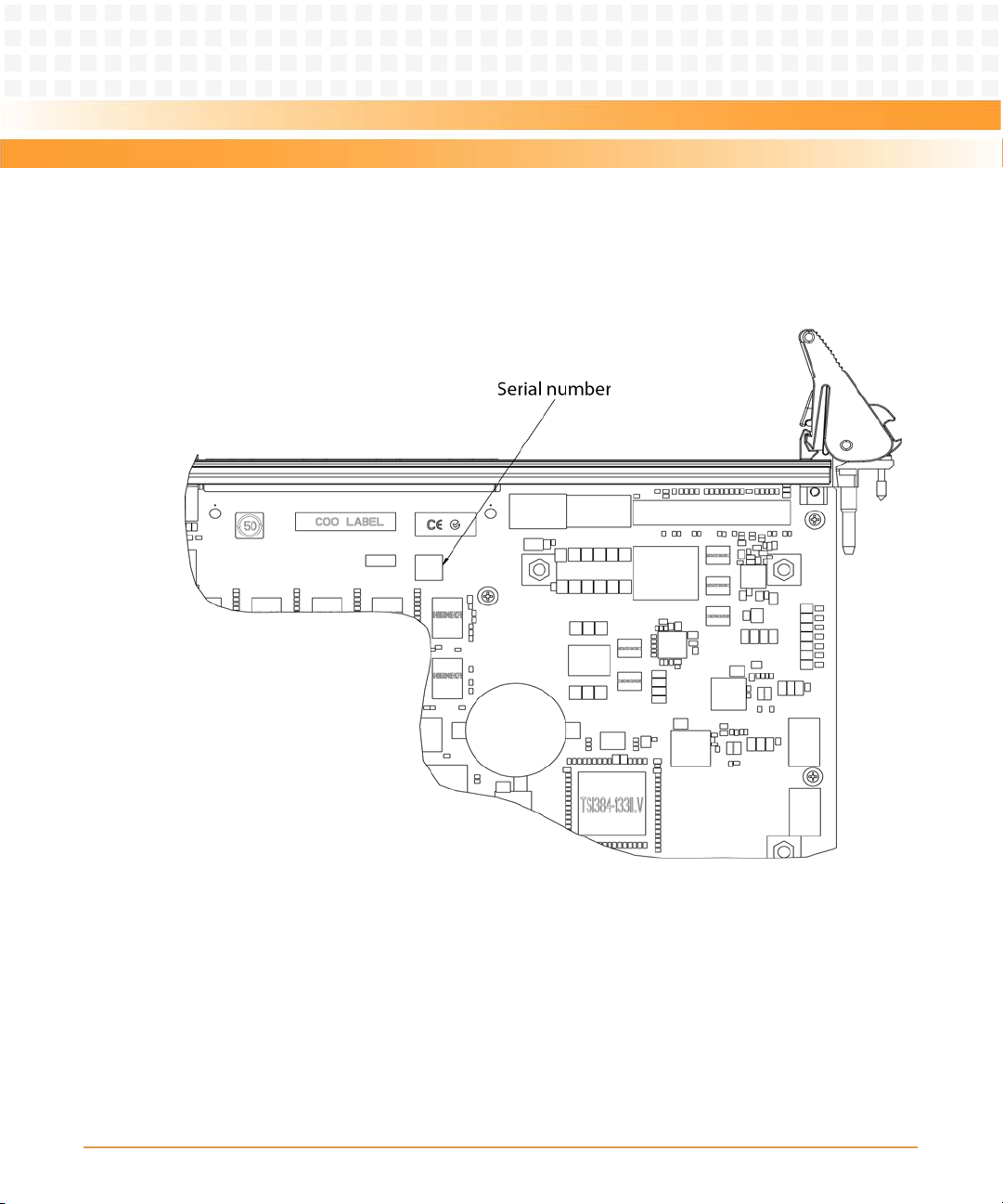

1.5 Product Identification

The following graphics shows the location of the serial number label.

Figure 1-1 Serial Number Location

24

MVME2500 Installation and Use (6806800L01H)

Page 25

Hardware Preparation and Installation

2.1 Overview

This chapter provides installation and safety instructions for this product. Installation

instructions for the optional PMC and transition module are also included.

A fully implemented MVME2500 consists of the base board plus:

PCI Mezzanine Card (PMC) or PCI-E Mezzanine Card (XMC) for added versatility

Rear transition module

SATA kit

The following are the things that need to be done before using the board. Be sure to read the

entire chapter, including all caution and warning notes, before you begin.

1. Unpack the hardware. Refer to Unpacking and Inspecting the Board on page 26

Chapter 2

2. Configure the hardware by setting jumpers on the board and RTM. Refer to Configuring the

Board on page 29

3. Install the transition module in the chassis. Refer to Rear Transition Module on page 30.

4. Install PMC module (if required). Refer to PMC/XMC Support on page 31.

5. Install XMC span module (if required). Refer to PMC/XMC Support on page 31.

6. Install the board in the chassis. Refer to Installing and Removing the Board on page 32.

7. Attach cables and apply power. Refer to Completing the Installation on page 34.

MVME2500 Installation and Use (6806800L01H)

25

Page 26

Hardware Preparation and Installation

2.2 Unpacking and Inspecting the Board

Read all notices and cautions prior to unpacking the product.

Damage of Circuits

Electrostatic discharge and incorrect installation and removal can damage circuits or

shorten its life.

Before touching the board or electronic components, make sure that you are working

in an ESD-safe environment.

Shipment Inspection

1. Verify that you have received all items of your shipment.

2. Check for damage and report any damage or differences to customer service.

3. Remove the desiccant bag shipped together with the board and dispose of it according to

your country’s legislation.

The product is thoroughly inspected before shipment. If any damage occurred during

transportation or any items are missing, contact customer service immediately.

2.3 Requirements

Make sure the board meets the requirements specified in the next sections when the board is

operated in your particular system configuration.

26

MVME2500 Installation and Use (6806800L01H)

Page 27

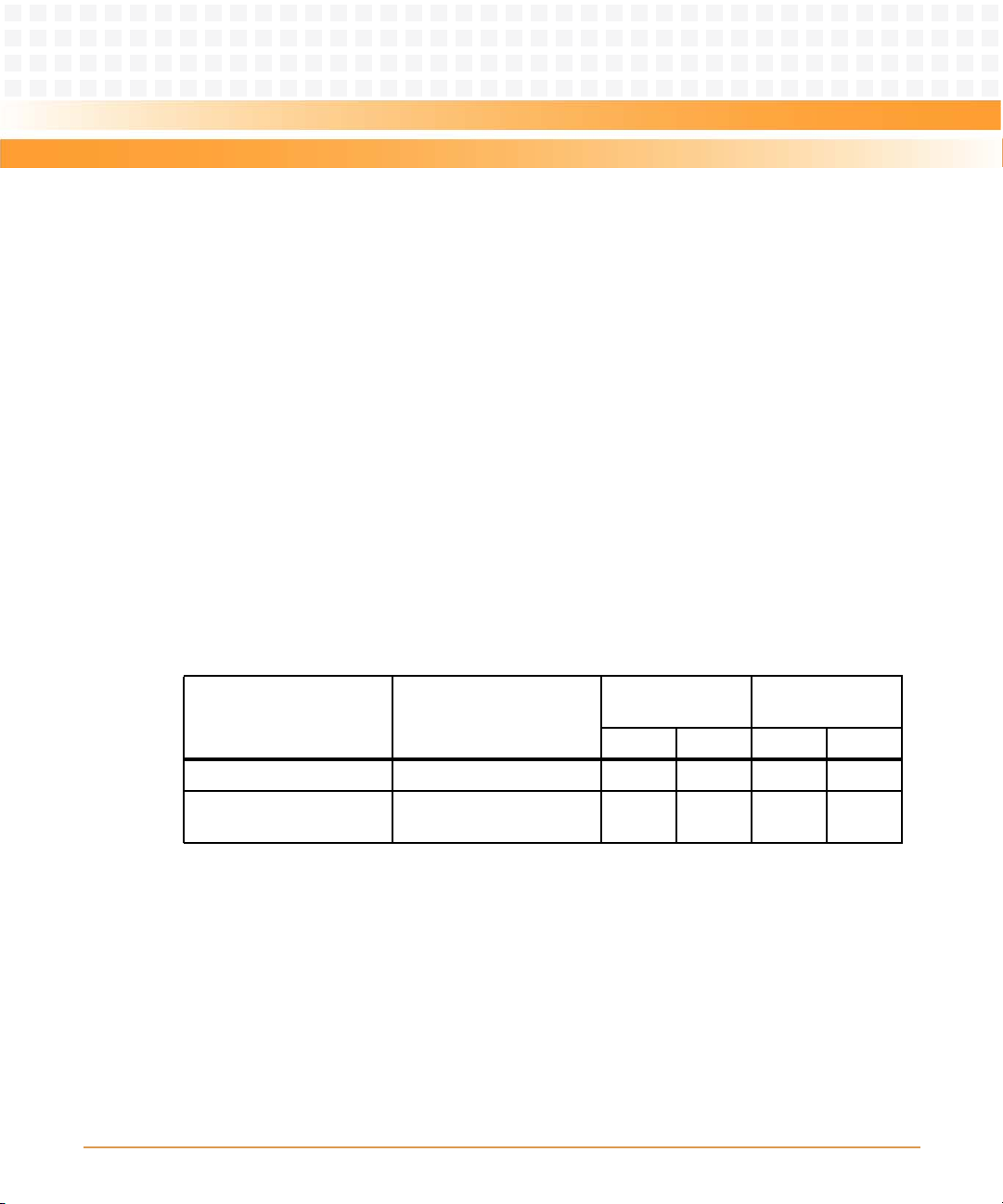

2.3.1 Environmental Requirements

Operating temperatures refer to the temperature of the air circulating around the board and

not to the component temperature.

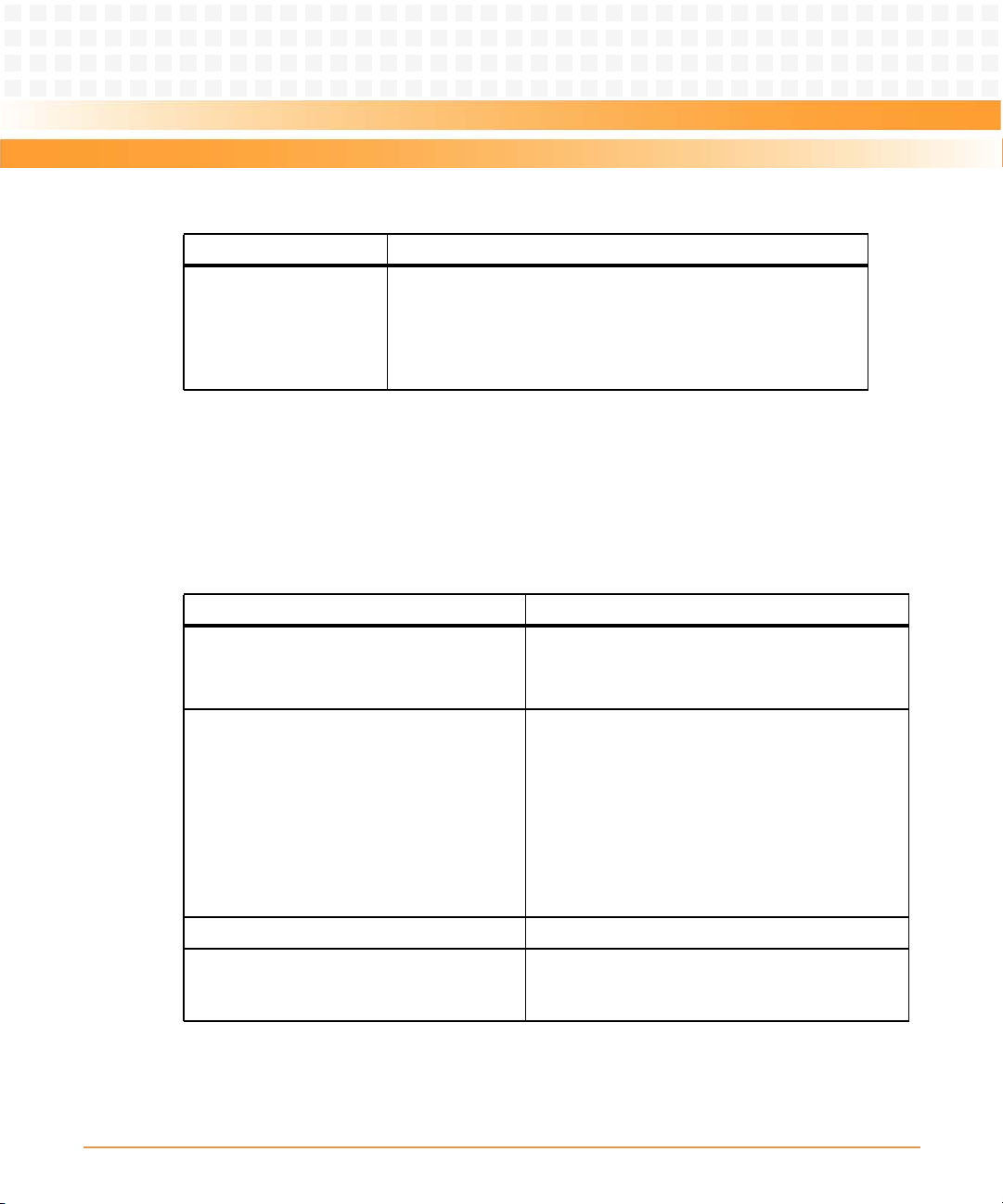

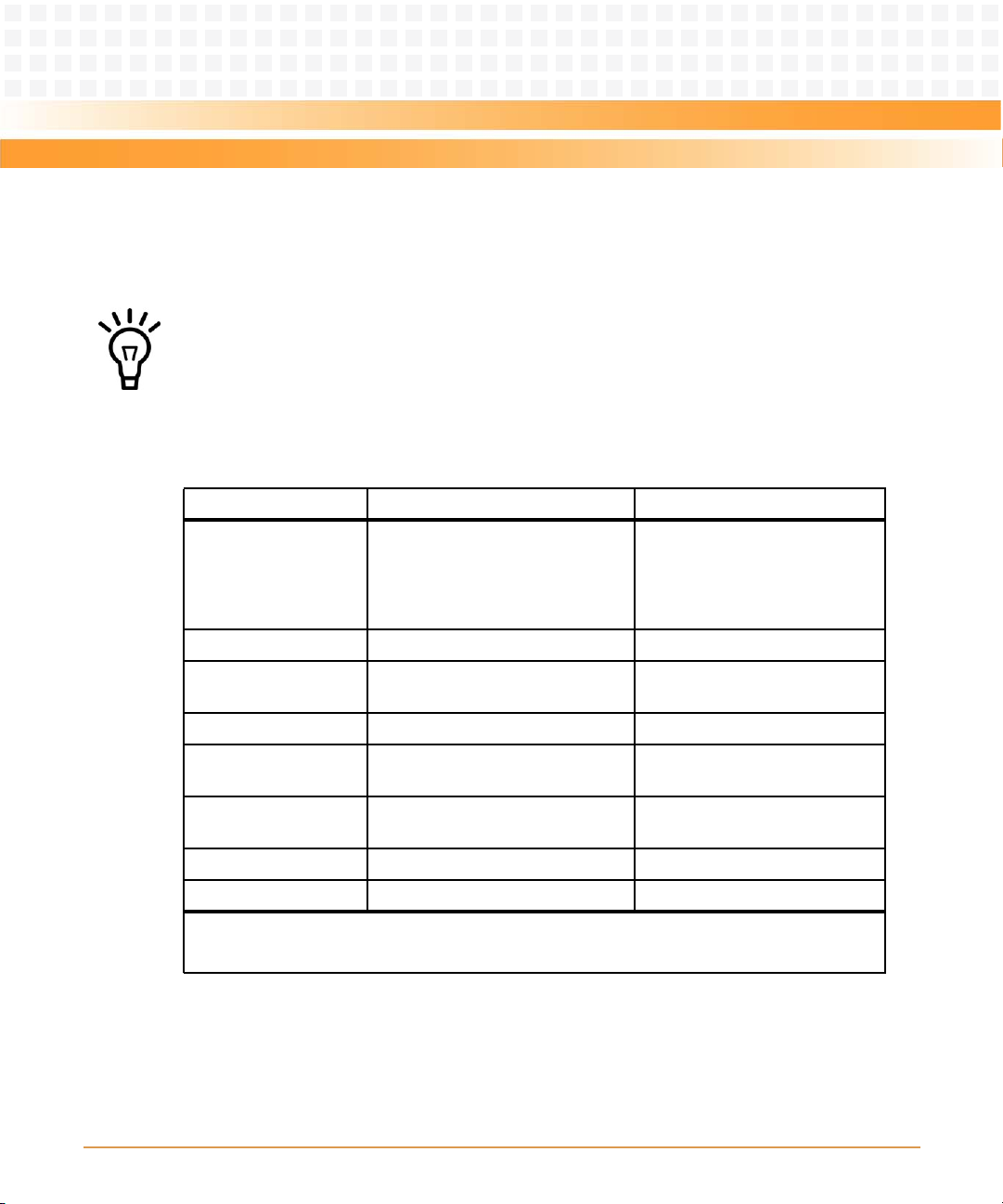

Table 2-1 Environmental Requirements

Characteristics Commercial Versions Extended Temperature Versions

Hardware Preparation and Installation

Applicable Variants MVME2500-0163

MVME2500-0161

MVME2500-0173

MVME2500-0171

Cooling Method Forced Air 7 CFM

Operating

Temperature

Storage -40°C to +85°C -50°C to +100°C

Vibration Sine

(10min/axis)

Vibration Random

(1hr/axis)

Shock 20g/11 mS 30g/11 mS

Humidity to 95% RH (non-condensing) to 100% RH (non-condensing)

1. ft3/min

2. Flat 15-1000Hz, -6db/octave 1000Hz - 2000Hz [MIL-STD 810F Figure 514.5C-17]

0°C to +55°C -40°C to +71°C

2 G, 5 to 2000 Hz 10 G, 15 to 2000 Hz

0.01g2/Hz, 15 to 2000 Hz 0.04g2/Hz, 15 to 2000 Hz (8

1

MVME2500ET-0173

MVME2500ET-0171

Forced Air 7 CFM

2

GRMS)

1

MVME2500 Installation and Use (6806800L01H)

27

Page 28

Hardware Preparation and Installation

Product Damage

High humidity and condensation on the board surface causes short circuits.

Do not operate the board outside the specified environmental limits.

Make sure the board is completely dry and there is no moisture on any surface before

applying power.

2.3.2 Power Requirements

The board uses +5.0 V from the VMEbus backplane. On board power supply generates the

required voltages for the various ICs. The MVME2500 connects the +12 V and -12 V supplies

from the backplane to the PMC sites, while the +3.3 V power supplied to the PMC sites comes

from the +5.0 V backplane power. A maximum of 10 A of +3.3 V power is available to the PMC

sites, however the 90 W +5.0 V limit must be observed as well as any cooling limitations.

28

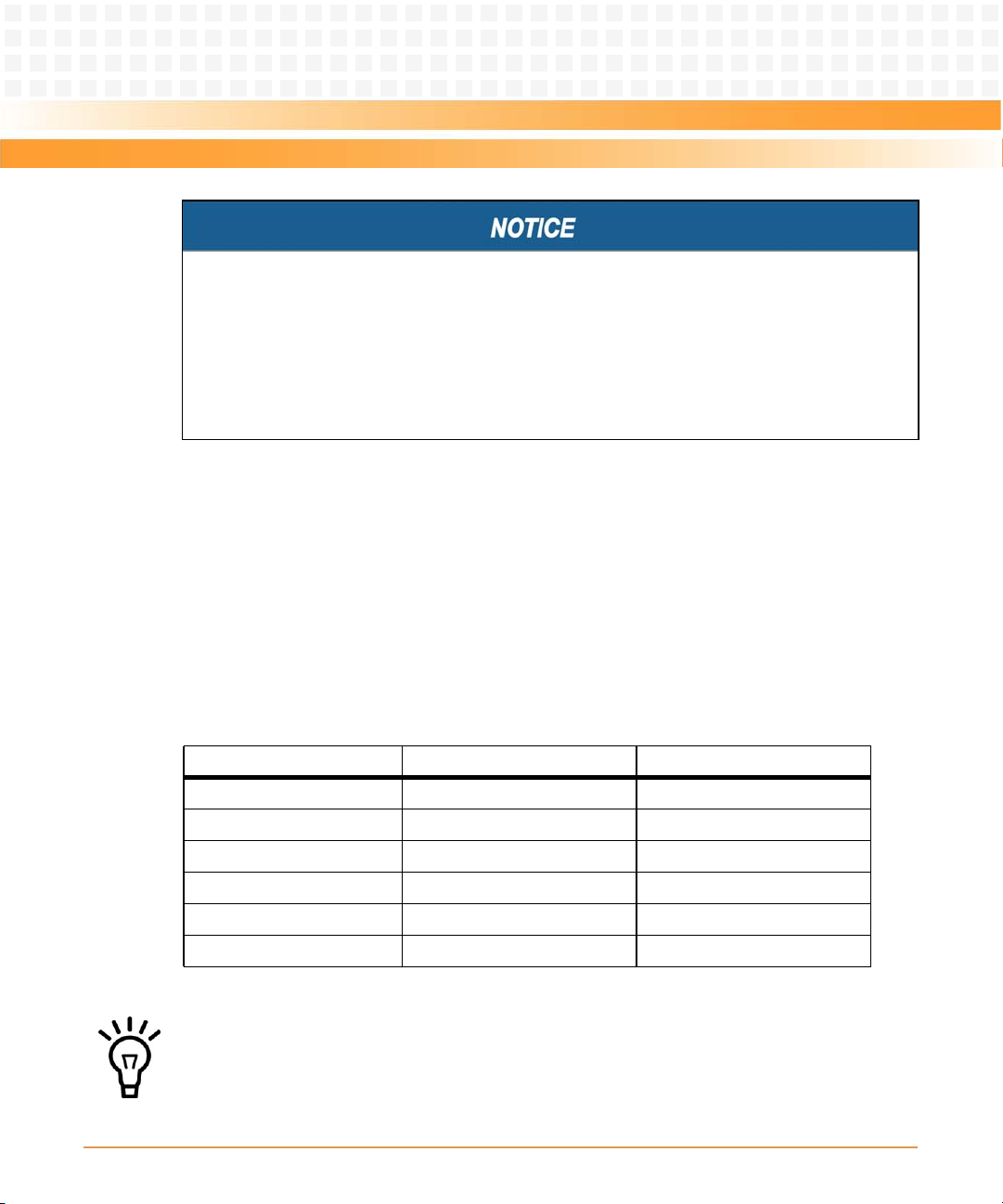

The following table provides an estimate of the typical and maximum power required.

Table 2-2 Power Requirements

Board Variant Maximum (Calculated) Typical (Measured Operating)

MVME2500-0163 18.5 W 14.8 W

MVME2500-0161 18.5 W 14.8 W

MVME2500-0173 24 W 16.6 W

MVME2500-0171 24 W 16.6 W

MVME2500ET-0173 24 W 16.6 W

MVME2500ET-0171 24 W 16.6 W

The power is measured when the board is in standby (Linux prompt). Power will significantly

increase when adding hard drives or a XMC/PMC card.

MVME2500 Installation and Use (6806800L01H)

Page 29

The following table shows the power available when the MVME2500 is installed in either a

three row or five row chassis and when PMCs are present.

Chassis Type Available Power Power With PMCs

Three Row 70 W maximum below 70 W

Five Row 90 W maximum below 90 W

Keep below power limit. Cooling limitations must be considered.

2.3.3 Equipment Requirements

Hardware Preparation and Installation

The following are recommended to complete a MVME2500 system:

VMEbus system enclosure

System console terminal

Operating system (and/or application software)

Transition module and connecting cables

2.4 Configuring the Board

The board provides software control over most options. Settings can be modified to fit the

user's specifications. To configure, set the bits in the control register after installing the board

in a system. Make sure that all user-defined switches are properly set before installing a

PMC/XMC module. For more information, see Switches on page 57.

MVME2500 Installation and Use (6806800L01H)

29

Page 30

Hardware Preparation and Installation

2.5 Installing Accessories

2.5.1 Rear Transition Module

The MVME2500 does not support hot swap. Remove power to the rear slot or system before

installing the module. A PCMI/O Module (PIM) needs to be manually configured and installed

before placing the transition module.

Damage of Circuits

Electrostatic discharge and incorrect installation and removal can damage circuits or

shorten its life.

Before touching the board or electronic components, make sure that you are working

in an ESD-safe environment.

30

Product Damage

Only use injector handles for board insertion to avoid damage to the front panel and/or

PCB. Deformation of the front panel can cause an electrical short or other board

malfunction.

Board Malfunction

Switches marked as “reserved” might carry production-related functions and can cause

the board to malfunction if their setting is changed.

Do not change settings of switches marked as “reserved”. The setting of switches which

are not marked as “reserved” has to be checked and changed before board installation.

Installation and Removal Procedure

1. Turn OFF all equipment and disconnect the power cable from the AC power source.

2. Remove the chassis cover.

3. Remove the filler panel(s) from the appropriate card slot(s) at the rear of the chassis (if the

chassis has a rear card cage).

MVME2500 Installation and Use (6806800L01H)

Page 31

4. Install the top and bottom edge of the transition module into the rear guides of the chassis.

5. Ensure that the levers of the two injector/ejectors are in the outward position.

6. Slide the transition module into the chassis until resistance is felt.

7. Move the injector/ejector levers in an inward direction.

8. Verify that the transition module is properly seated and secure it to the chassis using the

two screws adjacent to the injector/ejector levers.

9. Connect the cables to the transition module.

To remove the transition module from the chassis, reverse the procedure and press the red

locking tabs (IEEE handles only) to extract the board.

2.5.2 PMC/XMC Support

Installation Procedure

Hardware Preparation and Installation

Read all notices and follow these steps to install a PMC on the baseboard.

Damage of Circuits

Electrostatic discharge and incorrect installation and removal can damage circuits or

shorten its life.

Before touching the board or electronic components, make sure that you are working

in an ESD-safe environment.

Product Damage

Inserting or removing modules with power applied may result in damage to module

components.

Before installing or removing additional devices or modules, read the documentation

that came with the product.

MVME2500 Installation and Use (6806800L01H)

31

Page 32

Hardware Preparation and Installation

1. Attach an ESD strap to your wrist. Attach the other end of the strap to the chassis as a

ground. Make sure that it is securely fastened throughout the procedure.

2. Remove the PMC/XMC filler plate from the front panel cut-out.

3. Slide the front bezel of the PMC/XMC into the cut-out from behind. The front bezel of the

PMC/XMC module will be flushed with the board when the connectors on the module align

with the mating connectors on the board.

4. Align the mating connectors properly and apply minimal pressure to the PMC/XMC until it

is seated to the board.

5. Insert the four PMC/XMC mounting screws through the mounting holes on the bottom side

of the board, and then thread the four mount points on the PMC/XMC. Tighten the screws.

6. Install the board into the appropriate card slot. Make sure that the board is well seated into

the backplane connectors. Do not damage or bend connector pins.

7. Replace the chassis or system cover.

8. Reconnect the system to the power source and then turn on the system.

When removing the PMC/XMC, hold it by its long side and exert minimal force when pulling

it from the baseboad to prevent pin damage.

2.6 Installing and Removing the Board

This section describes the recommended procedure for installing the board in a chassis. Read

all warnings and instructions before installing the board.

The MVME2500 does not support hot swap. Power off the slot or system and make sure that

the serial ports and switches are properly configured.

32

MVME2500 Installation and Use (6806800L01H)

Page 33

Hardware Preparation and Installation

Damage of Circuits

Electrostatic discharge and incorrect installation and removal can damage circuits or

shorten its life.

Before touching the board or electronic components, make sure that you are working

in an ESD-safe environment.

Product Damage

Only use injector handles for board insertion to avoid damage to the front panel and/or

PCB. Deformation of the front panel can cause an electrical short or other board

malfunction.

1. Attach an ESD strap to your wrist. Attach the other end of the strap to an electrical ground.

Make sure that it is securely fastened throughout the procedure.

2. Remove VME filler panels from the VME enclosures, as appropriate.

3. Install the top and bottom edge of the board into the guides of the chassis.

4. Ensure that the levers of the two injector/ejectors are in the outward position.

5. Slide the board into the chassis until resistance is felt.

6. Simultaneously move the injector/ejector levers in an inward direction.

7. Verify that the board is properly seated and secure it to the chassis using the two screws

located adjacent to the injector/ejector levers.

8. Connect the appropriate cables to the board.

To remove the board from the chassis, reverse the procedure and press the red locking tabs

(IEEE handles only) to extract the board.

MVME2500 Installation and Use (6806800L01H)

33

Page 34

Hardware Preparation and Installation

2.7 Completing the Installation

The board is designed to operate as an application-specific computer blade or an intelligent I/O

board/carrier. It can be used in any slot in a VME chassis. Once the board is installed, you are

ready to connect peripherals and apply power to the board.

Product Damage

RJ-45 connectors on modules are either twisted-pair Ethernet (TPE) or E1/T1/J1

network interfaces. Connecting an E1/T1/J1 line to an Ethernet connector may damage

your system.

Make sure that TPE connectors near your working area are clearly marked as network

connectors.

Verify that the length of an electric cable connected to a TPE bushing does not exceed

100 meters.

Make sure the TPE bushing of the system is connected only to safety extra low voltage

circuits (SELV circuits).

If in doubt, ask your system administrator.

The console settings for the MVME2500 are:

Eight bits per character

One stop bit per character

Parity disabled (no parity)

Baud rate of 9600 baud

Verify that hardware is installed and the power/peripheral cables connected are appropriate

for your system configuration.

Replace the chassis or system cover, reconnect the chassis to power source, and turn the

equipment power on.

34

MVME2500 Installation and Use (6806800L01H)

Page 35

Controls, LEDs, and Connectors

3.1 Board Layout

The following figure shows the components and connectors on the MVME2500.

Figure 3-1 Component Layout

Chapter 3

MVME2500 Installation and Use (6806800L01H)

35

Page 36

Controls, LEDs, and Connectors

3.2 Front Panel

The following components are found on the MVME2500 front panel.

Figure 3-2 Front Panel LEDs, Connectors and Switches

36

MVME2500 Installation and Use (6806800L01H)

Page 37

3.2.1 Reset Switch

The MVME2500 has a single push button switch that has both the abort and reset functions.

Pressing the switch for less than three seconds generates an abort interrupt to the P20x0 QorIQ

PIC. Holding it down for more than three seconds will generate a hard reset. The VME SYSRESET

is generated if the MVME2500 is the VMEbus system controller.

3.3 LEDs

The MVME2500 utilizes light emitting diodes (LEDs) to provide a visible status indicator on the

front panel. These LEDs show power failures, power up states, Ethernet link/speed, ethernet

activity, SATA link and activity and PCI-E valid lane status. There are also a few user configurable

LEDs. Each LED description is necessary for troubleshooting and debugging.

3.3.1 Front Panel LEDs

Controls, LEDs, and Connectors

The front panel LEDs are listed below.

Figure 3-3 Front Panel LEDs

MVME2500 Installation and Use (6806800L01H)

37

Page 38

Controls, LEDs, and Connectors

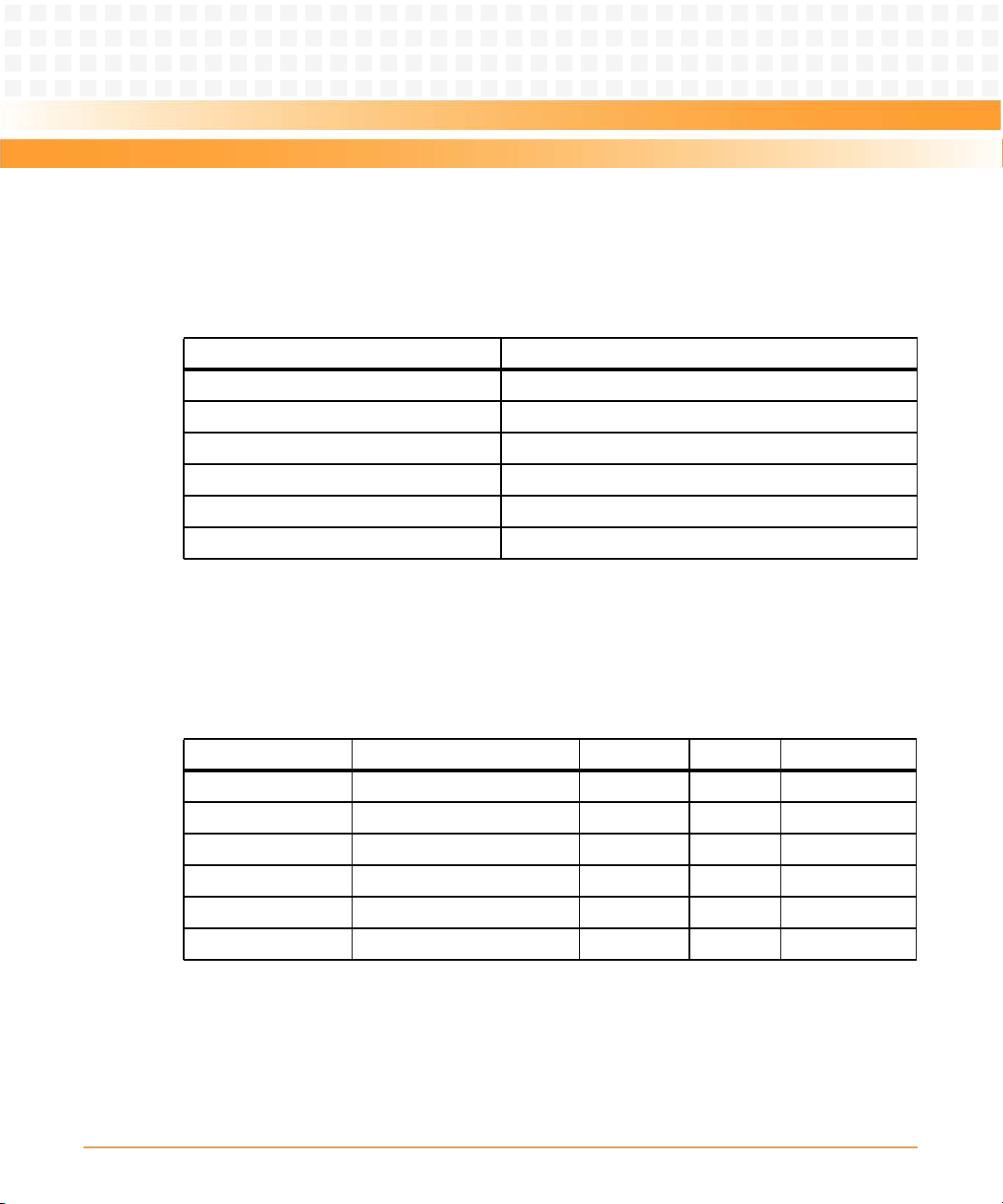

Table 3-1 Front Panel LEDs

Label Function Location Color Description

USER 1 User Defined Front panel Off

Yellow

Red

FAIL Board Fail Front panel Off

Red

GENET1

SPEED

GENET1

ACT

GENET2

SPEED

TSEC1

Link/Speed

TSEC1

Activity

TSEC2

Link/Speed

Front panel

Integrated

RJ45 LED

Front panel

Integrated

RJ45 LED

Front panel

Integrated

RJ45 LED

(Left)

Off

Amber

Green

Off

Blinking Green

Off

Amber

Green

By default

User Software Controllable. Refer to

the "User LED Register."

User Software Controllable. Refer to

the "User LED Register."

Normal operation after successful

firmware boot.

One or more on-board power rails

has failed and the board has

shutdown to protect the hardware.

Normal during power up, during

hardware reset (such as a front panel

reset). May be asserted by the BDFAIL

bit in the Tsi148 VSTAT register.

No link

10/100BASE-T operation

1000 BASE-T operation

No activity

Activity proportional to bandwidth

utilization

No link

10/100BASE-T operation

1000BASE-T operation

38

GENET2

ACT

TSEC2

Activity

Front panel

Integrated

RJ45 LED

Off

Blinking Green

MVME2500 Installation and Use (6806800L01H)

No activity

Activity proportional to bandwidth

utilization

Page 39

3.3.2 Onboard LEDs

The onboard LEDs are listed below. To view its location on the board, see Figure 3-1 on page 35.

Figure 3-4 Onboard LEDs

Controls, LEDs, and Connectors

Table 3-2 Onboard LEDs Status

Label Function Color Description

D9 Power Fail Red This indicator is illuminated when one or more of the on-

D33 User Defined Amber Controlled by the FPGA. Used for boot-up sequence

D34 User Defined Amber Controlled by the FPGA. Used for boot-up sequence

D35 User Defined Amber Controlled by the FPGA. Used for boot-up sequence

D36 Early Power Fail Amber This indicator is lit when the early 3.3V power supply fails.

D37 User Defined Amber Controlled by the FPGA

D38 User Defined Amber Controlled by the FPGA

3.4 Connectors

This section describes the pin assignments and signals for the connectors on the MVME2500.

board voltage rails fails.

indicator.

indicator.

indicator.

MVME2500 Installation and Use (6806800L01H)

39

Page 40

Controls, LEDs, and Connectors

3.4.1 Front Panel Connectors

The following connectors are found on the outside of the MVME2500. These connectors are

divided between the front panel connectors and the backplane connectors. The front panel

connectors include the J1 and J5 connectors. The backplane connectors include the P1 and P2

connectors.

3.4.1.1 RJ45 with Integrated Magnetics (J1)

The MVME2500 uses an X2 RJ45.

Table 3-3 Front Panel Tri-Speed Ethernet Connector (J1)

Pin Name Signal Description

1A GND

2A NC

3A Port A TRD3 -

4A Port A TRD3 +

5A Port A TRD2 -

6A Port A TRD2 +

7A Port A TRD1 -

8A Port A TRD1 +

9A Port A TRD0 -

10A Port A TRD0 +

D1A Port A Green LED1 Anode/ Yellow LED1 Cathode

D2A Port A Yellow LED1 Anode/ Green LED1 Cathode

D3A Port A Green LED2 Anode/ Yellow LED2 Cathode

D4A Port A Yellow LED2 Anode/ Green LED2 Cathode

1B GND

2B NC

3B Port B TRD3 -

4B Port B TRD3 +

5B Port B TRD2 -

40

MVME2500 Installation and Use (6806800L01H)

Page 41

Table 3-3 Front Panel Tri-Speed Ethernet Connector (J1) (continued)

Pin Name Signal Description

6B Port B TRD2 +

7B Port B TRD1 -

8B Port B TRD1 +

9B Port B TRD0 -

10B Port B TRD0 +

D1B Port B Green LED1Anode/ Yellow LED1 Cathode

D2B Port B Yellow LED1 Anode/ Green LED1 Cathode

D3B Port B Green LED2Anode/ Yellow LED2 Cathode

D4B Port B Yellow LED2 Anode/ Green LED2 Cathode

3.4.1.2 Front Panel Serial Port (J4)

Controls, LEDs, and Connectors

There is one front access asynchronous serial port interface that is routed to the micro mini DB9 front panel connector. A male-to-male micro-mini DB9 adapter cable is available under

Emerson part number SERIAL-MINI-D (30-W2400E01A). The pin assignments for these

connectors are as follows:

Table 3-4 Front Panel Serial Port (J4)

Pin Signal Description

1NC

2RX

3TX

4NC

5GND

6NC

7RTS

8CTS

9NC

MVME2500 Installation and Use (6806800L01H)

41

Page 42

Controls, LEDs, and Connectors

3.4.1.3 USB Connector (J5)

The MVME2500 uses upright USB receptable mounted in the front panel.

Table 3-5 USB Connector (J5)

Pin Name Signal Description

1 +5 V

2 Data -

3 Data +

4GND

MTG Mounting Ground

MTG Mounting Ground

MTG Mounting Ground

MTG Mounting Ground

3.4.1.4 VMEBus P1 Connector

The VME P1 connector is a 160-pin DIN. The P1 connector provides power and VME signals for

24-bit address and 16-bit data. The pin assignments for the P1 connector is as follows:

Table 3-6 VMEbus P1 Connector

Pin Row A Row B Row C Row D Row Z

1 DATA 0 BBSY DATA 8 +5V NC

2 DATA 1 BCLR DATA 9 GND GND

3 DATA 2 ACFAIL DATA 10 NC NC

4 DATA 3 BGIN0 DATA 11 NC GND

5 DATA 4 BGOUT0 DATA 12 NC NC

6 DATA 5 BGIN1 DATA 13 NC GND

7 DATA 6 BGOUT1 DATA 14 NC NC

8 DATA 7 BGIN2 DATA 15 NC GND

9 GND BGOUT2 GND GAP NC

42

MVME2500 Installation and Use (6806800L01H)

Page 43

Controls, LEDs, and Connectors

Table 3-6 VMEbus P1 Connector (continued)

Pin Row A Row B Row C Row D Row Z

10 SYSCLK BGIN3 SYSFAIL GA0 GND

11 GND BGOUT3 BERR GA1 NC

12 DS1 BR0 SYSRESET +3.3V (not used) GND

13 DS0 BR1 LWORD GA2 NC

14 WRITE BR2 AM 5 +3.3V (not used) GND

15 GND BR3 ADD 23 GA3 NC

16 DTACK AM 0 ADD 24 +3.3V (not used) GND

17 GND AM 1 ADD 25 GA4 NC

18 AS AM 2 ADD 26 +3.3V (not used) GND

19 GND AM 3 ADD 27 NC NC

20 IACK GND ADD 28 +3.3V (not used) GND

21 IACKIN NC ADD 29 NC NC

22 IACKOUT NC ADD 30 +3.3V (not used) GND

23 AM 4 GND ADD 31 NC NC

24 ADD 7 IRQ7 ADD 32 +3.3V (not used) GND

25 ADD 6 IRQ6 ADD 33 NC NC

26 ADD 5 IRQ5 ADD 34 +3.3V (not used) GND

27 ADD 4

28 ADD 3 IRQ3 ADD 36 +3.3V (not used) GND

29 ADD 2 IRQ2 ADD 37 NC NC

30 ADD 1 IRQ1 ADD 38 +3.3V (not used) GND

31 -12V NC +12V +12V

32 +5V +5V +5V +5V

MVME2500 Installation and Use (6806800L01H)

IRQ4 ADD 35 NC NC

43

Page 44

Controls, LEDs, and Connectors

3.4.1.5 VMEBus P2 Connector

The VME P2 connector is a 160-pin DIN. Row B of the P2 connector provides power to the

MVME2500 and to the upper eight VMEbus address lines and additional 16 VMEbus data lines.

The Z, A, C, and D pin assignments for the P2 connector are the same for both the MVME2500

and MVME7216E/ MVME721E, and are as follows:

Table 3-7 VMEbus P2 Connector

Pin Row A Row B Row C Row D Row Z

1 PMC IO 2 +5V PMC IO 1 GE3_0 + Serial 1 RX

2 PMC IO 4 GND PMC IO 3 GE3_0 - GND

3 PMC IO 6 RETRY PMC IO 5 GND Serial 1 TX

4 PMC IO 8 ADDRESS 24 PMC IO 7 GE3_1 + GND

5 PMC IO 10 ADDRESS 25 PMC IO 9 GE3_1 - Serial 1 CTS

6 PMC IO 12 ADDRESS 26 PMC IO 11 GND GND

7 PMC IO 14 ADDRESS 27 PMC IO 13 GE3_2 + Serial 1 RTS

8 PMC IO 16 ADDRESS 28 PMC IO 15 GE3_2 - GND

9 PMC IO 18 ADDRESS 29 PMC IO 17 GND Serial 2 RX

10 PMC IO 20 ADDRESS 30 PMC IO 19 GE3_3 + GND

11 PMC IO 22 ADDRESS 31 PMC IO 21 GE3_3 - Serial 2 TX

12 PMC IO 24 GND PMC IO 23 GND GND

13 PMC IO 26 +5V PMC IO 25 I2C DATA Serial 2 CTS

14 PMC IO 28 DATA 16 PMC IO 27 I2C CLK GND

15 PMC IO 30 DATA 17 PMC IO 29 GE3_LINK_ LED Serial 2 RTS

16 PMC IO 32 DATA 18 PMC IO 31 GE3_ACT_LED GND

17 PMC IO 34 DATA 19 PMC IO 33 GE4_LINK_LED Serial 3 RX

18 PMC IO 36 DATA 20 PMC IO 35 GE4_A_LED GND

19 PMC IO 38 DATA 21 PMC IO 37 GND Serial 3 TX

20 PMC IO 40 DATA 22 PMC IO 39 GE4_3 - GND

21 PMC IO 42 DATA 23 PMC IO 41 GE4_3 + Serial 3 CTS

22 PMC IO 44 GND PMC IO 43 GND GND

44

MVME2500 Installation and Use (6806800L01H)

Page 45

Controls, LEDs, and Connectors

Table 3-7 VMEbus P2 Connector (continued)

Pin Row A Row B Row C Row D Row Z

23 PMC IO 46 DATA 24 PMC IO 45 GE4_2 - Serial 3 RTS

24 PMC IO 48 DATA 25 PMC IO 47 GE4_2+ GND

25 PMC IO 50 DATA 26 PMC IO 49 GND Serial 4 RX

26 PMC IO 52 DATA 27 PMC IO 51 GE4_1 - GND

27 PMC IO 54 DATA 28 PMC IO 53 GE4_1 + Serial 4 TX

28 PMC IO 56 DATA 29 PMC IO 55 GND GND

29 PMC IO 58 DATA 30 PMC IO 57 GE4_0 - Serial 4 CTS

30 PMC IO 60 DATA 31 PMC IO 59 GE4_0 + GND

31 PMC IO 62 GND PMC IO 61 GND Serial 4 RTS

32 PMC IO 64 +5V PMC IO 63 +5V GND

3.4.2 Onboard Connectors

3.4.2.1 Flash Program Connector (P7)

The Flash Program Connector is depopulated in the production version of the MVME2500.

However, each pin is exposed for the 60-pin header connector for the JTAG boundary scan.

Table 3-8 Flash Programming Header (P7)

Pin Signal Description

1 HOLD 1

2 Chip Select 1

3 Chip Select 0

4 Programmer's VCC

5 Master In Slave OUT (MISO)

6 HOLD 0

7 Keying

8 CLOCK

MVME2500 Installation and Use (6806800L01H)

45

Page 46

Controls, LEDs, and Connectors

Table 3-8 Flash Programming Header (P7) (continued)

Pin Signal Description

10 Master OUT Slave IN (MOSI)

3.4.2.2 SATA Connector (J3)

The onboard customized SATA connector is compatible with the Emerson SATA kit, namely

VME-64GBSSDKIT and IVME7210-MNTKIT.

Table 3-9 Custom SATA Connector (J3)

Pin Signal Description Pin Signal Description

1 GND 21 GND

2 GND 22 SATA POWER ENABLE

GND

3NC 23NC

4 SATA TX + 24 SATA DETECT

5NC 25NC

6 SATA TX - 26 GND

7 GND 27 NC

8 GND 28 GND

9 GND 29 GND

10 GND 30 GND

11 NC 31 +3.3V

12 SATA RX - 32 +5V

13 NC 33 +3.3V

14 SATA RX + 34 +5V