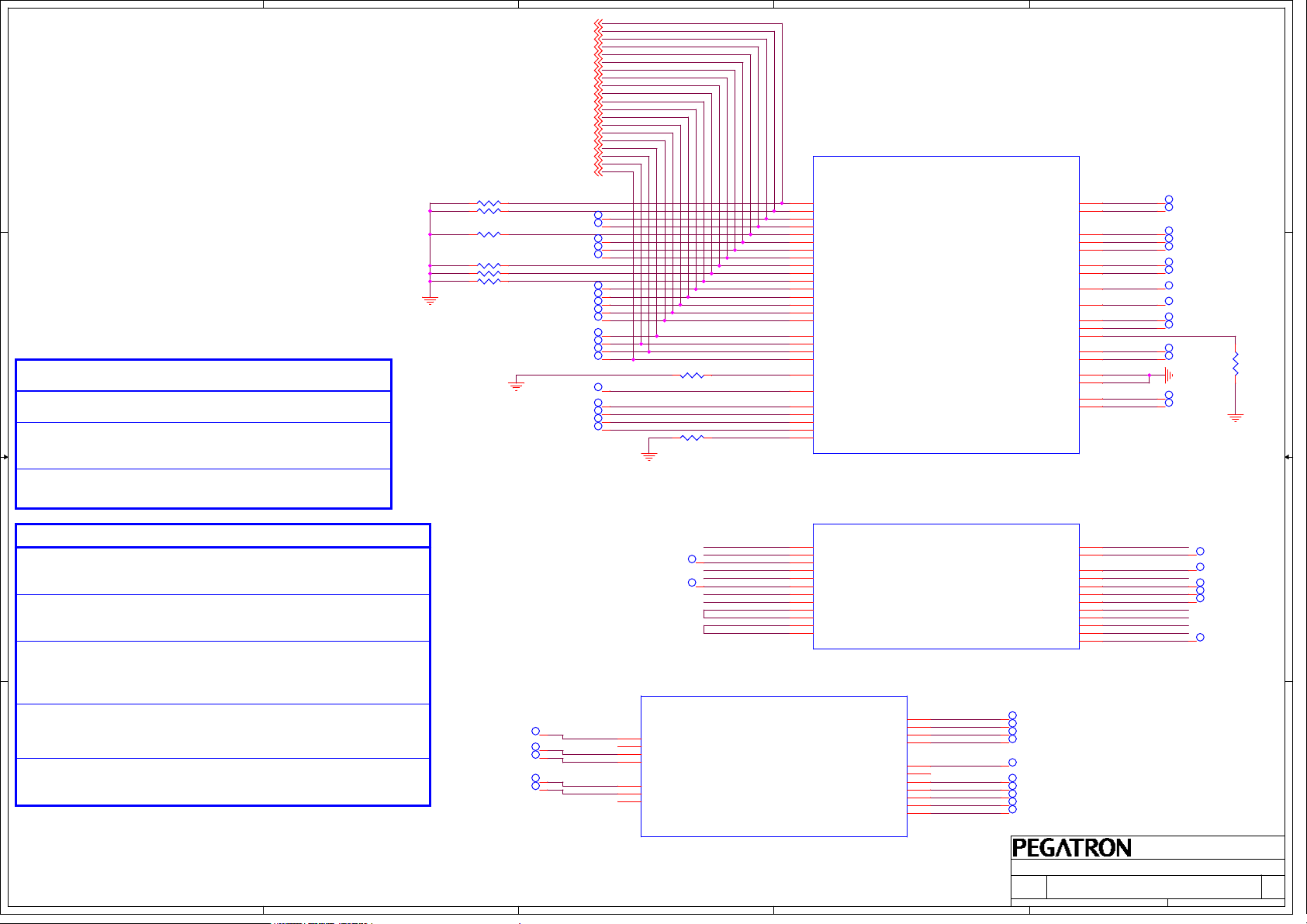

Dell XPS 18 1820 Schematics

5

SYSTEM PAGE REF.

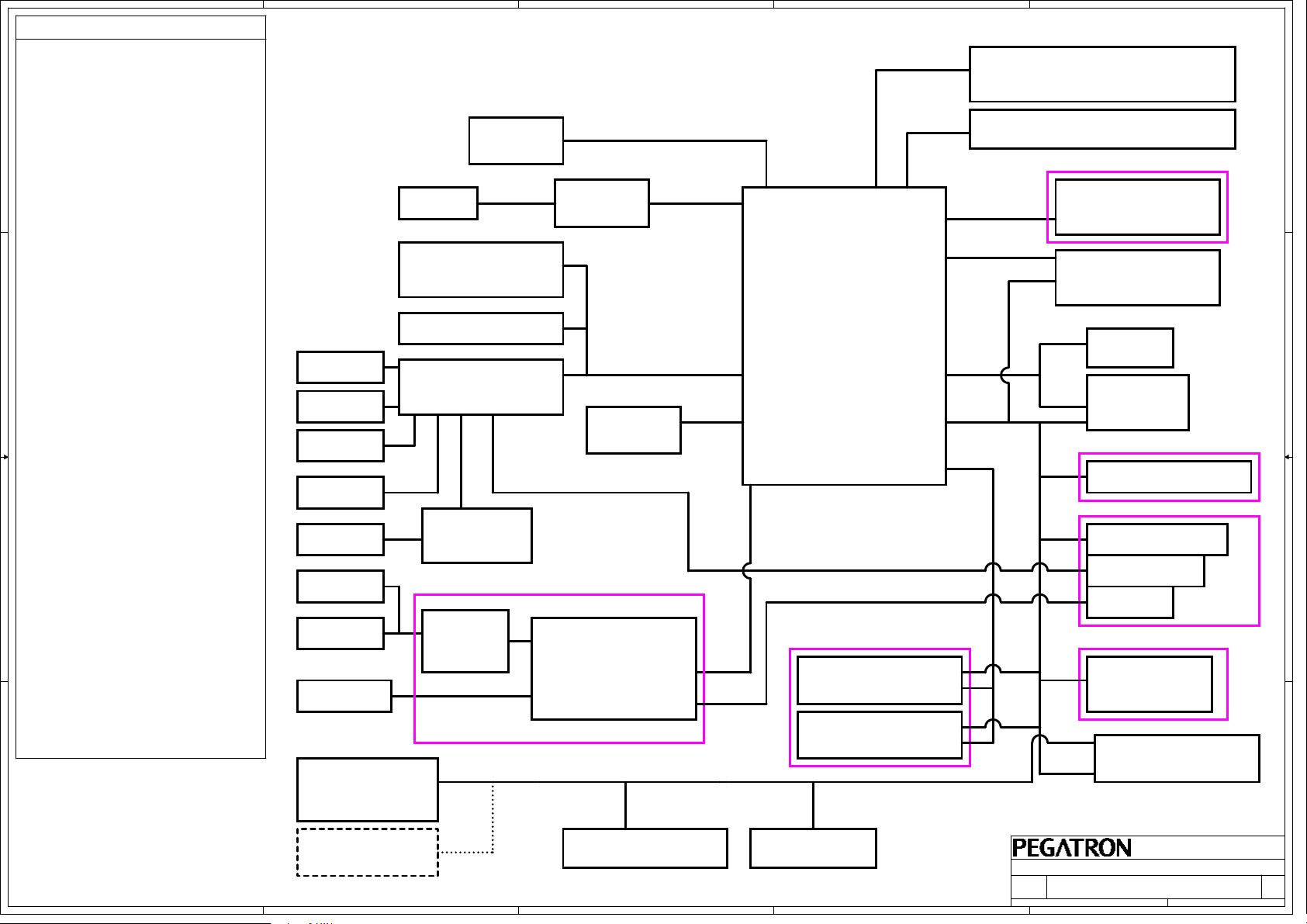

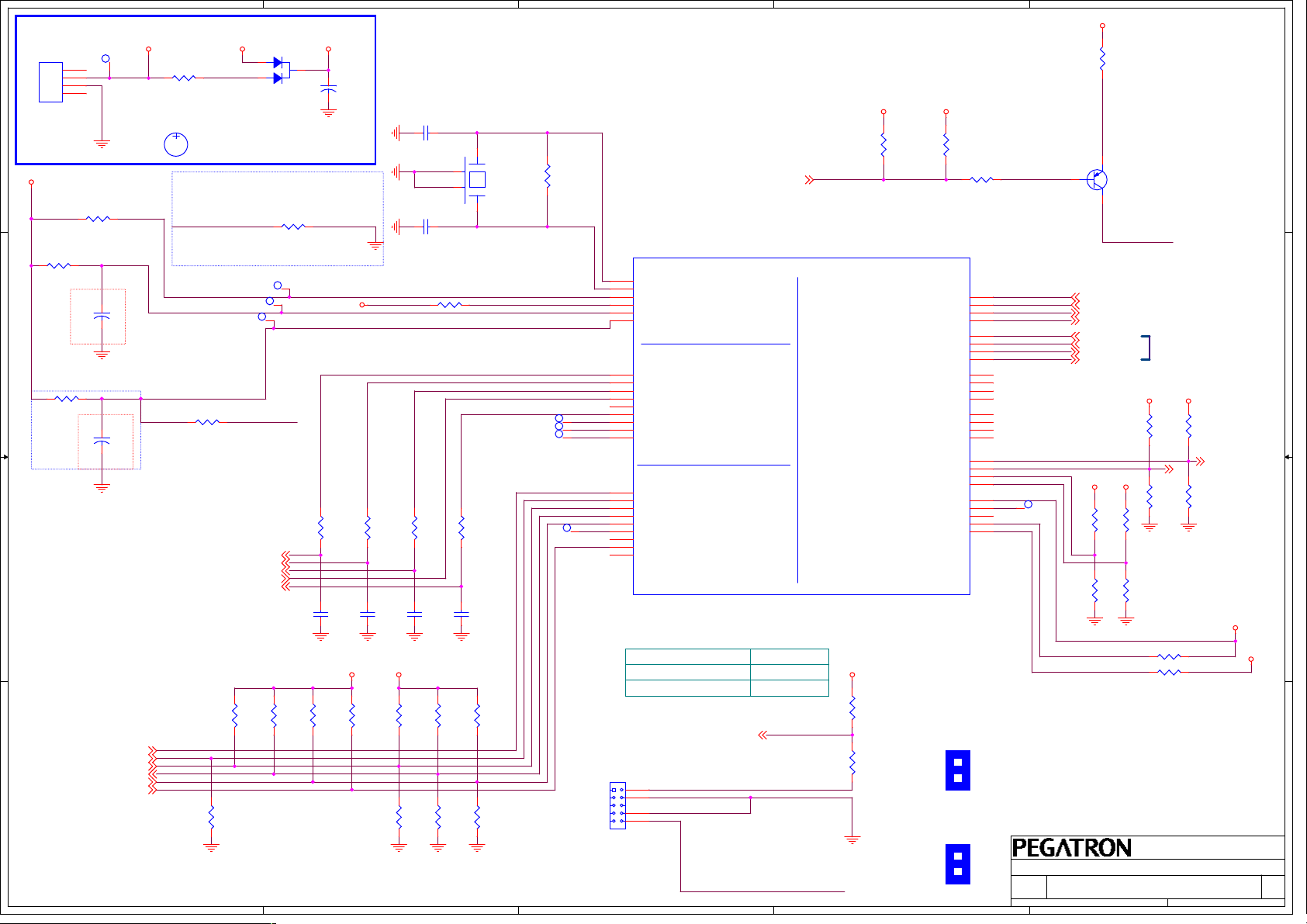

01. Block Diagram

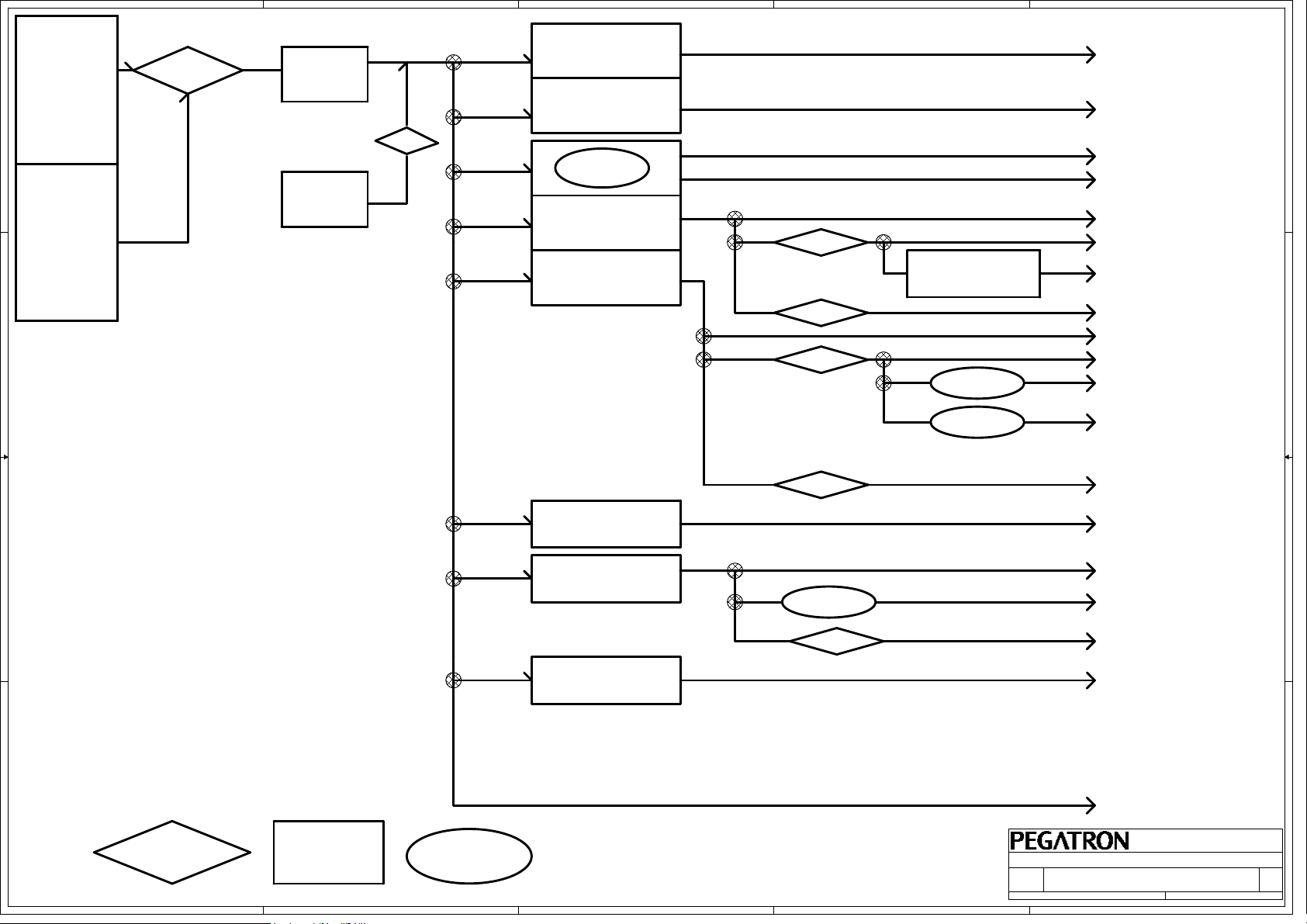

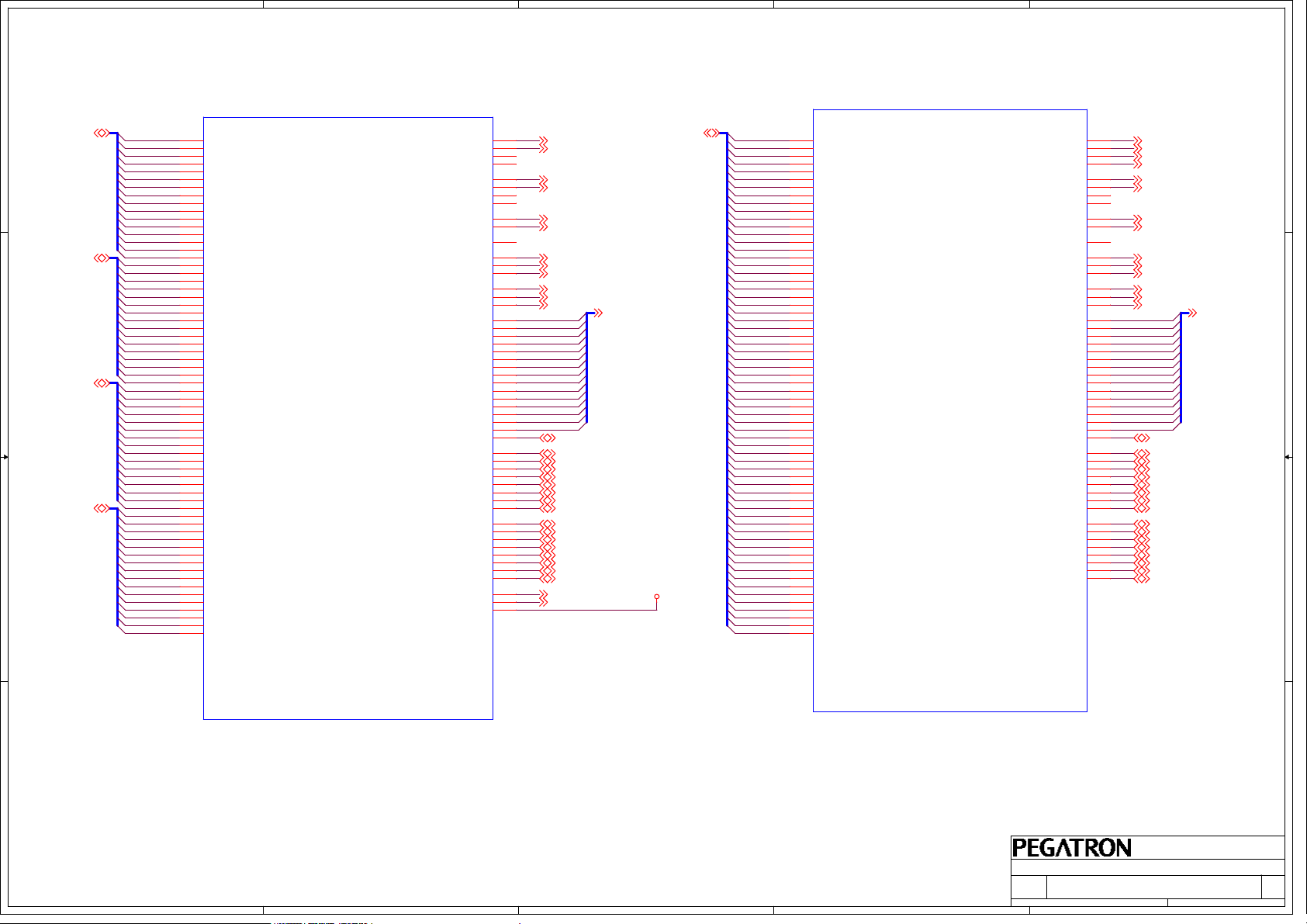

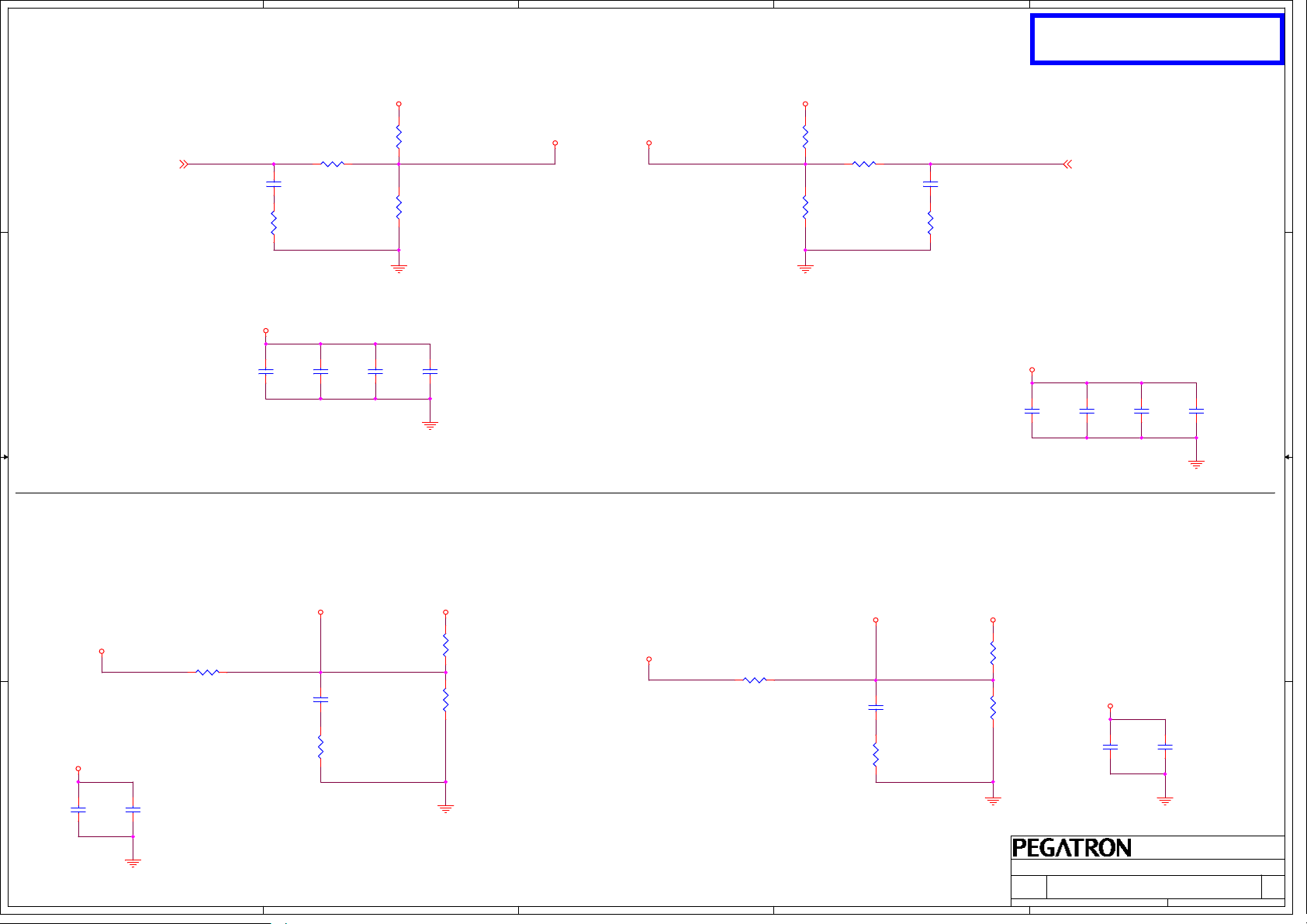

02. POWER FLOW

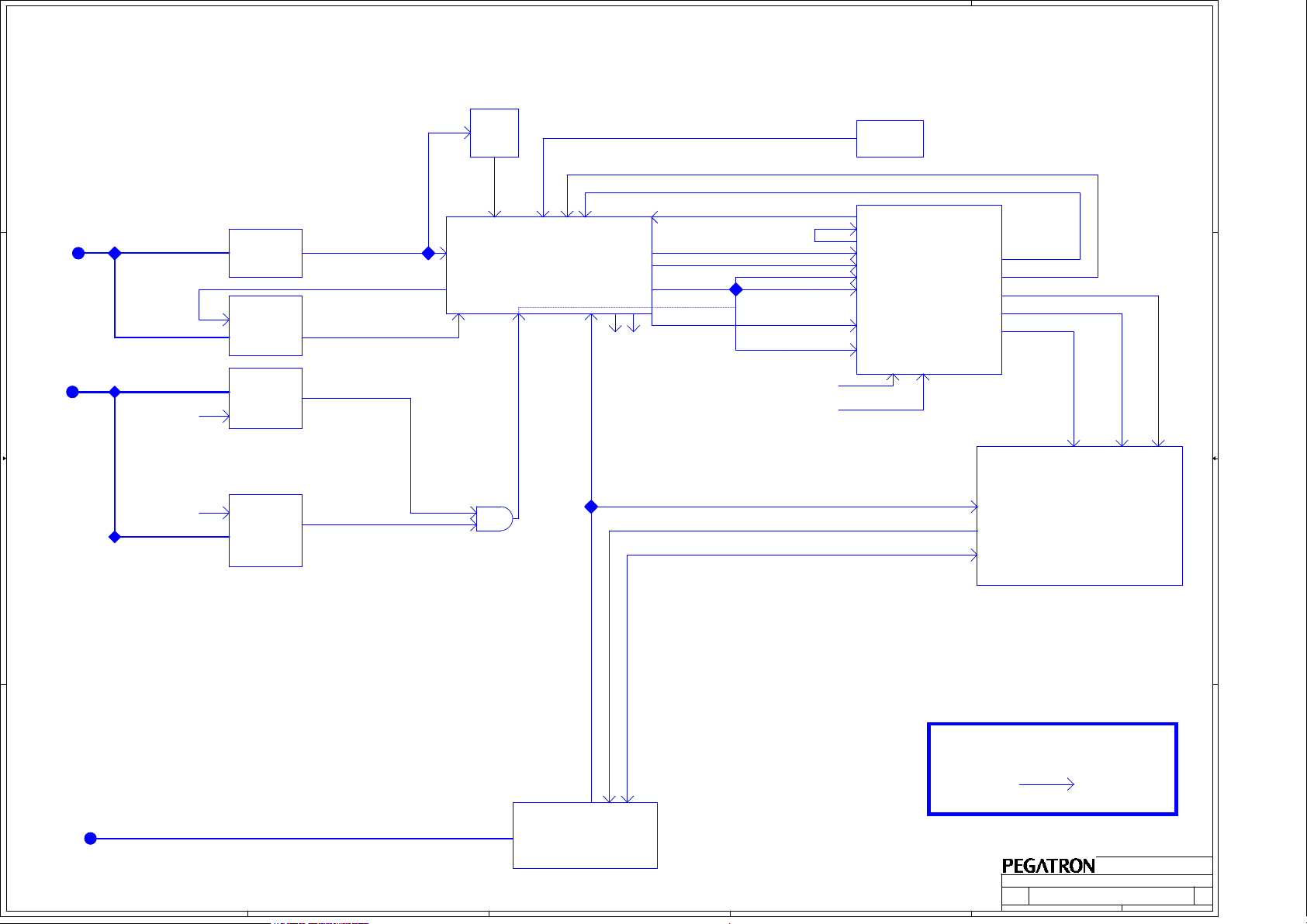

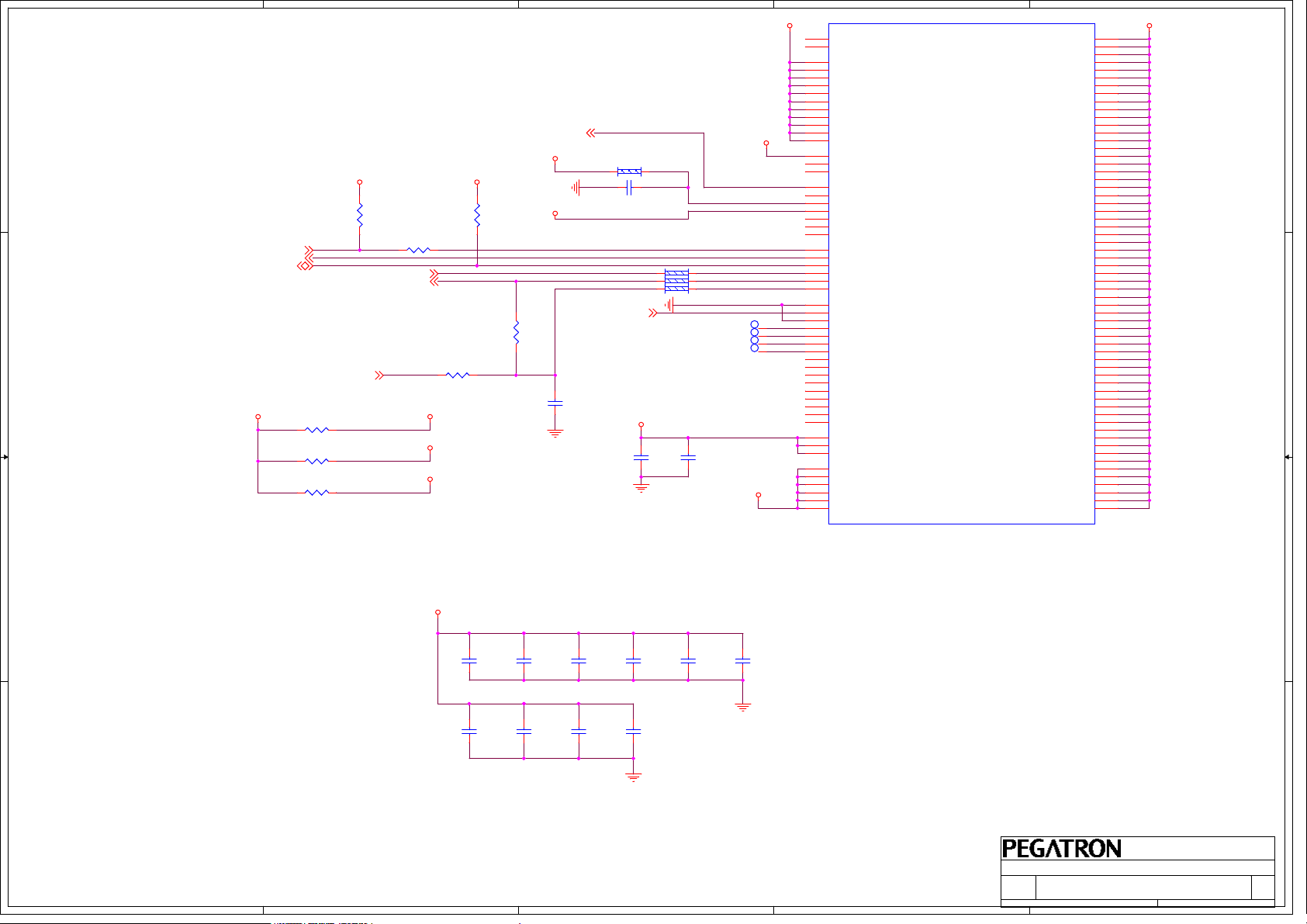

03. Power On Sequence

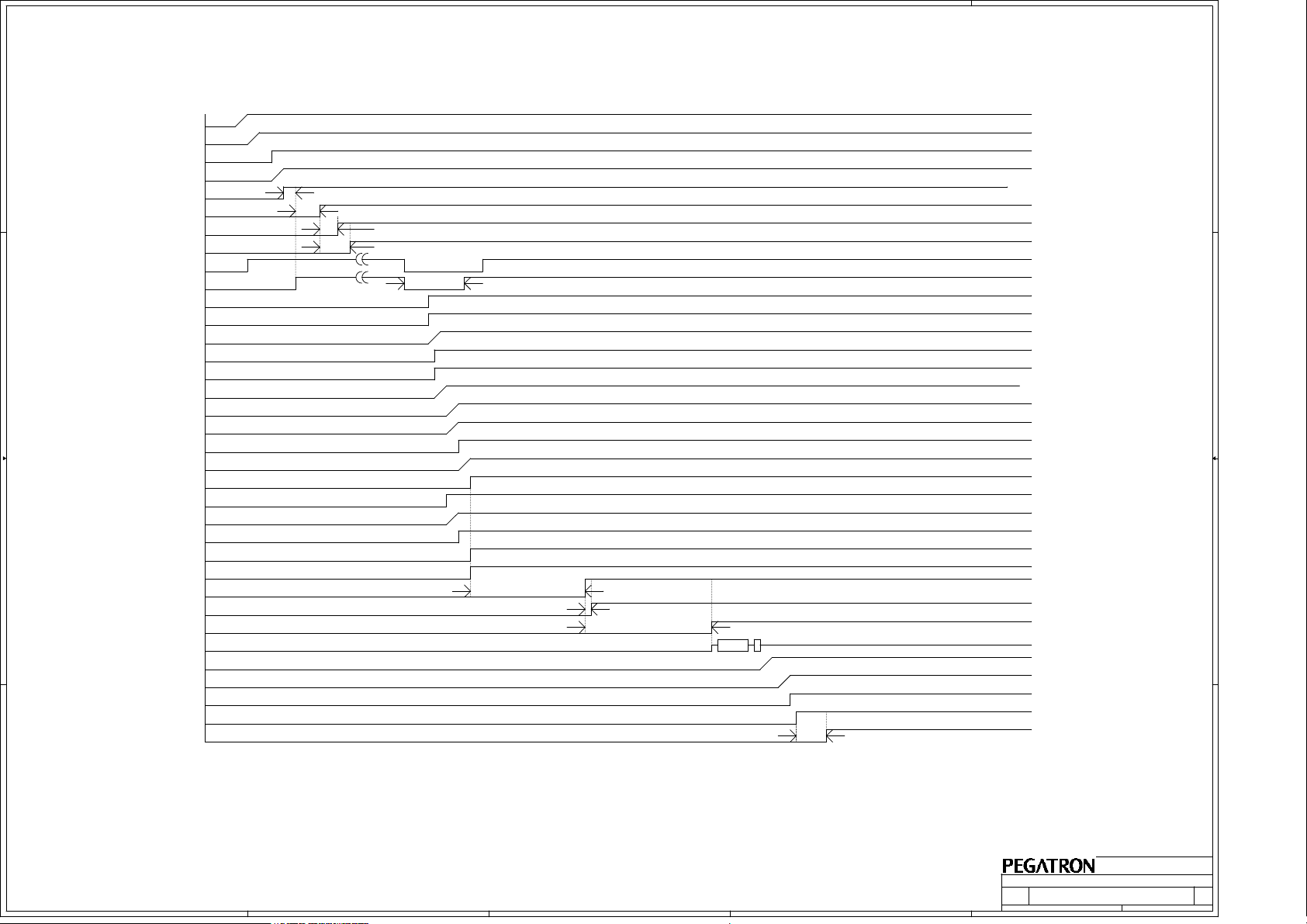

04. Power On Timing

05. CPU(1)_MISC.JTAG,DDI.EDP

06. CPU(2)_DDR3L-RS

07. CPU(3)_HSW POWER

D D

08. CPU(4)_GND

09. CPU(5)_RESERVED

10. CPU(6)_XDP

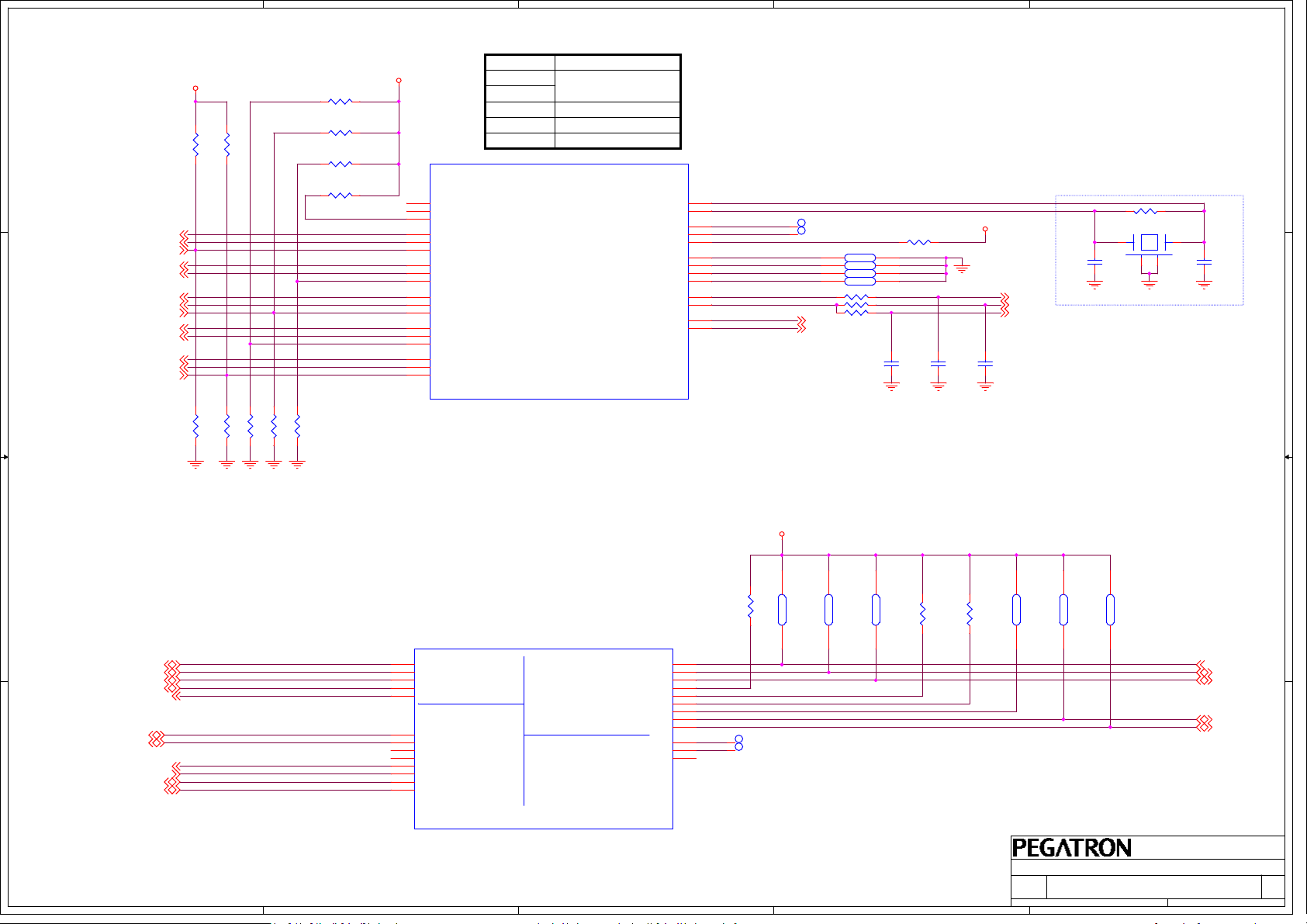

11. DDR3L-RS_Memory Down

12. DDR3L-RS_SO-DIMM

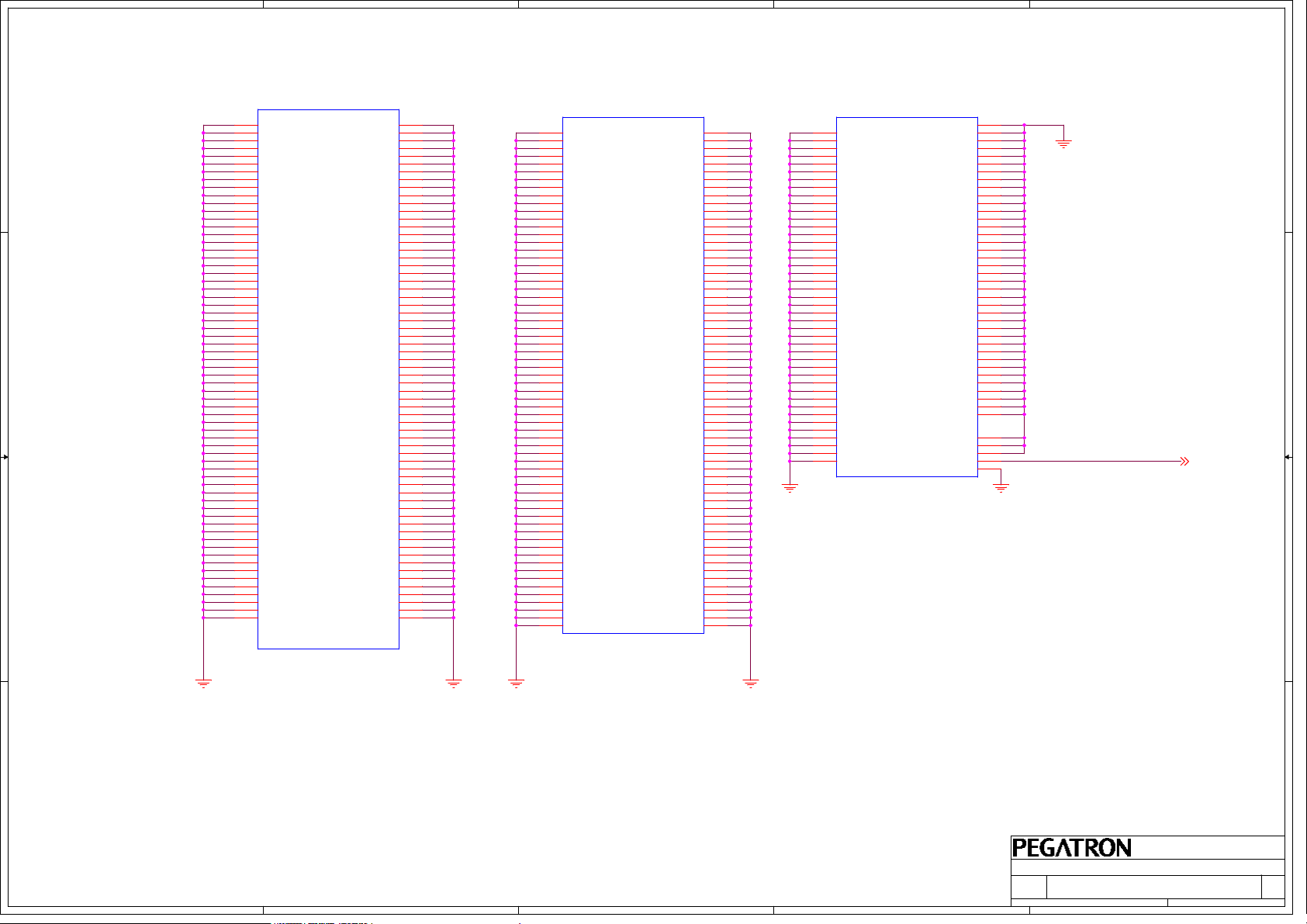

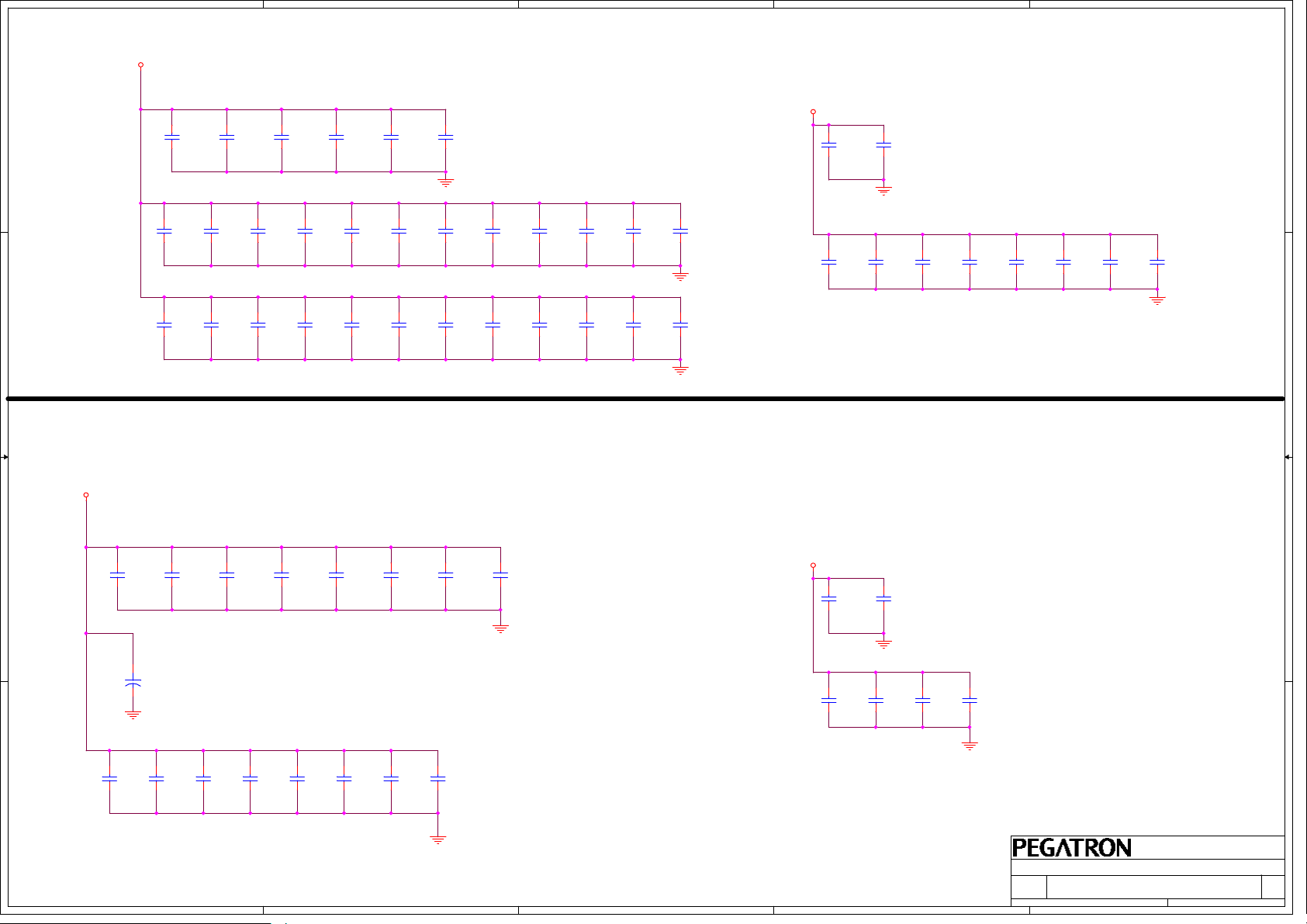

13. DDR3L-RS_Decoupling

14. DDR3L-RS_CA/DQ Voltage

15. PCH_SATA,IHDA,RTC

16. PCH_CLK,SMB,LPC

17. PCH_FDI,DMI,SYS PWR

18. PCH_DP,PCI

19. PCH_PCIE,NVRAM,USB

20. PCH_CPU,GPIO,MISC

21. PCH_POWER,GND

22. PCH_SPI,SMB

23. shippingmode

24. NGFF CARD_WLAN

25. NGFF CARD_mSATA

C C

26. SATA redriver

27. SATA conn

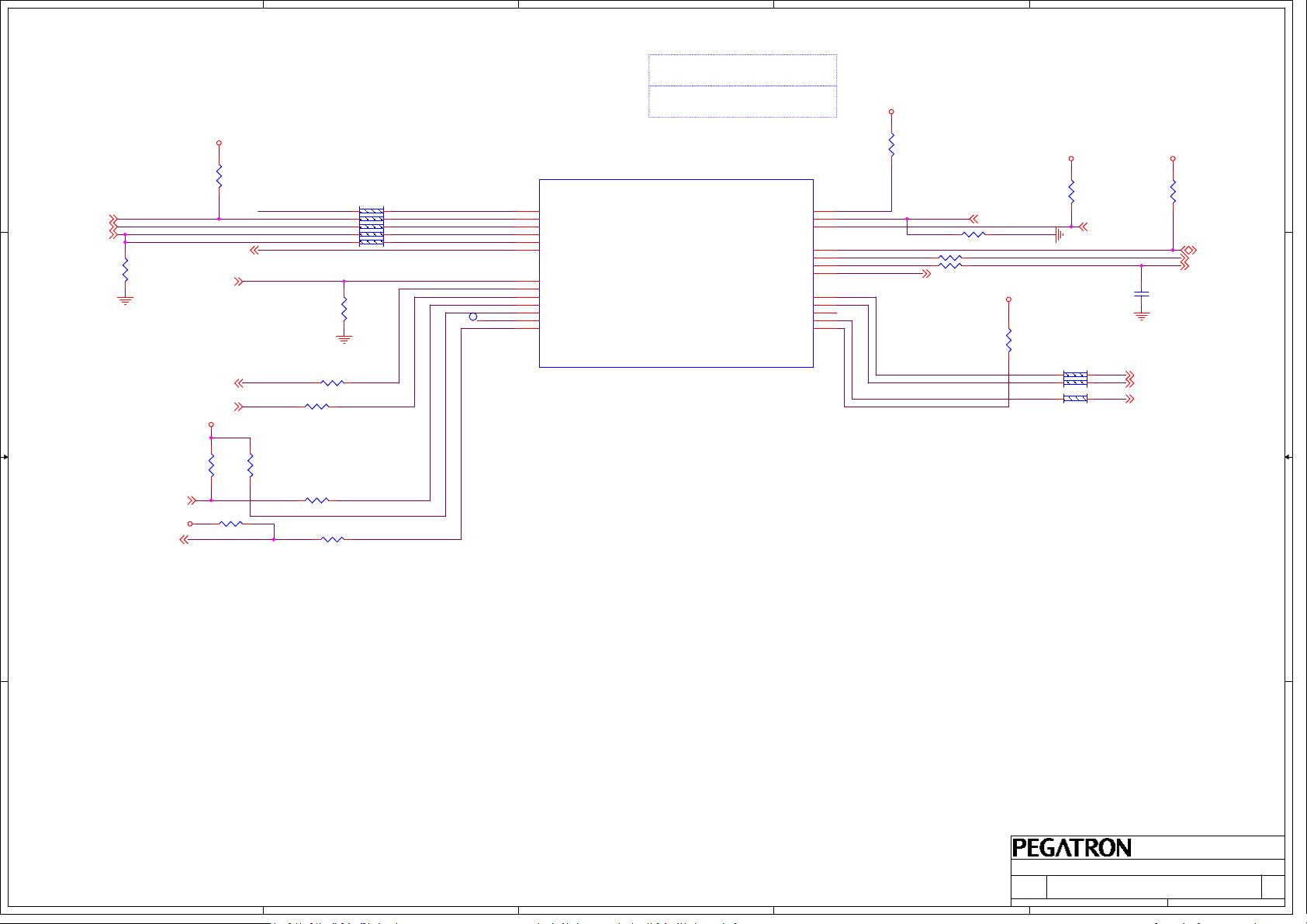

28. eDP_ANX1122

29. LVDS

30. USB3.0 redriver

31. USB Touch

32. ALS,CAMERA,DMIC

33. RIO LIO connector

34. Homekey_connector

35. Sensor_Hub_IT8350E

36. Gyro&G&Pressure-sensor

37. FFS

38. ITE 8528-1

39. ITE 8528-2

40. TPM

41. VIBRATER

42. THERMAL / FAN

43. RST_Reset Circuit

B B

44. BUG_Debug

45. DSG_Discharge

46. SCREW HOLE

47. POWER_PROTECT

48. DC_DC/BAT CONN

49. DC IN

50. +AC_BAT_SYS & Charger

51. +VCORE

52 .+VCORE1

53. +3P3VSB/+5VSB

54. +1P35V_DUAL/+VTT_DDR

55. +1P05V

56. +1P5V

57. Switch

IMPBW-CS

Corse MLK

FAN

Buttons

VIBRATER

HOME Button

Speaker R

Speaker L

GHS

Combo Jack

G Sensor

A A

E compass

4

FFS

LNG3DMTR

LCD Panel

LVDS

TPM

Atmel

AT97SC3204-X2A1D-AB

Debug Conn.

EC

IT8528

I2C&GPIO

Touch Sensing

Cypress

CG7216AMT

AMP 2W

stereo

TI TPA3113

3

SMBUS

PS8526

LPC

SPI ROM

Quad flash

SMBUS

IO Board-L

REALTEK

ALC3661-CG A3

2

1

Block Diagram

CHA

CHB

eDPBridge IC

SoC

Broadwell-U

DDR3L-RS 1600 1.35V

MEMORY DOWN x16 4GB

DDR3L 1600 SO-DIMM 1.35V

IO Board-L

PCIEx1

CardReader

RTS5209-GR

PCIEx1

NGFF

WLAN + BT4.0

Haswell-U

BDW ULV 15W DC

40 X 24 X1.3 mm

BGA 1168 pin

Azalia

IO Board-L

USB3.0 Port

USB3.0 Port

SATA

USB2.0

USB3.0

I2C

HDD

NGFF

mSATA

Touch COBSPI ROM

Touch Screen

Camera Module

CMOS Camera

ALS Sensor

DMICs

IO Board-R

RF Receiver

KB/MS

Sensor Hub

IT8350E

DE303DLHC

1.01FINAL

1.01FINAL

G Sensor

LIS3DH(A)

5

4

without E-compass

PRESSURE SENSOR

LPS331AP

3

Gyro

TX3GD20

2

1.01FINAL

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IMPBW-CS

IMPBW-CS

IMPBW-CS

Engineer:

1

Block Diagram

Block Diagram

Block Diagram

Stonko_Chen

Stonko_Chen

Stonko_Chen

1 57Tuesday, March 11, 2 014

1 57Tuesday, March 11, 2 014

1 57Tuesday, March 11, 2 014

Rev

Rev

Rev

A00

A00

A00

5

4

3

2

1

ISL95833HRTZ-T

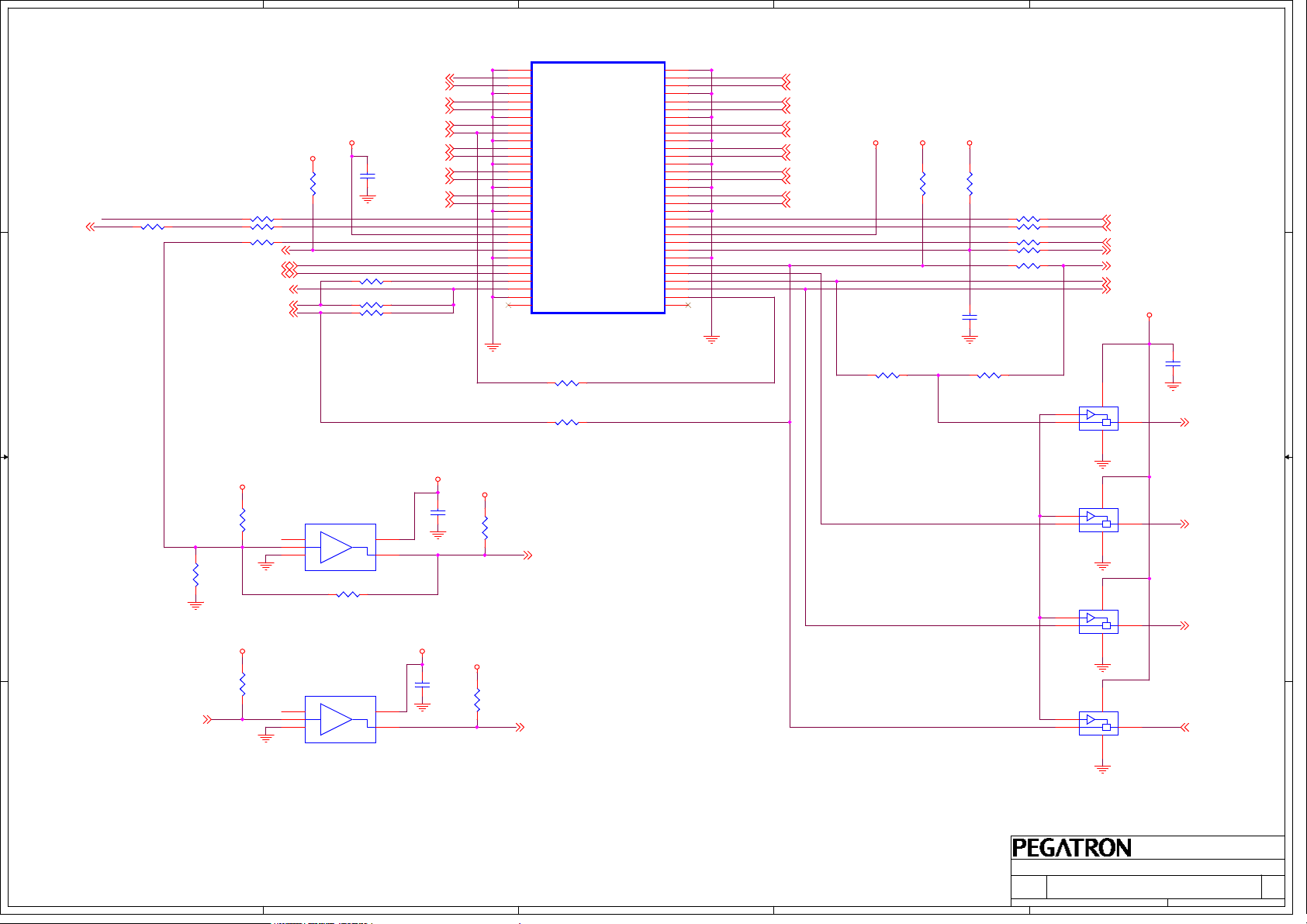

EXT_DC_IN +AC_BAT_SYS

Adapter_DCJACK

SWITCH

Charger

BQ24735RGRR

65W

D D

1.519A/19V

2.406A/12V

0.829A/19V

1.312A/12V

H/N-MOS 7mOhm

L/N-MOS 2.1mOhm

Efficiency is about 80%

ISL95833HRTZ-T

H/N-MOS 7mOhm

L/N-MOS 2.1mOhm

Efficiency is about 80%

N-MOS

0.141A/19V

0.223A/12V

TPS51225C LDO

23.1A

12.6A

0.07A

0.0707A

Battery

4S2P

69WHR

1.718A/19V

2.720A/12V

Adapter_Docking

1.717A/19V

65W

C C

2.719A/12V

0.553A/19V

0.875A/12V

TPS51225C

H/N-MOS 25mOhm

L/N-MOS 25mOhm

Efficiency is about 80%

TPS51225C

H/N-MOS 25mOhm

L/N-MOS 25mOhm

Efficiency is about 80%

RT8299A

Efficiency is about 80%

5.2227A

7.91A

N-MOS

N-MOS

N-MOS

N-MOS

3.2627A

7.1574A

TPS51463

Efficiency is a bout 80%

RT8204L LDO

+NMOS

RT9059 LDO

0.0007A

2.42A

2.8A

1.96A

0.0525A

4.8874A

1.4A

0.87A

0.7A

0.7A

+VCORE

TDC = 23.1A Ima x = 33A

+VGFX_CORE

TDC = 12.6A Ima x = 18A

+5VA

TDC = 0.07A Ima x = 0.1A

+3P3VA

TDC = 0.0707A I max = 0.101A

+5VSB

TDC= 0.0007A Im ax = 0.001A

+5V

TDC =2.6327A I max =3.761A

+VCCSA

TDC = 2.8A Ima x = 4A

+5V_DUAL

TDC = 1.96A Im ax = 2.8A

+3P3VSB

TDC = 0.0525A I max = 0.075A

+3P3V

TDC = 4.8874A Imax = 6.982A

+1P5V_PCH

TDC = 1.4A Ima x = 2A

+1P8V

TDC = 0.8694A Imax = 1.242A

+3P3V_DUAL

TDC = 0.7A Ima x = 1A

+12V

TDC = 0.7A Ima x = 1A

0.606A/19V

B B

0.959A/12V

TPS51216

H/N-MOS 25mOhm

L/N-MOS 25mOhm

Efficiency is about 80%

6.825A

TPS51216 LDO

N-MOS

0.788A/19V

1.248A/12V

A A

Switch ON/OFF

5

4

LinearSwitching

RT8204L

H/N-MOS 25mOhm

L/N-MOS 25mOhm

Efficiency is about 80%

3

2

2.8A

0.525A

3.5A

11.4121A

0.357A

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

+1P35V_DUAL

TDC = 2.8A Ima x = 4A

+0.675VS

TDC = 0.525A I max = 0.75A

+1P35V

TDC = 3.5A Ima x = 5A

+VCCIO

TDC = 11.4121A Imax = 16.303A

BL_VIN

TDC = 0.357A I max =0.51A

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

IMPBW-CS

IMPBW-CS

IMPBW-CS

1

POWER FLOW

POWER FLOW

POWER FLOW

Stonko_Chen

Stonko_Chen

Stonko_Chen

2 57Tuesday, March 11, 2 014

2 57Tuesday, March 11, 2 014

2 57Tuesday, March 11, 2 014

Rev

Rev

Rev

A00

A00

A00

5

4

3

2

1

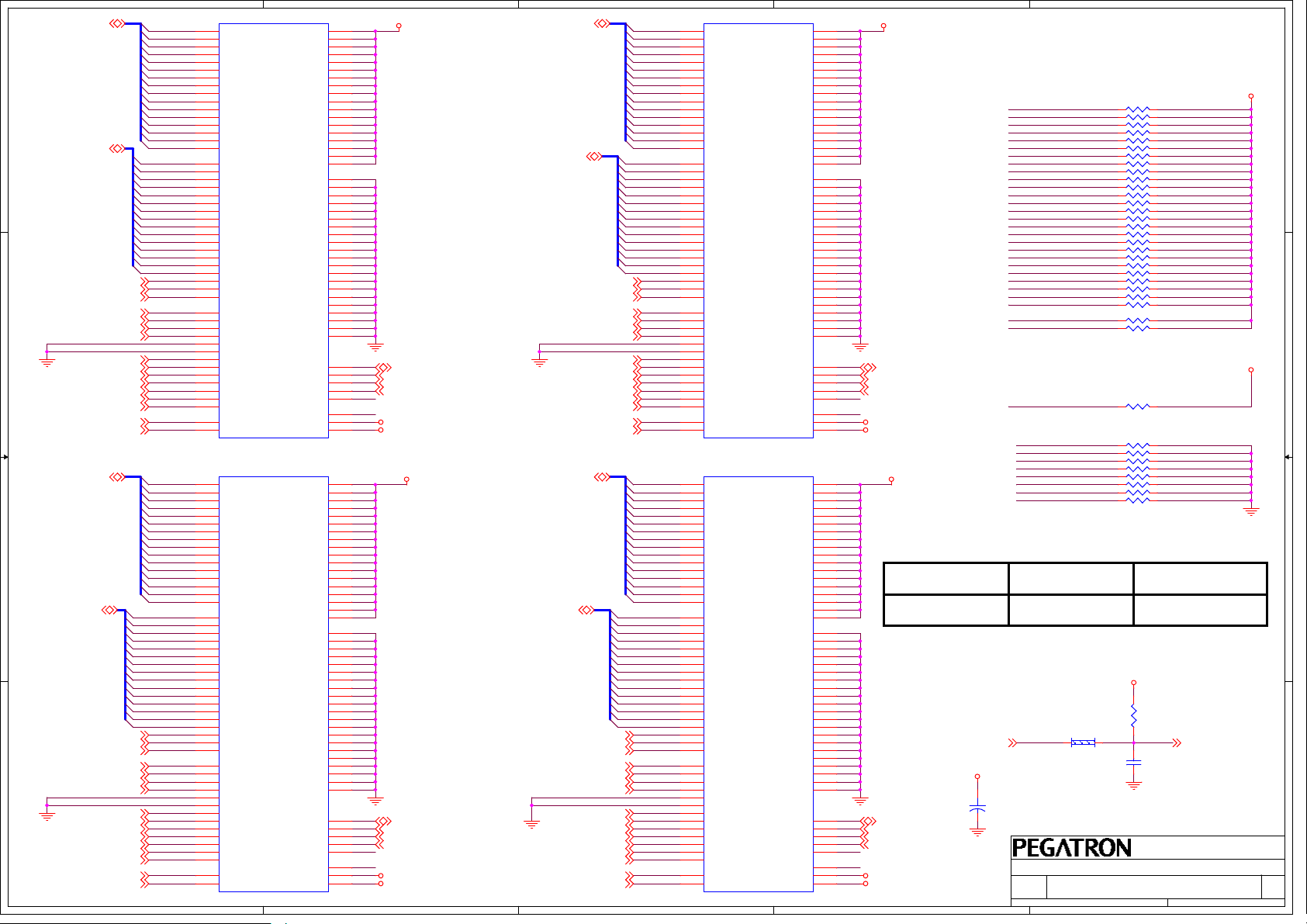

Power On Sequence Diagram G3-S0 R0.3 (non-iAMT,non-Deep Sx)

D D

Reset

Logic

(R)

PWR_SW#

10

Power On

Button

3

EC_RST#

AC_BAT_SYS

C C

AC_BAT_SYS & +5VSB & +3P3VSB

SUSC_EC#

13

+3VA

+5VA

+3P3VSB

+5VSB

+1P35V_DUAL

+3P3V_DUAL

+5V_DUAL

+3VA_EC

VSUS_ON

SUS_PWRGD

3

EC

ITE8519

6

7

16

delay 99ms

19

15

SUSC_EC#

SUSB_EC#

13

VRM_PWRGD

ALL_SYSTEM_PWRGD

SUSB_EC#

15

B B

+3P3V

+5V

+12V

+19V

PM_PWROK

DPWROK

SLP_SUS#

PM_PWRBTN#

PM_RSMRST#

17

4

5

11

8

PM_PWROK

SYS_PWROK

+VCC_RTC

RTC_RST#

VRM_PWRGD

19

CPU_VR_EN

18

SVID

22

9

23

SUSACK#

SUSWARN#

PCH_PWROK

APWROK

SYS_PWROK

1

2

SLP_S4#

SLP_S3#

DRAMPWROK

PLT_RST#

PROCPWRGD

PCH

VR_READY

VR_EN

SVID

SLP_S4#

SLP_S3#

12

14

H_CPUPWRGD

21 20

BUF_PLT_RST#

24

RSTIN#

UNCOREPWRGOOD

CPU

PM_DRAM_PWRGD

SM_DRAMPWROK

Power On Sequence

A A

SVID

1

+AC_BAT_SYS

+VCORE

5

4

3

2

1.01FINAL

1.01FINAL

1.01FINAL

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

IMPBW-CS

IMPBW-CS

IMPBW-CS

24

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

Power On Sequence

Power On Sequence

Power On Sequence

Stonko_Chen

Stonko_Chen

Stonko_Chen

Rev

Rev

Rev

A00

A00

A00

3 57Tuesday, March 11, 2014

3 57Tuesday, March 11, 2014

3 57Tuesday, March 11, 2014

5

4

3

2

1

Power On Sequence Diagram G3-S0 R0.3

D D

6

C C

+1.5V/+3V/+5V/+12V

+3VA_EC

1

EC_RST#

2

VSUS_ON

3

+3VSUS/+5VSUS

SUS_PWRGD

4

PM_RSMRST#

5

ME_SUSPWRDNACK

ME_AC_PRESENT

7

PWR_SW#

8

PM_PWRBTN#

9

PM_SUSC#

10

SUSC_EC#

11

PM_SUSB#

12

SUSB_EC#

13

T0>10ms

T1= 20ms

T2<200ms

0<T3<90ms

(falling edge)

T4=16ms

(non-iAMT,non-Deep Sx)

+0.75VS/+1.5VS/+1.8VS/+3VS/+5V S

+VTT_PCH

+VCCP

+VCCP_PWRGD

14

+VCCSA

+VCCSA_PWRGD

dGPU_PWR_EN

+VGA_CORE

dGPU_PWROK

ALL_SYSTEM_PWRGD

B B

15

16

ME_PWROK/PCH_PWROK

17

H_DRAM_PWRGD

18

H_CPUPWRGD

19

CPU_VRON

SVID

20

T5= TBD

T6>1ms

T7>100ms

+VCC_CORE

+VGFX_CORE

VRM_PWRGD

21

SYS_PWROK

22

BUF_PLT_RST#

23

T8>TBD

A A

1.01FINAL

1.01FINAL

1.01FINAL

Title :

Title :

Title :

Power On Timing

Power On Timing

Power On Timing

Stonko_Chen

Stonko_Chen

Engineer:

Engineer:

IMPBW-CS

IMPBW-CS

IMPBW-CS

1

Engineer:

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Stonko_Chen

4 57Tuesday, March 11, 2014

4 57Tuesday, March 11, 2014

4 57Tuesday, March 11, 2014

Rev

Rev

Rev

A00

A00

A00

5

+VCCST

12

HR2

62 OHM

D D

HR3

I

1 2

VR_HOT#59

from Vcore

THRO_CP U45

from EC

C C

H_PROCH OT# H_PROCH OT#_D

0 Ohm

HR6

I

1 2

0 Ohm

I

CATERR#51

H_PECI_EC45

32

3

D

HQ1

2N7002

1

1

I

G

S

2

GND

GND

12

I

PC219

47PF/50V

NPO 5%

NOBOM

C201

Do Not Stuff

SM_DRAM RST#14

NI

HT98

12

GND

4

1

1 2

R114

I

43 OHM

NOBOM

GND

check to XDP

12

GND GND GND

1 2

1 2

HT2

HR7

200 Ohm

1%

I

NOBOM

12

HR8

121 Ohm

1%

I

HT1

HR456 OHM I

HR510KOhm I

1

12

1

TP_D61

PECI_EC_L PCSB

H_CPUPW RGD_R

SM_RCOM P_0

SM_RCOM P_1

SM_RCOM P_2

HR9

100 Ohm

1%

I

DDR_PG_ CTRL_S

12

D61

K61

N62

K63

C61

AU60

AV60

AU61

AV15

AV61

HR12

Do Not Stuff

NI

U1B

PROC_DETECT#

CATERR#

PECI

PROCHOT#

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST#

SM_PG_CNTL1

CL80647 01478404

I

HU1

1

NC

A

2

3 4

GND

SN74AUP 1G07DCKR

3

HSW_ULT_DDR3L

MISC

12

GND

JTAG

<PART_S YM_NUM>

I

HC1

0.1UF/6.3V

THERMAL

PWR

DDR3L

+1P35V_ DUAL

I

5

VCC

Y

PROC_TCK

PROC_TMS

PROC_TRST#

PROC_TDI

PROC_TDO

12

HR10

220KOhm

I

1%

12

HR13

Do Not Stuff

NI

PRDY#

PREQ#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

+3P3V+3P3VSB

12

J62

K62

E60

E61

E59

F63

F62

J60

H60

H61

TP_H61

H62

TP_H62

K59

TP_K59

H63

TP_H63

K60

TP_K60

J61

TP_J61

HR11

Do Not Stuff

NI

1%

2

GR1

1

1

1

1

1

1

+VCCST

1

1

G

HT3

HT4

HT5

HT6

HT7

HT8

12

GR1

Do Not Stuff

NI

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

DDR_PG_ CTRL 62

+1P35V_ DUAL

32

3

D

HQ2

2N7002

I

S

2

M_A_B_D IMM_ODT

XDP_BPM 0 13

XDP_BPM 1 13

to 1P35V

S3 control

12

GR2

51 OHM

I

GND GND

GR3

GR2

12

GR3

Do Not Stuff

NI

1

XDP_PRD Y# 13

XDP_PRE Q# 13

XDP_TCK 13,42

XDP_TMS 13,42

XDP_TRS T# 13,19

XDP_TDI 1 3

XDP_TDO 13

1 2

GND GND GND

B B

DP_DDI1_T X0#29

DP_DDI1_T X029

DP_DDI1_T X1#29

DP_DDI1_T X129

DP_DDI1_T X2#29

DP_DDI1_T X229

DP_DDI1_T X3#29

DP_DDI1_T X329

A A

5

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

HT81

HT82

HT83

HT84

HT85

HT86

HT87

1

1

1

1

1

1

1

TP_C51

TP_C50

TP_C53

TP_B54

TP_C49

TP_B50

TP_A53

U1A

C54

DDI1_TXN[0]

C55

DDI1_TXP[0]

B58

DDI1_TXN[1]

C58

DDI1_TXP[1]

B55

DDI1_TXN[2]

A55

DDI1_TXP[2]

A57

DDI1_TXN[3]

B57

DDI1_TXP[3]

C51

DDI2_TXN[0]

C50

DDI2_TXP[0]

C53

DDI2_TXN[1]

B54

DDI2_TXP[1]

C49

DDI2_TXN[2]

B50

DDI2_TXP[2]

A53

DDI2_TXN[3]

B53

DDI2_TXP[3]

CL80647 01478404

I

4

HSW_ULT_DDR3L

C45

EDP_TXN0

B46

EDP_TXP0

A47

EDP_TXN1

B47

EDP_TXP1

C47

EDP_TXN2

EDP_TXP2

EDPDDI

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

TP_C47

C46

TP_C46

A49

TP_A49

B49

TP_B49

A45

B45

D20

A43

EDP_DISP_ UTIL

DP_COMP

1

1

1

1

EDP_TXN 0 33

EDP_TXP 0 33

EDP_TXN 1 33

EDP_TXP 1 33

HT89

NOBOM

HT90

NOBOM

HT91

NOBOM

HT92

NOBOM

EDP_AUX N 33

EDP_AUX P 33

1

3

HT95

+VCCIOA_O UT

12

NOBOM

HR16

24.9 OHM

I

1%

2

HR14 66.5OhmI 1%

1 2

HR15 66.5OhmI 1%

M_CHB_O DT1 15

M_CHB_O DT0 15

NUTS for Thermal

H1

CT197B6 3D47

I

1.01FINAL

1.01FINAL

1.01FINAL

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

H2

CT197B6 3D47

I

Engineer:

Engineer:

Engineer:

IMPBW-CS

IMPBW-CS

IMPBW-CS

H3

CT197B6 3D47

I

Title :

Title :

Title :

H4

CT197B6 3D47

I

CPU(1)_MISC.JTAG,DDI.EDP

CPU(1)_MISC.JTAG,DDI.EDP

CPU(1)_MISC.JTAG,DDI.EDP

Stonko_Chen

Stonko_Chen

Stonko_Chen

5 57Tuesday, March 11, 2 014

5 57Tuesday, March 11, 2 014

1

5 57Tuesday, March 11, 2 014

Rev

Rev

Rev

A00

A00

A00

5

4

3

2

1

HSW_ULT_DDR3L

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS#

SB_WE#

SB_CAS#

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

M_CHB_C LK0# 15

M_CHB_C LK0 15

M_CHB_C LK1# 15

M_CHB_C LK1 15

M_CHB_C KE0 15

M_CHB_C KE1 15

M_CHB_C S#0 15

M_CHB_C S#1 15

M_CHB_R AS# 15

M_CHB_W E# 15

M_CHB_C AS# 15

M_CHB_B A0 15

M_CHB_B A1 15

M_CHB_B A2 15

M_CHB_M AA0

M_CHB_M AA1

M_CHB_M AA2

M_CHB_M AA3

M_CHB_M AA4

M_CHB_M AA5

M_CHB_M AA6

M_CHB_M AA7

M_CHB_M AA8

M_CHB_M AA9

M_CHB_M AA10

M_CHB_M AA11

M_CHB_M AA12

M_CHB_M AA13

M_CHB_M AA14

M_CHB_D QS0# 15

M_CHB_D QS1# 15

M_CHB_D QS2# 15

M_CHB_D QS3# 15

M_CHB_D QS4# 15

M_CHB_D QS5# 15

M_CHB_D QS6# 15

M_CHB_D QS7# 15

M_CHB_D QS0 15

M_CHB_D QS1 15

M_CHB_D QS2 15

M_CHB_D QS3 15

M_CHB_D QS4 15

M_CHB_D QS5 15

M_CHB_D QS6 15

M_CHB_D QS7 15

M_CHB_M AA[0..14] 15

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

U1D

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HSW_ULT_DDR3L

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS#

SA_WE#

SA_CAS#

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_CHA_C LK0# 14

M_CHA_C LK0 14

M_CHA_C KE0 14

M_CHA_C KE1 14

M_CHA_C S#0 14

M_CHA_C S#1 14

M_CHA_R AS# 14

M_CHA_W E# 14

M_CHA_C AS# 14

M_CHA_B A0 14

M_CHA_B A1 14

M_CHA_B A2 14

M_CHA_M AA0

M_CHA_M AA1

M_CHA_M AA2

M_CHA_M AA3

M_CHA_M AA4

M_CHA_M AA5

M_CHA_M AA6

M_CHA_M AA7

M_CHA_M AA8

M_CHA_M AA9

M_CHA_M AA10

M_CHA_M AA11

M_CHA_M AA12

M_CHA_M AA13

M_CHA_M AA14

M_CHA_M AA15 14 M_CHB_M AA15 15

M_CHA_D QS0# 14

M_CHA_D QS1# 14

M_CHA_D QS2# 14

M_CHA_D QS3# 14

M_CHA_D QS4# 14

M_CHA_D QS5# 14

M_CHA_D QS6# 14

M_CHA_D QS7# 14

M_CHA_D QS0 14

M_CHA_D QS1 14

M_CHA_D QS2 14

M_CHA_D QS3 14

M_CHA_D QS4 14

M_CHA_D QS5 14

M_CHA_D QS6 14

M_CHA_D QS7 14

DIMM_VREF _CA 17

DIMM0_VRE F_DQ 17

M_CHB_D Q[0..63]15

M_CHA_M AA[0..14] 14

DIMM1_VRE F_DQ

M_CHB_D Q0

M_CHB_D Q1

M_CHB_D Q2

M_CHB_D Q3

M_CHB_D Q4

M_CHB_D Q5

M_CHB_D Q6

M_CHB_D Q7

M_CHB_D Q8

M_CHB_D Q9

M_CHB_D Q10

M_CHB_D Q11

M_CHB_D Q12

M_CHB_D Q13

M_CHB_D Q14

M_CHB_D Q15

M_CHB_D Q16

M_CHB_D Q17

M_CHB_D Q18

M_CHB_D Q19

M_CHB_D Q20

M_CHB_D Q21

M_CHB_D Q22

M_CHB_D Q23

M_CHB_D Q24

M_CHB_D Q25

M_CHB_D Q26

M_CHB_D Q27

M_CHB_D Q28

M_CHB_D Q29

M_CHB_D Q30

M_CHB_D Q31

M_CHB_D Q32

M_CHB_D Q33

M_CHB_D Q34

M_CHB_D Q35

M_CHB_D Q36

M_CHB_D Q37

M_CHB_D Q38

M_CHB_D Q39

M_CHB_D Q40

M_CHB_D Q41

M_CHB_D Q42

M_CHB_D Q43

M_CHB_D Q44

M_CHB_D Q45

M_CHB_D Q46

M_CHB_D Q47

M_CHB_D Q48

M_CHB_D Q49

M_CHB_D Q50

M_CHB_D Q51

M_CHB_D Q52

M_CHB_D Q53

M_CHB_D Q54

M_CHB_D Q55

M_CHB_D Q56

M_CHB_D Q57

M_CHB_D Q58

M_CHB_D Q59

M_CHB_D Q60

M_CHB_D Q61

M_CHB_D Q62

M_CHB_D Q63

D D

M_CHA_D Q[15:0]14

M_CHA_D Q[31:16]14

C C

M_CHA_D Q[47:32]14

M_CHA_D Q[63:48]14

B B

M_CHA_D Q0

M_CHA_D Q1

M_CHA_D Q2

M_CHA_D Q3

M_CHA_D Q4

M_CHA_D Q5

M_CHA_D Q6

M_CHA_D Q7

M_CHA_D Q8

M_CHA_D Q9

M_CHA_D Q10

M_CHA_D Q11

M_CHA_D Q12

M_CHA_D Q13

M_CHA_D Q14

M_CHA_D Q15

M_CHA_D Q16

M_CHA_D Q17

M_CHA_D Q18

M_CHA_D Q19

M_CHA_D Q20

M_CHA_D Q21

M_CHA_D Q22

M_CHA_D Q23

M_CHA_D Q24

M_CHA_D Q25

M_CHA_D Q26

M_CHA_D Q27

M_CHA_D Q28

M_CHA_D Q29

M_CHA_D Q30

M_CHA_D Q31

M_CHA_D Q32

M_CHA_D Q33

M_CHA_D Q34

M_CHA_D Q35

M_CHA_D Q36

M_CHA_D Q37

M_CHA_D Q38

M_CHA_D Q39

M_CHA_D Q40

M_CHA_D Q41

M_CHA_D Q42

M_CHA_D Q43

M_CHA_D Q44

M_CHA_D Q45

M_CHA_D Q46

M_CHA_D Q47

M_CHA_D Q48

M_CHA_D Q49

M_CHA_D Q50

M_CHA_D Q51

M_CHA_D Q52

M_CHA_D Q53

M_CHA_D Q54

M_CHA_D Q55

M_CHA_D Q56

M_CHA_D Q57

M_CHA_D Q58

M_CHA_D Q59

M_CHA_D Q60

M_CHA_D Q61

M_CHA_D Q62

M_CHA_D Q63

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

U1C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

2

<PART_S YM_NUM>

1.01FINAL

1.01FINAL

1.01FINAL

CPU(2)_DDR3L-RS

CPU(2)_DDR3L-RS

CPU(2)_DDR3L-RS

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IMPBW-CS

IMPBW-CS

IMPBW-CS

Engineer:

1

Stonko_Chen

Stonko_Chen

Stonko_Chen

6 57Tuesday, March 11, 2 014

6 57Tuesday, March 11, 2 014

6 57Tuesday, March 11, 2 014

Rev

Rev

Rev

A00

A00

A00

CL80647 01478404

I

A A

5

<PART_S YM_NUM>

4

3

CL80647 01478404

I

5

D D

to Vcore

C C

VIDALERT#5 9

VIDSCLK59

VIDSOUT59

chenge to EC pin

CPU_VR_ READY45

+1P05V +VCCST

1 2

HR32 0 OhmI

1 2

HR33 Do Not Stuff

NI

1 2

HR34 0 OhmI

+VCCST

12

HR22

75 OHM

I

HR24 43 OHMI

+1.05VS_ PWRGD_S13

1.29A

0.67A

4

1%

1 2

CPU_VR_ EN59

1 2

R60477 Do Not Stuff

+VCCIO_OU T

+VCCIO_OU T_XDP

NI

+VCCST

12

HR23

130 OHM

I

1%

+VCCIO_OU T

+VCCIOA_O UT

12

HR31

10KOhm

I

to Vcore

VCC_SEN SE59

GND

12

mx_c0402_ small

GND

1 2

HR21

HC3 Do Not Stuff

CPU_PW R_DEBUG13

I

HC8

0.1UF/16V

0Ohm

NI

12

HR27

HR28

HR29

+VCCST

12

GND

3

NOBOM

0Ohm

1 2

0Ohm

1 2

0Ohm

1 2

GND

HC5

22UF/6.3V

I

NOBOM

NOBOM

NOBOM

NOBOM

12

HC6

Do Not Stuff

NI

NOBOM

NOBOM

NOBOM

+VCORE

+VCCIO_OU T_R

H_CPU_S VIDALRT#

+1.05VS_ PWRGD_S_R

CPU_VR_ EN_R

CPU_VR_ READY_RRCPU_VR_ READY_R

HT9

HT10

HT11

HT12

+VCORE

+1P35V_ DUAL

1

RSVD_69

1

RSVD_70

1

RSVD_71

1

RSVD_72

U1L

L59

J58

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

F59

N58

AC58

E63

AB23

A59

E20

AD23

AA23

AE59

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

AD60

AD59

AA59

AE60

AC59

AG58

U59

V59

AC22

AE22

AE23

AB57

AD57

AG57

C24

C28

C32

CL80647 01478404

I

RSVD52

RSVD53

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VCC1

RSVD57

RSVD58

VCC_SENSE

RSVD59

VCCIO_OUT

VCOMP_OUT

RSVD60

RSVD61

RSVD62

VIDALERT#

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS2

PWR_DEBUG#

VSS1

RSVD_TP7

RSVD_TP8

IVR_ERROR

IST_TRIGGER

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD12

RSVD11

VCCST_1

VCCST_2

VCCST_3

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

2

HSW_ULT_DDR3L

HSW ULT POWER

<PART_S YM_NUM>

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

1

+VCORE

B B

+1P35V_ DUAL

12

12

A A

5

4

C1174

10UF/6.3V

X5R/+/-20%

C1180

2.2UF/6.3V

X5R/+/-20%

12

12

C1175

10UF/6.3V

X5R/+/-20%

C1181

2.2UF/6.3V

X5R/+/-20%

12

12

C1176

10UF/6.3V

X5R/+/-20%

C1182

2.2UF/6.3V

X5R/+/-20%

12

12

GND

C1177

10UF/6.3V

X5R/+/-20%

C1183

2.2UF/6.3V

X5R/+/-20%

3

12

C1178

10UF/6.3V

X5R/+/-20%

12

GND

C1179

10UF/6.3V

X5R/+/-20%

1.01FINAL

1.01FINAL

1.01FINAL

Title :

Title :

Title :

CPU(3)_HSW POWER

CPU(3)_HSW POWER

CPU(3)_HSW POWER

Stonko_Chen

Stonko_Chen

1

Stonko_Chen

7 57Tuesday, March 11, 2 014

7 57Tuesday, March 11, 2 014

7 57Tuesday, March 11, 2 014

Rev

Rev

Rev

A00

A00

A00

Engineer:

Engineer:

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

IMPBW-CS

IMPBW-CS

IMPBW-CS

Engineer:

5

4

3

2

1

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS17

VSS13

VSS14

VSS15

VSS16

VSS18

VSS19

VSS20

VSS22

VSS23

VSS24

VSS28

VSS25

VSS26

VSS27

VSS21

VSS29

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS40

VSS41

VSS38

VSS39

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

HSW_ULT_DDR3L

<PART_S YM_NUM>

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

AJ35

AJ39

AJ41

AJ43

AJ45

AJ47

AJ50

AJ52

AJ54

AJ56

AJ58

AJ60

AJ63

AK23

AK3

AK52

AL10

AL13

AL17

AL20

AL22

AL23

AL26

AL29

AL31

AL33

AL36

AL39

AL40

AL45

AL46

AL51

AL52

AL54

AL57

AL60

AL61

AM1

AM17

AM23

AM31

AM52

AN17

AN23

AN31

AN32

AN35

AN36

AN39

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN51

AN52

AN60

AN63

AN7

AP10

AP17

AP20

U1O

AP22

AP23

AP26

AP29

AP3

AP31

AP38

AP39

AP48

AP52

AP54

AP57

AR11

AR15

AR17

AR23

AR31

AR33

AR39

AR43

AR49

AR5

AR52

AT13

AT35

AT37

AT40

AT42

AT43

AT46

AT49

AT61

AT62

AT63

AU1

AU16

AU18

AU20

AU22

AU24

AU26

AU28

AU30

AU33

AU51

AU53

AU55

AU57

AU59

AV14

AV16

AV20

AV24

AV28

AV33

AV34

AV36

AV39

AV41

AV43

AV46

AV49

AV51

AV55

CL80647 01478404

I

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS153

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS30

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

HSW_ULT_DDR3L

<PART_S YM_NUM>

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS228

VSS223

VSS224

VSS225

VSS226

VSS227

VSS229

VSS230

VSS231

VSS232

VSS233

VSS235

VSS236

VSS237

VSS238

VSS240

VSS241

VSS242

VSS243

VSS244

VSS239

VSS245

VSS246

VSS247

VSS248

VSS234

VSS31

VSS322

VSS249

VSS250

VSS251

VSS258

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS259

VSS260

AV59

AV8

AW16

AW24

AW33

AW35

AW37

AW4

AW40

AW42

AW44

AW47

AW50

AW51

AW59

AW60

AY11

AY16

AY18

AY22

AY24

AY26

AY30

AY33

AY4

AY51

AY53

AY57

AY59

AY6

B20

B24

B26

B28

B32

B36

B4

B40

B44

B48

B52

B56

B60

C11

C14

C18

C20

C25

C27

C38

C39

C57

D12

D14

D18

D2

D21

D23

D25

D26

D27

D29

D30

D31

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS285

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS184

VSS329

VSS281

VSS282

VSS284

VSS286

VSS287

VSS288

VSS289

VSS283

VSS291

VSS292

VSS293

VSS294

VSS295

VSS296

VSS297

VSS298

VSS299

VSS290

VSS300

VSS301

HSW_ULT_DDR3L

<PART_S YM_NUM>

VSS302

VSS303

VSS304

VSS305

VSS306

VSS307

VSS308

VSS309

VSS311

VSS312

VSS313

VSS314

VSS315

VSS316

VSS317

VSS318

VSS319

VSS320

VSS321

VSS323

VSS324

VSS325

VSS310

VSS326

VSS327

VSS328

VSS330

VSS331

VSS332

VSS338

VSS333

VSS334

VSS335

VSS336

VSS341

VSS337

VSS339

VSS340

VSS342

VSS343

VSS344

VSS_SENSE

VSS345

H17

H57

J10

J22

J59

J63

K1

K12

L13

L15

L17

L18

L20

L58

L61

L7

M22

N10

N3

P59

P63

R10

R22

R8

T1

T58

U20

U22

U61

U9

V10

V3

V7

W20

W22

Y10

Y59

Y63

V58

AH46

V23

E62

AH16

U1P

D33

D34

D35

D37

D38

D39

D41

D42

D43

D45

D46

D47

D49

D5

D50

D51

D53

D54

D55

D57

D59

D62

D8

E11

E17

F20

F26

F30

F34

F38

F42

F46

F50

F54

F58

F61

G18

G22

G3

G5

G6

G8

H13

CL80647 01478404

GND GND

I

GND

VSS_SEN SE 59

to Vcore

U1N

D D

C C

B B

A11

A14

A18

A24

A28

A32

A36

A40

A44

A48

A52

A56

AA1

AA58

AB10

AB20

AB22

AB7

AC61

AD21

AD3

AD63

AE10

AE5

AE58

AF11

AF12

AF14

AF15

AF17

AF18

AG1

AG11

AG21

AG23

AG60

AG61

AG62

AG63

AH17

AH19

AH20

AH22

AH24

AH28

AH30

AH32

AH34

AH36

AH38

AH40

AH42

AH44

AH49

AH51

AH53

AH55

AH57

AJ13

AJ14

AJ23

AJ25

AJ27

AJ29

CL80647 01478404

I

GND GND GND GND

A A

1.01FINAL

1.01FINAL

1.01FINAL

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

IMPBW-CS

IMPBW-CS

IMPBW-CS

Engineer:

1

CPU(4)_GND

CPU(4)_GND

CPU(4)_GND

Stonko_Chen

Stonko_Chen

Stonko_Chen

8 57Tuesday, March 11, 2 014

8 57Tuesday, March 11, 2 014

8 57Tuesday, March 11, 2 014

Rev

Rev

Rev

A00

A00

A00

5

D D

4

CFG013

CFG113

CFG213

CFG313

CFG413

CFG513

CFG613

CFG713

CFG813

CFG913

CFG1013

CFG1113

CFG1213

CFG1313

CFG1413

CFG1513

CFG1613

CFG1713

CFG1813

CFG1913

3

U1S

2

1

HSW_ULT_DDR3L

1 2

1 2

1 2

1 2

1 2

1 2

GND

C C

CFG strapping information:

CFG[3:0]: Reserved configuration lane.

A test point may be placed on the board for these lanes.

The CFG signals have a default value of '1'

CFG[20:0] - INT. PU

GND

HR37Do Not Stuff NI

HR38Do Not Stuff NI

HR391KOhm I

HR40Do Not Stuff NI

HR41Do Not Stuff NI

HR42Do Not Stuff NI

CFG[4]: eDP enable

-1 = Disabled

-0 = Enabled

CFG[19:5]: Reserved configuration lanes.

A test point may be placed on the board for these lands.

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

HT14

HT15

HT16

HT20

HT22

CFG10

HT25

HT27

HT28

HT30

HT31

HT34

HT35

HT36

HT38

HT40

HT42

HT44

HT45

HT46

CFG0

CFG1

CFG4

CFG8

CFG9

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

HR44 49.9 OHMI

1 2

HR45 8.2KOHMI

GND

12

1%

1%

Follow Harris Beach

CFG strapping information:

CFG[0]: EAR-STALL/NOT STALL RESET SEQUENCE AFTER PCU PLL IS LOCKED

B B

-1 = (DEFAULT) NORMAL OPERATION; NO STALL

-0 = STALL

CFG[1]: PCH/ PCH LESS MODE SELECTION

-1 = (DEFAULT) NORMAL OPERATION

-0 = PCH-LESS MODE

CFG[8]: ALLOW THE USE OF NOA ON LOCKED UNITS

-1 = DISABLED(DEFAULT);

IN THIS CASE, NOA WILL BEDISABLED IN LOCKED UNITS

AND ENABLED IN UN-LOCKED UNITS

-0 = ENABLED;

NOA WILL BE AVAILABLE REGARDLESS OF THE LOCKING OF THE UNIT

CFG[9]: NO SVID PROTOCOL CAPABLE VR CONNECTED

-1 = VRS SUPPORTING SVID PROTOCOL ARE PRESENT

-0 = NO VR SUPPORTING SVID IS PRESENT.

THE CHIP WILL NOT GENERATE (OR RESPOND TO) SVID ACTIVITY

CFG[10]: SAFE MODE BOOT

-1 = POWER FEATURES ACTIVATED DURING RESET

A A

-0 = POWER FEATURES (ESPECIALLY CLOCK GATINE ARE NOT ACTIVATED

5

The CFG signals have a default value of '1'

4

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

HT57

HT61

HT62

HT65

HT67

DC_TEST _AY2_AW2

DC_TEST _AY3_AW3

1

HT48

NOBOM

HT50

NOBOM

U1R

1

1

1

1

1

RSVD31

RSVD33

RSVD34

RSVD35

RSVD36

AU44

AV44

AT2

D15

F22

H22

J21

RSVD40

RSVD41

RSVD42

RSVD43

RSVD37

RSVD38

RSVD39

CL80647 01478404

I

3

TP_DC_T EST_AY60

DC_TEST _AY61_AW61

DC_TEST _AY62_AW62

1

TP_DC_T EST_B2

DC_TEST _A3_B3

DC_TEST _A61_B61

DC_TEST _B62_B63

DC_TEST _C1_C2

HSW_ULT_DDR3L

AC60

AC62

AC63

AA63

AA60

Y62

Y61

Y60

V62

V61

V60

U60

T63

T62

T61

T60

AA62

U63

AA61

U62

V63

CFG_RCO MP

RSVD49

RSVD50

RSVD51

J20

RSVD52

H18

RSVD53

B12

TD_IREF

AY2

AY3

AY60

AY61

AY62

B61

B62

B63

<PART_S YM_NUM>

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[18]

CFG[17]

CFG[19]

CFG_RCOMP

A5

RSVD30

E1

RSVD46

D1

RSVD47

RSVD48

RSVD49

TD_IREF

CL80647 01478404

I

U1Q

DAISY_CHAIN_NCTF_AY2

DAISY_CHAIN_NCTF_AY3

DAISY_CHAIN_NCTF_AY60

DAISY_CHAIN_NCTF_AY61

DAISY_CHAIN_NCTF_AY62

B2

DAISY_CHAIN_NCTF_B2

B3

DAISY_CHAIN_NCTF_B3

DAISY_CHAIN_NCTF_B61

DAISY_CHAIN_NCTF_B62

DAISY_CHAIN_NCTF_B63

C1

DAISY_CHAIN_NCTF_C1

C2

DAISY_CHAIN_NCTF_C2

CL80647 01478404

I

Spare Pins

RSVD31

RSVD34

RSVD32

RSVD33

RSVD13

RSVD15

RSVD14

RSVD44

RSVD45

RSVD25

RSVD24

RESERVED

PROC_OPI_RCOMP

<PART_S YM_NUM>

Daisy Chain Non-Critical to Function:

These signals are for BGA solder joint reliability testing

and are non-critical to function.

HSW_ULT_DDR3L

N23

R23

T23

U10

AL1

AM11

AP7

AU10

AU15

AW14

AY14

2

<PART_S YM_NUM>

DC Test Pins

DAISY_CHAIN_NCTF_A3

DAISY_CHAIN_NCTF_A4

DAISY_CHAIN_NCTF_A60

DAISY_CHAIN_NCTF_A61

DAISY_CHAIN_NCTF_A62

DAISY_CHAIN_NCTF_AV1

DAISY_CHAIN_NCTF_AW1

DAISY_CHAIN_NCTF_AW2

DAISY_CHAIN_NCTF_AW3

DAISY_CHAIN_NCTF_AW61

DAISY_CHAIN_NCTF_AW62

DAISY_CHAIN_NCTF_AW63

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD44

RSVD45

RSVD46

RSVD47

RSVD48

1

HT55

1

HT56

1

HT58

1

HT60

1

HT63

1

HT66

1

HT68

1

HT70

1

HT71

1

HT72

1.01FINAL

1.01FINAL

1.01FINAL

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

RSVD_TP1

RSVD_TP2

RSVD_TP3

RSVD_TP4

RSVD3

RSVD_TP5

RSVD_TP6

RSVD_TP9

RSVD20

RSVD1

RSVD2

RSVD16

RSVD17

VSS3

VSS4

RSVD18

RSVD19

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

AV63

RSVD_TP 5

AU63

RSVD_TP 11

C63

RSVD_TP 10

C62

RSVD_TP 9

B43

RSVD54

A51

RSVD_TP 55

B51

RSVD_TP 66

L60

RSVD_TP 8

N60

RSVD55

W23

RSVD56

Y22

RSVD57

AY15

PROC_OP I_COMP

AV62

RSVD58

D58

RSVD59

P22

N21

P20

RSVD60

R20

RSVD61

A3

DC_TEST _A3_B3

A4

TP_DC_T EST_A4

A60

TP_DC_T EST_A60

A61

DC_TEST _A61_B61

A62

TP_DC_T EST_A62

AV1

TP_DC_T EST_AV1

AW1

TP_DC_T EST_AW1

AW2

DC_TEST _AY2_AW2

AW3

DC_TEST _AY3_AW3

AW61

DC_TEST _AY61_AW61

AW62

DC_TEST _AY62_AW62

AW63

TP_DC_T EST_AW63

Engineer:

Engineer:

Engineer:

IMPBW-CS

IMPBW-CS

IMPBW-CS

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Title :

Title :

Title :

1

HT13

NOBOM

HT17

NOBOM

HT18

NOBOM

HT19

NOBOM

HT21

NOBOM

HT23

NOBOM

HT24

NOBOM

HT26

NOBOM

HT29

NOBOM

HT32

NOBOM

HT33

NOBOM

12

NOBOM

NOBOM

NOBOM

NOBOM

GND

HT47

NOBOM

HT49

NOBOM

HT51

NOBOM

HT52

NOBOM

HT53

NOBOM

HT54

NOBOM

CPU(7)_RESERVED

CPU(7)_RESERVED

CPU(7)_RESERVED

Stonko_Chen

Stonko_Chen

Stonko_Chen

9 57Tuesday, March 11, 2 014

9 57Tuesday, March 11, 2 014

9 57Tuesday, March 11, 2 014

GND

HT37

HT39

HT41

HT43

1

1

1

1

1

1

HR43

49.9 OHM

I

1%

Rev

Rev

Rev

A00

A00

A00

5

4

3

2

1

CPU XDP connector

Intel recommend (R1.0 on 9/10)

XDP pin 40, 42/HOOK4, 5 should be left Open,

unstuff R1006, R1007.

D D

+1.05VS_ PWRGD_S +1.05VS_ PWRGD_XDP CLK_XDP _P_R

GR12 Do Not Stuff

PWR_ SW#45

C C

XDP

GR7 Do Not Stuff

12

GR10 Do Not Stuff

GR13 Do Not Stuff

XDP

XDP

XDP

SYS_PW ROK21,45

SMB_DAT _S15,26,29,3 0,44

SMB_CLK _S15,26,2 9,30,44

XDP_TCK8,42

PCH_JTA G_TCK19

PCH_JTA GX19

+VCCIO_OU T_XDP

+3P3VSB

12

GR4

Do Not Stuff

NI

12

12

12

GR17 Do Not Stuff

GR18 Do Not Stuff

GR19 Do Not Stuff

XDP_PRE Q#8

XDP_PRD Y#8

CFG012

CFG112

CFG212

CFG312

XDP_BPM 08

XDP_BPM 18

12

NI

CFG412

GC1

CFG512

Do Not Stuff

CFG612

GND

J1d

J1s

J2d

CFG712

PWR_ DEBUG_R XDP_RST #_R

12

12

12

XDP

NI

XDP

XDP_TCK 1

NI

XDP1

1

GND1

3

OBSFN_A0

5

OBSFN_A1

7

GND3

9

OBSDATA_A0

11

OBSDATA_A1

13

GND5

15

OBSDATA_A2

17

OBSDATA_A3

19

GND7

21

OBSFN_B0

23

OBSFN_B1

25

GND9

27

OBSDATA_B0

29

OBSDATA_B1

31

GND11

33

OBSDATA_B2

35

OBSDATA_B3

37

GND13

39

HOOK0

41

HOOK1

43

VCC_OBS_AB

45

HOOK2

47

HOOK3

49

GND15

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND17

61

NP_NC1

Do Not Stuff

mx_sconn60_epg082001

GND

XDP

GR22 Do Not Stuff

GR23 Do Not Stuff

J2s

NI

ITPCLK#/HOOK5

12

12

GND2

OBSFN_C0

OBSFN_C1

GND4

OBSDATA_C0

OBSDATA_C1

GND6

OBSDATA_C2

OBSDATA_C3

GND8

OBSFN_D0

OBSFN_D1

GND10

OBSDATA_D0

OBSDATA_D1

GND12

OBSDATA_D2

OBSDATA_D3

GND14

ITPCLK/HOOK4

VCC_OBS_CD

HOOK6/RESET#

HOOK7/DBR#

GND16

TDO

TRSTn

TMS

GND18

NP_NC2

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

TDI

58

60

62

CLK_XDP _N_RPM_PW RBTN#_XDP

XDP_DBR ESET#_R

XDP_TDO _BUF

CFG3_R

GND

CFG17 12

CFG16 12

CFG8 12

CFG9 12

CFG10 12

CFG11 12

CFG19 12

CFG18 12

CFG12 12

CFG13 12

CFG14 12

CFG15 12

+VCCIO_OU T_XDP +1P05V +3P3V

GR20 Do Not Stuff

XDP

12

12

12

R7

GR5

Do Not Stuff

NI

12

GND

GR21 Do Not Stuff

XDP_TDI_B UF

GR6

Do Not Stuff

NI

12

XDP

XDP

XDP

XDP

XDP

J3d

12

12

12

12

12

GU1A

1

2

Do Not Stuff

GR8 Do Not Stuff

GR11 Do Not Stuff

GR14 Do Not Stuff

GR15 Do Not Stuff

GR16 Do Not Stuff

GC2

0.01UF/25 V

I

NI

J3sJ4d

CK_100M _CPUXDP 20

CK_100M _CPUXDP# 2 0

PLT_RST # 21,29,3 9,45,47,50

PM_SYSRST # 21

PCH_JTA G_TDO 19

PCH_JTA G_TDI 19

PCH_JTA G_TMS 19

+3P3V

147

XDP

VCC

3

SW

GND

S3

12

GND

I

GC3

0.1UF/6.3V

XDP_TDI 8

+VCCST

12

GR24

Do Not Stuff

+3P3V

NI

12

HR46

Do Not Stuff

NI

PWR_ DEBUG

12

GND

GR26

Do Not Stuff

NI

B B

+1P05V_ PWRGD55,63

A A

5

GU2

1

NC

A

2

3 4

GND

Do Not Stuff

GND

GR27 0 Ohm

HU4

1

NC

A

2

3 4

GND

SN74AUP 1G07DCKR

GND

NI

VCC

Y

12

I

I

VCC

Y

+3P3V

+VCCST

12

NI

12

GC4

+3P3V

GND

GND

12

I

HC7

0.1UF/6.3V

Do Not Stuff

5

5

4

+VCCST

12

GR25

150 Ohm

I

1%

HR47

10KOhm

I

CPU_PW R_DEBUG 10

+1.05VS_ PWRGD_S 10

3

2

XDP_TRS T#_BUF

+1.05VS_ PWRGD

1.01FINAL

1.01FINAL

1.01FINAL

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

GND

147

GU1B

VCC

4

5

SW

GND

Do Not Stuff

GND

147

GU1C

VCC

10

9

SW

GND

Do Not Stuff

GND

147

GU1D

VCC

13

12

SW

GND

Do Not Stuff

GND

IMPBW-CS

IMPBW-CS

IMPBW-CS

S1

XDP

6

XDP

S2

8

XDP

S4

11

74CBTLV3126

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

XDP_TRS T# 8,19

XDP_TMS 8,42

XDP_TDO 8

CPU(6)_XDP

CPU(6)_XDP

CPU(6)_XDP

Stonko_Chen

Stonko_Chen

Stonko_Chen

10 57Tuesday, March 11, 2014

10 57Tuesday, March 11, 2014

10 57Tuesday, March 11, 2014

Rev

Rev

Rev

A00

A00

A00

5

M_CHA_D Q[15:0]9 M_CHA_D Q[31:16]9

D D

M_CHA_M AA[0..14]9,14

M_CHA_B A09,14

M_CHA_B A19,14

M_CHA_B A29,14

M_CHA_D QS19

M_CHA_D QS1#9

M_CHA_D QS09

C C

B B

A A

M_CHA_D QS0#9

M_CHA_R AS#9,14

M_CHA_C AS#9,14

GND

M_CHA_W E#9,14

M_CHA_C S#09 ,14

M_CHA_C KE09,14

M_CHA_O DT014

DDR3_DR AMRST#14,15 DDR3_DR AMRST#14,15

M_CHA_C LK09 ,14

M_CHA_C LK0#9,14

M_CHA_M AA[0..14]9,14 M_CHA_M AA[0..14]9,14

M_CHA_B A09,14

M_CHA_B A19,14

M_CHA_B A29,14

M_CHA_D QS59

M_CHA_D QS5#9

M_CHA_D QS49

M_CHA_D QS4#9

M_CHA_R AS#9,14

M_CHA_C AS#9,14

GND

M_CHA_W E#9,14

M_CHA_C S#09 ,14

M_CHA_C KE09,14

M_CHA_O DT014

DDR3_DR AMRST#14,15

M_CHA_C LK09 ,14

M_CHA_C LK0#9,14

M_CHA_D Q7

M_CHA_D Q3

M_CHA_D Q4

M_CHA_D Q2

M_CHA_D Q0

M_CHA_D Q5

M_CHA_D Q1

M_CHA_D Q6

M_CHA_D Q10

M_CHA_D Q12

M_CHA_D Q14

M_CHA_D Q13

M_CHA_D Q11

M_CHA_D Q9

M_CHA_D Q15

M_CHA_D Q8

M_CHA_M AA0

M_CHA_M AA1

M_CHA_M AA2

M_CHA_M AA3

M_CHA_M AA4

M_CHA_M AA5

M_CHA_M AA6

M_CHA_M AA7

M_CHA_M AA8

M_CHA_M AA9

M_CHA_M AA10

M_CHA_M AA11

M_CHA_M AA12

M_CHA_M AA13

M_CHA_M AA14

M_CHA_D Q39

M_CHA_D Q35

M_CHA_D Q32

M_CHA_D Q34

M_CHA_D Q37

M_CHA_D Q38

M_CHA_D Q33

M_CHA_D Q36

M_CHA_D Q43

M_CHA_D Q41

M_CHA_D Q42

M_CHA_D Q44

M_CHA_D Q46

M_CHA_D Q40

M_CHA_D Q47

M_CHA_D Q45

M_CHA_M AA0

M_CHA_M AA1

M_CHA_M AA2

M_CHA_M AA3

M_CHA_M AA4

M_CHA_M AA5

M_CHA_M AA6

M_CHA_M AA7

M_CHA_M AA8

M_CHA_M AA9

M_CHA_M AA10

M_CHA_M AA11

M_CHA_M AA12

M_CHA_M AA13

M_CHA_M AA14

5

U2

E3

DQL0

F7

DQL1

F2

DQL2

F8

DQL3

H3

DQL4

H8

DQL5

G2

DQL6

H7

DQL7

D7

DQU0

C3

DQU1

C8

DQU2

C2

DQU3

A7

DQU4

A2

DQU5

B8

DQU6

A3

DQU7

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC#

T3

A13

T7

A14

M2

BA0

N8

BA1

M3

BA2

C7

DQSU

B7

DQSU#

F3

DQSL

G3

DQSL#

D3

DMU

E7

DML

J3

RAS#

K3

CAS#

L3

WE#

L2

CS0#

K9

CKE0

K1

ODT0

T2

RESET#

J7

CK

K7

CK#

K4B8G16 46Q-MYK0

U4

E3

DQL0

F7

DQL1

F2

DQL2

F8

DQL3

H3

DQL4

H8

DQL5

G2

DQL6

H7

DQL7

D7

DQU0

C3

DQU1

C8

DQU2

C2

DQU3

A7

DQU4

A2

DQU5

B8

DQU6

A3

DQU7

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC#

T3

A13

T7

A14

M2

BA0

N8

BA1

M3

BA2

C7

DQSU

B7

DQSU#

F3

DQSL

G3

DQSL#

D3

DMU

E7

DML

J3

RAS#

K3

CAS#

L3

WE#

L2

CS0#

K9

CKE0

K1

ODT0

T2

RESET#

J7

CK

K7

CK#

K4B8G16 46Q-MYK0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

ODT1

CKE1

CS1#

ZQ1

ZQ0

VREFDQ

VREFCA

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

ODT1

CKE1

CS1#

ZQ1

ZQ0

VREFDQ

VREFCA

A1

C1

F1

D2

H2

A8

C9

E9

H9

N1

R1

B2

K2

G7

K8

D9

N9

R9

B1

D1

G1

E2

D8

E8

B9

F9

G9

E1

M1

P1

T1

J2

B3

G8

J8

A9

M9

P9

T9

M7

NC

J1

J9

L1

L9

L8

H1

M8

A1

C1

F1

D2

H2

A8

C9

E9

H9

N1

R1

B2

K2

G7

K8

D9

N9

R9

B1

D1

G1

E2

D8

E8

B9

F9

G9

E1

M1

P1

T1

J2

B3

G8

J8

A9

M9

P9

T9

M7

NC

J1

J9

L1

L9

L8

H1

M8

4

+1P35V_ DUAL

M_CHA_M AA[0..14]9,14

M_CHA_B A09,14

M_CHA_B A19,14

M_CHA_B A29,14

M_CHA_D QS39

M_CHA_D QS3#9

M_CHA_D QS29

M_CHA_D QS2#9

GND

M_CHA_M AA15 9,14

M_CHA_O DT0 14

M_CHA_C KE1 9,14

M_CHA_C S#1 9,14

DQA_ZQ5

DQA_ZQ1

+V_VREF _DQ_DIMM0

+V_VREF _CA_DIMM

+1P35V_ DUAL

GND

M_CHA_M AA15 9,14

M_CHA_O DT0 14

M_CHA_C KE1 9,14

M_CHA_C S#1 9,14

DQA_ZQ7 DQA_ZQ8

DQA_ZQ3 DQA_ZQ4

+V_VREF _DQ_DIMM0

+V_VREF _CA_DIMM

4

GND

GND

M_CHA_D Q[63:48]9M_CHA_D Q[47:32]9

M_CHA_R AS#9,14

M_CHA_C AS#9,14

M_CHA_W E#9,14

M_CHA_C S#09 ,14

M_CHA_C KE09,14

M_CHA_O DT014

M_CHA_C LK09 ,14

M_CHA_C LK0#9,14

M_CHA_B A09,14

M_CHA_B A19,14

M_CHA_B A29,14

M_CHA_D QS69

M_CHA_D QS6#9

M_CHA_D QS79

M_CHA_D QS7#9

M_CHA_R AS#9,14

M_CHA_C AS#9,14

M_CHA_W E#9,14

M_CHA_C S#09 ,14

M_CHA_C KE09,14

M_CHA_O DT014

DDR3_DR AMRST#14,15

M_CHA_C LK09 ,14

M_CHA_C LK0#9,14

3

M_CHA_D Q16

M_CHA_D Q18

M_CHA_D Q20

M_CHA_D Q19

M_CHA_D Q17

M_CHA_D Q23

M_CHA_D Q21

M_CHA_D Q22

M_CHA_D Q30

M_CHA_D Q29

M_CHA_D Q31

M_CHA_D Q26

M_CHA_D Q24

M_CHA_D Q27

M_CHA_D Q25

M_CHA_D Q28

M_CHA_M AA0

M_CHA_M AA1

M_CHA_M AA2

M_CHA_M AA3

M_CHA_M AA4

M_CHA_M AA5

M_CHA_M AA6

M_CHA_M AA7

M_CHA_M AA8

M_CHA_M AA9

M_CHA_M AA10

M_CHA_M AA11

M_CHA_M AA12

M_CHA_M AA13

M_CHA_M AA14

M_CHA_D Q58

M_CHA_D Q61

M_CHA_D Q59

M_CHA_D Q57

M_CHA_D Q62

M_CHA_D Q56

M_CHA_D Q63

M_CHA_D Q60

M_CHA_D Q55

M_CHA_D Q50

M_CHA_D Q49

M_CHA_D Q53

M_CHA_D Q54

M_CHA_D Q51

M_CHA_D Q48

M_CHA_D Q52

M_CHA_M AA0

M_CHA_M AA1

M_CHA_M AA2

M_CHA_M AA3

M_CHA_M AA4

M_CHA_M AA5

M_CHA_M AA6

M_CHA_M AA7

M_CHA_M AA8

M_CHA_M AA9

M_CHA_M AA10

M_CHA_M AA11

M_CHA_M AA12

M_CHA_M AA13

M_CHA_M AA14

3

U3

E3

DQL0

F7

DQL1

F2

DQL2

F8

DQL3

H3

DQL4

H8

DQL5

G2

DQL6

H7

DQL7

D7

DQU0

C3

DQU1

C8

DQU2

C2

DQU3

A7

DQU4

A2

DQU5

B8

DQU6

A3

DQU7

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC#

T3

A13

T7

A14

M2

BA0

N8

BA1

M3

BA2

C7

DQSU

B7

DQSU#

F3

DQSL

G3

DQSL#

D3

DMU

E7

DML

J3

RAS#

K3

CAS#

L3

WE#

L2

CS0#

K9

CKE0

K1

ODT0

T2

RESET#

J7

CK

K7

CK#

K4B8G16 46Q-MYK0

U5

E3

DQL0

F7

DQL1

F2

DQL2

F8

DQL3

H3

DQL4

H8

DQL5

G2

DQL6

H7

DQL7

D7

DQU0

C3

DQU1

C8

DQU2

C2

DQU3

A7

DQU4

A2

DQU5

B8

DQU6

A3

DQU7

N3

A0

P7

A1

P3

A2

N2

A3

P8

A4

P2

A5

R8

A6

R2

A7

T8

A8

R3

A9

L7

A10/AP

R7

A11

N7

A12/BC#

T3

A13

T7

A14

M2

BA0

N8

BA1

M3

BA2

C7

DQSU

B7

DQSU#

F3

DQSL

G3

DQSL#

D3

DMU

E7

DML

J3

RAS#

K3

CAS#

L3

WE#

L2

CS0#

K9

CKE0

K1

ODT0

T2

RESET#

J7

CK

K7

CK#

K4B8G16 46Q-MYK0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

ODT1

CKE1

CS1#

ZQ1

ZQ0

VREFDQ

VREFCA

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

ODT1

CKE1

CS1#

ZQ1

ZQ0

VREFDQ

VREFCA

A1

C1

F1

D2

H2

A8

C9

E9

H9

N1

R1

B2

K2

G7

K8

D9

N9

R9

B1

D1

G1

E2

D8

E8

B9

F9

G9

E1

M1

P1

T1

J2

B3

G8

J8

A9

M9

P9

T9

GND

M7

NC

J1

J9

L1

L9

DQA_ZQ6

L8

DQA_ZQ2

H1

M8

A1

C1

F1

D2

H2

A8

C9

E9

H9

N1

R1

B2

K2

G7

K8

D9

N9

R9

B1

D1

G1

E2

D8

E8

B9

F9

G9

E1

M1

P1

T1

J2

B3

G8

J8

A9

M9

P9

T9

GND

M7

NC

J1

J9

L1

L9

L8

H1

M8

2

+1P35V_ DUAL

M_CHA_M AA15 9,14

M_CHA_O DT0 14

M_CHA_C KE1 9,14

M_CHA_C S#1 9,14

+V_VREF _DQ_DIMM0

+V_VREF _CA_DIMM

+1P35V_ DUAL

Part Number

M_CHA_M AA15 9,14

M_CHA_O DT0 14

M_CHA_C KE1 9,14

M_CHA_C S#1 9,14

+V_VREF _DQ_DIMM0

+V_VREF _CA_DIMM

2

SM_DRAM RST#8

+1P35V_ DUAL

12

+

GND

1

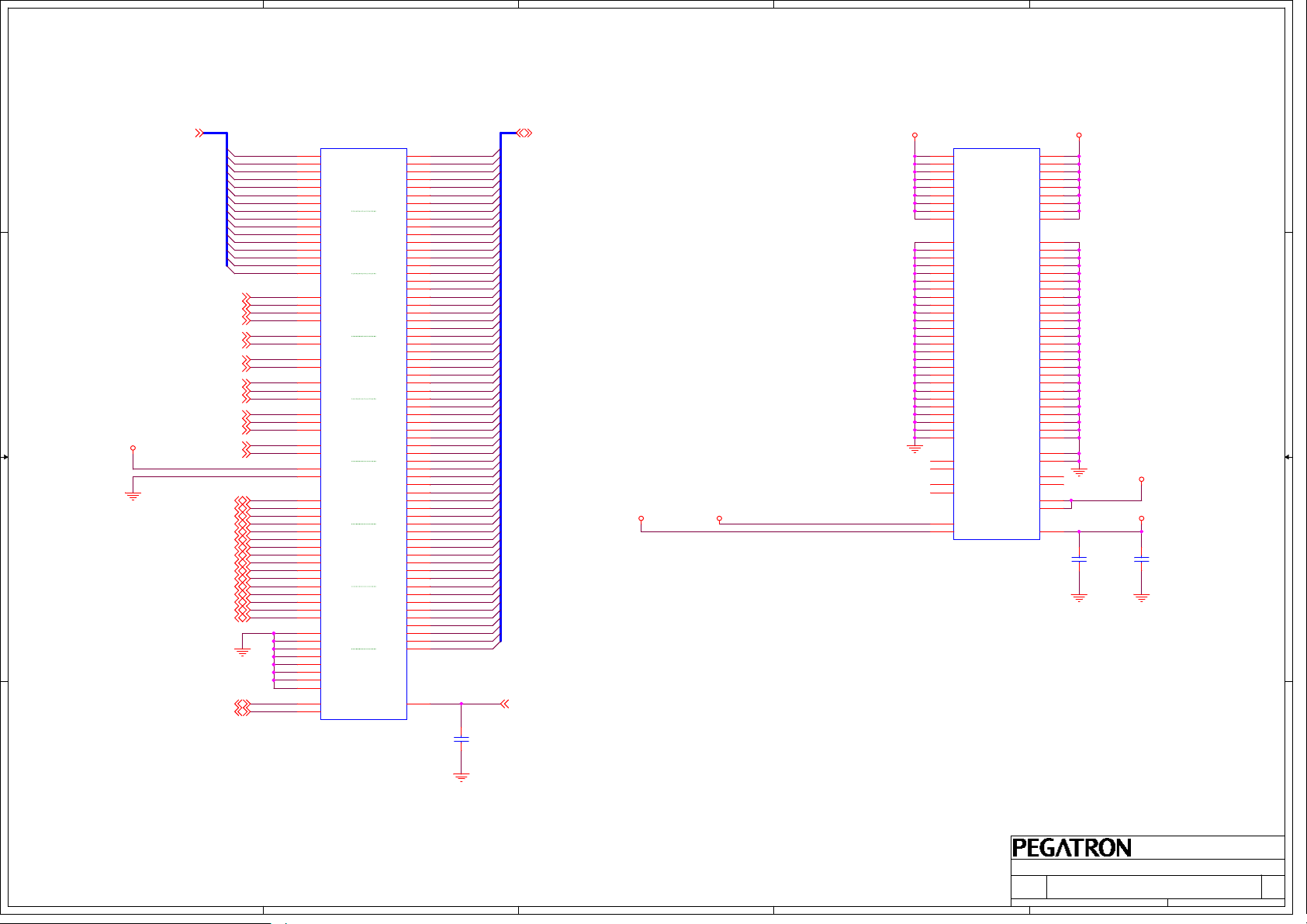

Memory Down CH A

+VTT_DD R

M_CHA_B A0

M_CHA_B A1

M_CHA_B A2

M_CHA_C S#0

M_CHA_C KE0

M_CHA_R AS#

M_CHA_C AS#

M_CHA_W E#

M_CHA_M AA0

M_CHA_M AA1

M_CHA_M AA2

M_CHA_M AA3

M_CHA_M AA4

M_CHA_M AA5

M_CHA_M AA6

M_CHA_M AA7

M_CHA_M AA8

M_CHA_M AA9

M_CHA_M AA10

M_CHA_M AA11

M_CHA_M AA12

M_CHA_M AA13

M_CHA_M AA14

M_CHA_MAA15

M_CHA_C KE1

M_CHA_C S#1

M_CHA_C LK0

M_CHA_C LK0#

M_CHA_O DT0

DQA_ZQ1

DQA_ZQ2

DQA_ZQ3

DQA_ZQ4

DQA_ZQ5

DQA_ZQ6

DQA_ZQ7

DQA_ZQ8

SAMSUNG Hynix

03X1500580DE 03X150053000

1 2

R39

CE1

Do Not Stuff

1.01FINAL

1.01FINAL

1.01FINAL

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

PEGATRO N COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

R1 34 .8 OHM1%

R2 34 .8 OHM1%

R3 34 .8 OHM1%

R4 34 .8 OHM1%

R5 34 .8 OHM1%

R6 34 .8 OHM1%

R7 34 .8 OHM1%

R8 34 .8 OHM1%

R9 34 .8 OHM1%

R10 34.8 OHM1%

R11 34.8 OHM1%

R12 34.8 OHM1%

R13 34.8 OHM1%

R14 34.8 OHM1%

R15 34.8 OHM1%

R16 34.8 OHM1%

R17 34.8 OHM1%

R18 34.8 OHM1%

R19 34.8 OHM1%

R20 34.8 OHM1%

R21 34.8 OHM1%

R22 34.8 OHM1%

R23 34.8 OHM1%

R24 34.8 OHM1%

R25 34.8 OHM1%

R26 34.8 OHM1%

R27 26.1OHM1%

R28 26.1OHM1%

R29 30Ohm1%

R30 240Ohm1%

R31 240Ohm1%

R32 240Ohm1%

R33 240Ohm1%

R34 240Ohm1%

R35 240Ohm1%

R36 240Ohm1%

R37 240Ohm1%

+1P35V_ DUAL

0Ohm

NOBOM

IMPBW-CS

IMPBW-CS

IMPBW-CS

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

R38

470 OHM

1%

12

C1

Do Not Stuff

X7R 10%

NI

GND

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

DDR3_DR AMRST# 14,15

MemoryDown

MemoryDown

MemoryDown

Stonko_Chen

Stonko_Chen

Stonko_Chen

1

11 57Tuesday, March 11, 2014

11 57Tuesday, March 11, 2014

11 57Tuesday, March 11, 2014

+1P35V_ DUAL

GND

Rev

Rev

Rev

A00

A00

A00

5

4

Memory SO-Dimm CH B

3

2

1

D D

C C

B B

M_CHB_M AA[0..15]9

+3P3V

GND

M_CHB_M AA0

M_CHB_M AA1

M_CHB_M AA2

M_CHB_M AA3

M_CHB_M AA4

M_CHB_M AA5

M_CHB_M AA6

M_CHB_M AA7

M_CHB_M AA8

M_CHB_M AA9

M_CHB_M AA10

M_CHB_M AA11

M_CHB_M AA12

M_CHB_M AA13

M_CHB_M AA14

M_CHB_M AA15

M_CHB_C LK19

M_CHB_C LK1#9

M_CHB_C LK09

M_CHB_C LK0#9

M_CHB_C S#19

M_CHB_C S#09

M_CHB_O DT18

M_CHB_O DT08

M_CHB_W E#9

M_CHB_R AS#9

M_CHB_C AS#9

M_CHB_B A29

M_CHB_B A19

M_CHB_B A09

M_CHB_C KE19

M_CHB_C KE09

M_CHB_D QS79

M_CHB_D QS7#9

M_CHB_D QS69

M_CHB_D QS6#9

M_CHB_D QS59

M_CHB_D QS5#9

M_CHB_D QS49

M_CHB_D QS4#9

M_CHB_D QS39

M_CHB_D QS3#9

M_CHB_D QS29

M_CHB_D QS2#9

M_CHB_D QS19

M_CHB_D QS1#9

M_CHB_D QS09

M_CHB_D QS0#9

GND

SMB_CLK _S13,26,2 9,30,44

SMB_DAT _S13,26,29,3 0,44

12X021893000

DIMM1A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

102

CK1

104

CK1#

101

CK0

103

CK0#

121

S1#

114

S0#

120

ODT1

116

ODT0

113

WE#

110

RAS#

115

CAS#

79

BA2

108

BA1

109

BA0

74

CKE1

73

CKE0

201

SA1

197

SA0

188

DQS7

186

DQS#7

171

DQS6

169

DQS#6

154

DQS5

152

DQS#5

137

DQS4

135

DQS#4

64

DQS3

62

DQS#3

47

DQS2

45

DQS#2

29

DQS1

27

DQS#1

12

DQS0

10

DQS#0

187

DM7

170

DM6

153

DM5

136

DM4

63

DM3

46

DM2

28

DM1

11

DM0

202

SCL

200

SDA

DDR3_DIMM _204P

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

0

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

1

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

2

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

3

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

4

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

5

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

6

DQ54