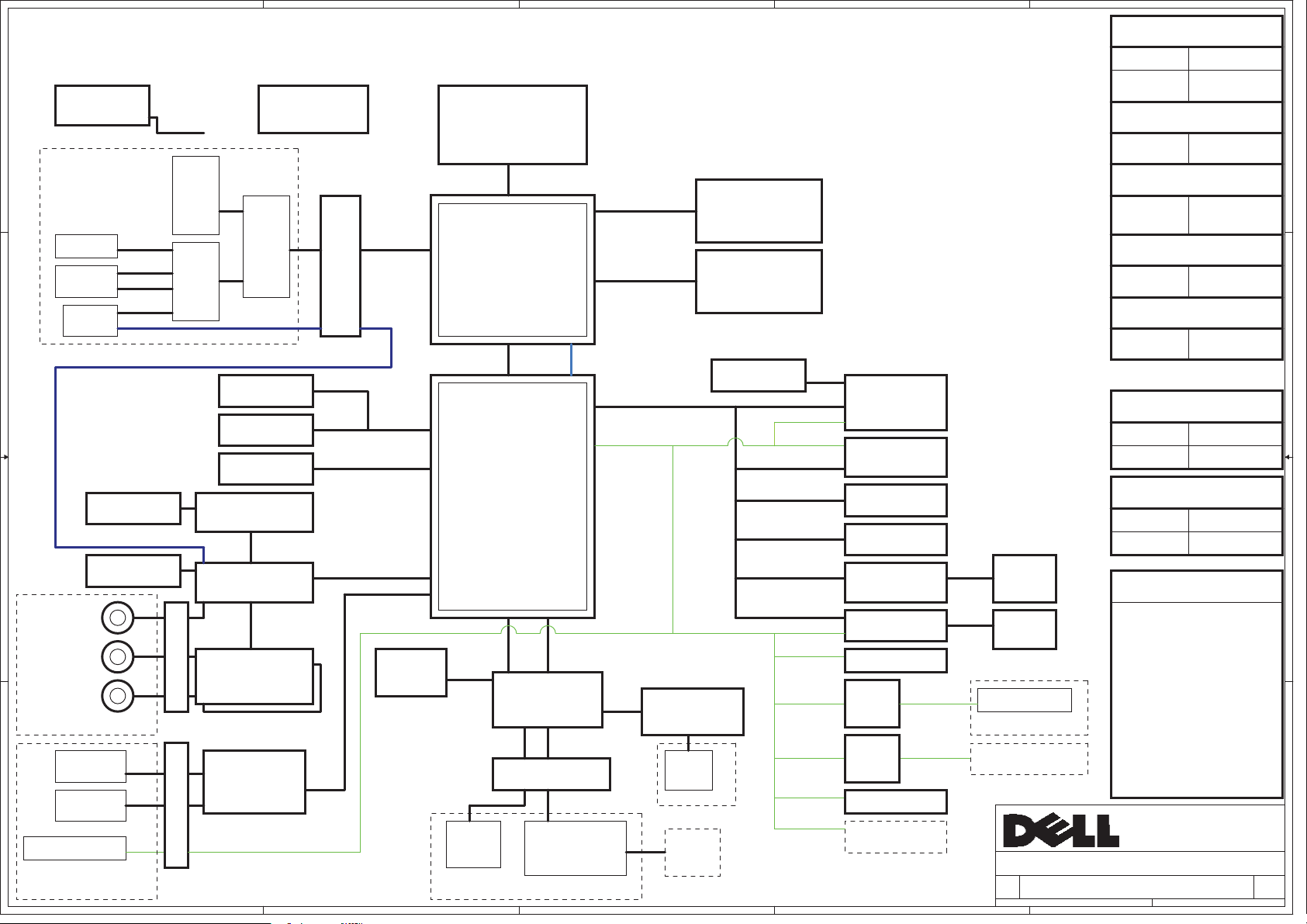

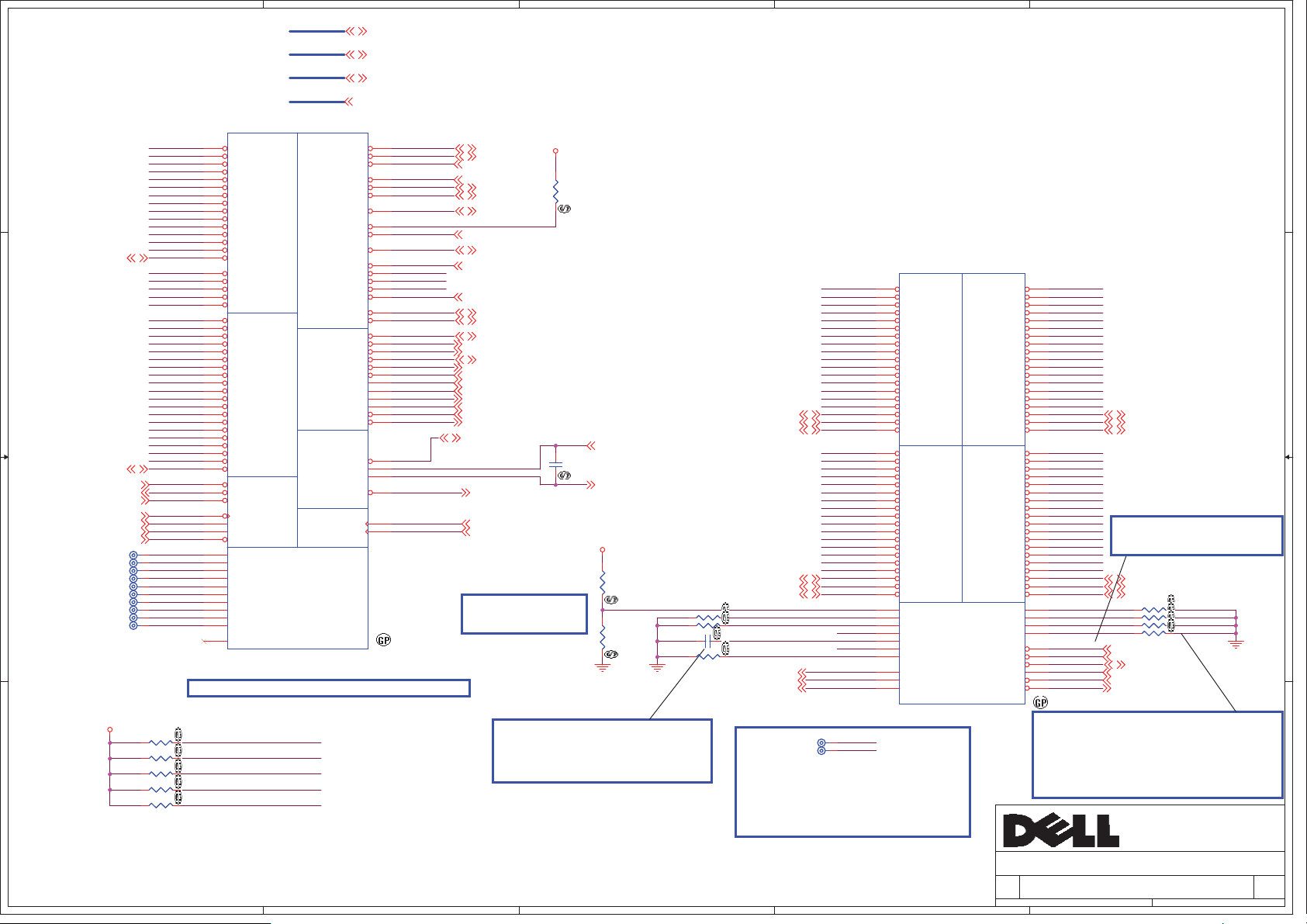

Dell XPS 1730 Schematics

A

Thermal Sensor

4 4

EMC4001

20

SMBus

Clock Generator

CY28547LFXC

SLi Graphic Card

GPU

LCD

DVI Port

TV-Out

3 3

LVDS

DVI-Out

RGB CRT

S-Video

SPDIF

GPU

Bridge

CONN.

Graphic

15

SPDIF

SATA (P0)

21

SATA (P2)

21

21

25

INT. Speaker

5W x 2

25

SATA HDD

SATA HDD

ODD Bay

Speaker AMP.

MAX9714

SPDIF

MIC IN

INT. Digital

Array MIC

24

2 2

LINE OUT / HP2

LINE OUT / HP1

Azalia CODEC

STAC 9228

Headphone AMP.

MAX4411 x 2

W to B CONN.

26

24

26

Audio Jack Board

7 in1

CONN

1 1

1394

CONN

USB CONN.x1

7 in1

1394

Ricoh R5C833

7 in 1 card reader

1394

B to B CONN.

USB2.0 (P0)

23

22

IO Board

A

B

C

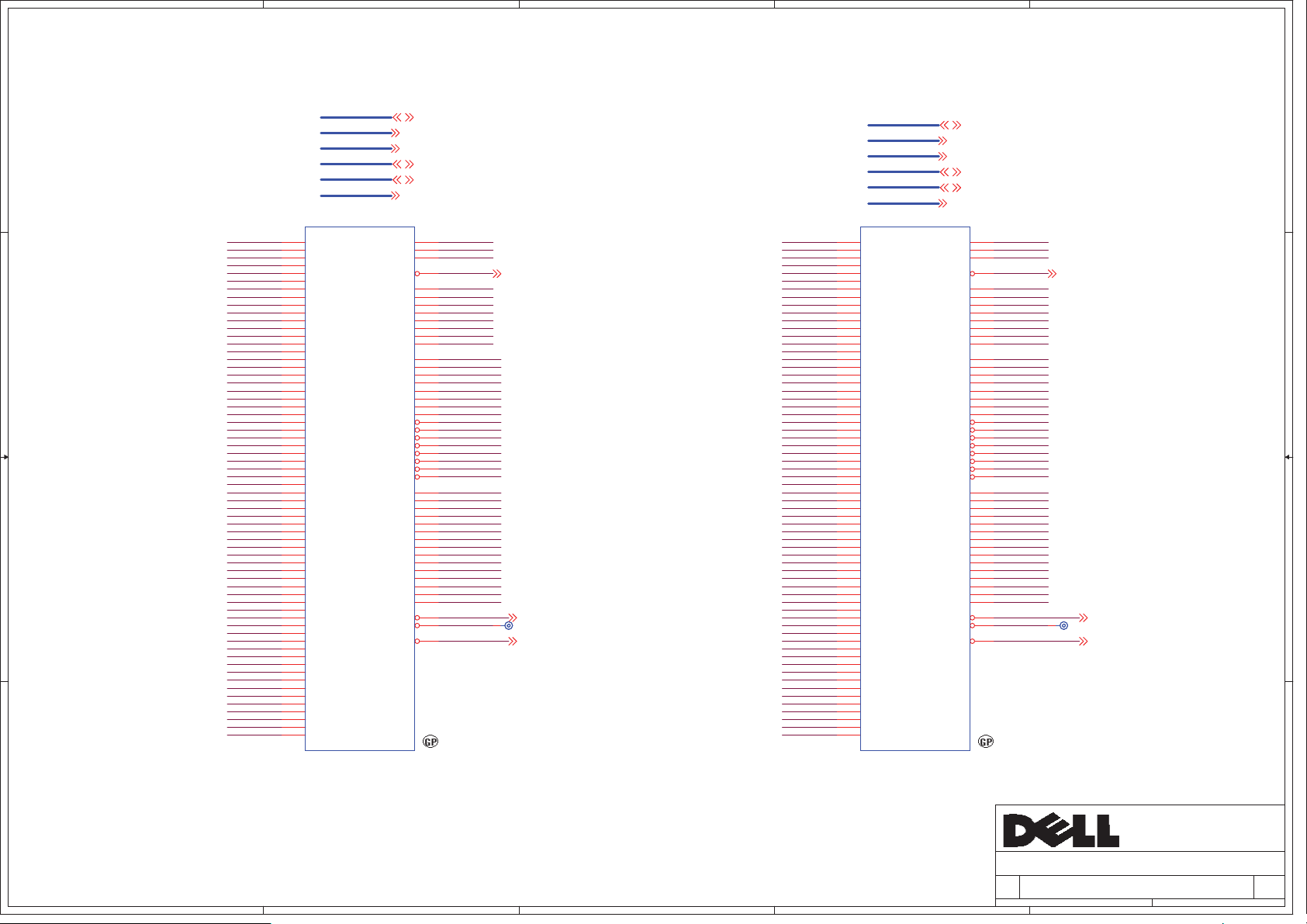

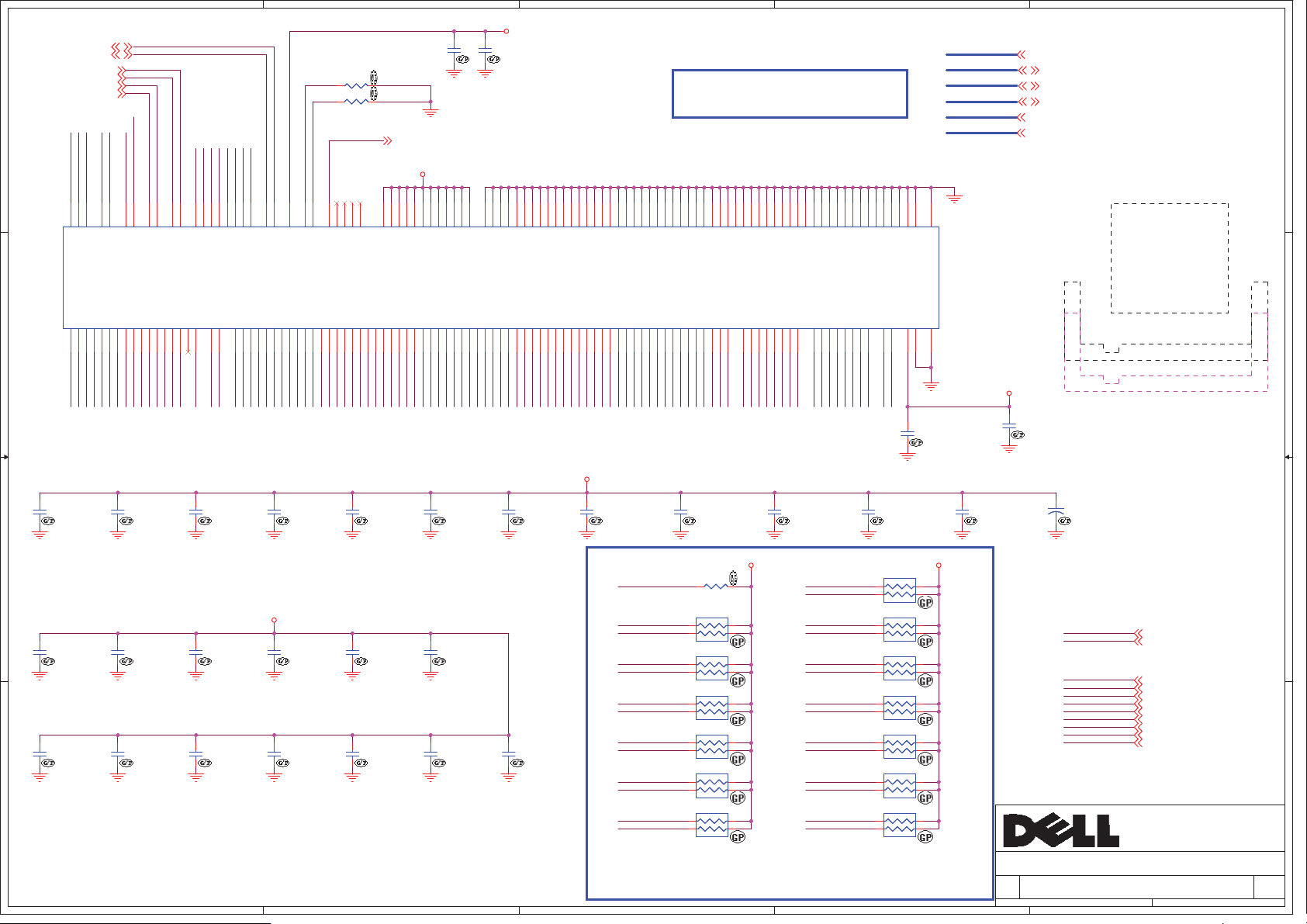

Siberia Block Diagram

Intel Mobile CPU

4

PCI-e x16

SATA (2)

PATA IDE

AZALIA

PCI BUS

BIOS

SPI FLASH

16Mb

B

Merom 4M

FSB:667/ 800 Mhz

FSB 667/800MHzHOST BUS

Crestline-PM

AGTL+ CPU I/F

DDR Memory I/F

EXTERNAL GRAHPICS

7,8,9,10,11,12

DMI x4 C-LINK0

Intel

ICH8-M

Enhanced

USB 2.0/1.1 ports (10)

PCI Express ports (6)

High Definition Audio

ATA 66/ 100

SATA (3)

LPC I/F

SPI

ACPI 1.1

PCI/PCI BRIDGE

SPI

36

Touch

Pad

Touch Pad Module

16,17,18,19

SPI

LPC

EC

SMSC MEC5025

PS/2

BC

Touch Pad CONN.

PS/2

BC

KBC

SMSC ECE1077

5,6

DDRII 533/667MHz

DDRII 533/667MHz

PCI Express (6)

USB2.0 (10)

SIO Expander

BC

33

35

http://hobi-elektronika.net

SMSC ECE5021

C

D

Project code:91.4Q601.001

PCB P/N :48.4Q613.011

REVISION :06248-1

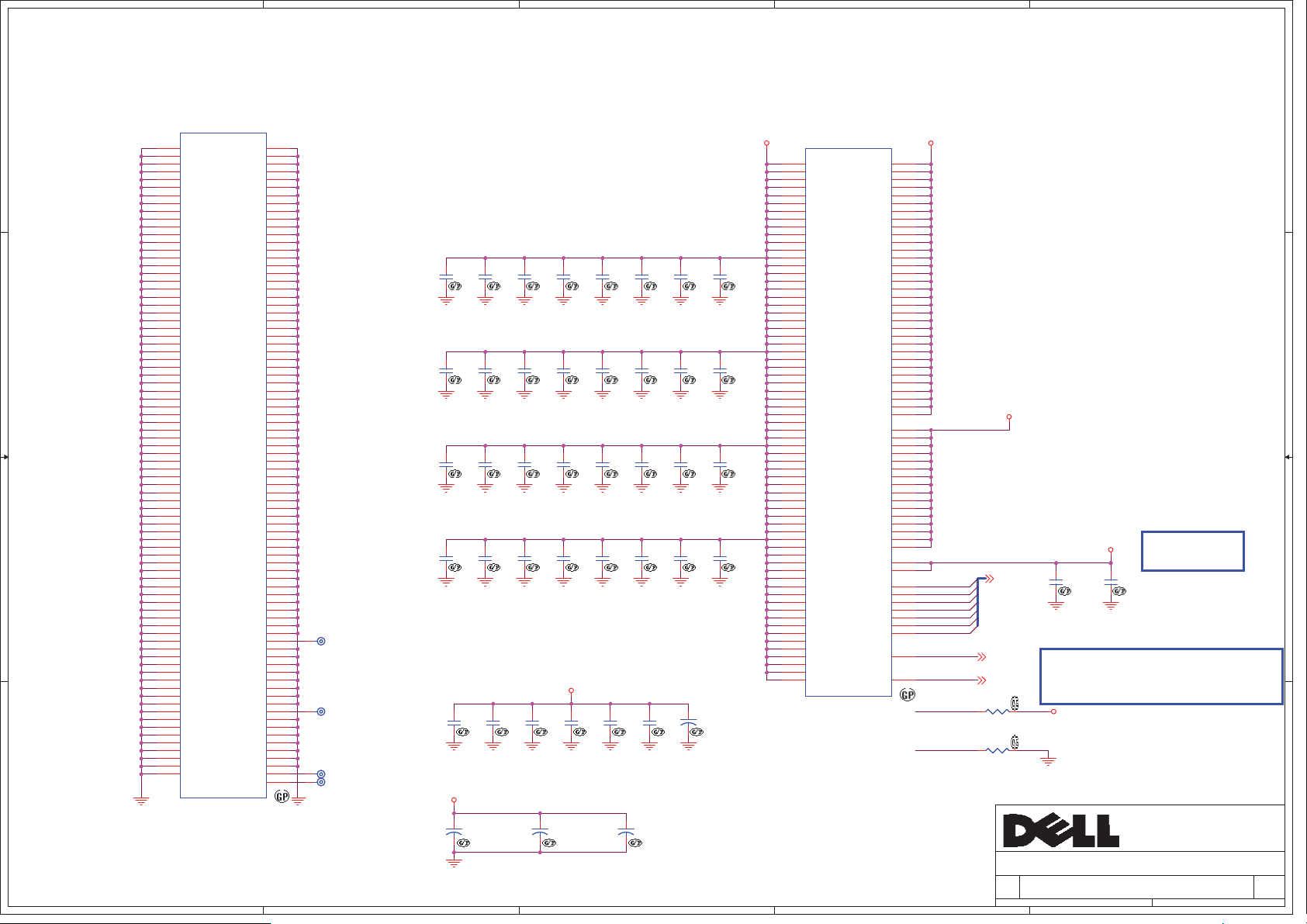

200-PIN DDR2 SODIMM

UNBUFFERED

DDR2 SODIMM

Socket

UNBUFFERED

DDR2 SODIMM

Socket

Power Switch

34

CIR

36

CIR Board

Int. KB

Numpad

13

14

31

PCIe (Lane4)

USB2.0 (P6)

USB2.0 (P4)

PCIe (Lane3)

PCIe (Lane2)

PCIe (Lane5)

PCIe (Lane6)

PCIe (Lane1)

USB2.0 (P9)

USB2.0 (P1)

USB2.0 (P2,P3)

USB2.0 (P8)

USB2.0 (P7)

USB2.0 (P5)

Express Card

Slot 54mm

Mini-Card

WPAN/Robson

Mini-Card

802.11a/g/n

PPU Card

CONN.

BCM5754M

Giga LAN

Mini-Card

WWAN

USB CONN.x1

W to B

CONN.

W to B

CONN.

USB2.0 (P2,P3)

32

USB2.0 (P8)

32

Buletooth 2.1

Camera

Module

D

30

31

30

29

RJ45

27

CONN

SIM

31

23

CONN

USB CONN.x2

Sniffer Board

Gaming LCD

Module

<Core Design>

<Core Design>

36

35

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet

Date: Sheet

E

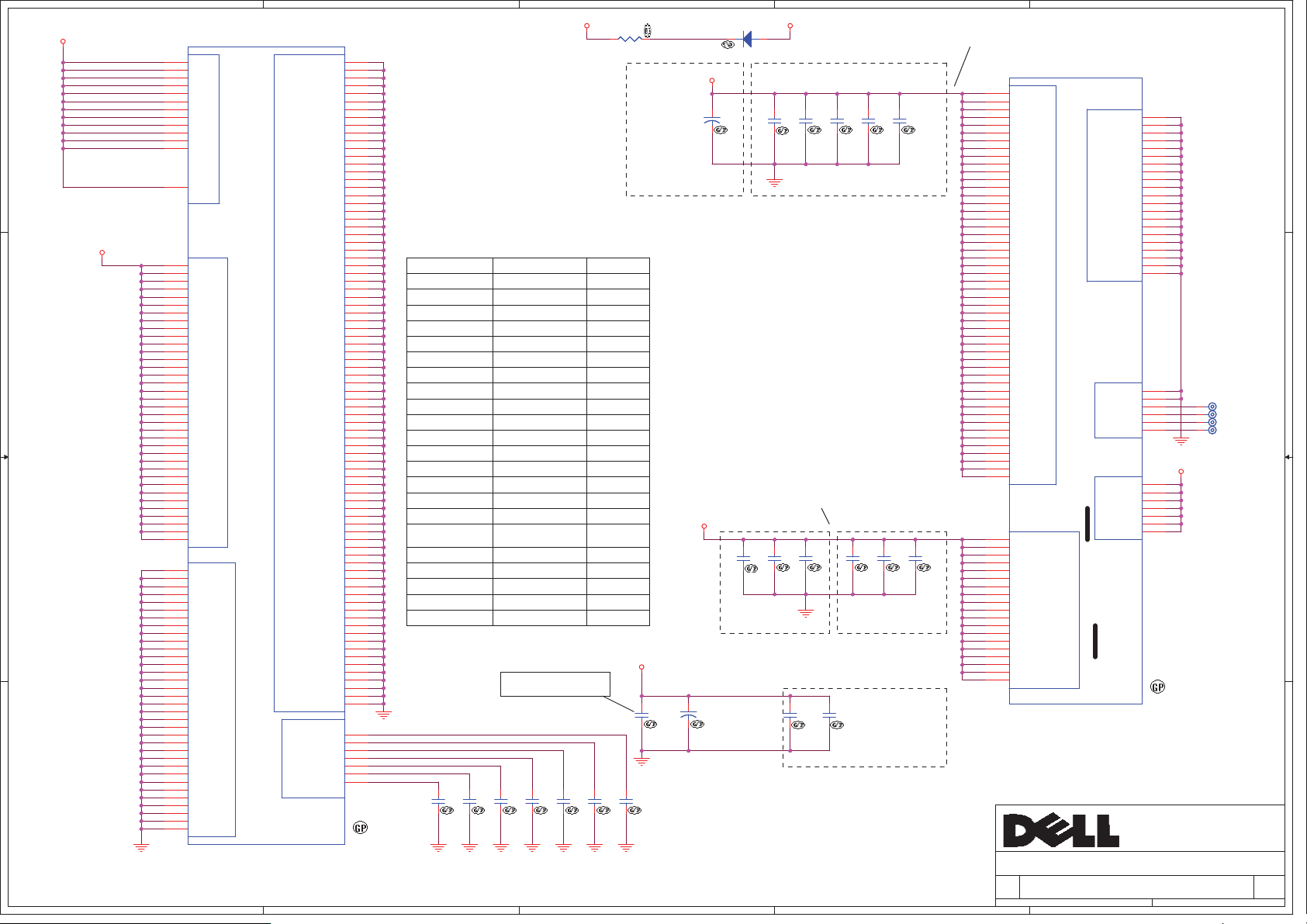

System DC/DC

TPS51120

OUTPUTSINPUTS

+PWR_SRC

+5V_ALW +5V_SUS

+3.3V_SUS

+3.3V_RTC_LDO

System DC/DC

SN0508073

+PWR_SRC

+1.5V_RUN

+1.25V_RUN

DDR2 DC/DC

SN0508073

+PWR_SRC

+1.8V_SUS

+1.05V_VCCP

LDO

TPS51100

+1.8V_SUS

+0.9V_DDR_VTT

LDO

MAX668

+PWR_SRC

+12V_S

Battery Charger

ISL88731

INPUTS OUTPUTS

+PWR_SRC

+VCHGR

CPU DC/DC

ISL6260C

INPUTS OUTPUTS

+PWR_SRC

28

PCB LAYER

+VCC_CORE

46

44

45

47

47

41

42,43

L1:TOP

31

L2:GND

L3:Signal

L4:Signal

L5:VCC

L6:Signal

L7:GND

L8:BOT

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

A3

A3

A3

Siberia

Siberia

Siberia

150Monday, July 16, 2007

150Monday, July 16, 2007

150Monday, July 16, 2007

E

A00

A00

A00

of

of

A

B

C

D

E

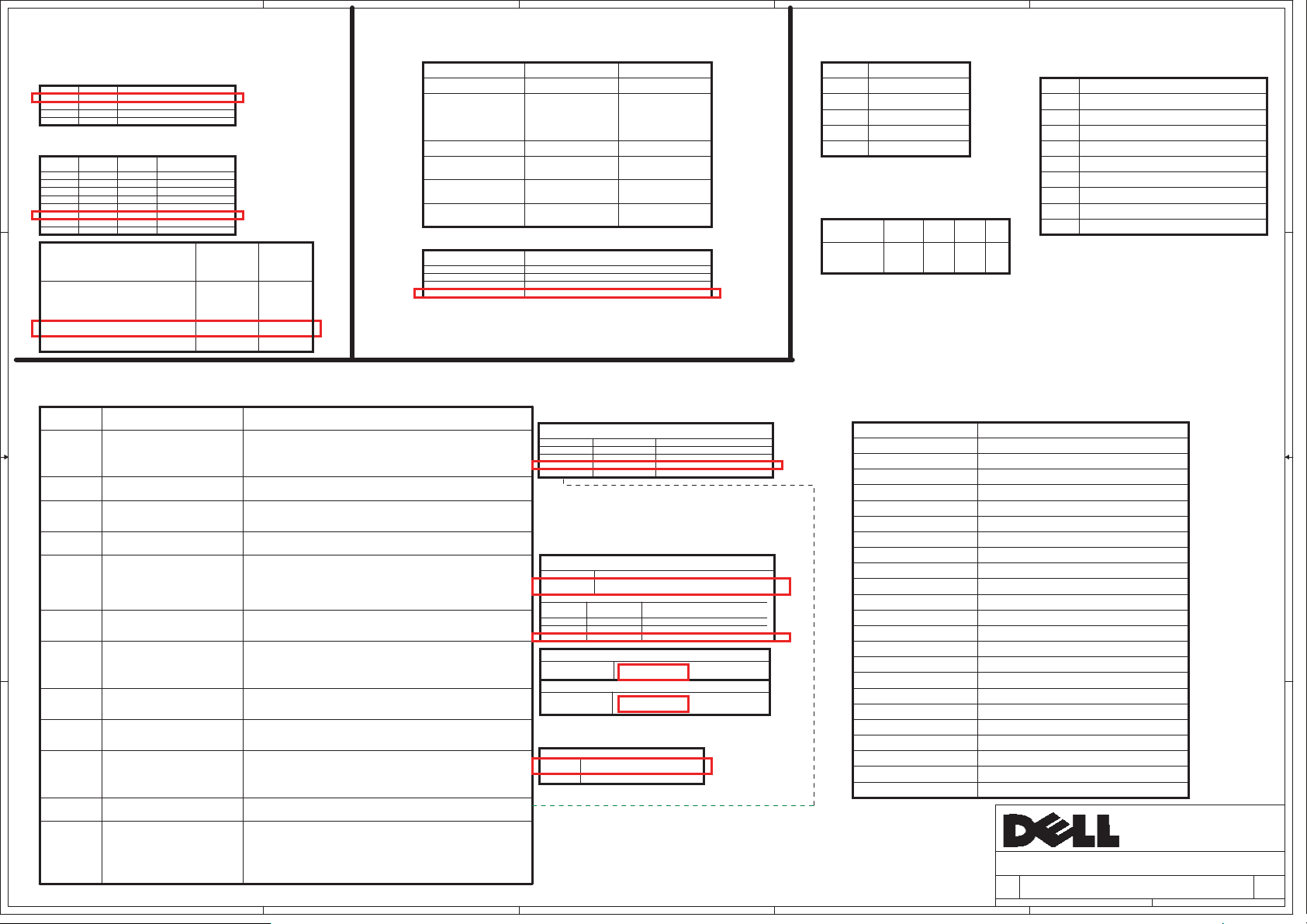

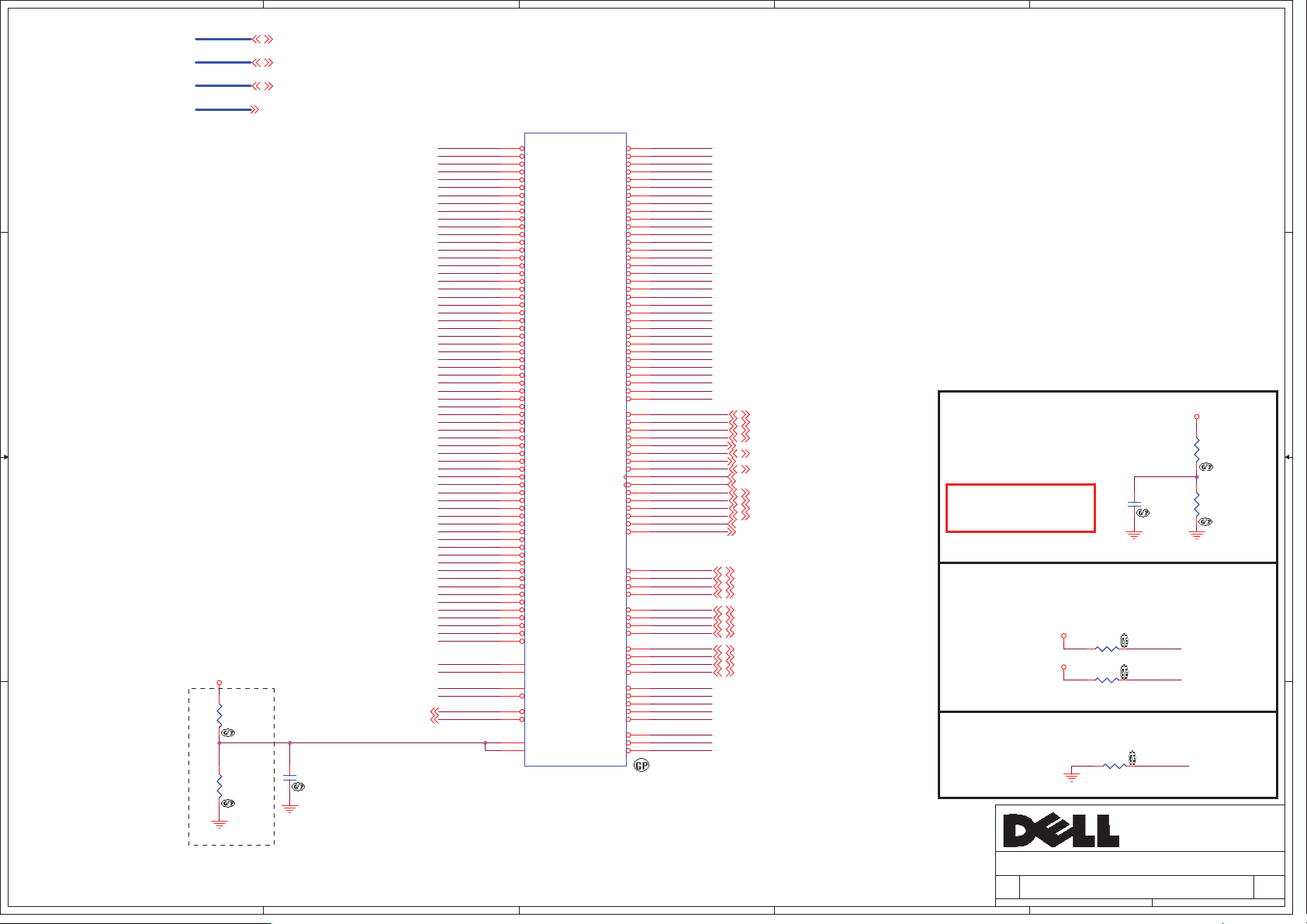

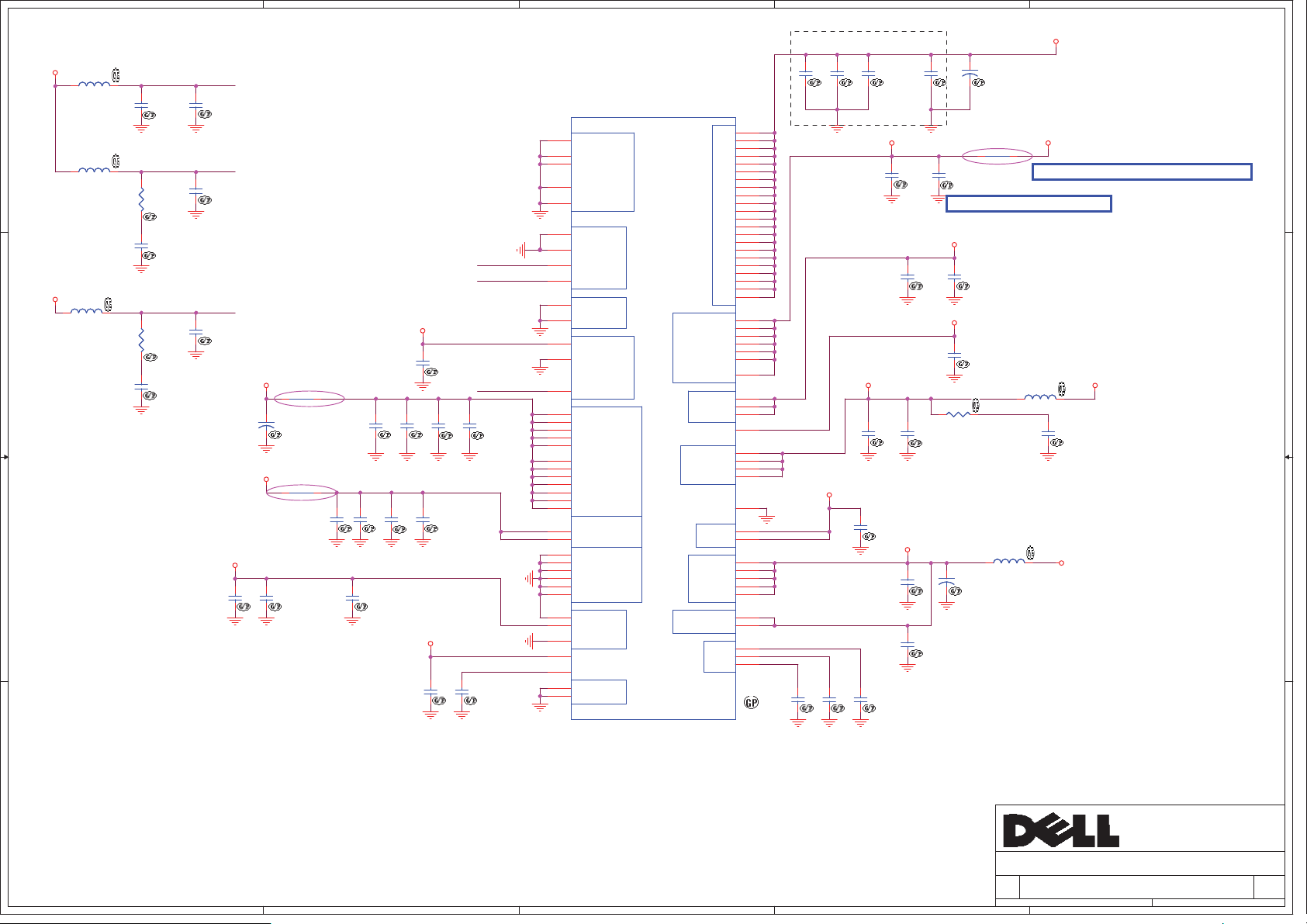

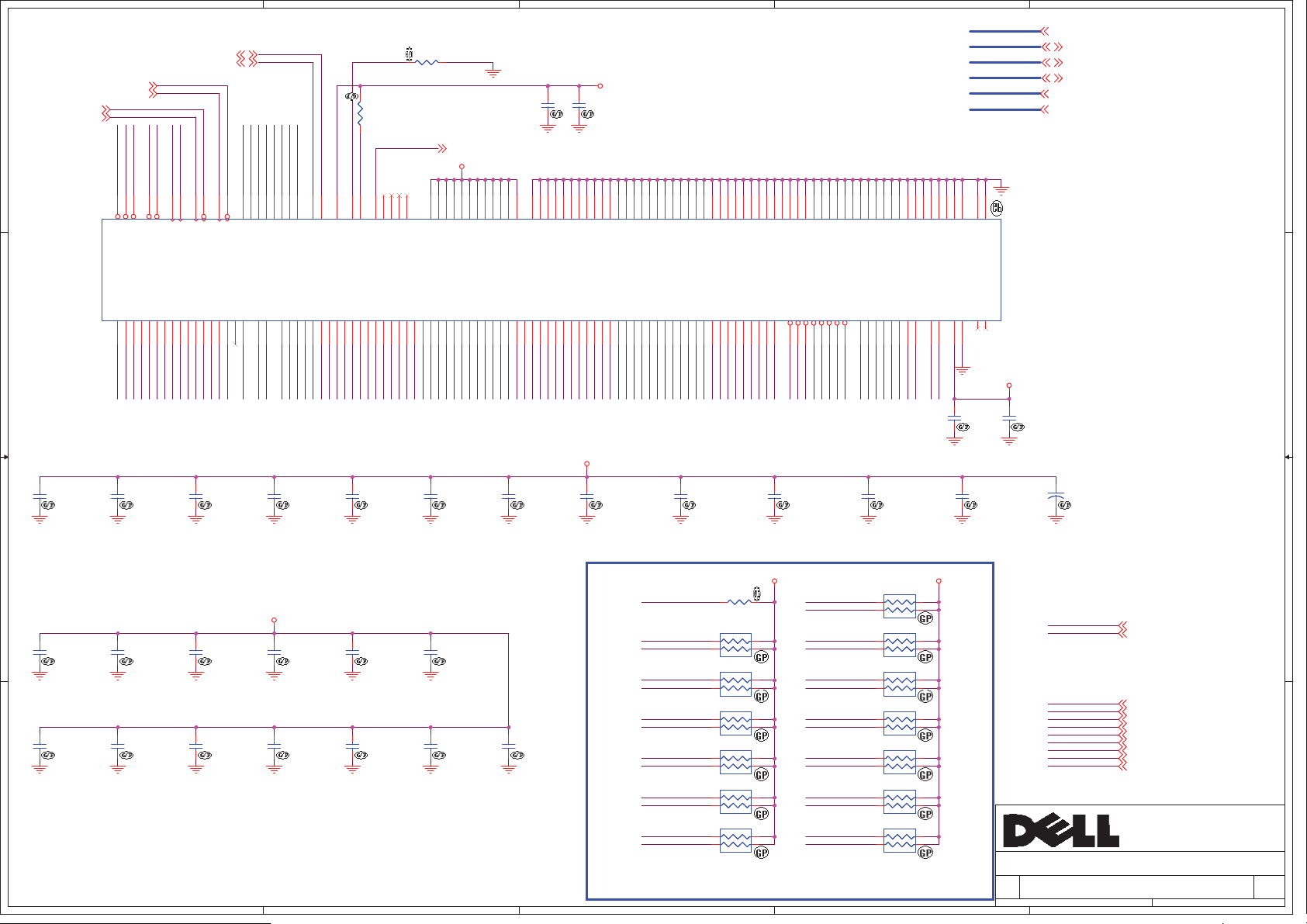

CLOCK GEN CY28547

27M_SS/LCD96_100M SELECTION TABLE

BYTE 10

Bit5 S1 Bit4 S0 Spread Spectrum S[1:0]

00

0

4 4

1

11

BYTE 15

IO_VOUT[2,1,0]

Bit2

Bit1

IO_VOUT2

IO_VOUT1

0

0

00

0

1

11

1

1

SEL2

FSC

1

0

0101

3 3

-0.5%(Default)

-1.0%

1

-1.5%

0

-2.0%

0

0

1

0

0

1

1

SEL1

FSB

Bit0

IO_VOUT0

0

1

11

0

0

1

SEL0

FSA

IO_VOUT[2,1,0]

0.3V

0.4V

0.5V

0.6V

0.7V

0.8V(Default)

0.9V

1.0V

01

01

01

CPU

100M

133M

166M

200M

FSB

X

X

667M

800M

INTEL ICH8-M STRAP PIN

INTEL CRESTLINE STRAP PIN

CFG Strap HIGH 1LOW 0

CFG 5

CFG 9

PCI Express Graphics

Lane Reversal

CFG 16

FSB Dynamic ODT Disabled Enabled

CFG 19

DMI Lane Reserved Normal Operation Lane Reserved

CFG 20

Concurrent SDVO/PCIE

SDVO_CTRL_DATA

SDVO Present

CFG 12

CFG 13

LL(00)

LH(01)

HL(10)

HH(11)

DMI X 2 DMI X 4

Lane Reversal Normal Mode(Lanes

Only PCIE or SDVO

is operation

NO SDVO Card

Present

Ϫ

Ϫ

Ϫ

Ϫ

number in order)

Ϫ

PCIE and SDVO are

operation simultaneous

SDVO Card Present

XOR/ALL-Z

Reserved

XOR Mode Enabled

All Z Mode Enabled

Normal Operation

Ϫ

PCIE Routing USB TABLE

LANE1

LANE2

LANE3

LANE4

LANE5

LANE6

MiniCard WWAN

MiniCard WLAN

BT/UWB/Robson

Express Card

PPU card

Giba Bit LOM

PCI ROUTING

INT REQ GNTIDSEL

1394/

MediaCard

AD17

C

D

11

ICH

USB0

USB1

USB2

USB3

USB4

USB5

USB6

USB7

USB8

USB9

Ext Lift Side

Ext Back

Ext Right Side (Top)

Ext Right Side (Bottom)

3rd mini card

Camera

Express Card

BT

Gaming LCD

WWAN

INTEL ICH8-M INTEGRATED

PULL-UPS and PULL-DOWNS

Signal

HDA_SDOUT

HDA_SYNC

GNT2#

GPIO20

GNT3#

2 2

GNT0#

SPI_CS1#

INTVRMEN

LAN100_SLP

SATALED#

SPKR

1 1

TP3

GPIO33/

HDA_DOCK_EN#

Usage/When Sampled Comment

XOR Chain Entrance/

PCIE Port Config 1 bit1,

Rising Edge of PWROK

PCIE Port Config 1 bit0,

Rising Edge of PWROK.

PCIE Port Config 2 bit0,

Rising Edge of PWROK.

Reserved.

Rising Edge of PWROK.

Top-Block Swap Override.

Rising Edge of PWROK.

Boot BIOS Destination

Selection.

Rising Edge of PWROK.

Integrated VccSus1_05

VccSus1_5 and VccCL1_5

VRM Enable/Disable.

Always sampled.

Integrated VccLAN1_05

VccCL1_05 VRM enable

/Disable. Always sampled.

PCIE LAN REVERSAL.Rising

Edge of PWROK.

No Reboot.

Rising Edge of PWROK.

XOR Chain Entrance.

Rising Edge of PWROK.

Flash Descriptor Security

Override Strap

Rising Edge of PWROK.

A

Allows entrance to XOR Chain testing when TP3

pulled low at rising edge of PWROK.When TP3 not

pulled low at rising edge of PWROK,sets bit1 of

RPC.PC(Config Registers:offset 224h)

Sets bit0 of RPC.PC(Config Registers:Offset 224h)

Sets bit2 of RPC.PC(Config Registers:Offset 224h)

Weak Internal PULL-DOWN.NOTE:This signal should

not be pull HIGH.

Sampled low:Top-Block Swap mode(inverts A16 for

all cycles targeting FWH BIOS space).

Note: Software will not be able to clear the

Top-Swap bit until the system is rebooted

without GNT3# being pulled down.

Controllable via Boot BIOS Destination bit

(Config Registers:Offset 3410h:bit 11:10).

GNT0# is MSB, 01-SPI, 10-PCI, 11-LPC.

Enables integrated VccSus1_05,VccSus1_5 and

VccCL1_5 VRM when sampled high

Enables integrated VccLAN1_05,VccCL1_05 VRM

when sampled high

This signal has weak internal pull-up.

set bit27 of MPC.LR(Device28:Function0:Offset D8)

If sampled high, the system is strapped to the

"No Reboot" mode(ICH8M will disable the TCO Timer

system reboot feature). The status is readable

via the NO REBOOT bit.(Offset:3410h:bit5)

This signal should not be pull low unless using

XOR Chain testing.

Internal Pull-Up.If sampled low,the Flash Descriptor

Security will be overidden.if high,the Security

measures defined in the Flash Descriptor will be in

effect.

This should only be used in manufacturing

environments

XOR Chain Entrance Strap

ICH_RSVD

A16 swap override strap

PCI_GNT#3 low = A16 swap override enable

BOOT BIOS Strap

integrated VccSus1_05,VccSus1_5,VccCL1_5

SM_INTVRMEN

integrated VccLan1_05VccCL1_05

LAN100_SLP

AZ_DOUT_ICH

tp3

0

0

11

0 1 SPI

0

1

01

high = default

SPI_CS#1

01

11

High=Enable Low=Disable

High=Enable Low=Disable

Description

RSVD

Enter XOR Chain

Normal Operation(default)

Set PCIE port cofig bit1

BOOT BIOS LocationPCI_GNT#0

PCI

LPC(Default)

DEFAULE HIGH

No Reboot Strap

SPKR

LOW = Defaule

High=No Reboot

8.2K PULL HIGH

B

http://hobi-elektronika.net

C

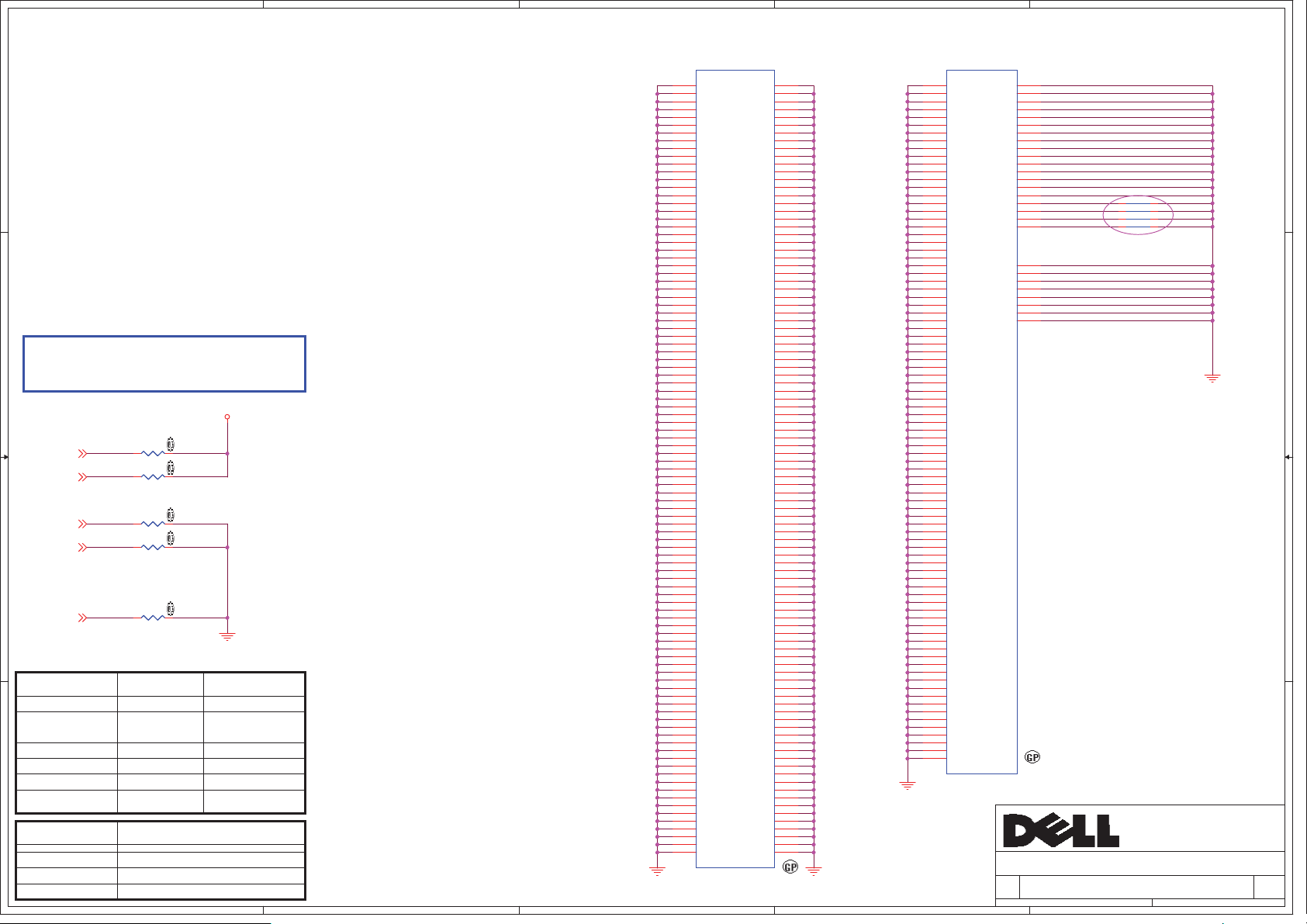

SIGNAL Resistor Type/Value

HDA_BIT_CLK

HDA_RST#

HDA_SDIN[3:0]

HDA_SDOUT

HDA_SYNC

GNT[3:0]

GPIO[20]

LDA[3:0]#/FHW[3:0]#

LAN_RXD[2:0]

LDRQ[0]

LDRQ[1]/GPIO23

PME#

PWRBTN#

SATALED#

SPI_CS1#

SPI_CLK

SPI_MOSI

SPI_MISO

TACH_[3:0]

SPKR

TP[3]

USB[9:0][P,N]

CL_RST0#

D

PULL-DOWN 20K

NONE

PULL-DOWN 20K

PULL-DOWN 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-UP 10K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 15K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-UP 20K

PULL-DOWN 20K

PULL-UP 20K

PULL-DOWN 15K

PULL-UP 13K

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet

Date: Sheet

Table of Content

Table of Content

Table of Content

Siberia

Siberia

Siberia

A00

A00

A00

of

of

250Monday, July 16, 2007

250Monday, July 16, 2007

250Monday, July 16, 2007

E

A

4 4

B

C

D

E

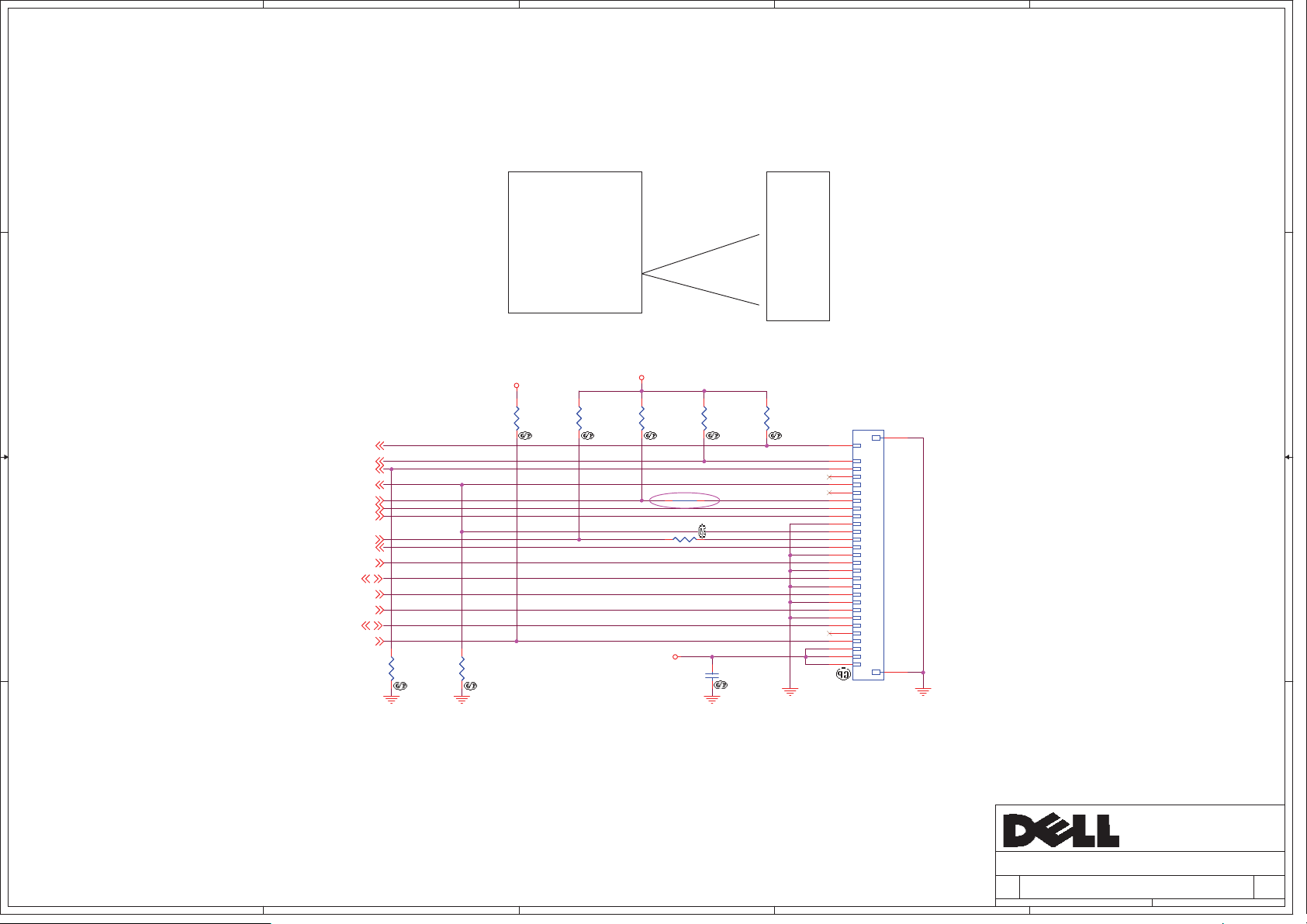

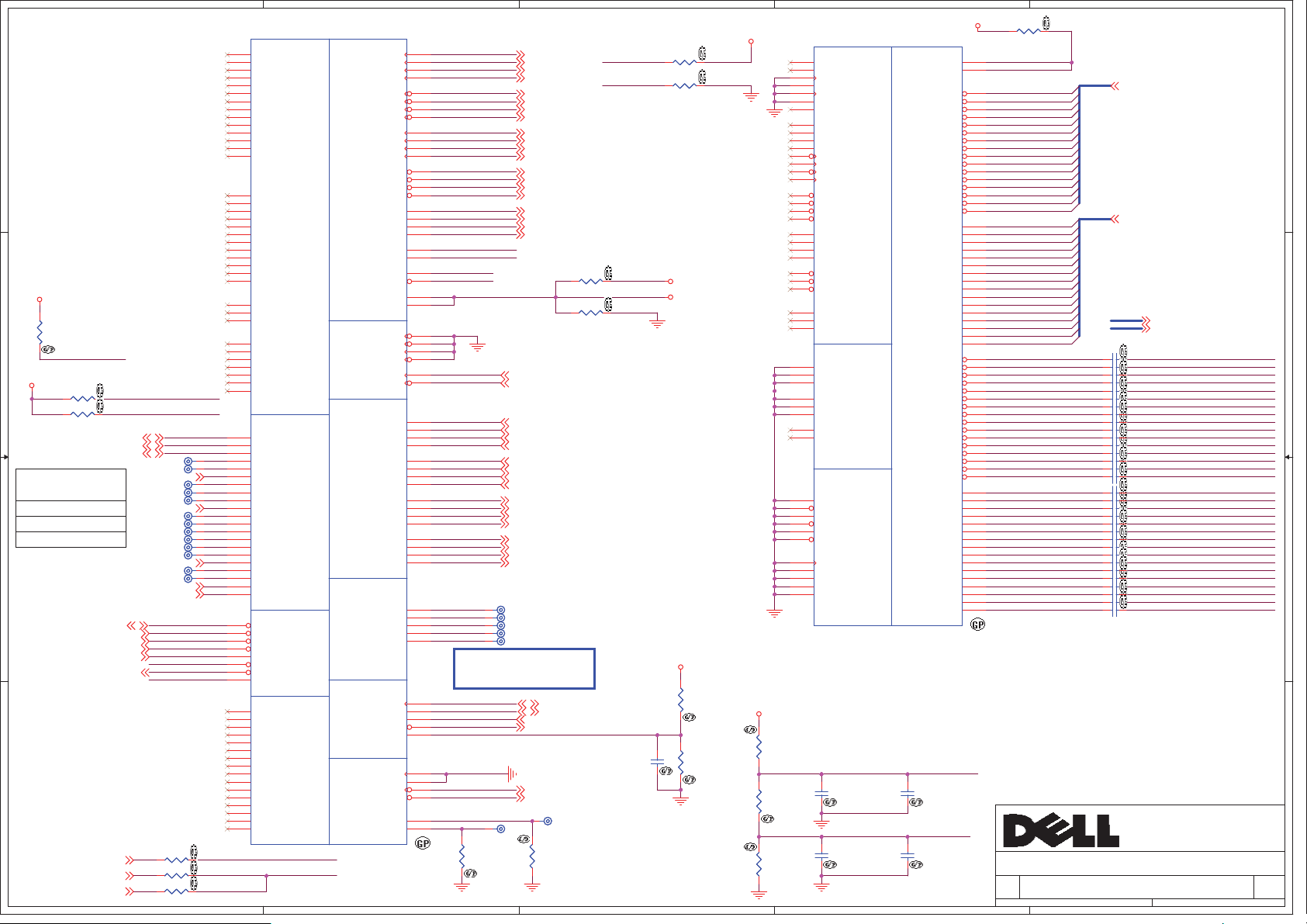

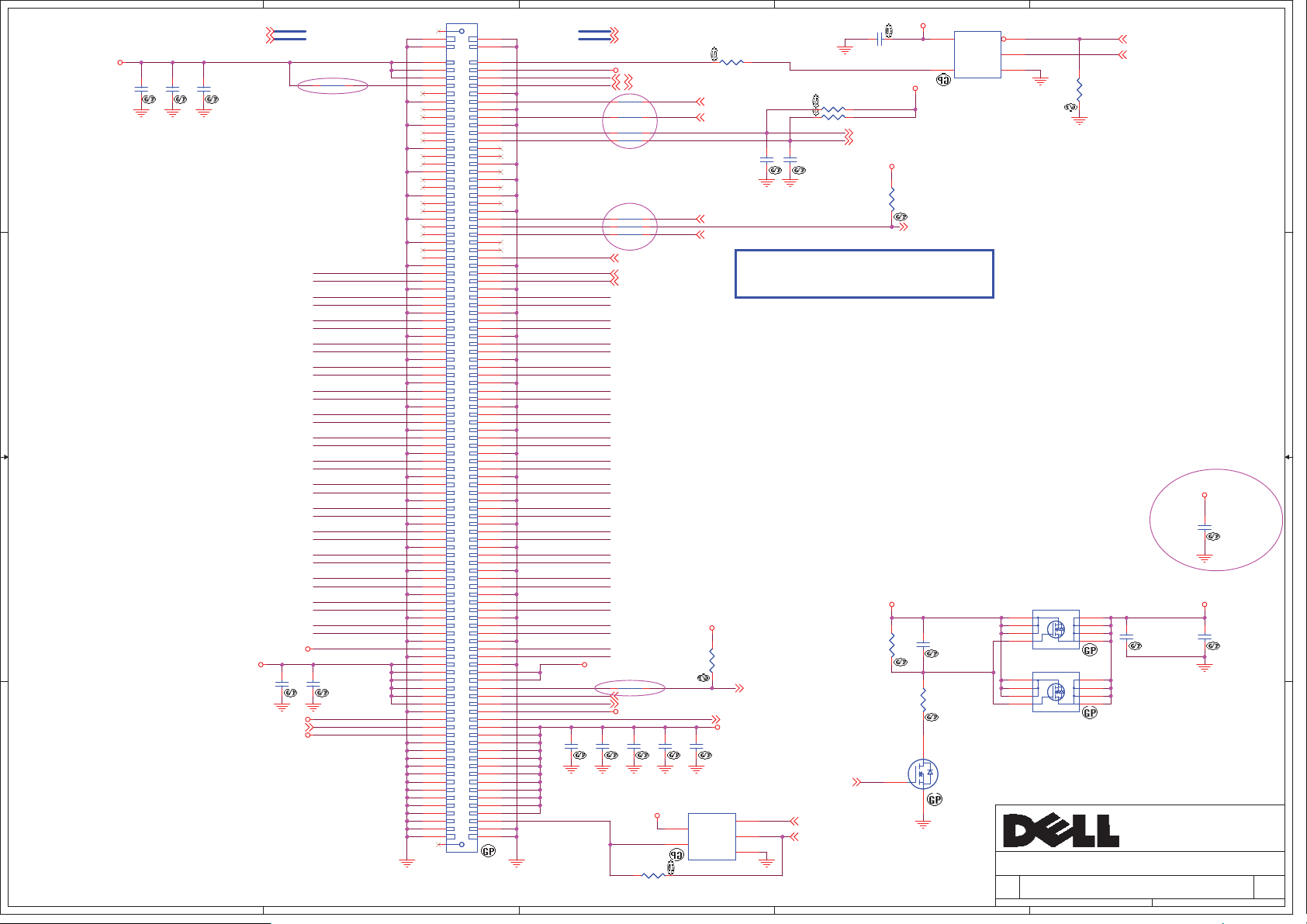

CPU

ITP Conn.

TCK(PIN 5)

TCK(PIN AC5)

FBO(PIN 11)

3 3

12

R10

R10

51R2F-2-GP

51R2F-2-GP

+1.05V_VCCP

12

R14

R14

51R2F-2-GP

51R2F-2-GP

A00

R13 0R0402-PADR13 0R0402-PAD

R11 22D6R2F-L1-GPR11 22D6R2F-L1-GP

+1.05V_VCCP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

1 2

1 2

C28

C28

12

R16

R16

39D2R2F-L-GP

39D2R2F-L-GP

XDP_TDO_FELX

CPURST_FLEX#

12

12

R17

R17

150R2F-1-GP

150R2F-1-GP

ITP1

ITP1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

MLX-CON28-3-GP

MLX-CON28-3-GP

20.K0116.028

20.K0116.028

DY

DY

29

H_RESET# use pull-up Resistor close

ITP connector 500 mil ( max )

30

+1.05V_VCCP use Decoupling Capacitor close

ITP connector 100 mil ( max )

+3.3V_SUS

12

R9

R9

150R2F-1-GP

150R2F-1-GP

ITP_TDI5

ITP_TMS5

ITP_TRST#5

ITP_TCK5

ITP_TDO5

CLK_CPU_ITP#4

CLK_CPU_ITP4

H_RESET#5,7

ITP_BPM#55

2 2

ITP_BPM#45

ITP_BPM#35

ITP_BPM#25

ITP_BPM#15

ITP_BPM#05

ITP_DBRESET#5,18,34

ITP_TDI

ITP_TMS

ITP_TRST#

ITP_TDO

CLK_CPU_ITP#

CLK_CPU_ITP

H_RESET#

ITP_BPM#5

ITP_BPM#4

ITP_BPM#3

ITP_BPM#2

ITP_BPM#1

ITP_BPM#0

12

R15

R15

680R2J-3-GP

680R2J-3-GP

ITP_TCK

12

R12

R12

27D4R2F-L1-GP

27D4R2F-L1-GP

ITP_DBRESET#

1 1

A

B

ITP Debug Conn.

http://hobi-elektronika.net

C

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size

Size Document Number Rev

Size Document Number Rev

Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

D

Date: Sheet

ITP Debug

ITP Debug

ITP Debug

Siberia

Siberia

Siberia

A00

A00

A00

of

of

of

350Monday, July 16, 2007

350Monday, July 16, 2007

350Monday, July 16, 2007

E

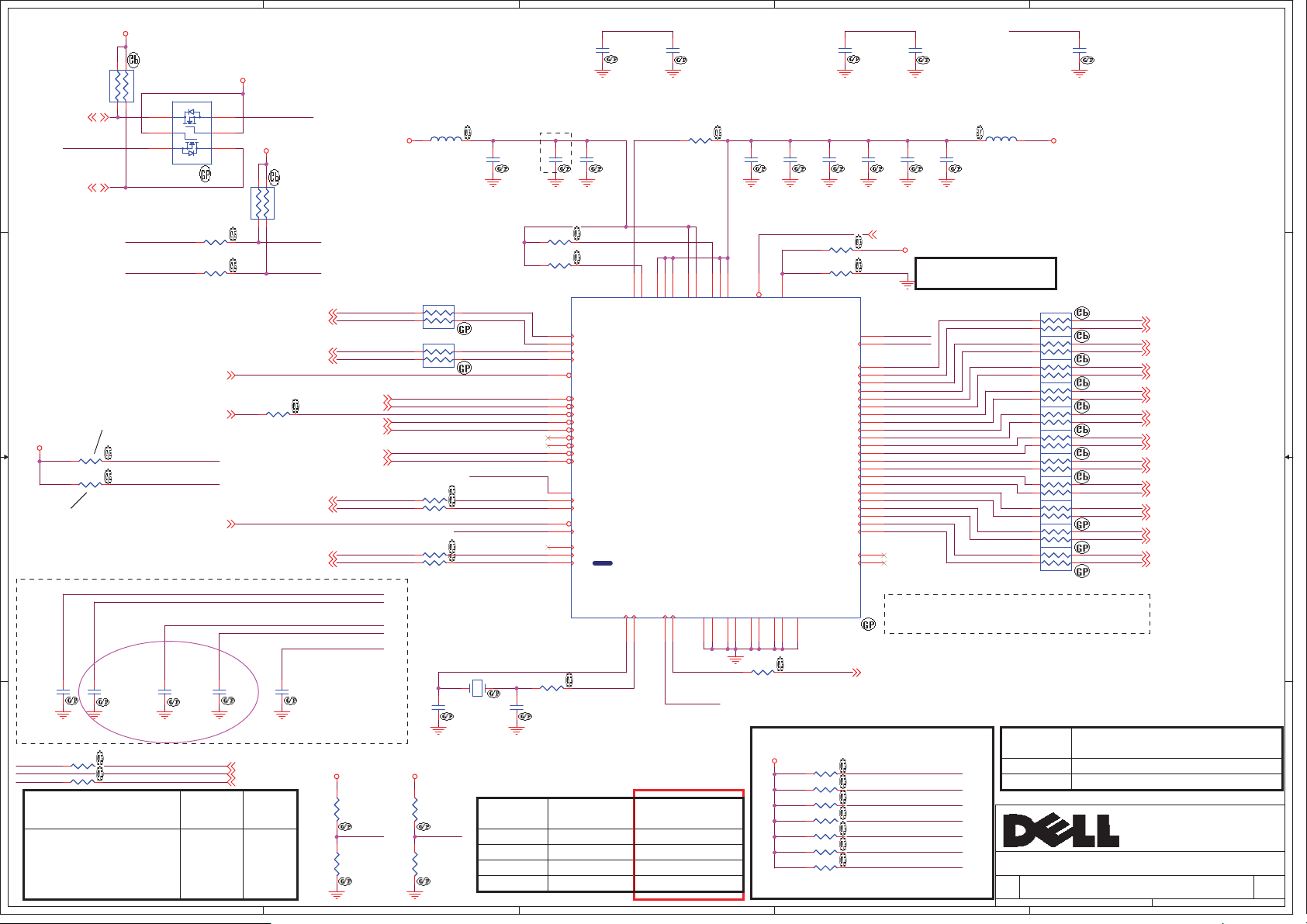

A

+3.3V_ALW

4

1

CKG_SMBDAT33

4 4

CLK_SCLK

CKG_SMBCLK33

3 3

2 3

Enable ITP

+3.3V_RUN

R122 10KR2J-3-GPR122 10KR2J-3-GP

1 2

R135 10KR2J-3-GPR135 10KR2J-3-GP

1 2

Enable TME

2 2

A00

DY

DY

12

12

C657

C657

C661

C661

SC10P50V2JN-4GP

SC10P50V2JN-4GP

SC27P50V2JN-2-GP

SC27P50V2JN-2-GP

R111 8K2R2J-3-GPR111 8K2R2J-3-GP

1 2

FSC CPU_MCH_BSEL2

R126 8K2R2J-3-GPR126 8K2R2J-3-GP

1 2

1 1

SEL2

FSC

SEL1

FSB

1

0

SEL0

FSA

01

01

0101

SMBus address:D2

RN2

RN2

SRN2K2J-1-GP

SRN2K2J-1-GP

U24

U24

6

5

2N7002DW-7F-GP

2N7002DW-7F-GP

SRN2K2J-1-GP

SRN2K2J-1-GP

R119

CKG_SMBDAT

CKG_SMBCLK

R119

1 2

DY

DY

0R2J-2-GP

0R2J-2-GP

R120

R120

1 2

DY

DY

0R2J-2-GP

0R2J-2-GP

H_STP_CPU#18

CLK_3GPLLREQ#8

PCI_ICH

PCI_PCCARD

H_STP_PCI#18

12

C694

C694

SC10P50V2JN-4GP

SC10P50V2JN-4GP

CPU_MCH_BSEL0FSA

CPU_MCH_BSEL1

CPU

100M

133M

166M

01

A

200M

+3.3V_RUN

1

2

34

12

CLK_SDATA

+3.3V_RUN

4

RN47

RN47

1

2 3

CLK_SDATA

CLK_SCLK

CLK_CPU_BCLK#5

CLK_CPU_BCLK5

CLK_MCH_BCLK#7

CLK_MCH_BCLK7

R529

R529

1 2

475R2F-L1-GP

475R2F-L1-GP

CLK_ICH_48M18

CLK_PCI_ICH18

CLK_PCI_PCCARD22

CLK_PCI_502533

CLK_ICH_48M

CLK_PCI_ICH

CLK_PCI_PCCARD

CLK_PCI_5025

CLK_ICH_14M

DY

DY

12

C187

C693

C693

SC8P250V2CC-GP

SC8P250V2CC-GP

CPU_MCH_BSEL0 5,8

CPU_MCH_BSEL1 5,8

CPU_MCH_BSEL2 5,8

C187

SC27P50V2JN-2-GP

For wireless performance

SC27P50V2JN-2-GP

FSB

X

X

667M

800M

SATA_CLKREQ#18

MINI3CLK_REQ#31

LOM_CLKREQ#27

CARD_CLK_REQ#30

MINI2CLK_REQ#31

MINI1CLK_REQ#30

+3.3V_RUN +3.3V_RUN

12

R115

R115

10KR2J-3-GP

10KR2J-3-GP

DY

DY

12

R116

R116

10KR2J-3-GP

10KR2J-3-GP

DY

DY

B

L34

L34

1 2

BLM21PG600SN-1GP

BLM21PG600SN-1GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

RN46

CLK_CPU_BCLK#

CLK_CPU_BCLK

CLK_MCH_BCLK#

CLK_MCH_BCLK

SC27P50V2JN-2-GP

SC27P50V2JN-2-GP

FSA PCI_TPM

RN46

1

2 3

SRN33J-5-GP-U

SRN33J-5-GP-U

RN43

RN43

1

2 3

SRN33J-5-GP-U

SRN33J-5-GP-U

R503 33R2J-2-GPR503 33R2J-2-GP

1 2

R515 33R2J-2-GPR515 33R2J-2-GP

1 2

R527 33R2J-2-GPR527 33R2J-2-GP

1 2

R528 33R2J-2-GPR528 33R2J-2-GP

1 2

CL=20pF±0.2pF

Freq. Tolerance:±30ppm

C670

C670

12

R129

R129

10KR2J-3-GP

10KR2J-3-GP

12

R128

R128

10KR2J-3-GP

10KR2J-3-GP

DY

DY

B

+CK_VDD_MAIN2

12

C679

C679

CPU_BCLK#

4

CPU_BCLK

MCH_BCLK#

4

MCH_BCLK

H_STP_CPU#

SATA_CLKREQ#

MCH_3GPLL_REQ#

LOM_CLKREQ#

CARD_CLK_REQ#

MINI2CLK_REQ#

MINI1CLK_REQ#

CPU_MCH_BSEL1

H_STP_PCI#

X5

X5

CLK_XOUT

1 2

12

X-14D31818M-25GP

X-14D31818M-25GP

PCI_TPM=FCTSEL1

PIN34

FCTSEL1

PIN43

PIN44

PIN47

PIN48

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

Place near C10

12

C668

C668

R121

R121

1 2

1R3F-GP

1R3F-GP

R507

R507

1 2

2R3J-2-GP

2R3J-2-GP

13

CPUC0

14

CPUT0

10

CPUC1

11

CPUT1

24

CPU_STP#

46

CLKREQ1#

26

CLKREQ2#

28

CLKREQ3#

57

CLKREQ4#

29

CLKREQ5#

62

CLKREQ6#

38

CLKREQ7#

71

CLKREQ8#

72

CLKREQ9#

45

FSAFSA

PCI_ICH

PCI_TPM

PCI_PCCARD

PCI_SIO

12

C669

C669

SC27P50V2JN-2-GP

SC27P50V2JN-2-GP

41

37

25

34

33

32

27

R518

R518

1 2

0R2J-2-GP

0R2J-2-GP

FSB/TEST_MODE

48M/FSA

PCIF0/ITP_SEL

PCI_STP#

PCI4/FCTSEL1

PCI3

PCI2

PCI1/TME

DOT96T

DOT96C

LCD100/96T

LCD100/96C

http://hobi-elektronika.net

+CK_VDD_A

12

C148

C148

12

C665

C665

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

+CK_VDD_REF

+CK_VDD_48

U87

U87

20

CLK_XTAL_IN

CLK_XTAL_OUT

0

C

12

C644

C644

SCD047U10V2KX-2GP

SCD047U10V2KX-2GP

R99

R99

1 2

2D2R3J-2-GP

2D2R3J-2-GP

7

40

VDDA

XOUT19XIN

VDD_48

36

65

DD_PCI

DD_SRC

VDD_PCI30V

VDD_SRC49VDD_SRC54V

REF122REF0/FSC_TEST_SEL

VSS_REF21VSS_CPU15VSS_SRC

23

CLKREF

FSC

1

27M_NonSpread

27M_Spread

SRCT_0

SRCC_0

C

SC4D7U6D3V3KX-GP

SC4D7U6D3V3KX-GP

12

12

C168

C168

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

PGMODE

1

12

18

39

9

VDD_REF

VDD_SRC

VDD_CPU

VSS_SRC

4

68

R127 33R2J-2-GPR127 33R2J-2-GP

VSS_CPU

VTT_PWRGD#/PD

SRCT_0/LCD100MT

SRCC_0/LCD100MC

CPUT2_ITP/SRCT_10

CPUC2_ITP/SRCC_10

DOT96T/27M_NSS

DOT96C/27M_SS

VSSA

VSS_PCI31VSS_PCI35VSS_48

8

42

73

1 2

+3.3V_RUN

R451 10KR2J-3-GPR451 10KR2J-3-GP

R452 10KR2J-3-GPR452 10KR2J-3-GP

R140 10KR2J-3-GPR140 10KR2J-3-GP

R139 10KR2J-3-GPR139 10KR2J-3-GP

R108 10KR2J-3-GPR108 10KR2J-3-GP

R532 10KR2J-3-GPR532 10KR2J-3-GP

R93 10KR2J-3-GPR93 10KR2J-3-GP

D

12

C658

C658

12

C640

C640

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

R107

R107

DY

DY

10KR2J-3-GP

10KR2J-3-GP

R104

R104

DY

DY

10KR2J-3-GP

10KR2J-3-GP

SDATA

SCLK

SRCT_1

SRCC_1

SRCT_2

SRCC_2

SRCT_3

SRCC_3

SRCT_4

SCRC_4

SRCT_5

SCRC_5

SRCT_6

SRCC_6

SRCT_7

SRCC_7

SRCT_8

SRCC_8

SRCT_9

SRCC_9

12

17

16

47

48

50

51

52

53

55

56

58

59

60

61

63

64

66

67

70

69

3

2

6

5

43

44

CLK_ICH_14M 18

C637

C637

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

CLK_PWRGD

1 2

1 2

GND

CY28547LFXCT-GP

CY28547LFXCT-GP

Solder Thermal Pad to

GND add min 4 vias

12

+CK_VDD_MAIN+CK_VDD_A

12

C635

C635

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

CLK_PWRGD 18

+3.3V_RUN

CLK_SDATA

CLK_SCLK

PCIE_PPU

PCIE_PPU#

PCIE_SATA

PCIE_SATA#

PCIE_MINI3

PCIE_MINI3#MINI3CLK_REQ#

MCH_3GPLL

MCH_3GPLL#

PCIE_LOM

PCIE_LOM#

PCIE_EXPCARD

PCIE_EXPCARD#

PCIE_VGA

PCIE_VGA#

PCIE_ICH

PCIE_ICH#

PCIE_MINI2

PCIE_MINI2#

PCIE_MINI1

PCIE_MINI1#

CPU_ITP

CPU_ITP#

Clock Gen.

1st source: ICS ICS9LPR333CKLF (71.09333.A03)

2nd source: Cypress CY28547LFXC (71.28547.003)

CLKREQ PULL HIGH

1 2

1 2

1 2

1 2

1 2

1 2

1 2

MINI1CLK_REQ#

MINI2CLK_REQ#

MINI3CLK_REQ#

CARD_CLK_REQ#

SATA_CLKREQ#

CLK_3GPLLREQ#

LOM_CLKREQ#

D

+CK_VDD_REF+CK_VDD_48

C179

C179

SCD047U10V2KX-2GP

SCD047U10V2KX-2GP

L9

L9

BLM21PG600SN-1GP

BLM21PG600SN-1GP

12

C650

C650

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

C648

C648

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

Pull low to Decide

VTT_PWRGO Low active

12

PIN9

PGMODE

0

1

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

+3.3V_RUN+3.3V_RUN

2 3

1

2 3

1

2 3

1

2 3

1

2 3

1

2 3

1

2 3

1

2 3

1

1

2 3

1

2 3

1

2 3

E

12

C660

C660

SCD047U10V2KX-2GP

SCD047U10V2KX-2GP

RN44

RN44

SRN33J-5-GP-U

SRN33J-5-GP-U

4

RN41

RN41

SRN33J-5-GP-U

SRN33J-5-GP-U

4

RN38

RN38

SRN33J-5-GP-U

SRN33J-5-GP-U

4

RN35

RN35

SRN33J-5-GP-U

SRN33J-5-GP-U

4

RN34

RN34

SRN33J-5-GP-U

SRN33J-5-GP-U

4

RN33

RN33

SRN33J-5-GP-U

SRN33J-5-GP-U

4

RN32

RN32

SRN33J-5-GP-U

SRN33J-5-GP-U

4

RN31

RN31

SRN33J-5-GP-U

SRN33J-5-GP-U

4

RN30

RN30

4

SRN33J-5-GP-U

SRN33J-5-GP-U

RN36

RN36

4

SRN33J-5-GP-U

SRN33J-5-GP-U

RN39

RN39

4

SRN33J-5-GP-U

SRN33J-5-GP-U

CLK_PCIE_PPU 29

CLK_PCIE_PPU# 29

CLK_PCIE_SATA 16

CLK_PCIE_SATA# 16

CLK_PCIE_MINI3 31

CLK_PCIE_MINI3# 31

CLK_MCH_3GPLL 8

CLK_MCH_3GPLL# 8

CLK_PCIE_LOM 27

CLK_PCIE_LOM# 27

CLK_PCIE_EXPCARD 30

CLK_PCIE_EXPCARD# 30

CLK_PCIE_VGA 15

CLK_PCIE_VGA# 15

CLK_PCIE_ICH 17

CLK_PCIE_ICH# 17

CLK_PCIE_MINI2 31

CLK_PCIE_MINI2# 31

CLK_PCIE_MINI1 30

CLK_PCIE_MINI1# 30

CLK_CPU_ITP 3

CLK_CPU_ITP# 3

PIN39

DISCRIPTION

VTT_PWRGD#/PD

CKPWRGD/PD#(DEFAULT)

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CLK GEN CY28547

CLK GEN CY28547

CLK GEN CY28547

Siberia

Siberia

Siberia

E

of

of

of

450Monday, July 16, 2007

450Monday, July 16, 2007

450Monday, July 16, 2007

A00

A00

A00

A

H_D#[63..0]

H_A#[35..3]

H_REQ#[4..0]

H_RS#[2..0]

4 4

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_ADSTB#07

3 3

H_ADSTB#17

H_A20M#16

H_FERR#16

H_IGNNE#16

H_STPCLK#16

H_INTR#16

H_NMI#16

H_SMI#16

TP6TPAD28 TP6TPAD28

TP8TPAD28 TP8TPAD28

2 2

TP7TPAD28 TP7TPAD28

TP3TPAD28 TP3TPAD28

TP51TPAD28 TP51TPAD28

TP4TPAD28 TP4TPAD28

TP2TPAD28 TP2TPAD28

TP10TPAD28 TP10TPAD28

TP5TPAD28 TP5TPAD28

TP9TPAD28 TP9TPAD28

H_ADSTB#0

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADSTB#1

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK#

H_INTR#

H_NMI#

H_SMI#

CPU_RSVD01

CPU_RSVD02

CPU_RSVD03

CPU_RSVD04

CPU_RSVD05

CPU_RSVD06

CPU_RSVD07

CPU_RSVD08

CPU_RSVD09

CPU_RSVD10

U76A

U76A

J4

A3#

L5

A4#

L4

A5#

K5

A6#

M3

A7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L2

A13#

P4

A14#

P1

A15#

R1

A16#

M1

ADSTB0#

K3

REQ0#

H2

REQ1#

K2

REQ2#

J3

REQ3#

L1

REQ4#

Y2

A17#

U5

A18#

R3

A19#

W6

A20#

U4

A21#

Y5

A22#

U1

A23#

R4

A24#

T5

A25#

T3

A26#

W2

A27#

W5

A28#

Y4

A29#

U2

A30#

V4

A31#

W3

A32#

AA4

A33#

AB2

A34#

AA3

A35#

V1

ADSTB1#

A6

A20M#

A5

FERR#

C4

IGNNE#

D5

STPCLK#

C6

LINT0

B4

LINT1

A3

SMI#

M4

RSVD#M4

N5

RSVD#N5

T2

RSVD#T2

V3

RSVD#V3

B2

RSVD#B2

C3

RSVD#C3

D2

RSVD#D2

D22

RSVD#D22

D3

RSVD#D3

F6

RSVD#F6

B1

KEY_NC

SKT-CPU478P-GP

SKT-CPU478P-GP

62.10079.021

62.10079.021

1 OF 4

1 OF 4

ADDR GROUP 0

ADDR GROUP 0

ADDR GROUP 1

ADDR GROUP 1

XDP/ITP SIGNALS CONTROL

XDP/ITP SIGNALS CONTROL

THERMAL

THERMAL

PROCHOT#

ICH

ICH

THERMTRIP#

HCLK

HCLK

RESERVED

RESERVED

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

IERR#

LOCK#

RESET#

TRDY#

HITM#

BPM0#

BPM1#

BPM2#

BPM3#

PRDY#

PREQ#

TRST#

DBR#

THRMDA

THRMDC

BCLK0

BCLK1

Use old Symbol replace New P/N

original value:MEROM-CPU479P-GP-U

+1.05V_VCCP

R21 200R2F-L-GP

R21 200R2F-L-GP

1 2

DY

DY

R20 56R2J-4-GPR20 56R2J-4-GP

1 2

R30 56R2J-4-GPR30 56R2J-4-GP

1 2

R19 56R2J-4-GPR19 56R2J-4-GP

1 1

1 2

R23 54D9R2F-L1-GP

R23 54D9R2F-L1-GP

1 2

DY

DY

A

H_PWRGOOD

H_THERMTRIP#

EC_CPU_PROCHOT#

H_FERR#

ITP_BPM#4

H_D#[63..0] 7

H_A#[35..3] 7

H_REQ#[4..0] 7

H_RS#[2..0] 7

H1

E2

G5

H5

F21

E1

F1

BR0#

D20

B3

INIT#

H4

C1

F3

RS0#

F4

RS1#

G3

RS2#

G2

G6

HIT#

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

TCK

AA6

TDI

AB3

TDO

AB5

TMS

AB6

C20

D21

A24

B25

C7

A22

A21

B

H_ADS#

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BR0#

H_IERR#

H_INIT#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

H_HIT#

H_HITM#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_DBRESET#

H_THERMDA

H_THERMDC

H_THERMTRIP#

CLK_CPU_BCLK

CLK_CPU_BCLK#

B

H_ADS# 7

H_BNR# 7

H_BPRI# 7

H_DEFER# 7

H_DRDY# 7

H_DBSY# 7

H_BR0# 7

H_INIT# 16

H_LOCK# 7

H_RESET# 3,7

H_TRDY# 7

H_HIT# 7

H_HITM# 7

ITP_BPM#0 3

ITP_BPM#1 3

ITP_BPM#2 3

ITP_BPM#3 3

ITP_BPM#4 3

ITP_BPM#5 3

ITP_TCK 3

ITP_TDI 3

ITP_TDO 3

ITP_TMS 3

ITP_TRST# 3

ITP_DBRESET# 3,18,34

EC_CPU_PROCHOT# 33

H_THERMTRIP# 20

CLK_CPU_BCLK 4

CLK_CPU_BCLK# 4

layout note:Zo =55

ohm , 0.5" MAX for

GTLREF

+1.05V_VCCP

12

R28

R28

56R2J-4-GP

56R2J-4-GP

H_THERMDA 20

12

C63

C63

SC2200P50V2KX-2GP

SC2200P50V2KX-2GP

DY

DY

H_THERMDC 20

+1.05V_VCCP

12

R34

R34

1KR2F-3-GP

1KR2F-3-GP

V_CPU_GTLREF

12

R33

R33

2KR2F-3-GP

2KR2F-3-GP

PLACE C66 close to the TEST4 PIN,

make sure TEST4 PIN routing is

reference to GND and away from

other noisy signals

http://hobi-elektronika.net

C

R31 1KR2J-1-GP

R31 1KR2J-1-GP

1 2

DY

DY

R298 1KR2J-1-GP

R298 1KR2J-1-GP

1 2

DY

DY

C66 SCD1U10V2KX-4GP

C66 SCD1U10V2KX-4GP

1 2

DY

DY

R299 0R2J-2-GP

R299 0R2J-2-GP

1 2

DY

DY

CPU_MCH_BSEL04,8

CPU_MCH_BSEL14,8

CPU_MCH_BSEL24,8

C

D

2 OF 4

2 OF 4

U76B

U76B

H_D#0

E22

F24

E26

G22

F23

G25

E25

E23

K24

G24

J24

J23

H22

F26

K22

H23

J26

H26

H25

N22

K25

P26

R23

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

T25

N25

L26

M26

N24

AD26

C23

D25

C24

AF26

AF1

A26

B22

B23

C21

SKT-CPU478P-GP

SKT-CPU478P-GP

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

DSTBN0#

DSTBP0#

DINV0#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DSTBN1#

DSTBP1#

DINV1#

GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

BSEL0

BSEL1

BSEL2

D

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#07

H_DSTBP#07

H_DINV#07

H_DSTBN#17

H_DSTBP#17

H_DINV#17

For the purpose of testability,

route thes signals through a ground

referenced Zo=55ohm trace thatends

in a via that is near a GND via

and is accessible through an

oscilloscope connection.

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_DSTBN#1

H_DSTBP#1

H_DINV#1

CPU_MCH_BSEL0

CPU_MCH_BSEL1

CPU_MCH_BSEL2

TP11TPAD28 TP11TPAD28

TP1TPAD28 TP1TPAD28

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

TEST3

TEST5

E

H_D#32

Y22

D32#

D33#

D34#

D35#

DATA GRP0 DATA GRP1

DATA GRP0 DATA GRP1

D36#

D37#

D38#

D39#

D40#

D41#

D42#

DATA GRP2DATA GRP3

DATA GRP2DATA GRP3

D43#

D44#

D45#

D46#

D47#

DSTBN2#

DSTBP2#

DINV2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DSTBN3#

DSTBP3#

DINV3#

COMP0

MISC

MISC

COMP1

COMP2

COMP3

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

H_D#33

AB24

H_D#34

V24

H_D#35

V26

H_D#36

V23

H_D#37

T22

H_D#38

U25

H_D#39

U23

H_D#40

Y25

H_D#41

W22

H_D#42

Y23

H_D#43

W24

H_D#44

W25

H_D#45

AA23

H_D#46

AA24

H_D#47

AB25

H_DSTBN#2

Y26

H_DSTBP#2

AA26

H_DINV#2

U22

H_D#48

AE24

H_D#49

AD24

H_D#50

AA21

H_D#51

AB22

H_D#52

AB21

H_D#53

AC26

H_D#54

AD20

H_D#55

AE22

H_D#56

AF23

H_D#57

AC25

H_D#58

AE21

H_D#59

AD21

H_D#60

AC22

H_D#61

AD23

H_D#62

AF22

H_D#63

AC23

H_DSTBN#3

AE25

H_DSTBP#3

AF24

H_DINV#3

AC20

COMP0

R26

COMP1

U26

COMP2

AA1

COMP3

Y1

H_DPRSTP#

E5

H_DPSLP#

B5

H_DPWR#

D24

H_PWRGOOD

D6

H_CPUSLP#

D7

H_PSI#

AE6

Make COMP[3..0] traces length shorter

than 0.5". Trace should be at least 25

mils away from any other toggling

signal.

COMP 0,2 connect Zo=27.4ohm.

COMP 1,3 connect Zo=55ohm.

H_DSTBN#2 7

H_DSTBP#2 7

H_DINV#2 7

Note:

H_DPRSTP# need to daisy chain

from ICH8 to IMVP6 to CPU

H_DSTBN#3 7

H_DSTBP#3 7

H_DINV#3 7

R297 27D4R2F-L1-GPR297 27D4R2F-L1-GP

1 2

R296 54D9R2F-L1-GPR296 54D9R2F-L1-GP

1 2

R22 27D4R2F-L1-GPR22 27D4R2F-L1-GP

1 2

R24 54D9R2F-L1-GPR24 54D9R2F-L1-GP

1 2

H_DPRSTP# 8,16,42

H_DPSLP# 16

H_DPWR# 7

H_PWRGOOD 16

H_CPUSLP# 7

H_PSI# 42

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU-FSB (1/2)

CPU-FSB (1/2)

CPU-FSB (1/2)

Siberia

Siberia

Siberia

E

A00

A00

A00

of

of

of

550Monday, July 16, 2007

550Monday, July 16, 2007

550Monday, July 16, 2007

A

B

C

D

E

4 4

A11

A14

A16

A19

A23

AF2

B11

B13

B16

B19

B21

B24

C11

C14

C16

C19

C22

3 3

2 2

1 1

C25

D11

D13

D16

D19

D23

D26

E11

E14

E16

E19

E21

E24

F11

F13

F16

F19

F22

F25

G4

G1

G23

G26

H21

H24

J22

J25

K23

K26

L21

L24

M2

M5

M22

M25

N23

N26

A

U76D

U76D

A4

VSS

A8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B6

VSS

B8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C5

VSS

C8

VSS

VSS

VSS

VSS

VSS

C2

VSS

VSS

VSS

D1

VSS

D4

VSS

D8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E3

VSS

E6

VSS

E8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F5

VSS

F8

VSS

VSS

VSS

VSS

VSS

F2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H3

VSS

H6

VSS

VSS

VSS

J2

VSS

J5

VSS

VSS

VSS

K1

VSS

K4

VSS

VSS

VSS

L3

VSS

L6

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N1

VSS

N4

VSS

VSS

VSS

P3

VSS

SKT-CPU478P-GP

SKT-CPU478P-GP

4 OF 4

4 OF 4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

TP131 TPAD28TP131 TPAD28

TP132 TPAD28TP132 TPAD28

TP134 TPAD28TP134 TPAD28

TP133 TPAD28TP133 TPAD28

12

C43

C43

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

C47

C47

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

C503

C503

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

C44

C44

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

C37

C37

SCD1U10V2KX-4GP

+PWR_SRC

12

SCD1U10V2KX-4GP

TC27

TC27

SE100U25VM-14GP

SE100U25VM-14GP

Please these inside socket cavity on L8 ( North side Secondary )

Need to add 100uF cap on PWR_SRC for cap singing.

Please this capacitor near +VCC_CORE

B

12

12

C45

C45

C505

C505

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

12

C53

C53

C490

C490

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

12

C501

C501

C498

C498

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

12

C52

C52

C49

C49

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

10uF 0805 X5R -> 85 degree C ,

Or better such As X6S and X7R

+1.05V_VCCP

12

12

C35

C35

C58

C58

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

TC28

TC28

SE100U25VM-14GP

SE100U25VM-14GP

12

12

12

12

12

C488

C488

C491

C491

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

C495

C495

C502

C502

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

C50

C50

C54

C54

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

C504

C504

C493

C493

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

12

C36

C36

C60

C60

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

TC30

TC30

http://hobi-elektronika.net

12

12

C51

C51

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

12

C492

C492

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

12

C500

C500

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

12

C57

C57

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

12

C59

C59

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

SE100U25VM-14GP

SE100U25VM-14GP

C

12

C48

C48

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

C56

C56

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

C38

C38

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

C497

C497

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

TC1

TC1

SE220U2VDM-8GP

SE220U2VDM-8GP

C489

C489

C55

C55

C46

C46

C494

C494

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

+VCC_CORE +VCC_CORE

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AC10

AB10

AB12

AB14

AB15

AB17

AB18

U76C

U76C

A7

VCC

A9

VCC

A10

VCC

A12

VCC

A13

VCC

A15

VCC

A17

VCC

A18

VCC

A20

VCC

B7

VCC

B9

VCC

B10

VCC

B12

VCC

B14

VCC

B15

VCC

B17

VCC

B18

VCC

B20

VCC

C9

VCC

C10

VCC

C12

VCC

C13

VCC

C15

VCC

C17

VCC

C18

VCC

D9

VCC

D10

VCC

D12

VCC

D14

VCC

D15

VCC

D17

VCC

D18

VCC

E7

VCC

E9

VCC

E10

VCC

E12

VCC

E13

VCC

E15

VCC

E17

VCC

E18

VCC

E20

VCC

F7

VCC

F9

VCC

F10

VCC

F12

VCC

F14

VCC

F15

VCC

F17

VCC

F18

VCC

F20

VCC

AA7

VCC

AA9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AB9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SKT-CPU478P-GP

SKT-CPU478P-GP

3 OF 4

3 OF 4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCA

VCCA

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VCCSENSE

VSSSENSE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AF7

AE7

D

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

VCCSENSE

VSSSENSE

VCCSENSE

VSSSENSE

+1.05V_VCCP

+1.5V_RUN

H_VID[6..0] 42

VCCSENSE 42

VSSSENSE 42

R26

R26

1 2

100R2F-L1-GP-U

100R2F-L1-GP-U

R27

R27

1 2

100R2F-L1-GP-U

100R2F-L1-GP-U

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet

Date: Sheet

12

C507

C507

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

Layout note:

Place R26 and R27 within 1" of CPU.

Routing VCC_SENSE and VSS_SENSE at

27.4 ohms with 50 mils spacing.

+VCC_CORE

CPU-POWER (2/2)

CPU-POWER (2/2)

CPU-POWER (2/2)

Siberia

Siberia

Siberia

Layout note:

Place C507 near

PIN B26

12

C508

C508

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

650Monday, July 16, 2007

650Monday, July 16, 2007

650Monday, July 16, 2007

E

A00

A00

A00

of

of

A

B

C

D

E

H_D#[63..0]

H_A#[35..3]

H_REQ#[4..0]

H_RS#[2..0]

4 4

3 3

2 2

H_REF Decoupling Crestline

close Crestline 100 mil

+1.05V_VCCP

12

R49

R49

1KR2F-3-GP

1KR2F-3-GP

12

R48

R48

2KR2F-3-GP

1 1

2KR2F-3-GP

H_D#[63..0] 5

H_A#[35..3] 5

H_REQ#[4..0] 5

H_RS#[2..0] 5

12

C71

C71

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

1 OF 10

1 OF 10

U84A

U84A

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

H_SCOMP

H_SCOMP#

H_RESET#3,5

H_CPUSLP#5

H_RESET#

H_CPUSLP#

H_REF

E2

H_D#0

G2

H_D#1

G7

H_D#2

M6

H_D#3

H7

H_D#4

H3

H_D#5

G4

H_D#6

F3

H_D#7

N8

H_D#8

H2

H_D#9

M10

H_D#10

N12

H_D#11

N9

H_D#12

H5

H_D#13

P13

H_D#14

K9

H_D#15

M2

H_D#16

W10

H_D#17

Y8

H_D#18

V4

H_D#19

M3

H_D#20

J1

H_D#21

N5

H_D#22

N3

H_D#23

W6

H_D#24

W9

H_D#25

N2

H_D#26

Y7

H_D#27

Y9

H_D#28

P4

H_D#29

W3

H_D#30

N1

H_D#31

AD12

H_D#32

AE3

H_D#33

AD9

H_D#34

AC9

H_D#35

AC7

H_D#36

AC14

H_D#37

AD11

H_D#38

AC11

H_D#39

AB2

H_D#40

AD7

H_D#41

AB1

H_D#42

Y3

H_D#43

AC6

H_D#44

AE2

H_D#45

AC5

H_D#46

AG3

H_D#47

AJ9

H_D#48

AH8

H_D#49

AJ14

H_D#50

AE9

H_D#51

AE11

H_D#52

AH12

H_D#53

AJ5

H_D#54

AH5

H_D#55

AJ6

H_D#56

AE7

H_D#57

AJ7

H_D#58

AJ2

H_D#59

AE5

H_D#60

AJ3

H_D#61

AH2

H_D#62

AH13

H_D#63

B3

H_SWING

C2

H_RCOMP

W1

H_SCOMP

W2

H_SCOMP#

B6

H_CPURST#

E5

H_CPUSLP#

B9

H_AVREF

A9

H_DVREF

CRESTLINE-GP-U-NF

CRESTLINE-GP-U-NF

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR#

HOST

HOST

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_HIT#

J13

B11

C11

M11

C15

F16

L13

G17

C14

K16

B13

L16

J17

B14

K19

P15

R17

B16

H20

L19

D17

M17

N16

J19

B18

E19

B17

B15

E17

C18

A19

B19

N19

H_ADS#

G12

H_ADSTB#0

H17

H_ADSTB#1

G20

H_BNR#

C8

H_BPRI#

E8

H_BR0#

F12

H_DEFER#

D6

H_DBSY#

C10

CLK_MCH_BCLK

AM5

CLK_MCH_BCLK#

AM7

H_DPWR#

H8

H_DRDY#

K7

E4

C6

H_LOCK#

G10

H_TRDY#

B7

H_DINV#0

K5

H_DINV#1

L2

H_DINV#2

AD13

H_DINV#3

AE13

H_DSTBN#0

M7

H_DSTBN#1

K3

H_DSTBN#2

AD2

H_DSTBN#3

AH11

H_DSTBP#0

L7

H_DSTBP#1

K2

H_DSTBP#2

AC2

H_DSTBP#3

AJ10

M14

E13

A11

H13

B12

E12

D7

D8

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_HIT#

H_HITM#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_ADS# 5

H_ADSTB#0 5

H_ADSTB#1 5

H_BNR# 5

H_BPRI# 5

H_BR0# 5

H_DEFER# 5

H_DBSY# 5

CLK_MCH_BCLK 4

CLK_MCH_BCLK# 4

H_DPWR# 5

H_DRDY# 5

H_HIT# 5

H_HITM# 5

H_LOCK# 5

H_TRDY# 5

H_DINV#0 5

H_DINV#1 5

H_DINV#2 5

H_DINV#3 5

H_DSTBN#0 5

H_DSTBN#1 5

H_DSTBN#2 5

H_DSTBN#3 5

H_DSTBP#0 5

H_DSTBP#1 5

H_DSTBP#2 5

H_DSTBP#3 5

H_SWING routing Trace width and

Spacing use 10 / 20 mil

H_SWING Resistors and

Capacitors close

Caliistoga 500 mil ( MAX )

From Schematic Design

Checklit v.1201

221 1% pull high 100

1% pull low

H_SCOMP and H_SCOMP# Resistors

and Capacitors close Caliistoga

500 mil ( MAX )

Zo=55ohms

+1.05V_VCCP

1 2

54D9R2F-L1-GP

54D9R2F-L1-GP

R74

R74

+1.05V_VCCP

1 2

54D9R2F-L1-GP

54D9R2F-L1-GP

R77

R77

H_RCOMP routing Trace width and

Spacing use 10 / 20 mil

1 2

24D9R2F-L-GP

24D9R2F-L-GP

R353

R353

<Core Design>

<Core Design>

<Core Design>

H_SWING

12

C548

C548

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

H_SCOMP

H_SCOMP#

H_RCOMP

+1.05V_VCCP

12

R344

R344

221R2F-2-GP

221R2F-2-GP

12

R343

R343

100R2F-L1-GP-U

100R2F-L1-GP-U

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

CRB v0.9 REQUEST

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A

B

http://hobi-elektronika.net

C

D

A3

Date: Sheet

Date: Sheet

Date: Sheet

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

GMCH-FSB LIBC (1/6)

GMCH-FSB LIBC (1/6)

GMCH-FSB LIBC (1/6)

Siberia

Siberia

Siberia

750Monday, July 16, 2007

750Monday, July 16, 2007

750Monday, July 16, 2007

E

A00

A00

A00

of

of

of

A

2 OF 10

2 OF 10

U84B

U84B

P36

RSVD#P36

P37

RSVD#P37

R35

RSVD#R35

N35

RSVD#N35

AR12

RSVD#AR12

AR13

RSVD#AR13

AM12

RSVD#AM12

AN13

RSVD#AN13

J12

RSVD#J12

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

AR37

AM36

AL36

AM37

BJ20

BK22

BF19

BH20

BK18

BJ18

BF23

BG23

BC23

BD24

BH39

AW20

BK20

G23

M20

M24

G41

AW49

AV20

G36

BJ51

BK51

BK50

BL50

BL49

BK1

BK2

D20

H10

B51

B44

C44

A35

B37

B36

B34

C34

P27

N27

N24

C21

C23

F23

N23

C20

R24

L23

E23

E20

K23

L32

N33

L35

L39

L36

N20

BL3

BL2

BJ1

C51

B50

A50

A49

J20

J23

J36

RSVD#AR37

RSVD#AM36

RSVD#AL36

RSVD#AM37

RSVD#D20

RSVD#H10

RSVD#B51

RSVD#BJ20

RSVD#BK22

RSVD#BF19

RSVD#BH20

RSVD#BK18

RSVD#BJ18

RSVD#BF23

RSVD#BG23

RSVD#BC23

RSVD#BD24

RSVD#BH39

RSVD#AW20

RSVD#BK20

RSVD#B44

RSVD#C44

RSVD#A35

RSVD#B37

RSVD#B36

RSVD#B34

RSVD#C34

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

PM_BM_BUSY#

PM_DPRSTP#

PM_EXT_TS#0

PM_EXT_TS#1

PWROK

RSTIN#

THERMTRIP#

DPRSLPVR

NC#BJ51

NC#BK51

NC#BK50

NC#BL50

NC#BL49

NC#BL3

NC#BL2

NC#BK1

NC#BJ1

E1

NC#E1

A5

NC#A5

NC#C51

NC#B50

NC#A50

NC#A49

NC#BK2

RSVD

RSVD

CFG PM NC

CFG PM NC

DPRSLPVR_R

SB_NB_PCIE_RST#

SB_NB_PCIE_RST#

SM_RCOMP_VOH

SM_RCOMP_VOL

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

CLK

CLK

SDVO_CTRL_CLK

SDVO_CTRL_DATA

4 4

+1.05V_VCCP

12

R72

R72

56R2J-4-GP

56R2J-4-GP

3 3

2 2

1 1

THERMTRIP_MCH#

+3.3V_RUN

R338 10KR2J-3-GPR338 10KR2J-3-GP

1 2

R339 10KR2J-3-GPR339 10KR2J-3-GP

1 2

CPU_MCH_BSEL04,5

CPU_MCH_BSEL14,5

CPU_MCH_BSEL24,5

CFG[2..0] FSB

Select

010 = FSB 800

011 = FSB 667

Other = Reserved

PM_BMBUSY#18

H_DPRSTP#5,16,42

PM_EXTTS#013

PM_EXTTS#114

ICH_PWRGD18,39

THERMTRIP_MCH#20

DPRSLPVR18,42

PLTRST#18,27,29,30,31,33

GPIO4_PIRQG#18

PM_EXTTS#0

PM_EXTTS#1

CPU_MCH_BSEL0

CPU_MCH_BSEL1

CPU_MCH_BSEL2

TP20TP20

TP52TP52

CFG512

TP32TP32

TP24TP24

TP22TP22

CFG912

TP34TP34

TP27TP27

TP23TP23

TP19TP19

TP21TP21

TP28TP28

CFG1612

TP31TP31

TP29TP29

CFG1912

CFG2012

PM_BMBUSY#

H_DPRSTP#

PM_EXTTS#0

PM_EXTTS#1

ICH_PWRGD

SB_NB_PCIE_RST#

THERMTRIP_MCH#

DPRSLPVR_R

R336 0R2J-2-GPR336 0R2J-2-GP

1 2

R97 100R2F-L1-GP-UR97 100R2F-L1-GP-U

1 2

R96 0R2J-2-GP

R96 0R2J-2-GP

1 2

DY

DY

A

B

AV29

SM_CK0

BB23

SM_CK1

BA25

SM_CK3

AV23

SM_CK4

AW30

SM_CK#0

BA23

SM_CK#1

AW25

SM_CK#3

AW23

SM_CK#4

BE29

SM_CKE0

AY32

SM_CKE1

BD39

SM_CKE3

BG37

SM_CKE4

BG20

SM_CS#0

BK16

SM_CS#1

BG16

SM_CS#2

BE13

SM_CS#3

DDR MUXING

DDR MUXING

SM_RCOMP

SM_RCOMP#

SM_VREF#AR49

SM_VREF#AW4

DPLL_REF_CLK

DPLL_REF_CLK#

PEG_CLK#

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI

DMI

GFX_VR_EN

CL_PWROK

ICH_SYNC#

MISC ME GRAPHICS VID

MISC ME GRAPHICS VID

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

PEG_CLK

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VID3

CL_CLK

CL_DATA

CL_RST#

CL_VREF

CLKREQ#

TEST1

TEST2

BH18

BJ15

BJ14

BE16

BK31

BL31

BL15

BK14

AR49

AW4

B42

C42

H48

H47

K44

K45

AN47

AJ38

AN42

AN46

AM47

AJ39

AN41

AN45

AJ46

AJ41

AM40

AM44

AJ47

AJ42

AM39

AM43

E35

A39

C38

B39

E36

AM49

AK50

AT43

AN49

AM50

H35

K36

G39

G40

A37

R32

B

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR2

M_CLK_DDR3

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#2

M_CLK_DDR#3

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

M_ODT0

M_ODT1

M_ODT2

M_ODT3

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_RCOMP

SM_RCOMP#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

DMI_MRX_ITX_N0

DMI_MRX_ITX_N1

DMI_MRX_ITX_N2

DMI_MRX_ITX_N3

DMI_MRX_ITX_P0

DMI_MRX_ITX_P1

DMI_MRX_ITX_P2

DMI_MRX_ITX_P3

DMI_MTX_IRX_N0

DMI_MTX_IRX_N1

DMI_MTX_IRX_N2

DMI_MTX_IRX_N3

DMI_MTX_IRX_P0

DMI_MTX_IRX_P1

DMI_MTX_IRX_P2

DMI_MTX_IRX_P3

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VID3

GFX_VR_EN

Layout Note:

MCH_CLVREF ~= 0.350V

Width/Spacing = 12/12

MCH_CLVREF

CLK_3GPLLREQ#

MCH_ICH_SYNC#

TEST1_GMCH

TEST2_GMCH

12

R64

R64

20KR2J-L2-GP

20KR2J-L2-GP

CLK_MCH_3GPLL 4

CLK_MCH_3GPLL# 4

DMI_MRX_ITX_N0 17

DMI_MRX_ITX_N1 17

DMI_MRX_ITX_N2 17

DMI_MRX_ITX_N3 17

DMI_MRX_ITX_P0 17

DMI_MRX_ITX_P1 17

DMI_MRX_ITX_P2 17

DMI_MRX_ITX_P3 17

DMI_MTX_IRX_N0 17

DMI_MTX_IRX_N1 17

DMI_MTX_IRX_N2 17

DMI_MTX_IRX_N3 17

DMI_MTX_IRX_P0 17

DMI_MTX_IRX_P1 17

DMI_MTX_IRX_P2 17

DMI_MTX_IRX_P3 17

TP17TP17

TP15TP15

TP18TP18

TP14TP14

TP16TP16

TP33TP33

C

CLOSE PIN BL15 BK14

M_CLK_DDR0 13

M_CLK_DDR1 13

M_CLK_DDR2 14

M_CLK_DDR3 14

M_CLK_DDR#0 13

M_CLK_DDR#1 13

M_CLK_DDR#2 14

M_CLK_DDR#3 14

DDR_CKE0_DIMMA 13

DDR_CKE1_DIMMA 13

DDR_CKE2_DIMMB 14

DDR_CKE3_DIMMB 13,14

DDR_CS0_DIMMA# 13

DDR_CS1_DIMMA# 13

DDR_CS2_DIMMB# 14

DDR_CS3_DIMMB# 14

M_ODT0 13

M_ODT1 13

M_ODT2 14

M_ODT3 14

CL_CLK0 18

CL_DATA0 18

ICH_CL_PWROK 18,33

ICH_CL_RST0# 18

CLK_3GPLLREQ# 4

MCH_ICH_SYNC# 18

TP53TP53

R341

R341

0R2J-2-GP

0R2J-2-GP

1 2

http://hobi-elektronika.net

R95

R95

1 2

DY

DY

R90

R90

1 2

DY

DY

SM_RCOMP

SM_RCOMP#

10KR2F-2-GP

10KR2F-2-GP

10KR2F-2-GP

10KR2F-2-GP

C630

C630

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

C

R517

R517

1 2

R516

R516

1 2

+1.8V_SUS

V_DDR_MCH_REF

+1.25V_RUN

12

12

12

20R2F-GP

20R2F-GP

20R2F-GP

20R2F-GP

R441

R441

1KR2F-3-GP

1KR2F-3-GP

R442

R442

392R2F-GP

392R2F-GP

+1.8V_SUS

+1.8V_SUS

R124

R124

1KR2F-3-GP

1KR2F-3-GP

1 2

12

R132

R132

3K01R2F-3-GP

3K01R2F-3-GP

R125

R125

1KR2F-3-GP

1KR2F-3-GP

1 2

H39

E39

E40

C37

D35

K40

N41

N40

D46

C45

D44

E42

G51

E51

F49

C48

G50

E50

F48

D47

G44

B47

B45

E44

A47

A45

E27

G27

K27

F27

M35

P33

H32

G32

K29

F29

E29

K33

G35

E33

C32

F33

U84C

U84C

J40

L41

L43

J27

L27

J29

L_BKLT_CTRL

L_BKLT_EN

L_CTRL_CLK

L_CTRL_DATA

L_DDC_CLK

L_DDC_DATA

L_VDD_EN

LVDS_IBG

LVDS_VBG

LVDS_VREFH

LVDS_VREFL

LVDSA_CLK#

LVDSA_CLK

LVDSB_CLK#

LVDSB_CLK

LVDSA_DATA#0

LVDSA_DATA#1

LVDSA_DATA#2

LVDSA_DATA#3

LVDSA_DATA0

LVDSA_DATA1

LVDSA_DATA2

LVDSA_DATA3

LVDSB_DATA#0

LVDSB_DATA#1

LVDSB_DATA#2

LVDSB_DATA0

LVDSB_DATA1

LVDSB_DATA2

TVA_DAC

TVB_DAC

TVC_DAC

TVA_RTN

TVB_RTN

TVC_RTN

TV_DCONSEL0

TV_DCONSEL1

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_VSYNC

CRT_TVO_IREF

CRT_HSYNC

3 OF 10

3 OF 10

12

C180

C180

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

12

C181

C181

SCD01U16V2KX-3GP

SCD01U16V2KX-3GP

D

LVDS

LVDS

TV

TV

PCI_EXPRESS GRAPHICS

PCI_EXPRESS GRAPHICS

VGA

VGA

12

SM_RCOMP_VOL

12

D

+VCC_PEG

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX#8

PEG_RX#9

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX#8

PEG_TX#9

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

N43

M43

J51

L51

N47

T45

T50

U40

Y44

Y40

AB51

W49

AD44

AD40

AG46

AH49

AG45

AG41

J50

L50

M47

U44

T49

T41

W45

W41

AB50

Y48

AC45

AC41

AH47

AG49

AH45

AG42

N45

U39

U47

N51

R50

T42

Y43

W46

W38

AD39

AC46

AC49

AC42

AH39

AE49

AH44

M45

T38

T46

N50

R51

U43

W42

Y47

Y39

AC38

AD47

AC50

AD43

AG39

AE50

AH43

PEG_COMPI

PEG_COMPO

PEG_RX#10

PEG_RX#11

PEG_RX#12

PEG_RX#13

PEG_RX#14

PEG_RX#15

PEG_TX#10

PEG_TX#11

PEG_TX#12

PEG_TX#13

PEG_TX#14

PEG_TX#15

SM_RCOMP_VOH

C184

C184

SC2D2U6D3V3MX-1-GP

SC2D2U6D3V3MX-1-GP

C185

C185

SC2D2U6D3V3MX-1-GP

SC2D2U6D3V3MX-1-GP

E

R62

R62

1 2

24D9R2F-L-GP

24D9R2F-L-GP

PEG_COMP_GMCH

PCIE_MRX_GTX_N0

PCIE_MRX_GTX_N1

PCIE_MRX_GTX_N2

PCIE_MRX_GTX_N3

PCIE_MRX_GTX_N4

PCIE_MRX_GTX_N5

PCIE_MRX_GTX_N6

PCIE_MRX_GTX_N7

PCIE_MRX_GTX_N8

PCIE_MRX_GTX_N9

PCIE_MRX_GTX_N10

PCIE_MRX_GTX_N11

PCIE_MRX_GTX_N12

PCIE_MRX_GTX_N13

PCIE_MRX_GTX_N14

PCIE_MRX_GTX_N15

PCIE_MRX_GTX_P0

PCIE_MRX_GTX_P1

PCIE_MRX_GTX_P2

PCIE_MRX_GTX_P3

PCIE_MRX_GTX_P4

PCIE_MRX_GTX_P5

PCIE_MRX_GTX_P6

PCIE_MRX_GTX_P7

PCIE_MRX_GTX_P8

PCIE_MRX_GTX_P9

PCIE_MRX_GTX_P10

PCIE_MRX_GTX_P11

PCIE_MRX_GTX_P12

PCIE_MRX_GTX_P13

PCIE_MRX_GTX_P14

PCIE_MRX_GTX_P15

PCIE_MTX_GRX_C_N0 PCIE_MTX_GRX_N0

PCIE_MTX_GRX_C_N3 PCIE_MTX_GRX_N3

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet

Date: Sheet

GMCH-LVDS/VGA/DMI/DDR (2/6)

GMCH-LVDS/VGA/DMI/DDR (2/6)

GMCH-LVDS/VGA/DMI/DDR (2/6)

PCIE_MRX_GTX_N[15..0] 15

PCIE_MRX_GTX_P[15..0] 15

PCIE_MTX_GRX_N[15..0] 15

PCIE_MTX_GRX_P[15..0] 15

C524 SCD1U10V2KX-4GPC524 SCD1U10V2KX-4GP

1 2

C567 SCD1U10V2KX-4GPC567 SCD1U10V2KX-4GP

1 2

C526 SCD1U10V2KX-4GPC526 SCD1U10V2KX-4GP

1 2

C557 SCD1U10V2KX-4GPC557 SCD1U10V2KX-4GP

1 2

C528 SCD1U10V2KX-4GPC528 SCD1U10V2KX-4GP

1 2

C559 SCD1U10V2KX-4GPC559 SCD1U10V2KX-4GP

1 2

C522 SCD1U10V2KX-4GPC522 SCD1U10V2KX-4GP

1 2

C561 SCD1U10V2KX-4GPC561 SCD1U10V2KX-4GP

1 2

C530 SCD1U10V2KX-4GPC530 SCD1U10V2KX-4GP

1 2

C555 SCD1U10V2KX-4GPC555 SCD1U10V2KX-4GP

1 2

C538 SCD1U10V2KX-4GPC538 SCD1U10V2KX-4GP

1 2

C563 SCD1U10V2KX-4GPC563 SCD1U10V2KX-4GP

1 2

C565 SCD1U10V2KX-4GPC565 SCD1U10V2KX-4GP

1 2

C532 SCD1U10V2KX-4GPC532 SCD1U10V2KX-4GP

1 2

C534 SCD1U10V2KX-4GPC534 SCD1U10V2KX-4GP

1 2

C536 SCD1U10V2KX-4GPC536 SCD1U10V2KX-4GP

1 2

C523 SCD1U10V2KX-4GPC523 SCD1U10V2KX-4GP

1 2

C566 SCD1U10V2KX-4GPC566 SCD1U10V2KX-4GP

1 2

C525 SCD1U10V2KX-4GPC525 SCD1U10V2KX-4GP

1 2

C556 SCD1U10V2KX-4GPC556 SCD1U10V2KX-4GP

1 2

C527 SCD1U10V2KX-4GPC527 SCD1U10V2KX-4GP

1 2

C558 SCD1U10V2KX-4GPC558 SCD1U10V2KX-4GP

1 2

C521 SCD1U10V2KX-4GPC521 SCD1U10V2KX-4GP

1 2

C560 SCD1U10V2KX-4GPC560 SCD1U10V2KX-4GP

1 2

C529 SCD1U10V2KX-4GPC529 SCD1U10V2KX-4GP

1 2

C554 SCD1U10V2KX-4GPC554 SCD1U10V2KX-4GP

1 2

C537 SCD1U10V2KX-4GPC537 SCD1U10V2KX-4GP

1 2

C562 SCD1U10V2KX-4GPC562 SCD1U10V2KX-4GP

1 2

C564 SCD1U10V2KX-4GPC564 SCD1U10V2KX-4GP

1 2

C531 SCD1U10V2KX-4GPC531 SCD1U10V2KX-4GP

1 2

C533 SCD1U10V2KX-4GPC533 SCD1U10V2KX-4GP

1 2

C535 SCD1U10V2KX-4GPC535 SCD1U10V2KX-4GP

1 2

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Siberia

Siberia

Siberia

E

PCIE_MTX_GRX_N1PCIE_MTX_GRX_C_N1

PCIE_MTX_GRX_N2PCIE_MTX_GRX_C_N2

PCIE_MTX_GRX_N4PCIE_MTX_GRX_C_N4

PCIE_MTX_GRX_N5PCIE_MTX_GRX_C_N5

PCIE_MTX_GRX_N6PCIE_MTX_GRX_C_N6

PCIE_MTX_GRX_N7PCIE_MTX_GRX_C_N7

PCIE_MTX_GRX_N8PCIE_MTX_GRX_C_N8

PCIE_MTX_GRX_N9PCIE_MTX_GRX_C_N9

PCIE_MTX_GRX_N10PCIE_MTX_GRX_C_N10

PCIE_MTX_GRX_N11PCIE_MTX_GRX_C_N11

PCIE_MTX_GRX_N12PCIE_MTX_GRX_C_N12

PCIE_MTX_GRX_N13PCIE_MTX_GRX_C_N13

PCIE_MTX_GRX_N14PCIE_MTX_GRX_C_N14

PCIE_MTX_GRX_N15PCIE_MTX_GRX_C_N15

PCIE_MTX_GRX_P0PCIE_MTX_GRX_C_P0

PCIE_MTX_GRX_P1PCIE_MTX_GRX_C_P1

PCIE_MTX_GRX_P2PCIE_MTX_GRX_C_P2

PCIE_MTX_GRX_P3PCIE_MTX_GRX_C_P3

PCIE_MTX_GRX_P4PCIE_MTX_GRX_C_P4

PCIE_MTX_GRX_P5PCIE_MTX_GRX_C_P5

PCIE_MTX_GRX_P6PCIE_MTX_GRX_C_P6

PCIE_MTX_GRX_P7PCIE_MTX_GRX_C_P7

PCIE_MTX_GRX_P8PCIE_MTX_GRX_C_P8

PCIE_MTX_GRX_P9PCIE_MTX_GRX_C_P9

PCIE_MTX_GRX_P10PCIE_MTX_GRX_C_P10

PCIE_MTX_GRX_P11PCIE_MTX_GRX_C_P11

PCIE_MTX_GRX_P12PCIE_MTX_GRX_C_P12

PCIE_MTX_GRX_P13PCIE_MTX_GRX_C_P13

PCIE_MTX_GRX_P14PCIE_MTX_GRX_C_P14

PCIE_MTX_GRX_P15PCIE_MTX_GRX_C_P15

A00

A00

A00

of

of

850Monday, July 16, 2007

850Monday, July 16, 2007

850Monday, July 16, 2007

A

B

C

D

E

U84D

U84D

AR43

SA_DQ0

AW44

SA_DQ1

BA45

SA_DQ2

AY46

SA_DQ3

AR41

SA_DQ4

AR45

SA_DQ5

AT42

SA_DQ6

AW47

SA_DQ7

BB45

SA_DQ8

BF48

SA_DQ9

BG47

SA_DQ10

BJ45

SA_DQ11

BB47

SA_DQ12

BG50

SA_DQ13

BH49

SA_DQ14

BE45

SA_DQ15

AW43

SA_DQ16

BE44

SA_DQ17

BG42

SA_DQ18

BE40

SA_DQ19

BF44

SA_DQ20

BH45

SA_DQ21

BG40

SA_DQ22

BF40

SA_DQ23

AR40

SA_DQ24

AW40

SA_DQ25

AT39

SA_DQ26

AW36

SA_DQ27

AW41

SA_DQ28

AY41

SA_DQ29

AV38

SA_DQ30

AT38

SA_DQ31

AV13

SA_DQ32

AT13

SA_DQ33

AW11