Dell XPS 13 9370 boardview

A

B

C

D

E

MODEL NAME :

PCB NO :

BOM P/N :

ZZZ

1 1

MB_PCB

LA-E671P

43xxxxx

CAZ60

Dell/Compal Confidential

2 2

Schematic Document

Italia

@ : N o p o p C o m p o n e n t

@ C O N N @ : R e s e r v e C o n n e c t o r C o m p o n e n t

3 3

2017-09-15

@ E M C @ : R e s e r v e E M C C o m p o n e n t

C O N N @ : C o n n e c t o r C o m p o n e n t

Rev: 1.0 ( A00 )

X P S @ : f o r I t a l i a

L @ : f o r I t a l i a - L

R F @ : R F S o l u t i o n C o m p o n e n t

X D P @ : X D P D e b u g C o m p o n e n t

E M C @ : E M C C o m p o n e n t

U 2 2 @ : U 2 2 C P U S u p p o r t

U 2 3 @ : U 2 3 C P U S u p p o r t

U 4 2 @ : U 4 2 C P U S u p p o r t

4 4

U 2 2 U 2 3 @ : U 2 2 a n d U 2 3 C P U S u p p o r t

D E B U G @ : f o r O t h e r D e b u g

6 5 0 @ : T P M

7 5 0 @ : T P M

D C I @ : f o r D C I D e b u g

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2016/12/16 2016/12/13

2016/12/16 2016/12/13

2016/12/16 2016/12/13

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

DELL CONFIDENTIAL/PROPRIETARY

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

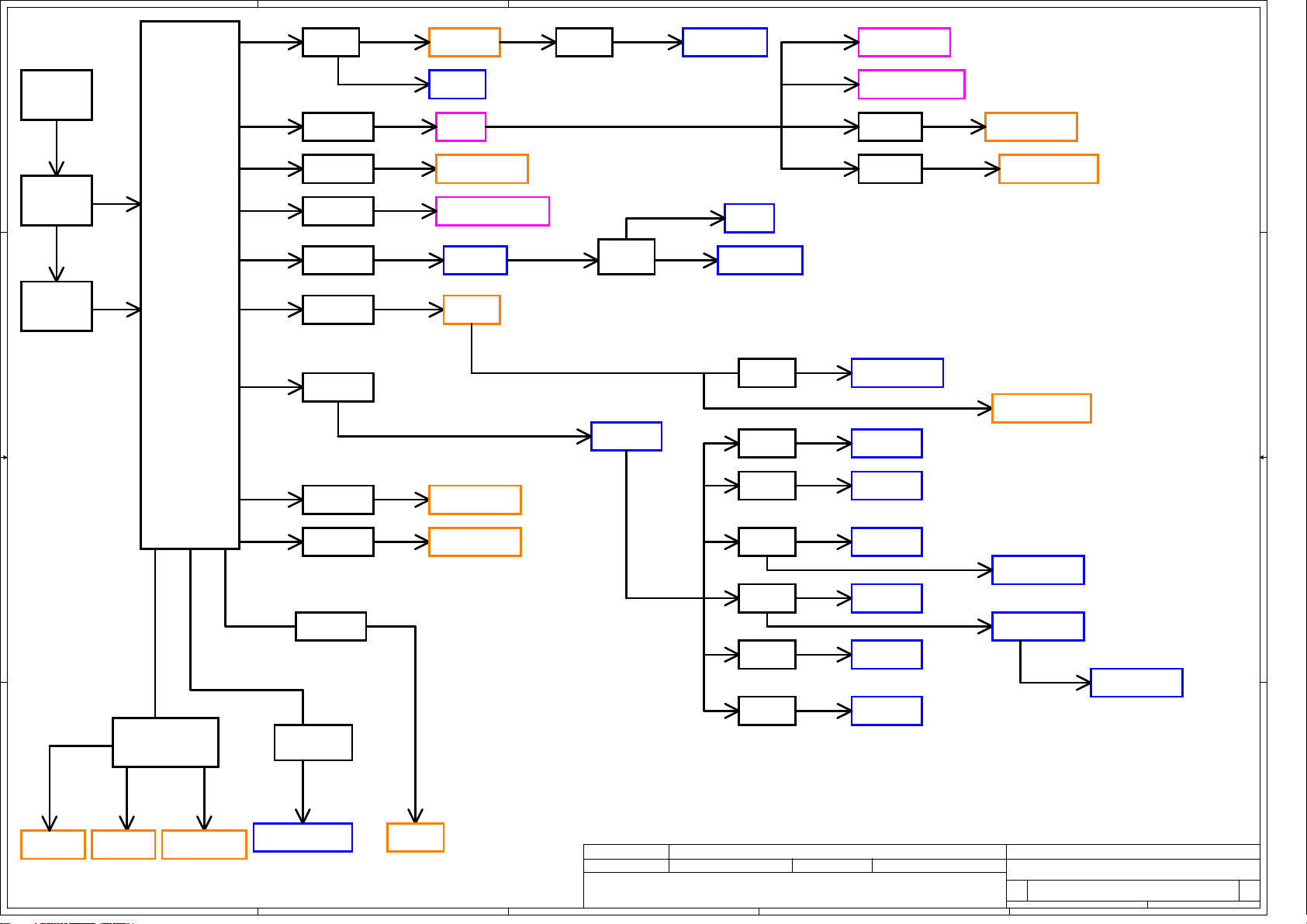

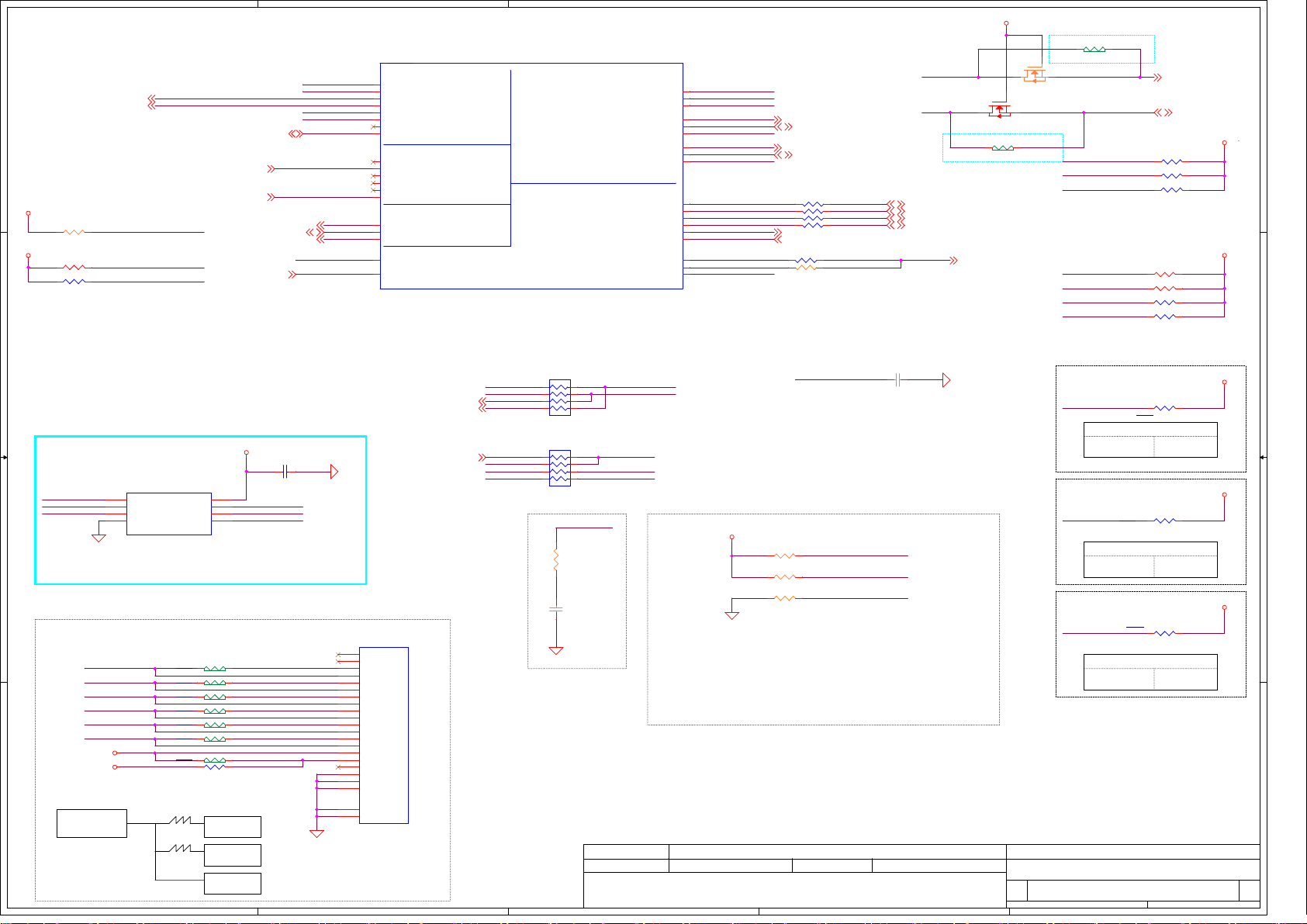

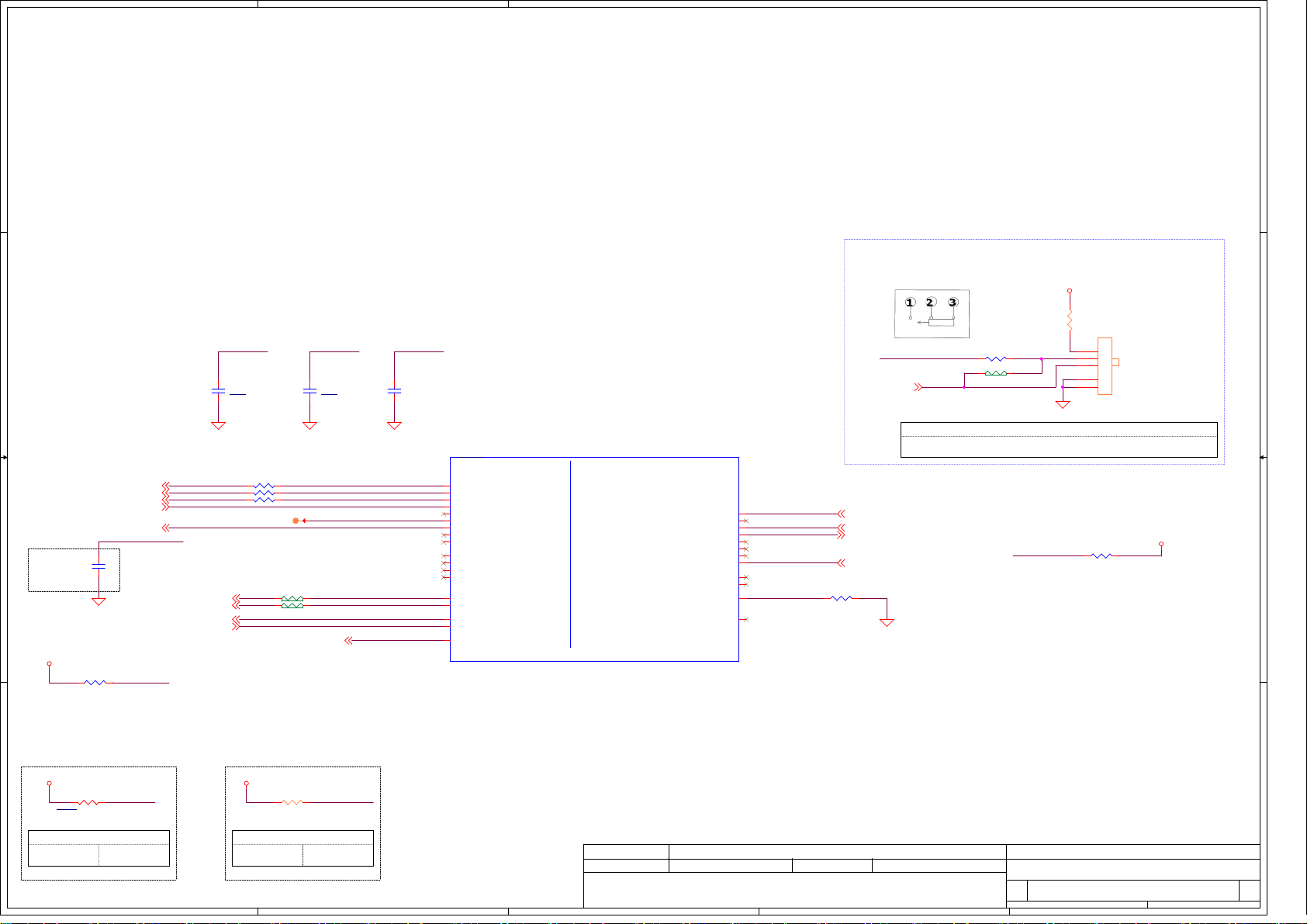

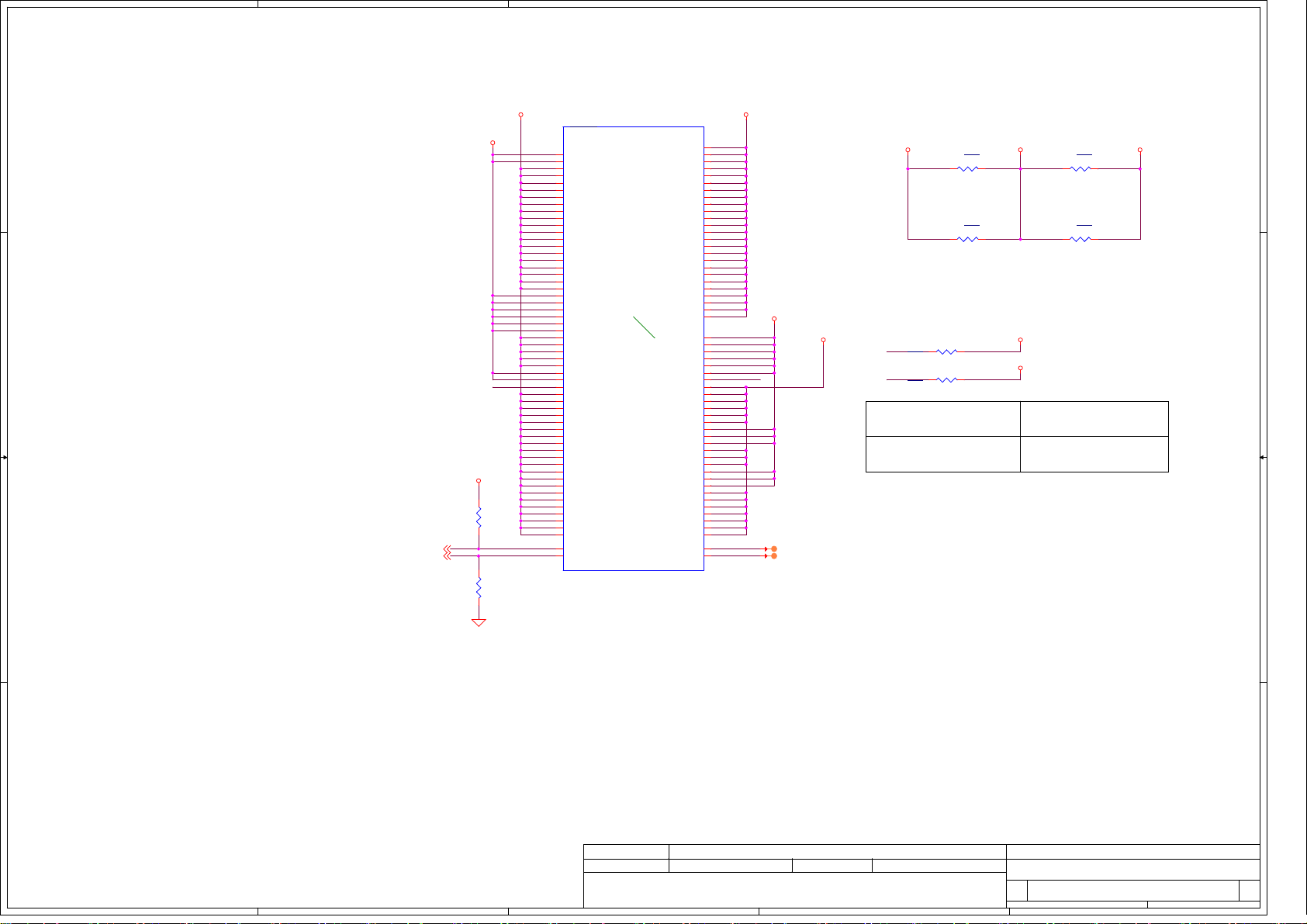

P01-Cover Page

P01-Cover Page

P01-Cover Page

Document Number Re v

Document Number Re v

Document Number Re v

LA-E671P

LA-E671P

LA-E671P

E

1 61Tuesday, October 17, 2017

1 61Tuesday, October 17, 2017

1 61Tuesday, October 17, 2017

1.0

1.0

1.0

A

B

C

D

E

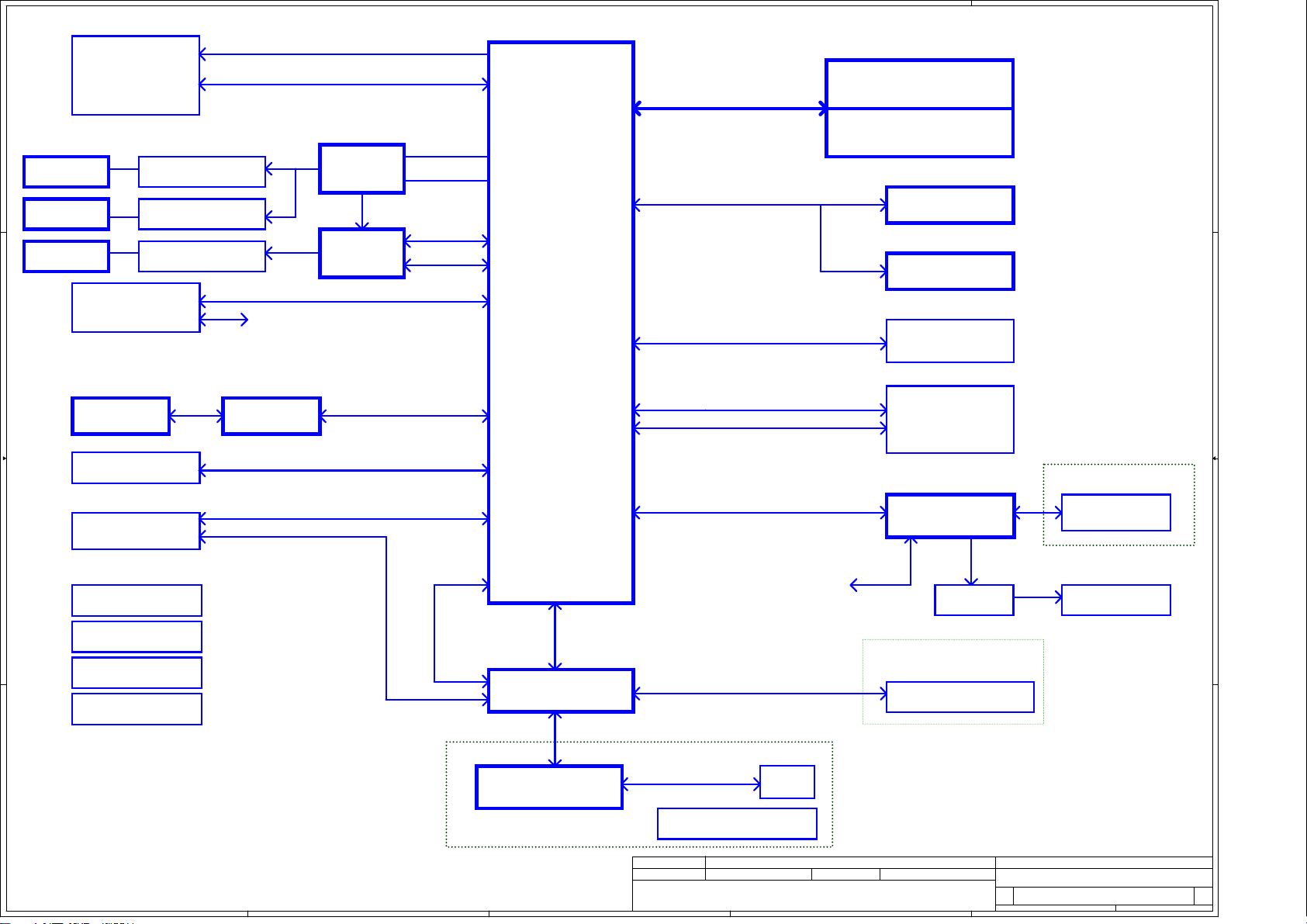

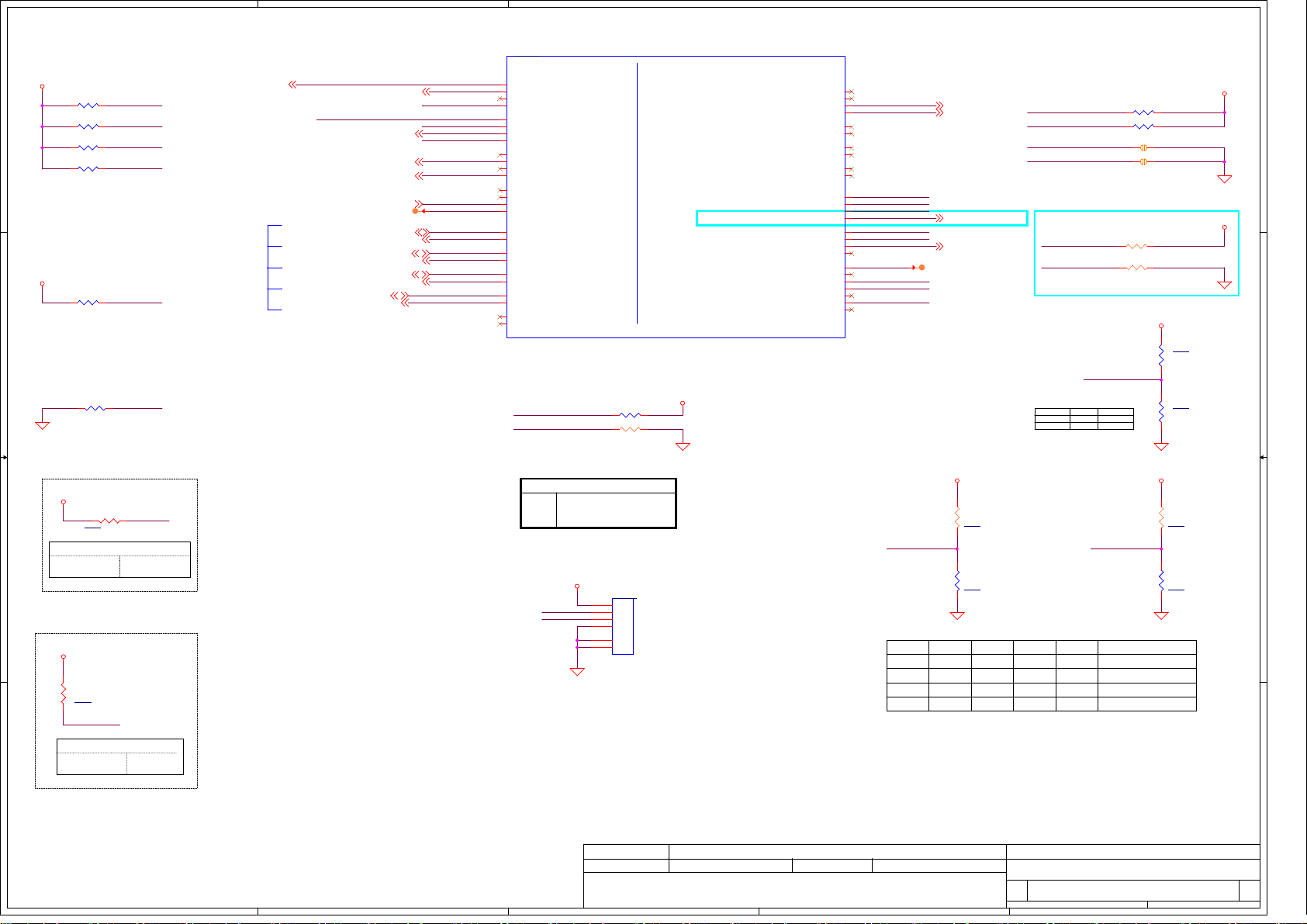

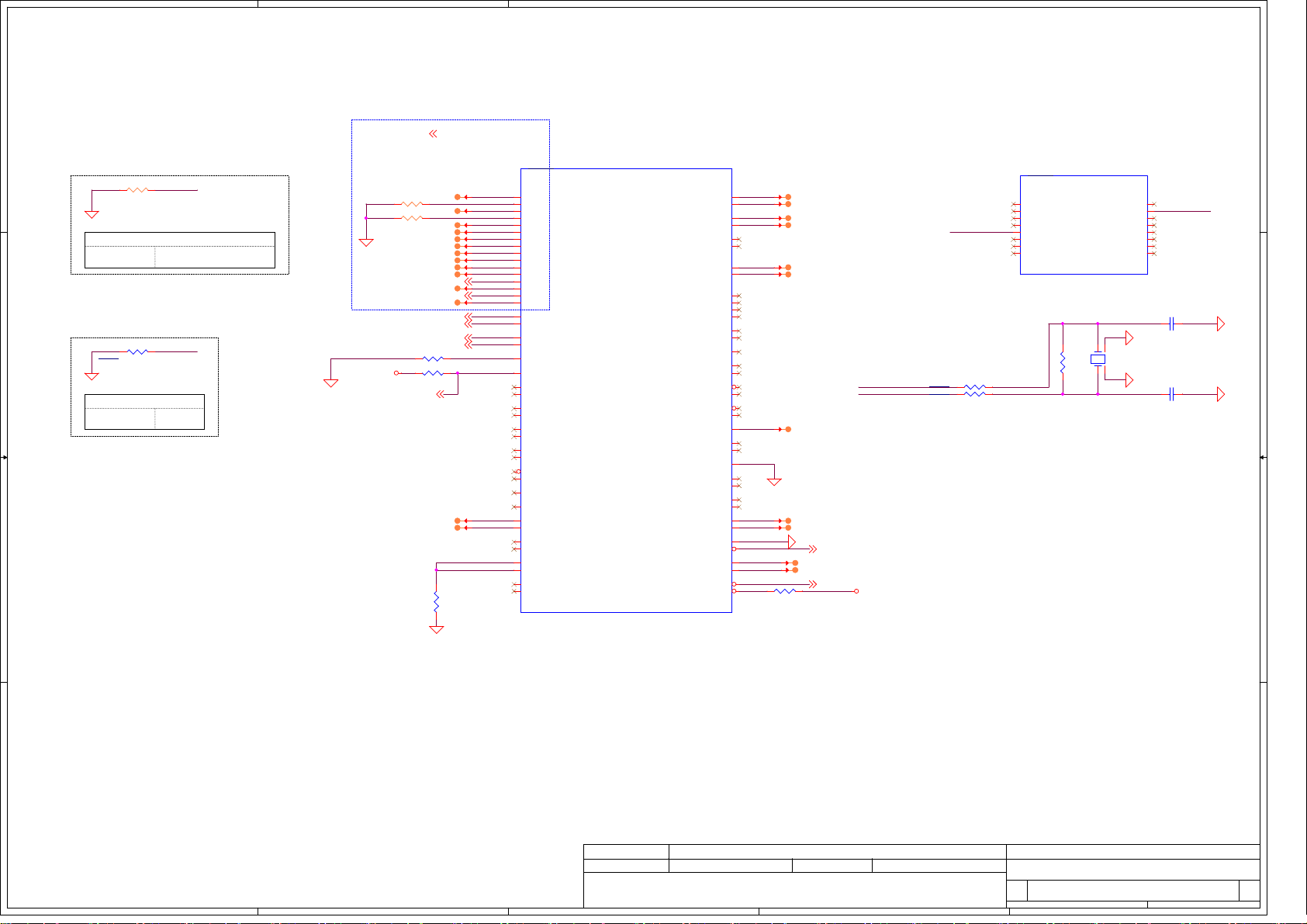

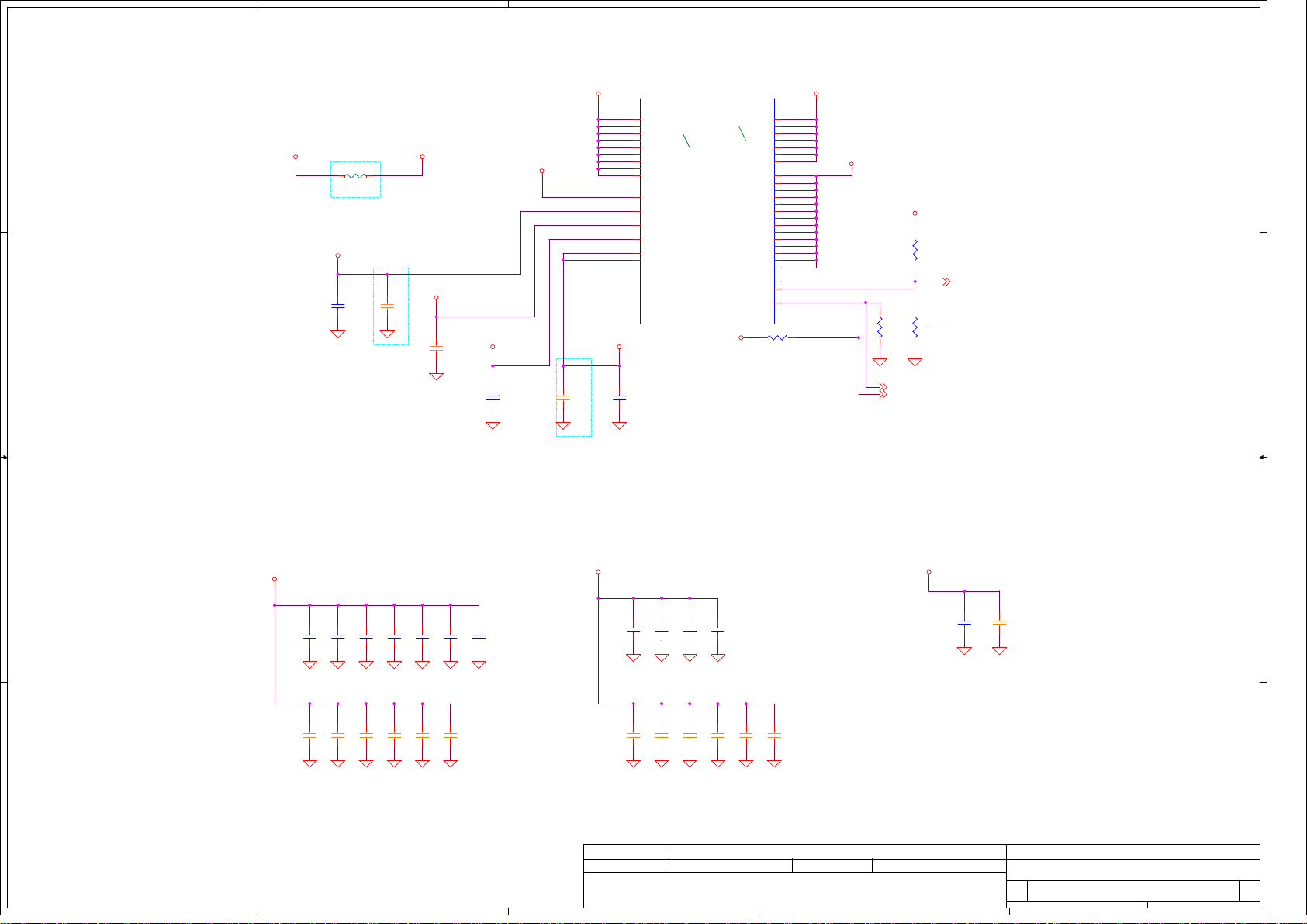

DP 1.2 X1

eDP 1.3

I2C

DP 1.2 X2

PCIe Gen3 X 4

USB3.0

USB2.0

USB2.0

PCIE Gen2

USB2.0

I2C

SMBus

Intel

Kaby Lake

ULT

15W TDP

Page 7 ~ 20

Memory Bus (LPDDR3)

Dual Channel

1.2V LPDDR3 1866 MHz Non-Interleave

SPI

SATA3 X1 / PCIE X4

USB2.0

PCIE

HDA

Channel A

LPDDR3 8Gb or 16Gb (x32) * 2

P.21

Channel B

LPDDR3 8Gb or 16Gb (x32) * 2

P.22

SPI ROM

128/256Mb

TPM2.0

Nuvoton

M.2 Socket3 M-Key

SSD

WLAN1216

WLAN

BT4.0

Audio Codec

ALC3271

I2S

DMIC

Audio AMP

ALC1309

P.09

P.27

P.30

P.28

P.24

P.25

Audio/B with FPC

Headphone Jack

( iPhone & Nokia compatible)

Int. Speaker

P.26

P.25

eDP Panel Conn.

+ Touch Screen

(IPT)

1 1

TI PD

TPS65982

P.43

TI PD

TPS65982

TI PD

TPS65982

P.45

IR Digital Camera

2 2

uSD 4.0

Fingerprint

P.37

USB TypeC Conn.

USB TypeC Conn.

USB TypeC Conn.

P.37

P.46

P.46P.44

P.47

DMIC

CardReader

P.29 P.29

P.36

RTS5242

Alpine Ridge

Thunderbolt

P.41

DP Switch

TI TUSB546

P.31

Precision Touch Pad

P.36

3 3

Fan conn. x 2

P.30

RTC conn.

DC/DC Interface CKT.

Power Circuit DC/DC

P.35

P.34~ 35

P.49~ 61

PS/2

EC

MEC 5105

ESPI

P.38

User Interface

Battery Gauge LED

P.32

BCBUS

KBC/B

Keyboard Controller

4 4

A

B

ECE1117B

C

KSIO

Int.KBD

Front Side LED + 4 MIC

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2015/12/16 2016/12/13

2015/12/16 2016/12/13

2015/12/16 2016/12/13

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

DELL CONFIDENTIAL/PROPRIETARY

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

P02-Block Diagram

P02-Block Diagram

P02-Block Diagram

Document Number Re v

Document Number Re v

Document Number Re v

LA-E671P

LA-E671P

LA-E671P

E

2 61Tuesday, October 17, 2017

2 61Tuesday, October 17, 2017

2 61Tuesday, October 17, 2017

1.0

1.0

1.0

A

B

C

D

E

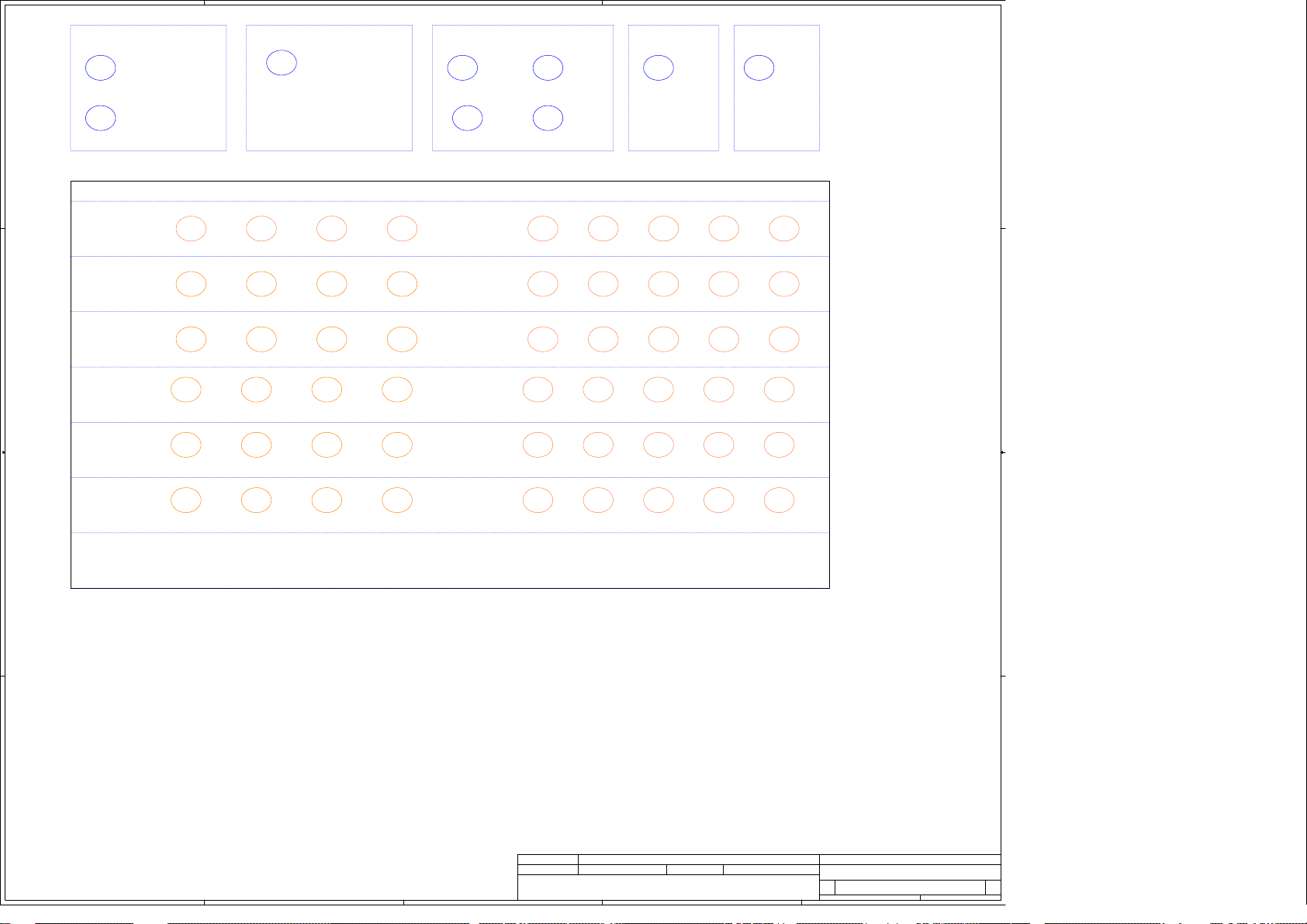

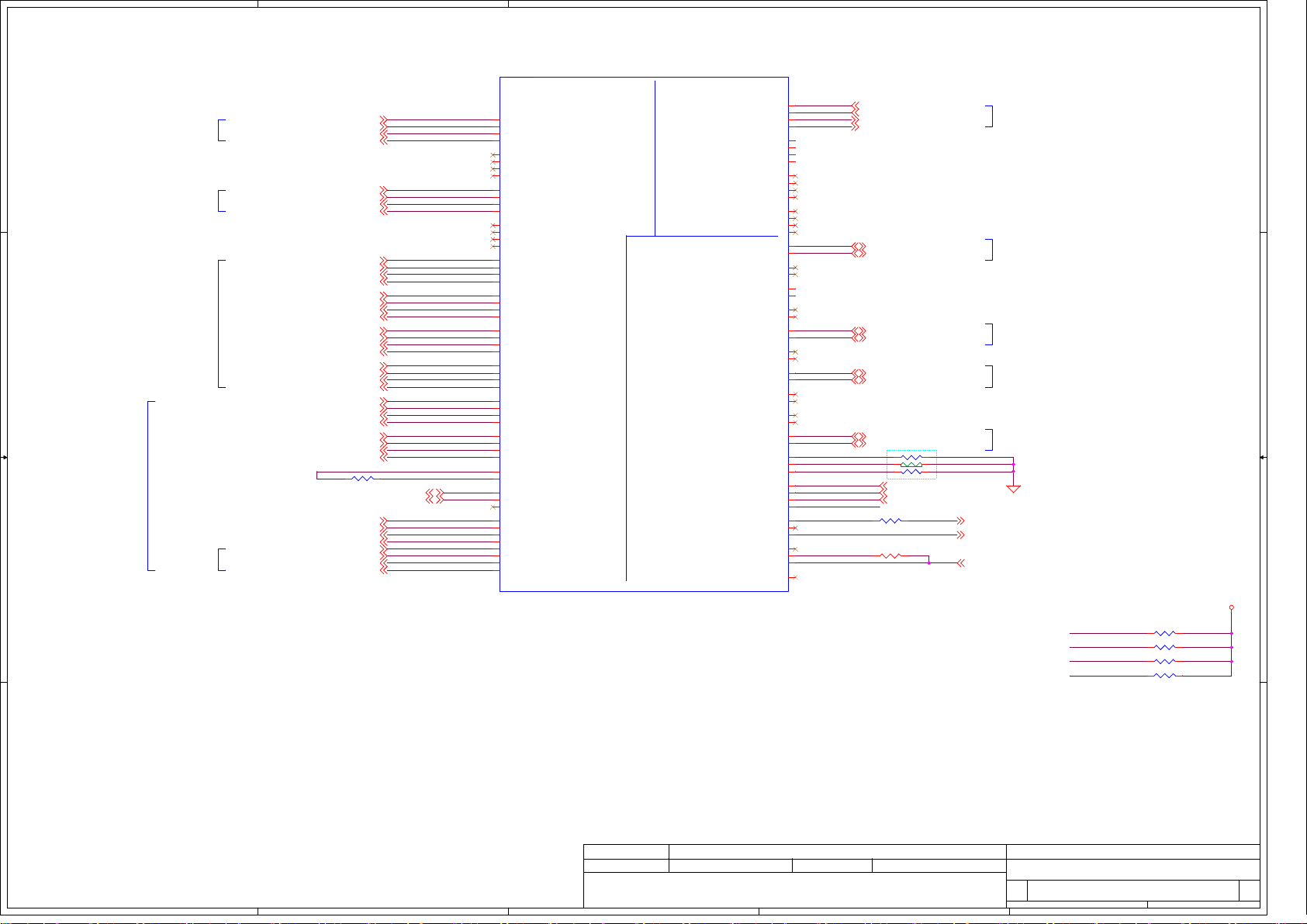

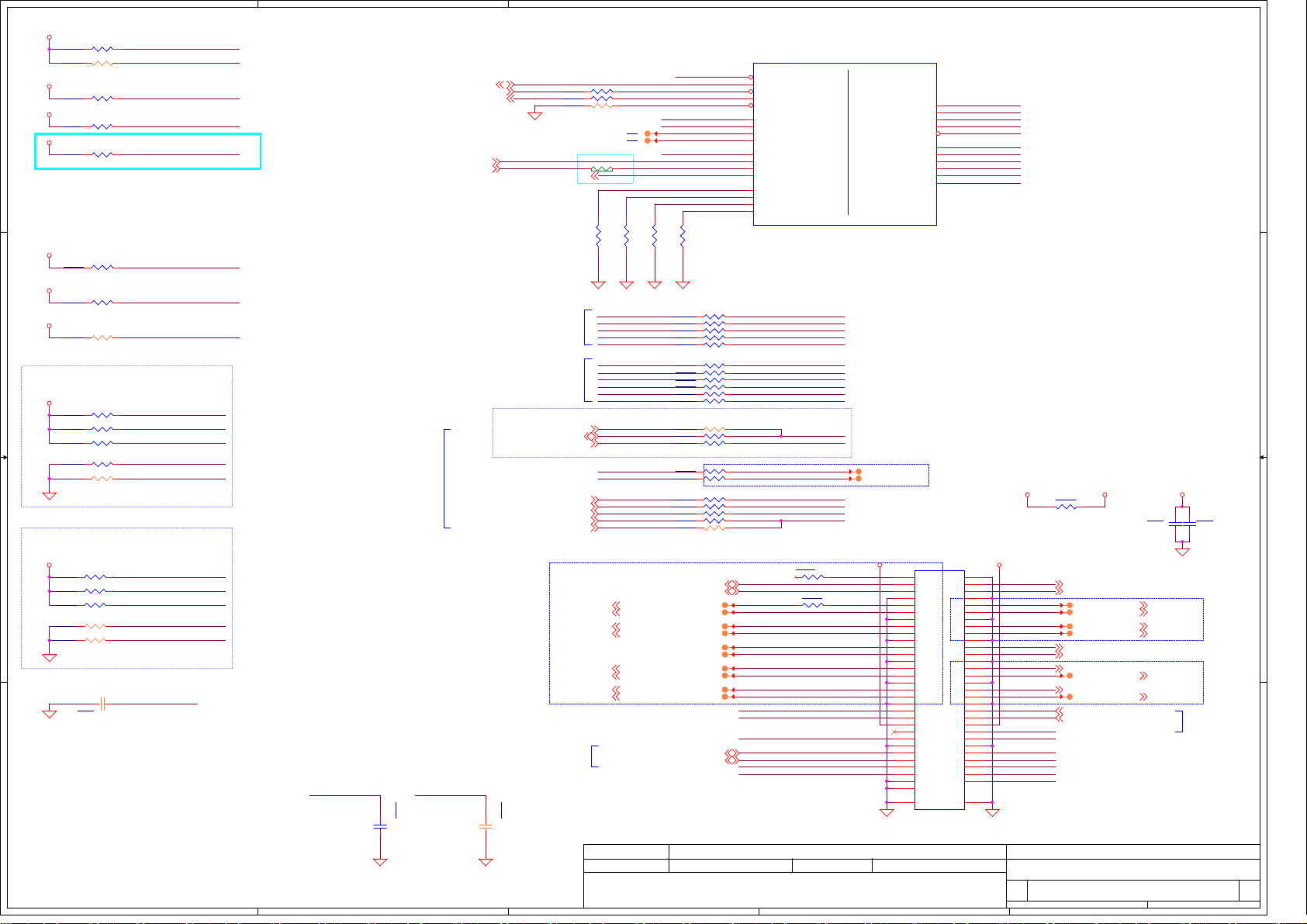

2+2 CPU Option

UCPU1 QNB1_ 2+2@

SA0000B2Y0L

UCPU1 QL YJ_2+2_R3@

1 1

SA0000A377L

DRAM Option DRAM Config Option

Micron 4G/1866

SA00009XU1L

Micron 8G/1866

SA00009U71L

2 2

Mircon 16G/1866

SA00009ZN1L

Hynix 4G/1866

SA00008G64L

Hynix 8G/1866

SA00008FJ4L

Hynix 16G/1866

SA0000AEN0L

UD41 M4G_1866@

SA00009XU1L

UD41 M8G_1866@

SA00009U71L

UD41 M16G_1866@

SA00009ZN1L

UD41

H4G_1866@

SA00008G64L

H9CCNNN8GTALAR-NUD

UD41

H8G_1866@

SA00008FJ4L

H9CCNNNBJTALAR-NUD

UD41

H16G_1866@

SA0000AEN0L

H9CCNNNCLGALAR-NUD

2+3 CPU Option

UCPU1 QM 6R_2+3_R3@

SA0000AHS1L

UD42 M4G_1866@

SA00009XU1L

UD42 M8G_1866@

SA00009U71L

UD42 M16G_1866@

SA00009ZN1L

UD42

H4G_1866@

SA00008G64L

H9CCNNN8GTALAR-NUD

UD42

H8G_1866@

SA00008FJ4L

H9CCNNNBJTALAR-NUD

UD42

H16G_1866@

SA0000AEN0L

H9CCNNNCLGALAR-NUD

UD43 M4G_1866@

SA00009XU1L

UD43 M8G_1866@

SA00009U71L

UD43 M16G_1866@

SA00009ZN1L

UD43

H4G_1866@

SA00008G64L

H9CCNNN8GTALAR-NUD

UD43

H8G_1866@

SA00008FJ4L

H9CCNNNBJTALAR-NUD

UD43

H16G_1866@

SA0000AEN0L

H9CCNNNCLGALAR-NUD

UD44 M4G_1866@

SA00009XU1L

UD44 M8G_1866@

SA00009U71L

UD44 M16G_1866@

SA00009ZN1L

UD44

H4G_1866@

SA00008G64L

H9CCNNN8GTALAR-NUD

UD44

H8G_1866@

SA00008FJ4L

H9CCNNNBJTALAR-NUD

UD44

H16G_1866@

SA0000AEN0L

H9CCNNNCLGALAR-NUD

4+2 CPU Option

UCPU1 QNEE_4 +2_R3@

SA0000AWS2L

UCPU1 QNEF_ 4+2_R3@

SA0000AWB3L

MEM_CON FIG0 MEM_ CONFIG1 MEM_CONFIG2

RH51

RH52

RH51

10K_0402_5%~D

RH52

SD028100280

10K_0402_5%~D

RH51

SD028100280

10K_0402_5%~D

RH52

SD028100280

10K_0402_5%~D

UCPU1 QNBF_ 4+2_R3@

SA0000AWC2L

UCPU1 QNBE_4 +2_R3@

SA0000AWR2L

M4G_1866@

SD028100280

10K_0402_5%

M8G_1866@

SD028100280

10K_0402_5%

M16G_1866@

SD028100280

H4G_1866@

H8G_1866@

H16G_1866@

RH54

SD028100280

10K_0402_5%

RH53

SD028100280

10K_0402_5%

RH53

SD028100280

10K_0402_5%~D

RH54

SD028100280

10K_0402_5%~D

RH54

SD028100280

10K_0402_5%~D

RH53

SD028100280

10K_0402_5%~D

M4G_1866@

M8G_1866@

M16G_1866@

H4G_1866@

H8G_1866@

H16G_1866@

AR Option

UT2

AR_SLL42@

SA00009ZV3L

DSL6340 SLL42 B2

RH56

M4G_1866@

SD028100280

10K_0402_5%

RH56

M8G_1866@

SD028100280

10K_0402_5%

RH56

M16G_1866@

SD028100280

10K_0402_5%~D

RH55

H4G_1866@

SD028100280

10K_0402_5%~D

RH55

H8G_1866@

SD028100280

10K_0402_5%~D

RH55

H16G_1866@

SD028100280

10K_0402_5%~D

RH57

M4G_1866@

SD028100280

10K_0402_5%

RH57

M8G_1866@

SD028100280

10K_0402_5%

RH57

M16G_1866@

SD028100280

10K_0402_5%~D

RH57

H4G_1866@

SD028100280

10K_0402_5%~D

RH57

H8G_1866@

SD028100280

10K_0402_5%~D

RH57

H16G_1866@

SD028100280

10K_0402_5%~D

TPM Option

U7

TPM750@

SA0000AQ200

TPM750 - ES FW:7.1.0.0

MEM_CON FIG4MEM_CON FIG3

RH60

M4G_1866@

SD028100280

10K_0402_5%

RH60

M8G_1866@

SD028100280

10K_0402_5%

RH60

M16G_1866@

SD028100280

10K_0402_5%~D

RH60

H4G_1866@

SD028100280

10K_0402_5%~D

RH60

H8G_1866@

SD028100280

10K_0402_5%~D

RH60

H16G_1866@

SD028100280

10K_0402_5%~D

3 3

4 4

LA-E671P

LA-E671P

LA-E671P

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2015/12/16 2016/12/13

2015/12/16 2016/12/13

2015/12/16 2016/12/13

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

P03-BoM Option

P03-BoM Option

P03-BoM Option

Size

Document Number Re v

Size

Document Number Re v

Size

Document Number Re v

LA-E671P

Date: Sheet of

Date: Sheet of

Date: Sheet of

3 61Tuesday, October 17, 2017

3 61Tuesday, October 17, 2017

3 61Tuesday, October 17, 2017

E

1.0

1.0

1.0

A

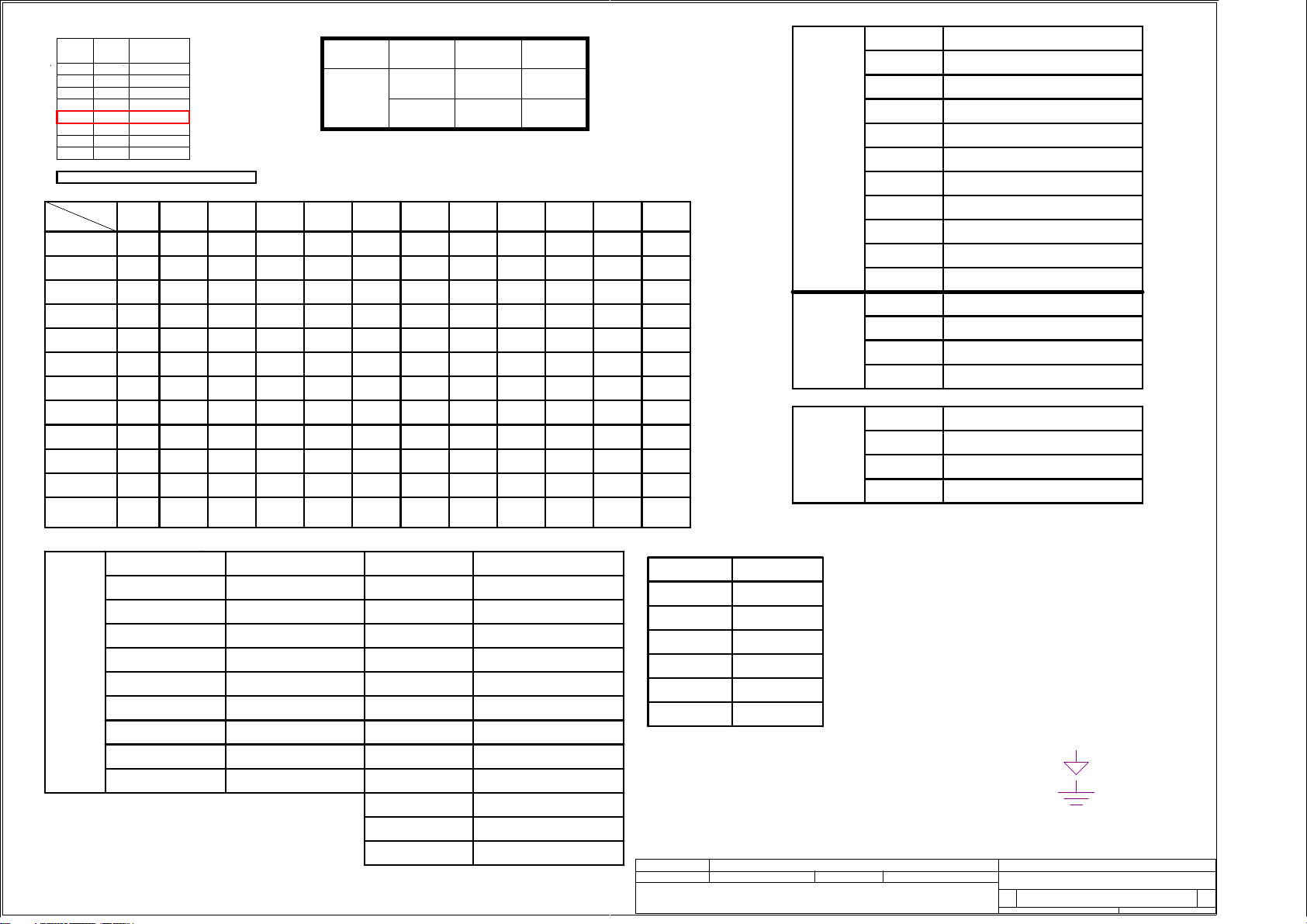

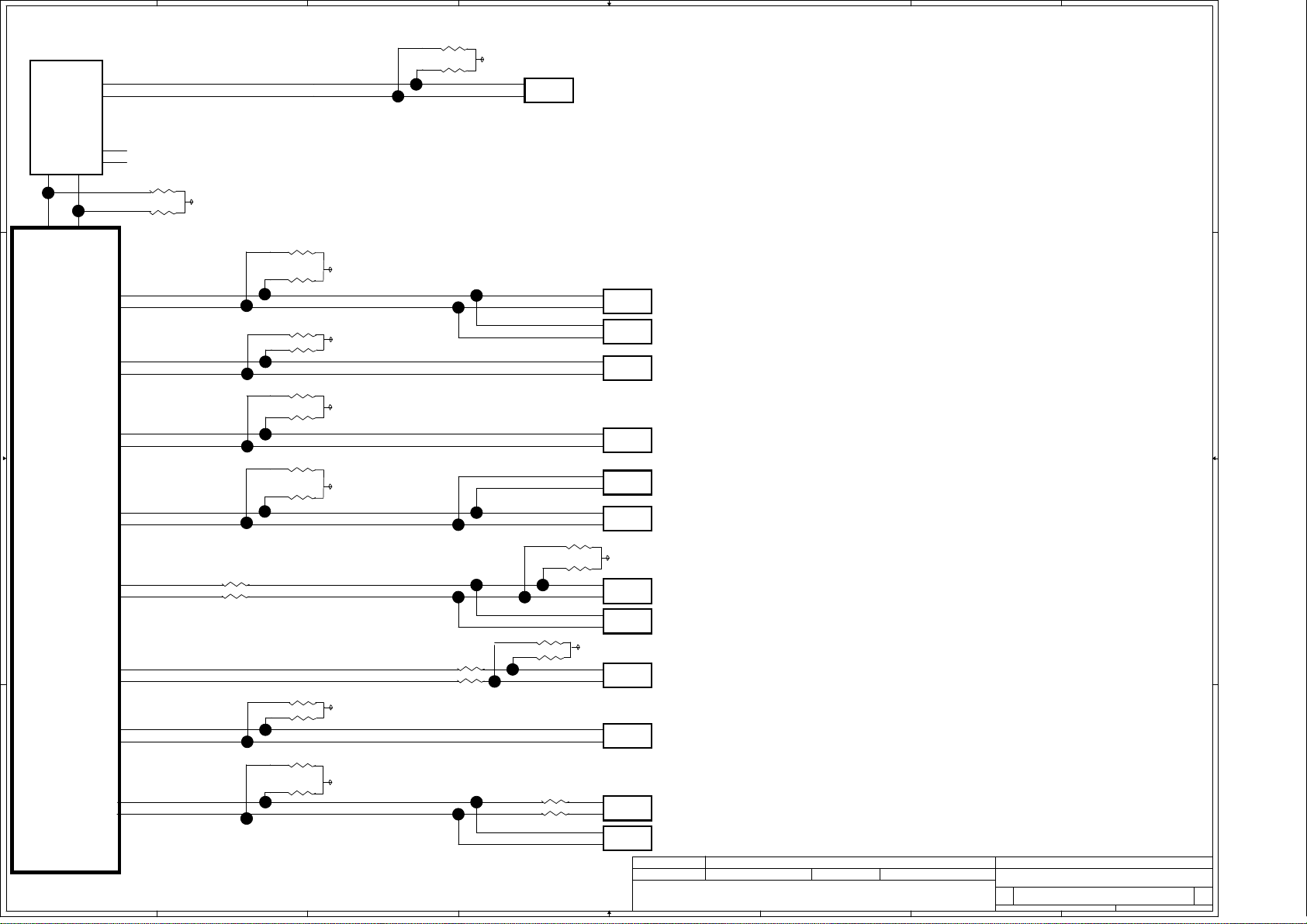

Board ID Table for AD channel

USB PORT# DESTINATION

1

2

3

4

5

6

7

8

9

10

1

PD PORT3

NC

NC

NC

IR Camera & Cam

NC

NGFF WLAN BT

NC

NC

Fingerprint

DP MX (PS8743B)

2

DDI PORT# DESTINATION

1

2

Alpine Ridge

Alpine Ridge

X00240K

X01

X02

X03

A00

SOURCE

MEC5105

MEC5105

MEC5105SMB04_CLK

MEC5105

MEC5105

MEC5105

PCH

PCH

PCH

PCH

PCHI2C2_CLK

REV

BATTERY

Charger

PD1

V

PD2

V

PWR_MON

V

Italia

CAZ60

5105

4+2 2+3 3+2CPU

PCH

USB 2.0

Port

Mapping

XDP

Audio

AMP

eDP

Touch Pad

Touch S

IR_THER_S

V

V

PCH

USB 3.0

V

Port

Mapping

V

V

V

PCH

DDI

Port

Mapping

V

V

CE75RE194

4700p

4700p

130K

4700p

62K

4700p

33K

4700p

8.2K

4.3K

4700p

4700p

2K

1K

4700p

BOARD_ID rise t i me i s meas ur ed fr o m 5 %~68 %.

SMBUS Control Table

SMB00_CLK

SMB00_DATA

SMB01_CLK

SMB01_DATA

SMB02_CLKVMEC5105

SMB02_DATA

SMB04_DATA

SMB05_CLK

SMB05_DATA

SMB07_CLK

SMB07_DATA

SMB10_CLK

SMB10_DATA

PCH_SML1CLK

PCH_SML1DATA

SMBCLK

SMBDATA

1 1

I2C0_CLK

I2C0_DATA

I2C2_DATA

I2C1_CLK

I2C1_DATA

I2C2_DATA

CLK

CLKOUT_PCIE0

CLKOUT_PCIE1

CLKOUT_PCIE2

CLKOUT_PCIE3

CLKOUT_PCIE4

CLKOUT_PCIE5

FLEX CLK#

CLKOUT_LPC_0

CLKOUT_LPC_1

DESTINATIONDIFFERENTIAL CLK#

Alpine Ridge

NGFF WLAN

NC

M.2 SSD

NC

Card Reader

DESTINATION

ESPI 5105

NC

PCI EXPRESS PORT#

Lane 1 Card Reader

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8

Lane 9

Lane 10

Lane 11

Lane 12 / SATA 2

DESTINATION

NC

NGFF WLAN

NC

Alpine Ridge

Alpine Ridge

Alpine Ridge

Alpine Ridge

M.2 SSD

M.2 SSD

M.2 SSD

M.2 SSD

SATA PORT#

SATA-0

SATA-1A

SATA-1B

SATA-2

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

DESTINATION

NC

NC

NC

M.2 SSD

Compal Secret Data

Compal Secret Data

2015/12/16 2016/12/13

2015/12/16 2016/12/13

2015/12/16 2016/12/13

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Symbol Note :

: means Digital Ground

: means Analog Ground

DELL CONFIDENTIAL/PROPRIETARY

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

P04-Notes List

P04-Notes List

P04-Notes List

Document Number Re v

Document Number Re v

Document Number Re v

LA-E671P

LA-E671P

LA-E671P

4 61Tuesday, October 17, 2017

4 61Tuesday, October 17, 2017

4 61Tuesday, October 17, 2017

1.0

1.0

1.0

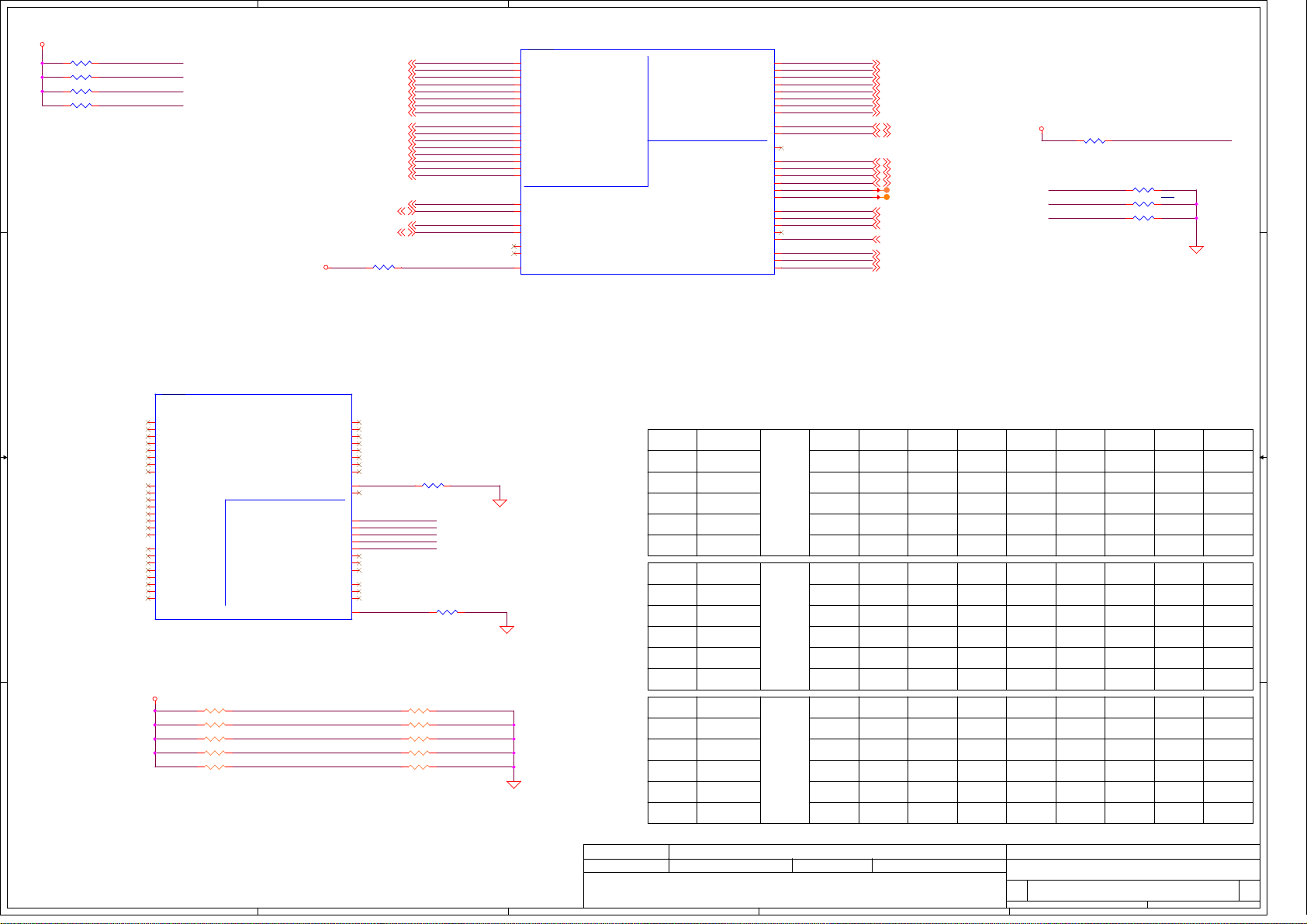

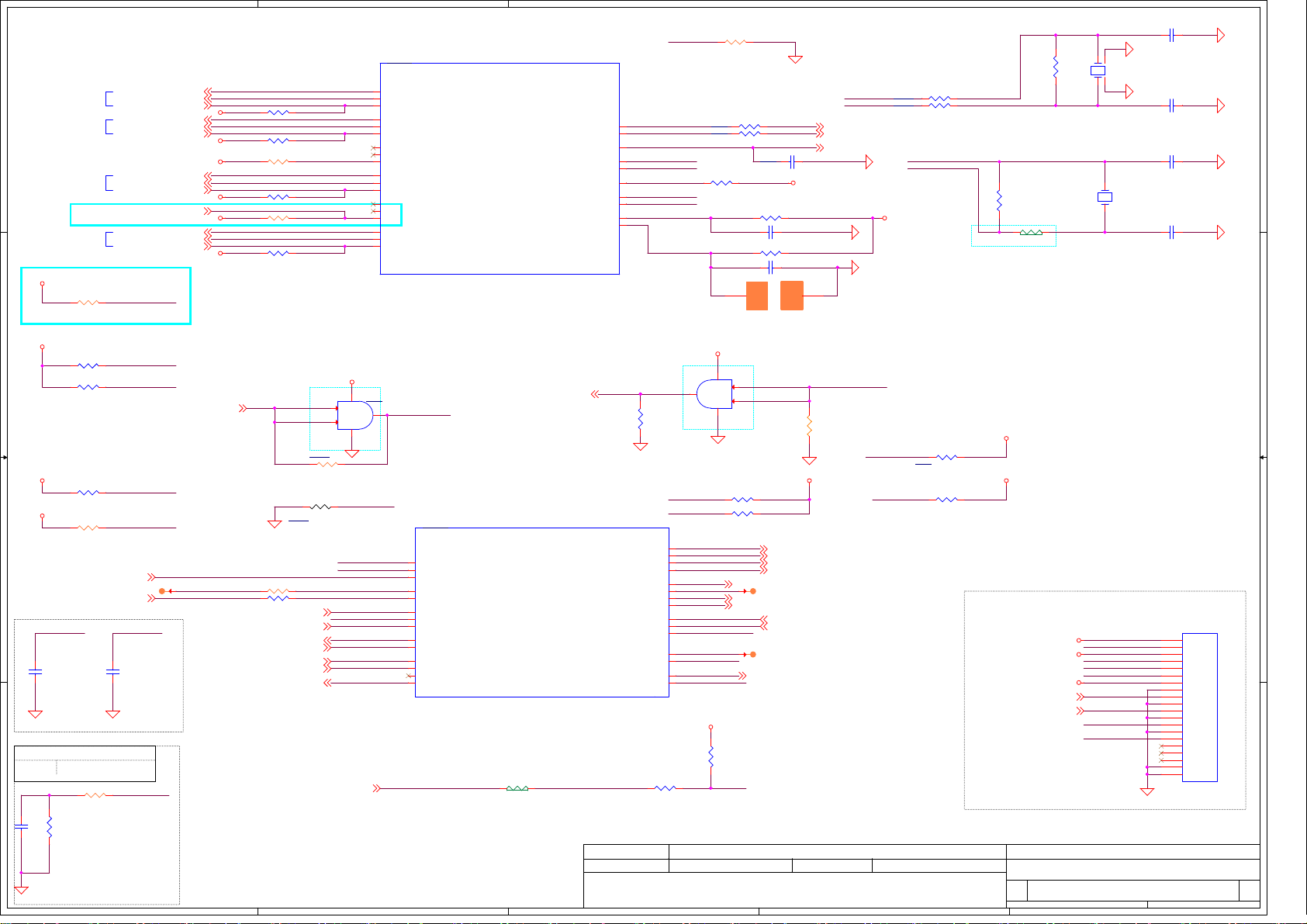

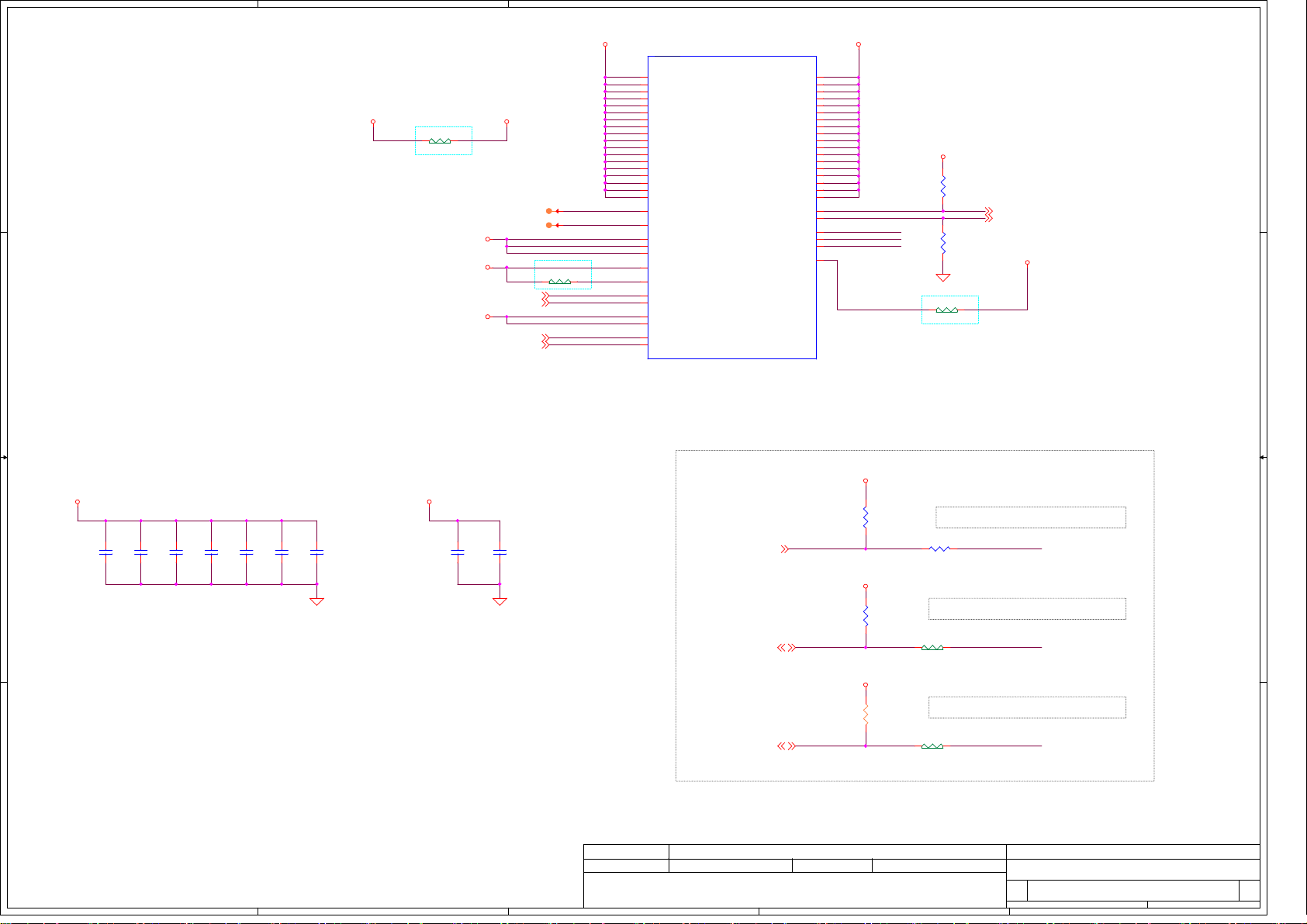

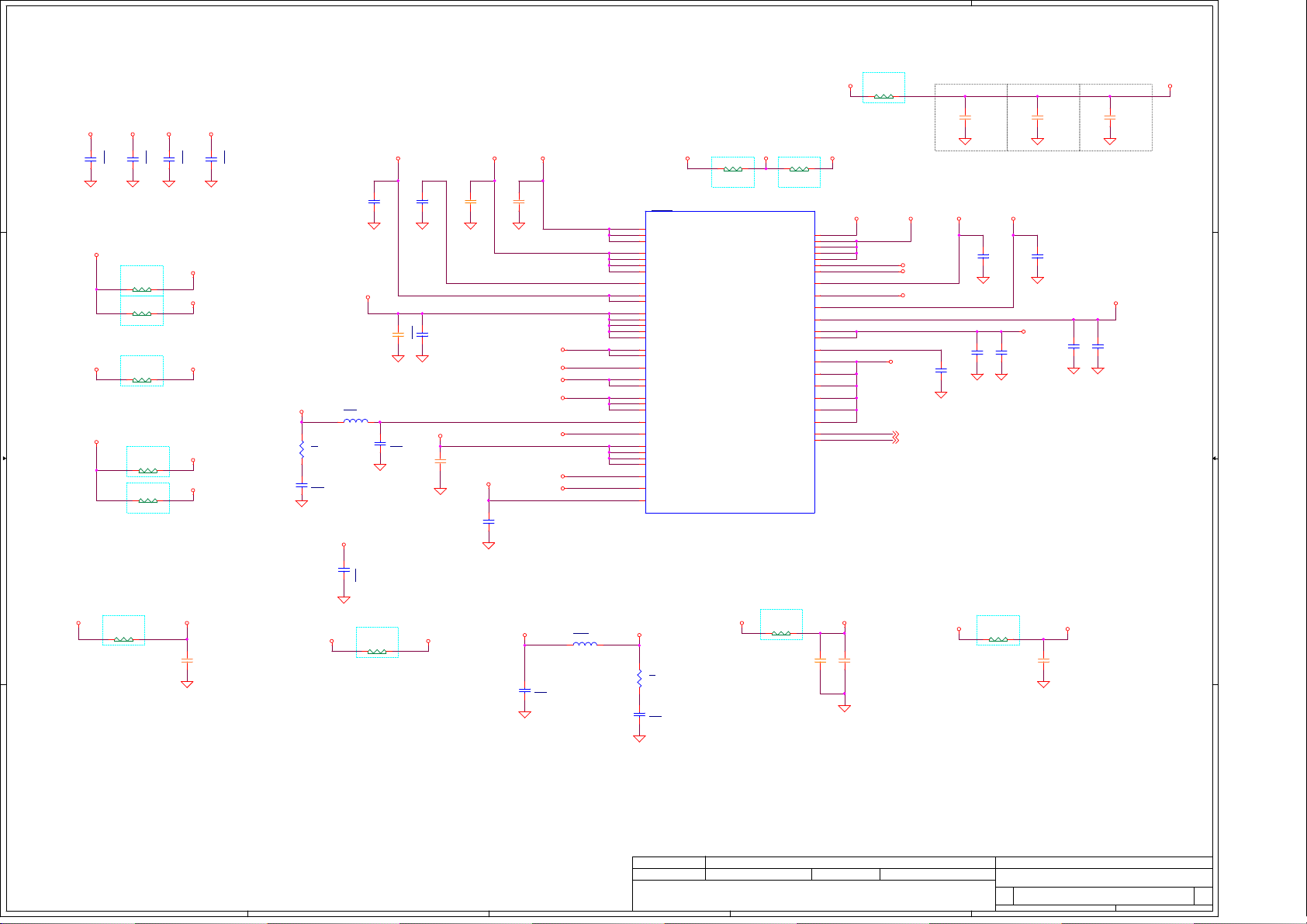

5

SY8210A

(PU600)

Type C X 3

D D

ISL88738

(PU300)

SY8286

(PU700)

TPS62134A

(PU1400)

TPS62134B

(PU1401)

4

SIO_SLP_S4# &

SUS_ON_EC

5500 mA

SM_PG_CTRL

600mA

SIO_SLP_SUS#

880mA 240mA

SIO_SLP_S0# &

RUN_ON_P

SIO_SLP_SUS#

2570 mA

+1.2V_DDR

+0.6VS

+1.0VA

+1.0VS_VCCIO

+1.0V_PRIM_CORE

TPS22961

(UZ5)

3

SIO_SLP_S0# &

RUN_ON_P

260mA

+VCCPLL_OC

RUN_ON_P

200mA

+5VS

2

+1.0V_MPHYGT

+1.0V_MPHYAON

TPS22961

(UZ3)

TPS22961

(UZ4)

SIO_SLP_SUS# &

SUS_ON_P

SIO_SLP_S0# &

RUN_ON_P

40mA3100 mA

1

CPU PWR

PCH PWR

GPU PWR

Peripheral Device PWR

+1.0V_VCCST

+1.0V_VCCSTG

SY8288C

B+

BATTERY

(JT100)

C C

(PU501)

TLV6215

(PU800)

SY8286B

(PU500)

ALWON

530mA

SIO_SLP_SUS#

210mA

+5VALW

+1.8VA

AOZ1331

(U12)

AUD_PWR_EN

3150 mA

+5VS_AUDIO

AOZ1331

(U14)

AUD_PWR_EN

400mA

+1.8VS_AUDIO

+V1.8S_EDRAM

ALWON

590mA

TPS62134C

(PU1500)

TPS62134C

(PU1501)

B B

TLV62150R

(PU900)

ISL95829

(PU1000)

AP22850

IMVP_VR_ON_P

2500 mA

IMVP_VR_ON_P

2000 mA

SUS_ON_P

+VCC_EDRAM

+VCC_EOPIO

660mA

+3VALW

SY6288C

(UZ2)

AP22850

(U10)

AOZ1331

(U11)

AOZ1331

(U13)

TPS22961

(UZ1)

AOZ1331

(U14)

ENVDD

545mA

TP_PW_EN

35mA

PCH_PWR_EN

(SIO_SLP_SUS#)

535mA

AUX_EN_WOWL

620mA

3.3V_TS_EN

300mA

AUD_PWR_EN

50mA

+LCDVDD

+3VS_TP

+3V_PCH

+3VS_NGFF

+3VS_TS

+3VS_AUDIO

RUN_ON_P

2500 mA

RUN_ON_P

480mA

+3.3VDX_SSD

+3VS

SD_PWR_EN

1200 mA

+3VS_CR

A A

5100 mA

IMVP_VR_ON

6400 0mA

IMVP_VR_ON

+VCC_GT+VCC_SA

5

2900 0mA

IMVP_VR_ON

+VCC_CORE

+INV_PWR_SRC

590mA

EN_INVPWR

+1.8VU

4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2015/12/16 2016/12/13

2015/12/16 2016/12/13

2015/12/16 2016/12/13

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P05-Power rails

P05-Power rails

P05-Power rails

LA-E671P

LA-E671P

LA-E671P

1

5 61Tuesday, October 17, 2017

5 61Tuesday, October 17, 2017

5 61Tuesday, October 17, 2017

1.0

1.0

1.0

A

B

C

D

E

F

G

H

2.2K

R7

R8

1 1

2 2

KBL-U

W3 V3

E11 D 8

SMB03

R9

W2

SML1_SMBDATA

SML1_SMBCLK

SMB00

SMB01

MEM_SMBCLK

MEM_SMBDATA

1K

1K

D7

UPD2_SMBCLK

E7

UPD2_SMBDAT

B3

IR_THER_SEN_SMBCLK

E5

IR_THER_SEN_SMBDAT

+3V_PCH

2.2K

2.2K

2.2K

2.2K

+3.3V_EC5105

+3.3V_EC5105

2.2K

+3VS

53

51

XDP

B3

C3

B5

A1

L2

K2

TI PD2

PD2_Debug

IR_THER_S

TI PD address selection 0x70_TBD

PD_Debug address selection 0xEC_TBD

4.7K

KBC

SMB02

C12

E10

CLK_TP_SIO

DAT_TP_SIO

4.7K

2.2K

2.2K

C3

B4

UPD1_SMBCLK

UPD1_SMBDAT

SMB04

MEC 5105

3 3

SMB05

SMB06

SMB07

F7

B6

A12

PWR_MONITOR_EC_SMBCLK

PWR_MONITOR_EC_SMBDAT

M4

UPD3_SMBCLK

M7

UPD3_SMBDAT

0 ohm

0 ohm

EC_I2C_CLK

EC_I2C_DAT

2.2K

2.2K

+3VS_TP

+3.3V_EC5105

+3.3V_EC5105

0 ohm

0 ohm

2.2K

2.2K

PWRM_SCL

PWRM_SDA

2.2K

2.2K

+3VS_PWRM

8

9

L2

K2

B5

A1

7

8

6

7

C4

D4N10

B5

A5

TP

PD1_Debug

TI PD1

+DVDD

AMP

Audio

MAX34407

TI PD3

TP address :0x42_TBD

PD_Debug address selection 0xEC_TBD

TI PD address selection 0x70_TBD

I2C address selection L= 0x20H (L= 0x20H ; H= 0x22H)_TBD

2.2K

+3.3V_EC5105

4 4

A

SMB10

N2

PBAT_CHARGER_SMBCLK

M3

PBAT_CHARGER_SMBDAT

B

2.2K

C

100 ohm

100 ohm

D

8

BATTERY

7

CONN

22

Charger

21

Battery address selection 0x16_TBD

Charger address selection 0x12_TBD

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE S ECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

E

2013/07/04 2013/10/28

2013/07/04 2013/10/28

2013/07/04 2013/10/28

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

F

DELL CONFIDENTIAL/PROPRIETARY

Title

Title

Title

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

G

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

P06-SMBus block diagram

P06-SMBus block diagram

P06-SMBus block diagram

Document Number Re v

Document Number Re v

Document Number Re v

LA-E671P

LA-E671P

LA-E671P

6 61Tuesday, October 17, 2017

6 61Tuesday, October 17, 2017

6 61Tuesday, October 17, 2017

H

1.0

1.0

1.0

5

CAD Note:Trace width=5 mils, Isolat i on Spaci ng=25 mil,

4

3

2

1

+3VS

CPU_DP1_CTRL_CLK

RC1 2.2K_0402_5%

RC3 2.2K_0402_5%

RC5 2.2K_0402_5%

D D

RC7 2.2K_0402_5%

12

CPU_DP1_CTRL_DATA

12

CPU_DP2_CTRL_CLK

12

CPU_DP2_CTRL_DATA

12

Alpine Ridge

+1.0VS_VCCIO

DDI1_PTX_TBRX_N0<41>

DDI1_PTX_TBRX_P0<41>

DDI1_PTX_TBRX_N1<41>

DDI1_PTX_TBRX_P1<41>

DDI1_PTX_TBRX_N2<41>

DDI1_PTX_TBRX_P2<41>

DDI1_PTX_TBRX_N3<41>

DDI1_PTX_TBRX_P3<41>

DDI2_PTX_TBRX_N0<41>

DDI2_PTX_TBRX_P0<41>

DDI2_PTX_TBRX_N1<41>

DDI2_PTX_TBRX_P1<41>

DDI2_PTX_TBRX_N2<41>

DDI2_PTX_TBRX_P2<41>

DDI2_PTX_TBRX_N3<41>

DDI2_PTX_TBRX_P3<41>

CPU_DP1_CTRL_CLK<41>

CPU_DP1_CTRL_DATA<41> CPU_DP1_HPD <41>

CPU_DP2_CTRL_CLK<41>

CPU_DP2_CTRL_DATA<41>

1 2

RC8 24.9_0402_1%

CPU_DP1_CTRL_CLK

CPU_DP1_CTRL_DATA CPU_DP1_HPD

CPU_DP2_CTRL_CLK

CPU_DP2_CTRL_DATA

EDP_COMP

COMPENSATION PU FOR eDP

Max length=600 mils.

C C

UCPU1I

@

CSI-2

A36

CSI2_DN0

B36

CSI2_DP0

C38

CSI2_DN1

D38

CSI2_DP1

C36

CSI2_DN2

D36

CSI2_DP2

A38

CSI2_DN3

B38

CSI2_DP3

C31

CSI2_DN4

D31

CSI2_DP4

C33

CSI2_DN5

D33

CSI2_DP5

A31

CSI2_DN6

B31

CSI2_DP6

A33

CSI2_DN7

B33

CSI2_DP7

A29

CSI2_DN8

B29

CSI2_DP8

C28

CSI2_DN9

D28

B B

CSI2_DP9

A27

CSI2_DN10

B27

CSI2_DP10

C27

CSI2_DN11

D27

CSI2_DP11

SKL-U_BGA1356

SKL_U LT

CSI2_CLKN0

CSI2_CLKP0

CSI2_CLKN1

CSI2_CLKP1

CSI2_CLKN2

CSI2_CLKP2

CSI2_CLKN3

CSI2_CLKP3

CSI2_COMP

GPP_D4/FLASHTRIG

EMMC

GPP_F13/EMMC_DATA0

GPP_F14/EMMC_DATA1

GPP_F15/EMMC_DATA2

GPP_F16/EMMC_DATA3

GPP_F17/EMMC_DATA4

GPP_F18/EMMC_DATA5

GPP_F19/EMMC_DATA6

GPP_F20/EMMC_DATA7

GPP_F21/EMMC_RCLK

GPP_F22/EMMC_CLK

GPP_F12/EMMC_CMD

EMMC_RCOMP

9 OF 20

C37

D37

C32

D32

C29

D29

B26

A26

E13

B7

AP2

AP1

AP3

AN3

AN1

AN2

AM4

AM1

AM2

AM3

AP4

AT1

CSI2_COMP

MEM_CONFIG0

MEM_CONFIG1

MEM_CONFIG2

MEM_CONFIG3

MEM_CONFIG4

EMMC_RCOMP

1 2

RC9 100_0402_1%

1 2

RC10 200_0402_1%

UCPU1A

@

E55

DDI1_TXN[0]

F55

DDI1_TXP[0]

E58

DDI1_TXN[1]

F58

DDI1_TXP[1]

F53

DDI1_TXN[2]

G53

DDI1_TXP[2]

F56

DDI1_TXN[3]

G56

DDI1_TXP[3]

C50

DDI2_TXN[0]

D50

DDI2_TXP[0]

C52

DDI2_TXN[1]

D52

DDI2_TXP[1]

A50

DDI2_TXN[2]

B50

DDI2_TXP[2]

D51

DDI2_TXN[3]

C51

DDI2_TXP[3]

L13

GPP_E18/DDPB_CTRLCLK

L12

GPP_E19/DDPB_CTRLDATA

N7

GPP_E20/DDPC_CTRLCLK

N8

GPP_E21/DDPC_CTRLDATA

N11

GPP_E22/DDPD_CTRLCLK

N12

GPP_E23/DDPD_CTRLDATA

E52

EDP_RCOMP

SKL-U_BGA1356

SKL-U Ballout Rev0.71 & INTEL symbol Rev1.0

DDR Memory Conf i gur at i no Type Str ap pin

+1.8VA

RH51 10K_0402_5%@

RH53 10K_0402_5%@

RH55 10K_0402_5%@

RH57 10K_0402_5%@

RH59 10K_0402_5%@

A A

12

12

12

12

12

MEM_CONFIG0

MEM_CONFIG1

MEM_CONFIG2

MEM_CONFIG3

MEM_CONFIG4

RH52 10K_0402_5%@

RH54 10K_0402_5%@

RH56 10K_0402_5%@

RH58 10K_0402_5%@

RH60 10K_0402_5%@

12

12

12

12

12

SKL-U

DDI

DISPLAY SIDEBANDS

EDP

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

1 OF 20

GPIO Pin

GPP_ F13

GPP_ F14

GPP_ F15

Pin Name

MEM_C ONF IG0

MEM_C ONF IG1

MEM_C ONF IG2

GPP_ F16 MEM_CONFIG3

GPP_ F17 MEM_CONFIG4

GPIO Pin

GPP_ F13

GPP_ F14

GPP_ F15

GPP_ F16

GPP_ F17

GPIO Pin

GPP_ F13

GPP_ F14

Pin Name

MEM_C ONF IG0

MEM_C ONF IG1

MEM_C ONF IG2

MEM_C ONF IG3

MEM_C ONF IG4

Pin Name

MEM_C ONF IG0

MEM_C ONF IG1

GPP_ F15

GPP_ F16

GPP_ F17

MEM_C ONF IG3

MEM_C ONF IG4

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

C47

C46

D46

C45

A45

B45

A47

B47

E45

F45

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

1600 Mbps

1866 Mbps

2133 Mbps

eDP_TXN_P0 <37>

eDP_TXP_P0 <37>

CPU_DP2_HPD

EDP_HPD

Micron 4G

0

0

0

eDP_TXN_P1 <37>

eDP_TXP_P1 <37>

eDP_TXN_P2 <37>

eDP_TXP_P2 <37>

eDP_TXN_P3 <37>

eDP_TXP_P3 <37>

eDP_AUXN <37>

eDP_AUXP <37>

CPU_DDI1_AUXN <41>

CPU_DDI1_AUXP <41>

CPU_DDI2_AUXN <41>

CPU_DDI2_AUXP <41>

PAD~D

PAD~D

CPU_DP2_HPD <41>

I2C2_IRQ_TS <37>

EDP_HPD <37>

PANEL_BKLEN <37>

EDP_BIA_PWM <37>

ENVDD_PCH <33,38>

Micron 8G

1

0 1

0

@

T1

@

T2

Mircon 16G

0 1

0

Hynix 4G

1

0 11

Support QHD

+3VS

EDP_HPD

CPU_DP1_HPD

CPU_DP2_HPD

01

0

1 2

RH83 100K_0402_5%

Hynix 16GHynix 8G

0 1

0

1 1

1 1

I2C2_IRQ_TS

12

RC2100K_0402_5%

12

RC4100K_0402_5%

12

RC6100K_0402_5%

Samsung 8GSamsung 4G

Samsung 16G

0

0

0

0 0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 0 0

Micron 4G

1

0

0

Micron 8G

0

1 1

0

Mircon 16G

Hynix 4G

1 0

0

0

1 11

Hynix 16GHynix 8G

10

0

1

1 1 1 1 1 1 1

0 0 0 0 0 0 0

Micron 4G Samsung 16G

Micron 8G

0

1

0

0

1

Mircon 16G

1

1

0MEM_C ONF IG2

0

1

Hynix 4G

0

1

0

1

Hynix 8G Hynix 16G

1

0

0

1

1 11

0 0 0

11

Samsung 4G Samsung 8G

10

1

1

Samsung 8GSamsung 4G

1

1

1

0

0

0

1

1

Samsung 16G

0

0

0

0

1

1

0

0 0

1

1

1

0

0

0

1

0

1

1

1

5

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2015/12/16 2016/12/13

2015/12/16 2016/12/13

2015/12/16 2016/12/13

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

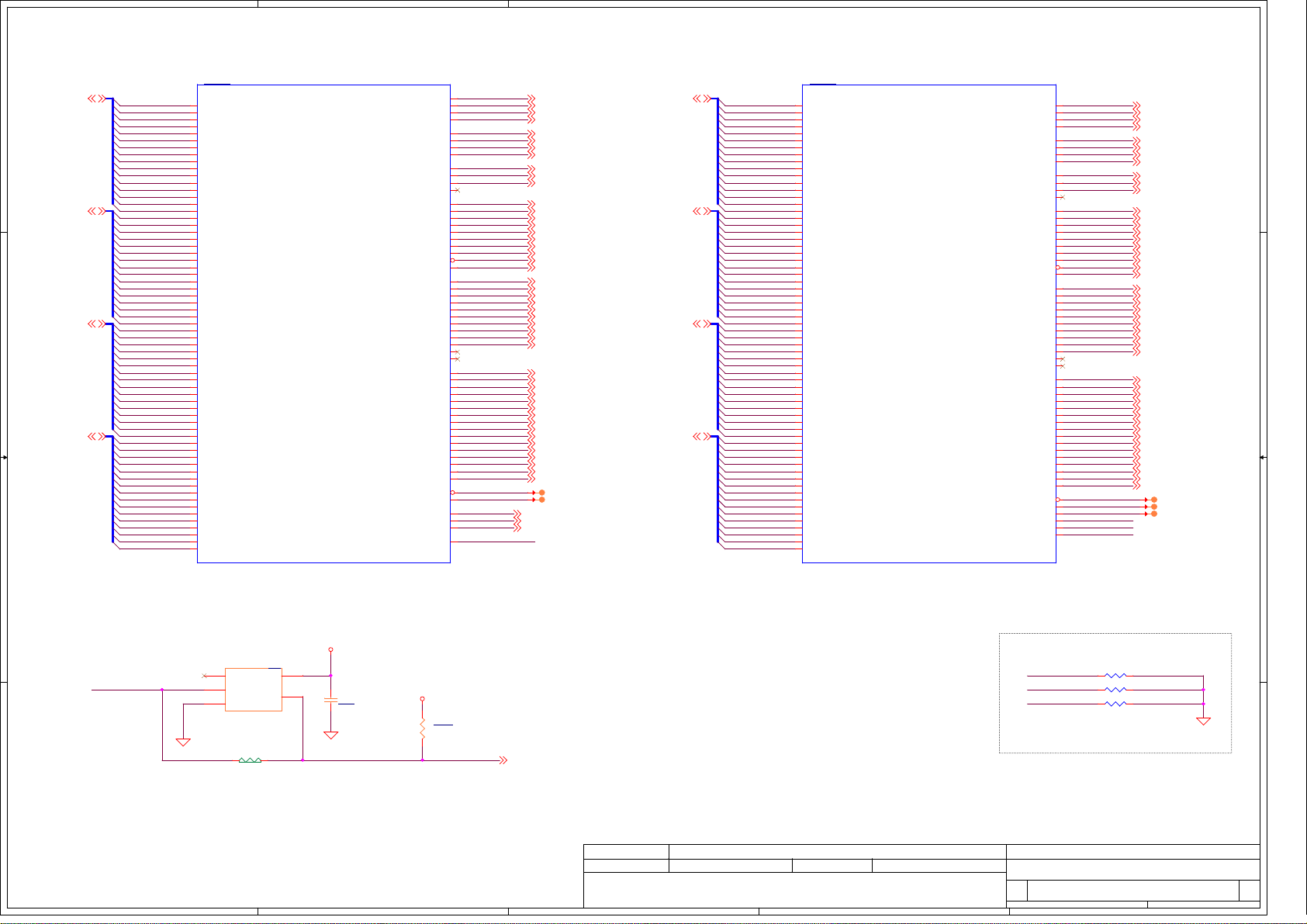

P07-MCP(1/14)DDI,EDP,CSI2,EMMC

P07-MCP(1/14)DDI,EDP,CSI2,EMMC

P07-MCP(1/14)DDI,EDP,CSI2,EMMC

LA-E671P

LA-E671P

LA-E671P

1

7 61Tuesday, October 17, 2017

7 61Tuesday, October 17, 2017

7 61Tuesday, October 17, 2017

1.0

1.0

1.0

5

LPDDR3, Ballout for side by side(Non-Interleave)

4

3

2

1

UCPU1B

@

DDR_A_D0

AL71

DDR_A_D1

DDR_A_D2

D D

DDR_A_D[32..47]<21>

DDR_B_D[0..15]<22>

C C

DDR_B_D[32..47]<22>

B B

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR0_DQ[0]

AL68

DDR0_DQ[1]

AN68

DDR0_DQ[2]

AN69

DDR0_DQ[3]

AL70

DDR0_DQ[4]

AL69

DDR0_DQ[5]

AN70

DDR0_DQ[6]

AN71

DDR0_DQ[7]

AR70

DDR0_DQ[8]

AR68

DDR0_DQ[9]

AU71

DDR0_DQ[10]

AU68

DDR0_DQ[11]

AR71

DDR0_DQ[12]

AR69

DDR0_DQ[13]

AU70

DDR0_DQ[14]

AU69

DDR0_DQ[15]

BB65

DDR0_DQ[16]/DDR0_DQ[32]

AW65

DDR0_DQ[17]/DDR0_DQ[33]

AW63

DDR0_DQ[18]/DDR0_DQ[34]

AY63

DDR0_DQ[19]/DDR0_DQ[35]

BA65

DDR0_DQ[20]/DDR0_DQ[36]

AY65

DDR0_DQ[21]/DDR0_DQ[37]

BA63

DDR0_DQ[22]/DDR0_DQ[38]

BB63

DDR0_DQ[23]/DDR0_DQ[39]

BA61

DDR0_DQ[24]/DDR0_DQ[40]

AW61

DDR0_DQ[25]/DDR0_DQ[41]

BB59

DDR0_DQ[26]/DDR0_DQ[42]

AW59

DDR0_DQ[27]/DDR0_DQ[43]

BB61

DDR0_DQ[28]/DDR0_DQ[44]

AY61

DDR0_DQ[29]/DDR0_DQ[45]

BA59

DDR0_DQ[30]/DDR0_DQ[46]

AY59

DDR0_DQ[31]/DDR0_DQ[47]

AY39

DDR0_DQ[32]/DDR1_DQ[0]

AW39

DDR0_DQ[33]/DDR1_DQ[1]

AY37

DDR0_DQ[34]/DDR1_DQ[2]

AW37

DDR0_DQ[35]/DDR1_DQ[3]

BB39

DDR0_DQ[36]/DDR1_DQ[4]

BA39

DDR0_DQ[37]/DDR1_DQ[5]

BA37

DDR0_DQ[38]/DDR1_DQ[6]

BB37

DDR0_DQ[39]/DDR1_DQ[7]

AY35

DDR0_DQ[40]/DDR1_DQ[8]

AW35

DDR0_DQ[41]/DDR1_DQ[9]

AY33

DDR0_DQ[42]/DDR1_DQ[10]

AW33

DDR0_DQ[43]/DDR1_DQ[11]

BB35

DDR0_DQ[44]/DDR1_DQ[12]

BA35

DDR0_DQ[45]/DDR1_DQ[13]

BA33

DDR0_DQ[46]/DDR1_DQ[14]

BB33

DDR0_DQ[47]/DDR1_DQ[15]

AY31

DDR0_DQ[48]/DDR1_DQ[32]

AW31

DDR0_DQ[49]/DDR1_DQ[33]

AY29

DDR0_DQ[50]/DDR1_DQ[34]

AW29

DDR0_DQ[51]/DDR1_DQ[35]

BB31

DDR0_DQ[52]/DDR1_DQ[36]

BA31

DDR0_DQ[53]/DDR1_DQ[37]

BA29

DDR0_DQ[54]/DDR1_DQ[38]

BB29

DDR0_DQ[55]/DDR1_DQ[39]

AY27

DDR0_DQ[56]/DDR1_DQ[40]

AW27

DDR0_DQ[57]/DDR1_DQ[41]

AY25

DDR0_DQ[58]/DDR1_DQ[42]

AW25

DDR0_DQ[59]/DDR1_DQ[43]

BB27

DDR0_DQ[60]/DDR1_DQ[44]

BA27

DDR0_DQ[61]/DDR1_DQ[45]

BA25

DDR0_DQ[62]/DDR1_DQ[46]

BB25

DDR0_DQ[63]/DDR1_DQ[47]

SKL-U_BGA1356

SKL-U

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR CH - A

DDR0_ODT[1]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR0_ALERT#

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR_VTT_CNTL

DDR0_MA[3]

DDR0_MA[4]

DDR0_PAR

2 OF 20

AU53

AT53

AU55

AT55

BA56

BB56

AW56

AY56

AU45

AU43

AT45

AT43

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

AM70

AM69

AT69

AT70

BA64

AY64

AY60

BA60

BA38

AY38

AY34

BA34

BA30

AY30

AY26

BA26

AW50

AT52

AY67

AY68

BA67

AW67

DDR_A_CLK#0

DDR_A_CLK0

DDR_A_CLK#1

DDR_A_CLK1

DDR_A_CKE0

DDR_A_CKE1

DDR_A_CKE2

DDR_A_CKE3

DDR_A_CS#0

DDR_A_CS#1

DDR_A_ODT0

DDR_VTT_CNTL

DDR_A_CLK#0 <21,23>

DDR_A_CLK0 <21,23>

DDR_A_CLK#1 <21,23>

DDR_A_CLK1 <21,23>

DDR_A_CKE0 <21,23>

DDR_A_CKE1 <21,23>

DDR_A_CKE2 <21,23>

DDR_A_CKE3 <21,23>

DDR_A_CS#0 <21,23>

DDR_A_CS#1 <21,23>

DDR_A_ODT0 <21,23>

DDR_A_CA1_0 <21,23>

DDR_A_CA1_1 <21,23>

DDR_A_CA1_2 <21,23>

DDR_A_CA1_3 <21,23>

DDR_A_CA1_4 <21,23>

DDR_A_CA1_5 <21,23>

DDR_A_CA1_6 <21,23>

DDR_A_CA1_7 <21,23>

DDR_A_CA1_8 <21,23>

DDR_A_CA1_9 <21,23>

DDR_A_CA2_0 <21,23>

DDR_A_CA2_1 <21,23>

DDR_A_CA2_2 <21,23>

DDR_A_CA2_3 <21,23>

DDR_A_CA2_4 <21,23>

DDR_A_CA2_5 <21,23>

DDR_A_CA2_6 <21,23>

DDR_A_CA2_7 <21,23>

DDR_A_CA2_8 <21,23>

DDR_A_CA2_9 <21,23>

DDR_A_DQS#0 <21>

DDR_A_DQS0 <21>

DDR_A_DQS#1 <21>

DDR_A_DQS1 <21>

DDR_A_DQS#4 <21>

DDR_A_DQS4 <21>

DDR_A_DQS#5 <21>

DDR_A_DQS5 <21>

DDR_B_DQS#0 <22>

DDR_B_DQS0 <22>

DDR_B_DQS#1 <22>

DDR_B_DQS1 <22>

DDR_B_DQS#4 <22>

DDR_B_DQS4 <22>

DDR_B_DQS#5 <22>

DDR_B_DQS5 <22>

@

T3

PAD~D

@

T4

PAD~D

+V_DDR_REF_CA <23>

+V_DDR_REFA_R <23>

+V_DDR_REFB_R <23>

UCPU1C

@

DDR_A_D[16..31]<21>DDR_A_D[0..15]<21>

DDR_A_D[48..63]<21>

DDR_B_D[16..31]<22>

DDR_B_D[48..63]<22>

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

AF65

DDR1_DQ[0]/DDR0_DQ[16]

AF64

DDR1_DQ[1]/DDR0_DQ[17]

AK65

DDR1_DQ[2]/DDR0_DQ[18]

AK64

DDR1_DQ[3]/DDR0_DQ[19]

AF66

DDR1_DQ[4]/DDR0_DQ[20]

AF67

DDR1_DQ[5]/DDR0_DQ[21]

AK67

DDR1_DQ[6]/DDR0_DQ[22]

AK66

DDR1_DQ[7]/DDR0_DQ[23]

AF70

DDR1_DQ[8]/DDR0_DQ[24]

AF68

DDR1_DQ[9]/DDR0_DQ[25]

AH71

DDR1_DQ[10]/DDR0_DQ[26]

AH68

DDR1_DQ[11]/DDR0_DQ[27]

AF71

DDR1_DQ[12]/DDR0_DQ[28]

AF69

DDR1_DQ[13]/DDR0_DQ[29]

AH70

DDR1_DQ[14]/DDR0_DQ[30]

AH69

DDR1_DQ[15]/DDR0_DQ[31]

AT66

DDR1_DQ[16]/DDR0_DQ[48]

AU66

DDR1_DQ[17]/DDR0_DQ[49]

AP65

DDR1_DQ[18]/DDR0_DQ[50]

AN65

DDR1_DQ[19]/DDR0_DQ[51]

AN66

DDR1_DQ[20]/DDR0_DQ[52]

AP66

DDR1_DQ[21]/DDR0_DQ[53]

AT65

DDR1_DQ[22]/DDR0_DQ[54]

AU65

DDR1_DQ[23]/DDR0_DQ[55]

AT61

DDR1_DQ[24]/DDR0_DQ[56]

AU61

DDR1_DQ[25]/DDR0_DQ[57]

AP60

DDR1_DQ[26]/DDR0_DQ[58]

AN60

DDR1_DQ[27]/DDR0_DQ[59]

AN61

DDR1_DQ[28]/DDR0_DQ[60]

AP61

DDR1_DQ[29]/DDR0_DQ[61]

AT60

DDR1_DQ[30]/DDR0_DQ[62]

AU60

DDR1_DQ[31]/DDR0_DQ[63]

AU40

DDR1_DQ[32]/DDR1_DQ[16]

AT40

DDR1_DQ[33]/DDR1_DQ[17]

AT37

DDR1_DQ[34]/DDR1_DQ[18]

AU37

DDR1_DQ[35]/DDR1_DQ[19]

AR40

DDR1_DQ[36]/DDR1_DQ[20]

AP40

DDR1_DQ[37]/DDR1_DQ[21]

AP37

DDR1_DQ[38]/DDR1_DQ[22]

AR37

DDR1_DQ[39]/DDR1_DQ[23]

AT33

DDR1_DQ[40]/DDR1_DQ[24]

AU33

DDR1_DQ[41]/DDR1_DQ[25]

AU30

DDR1_DQ[42]/DDR1_DQ[26]

AT30

DDR1_DQ[43]/DDR1_DQ[27]

AR33

DDR1_DQ[44]/DDR1_DQ[28]

AP33

DDR1_DQ[45]/DDR1_DQ[29]

AR30

DDR1_DQ[46]/DDR1_DQ[30]

AP30

DDR1_DQ[47]/DDR1_DQ[31]

AU27

DDR1_DQ[48]

AT27

DDR1_DQ[49]

AT25

DDR1_DQ[50]

AU25

DDR1_DQ[51]

AP27

DDR1_DQ[52]

AN27

DDR1_DQ[53]

AN25

DDR1_DQ[54]

AP25

DDR1_DQ[55]

AT22

DDR1_DQ[56]

AU22

DDR1_DQ[57]

AU21

DDR1_DQ[58]

AT21

DDR1_DQ[59]

AN22

DDR1_DQ[60]

AP22

DDR1_DQ[61]

AP21

DDR1_DQ[62]

AN21

DDR1_DQ[63]

SKL-U_BGA1356

SKL-U

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DRAM_RESET#

DDR_RCOMP[0]

DDR CH - B

DDR_RCOMP[1]

DDR_RCOMP[2]

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[3]

DDR1_MA[4]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

3 OF 20

AN45

AN46

AP45

AP46

AN56

AP55

AN55

AP53

BB42

AY42

BA42

AW42

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

AH66

AH65

AG69

AG70

AR66

AR65

AR61

AR60

AT38

AR38

AT32

AR32

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

DDR_B_CLK#0

DDR_B_CLK#1

DDR_B_CLK0

DDR_B_CLK1

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CKE2

DDR_B_CKE3

DDR_B_CS#0

DDR_B_CS#1

DDR_B_ODT0

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

DDR_B_CLK#0 <22,23>

DDR_B_CLK#1 <22,23>

DDR_B_CLK0 <22,23>

DDR_B_CLK1 <22,23>

DDR_B_CKE0 <22,23>

DDR_B_CKE1 <22,23>

DDR_B_CKE2 <22,23>

DDR_B_CKE3 <22,23>

DDR_B_CS#0 <22,23>

DDR_B_CS#1 <22,23>

DDR_B_ODT0 <22,23>

DDR_B_CA1_0 <22,23>

DDR_B_CA1_1 <22,23>

DDR_B_CA1_2 <22,23>

DDR_B_CA1_3 <22,23>

DDR_B_CA1_4 <22,23>

DDR_B_CA1_5 <22,23>

DDR_B_CA1_6 <22,23>

DDR_B_CA1_7 <22,23>

DDR_B_CA1_8 <22,23>

DDR_B_CA1_9 <22,23>

DDR_B_CA2_0 <22,23>

DDR_B_CA2_1 <22,23>

DDR_B_CA2_2 <22,23>

DDR_B_CA2_3 <22,23>

DDR_B_CA2_4 <22,23>

DDR_B_CA2_5 <22,23>

DDR_B_CA2_6 <22,23>

DDR_B_CA2_7 <22,23>

DDR_B_CA2_8 <22,23>

DDR_B_CA2_9 <22,23>

DDR_A_DQS#2 <21>

DDR_A_DQS2 <21>

DDR_A_DQS#3 <21>

DDR_A_DQS3 <21>

DDR_A_DQS#6 <21>

DDR_A_DQS6 <21>

DDR_A_DQS#7 <21>

DDR_A_DQS7 <21>

DDR_B_DQS#2 <22>

DDR_B_DQS2 <22>

DDR_B_DQS#3 <22>

DDR_B_DQS3 <22>

DDR_B_DQS#6 <22>

DDR_B_DQS6 <22>

DDR_B_DQS#7 <22>

DDR_B_DQS7 <22>

@

T5

PAD~D

@

T6

PAD~D

@

T7

PAD~D

+1.2V_DDR

NC

A

GND

@

1 2

UC9

5

VCC

4

Y

@

1

@

CC92

0.1U_0402_10V7K

2

+3VS

12

@

RE241

100K_0402_5%

SM_PG_CTRL <52>

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2015/12/16 2016/12/13

2015/12/16 2016/12/13

2015/12/16 2016/12/13

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

DDR_VTT_CNTL

A A

5

1

2

3

SN74AUP1G07DCKR_SC70

RC383 0_0402_1%

LPDDR3 COMPENSATION SIGNALS

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

CAD Note:

Trace width=12~15 mil, Spacing=20 mils

Max trace length= 500 mil

1 2

RC11 200_0402_1%

1 2

RC12 80.6_0402_1%

1 2

RC13 162_0402_1%

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P08-MCP(2/14)LPDDR3

P08-MCP(2/14)LPDDR3

P08-MCP(2/14)LPDDR3

LA-E671P

LA-E671P

LA-E671P

1

8 61Tuesday, October 17, 2017

8 61Tuesday, October 17, 2017

8 61Tuesday, October 17, 2017

0.1

0.1

0.1

5

SPI_MOSI= SPI_IO0

SPI_MISO= SPI_IO1

PCH EDS R0.7 p.235~236

PCH_SPI_CLK

PCH_SPI_SO

MEDIACARD_IRQ#

CL_CLK<28>

CL_DAT<28>

CL_RST#<28>

SIO_RCIN#

ESPI_ALERT#

PCH_SPI_SI

PCH_SPI_IO2

PCH_SPI_IO3

PCH_SPI_CS0#

PCH_SPI_SI<15>

1 2

1 2

1 2

PCH_SPI_IO2<15>

PCH_SPI_CS2#<27>

TPM_PIRQ#<27>

MEDIACARD_IRQ#<29>

MEDIACARD_IRQ#

SIO_RCIN#

ESPI_ALERT#

ESPI_ALERT#<38>

D D

+3V_PCH

RC17 10K_0402_5%@

+3.3V_1.8V_ESPI

RC21 10K_0402_5%@

RC24 10K_0402_1%

C C

AV2

AW3

AV3

AW2

AU4

AU3

AU2

AU1

AW13

AY11

M2

M3

J4

V1

V2

M1

G3

G2

G1

4

UCPU1E

@

SPI - FLASH

SPI0_CLK

SPI0_MISO

SPI0_MOSI

SPI0_IO2

SPI0_IO3

SPI0_CS0#

SPI0_CS1#

SPI0_CS2#

SPI - TOUCH

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_D3/SPI1_MOSI

GPP_D21/SPI1_IO2

GPP_D22/SPI1_IO3

GPP_D0/SPI1_CS#

C LINK

CL_CLK

CL_DATA

CL_RST#

GPP_A0/RCIN#

GPP_A6/SERIRQ

SKL-U_BGA1356

SKL-U

SMBUS, SMLINK

LPC

GPP_A14/SUS_STAT#/ESPI_RESET#

3

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

GPP_A8/CLKRUN#

5 OF 20

R7

R8

R10

R9

W2

W1

W3

V3

AM7

AY13

BA13

BB13

AY12

BA12

BA11

AW9

AY9

AW11

MEM_SMBCLK

MEM_SMBDATA

PCH_SMB_ALERT#

GPP_C5

SML1_SMBCLK

SML1_SMBDAT

GPP_B23

ESPI_IO0_R

ESPI_IO1_R

ESPI_IO2_R

ESPI_IO3_R

PCI_CLK_LPC0

PCI_CLK_LPC1

CLKRUN#

PWR_MONITOR_SMBCLK <35>

PWR_MONITOR_SMBDAT <35>

SML1_SMBCLK <38>

SML1_SMBDAT <38>

1 2

RC366 15_0402_5%

1 2

RC367 15_0402_5%

1 2

RC368 15_0402_5%

1 2

RC369 15_0402_5%

ESPI_CS# <38,39>

ESPI_RESET# <38>

1 2

RC19 EMC@15_0402_5%

1 2

RC22 22_0402_5% @

2

ESPI_IO0 <38,39>

ESPI_IO1 <38,39>

ESPI_IO2 <38,39>

ESPI_IO3 <38,39>

MEM_SMBCLK

MEM_SMBDATA

RC387 0_0402_1%@

+3VS

6

@

5

DMN66D0LDW-7_SOT363-6

3 4

QC1B

@

DMN66D0LDW-7_SOT363-6

1 2

ESPI_CLK_5105 <38,39>

RC388 0_0402_1%@

2

DDR_XDP_SMBCLK

1

QC1A

DDR_XDP_SMBDAT

DDR_XDP_SMBCLK

MEM_SMBCLK

MEM_SMBDATA

SML1_SMBCLK

SML1_SMBDAT

PVT_0008

1 2

DDR_XDP_SMBDAT

CLKRUN#

1

DDR_XDP_SMBCLK <15>

DDR_XDP_SMBDAT <15>

12

RN12.2K_0402_5%

12

RN22.2K_0402_5%

12

RC168.2K_0402_5%

+3V_PCH

1 2

RC18 1K_0402_5%@

1 2

RC20 1K_0402_5%@

1 2

RC23 1K_0402_5%

1 2

RC25 1K_0402_5%

+3VS

SPI_SI_VROM

PCH_SPI_CLK_TPM<27>

PCH_SPI_SI_TPM<27>

SPI_CLK_VROM

PVT_0012

+3V_PCH

ROM is Quad SPI

PCH_SPI_CS0#_R

SPI_SO_VROM

SPI_IO2_VROM SPI_CLK_VROM

B B

SPI ROM FOR ME ( 32 MByte )

U1

1

CS#

2

HOLD#_RESET#

DO

3

WP#

4

GND

W25Q256FVEIQ_WSON8

VCC

CLK

8

7

6

5

DI

1 2

0.1U_0402_25V6

SPI_IO3_VROM

SPI_SI_VROM

CC4

PCH_SPI_SO_TPM<27>

SPI_SO_VROM

SPI_IO2_VROM

SPI_IO3_VROM

RP1

1 8

2 7

3 6

4 5

33_8P4R_5%

RP2

1 8

2 7

3 6

4 5

33_8P4R_5%

SPI_CLK_VROM

33_0402_5%

RC28@

1 2

33P_0402_50V8J

1 2

from CPU to SPI ROM

JSPI1

1

1

2

PCH_SPI_SI

PCH_SPI_SO

PCH_SPI_CLK

PCH_SPI_CS0#

PCH_SPI_IO2

PCH_SPI_IO3

+3V_PCH

+3VALW

A A

Serial Peripheral Interface (SPI) Topology Guidelines

1 2

RC30 0_0402_1%@

1 2

RC31 0_0402_1%@

1 2

RC32 0_0402_1%@

1 2

RC33 0_0402_1%@

1 2

RC34 0_0402_1%@

1 2

RC35 0_0402_1%@

1 2

RC36 0_0402_1%@

1 2

RC37 0_0402_5%

@

PCH_SPI_SI_R

PCH_SPI_SO_R

PCH_SPI_CLK_R

PCH_SPI_CS0#_R

PCH_SPI_IO2_R

PCH_SPI_IO3_R

PCH SPI

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

GND_1

22

GND_2

ACES_50696-0200M-P01

CONN@

TPM

JSPI

5

4

PCH_SPI_SI_R

PCH_SPI_CLK_R

PCH_SPI_SO_R

PCH_SPI_IO2_R

PCH_SPI_IO3_R

+3V_PCH

RH61 1K_0402_5%~D@

RH62 1K_0402_5%~D@

CC5@

Option 1: Implement a 1 k Ohm pull-down resistor on the signal and de-populate the

required 1 kOhm pull-up resistor(MOW WW5).

In this case, customers mu st ensure that the SPI

flash device on the platform has HOLD f unctionality disabled by d efault.

Note that the pull down resistor on SPI0_IO3 is only needed for SKL U/Y platforms

with ES and SKL S/H platforms with pre-ES1/ES1 samples(MOW WW9).

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

RH63 1K_0402_5%~D@

2015/12/16 2016/12/13

2015/12/16 2016/12/13

2015/12/16 2016/12/13

ESPI_CLK_5105

1 2

1 2

1 2

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Reserve for RF

PCH_SPI_IO2

PCH_SPI_IO3

PCH_SPI_IO3

2

12

EMC@12P_0402_50V8J

CC2

PCH_SMB_ALERT#

1 2

RC26 2.2K_0402_5%

TLS C ONFIDENTIALITY

HIGH

LOW(DEFAULT)

GPP_C5

1 2

RC27 4.7K_0402_5%

EC interface

HIGH

LOW(DEFAULT)

@

GPP_B23

RC29

1 2

EXI BOOT STALL BYPASS

HIGH

LOW(DEFAULT)

RC29 DCI need pop 4.7 k ohm

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P09-MCP(3/14)SPI,SMB,LPC

P09-MCP(3/14)SPI,SMB,LPC

P09-MCP(3/14)SPI,SMB,LPC

LA-E671P

LA-E671P

LA-E671P

1

ENABLE

DISAB LE

ESPI

LPC

150K_0402_1%

ENABLE

DISAB LE

9 61Tuesday, October 17, 2017

9 61Tuesday, October 17, 2017

9 61Tuesday, October 17, 2017

+3V_PCH

+3V_PCH

+3V_PCH

1.0

1.0

1.0

5

4

3

2

1

UCPU1F

@

LPSS ISH

+3VS

HOST_SD_WP#

1 2

D D

RC38 10K_0402_5%

RC39 10K_0402_5%

RH64 49.9K_0402_1%

RH65 49.9K_0402_1%

1 2

1 2

1 2

SIO_EXT_SCI#

UART1_TXD

UART1_RXD

change to net name ==> I2C0_SDA_TS and I2C0_SCK_TS

+3V_PCH

SIO_EXT_WAKE#

1 2

RC40 10K_0402_5%

TS_I2C_RST#<37>

TS

TP

eDP

PWRMON ITOR

PWR_MONITOR_I2CSDA<35>

PWR_MONITOR_I2CCLK<35>

TPM_DET

DBC_EN<37>

NRB_BIT

@

PAD~D

SIO_EXT_SCI#

GPP_B22

HOST_SD_WP#

SIO_EXT_WAKE#

I2C1_SDA_TP

I2C1_SCK_TP

3.3V_TS_EN<33>

SBIOS_TX<39>

HOST_SD_WP#<29>

SIO_EXT_WAKE#<38>

T8

I2C0_SDA_TS<37>

I2C0_SCK_TS<37>

I2C1_SDA_TP<36>

I2C1_SCK_TP<36>

I2C2_SDA_EDP_PCH<37>

I2C2_SCK_EDP_PCH<37>

change to net name ==> I2C2_SDA_EDP_PCH and I2C2_SCK_EDP_PCH

C C

TBT_PWR_EN

RH70 100K_0402_5%~D

12

AN8

GPP_B15/GSPI0_CS#

AP7

GPP_B16/GSPI0_CLK

AP8

GPP_B17/GSPI0_MISO

AR7

GPP_B18/GSPI0_MOSI

AM5

GPP_B19/GSPI1_CS#

AN7

GPP_B20/GSPI1_CLK

AP5

GPP_B21/GSPI1_MISO

AN5

GPP_B22/GSPI1_MOSI

AB1

GPP_C8/UART0_RXD

AB2

GPP_C9/UART0_TXD

W4

GPP_C10/UART0_RTS#

AB3

GPP_C11/UART0_CTS#

AD1

GPP_C20/UART2_RXD

AD2

GPP_C21/UART2_TXD

AD3

GPP_C22/UART2_RTS#

AD4

GPP_C23/UART2_CTS#

U7

GPP_C16/I2C0_SDA

U6

GPP_C17/I2C0_SCL

U8

GPP_C18/I2C1_SDA

U9

GPP_C19/I2C1_SCL

AH9

GPP_F4/I2C2_SDA

AH10

GPP_F5/I2C2_SCL

AH11

GPP_F6/I2C3_SDA

AH12

GPP_F7/I2C3_SCL

AF11

GPP_F8/I2C4_SDA

AF12

GPP_F9/I2C4_SCL

SKL-U_BGA1356

TPM_DET

TPM_DET

TPM BOM Optional

+3V_PCH

NRB_BIT

1 2

RC45 2.2K_0402_5%@

NO REBOOT STRAP

HIGH

B B

LOW(DEFAULT)

Weak IPD

+3V_PCH

12

@

2.2K_0402_5%

RC46

GPP_B22

No REBOOT

REBOOT ENABLE

TPM_DET

TPM

UART1_TXD

UART1_RXD

1 = W/TPM

0 = W/O TPM

+5VS

SKL-U

12

RH71100K_0402_5%

1 2

RH72100K_0402_5% @

JUART1

1

1

2

2

3

3

4

4

5

GND

6

GND

CVILU_CI1804M1VRA-NH

CONN@

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD/SML0BDATA/I2C4B_SDA

GPP_D14/ISH_UART0_TXD/SML0BCLK/I2C4B_SCL

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

+3V_PCH

GPP_D15/ISH_UART0_RTS#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

GPP_A12/BM_BUSY#/ISH_GP6

GPP_D9

GPP_D10

GPP_D11

GPP_D12

6 OF 20

P2

P3

P4

P1

M4

N3

N1

N2

AD11

AD12

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

DCI_CLK <31>

DCI_DATA <31>

DDR_CHB_EN

DDR_CHA_EN

BID_BC

PCH_TBT_PERST#

UART1_RXD

UART1_TXD

SUPPLIER_ID0

SUPPLIER_ID1

TBT_PWR_EN

PCH_TBT_PERST# <41>

PCH_MUTE# <24>

@

PAD~D

+3.3V_1.8V_PGPPA +3.3V_1.8V_PGPPA

1 2

@

1 2

RH88 RH89

*

V V

V V

V V

PVT_0011

T9

100K_0402_5%

RH87

100K_0402_5%

RH88

RH86RH87

+3VS

DDR_CHA_EN

DDR_CHB_EN

DDR_CHA_EN

DDR_CHB_EN

PCH_TBT_PERST#

PCH_TBT_PERST#

Produc t

XPS

L

POP

RH84

RH85

1 2

RH66 100K_0402_5%~D

1 2

RH67 100K_0402_5%~D

1 2

RH68 SHORT PADS@

1 2

RH69 SHORT PADS@

RC395

@

1 2

High

Low

@

12

RH90100K_0402_5%~D

+3V_PCH

1 2

1 2

1 2

@

1 2

RH84

100K_0201_5%

RH85

100K_0201_5%

100K_0402_5%

RH86

100K_0402_5%

RH89

10K_0402_5%

BID_BC

STATUS

SUPPLIER_ID0SUPPLIER_ID1

+3V_PCH

XPS@

L@

REV

0 0

VV

0 1

1 0

1 1

Supplier A

Supplier B

Supplier C

Supplier D

BOOT BIOS Dest i nat i on(Bi t 6)

HIGH

LOW(DEFAULT)

LPC

SPI

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2015/12/16 2016/12/13

2015/12/16 2016/12/13

2015/12/16 2016/12/13

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

P10-MCP(4/14)GSPI,I2C,UART,ISH

P10-MCP(4/14)GSPI,I2C,UART,ISH

P10-MCP(4/14)GSPI,I2C,UART,ISH

LA-E671P

LA-E671P

LA-E671P

1

10 61Tuesday, October 17, 2017

10 61Tuesday, October 17, 2017

10 61Tuesday, October 17, 2017

1.0

1.0

1.0

5

4

3

2

1

UCPU1H

@

PCIE/US B3/SATA

D D

C C

M.2 SSD

PCIe Gen3 x 4

B B

Cardreade r

PCIe Gen2 x 1

WLAN

PCIe Gen2 x 1

Alpine Ridge

PCIe Gen3 x 4

SATA SSD

PCIE_PRX_CARDTX_N1<29>

PCIE_PRX_CARDTX_P1<29>

PCIE_PTX_CARDRX_N1<29>

PCIE_PTX_CARDRX_P1<29>

PCIE_PRX_WLANTX_N3<28>

PCIE_PRX_WLANTX_P3<28>

PCIE_PTX_WLANRX_N3<28>

PCIE_PTX_WLANRX_P3<28>

PCIE_PRX_TBTX_N5<41>

PCIE_PRX_TBTX_P5<41>

PCIE_PTX_TBRX_N5<41>

PCIE_PTX_TBRX_P5<41>

PCIE_PRX_TBTX_N6<41>

PCIE_PRX_TBTX_P6<41>

PCIE_PTX_TBRX_N6<41>

PCIE_PTX_TBRX_P6<41>

PCIE_PRX_TBTX_N7<41>

PCIE_PRX_TBTX_P7<41>

PCIE_PTX_TBRX_N7<41>

PCIE_PTX_TBRX_P7<41>

PCIE_PRX_TBTX_N8<41>

PCIE_PRX_TBTX_P8<41>

PCIE_PTX_TBRX_N8<41>

PCIE_PTX_TBRX_P8<41>

PCIE_PRX_SSDTX_N9<30>

PCIE_PRX_SSDTX_P9<30>

PCIE_PTX_SSDRX_N9<30>

PCIE_PTX_SSDRX_P9<30>

PCIE_PRX_SSDTX_N10<30>

PCIE_PRX_SSDTX_P10<30>

PCIE_PTX_SSDRX_N10<30>

PCIE_PTX_SSDRX_P10<30>

1 2

RC50 100_0402_1%

CPU_XDP_PRDY#<15>

CPU_XDP_PREQ#<15>

PCIE_PRX_SSDTX_N11<30>

PCIE_PRX_SSDTX_P11<30>

PCIE_PTX_SSDRX_N11<30>

PCIE_PTX_SSDRX_P11<30>

SATA_PRX_SSDTX_N2<30>

SATA_PRX_SSDTX_P2<30>

SATA_PTX_SSDRX_N2<30>

SATA_PTX_SSDRX_P2<30>

PCIE_RCOMPN

PCIE_RCOMPP

H13

PCIE1_RXN/USB3_5_RXN

G13

PCIE1_RXP/USB3_5_RXP

B17

PCIE1_TXN/USB3_5_TXN

A17

PCIE1_TXP/USB3_5_TXP

G11

PCIE2_RXN/USB3_6_RXN

F11

PCIE2_RXP/USB3_6_RXP

D16

PCIE2_TXN/USB3_6_TXN

C16

PCIE2_TXP/USB3_6_TXP

H16

PCIE3_RXN

G16

PCIE3_RXP

D17

PCIE3_TXN

C17

PCIE3_TXP

G15

PCIE4_RXN

F15

PCIE4_RXP

B19

PCIE4_TXN

A19

PCIE4_TXP

F16

PCIE5_RXN

E16

PCIE5_RXP

C19

PCIE5_TXN

D19

PCIE5_TXP

G18

PCIE6_RXN

F18

PCIE6_RXP

D20

PCIE6_TXN

C20

PCIE6_TXP

F20

PCIE7_RXN/SATA0_RXN

E20

PCIE7_RXP/SATA0_RXP

B21

PCIE7_TXN/SATA0_TXN

A21

PCIE7_TXP/SATA0_TXP

G21

PCIE8_RXN/SATA1A_RXN

F21

PCIE8_RXP/SATA1A_RXP

D21

PCIE8_TXN/SATA1A_TXN

C21

PCIE8_TXP/SATA1A_TXP

E22

PCIE9_RXN

E23

PCIE9_RXP

B23

PCIE9_TXN

A23

PCIE9_TXP

F25

PCIE10_RXN

E25

PCIE10_RXP

D23

PCIE10_TXN

C23

PCIE10_TXP

F5

PCIE_RCOMPN

E5

PCIE_RCOMPP

D56

PROC_PRDY#

D61

PROC_PREQ#

BB11

GPP_A7/PIRQA#

E28

PCIE11_RXN/SATA1B_RXN

E27

PCIE11_RXP/SATA1B_RXP

D24

PCIE11_TXN/SATA1B_TXN

C24

PCIE11_TXP/SATA1B_TXP

E30

PCIE12_RXN/SATA2_RXN

F30

PCIE12_RXP/SATA2_RXP

A25

PCIE12_TXN/SATA2_TXN

B25

PCIE12_TXP/SATA2_TXP

SKL-U_BGA1356

SKL-U

SSIC / USB3

USB3_2_RXN/SSIC_1_RXN

USB3_2_RXP/SSIC_1_RXP

USB3_2_TXN/SSIC_1_TXN

USB3_2_TXP/SSIC_1_TXP

USB3_3_RXN/SSIC_2_RXN

USB3_3_RXP/SSIC_2_RXP

USB3_3_TXN/SSIC_2_TXN

USB3_3_TXP/SSIC_2_TXP

USB2

USB2_VBUSSENSE

GPP_E9/USB2_OC0#

GPP_E10/USB2_OC1#

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

GPP_E8/SATALED#

USB3_1_RXN

USB3_1_RXP

USB3_1_TXN

USB3_1_TXP

USB3_4_RXN

USB3_4_RXP

USB3_4_TXN

USB3_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

USB2_ID

8 OF 20

H8

G8

C13

D13

J6

H6

B13

A13

J10

H10

B15

A15

E10

F10

C15

D15

AB9

AB10

AD6

AD7

AH3

AJ3

AD9