Dell XPS13 Schematics

Vinafix.com

1

2

3

4

5

6

7

8

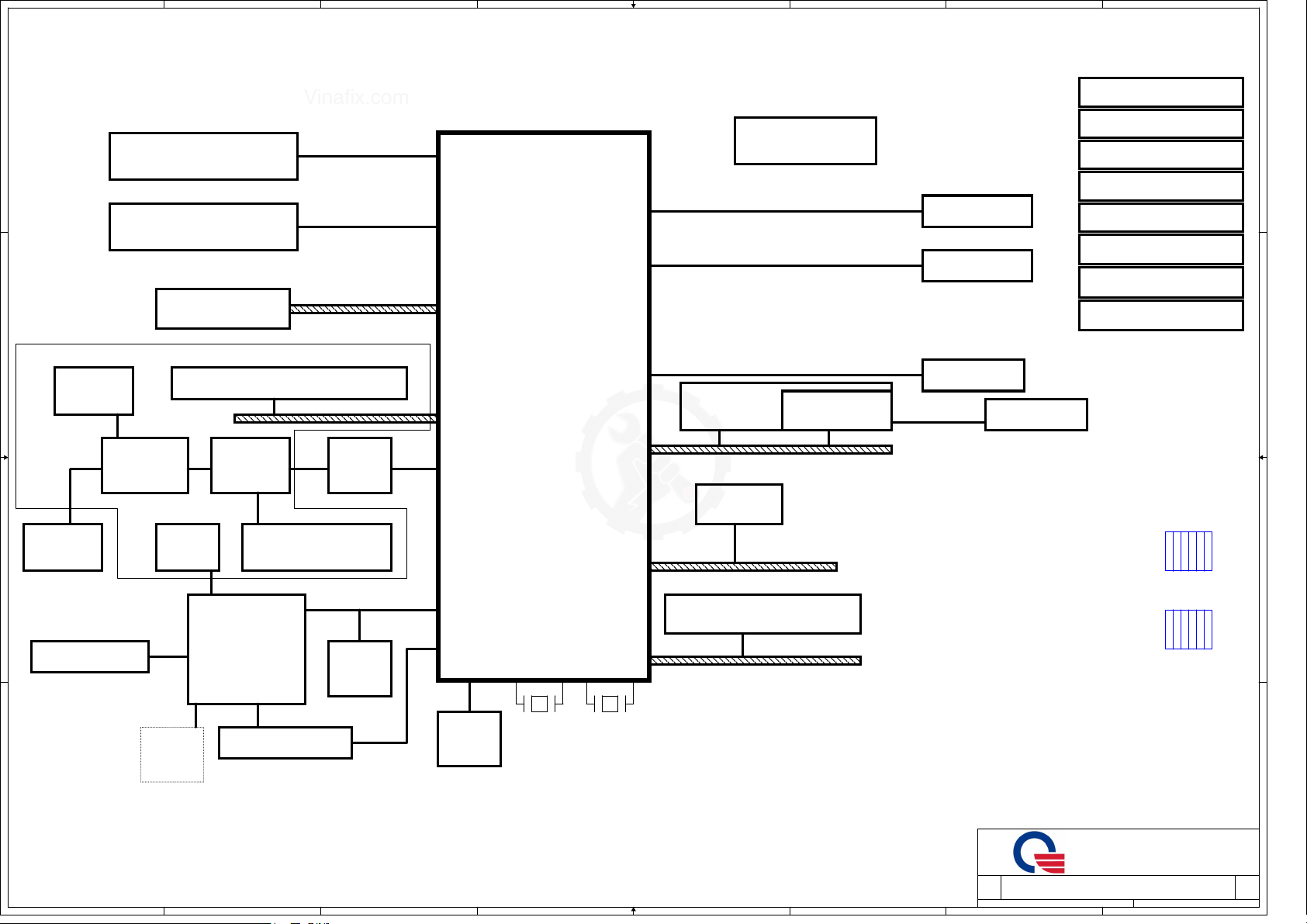

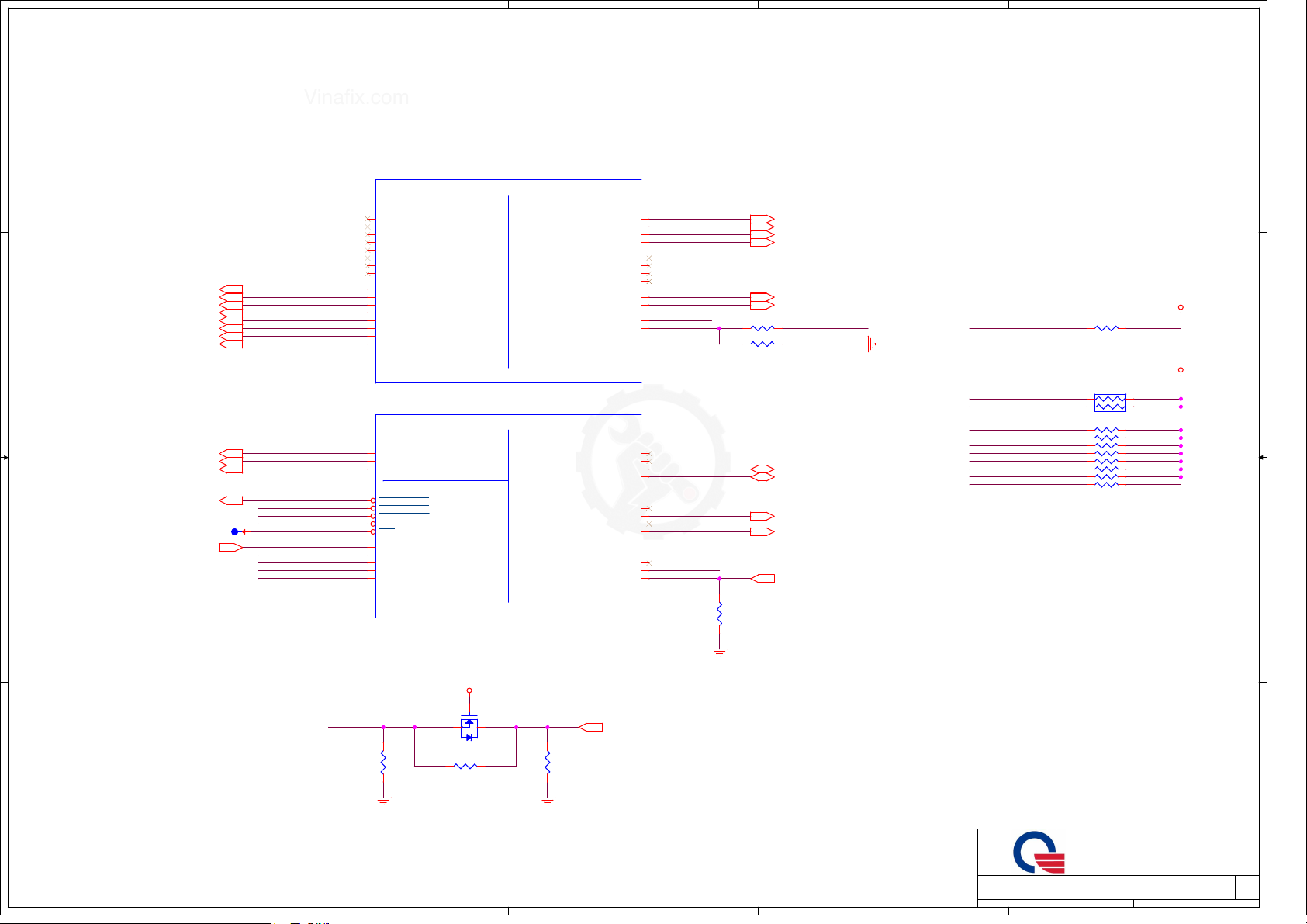

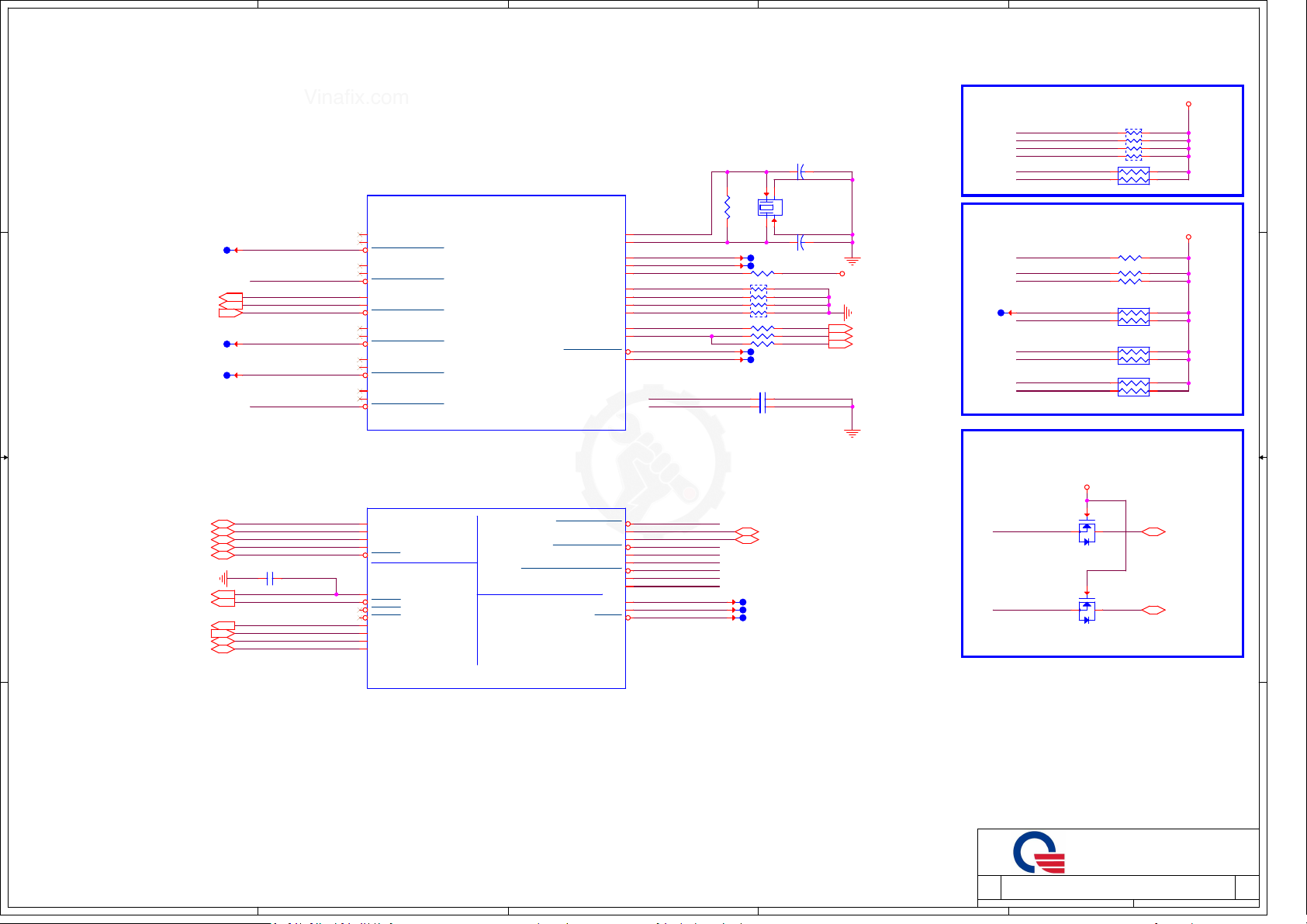

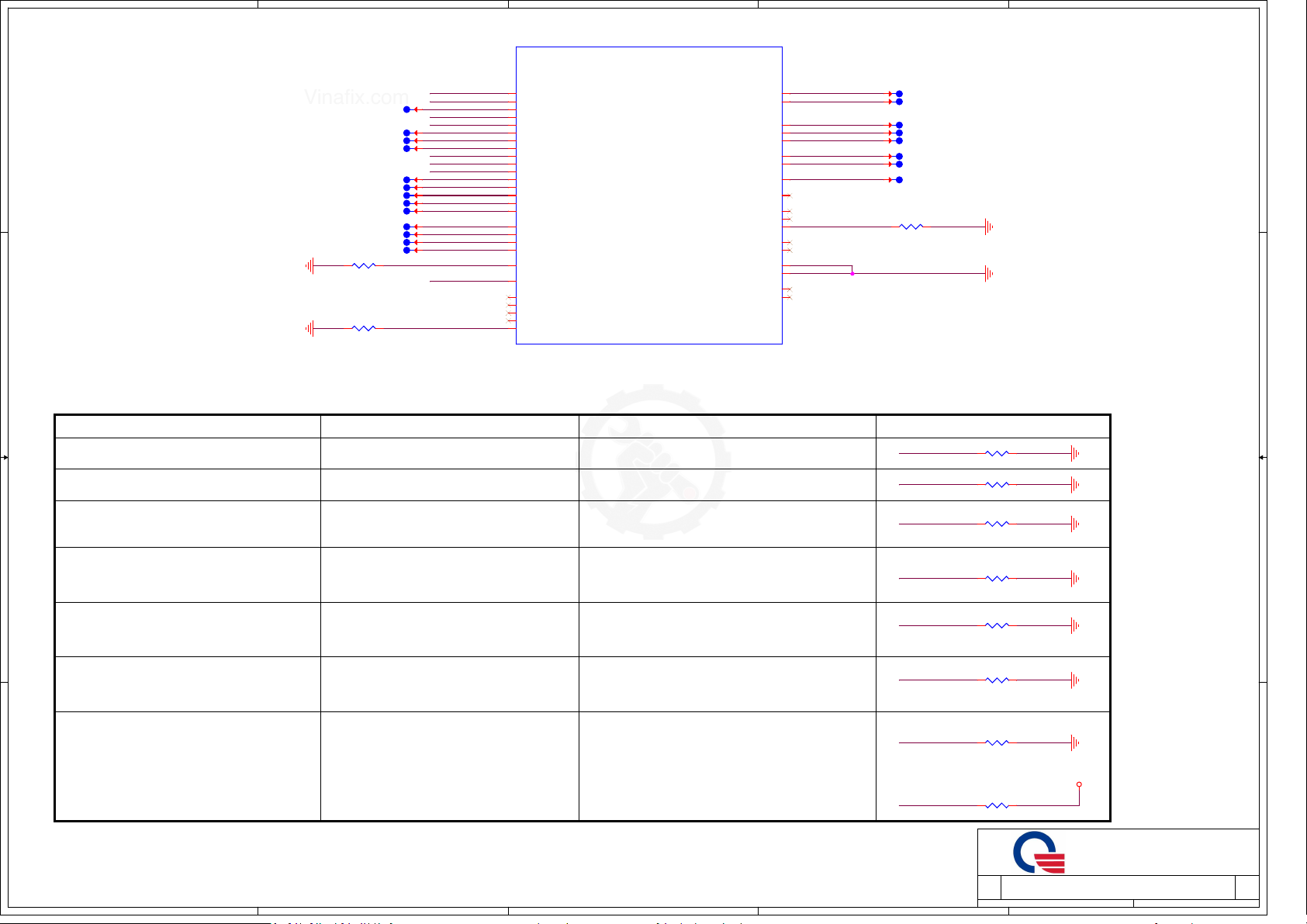

Spyder ULT 13.3" Block Diagram

A A

DDR3L-RS-Memory Onboard

-1600MT/s

PAGE 17

DDR3L-RS-Memory Onboard

-1600MT/s

SSD mSATA -HDD

SATA GEN III

B B

Audio Board

Speaker 1W

PAGE 04

USB3.0 Port / USB Powershare

TPS2546ARTER

PAGE 18

PAGE 23

1600 MT/s

1600 MT/s

SATA 6G

PAGE 02

USB3.0

Haswell ULT 15W

DC+GT3/GT2

Lynx Point LP

MCP 1168pins

eDP Interface

USB2.0

DISPLAY PORT C

Camera

USB2.0

SPEAKER AMP

TPA3130D2

PAGE 05

Speaker 1W

C C

PAGE 31

Keyboard

PAGE 22

PWM FAN

Audio Codec

ALC3661

PAGE 03

HP+MIC Combo Jack x1

PAGE 04

KBC

ITE 8587

PAGE 21

PS2

SPI ROM

64Mbit

PAGE 23

D D

Touch Pad

IHDA

PAGE 22

DSP

ALC5505

PAGE 30

PAGE 04

LPC

TPM

PAGE 27

I2C

IHDA

SPI

SPI ROM

64Mbit

PAGE 23

PAGE 5~16

24MHz

32.768KHz

PCI-E/SDIO

USB3.0 Port / USB Powershare

TPS2546ARTER

USB3.0

FAN & THERMAL

EMC1423

PAGE 20

NGFF

WLAN/BT

PAGE 28

USB2.0/UART

PAGE 25

ALS + SLC sensor

TCS3472

PAGE 20

SMBUS

PAGE 26

eDP PANEL(FHD)

Touch Screen

Mini DP CONN

SMBUS

PAGE 20

PAGE 20

PAGE 18

KBC ITE 8587

PAGE 21

+VCHGR

PAGE 35

+3.3V_ALW/+5V_ALW

PAGE 38

+1.35V_SUS/+0.675V_DDR_VTT

PAGE 37

+1.05V_SUS

PAGE 39

+1.5V_RUN/+1.8V_SUS

PAGE 40

+VCCIN

PAGE 41

DCin & Batt

PAGE 34

Run Power Switch

PAGE 43

PPID LABEL1

Label

AOI LABEL1

Label

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

1

2

3

4

5

6

Friday, September 27, 2013

7

PROJECT :

Block Diagram

Block Diagram

Block Diagram

D13C

D13C

D13C

1 44

1 44

1 44

8

4A

4A

4A

Vinafix.com

1

2

3

4

5

6

7

8

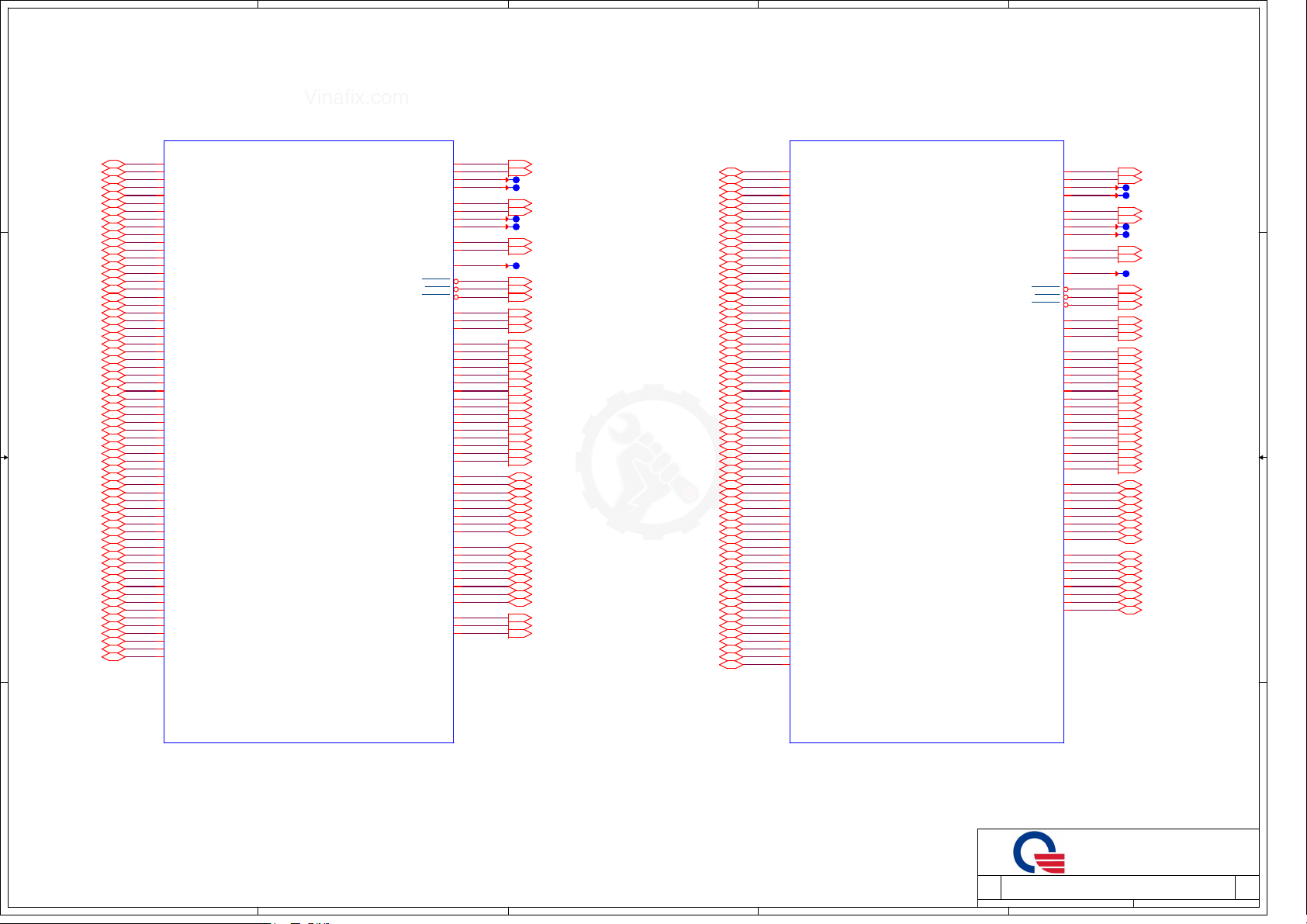

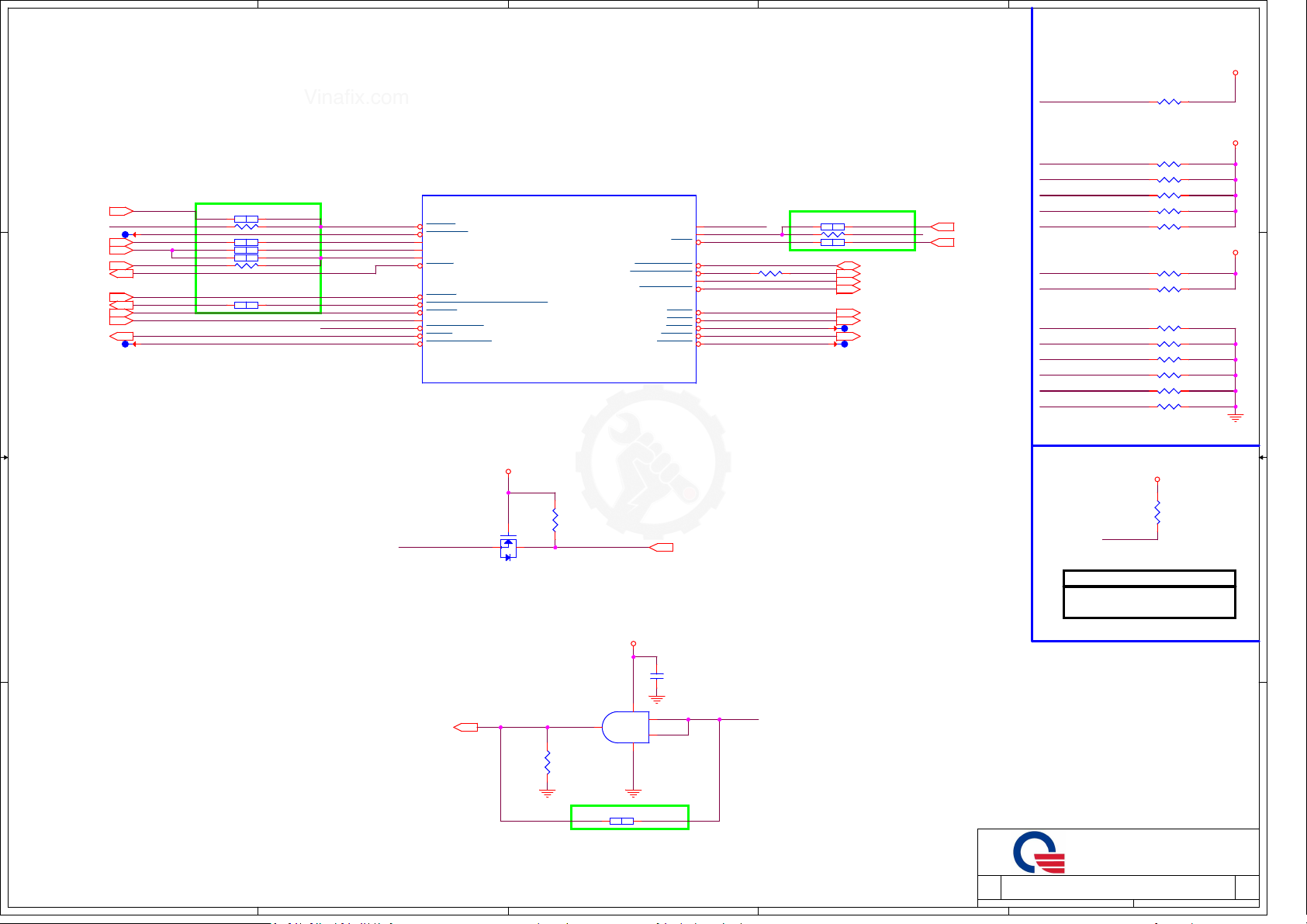

Power

SLP_S3#

State

S0

A A

S3

S4/S5 AC

S4/S5

H

L

L

L

SLP_S4#

SLP_S5#

+3.3V_DSW +15V_ALW

+5V_ALW

+3V_ALW

+3.3V_DEEP_SLEEP_OFF +0.675V_DDR_VTT

+VDDQ_VR +1.05V_RUN +VCCIN

H H H H H H H H H

H H H H H L L

L

L

H

H

H H

L L

L

L

L

L

L L L L

L

L

+5V_RUN

+3.3V_RUN

+1.5V_RUN

L L

H

L

L

L

+V1.05S_VCCST

H

L

L

L

DC Only

AC/DC

Not Exist

B B

Deep Sx

CS AC

CS

DC Only

L

L

L

L L

L

L

L

L

H

H

H

L L

H L

L

HH

L L

L

L

L

L

LL

L

L

L L L

L

L

L

L

L

L

L

L

L

L

L

L

LL

L

L

C C

D D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

1

2

3

4

5

6

Friday, September 27, 2013

7

PROJECT :

Power Rails

Power Rails

Power Rails

D13C

D13C

D13C

2 44

2 44

2 44

8

4A

4A

4A

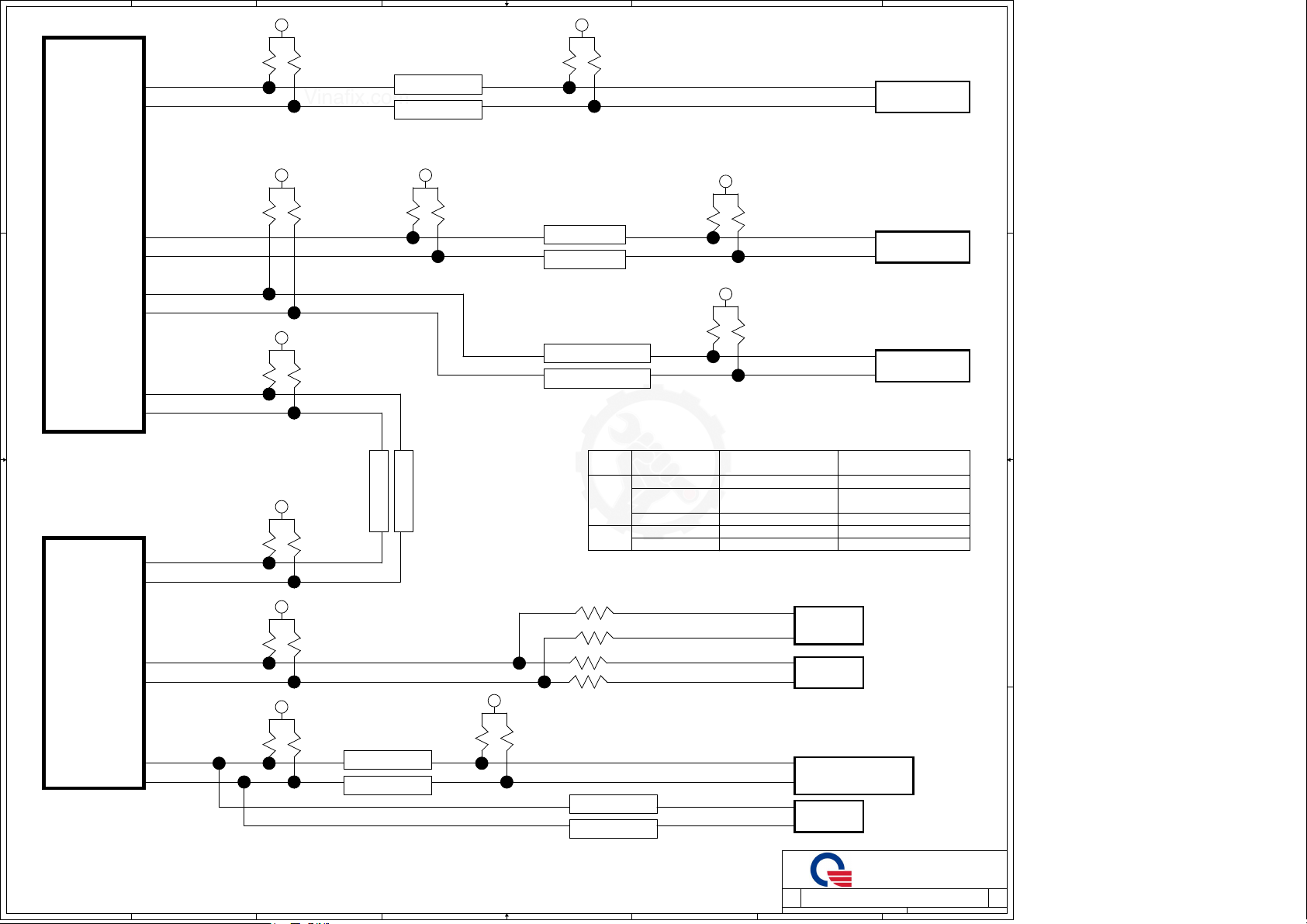

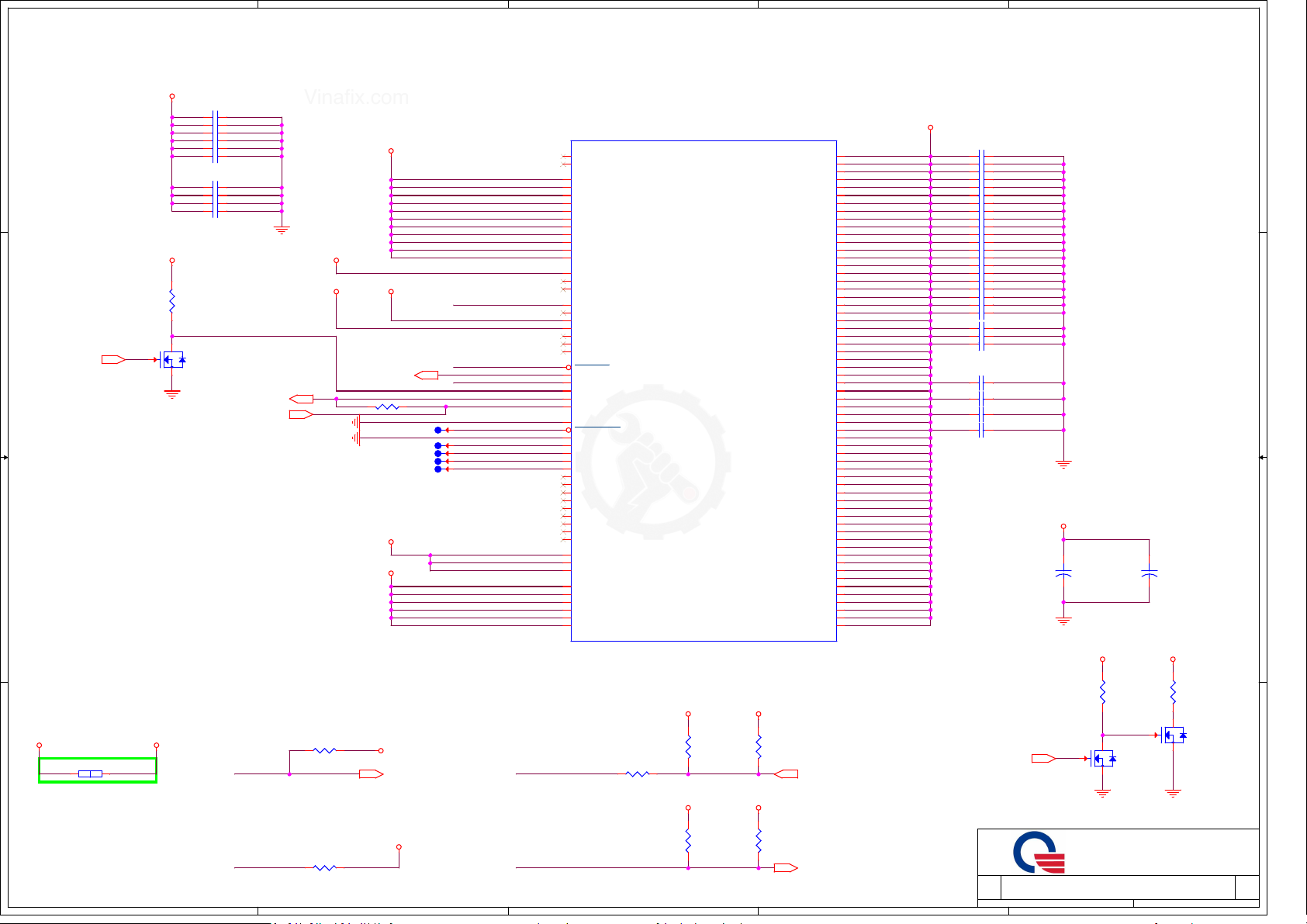

Vinafix.com

1

2

+3.3V_DEEP_SLEEP_OFF

3

4

5

+3.3DX_ALS

6

7

8

100

100

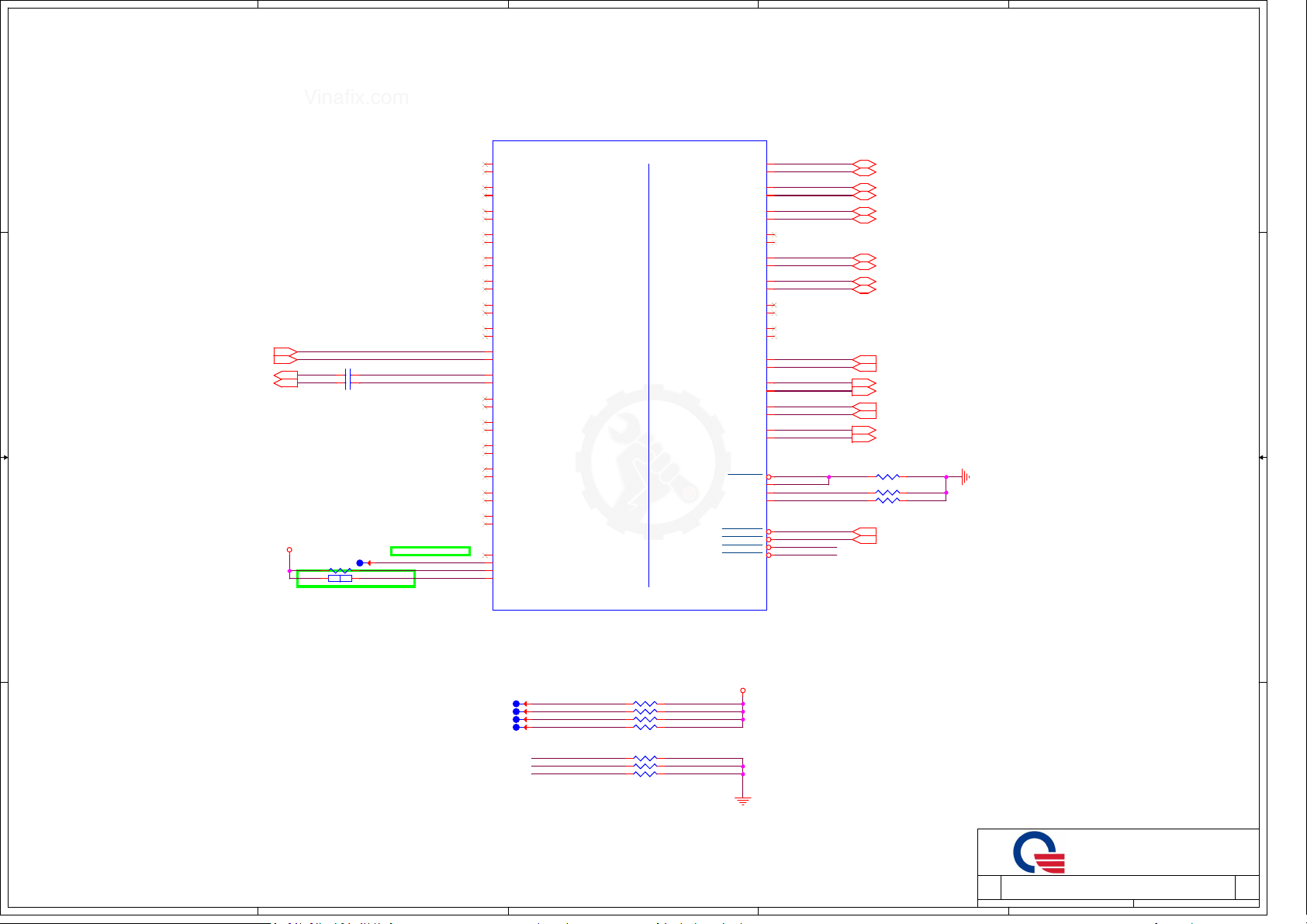

SMBUS

0

0

2.2K2.2K

SMBCLK3_R

SMBDAT3_R

+V3.3DX_TCH_PAD

1K 1K

+V3.3DX_AUDIO

1K 1K

Function

Thermal IC

Charger

Battery

ALS

DSP ALC5055

I2C

Touch PAD Touch PAD 2C

EMC1423 1001_1000b (0x98h)

BQ24715

Battery

SMBCLK0_B

SMBDAT0_B

SMBCLK0_P

SMBDAT0_P

TOUCH_PAD_DAT 2

TOUCH_PAD_CLK

I2C0_SCL_DSP

I2C0_SDA_DSP

0b00010010 (0x12H)

00100100 (0x24h)

B7

Battery

B6

9

Charger

8

17

16

3

27

26

AddressIC

ALS

Touch Pad

DSP

2.2K2.2K

AP2

SMBCLK

AH1

SMBDATA

A A

+3.3V_RUN

1K1K

Haswell

ULT

G4F1I2C1_SDA

I2C1_SCL

F2F3I2C0_SDA

I2C0_SCL

+V3.3DX_ALS

DMN66D0LDW-7

DMN66D0LDW-7

+V3.3DX_ALS

+3.3V_RUN

1K1K

+V3.3DX_TCH_PAD

DMN66D0LDW-7

DMN66D0LDW-7

+V3.3DX_TCH_PAD

+3.3V_DEEP_SLEEP_OFF

B B

2.2K2.2K

AU3

SMB_CLK_ME1

AH3

SMB_DATA_ME1

+V3.3DX_AUDIO

*DMN66D0LDW-7_NC

*DMN66D0LDW-7_NC

+V3.3DX_AUDIO

+3.3V_ALW

DMN66D0LDW-7

DMN66D0LDW-7

2.2K2.2K

SMBDAT1

115

SMBCLK1

C C

116

+3.3V_DEEP_SLEEP_OFF

+3.3V_DEEP_SLEEP_OFF

+3.3V_ALW

SIO

ITE8587

110

SMBCLK0

111 SMBDAT0

+3.3V_RUN

2.2K2.2K

+3.3V_THERMAL

2.2K2.2K

94

95

SMBDAT3

D D

+3.3V_THERMAL

DMN66D0LDW-7

DMN66D0LDW-7

+3.3V_THERMAL

2.2K2.2K

10SMBCLK3

9

Thermal (EMC1423)

17

ALS

16

+V3.3DX_ALS

DMN66D0LDW-7

DMN66D0LDW-7

SMBCLK3_Q

SMBDAT3_Q

SMBCLK3_R

SMBDAT3_R

+V3.3DX_ALS

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

7

PROJECT :

SMBUS & I2C

SMBUS & I2C

SMBUS & I2C

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

1

2

3

4

5

6

Friday, September 27, 2013

D13C

D13C

D13C

3 44

3 44

3 44

8

4A

4A

4A

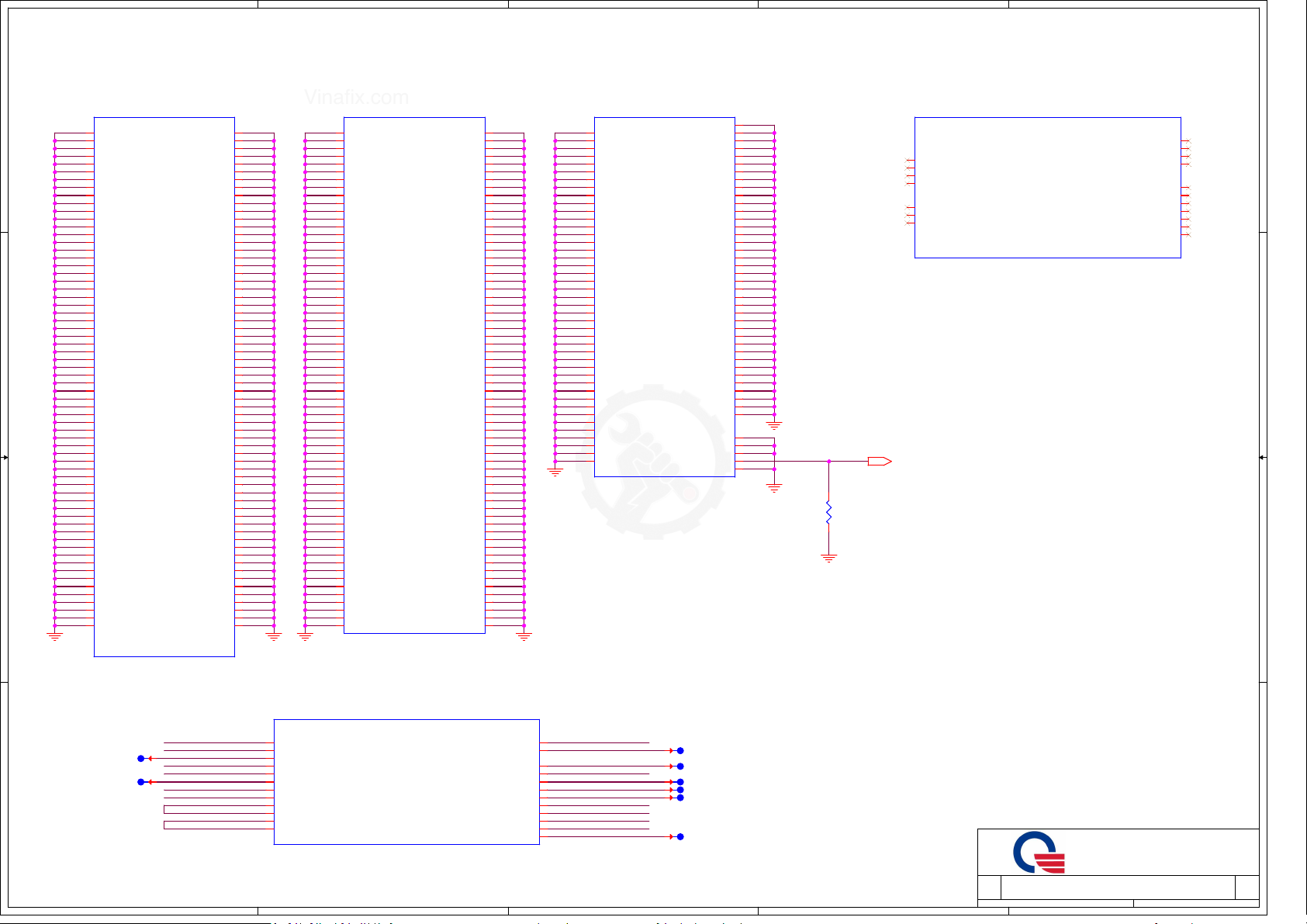

Vinafix.com

1

2

3

4

5

6

7

8

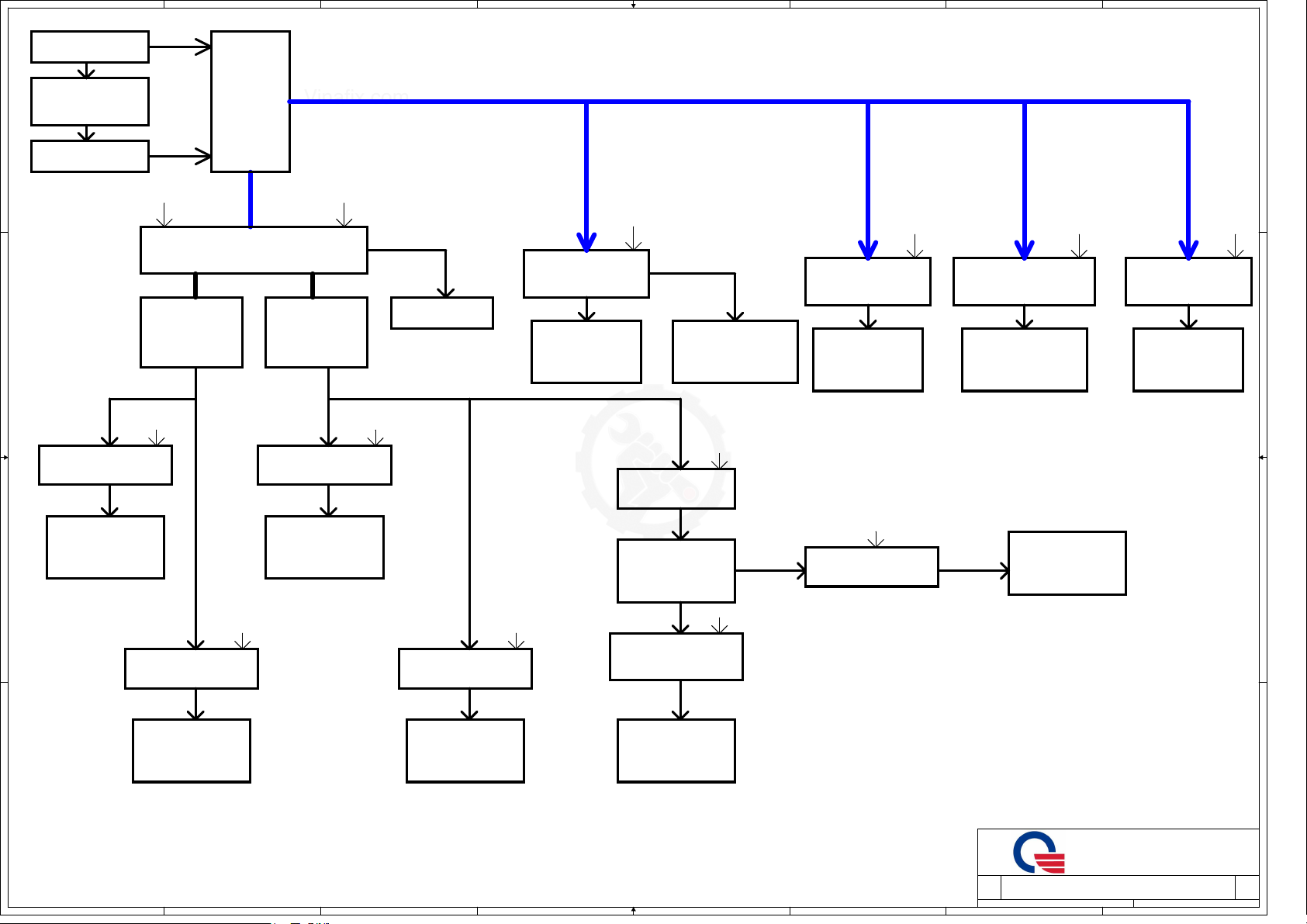

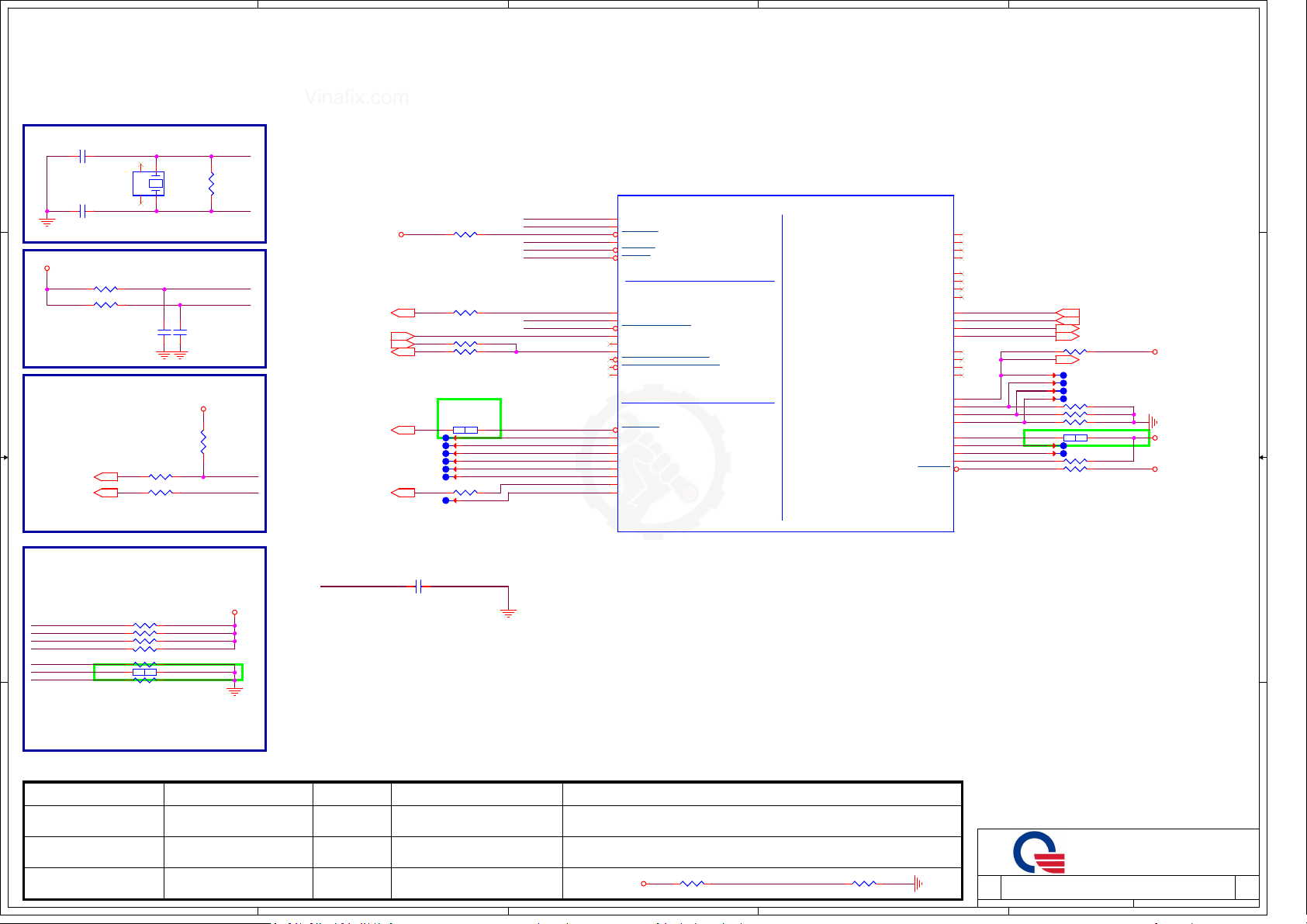

Adapter 45W

VER : 1A

Charger

BQ24737RGRR

A A

PWR_SRC

Battery 2S3P

+3.3V_EN2 ALW_ON

SLP_S4#

RUN_ON

IMVP_VR_ON

LCD_BAK

TI

TPS51285BRUKR

+15V_ALW

+3.3V_ALW

B B

SUS_ON

Load Switch

FDC655BN

+5V_ALW

SUS_ON

Load Switch

FDMC8884

TI

TPS51216RUKR

+V_VDDQ_VR

+0.675V_DDR_VTT

RichTek

SUS_ON

Richtek

RT8240BGQW

+1.05V_SUS

TI

TPS51622RSM

+VCC_IN

O2

OZ9955H

+LED_BL

RT8068AZQW

RUN_ON

+3.3V_SUS

C C

+5V_SUS

+1.8V_SUS

RUN_ONRUN_ON

RUN_ON

Load Switch

FDMC8884

+1.5V_RUN

GMT (LDO)

Load Switch

FDMC8884

Load Switch

FDMC8884

+3.3V_RUN +5V_RUN

D D

1

2

3

4

G9661-25ADJTP1U

+1.5V_RUN

5

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, September 27, 2013 4 44

Date: Sheet of

Friday, September 27, 2013 4 44

Date: Sheet of

6

Friday, September 27, 2013 4 44

7

PROJECT :

Power Block Diagram

Power Block Diagram

Power Block Diagram

D13C

D13C

D13C

4A

4A

4A

8

Vinafix.com

5

4

3

2

1

D D

INT_DP_TXN0_C29

INT_DP_TXP0_C29

INT_DP_TXN1_C29

INT_DP_TXP1_C29

INT_DP_TXN2_C29

INT_DP_TXP2_C29

INT_DP_TXN3_C29

C C

B B

INT_DP_TXP3_C29

LCD_PWM20

PANEL_BKEN21,42

ENVDD20,42

MPCIE_RST_N28

TP93

TOUCHPAD_INTR#_PCH22

GPIO78

GPIO79

PCH_GPIO80

PCI_PME_N

TOUCHPAD_INTR#_PCH

GPIO52

GPIO54

GPIO51

GPIO53

Haswell ULT (Display/eDP)

PCIE

HSW_ULT_DDR3L

1 OF 19

HSW_ULT_DDR3L

EDPDDI

DISPLAY

EDP_DISP_UTIL

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

AD4

B8

A9

C6

U6

P4

N4

N2

U7

L1

L3

R5

L4

U16A

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

U16I

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

eDP SIDEBAND

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

EDP_COMP

DP_UTIL

INT_DP_SCL

INT_DP_SDA

INT_DP_HPD

EDP_TXN0 20

EDP_TXP0 20

EDP_TXN1 20

EDP_TXP1 20

EDP_AUXN 20

EDP_AUXP 20

R258 *0_4_NC

R259 *0_4_NC

INT_DP_SCL 29

INT_DP_SDA 29

INT_DP_AUXN 29

INT_DP_AUXP 29

EDP_HPD 20

LCD_PWM

EDP_COMP

INT_DP_SCL

INT_DP_SDA

GPIO78

GPIO79

PCH_GPIO80

GPIO51

GPIO53

GPIO54

TOUCHPAD_INTR#_PCH

GPIO52

R40 24.9/F_4

RP3 2.2KX2

R78 10K_4

R65 10K_4

R270 10K_4

R84 10K_4

R276 10K_4

R277 10K_4

R93 100K_4

R269 10K_4

2

1

4

3

+VCCIOA_OUT

+3.3V_RUN

9 OF 19

+5V_RUN

2

INT_DP_HPD

R14

1M_4

A A

5

4

31

Q1

DMN5L06WK-7

R3 *0_4_NC

R4

100K_4

INT_DP_HPD_R 29

3

R36

100K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

2

Friday, September 27, 2013

PROJECT :

Haswell ULT 1/12

Haswell ULT 1/12

Haswell ULT 1/12

1

D13C

D13C

D13C

5 44

5 44

5 44

4A

4A

4A

Vinafix.com

5

Haswell ULT (DDR3L-RS)

4

3

2

1

D D

M_A_DQ017

M_A_DQ117

M_A_DQ217

M_A_DQ317

M_A_DQ417

M_A_DQ517

M_A_DQ617

M_A_DQ717

M_A_DQ817

M_A_DQ917

M_A_DQ1017

M_A_DQ1117

M_A_DQ1217

M_A_DQ1317

M_A_DQ1417

M_A_DQ1517

M_A_DQ1617

M_A_DQ1717

M_A_DQ1817

M_A_DQ1917

M_A_DQ2017

M_A_DQ2117

M_A_DQ2217

C C

B B

M_A_DQ2317

M_A_DQ2417

M_A_DQ2517

M_A_DQ2617

M_A_DQ2717

M_A_DQ2817

M_A_DQ2917

M_A_DQ3017

M_A_DQ3117

M_A_DQ3217

M_A_DQ3317

M_A_DQ3417

M_A_DQ3517

M_A_DQ3617

M_A_DQ3717

M_A_DQ3817

M_A_DQ3917

M_A_DQ4017

M_A_DQ4117

M_A_DQ4217

M_A_DQ4317

M_A_DQ4417

M_A_DQ4517

M_A_DQ4617

M_A_DQ4717

M_A_DQ4817

M_A_DQ4917

M_A_DQ5017

M_A_DQ5117

M_A_DQ5217

M_A_DQ5317

M_A_DQ5417

M_A_DQ5517

M_A_DQ5617

M_A_DQ5717

M_A_DQ5817

M_A_DQ5917

M_A_DQ6017

M_A_DQ6117

M_A_DQ6217

M_A_DQ6317

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

U16C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

HSW_ULT_DDR3L

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_A_CLKN0 17,19

M_A_CLKP0 17,19

TP136

TP134

M_A_CKE0 17,19

M_A_CKE1 17,19

TP127

TP126

M_A_CS#0 17,19

M_A_CS#1 17,19

TP129

M_A_RAS# 17,19

M_A_WE# 17,19

M_A_CAS# 17,19

M_A_BS0 17,19

M_A_BS1 17,19

M_A_BS2 17,19

M_A_A0 17,19

M_A_A1 17,19

M_A_A2 17,19

M_A_A3 17,19

M_A_A4 17,19

M_A_A5 17,19

M_A_A6 17,19

M_A_A7 17,19

M_A_A8 17,19

M_A_A9 17,19

M_A_A10 17,19

M_A_A11 17,19

M_A_A12 17,19

M_A_A13 17,19

M_A_A14 17,19

M_A_A15 17,19

M_A_DQSN0 17

M_A_DQSN1 17

M_A_DQSN2 17

M_A_DQSN3 17

M_A_DQSN4 17

M_A_DQSN5 17

M_A_DQSN6 17

M_A_DQSN7 17

M_A_DQSP0 17

M_A_DQSP1 17

M_A_DQSP2 17

M_A_DQSP3 17

M_A_DQSP4 17

M_A_DQSP5 17

M_A_DQSP6 17

M_A_DQSP7 17

SM_VREF_CA 19

SM_VREF_DQ0 19

SM_VREF_DQ1 19

U16D

M_B_DQ018

M_B_DQ118

M_B_DQ218

M_B_DQ318

M_B_DQ418

M_B_DQ518

M_B_DQ618

M_B_DQ718

M_B_DQ818

M_B_DQ918

M_B_DQ1018

M_B_DQ1118

M_B_DQ1218

M_B_DQ1318

M_B_DQ1418

M_B_DQ1518

M_B_DQ1618

M_B_DQ1718

M_B_DQ1818

M_B_DQ1918

M_B_DQ2018

M_B_DQ2118

M_B_DQ2218

M_B_DQ2318

M_B_DQ2418

M_B_DQ2518

M_B_DQ2618

M_B_DQ2718

M_B_DQ2818

M_B_DQ2918

M_B_DQ3018

M_B_DQ3118

M_B_DQ3218

M_B_DQ3318

M_B_DQ3418

M_B_DQ3518

M_B_DQ3618

M_B_DQ3718

M_B_DQ3818

M_B_DQ3918

M_B_DQ4018

M_B_DQ4118

M_B_DQ4218

M_B_DQ4318

M_B_DQ4418

M_B_DQ4518

M_B_DQ4618

M_B_DQ4718

M_B_DQ4818

M_B_DQ4918

M_B_DQ5018

M_B_DQ5118

M_B_DQ5218

M_B_DQ5318

M_B_DQ5418

M_B_DQ5518

M_B_DQ5618

M_B_DQ5718

M_B_DQ5818

M_B_DQ5918

M_B_DQ6018

M_B_DQ6118

M_B_DQ6218

M_B_DQ6318

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HSW_ULT_DDR3L

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

M_B_CLKN0 18,19

M_B_CLKP0 18,19

TP28

TP133

M_B_CKE0 18,19

M_B_CKE1 18,19

TP125

TP124

M_B_CS#0 18,19

M_B_CS#1 18,19

TP128

M_B_RAS# 18,19

M_B_WE# 18,19

M_B_CAS# 18,19

M_B_BS0 18,19

M_B_BS1 18,19

M_B_BS2 18,19

M_B_A0 18,19

M_B_A1 18,19

M_B_A2 18,19

M_B_A3 18,19

M_B_A4 18,19

M_B_A5 18,19

M_B_A6 18,19

M_B_A7 18,19

M_B_A8 18,19

M_B_A9 18,19

M_B_A10 18,19

M_B_A11 18,19

M_B_A12 18,19

M_B_A13 18,19

M_B_A14 18,19

M_B_A15 18,19

M_B_DQSN0 18

M_B_DQSN1 18

M_B_DQSN2 18

M_B_DQSN3 18

M_B_DQSN4 18

M_B_DQSN5 18

M_B_DQSN6 18

M_B_DQSN7 18

M_B_DQSP0 18

M_B_DQSP1 18

M_B_DQSP2 18

M_B_DQSP3 18

M_B_DQSP4 18

M_B_DQSP5 18

M_B_DQSP6 18

M_B_DQSP7 18

3 OF 19

A A

5

4

3

4 OF 19

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

2

Friday, September 27, 2013

PROJECT :

Haswell ULT 2/12

Haswell ULT 2/12

Haswell ULT 2/12

1

D13C

D13C

D13C

6 44

6 44

6 44

4A

4A

4A

Vinafix.com

5

D D

AUDIO_EN30,31

PCIE_SLOT3_WAKE_N28

NGFF_WLAN_PWR_EN27,28

C C

B B

KB_DET#22

SIO_WAKE_SCI#21

BT_RADIO_DIS#28

TPM_RST#27

WLAN_ON/OFF#28

SDIO_WLAN_WAKE_L28

USB2_CAM_PWR_EN20

TP36

LCD_CE20

LCD_DBC20

MODPHY_EN15

TPM_PWR_EN27

ALS_PWR_EN22

BT_WAKE#28

SIO_EXT_SCI#21

TP145

DEVSLP227

ACZ_SPKR32

AUDIO_EN

PCIE_SLOT3_WAKE_N

NGFF_WLAN_PWR_EN

GPIO15

KB_DET#

CRIT_TEMP_REP_N

GPIO24

SIO_WAKE_SCI#

GPIO28

GPIO26

BT_RADIO_DIS#

GPIO58

WLAN_ON/OFF#

GPIO44

LCD_CE

LCD_DBC

USB2_CAM_PWR_EN

USB3_P0_EN

GPIO14

GPIO25

TPM_PWR_EN

BT_WAKE#

SIO_EXT_SCI#

DEVSLP0

GPIO70

DEVSLP1

DEVSLP2

17

112

2

R118 *SJ_4_NC

SDIO_D0 : Top Swap Strap

R272

R272_NC

ENABLE

DISABLE(Default)

No Reboot Strap(GPIO81)

NC

PU

Default

EN

TLS CONFIDENTIALITY STRAP(GPIO15)

NC

A A

PU

Default

EN

4

Hasswell ULT (GPIO,LPIO,MISC)

GPIO

+V3.3DX_TCH_PAD

Q25A

Q25B

+V3.3DX_AUDIO

Q24A

HSW_ULT_DDR3L

+3V

DSW

+3V

+3V

DSW

+3V

+3V

+3V

+3V

DSW

+3V

+3V

+3V

+3V

+3V

10 OF 19

5

3 4

2

6 1

5

3 4

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

+3V

CPU/

MISC

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

SERIAL IO

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_RST/GPIO2

UART1_CTS/GPIO3

Touch Pad

RCIN/GPIO82

PCH_OPI_RCOMP

UART1_TXD/GPIO1

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

TOUCH_PAD_CLK 22

TOUCH_PAD_DAT 22

I2C0_SCL_DSP 30

U16J

P1

BMBUSY/GPIO76

AU2

GPIO8

AM7

LAN_PHY_PWR_CTRL/GPIO12

AD6

GPIO15

Y1

GPIO16

T3

GPIO17

AD5

GPIO24

AN5

GPIO27

AD7

GPIO28

AN3

GPIO26

AG6

GPIO56

AP1

GPIO57

AL4

GPIO58

AT5

GPIO59

AK4

GPIO44

AB6

GPIO47

U4

GPIO48

Y3

GPIO49

P3

GPIO50

Y2

HSIOPC/GPIO71

AT3

GPIO13

AH4

GPIO14

AM4

GPIO25

AG5

GPIO45

AG3

GPIO46

AM3

GPIO9

AM2

GPIO10

P2

DEVSLP0/GPIO33

C4

SDIO_POWER_EN/GPIO70

L2

DEVSLP1/GPIO38

N5

DEVSLP2/GPIO39

V2

SPKR/GPIO81

+3.3V_RUN

1

3

2

4

I2C1_SCL

I2C1_SDA

+3.3V_RUN

1

3

2

4

I2C0_SCL

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

+3V_S5

RP29

1KX2

DMN66D0LDW-7

DMN66D0LDW-7

RP27

1KX2

*DMN66D0LDW-7_NC

3

THRMTRIP

SERIRQ

RSVD

RSVD

+V1.05S_VCCST

R253

1K_4

D60

PCH_THRMTRIP#

V4

SIO_RCIN#

T4

IRQ_SERIRQ

AW15

PCH_OPIRCOMP

AF20

PCH_OPIICCCTL

AB21

PCH_OPIICCOBS

TOUCHSCREEN_EN TOUCHPAD_EN

R6

CAP_LED

L6

KB_LED_DET

N6

GPIO85

L8

BBS

R7

GPIO87

L5

N7

TOUCHSCREEN_EN

K2

GPIO90

J1

GPIO91

K3

GPIO92

J2

GPIO93

G1

GPIO94

K4

UART1_RX

G2

UART1_TX

J3

UART1_RTS

J4

UART1_CTS

F2

I2C0_SDA

F3

I2C0_SCL

G4

I2C1_SDA

F1

I2C1_SCL

E3

SDIO_CLK

F4

SDIO_CMD

D3

SDIO_D0

E4

SDIO_D1

C3

SDIO_D2

E2

SDIO_D3

+3.3V_RUN

+V3.3S_1.8S_LPSS_SDIO

GPIO90

GPIO91

GPIO92

GPIO93

R79 *0_4_NC

112

112

2

2

R37 *SJ0402_NC

R69 *SJ0402_NC

17

R44 *1K_4_NC

R272 *1K_4_NC

+3.3V_RUN

R459

*10K_4_NC

R460

10K_4

R273

10K_4

R274

*10K_4_NC

2

SIO_RCIN# 21

IRQ_SERIRQ 21,27

TP26

TP25

CAP_LED 22

KB_LED_DET 22

NGFF_SATA_SSD_PWREN 27

TOUCHPAD_EN 22

TOUCHSCREEN_EN 20

UART1_RX 28

UART1_TX 28

UART1_RTS 28

UART1_CTS 28

SDIO_CLK 28

SDIO_CMD 28

SDIO_D0 28

SDIO_D1 28

SDIO_D2 28

SDIO_D3 28

BBS

R43 *1K_4_NC

SDIO_D0

R271 *1K_4_NC

R278

10K_4

R275

*10K_4_NC

R266

10K_4

R268

*10K_4_NC

1

GPIO Pull-up/Pull-down (CLG)

TP112

TP120

TP111

TP23

TP31

TP86

TP79

TP77

TP21

TP96

GPIO25

SIO_WAKE_SCI#

NGFF_WLAN_PWR_EN

GPIO44

GPIO58

USB3_P0_EN

SIO_EXT_SCI#

GPIO24

TPM_PWR_EN

GPIO15

PCIE_SLOT3_WAKE_N

BT_WAKE#

GPIO28

GPIO14

BT_RADIO_DIS#

WLAN_ON/OFF#

DEVSLP2

KB_LED_DET

TOUCHPAD_EN

DEVSLP2

USB2_CAM_PWR_EN

KB_DET#

DEVSLP0

SIO_RCIN#

CRIT_TEMP_REP_N

AUDIO_EN

LCD_CE

CAP_LED

LCD_DBC

GPIO87

DEVSLP1

IRQ_SERIRQ

GPIO85

GPIO94

UART1_RX

UART1_TX

UART1_RTS

UART1_CTS

SDIO_CMD

SDIO_CLK

SDIO_D2

SDIO_D1

SDIO_D3

GPIO70

GPIO26

PCH_OPIRCOMP

USB3_P0_EN

R476 10K_4

R131 10K_4

R114 10K_4

R127 10K_4

R124 10K_4

R156 10K_4

R326 10K_4

R100 10K_4

R143 10K_4

R108 10K_4

R347 10K_4

R323 100K_4

R107 1M_4

R116 10K_4

R113 10K_4

R141 10K_4

R474 *10K_4_NC

R28 *10K_4_NC

R87 *10K_4_NC

R68 *10K_4_NC

R280 100K_4

R291 10K_4

R267 *10K_4_NC

R86 10K_4

R286 10K_4

R281 10K_4

R98 10K_4

R85 *10K_4_NC

R302 10K_4

R91 10K_4

RP4 10KX2

RP26 10KX2

RP33 10KX2

RP34 10KX2

RP35 10KX2

RP36 10KX2

R477 10K_4

R34 *100K_4_NC

R329 100K_4

R354 49.9/F_4

R157 *100K_4_NC

RAM Vendor select

RAM Select

GPIO90

Micron 4G

Micron 8G

Hynix 4G

GPIO91

0

0

0

0

0 0

1

Hynix 8G 0

SAM 4G 00 0 1

+3.3V_DEEP_SLEEP_OFF

40

1

3

1

3

1

3

1

3

1

3

1

3

1 2

GPIO92

GPIO93

0

1

11

+3.3V_SUS

+V3.3DX_SSD

+3.3V_RUN

2

4

2

4

2

4

2

4

2

4

2

4

0

1

0

1

GPIO86

SPI (Default)

5

I2C0_SDA

4

Q24B

*DMN66D0LDW-7_NC

2

6 1

DSPPUPDLPC

I2C0_SDA_DSP 30

3

2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Haswell ULT 3/12

Haswell ULT 3/12

Haswell ULT 3/12

1

D13C

D13C

D13C

7 44

7 44

7 44

4A

4A

4A

Vinafix.com

5

4

3

2

1

Haswell ULT (PCIE,USB)

D D

C C

WiFi NGFF

B B

PCIE_RXN328

PCIE_RXP328

PCIE_TXN328

PCIE_TXP328

+V1.05S_AUSB3PLL

R25 3K/F_4

R27 *SJ0402_NC

C240 0.1U/16V_4

C241 0.1U/16V_4

TP5

2

112

PCIE_TXN3_C

PCIE_TXP3_C

48

PCIE_PLLOBS1

PCIE_RCOMP

PCIE_IREF

G10

G11

G13

G17

G15

F10

E10

C23

C22

B23

A23

H10

B21

C21

B22

A21

F11

C29

B30

F13

B29

A29

F17

C30

C31

F15

B31

A31

E15

E13

A27

B27

F8

E8

E6

F6

U16K

PERN5_L0

PERP5_L0

PETN5_L0

PETP5_L0

PERN5_L1

PERP5_L1

PETN5_L1

PETP5_L1

PERN5_L2

PERP5_L2

PETN5_L2

PETP5_L2

PERN5_L3

PERP5_L3

PETN5_L3

PETP5_L3

PERN3

PERP3

PETN3

PETP3

PERN4

PERP4

PETN4

PETP4

PERN1/USB3RN3

PERP1/USB3RP3

PETN1/USB3TN3

PETP1/USB3TP3

PERN2/USB3RN4

PERP2/USB3RP4

PETN2/USB3TN4

PETP2/USB3TP4

RSVD

RSVD

PCIE_RCOMP

PCIE_IREF

18

HSW_ULT_DDR3L

PCIE USB

11 OF 19

+3V_S5

+3V_S5

+3V_S5

+3V_S5

USB2N0

DSW

USB2P0

USB2N1

DSW

USB2P1

USB2N2

DSW

USB2P2

USB2N3

DSW

USB2P3

USB2N4

DSW

USB2P4

USB2N5

DSW

USB2P5

USB2N6

DSW

USB2P6

USB2N7

DSW

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

RSVD

RSVD

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

USB_BIAS

AJ11

AN10

USBPLLMON_N

AM10

USBPLLMON_P

AL3

USB_OC0#

AT1

USB_OC1#

AH2

USB_OC2#

AV3

USB3_P1_EN

USBP0- 26

USBP0+ 26

USBP1- 32

USBP1+ 32

USBP2- 20

USBP2+ 20

USBP4- 20

USBP4+ 20

USBP5- 28

USBP5+ 28

USB3.0_RX1- 26

USB3.0_RX1+ 26

USB3.0_TX1- 26

USB3.0_TX1+ 26

USB3.0_RX2- 32

USB3.0_RX2+ 32

USB3.0_TX2- 32

USB3.0_TX2+ 32

R126 22.6/F_4

R148 49.9/F_4

R140 49.9/F_4

USB_OC0# 26

USB_OC1# 32

USB3.0 Port 0 CN2

USB3.0 Port 1 CN6

Touch Screen

Camara

WiFi NGFF

USB3.0 Port 0 CN2

USB3.0 Port 1 CN6

+3.3V_DEEP_SLEEP_OFF

TP32

TP119

TP107

TP123

A A

5

4

USB_OC0#

USB_OC1#

USB_OC2#

USB3_P1_EN

USB3_P1_EN

USB_OC0#

USB_OC1#

R119 10K_4

R342 10K_4

R317 10K_4

R350 10K_4

R351 *100K_4_NC

R121 *15K_4_NC

R343 *15K_4_NC

3

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

2

Friday, September 27, 2013

PROJECT :

Haswell ULT 4/12

Haswell ULT 4/12

Haswell ULT 4/12

1

D13C

D13C

D13C

8 44

8 44

8 44

4A

4A

4A

Vinafix.com

5

4

3

2

1

D D

SRTC_RST#

C162

1U/6.3V_4

+3.3V_SUS

RTC_X1

R366

10M_4

RTC_X2

RTC_RST#

R182

*1K_4_NC

HDA_SYNC_R

HDA_RST#_R

+1.05V_SUS

HDA_BITCLK30

HDA_SDIN030

PCH_MELOCK21

HDA_SDOUT30

XDP_TRST_CPU_N16

XDP_TCK016

HDA_BITCLK_R

+RTC_CELL

19

TP109

TP110

TP113

TP105

TP29

TP24

TP135

1 2

EC59 *10P/50V_4_NC

R365 1M_4

R359 33_4

R357 1K_4

R38

*SJ0402_NC

2

112

R405 0_4

RTC_X1

RTC_X2

SM_INTRUDER#

PCH_INTVRMEN

SRTC_RST#

RTC_RST#

HDA_BITCLK_R

HDA_SYNC_R

HDA_RST#_R

HDA_SDOUT_R

XDP_TRST_CPU

XDP_TCK1

XDP_TDI

PCH_JTAG_TDO

XDP_TMS

PM_TEST_RST_N

PCH_JTAGX

PCH_EDM

C261 15P/50V_4

C267 15P/50V_4

+RTC_CELL

R179 20K/F_4

R180 20K/F_4

C C

HDA_SYNC30

HDA_RST#30

PCH JTAG Debug (CLG)

B B

14

23

C161

1U/6.3V_4

R175 33_4

R178 33_4

Y3

32.768KHZ

MP remove(Intel)

XDP_TMS

XDP_TDI

PCH_JTAG_TDO

PCH_JTAGX

XDP_TCK1

PCH_EDM

RSVD_PGDMON

R134 51_4

R133 51_4

R132 51_4

R135 *1K_4_NC

R112 *51_4_NC

R353 *SJ0402_NC

R120 *1K_4_NC

112

2

Haswell ULT (RTC, HDA, JTAG, SATA)

U16E

AW5

RTCX1

AY5

RTCX2

AU6

INTRUDER

AV7

INTVRMEN

AV6

SRTCRST

AU7

RTCRST

AW8

HDA_BCLK/I2S0_SCLK

AV11

HDA_SYNC/I2S0_SFRM

AU8

HDA_RST/I2S_MCLK

AY10

HDA_SDI0/I2S0_RXD

AU12

HDA_SDI1/I2S1_RXD

AU11

HDA_SDO/I2S0_TXD

AW10

HDA_DOCK_EN/I2S1_TXD

AV10

HDA_DOCK_RST/I2S1_SFRM

AY8

I2S1_SCLK

AU62

PCH_TRST

AE62

PCH_TCK

AD61

PCH_TDI

AE61

PCH_TDO

AD62

PCH_TMS

AL11

RSVD

AC4

RSVD

AE63

JTAGX

AV2

RSVD

HSW_ULT_DDR3L

RTC

AUDIO SATA

JTAG

5 OF 19

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

SATA0GP/GPIO34

+3V

SATA1GP/GPIO35

+3V

SATA2GP/GPIO36

+3V

SATA3GP/GPIO37

+3V

SATA_RCOMP

SATA_IREF

RSVD

RSVD

SATALED

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

U1

V6

AC1

A12

L11

K10

C12

U3

GPIO35

GPIO36

GPIO37

SATA_IREF

SATA_PLLOBS0

SATA_PLLOBS1

SATA_RCOMP

PCH_SATA_LED#RSVD_PGDMON

SATA_RXN2 27

SATA_RXP2 27

SATA_TXN2 27

R292 10K_4R358 33_4

R287 10K_4

R97 10K_4

R301 10K_4

R263 *SJ0402_NC

R254 3K/F_4

R94 10K_4

SATA_TXP2 27

SMC_EXTSMI_N 21

TP83

TP80

TP22

TP94

2

112

TP7

TP6

mSATA

+3.3V_RUN

+V1.05S_ASATA3PLL

19

+3.3V_RUN

19

PCH Strap Table

Pin Name Strap description

A A

SPKR

HDA_SDO PWROK

No reboot mode setting PWROK 0 = Default (weak pull-down 20K)

Flash Descriptor Security

Override / Intel ME Debug Mode

INTVRMEN Integrated 1.05V VRM enable ALWAYS Should be always pull-up

5

Sampled

Configuration

1 = Setting to No-Reboot mode

0 = Security Effect (Int PD)

1 = Can be Override

4

+RTC_CELL

Note

R361 *330K_4_NC

3

PCH_INTVRMEN

R360 330K_4

2

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

PROJECT :

Haswell ULT 5/12

Haswell ULT 5/12

Haswell ULT 5/12

1

D13C

D13C

D13C

9 44

9 44

9 44

4A

4A

4A

Vinafix.com

5

D D

TP89

WiFi/BT (NGFF)

C C

CLK_PCIE_WLANN28

CLK_PCIE_WLANP28

PCIE_CLK_REQ2#28

TP87

TP84

PCIE_CLK_REQ0#

PCIE_CLK_REQ1#

PCIE_CLK_REQ2#

PCIE_CLK_REQ3#

PCIE_CLK_REQ4#

PCIE_CLK_REQ5#

4

Haswell ULT (CLK)

U16F

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

HSW_ULT_DDR3L

+3V

+3V

+3V

+3V

+3V

+3V

CLOCK

SIGNALS

6 OF 19

XTAL24_IN

XTAL24_OUT

RSVD

RSVD

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

3

A25

XTAL24_IN

B25

XTAL24_OUT

K21

XCKPLL_MON_DN

M21

XCKPLL_MON_DP

C26

C35

TESTLOW_0

C34

TESTLOW_1

AK8

TESTLOW_2

AL8

TESTLOW_3

AN15

LPC_CLK_0

AP15

LPC_CLK_1

B35

A35

LPC_CLK_EC

LPC_CLK_1

C242 12P/50V_4

4

3

1

TP16

TP15

1 2

1

3

5

7

1 2

1 2

1 2

TP53

TP62

1 2

1 2

Y2

24MHz

2

C237 12P/50V_4

2

4

6

8

R260

1M_4

R35 3K/F_4

RP25 10KX4

R139 22_4

R158 22_4

R154 22_4

EC4 *10P/50V_4_NC

EC3 *10P/50V_4_NC

2

+V1.05S_AXCK_LCPLL

LPC_CLK_EC 21

LPC_CLK_TPM 27

LPC_CLK_DEBUG 28

TP34

PCIE_CLK_REQ2#

PCIE_CLK_REQ1#

PCIE_CLK_REQ0#

PCIE_CLK_REQ3#

PCIE_CLK_REQ4#

PCIE_CLK_REQ5#

GPIO60

SML0CLK

SML0DATA

GPIO73

PCH_SMB_ALERT#

SMB_CLK_ME1

SMB_DATA_ME1

SMBCLK

SMBDATA

1

+3.3V_RUN

RP31 10KX4

1

2

3

4

5

6

7

8

RP30 10KX2

1

3

R325 1K_4

R328 2.2K_4

R322 2.2K_4

RP7 10KX2

1

3

RP6 2.2KX2

1

3

RP8 2.2KX2

1

3

2

4

+3.3V_DEEP_SLEEP_OFF

2

4

2

4

2

4

SMBus / Pull-up (CLG)

Haswell ULT (LPC/SPI/SMB/CLINK)

U16G

LPC_LAD021,27,28

LPC_LAD121,27,28

LPC_LAD221,27,28

LPC_LAD321,27,28

LPC_LFRAME#21,27,28

B B

PCH_SPI_CLK23

PCH_SPI_CS0#23

PCH_SPI_SI23

PCH_SPI_SO23

PCH_SPI_IO223

PCH_SPI_IO323

A A

5

1 2

EC2 *10P/50V_4_NC

AU14

AW12

AY12

AW11

AV12

AA3

AC2

AA2

AA4

AF1

Y7

Y4

Y6

LAD0

LAD1

LAD2

LAD3

LFRAME

SPI_CLK

SPI_CS0

SPI_CS1

SPI_CS2

SPI_MOSI

SPI_MISO

SPI_IO2

SPI_IO3

4

HSW_ULT_DDR3L

LPC

+3V_S5

SMBUS

+3V_S5

+3V_S5

SML1ALERT/PCHHOT/GPIO73

+3V_S5

+3V_S5

C-LINKSPI

SMBALERT/GPIO11

SMBCLK

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_CLK

CL_DATA

CL_RST

7 OF 19

AN2

PCH_SMB_ALERT#

AP2

SMBCLK

AH1

SMBDATA

AL2

GPIO60

AN1

SML0CLK

AK1

SML0DATA

AU4

GPIO73

AU3

SMB_CLK_ME1

AH3

SMB_DATA_ME1

AF2

AD2

AF4

3

SMBCLK 20

SMBDATA 20

TP106

TP101

TP27

ALS

SMB_CLK_ME1

SMB_DATA_ME1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

+3.3V_DEEP_SLEEP_OFF

Q28A

DMN66D0LDW-7

Q28B

DMN66D0LDW-7

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Haswell ULT 6/12

Haswell ULT 6/12

Friday, September 27, 2013

Friday, September 27, 2013

Friday, September 27, 2013

Haswell ULT 6/12

5

34

2

61

1

SMBCLK1 21

SMBDAT1 21

D13C

D13C

D13C

10 44

10 44

10 44

4A

4A

4A

Vinafix.com

5

4

3

2

1

Haswell ULT (SYSTEM POWER MANAGEMENT)

D D

20

SUSACK#21

ME_SUS_PWR_ACK_R

TP88

SYS_PWROK21

HWPG33

EC_VCCST_PWRGD21,33

PLTRST#28

RSMRST#21

ME_SUS_PWR_ACK21

SIO_PWRBTN#21

AC_PRESENT21

SLP_S0#35,39

C C

TP118

R324 *SJ0402_NC

R319 *0_4_NC

R311 *SJ0402_NC

R364 *SJ0402_NC

R103 *SJ0402_NC

R406 *0_4_NC

R145 *SJ0402_NC

112

1 2

112

112

112

1 2

112

2

2

2

2

2

SUSACK#_R

SYS_PWROK_R

PCH_PWROK

APWROK

PLTRST#

RSMRST#

ME_SUS_PWR_ACK_R

SIO_PWRBTN#

AC_PRESENT

PM_BATLOW#

SLP_WLAN SIO_SLP_LAN#

U16H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

HSW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

DSW

DSW

DSW

DSW

+3.3V_EC

+3V_S5

8 OF 19

DSW

+3V

+3V_S5

+3V_S5

DSW

DSW

DSW

DSW

DSW

DSW

DSWVRMEN

DPWROK

WAKE

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

AW7

DSWVRMEN

AV5

DPWROK_RSYS_RESET#

AJ5

PCIE_WAKE#_R

V5

CLKRUN#

AG4

AE6

AP5

AJ6

AT4

AL5

SIO_SLP_A#

AP4

AJ7

20

112

1 2

112

2

2

CLKRUN# 21,27

TPM_LPC_PD 27

SUSCLK 28

SIO_SLP_S5# 21,37

SIO_SLP_S4# 21,37,40

SIO_SLP_S3# 21,37

TP33

SLP_SUS# 15,21,39,40

TP117

R168 *SJ0402_NC

R167 *0_4_NC

R314 *SJ0402_NC

RSMRST#

DPWROK 21

PCIE_WAKE# 28

PCH Pull-up/down (CLG)

+3.3V_DEEP_SLEEP_OFF

ME_SUS_PWR_ACK_R

PCIE_WAKE#_R

AC_PRESENT

PM_BATLOW#

SIO_PWRBTN#

SLP_WLAN

CLKRUN#

SYS_RESET#

SYS_RESET#

RSMRST#

SYS_PWROK_R

DPWROK_R

PCH_PWROK

APWROK

1 2

R144 *10K_4_NC

1 2

R318 10K_4

1 2

R115 *10K_4_NC

1 2

R349 10K_4

1 2

R348 *10K_4_NC

1 2

R332 *10K_4_NC

R92 8.2K_4R315 *0_4_NC

1 2

R295 10K_4

R296 *1K_4_NC

1 2

R166 100K_4

1 2

R310 *47K_4_NC

1 2

R163 100K_4

1 2

R363 *10K_4_NC

1 2

R102 *47K_4_NC

+RTC_CELL

+3.3V_SUS

+3.3V_RUN

12

R344

2

PM_BATLOW#

B B

Q29

2N7002W

*10K_4_NC

31

PM_BATLOW_N 21

DSWVRMEN

On Die DSW VR Enable

R362

330K_4

High = Enable (Default)

Low = Disable

+3.3V_RUN

C140

*0.1U/10V_4_NC

3 5

112

2

1

U9

*TC7SH08FU_NC

2

BUF_PLT_RST#21,27,28

12

A A

4

R142

100K_4

R152 *SJ0402_NC

20

5

4

3

PLTRST#

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

2

Friday, September 27, 2013

PROJECT :

Haswell ULT 7/12

Haswell ULT 7/12

Haswell ULT 7/12

1

D13C

D13C

D13C

11 44

11 44

11 44

4A

4A

4A

Vinafix.com

5

4

3

2

1

+V_VDDQ_VR

C265 10U/6.3V_6

+V1.05S_VCCST

12

31

2

C117 10U/6.3V_6

C114 10U/6.3V_6

C118 10U/6.3V_6

C263 10U/6.3V_6

C136 10U/6.3V_6

C115 2.2U/6.3V_6

C116 2.2U/6.3V_6

C266 2.2U/6.3V_6

C264 2.2U/6.3V_6

R261

10K_4

Q23

2N7002W

H_VR_ENABLE_MCP41

IMVP_PWRGD41

+VCCIN

+VCCIOA_OUT

VR_SVID_CLK41

R262 10K_4

D D

6X10UF MLCC

4X2.2UF MLCC

C C

VCCST_PWRGD#21,33

B B

CPU VDDQ

Haswell ULT 15W : 1.4A Haswell ULT 15W : 32A

+V_VDDQ_VR

AH26

AN33

AP43

AR48

AY35

AY40

AY44

AY50

+VCCIO_OUT

1 2

+V1.05S_VCCST

+VCCIN

TP57

TP20

TP14

TP18

TP11

VCCSENSE

H_CPU_SVIDALRT_N

VR_SVID_DATA

VCCST_PWRGD_L

VR_READY

PWR_DEBUG#

MCP_RSVD_69

MCP_RSVD_70

MCP_RSVD_71

MCP_RSVD_72

AC58

AB23

AD23

AA23

AE59

AD60

AD59

AA59

AE60

AC59

AG58

AC22

AE22

AE23

AB57

AD57

AG57

Haswell ULT MCP(POWER)

HSW_ULT_DDR3L

HSW ULT POWER

12 OF 19

L59

AJ31

AJ33

AJ37

F59

N58

E63

A59

E20

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

U59

V59

C24

C28

C32

J58

U16L

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC

RSVD

RSVD

VCC_SENSE

RSVD

VCCIO_OUT

VCCIOA_OUT

RSVD

RSVD

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS

PWR_DEBUG

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCST

VCCST

VCCST

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

CPU VCC

+VCCIN

C98 22U/6.3V_6

C84 22U/6.3V_6

C65 22U/6.3V_6

C92 22U/6.3V_6

C33 22U/6.3V_6

C76 22U/6.3V_6

C21 22U/6.3V_6

C70 22U/6.3V_6

C52 22U/6.3V_6

C46 22U/6.3V_6

C35 22U/6.3V_6

C22 22U/6.3V_6

C25 22U/6.3V_6

C29 22U/6.3V_6

C32 22U/6.3V_6

C59 22U/6.3V_6

C24 22U/6.3V_6

C28 22U/6.3V_6

C31 22U/6.3V_6

C57 22U/6.3V_6

C23 22U/6.3V_6

C27 10U/6.3V_6

C30 10U/6.3V_6

C34 10U/6.3V_6

C38 100P/50V_4

C26 100P/50V_4

C36 100P/50V_4

C37 100P/50V_4

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

16 X 22UF(0603 MLCC)

3 X 10UF(0603 MLCC)

+VCCIN

+

C110

100U/6.3V/3216

+5V_ALW2 +VCCIN

+

C87

100U/6.3V/3216

R407

100K_4

31

2

Q38

2N7002W

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

1

R289

75_4

R293

130_4

+VCCIO_OUT

+VCCIO_OUT

12

R288

*75_4_NC

R290

*130_4_NC

VR_SVID_DATA 41

RUN_ON15,21,40,42,43

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

2

Friday, September 27, 2013

Haswell ULT 8/12

Haswell ULT 8/12

Haswell ULT 8/12

+V1.05S_VCCST

2

+V1.05S_VCCST

5

R32 100/F_4

VCCSENSE H_CPU_SVIDALRT_N

PWR_DEBUG#

R1 150_6

+VCCIN

VCCSENSE 41 VR_SVID_ALERT# 41

+1.05V_RUN

4

+1.05V_RUN

R95 *SJ1206_NC

112

A A

21

SVID ALERT

R284 43_4

SVID DATA

VR_SVID_DATA

+V1.05S_VCCST

+V1.05S_VCCST

12

3

2

D13C

D13C

D13C

31

R408

49.9/F_6

Q39

2N7002W

12 44

12 44

12 44

4A

4A

4A

Vinafix.com

5

Haswell ULT (GND)

4

3

2

1

HSW_ULT_DDR3L

18 OF 19

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

N23

R23

T23

U10

AL1

AM11

AP7

AU10

AU15

AW14

AY14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U16O

HSW_ULT_DDR3L

15 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AV59

AV8

AW16

AW24

AW33

AW35

AW37

AW4

AW40

AW42

AW44

AW47

AW50

AW51

AW59

AW60

AY11

AY16

AY18

AY22

AY24

AY26

AY30

AY33

AY4

AY51

AY53

AY57

AY59

AY6

B20

B24

B26

B28

B32

B36

B4

B40

B44

B48

B52

B56

B60

C11

C14

C18

C20

C25

C27

C38

C39

C57

D12

D14

D18

D2

D21

D23

D25

D26

D27

D29

D30

D31

D33

D34

D35

D37

D38

D39

D41

D42

D43

D45

D46

D47

D49

D50

D51

D53

D54

D55

D57

D59

D62

E11

E17

G18

G22

H13

HSW_ULT_DDR3L

U16P

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D8

VSS

VSS

VSS

F20

VSS

F26

VSS

F30

VSS

F34

VSS

F38

VSS

F42

VSS

F46

VSS

F50

VSS

F54

VSS

F58

VSS

F61

VSS

VSS

VSS

G3

VSS

G5

VSS

G6

VSS

G8

VSS

VSS

16 OF 19

VSS_SENSE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H17

H57

J10

J22

J59

J63

K1

K12

L13

L15

L17

L18

L20

L58

L61

L7

M22

N10

N3

P59

P63

R10

R22

R8

T1

T58

U20

U22

U61

U9

V10

V3

V7

W20

W22

Y10

Y59

Y63

V58

AH46

V23

E62

AH16

R33

100/F_4

AT2

RSVD

AU44

RSVD

AV44

RSVD

D15

RSVD

F22

RSVD

H22

RSVD

J21

RSVD

VSSSENSE 41

U16R

HSW_ULT_DDR3L

D D

C C

B B

A11

A14

A18

A24

A28

A32

A36

A40

A44

A48

A52

A56

AA1

AA58

AB10

AB20

AB22

AB7

AC61

AD21

AD3

AD63

AE10

AE5

AE58

AF11

AF12

AF14

AF15

AF17

AF18

AG1

AG11

AG21

AG23

AG60

AG61

AG62

AG63

AH17

AH19

AH20

AH22

AH24

AH28

AH30

AH32

AH34

AH36

AH38

AH40

AH42

AH44

AH49

AH51

AH53

AH55

AH57

AJ13

AJ14

AJ23

AJ25

AJ27

AJ29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U16N

14 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ35

AJ39

AJ41

AJ43

AJ45

AJ47

AJ50

AJ52

AJ54

AJ56

AJ58

AJ60

AJ63

AK23

AK3

AK52

AL10

AL13

AL17

AL20

AL22

AL23

AL26

AL29

AL31

AL33

AL36

AL39

AL40

AL45

AL46

AL51

AL52

AL54

AL57

AL60

AL61

AM1

AM17

AM23

AM31

AM52

AN17

AN23

AN31

AN32

AN35

AN36

AN39

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN51

AN52

AN60

AN63

AN7

AP10

AP17

AP20

AP22

AP23

AP26

AP29

AP3

AP31

AP38

AP39

AP48

AP52

AP54

AP57

AR11

AR15

AR17

AR23

AR31

AR33

AR39

AR43

AR49

AR5

AR52

AT13

AT35

AT37

AT40

AT42

AT43

AT46

AT49

AT61

AT62

AT63

AU1

AU16

AU18

AU20

AU22

AU24

AU26

AU28

AU30

AU33

AU51

AU53

AU55

AU57

AU59

AV14

AV16

AV20

AV24

AV28

AV33

AV34

AV36

AV39

AV41

AV43

AV46

AV49

AV51

AV55

U16Q

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

5

TP_DC_TEST_AY60

DC_TEST_AY61_AW61

DC_TEST_AY62_AW62

TP_DC_TEST_B2

DC_TEST_A3_B3

DC_TEST_A61_B61

DC_TEST_B62_B63

DC_TEST_C1_C2

TP131

TP2

A A

AY2

DAISY_CHAIN_NCTF_AY2

AY3

DAISY_CHAIN_NCTF_AY3

AY60

DAISY_CHAIN_NCTF_AY60

AY61

DAISY_CHAIN_NCTF_AY61

AY62

DAISY_CHAIN_NCTF_AY62

B2

DAISY_CHAIN_NCTF_B2

B3

DAISY_CHAIN_NCTF_B3

B61

DAISY_CHAIN_NCTF_B61

B62

DAISY_CHAIN_NCTF_B62

B63

DAISY_CHAIN_NCTF_B63

C1

DAISY_CHAIN_NCTF_C1

C2

DAISY_CHAIN_NCTF_C2

HSW_ULT_DDR3L

17 OF 19

4

DAISY_CHAIN_NCTF_A3

DAISY_CHAIN_NCTF_A4

DAISY_CHAIN_NCTF_A60

DAISY_CHAIN_NCTF_A61

DAISY_CHAIN_NCTF_A62

DAISY_CHAIN_NCTF_AV1

DAISY_CHAIN_NCTF_AW1

DAISY_CHAIN_NCTF_AW2

DAISY_CHAIN_NCTF_AW3

DAISY_CHAIN_NCTF_AW61

DAISY_CHAIN_NCTF_AW62

DAISY_CHAIN_NCTF_AW63

A3

DC_TEST_A3_B3

A4

TP_DC_TEST_A4

A60

TP_DC_TEST_A60

A61

DC_TEST_A61_B61

A62

TP_DC_TEST_A62

AV1

TP_DC_TEST_AV1

AW1

TP_DC_TEST_AW1

AW2

DC_TEST_AY2_AW2

AW3

DC_TEST_AY3_AW3

AW61

DC_TEST_AY61_AW61

AW62

DC_TEST_AY62_AW62

AW63

TP_DC_TEST_AW63

TP48

TP51

TP58

TP130

TP138

TP132

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

3

2

Friday, September 27, 2013

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

Haswell ULT 9/12

Haswell ULT 9/12

Haswell ULT 9/12

1

D13C

D13C

D13C

13 44

13 44

13 44

4A

4A

4A

Vinafix.com

5

4

3

2

1

U16S

CFG0

CFG1

D D

R298 49.9/F_4

R2 8.25K/F_4

C C

TP103

TP98

TP99

TP104

TP100

TP85

TP90

TP82

TP19

TP97

TP91

TP102

TP92

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

NOA_RCOMP

REFPKG_OCC

TD_IREF

AC60

AC62

AC63

AA63

AA60

Y61

Y60

V62

V61

V60

U60

T63

T62

T61

T60

AA62

U63

AA61

U62

V63

H18

B12

Y62

J20

A5

E1

D1

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

RSVD

RSVD

RSVD

RSVD

RSVD

TD_IREF

HSW_ULT_DDR3L

RESERVED

19 OF 19

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

PROC_OPI_RCOMP

RSVD

RSVD

RSVD

VSS

VSS

RSVD

RSVD

AV63

MCP_RSVD_19

AU63

MCP_RSVD_20

C63

MCP_RSVD_21

C62

MCP_RSVD_22

B43

MCP_RSVD_23

A51

MCP_RSVD_24

B51

MCP_RSVD_25

L60

MCP_RSVD_26

N60

W23

Y22

AY15

PROC_OPI_COMP

AV62

D58

P22

N21

P20

R20

TP114

TP115

TP67

TP68

TP49

TP59

TP54

TP12

R355 49.9/F_4

Processor Strapping

01

CFG0

EAR-STALL/NOT STALL RESET SEQUENCE

AFTER PCU PLL IS LOCKED

CFG1

PCH/ PCH LESS MODE SELECTION

STALL(DEFAULT) NORMAL OPERATION; NO STALL

PCH-LESS MODE(DEFAULT) NORMAL OPERATION

CFG0

CFG1

R117 *1K_4_NC

R109 *1K_4_NC

CFG3

PHYSICAL_DEBUG_ENABLED (DFX PRIVACY)

B B

A A

CFG4

DISPLAY PORT PRESENCE STRAP

CFG 8

ALLOW THE USE OF NOA ON LOCKED UNITS

CFG9

NO SVID PROTOCOL CAPABLE VR CONNECTED

CFG10

SAFE MODE BOOT

REFPKG_OCC

SIGNAL USAGE

5

DISABLED

NO PHYSICAL DISPLAY PORT ATTACHED TO

EMBEDDED DISPLAY PORT

DISABLED

NO PHYSICAL DISPLAY PORT ATTACHED TO

EMBEDDED DISPLAY PORT

DISABLED(DEFAULT); IN THIS CASE,

NOA WILL BE DISABLED IN LOCKED

UNITS AND ENABLED IN UN-LOCKED

UNITS

VRS SUPPORTING SVID PROTOCOL ARE

PRESENT

POWER FEATURES ACTIVATED

DURING RESET

OPEN

NORMAL HSW ULT PACKAGE

4

ENABLED

AN EXTERNAL DISPLAY PORT DEVICE IS CONNECTED

TO THE EMBEDDED DISPLAY PORT

ENABLED

AN EXTERNAL DISPLAY PORT DEVICE IS CONNECTED

TO THE EMBEDDED DISPLAY PORT

ENABLED; NOA WILL BE AVAILABLE

REGARDLESS OF THE LOCKING OF THE UNIT

NO VR SUPPORTING SVID IS PRESENT. THE

CHIP WILL NOT GENERATE (OR RESPOND TO)

SVID ACTIVITY

POWER FEATURES (ESPECIALLY CLOCK

GATINE ARE NOT ACTIVATED

GND

HSW INTERPOSTER

3

CFG3

CFG4

CFG8

CFG9

CFG10

REFPKG_OCC

2

R300 *1K_4_NC

R101 1K_4

R88 *1K_4_NC

R83 *1K_4_NC

R96 *1K_4_NC

+3.3V_RUN

1 2

R265 *100K/F_4_NC

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

Date: Sheet of

Friday, September 27, 2013

PROJECT :

Haswell ULT 10/12

Haswell ULT 10/12

Haswell ULT 10/12

1

D13C

D13C

D13C

14 44

14 44

14 44

4A

4A

4A

Loading...

Loading...