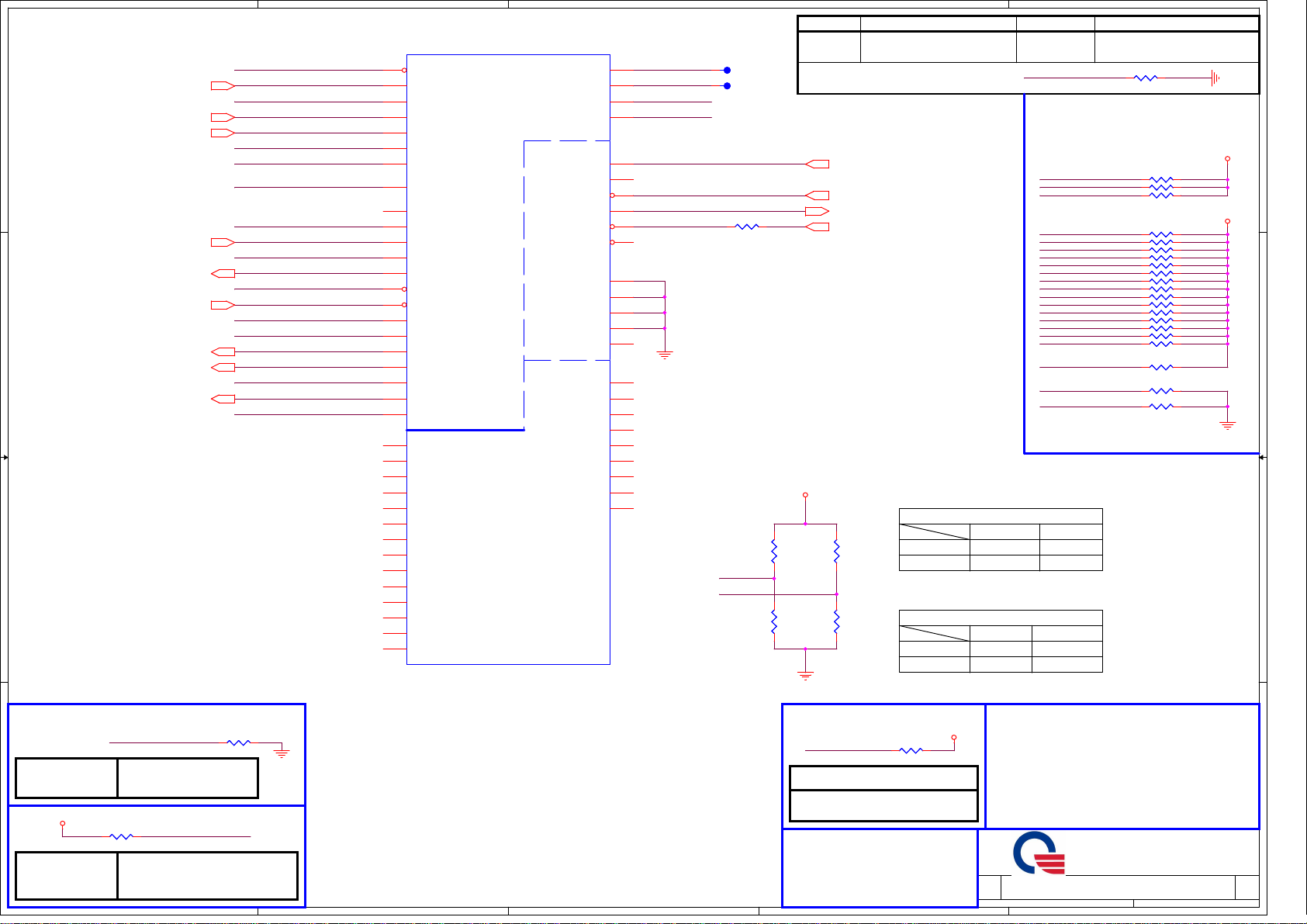

Dell XPS 13 Schematics

1

2

3

4

5

6

7

8

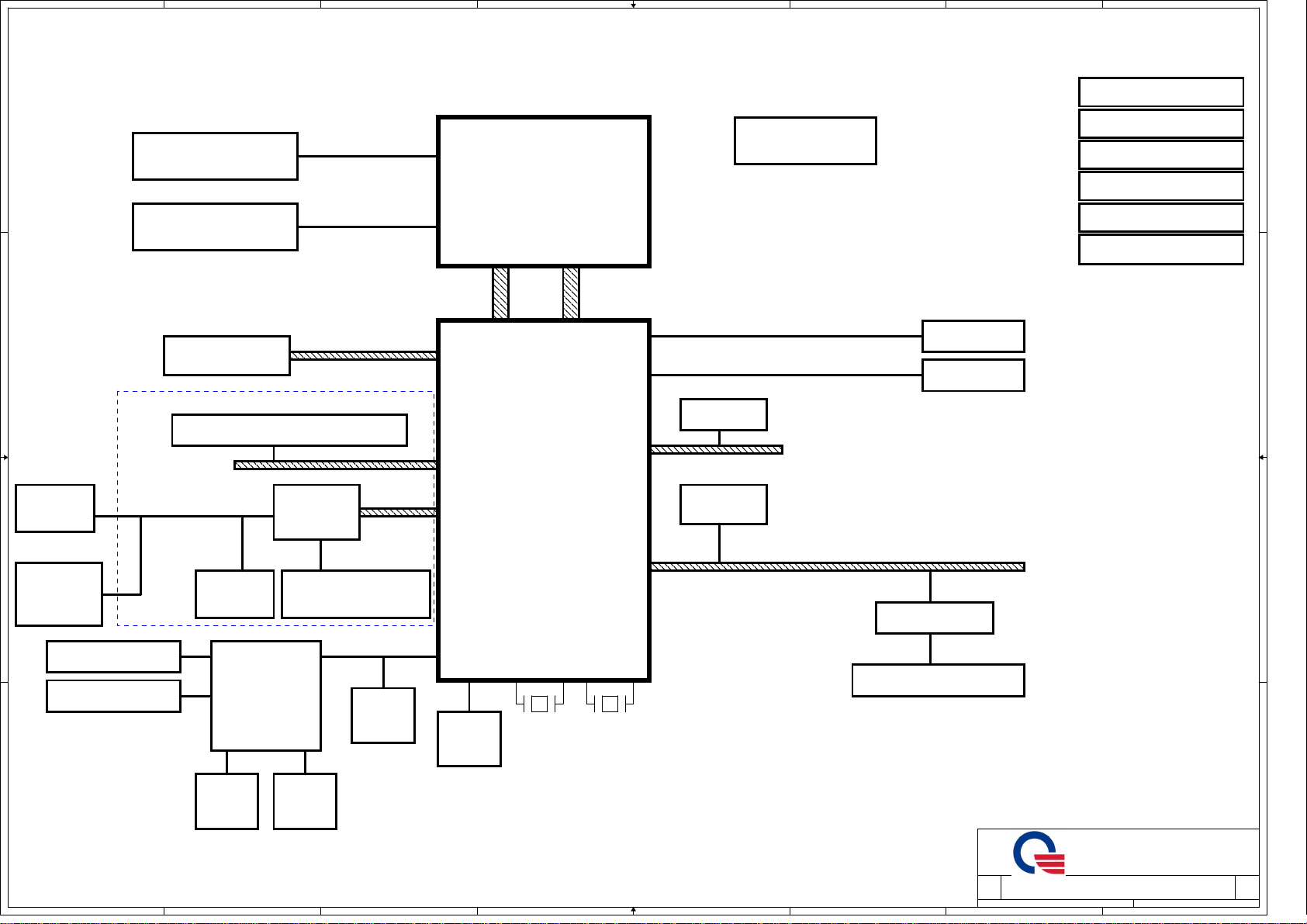

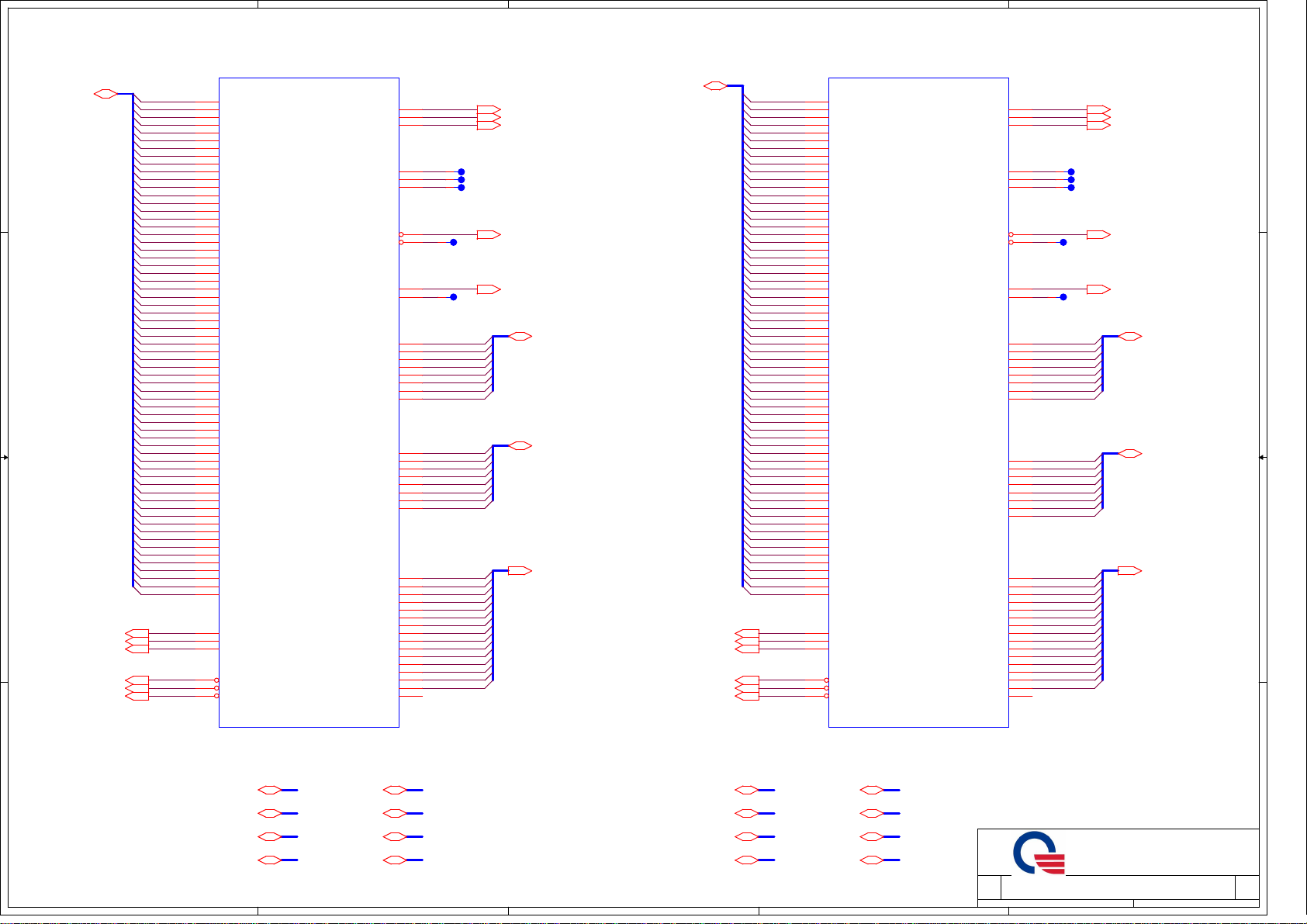

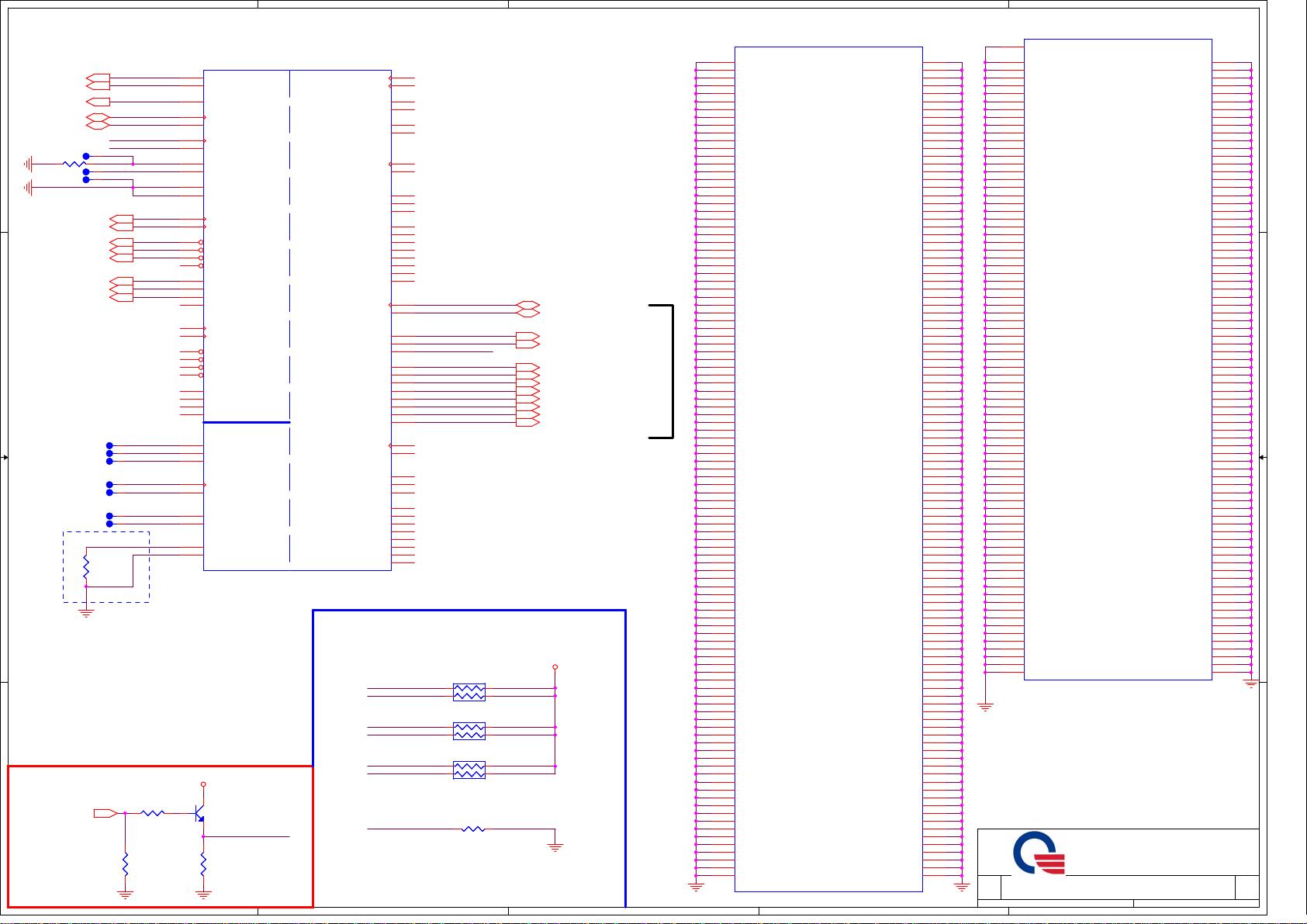

Spyder 13.3" UMA BLOCK DIAGRAM

A A

DDR3-Memory Onboard

H=4.0mm

PAGE 15

DDR3 1333 MHZ

Sandy Bridge(ULV) 17W

CPU

BGA 1023 DC

DDR3-Memory Onboard

H=4.0mm

B B

SSD mSATA -HDD

SATA GEN II

PAGE 16

PAGE 27

DDR3 1333 MHZ

SATA 6G

FDI LINK

2.7GT /s

Audio Board

USB2.0 Port / USB Powershare

PAGE 03

SLG55584 x1

2C GT2

31 mm X 24 mm

PAGE 3~7

DMI LINK

5GT /s

Mobile Intel

Series 6 Chipset

SINGLE CHANNEL LVDS

DISPLAY PORT C

Camera

USB2.0

FAN & THERMAL

SMSC1422

PAGE 19

PG 28

LCD CONN

PAGE 19

Mini DP CONN

PAGE 18

+VCHGR

PAGE 32

+3.3V_ALW/+5V_ALW

PAGE 33

+1.5V_SUS/+0.75V_DDR_VTT

PAGE 34

+VCCSA_CORE

PAGE 36

+1.05V_PCH/+1.8V_RUN

PAGE 35

+VCC_CORE/+VCC_GFX_CORE

PAGE 37

USB2.0

PCH

Speaker 1W

PAGE 29

Audio Codec

ALC275

PAGE 04

IHDA

QS67

Couger Point

WLAN/BT 3.0

i6230

PAGE 21

C C

AUDIO

HEADSET

SWITCH

-TS3A225E

PAGE 29

Keyboard Conn.

Touch Pad

D D

PAGE 24

PAGE 24

PAGE 04 PAGE 04

KBC

ITE 8519

PWM FAN

PAGE 28

HP+MIC Combo Jack x1Speaker 1W

PAGE 22

SPI ROM

4Mbit

PAGE 25

LPC

TPM

PAGE 23

SPI

SPI ROM

32Mbit

FCBGA 1017

22 mm X 22 mm

25MHz

PAGE 25

PAGE 8~14

32.768KHz

www.schematic-x.blogspot.com

1

2

3

4

PCI-E

USB3.0 Controller

USB 3.0/2.0 Combo Ports x1

5

6

PAGE 25

PAGE 20

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

Thursday, October 13, 2011

7

PROJECT :

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

D13

D13

D13

1 41

1 41

1 41

8

1A

1A

1A

1

2

3

4

5

6

7

8

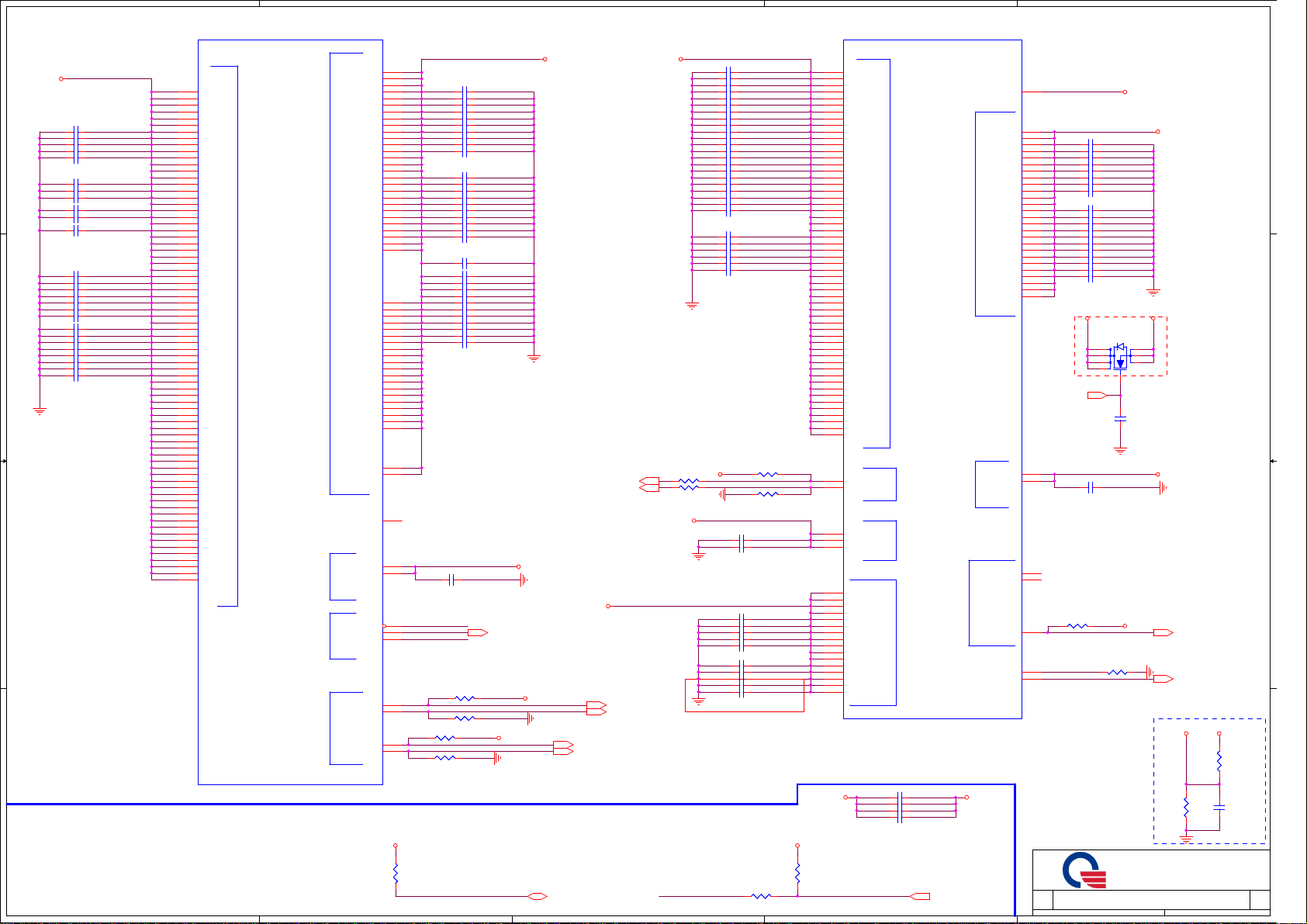

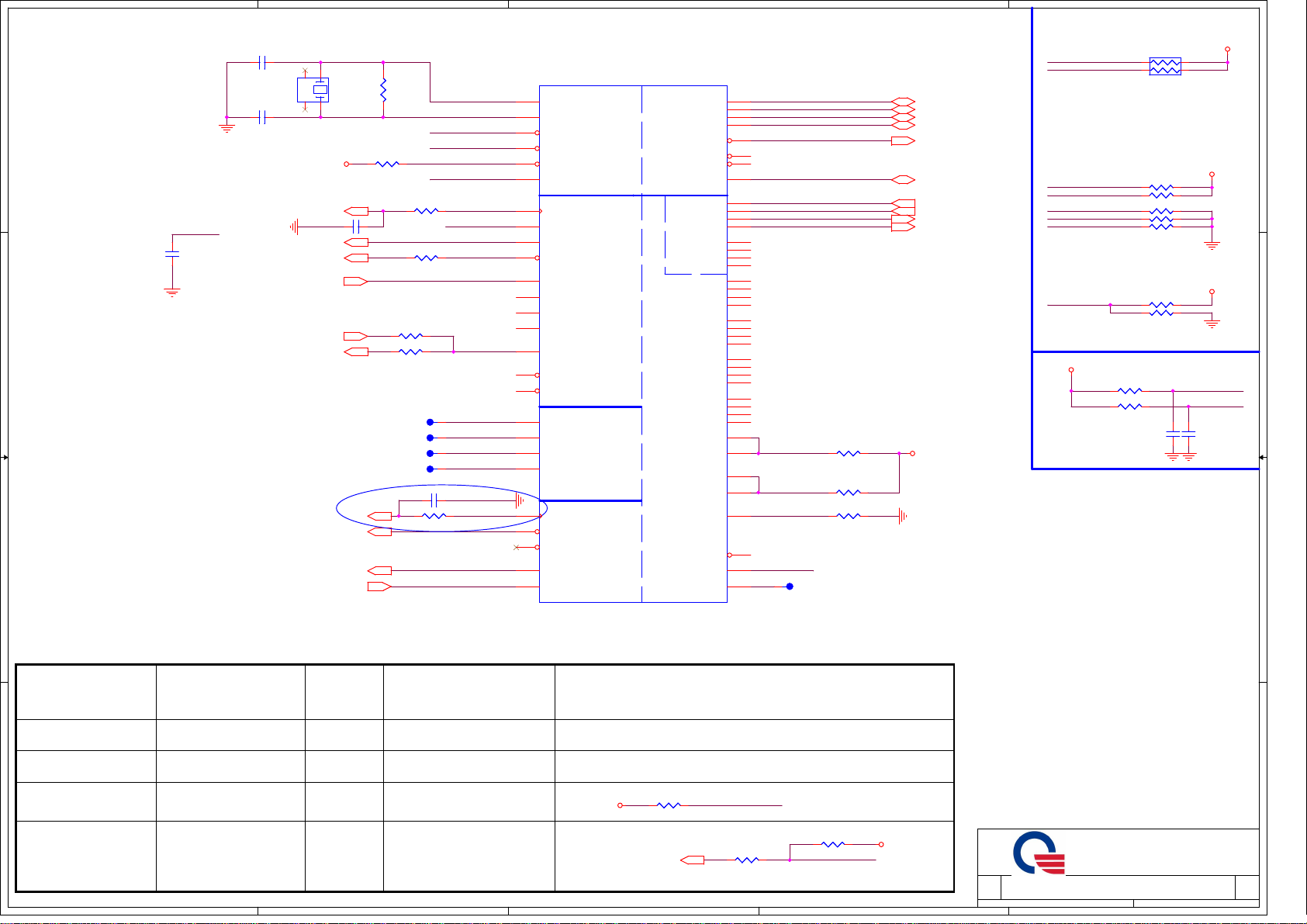

power

SLP_S3# SLP_S4# SLP_S5# ALW_ON +3.3V_ALW +5V_ALW SUS_ON +3.3V_SUS +5V_SUS RUN_ON +3.3V_RUN +5V_RUN

AOAC flag

State

A A

S0

S3

S4/S5 AC

S4/S5

H H H H H H H H H H H H

L

L

L

H H H H H H H H L L L

L L H H H L L L L L L

L L L L L L L L

L LL

L

L

L

L

USB2.0

Power share

USB_BAK_EN#

L

L

L

L

DC Only

AC/DC

L

L L L L L L L L L L L

L

L

No Exist

B B

AOAC(S4)

H H H H H H L L LL LL

H

H

C C

D D

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

1

2

3

4

5

6

Thursday, October 13, 2011

7

PROJECT :

Power Rails

Power Rails

Power Rails

D13

D13

D13

2 41

2 41

2 41

8

1A

1A

1A

5

4

3

2

1

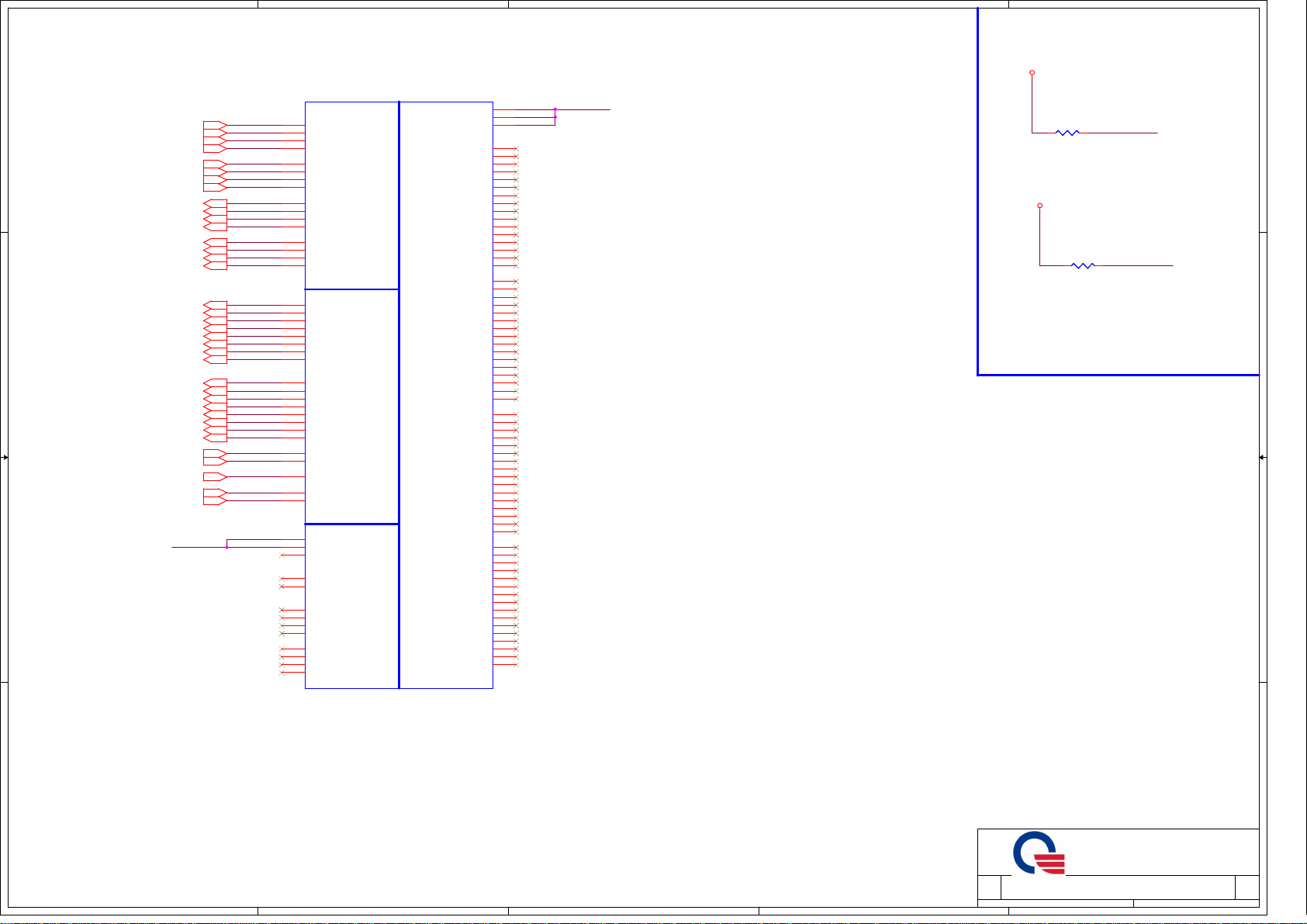

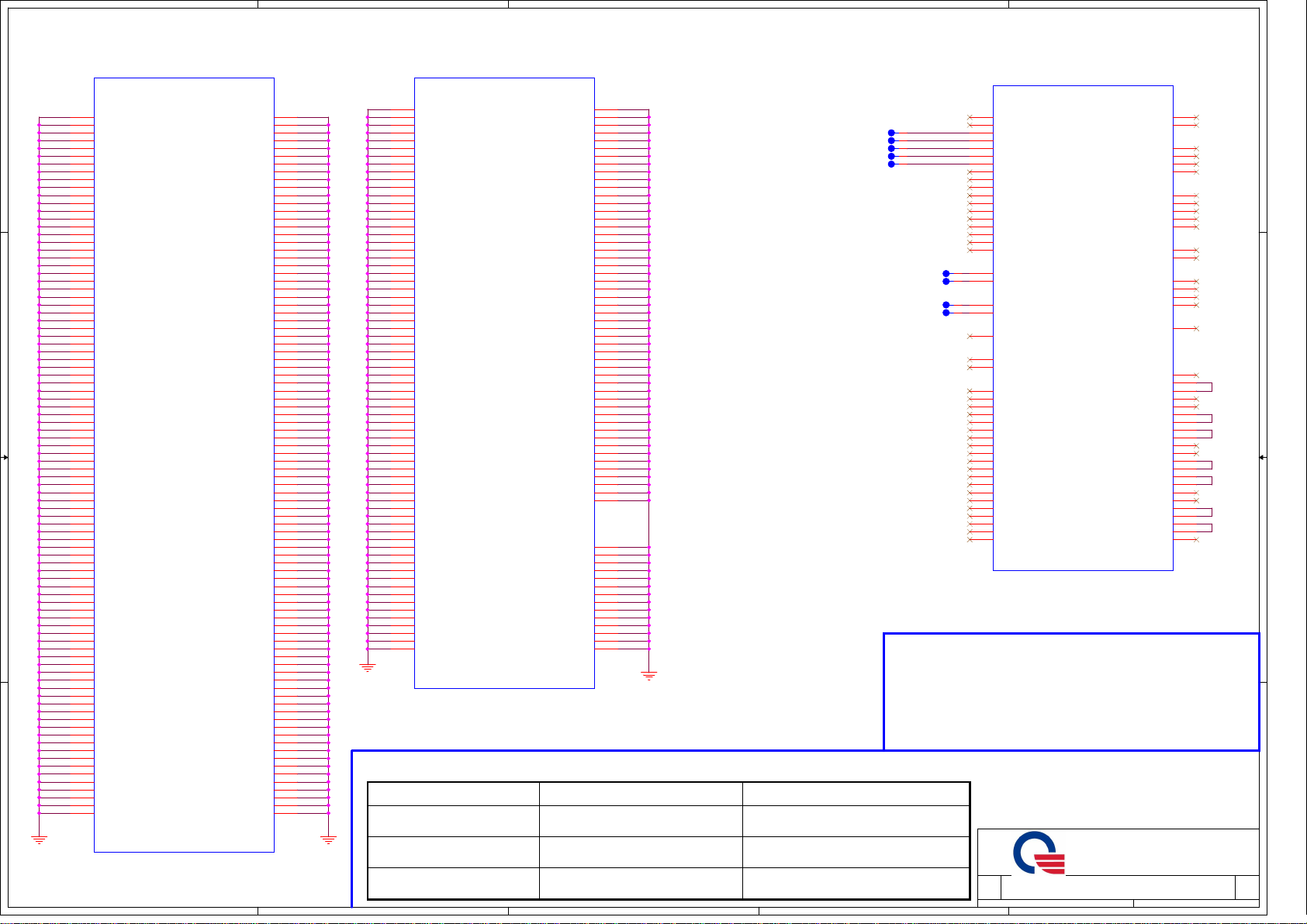

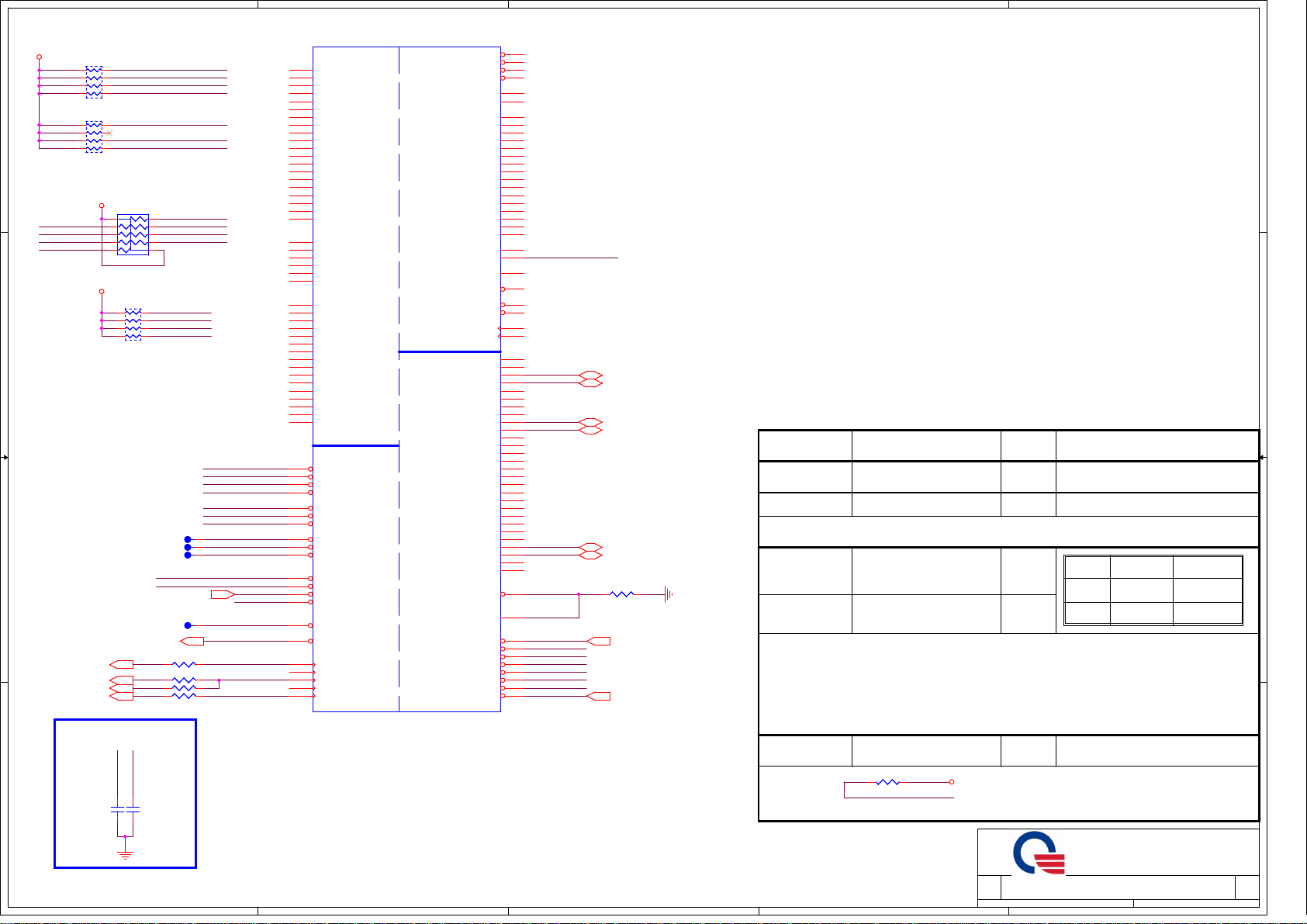

DP & PEG Compensation

Sandy Bridge Processor (DMI,PEG,FDI)

CPU is i7 in schematic

U25A

U25A

D D

C C

eDP_ICOMPO 12mil

eDP_COMPIO 4mil

B B

DMI_TXN0[8]

DMI_TXN1[8]

DMI_TXN2[8]

DMI_TXN3[8]

DMI_TXP0[8]

DMI_TXP1[8]

DMI_TXP2[8]

DMI_TXP3[8]

DMI_RXN0[8]

DMI_RXN1[8]

DMI_RXN2[8]

DMI_RXN3[8]

DMI_RXP0[8]

DMI_RXP1[8]

DMI_RXP2[8]

DMI_RXP3[8]

FDI_TXN0[8]

FDI_TXN1[8]

FDI_TXN2[8]

FDI_TXN3[8]

FDI_TXN4[8]

FDI_TXN5[8]

FDI_TXN6[8]

FDI_TXN7[8]

FDI_TXP0[8]

FDI_TXP1[8]

FDI_TXP2[8]

FDI_TXP3[8]

FDI_TXP4[8]

FDI_TXP5[8]

FDI_TXP6[8]

FDI_TXP7[8]

FDI_FSYNC0[8]

FDI_FSYNC1[8]

FDI_INT[8]

FDI_LSYNC0[8]

FDI_LSYNC1[8]

EDP_COMP

M2

DMI_RX#[0]

P6

DMI_RX#[1]

P1

DMI_RX#[2]

P10

DMI_RX#[3]

N3

DMI_RX[0]

P7

DMI_RX[1]

P3

DMI_RX[2]

P11

DMI_RX[3]

K1

DMI_TX#[0]

M8

DMI_TX#[1]

N4

DMI_TX#[2]

R2

DMI_TX#[3]

K3

DMI_TX[0]

M7

DMI_TX[1]

P4

DMI_TX[2]

T3

DMI_TX[3]

U7

FDI0_TX#[0]

W11

FDI0_TX#[1]

W1

FDI0_TX#[2]

AA6

FDI0_TX#[3]

W6

FDI1_TX#[0]

V4

FDI1_TX#[1]

Y2

FDI1_TX#[2]

AC9

FDI1_TX#[3]

U6

FDI0_TX[0]

W10

FDI0_TX[1]

W3

FDI0_TX[2]

AA7

FDI0_TX[3]

W7

FDI1_TX[0]

T4

FDI1_TX[1]

AA3

FDI1_TX[2]

AC8

FDI1_TX[3]

AA11

FDI0_FSYNC

AC12

FDI1_FSYNC

U11

FDI_INT

AA10

FDI0_LSYNC

AG8

FDI1_LSYNC

AF3

eDP_COMPIO

AD2

eDP_ICOMPO

AG11

eDP_HPD

AG4

eDP_AUX#

AF4

eDP_AUX

AC3

eDP_TX#[0]

AC4

eDP_TX#[1]

AE11

eDP_TX#[2]

AE7

eDP_TX#[3]

AC1

eDP_TX[0]

AA4

eDP_TX[1]

AE10

eDP_TX[2]

AE6

eDP_TX[3]

IC,SNB_2CBGA,1P0

IC,SNB_2CBGA,1P0

DMI Intel(R) FDI DP

DMI Intel(R) FDI DP

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

PEG_COMP

PEG_ICOMPO 12mil

PEG_ICOMPI, PEG_RCOMPO 4mil,

+1.05V_VCCIO

R189 24.9/F_4R189 24.9/F_4

eDP_COMPIO and ICOMPO signals should

be shorted near balls and routed with

typical impedance <25 mohms

+1.05V_VCCIO

R184 24.9/F_4R184 24.9/F_4

PEG_ICOMPI and RCOMPO signals should

be routed within 500 mils

typical impedance = 43 mohms

PEG_ICOMPO signals should

be routed within 500 mils

typical impedance = 14.5 mohms

EDP_COMP

PEG_COMP

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

5

4

3

2

Thursday, October 13, 2011

PROJECT :

Sandy Bridge 1/5

Sandy Bridge 1/5

Sandy Bridge 1/5

1

D13

D13

D13

3 41

3 41

3 41

1A

1A

1A

5

4

3

2

1

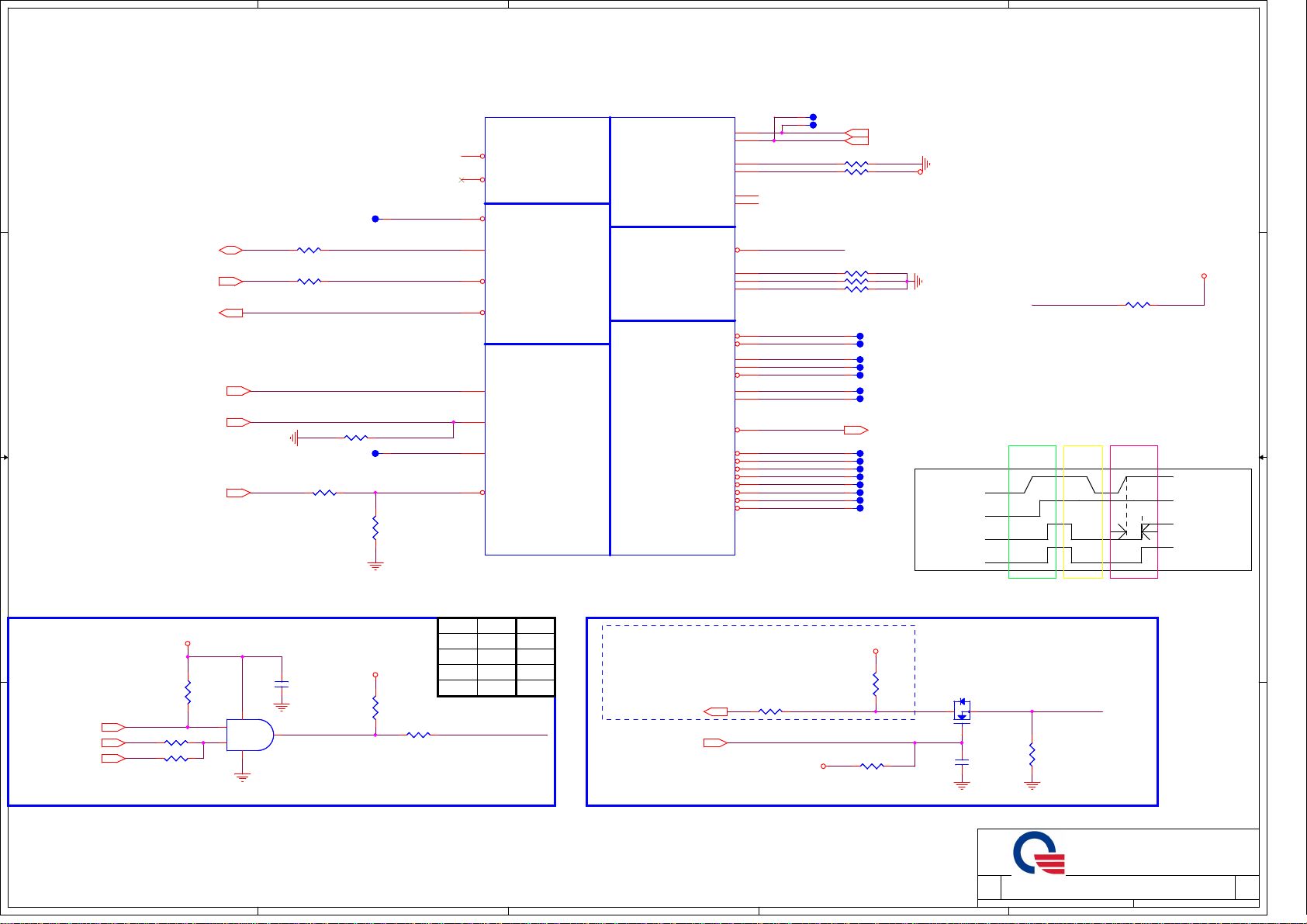

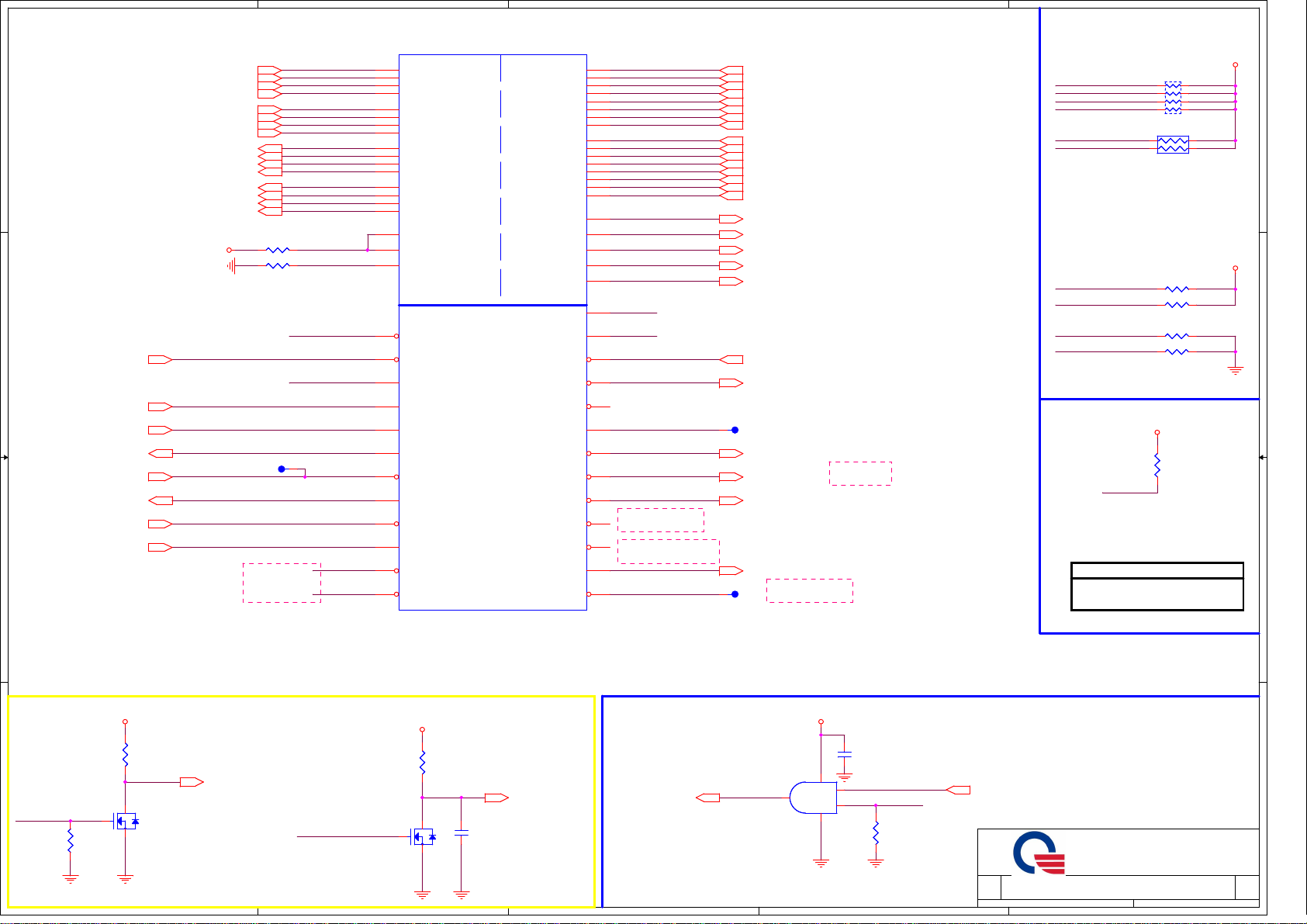

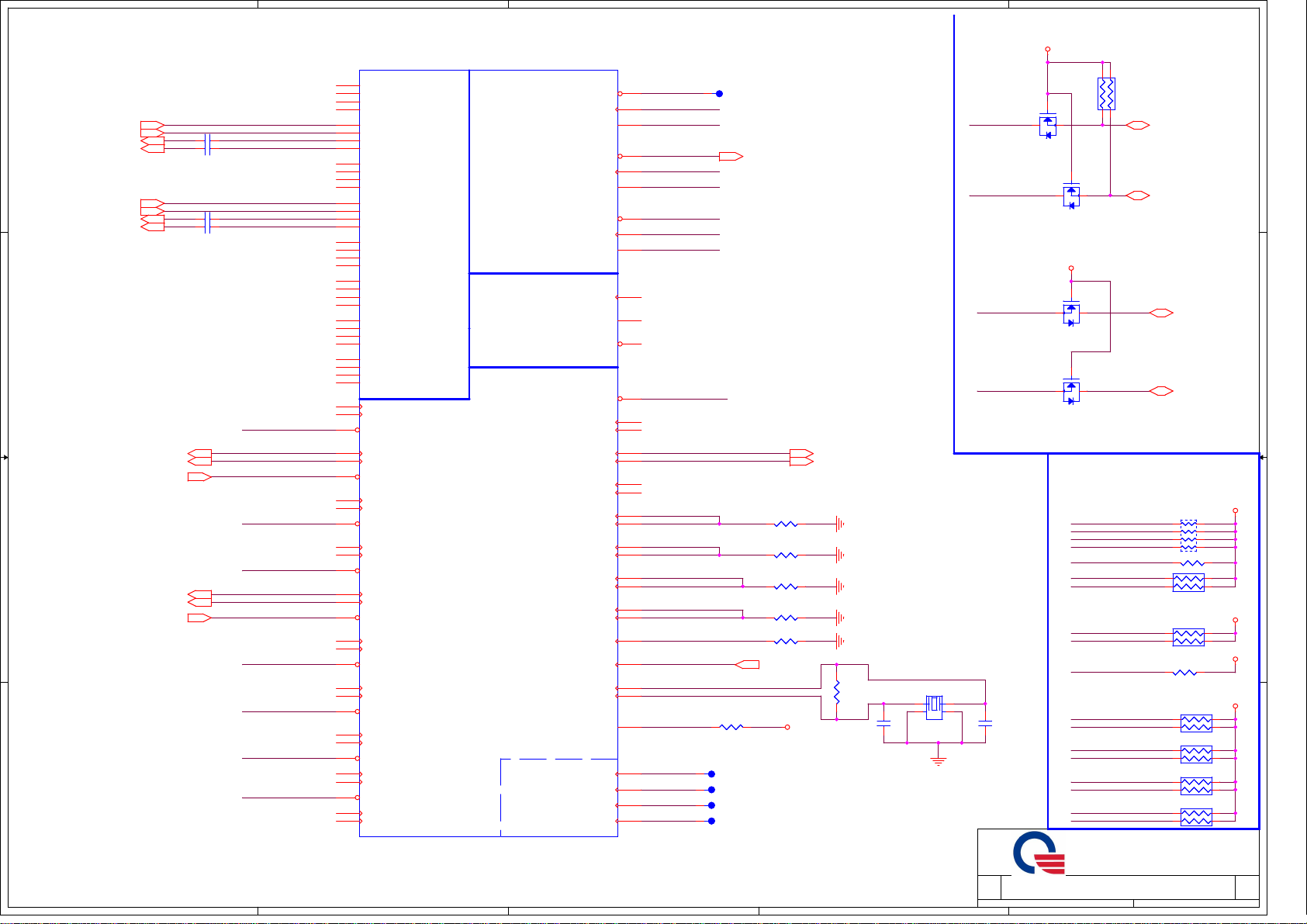

Sandy Bridge Processor (CLK,MISC,JTAG)

CPU is i7 in schematic

U25B

D D

SNB can be floating

T77T77

TP_CATERR#

U25B

F49

C57

C49

PROC_SELECT#

PROC_DETECT#

CATERR#

J3

BCLK

MISC THERMAL PWR MANAGEMENT

MISC THERMAL PWR MANAGEMENT

DPLL_REF_CLK

DPLL_REF_CLK#

CLOCKS

CLOCKS

BCLK#

BCLK_ITP

BCLK_ITP#

H2

AG3

AG1

N59

N58

CLK_DP_P_R

CLK_DP_N_R

T81T81

T82T82

R188 1K_4R188 1K_4

R187 1K_4R187 1K_4

CLK_CPU_BCLKP [12]

CLK_CPU_BCLKN [12]

+1.05V_VCCIO

CPU_DRAMRST#

AT30

SM_RCOMP_0

BF44

SM_RCOMP_1

BE43

SM_RCOMP_2

BG43

N53

N55

L56

L55

J58

M60

L59

K58

G58

E55

E59

G55

G59

H60

J59

J61

R122 1K_4R122 1K_4

+3.3V_SUS

R172 140/F_4R172 140/F_4

R174 25.5/F_4R174 25.5/F_4

R177 200/F_4R177 200/F_4

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDI

XDP_TDO

T57T57

T61T61

T60T60

T56T56

T63T63

T65T65

T64T64

XDP_DBRST# [8]

T62T62

T58T58

T67T67

T59T59

T68T68

T69T69

T70T70

T66T66

+1.5V_SUS

R81 1K_4R81 1K_4

R123

R123

1K_4

1K_4

+1.5V_CPU

DRAM_PWRGD

SYS_PWROK

SM_DRAMPWROK

PMF780SN

PMF780SN

3 1

Q24

Q24

2

C73

C73

0.047U/10V_4

0.047U/10V_4

IMVP7_PROCHOT#

Boot S3

CPU_DRAMRST#DDR3_DRAMRST#_R

R124

R124

4.99K/F_4

4.99K/F_4

R168 62_4R168 62_4

S3 RSM

100 ns after +1.5V_CPU

reaches 80%

+1.05V_VCCIO

R171

R171

750/F_4

750/F_4

+1.5V_CPU

R165

R165

200/F_4

200/F_4

R164 130/F_4R164 130/F_4

PECI_EC_R

SM_DRAMPWROK

CPU_PLTRST#

Pin1

A48

C45

D45

C48

B46

BE45

D44

IC,SNB_2CBGA,1P0

IC,SNB_2CBGA,1P0

Pin2 Pin4

L L

H

H

SM_DRAMPWROKSM_DRAMPWROK_R

PECI

PROCHOT#

THERMTRIP#

PM_SYNC

UNCOREPWRGOOD

SM_DRAMPWROK

RESET#

L

HL

L

L

L

H

H

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

DDR3

MISC

DDR3

MISC

PRDY#

PREQ#

TCK

TMS

TRST#

TDI

TDO

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

JTAG & BPM

JTAG & BPM

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

Please close System RAM

DDR3_DRAMRST#[15,16]

DDR_HVREF_RST_PCH[12]

PECI_EC[22]

IMVP7_PROCHOT#[22,32,37]

PM_THRMTRIP#[13]

C C

H_PM_SYNC[8]

H_PWRGOOD[13]

PLTRST#[11,20,21,22,23]

B B

+3.3V_SUS

R160

R160

200_4

200_4

PM_DRAM_PWRGD[8]

SYS_PWROK[8]

EC_PWROK[8,22]

R163 0_4R163 0_4

1 2

1 2

R162 *0_4_NCR162 *0_4_NC

2

1

R166 43_4R166 43_4

R169 56_4R169 56_4

U23

U23

74AHC1G09GW

74AHC1G09GW

3 5

R167 10K_4R167 10K_4

R170 1.5K/F_4R170 1.5K/F_4

C290

C290

0.1U/16V_4

0.1U/16V_4

4

H_PROCHOT#

T79T79

A A

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

5

4

3

2

Thursday, October 13, 2011

PROJECT :

Sandy Bridge 2/5

Sandy Bridge 2/5

Sandy Bridge 2/5

1

D13

D13

D13

4 41

4 41

4 41

1A

1A

1A

5

4

3

2

1

Sandy Bridge Processor (DDR3)

CPU is i7 in schematic

U25C

U25C

M_A_DQ[63..0][15]

D D

C C

B B

M_A_BS0[15,17]

M_A_BS1[15,17]

M_A_BS2[15,17]

M_A_CAS#[15,17]

M_A_RAS#[15,17]

M_A_WE#[15,17]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AG6

AP11

AJ10

AR11

AP6

AU6

AV9

AR6

AP8

AT13

AU13

BC7

BB7

BA13

BB11

BA7

BA9

BB9

AY13

AV14

AR14

AY17

AR19

BA14

AU14

BB14

BB17

BA45

AR43

AW48

BC48

BC45

AR45

AT48

AY48

BA49

AV49

BB51

AY53

BB49

AU49

BA53

BB55

BA55

AV56

AP50

AP53

AV54

AT54

AP56

AP52

AN57

AN53

AG56

AG53

AN55

AN52

AG55

AK56

BD37

BF36

BA28

BE39

BD39

AT41

AJ6

AL6

AJ8

AL8

AL7

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

AU36

SA_CLK[0]

SA_CKE[0]

SA_CLK[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AV36

AY26

AT40

AU40

BB26

BB40

BC41

AY40

BA41

AL11

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW45

AV51

AT56

AK54

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW41

AY28

AU26

M_A_DQSN0

M_A_DQSN1

M_A_DQSN2

M_A_DQSN3

M_A_DQSN4

M_A_DQSN5

M_A_DQSN6

M_A_DQSN7

M_A_DQSP0

M_A_DQSP1

M_A_DQSP2

M_A_DQSP3

M_A_DQSP4

M_A_DQSP5

M_A_DQSP6

M_A_DQSP7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

SA_CLK#[0]

SA_CLK#[1]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

T48T48

T49T49

T45T45

T51T51

T50T50

M_A_CLKP0 [15,17]

M_A_CLKN0 [15,17]

M_A_CKE0 [15,17]

M_A_CS#0 [15,17]

M_A_ODT0 [15,17]

M_A_DQSN[7..0] [15]

M_A_DQSP[7..0] [15]

M_A_A[14..0] [15,17]

M_B_DQ[63..0][16]

M_B_BS0[16,17]

M_B_BS1[16,17]

M_B_BS2[16,17]

M_B_CAS#[16,17]

M_B_RAS#[16,17]

M_B_WE#[16,17]

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

CPU is i7 in schematic

U25D

U25D

AL4

SB_DQ[0]

AL1

SB_DQ[1]

AN3

SB_DQ[2]

AR4

SB_DQ[3]

AK4

SB_DQ[4]

AK3

SB_DQ[5]

AN4

SB_DQ[6]

AR1

SB_DQ[7]

AU4

SB_DQ[8]

AT2

SB_DQ[9]

AV4

SB_DQ[10]

BA4

SB_DQ[11]

AU3

SB_DQ[12]

AR3

SB_DQ[13]

AY2

SB_DQ[14]

BA3

SB_DQ[15]

BE9

SB_DQ[16]

BD9

SB_DQ[17]

BD13

SB_DQ[18]

BF12

SB_DQ[19]

BF8

SB_DQ[20]

BD10

SB_DQ[21]

BD14

SB_DQ[22]

BE13

SB_DQ[23]

BF16

SB_DQ[24]

BE17

SB_DQ[25]

BE18

SB_DQ[26]

BE21

SB_DQ[27]

BE14

SB_DQ[28]

BG14

SB_DQ[29]

BG18

SB_DQ[30]

BF19

SB_DQ[31]

BD50

SB_DQ[32]

BF48

SB_DQ[33]

BD53

SB_DQ[34]

BF52

SB_DQ[35]

BD49

SB_DQ[36]

BE49

SB_DQ[37]

BD54

SB_DQ[38]

BE53

SB_DQ[39]

BF56

SB_DQ[40]

BE57

SB_DQ[41]

BC59

SB_DQ[42]

AY60

SB_DQ[43]

BE54

SB_DQ[44]

BG54

SB_DQ[45]

BA58

SB_DQ[46]

AW59

SB_DQ[47]

AW58

SB_DQ[48]

AU58

SB_DQ[49]

AN61

SB_DQ[50]

AN59

SB_DQ[51]

AU59

SB_DQ[52]

AU61

SB_DQ[53]

AN58

SB_DQ[54]

AR58

AK58

AL58

AG58

AG59

AM60

AL59

AF61

AH60

BG39

BD42

AT22

AV43

BF40

BD45

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_CLK[0]

SB_CLK#[0]

SB_CKE[0]

SB_CLK[1]

SB_CLK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

BA34

AY34

AR22

BA36

BB36

BF27

BE41

BE47

AT43

BG47

AL3

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

T75T75

T78T78

M_B_DQSN0

M_B_DQSN1

M_B_DQSN2

M_B_DQSN3

M_B_DQSN4

M_B_DQSN5

M_B_DQSN6

M_B_DQSN7

M_B_DQSP0

M_B_DQSP1

M_B_DQSP2

M_B_DQSP3

M_B_DQSP4

M_B_DQSP5

M_B_DQSP6

M_B_DQSP7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

T46T46

T47T47

T80T80

M_B_CLKP0 [16,17]

M_B_CLKN0 [16,17]

M_B_CKE0 [16,17]

M_B_CS#0 [16,17]

M_B_ODT0 [16,17]

M_B_DQSN[7..0] [16]

M_B_DQSP[7..0] [16]

M_B_A[14..0] [16,17]

IC,SNB_2CBGA,1P0

IC,SNB_2CBGA,1P0

A A

5

M_A_DQ[0..7][15]

M_A_DQ[8..15][15]

M_A_DQ[16..23][15]

M_A_DQ[24..31][15]

M_A_DQ[32..39][15]

M_A_DQ[40..47][15]

M_A_DQ[48..55][15]

M_A_DQ[56..63][15]

4

M_B_DQ[0..7][16]

M_B_DQ[8..15][16]

M_B_DQ[16..23][16]

M_B_DQ[24..31][16]

3

M_B_DQ[32..39][16]

M_B_DQ[40..47][16]

M_B_DQ[48..55][16]

M_B_DQ[56..63][16]

IC,SNB_2CBGA,1P0

IC,SNB_2CBGA,1P0

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

2

Thursday, October 13, 2011

PROJECT :

Sandy Bridge 3/5

Sandy Bridge 3/5

Sandy Bridge 3/5

1

D13

D13

D13

5 41

5 41

5 41

1A

1A

1A

5

Sandy Bridge Processor (POWER)

U25F

U25F

+VCC_CORE

D D

C C

B B

A A

SNB:33A

C216 *10U/6.3V_6_NCC216 *10U/6.3V_6_NC

C211 10U/6.3V_6C211 10U/6.3V_6

C206 10U/6.3V_6C206 10U/6.3V_6

C196 10U/6.3V_6C196 10U/6.3V_6

C217 10U/6.3V_6C217 10U/6.3V_6

C190 10U/6.3V_6C190 10U/6.3V_6

C218 10U/6.3V_6C218 10U/6.3V_6

C180 10U/6.3V_6C180 10U/6.3V_6

C200 *10U/6.3V_6_NCC200 *10U/6.3V_6_NC

C201 10U/6.3V_6C201 10U/6.3V_6

C295 *10U/6.3V_6_NCC295 *10U/6.3V_6_NC

C184 1U/6.3V_4C184 1U/6.3V_4

C299 *1U/6.3V_4_NCC299 *1U/6.3V_4_NC

C204 1U/6.3V_4C204 1U/6.3V_4

C221 1U/6.3V_4C221 1U/6.3V_4

C173 *1U/6.3V_4_NCC173 *1U/6.3V_4_NC

C185 1U/6.3V_4C185 1U/6.3V_4

C205 1U/6.3V_4C205 1U/6.3V_4

C296 1U/6.3V_4C296 1U/6.3V_4

C203 1U/6.3V_4C203 1U/6.3V_4

C202 *1U/6.3V_4_NCC202 *1U/6.3V_4_NC

C172 1U/6.3V_4C172 1U/6.3V_4

C219 *1U/6.3V_4_NCC219 *1U/6.3V_4_NC

C174 1U/6.3V_4C174 1U/6.3V_4

C220 *1U/6.3V_4_NCC220 *1U/6.3V_4_NC

C186 1U/6.3V_4C186 1U/6.3V_4

A26

VCC[1]

A29

VCC[2]

A31

VCC[3]

A34

VCC[4]

A35

VCC[5]

A38

VCC[6]

A39

VCC[7]

A42

VCC[8]

C26

VCC[9]

C27

VCC[10]

C32

VCC[11]

C34

VCC[12]

C37

VCC[13]

C39

VCC[14]

C42

VCC[15]

D27

VCC[16]

D32

VCC[17]

D34

VCC[18]

D37

VCC[19]

D39

VCC[20]

D42

VCC[21]

E26

VCC[22]

E28

VCC[23]

E32

VCC[24]

E34

VCC[25]

E37

VCC[26]

E38

VCC[27]

F25

VCC[28]

F26

VCC[29]

F28

VCC[30]

F32

VCC[31]

F34

VCC[32]

F37

VCC[33]

F38

VCC[34]

F42

VCC[35]

G42

VCC[36]

H25

VCC[37]

H26

VCC[38]

H28

VCC[39]

H29

VCC[40]

H32

VCC[41]

H34

VCC[42]

H35

VCC[43]

H37

VCC[44]

H38

VCC[45]

H40

VCC[46]

J25

VCC[47]

J26

VCC[48]

J28

VCC[49]

J29

VCC[50]

J32

VCC[51]

J34

VCC[52]

J35

VCC[53]

J37

VCC[54]

J38

VCC[55]

J40

VCC[56]

J42

VCC[57]

K26

VCC[58]

K27

VCC[59]

K29

VCC[60]

K32

VCC[61]

K34

VCC[62]

K35

VCC[63]

K37

VCC[64]

K39

VCC[66]

K42

VCC[67]

L25

VCC[68]

L28

VCC[69]

L33

VCC[70]

L36

VCC[71]

L40

VCC[72]

N26

VCC[73]

N30

VCC[74]

N34

VCC[75]

N38

VCC[76]

IC,SNB_2CBGA,1P0

IC,SNB_2CBGA,1P0

5

CORE SUPPLY

CORE SUPPLY

PEG AND DDRSENSE LINES SVID QUIET RAILS

PEG AND DDRSENSE LINES SVID QUIET RAILS

POWER

POWER

VCCIO_SENSE

VSS_SENSE_VCCIO

4

3

CPU is i7 in schematic

8.5A 18A

AF46

VCCIO[1]

AG48

VCCIO[3]

AG50

VCCIO[4]

AG51

VCCIO[5]

AJ17

VCCIO[6]

AJ21

VCCIO[7]

AJ25

VCCIO[8]

AJ43

VCCIO[9]

AJ47

VCCIO[10]

AK50

VCCIO[11]

AK51

VCCIO[12]

AL14

VCCIO[13]

AL15

VCCIO[14]

AL16

VCCIO[15]

AL20

VCCIO[16]

AL22

VCCIO[17]

AL26

VCCIO[18]

AL45

VCCIO[19]

AL48

VCCIO[20]

AM16

VCCIO[21]

AM17

VCCIO[22]

AM21

VCCIO[23]

AM43

VCCIO[24]

AM47

VCCIO[25]

AN20

VCCIO[26]

AN42

VCCIO[27]

AN45

VCCIO[28]

AN48

VCCIO[29]

AA14

VCCIO[30]

AA15

VCCIO[31]

AB17

VCCIO[32]

AB20

VCCIO[33]

AC13

VCCIO[34]

AD16

VCCIO[35]

AD18

VCCIO[36]

AD21

VCCIO[37]

AE14

VCCIO[38]

AE15

VCCIO[39]

AF16

VCCIO[40]

AF18

VCCIO[41]

AF20

VCCIO[42]

AG15

VCCIO[43]

AG16

VCCIO[44]

AG17

VCCIO[45]

AG20

VCCIO[46]

AG21

VCCIO[47]

AJ14

VCCIO[48]

AJ15

VCCIO[49]

W16

VCCIO50

W17

VCCIO51

BC22

VCCIO_SEL

AM25

VCCPQE[1]

AN22

VCCPQE[2]

A44

VIDALERT#

B43

VIDSCLK

C44

VIDSOUT

F43

VCC_SENSE

G43

VSS_SENSE

AN16

AN17

+1.05V_VCCIO +1.05V_VCCIO

4

C167 10U/6.3V_6C167 10U/6.3V_6

C212 *10U/6.3V_6_NCC212 *10U/6.3V_6_NC

C166 10U/6.3V_6C166 10U/6.3V_6

C160 10U/6.3V_6C160 10U/6.3V_6

C229 10U/6.3V_6C229 10U/6.3V_6

C175 *10U/6.3V_6_NCC175 *10U/6.3V_6_NC

C162 10U/6.3V_6C162 10U/6.3V_6

C164 10U/6.3V_6C164 10U/6.3V_6

C157 10U/6.3V_6C157 10U/6.3V_6

C222 *10U/6.3V_6_NCC222 *10U/6.3V_6_NC

C245 *1U/6.3V_4_NCC245 *1U/6.3V_4_NC

C148 *1U/6.3V_4_NCC148 *1U/6.3V_4_NC

C147 *1U/6.3V_4_NCC147 *1U/6.3V_4_NC

C237 *1U/6.3V_4_NCC237 *1U/6.3V_4_NC

C232 *1U/6.3V_4_NCC232 *1U/6.3V_4_NC

C244 *1U/6.3V_4_NCC244 *1U/6.3V_4_NC

C224 1U/6.3V_4C224 1U/6.3V_4

C161 1U/6.3V_4C161 1U/6.3V_4

C168 1U/6.3V_4C168 1U/6.3V_4

C247 *1U/6.3V_4_NCC247 *1U/6.3V_4_NC

C231 1U/6.3V_4C231 1U/6.3V_4

C233 1U/6.3V_4C233 1U/6.3V_4

C243 *1U/6.3V_4_NCC243 *1U/6.3V_4_NC

C144 *1U/6.3V_4_NCC144 *1U/6.3V_4_NC

C240 1U/6.3V_4C240 1U/6.3V_4

C236 *1U/6.3V_4_NCC236 *1U/6.3V_4_NC

C230 1U/6.3V_4C230 1U/6.3V_4

C155 1U/6.3V_4C155 1U/6.3V_4

C149 *1U/6.3V_4_NCC149 *1U/6.3V_4_NC

C154 1U/6.3V_4C154 1U/6.3V_4

C146 *1U/6.3V_4_NCC146 *1U/6.3V_4_NC

C145 *1U/6.3V_4_NCC145 *1U/6.3V_4_NC

C246 1U/6.3V_4C246 1U/6.3V_4

H_CPU_SVIDALRT#

VR_SVID_CLK

VR_SVID_DATA

Follow check list of Intel

R134 100/F_4R134 100/F_4

R135 100/F_4R135 100/F_4

R127 *10/F_4_NCR127 *10/F_4_NC

R128 *10/F_4_NCR128 *10/F_4_NC

VR_SVID_CLK [37]

SVID DATA SVID ALERT

Place resistor R55 close to CPU

R173

R173

130/F_4

130/F_4

VR_SVID_DATA VR_SVID_ALERT#H_CPU_SVIDALRT#

+1.05V_VCCIO +VCC_GFX_CORE

+1.05V_VCCIO

+VCCSA_CORE

+VCC_CORE

+1.05V_VCCIO

VR_SVID_DATA [37]

VCC_AXG_SENSE[37]

VSS_AXG_SENSE[37]

VCCSENSE [37]

VSSSENSE [37]

VCCIO_SENSE [35]

VSSIO_SENSE [35]

C226 10U/6.3V_6C226 10U/6.3V_6

C288 10U/6.3V_6C288 10U/6.3V_6

C262 *10U/6.3V_6_NCC262 *10U/6.3V_6_NC

C286 10U/6.3V_6C286 10U/6.3V_6

C257 10U/6.3V_6C257 10U/6.3V_6

C284 *10U/6.3V_6_NCC284 *10U/6.3V_6_NC

C287 10U/6.3V_6C287 10U/6.3V_6

C258 10U/6.3V_6C258 10U/6.3V_6

C261 *10U/6.3V_6_NCC261 *10U/6.3V_6_NC

C285 *10U/6.3V_6_NCC285 *10U/6.3V_6_NC

C264 *10U/6.3V_6_NCC264 *10U/6.3V_6_NC

C239 10U/6.3V_6C239 10U/6.3V_6

C283 *10U/6.3V_6_NCC283 *10U/6.3V_6_NC

C260 *10U/6.3V_6_NCC260 *10U/6.3V_6_NC

C265 *10U/6.3V_6_NCC265 *10U/6.3V_6_NC

C263 *10U/6.3V_6_NCC263 *10U/6.3V_6_NC

C227 10U/6.3V_6C227 10U/6.3V_6

C238 10U/6.3V_6C238 10U/6.3V_6

C254 10U/6.3V_6C254 10U/6.3V_6

C225 10U/6.3V_6C225 10U/6.3V_6

C259 10U/6.3V_6C259 10U/6.3V_6

C252 10U/6.3V_6C252 10U/6.3V_6

C248 1U/6.3V_4C248 1U/6.3V_4

C250 1U/6.3V_4C250 1U/6.3V_4

C242 1U/6.3V_4C242 1U/6.3V_4

C249 1U/6.3V_4C249 1U/6.3V_4

C256 1U/6.3V_4C256 1U/6.3V_4

C235 1U/6.3V_4C235 1U/6.3V_4

Follow check list of Intel

+VCC_GFX_CORE

+1.8V_RUN

R14210/F_4 R14210/F_4

R14310/F_4 R14310/F_4

3A

C309 1U/6.3V_4C309 1U/6.3V_4

C310 1U/6.3V_4C310 1U/6.3V_4

R140 10/F_4R140 10/F_4

R141 10/F_4R141 10/F_4

SNB:6A

C170 10U/6.3V_6C170 10U/6.3V_6

C171 *10U/6.3V_6_NCC171 *10U/6.3V_6_NC

C156 *10U/6.3V_6_NCC156 *10U/6.3V_6_NC

C163 10U/6.3V_6C163 10U/6.3V_6

C152 10U/6.3V_6C152 10U/6.3V_6

C158 1U/6.3V_4C158 1U/6.3V_4

C159 1U/6.3V_4C159 1U/6.3V_4

C165 1U/6.3V_4C165 1U/6.3V_4

C151 *1U/6.3V_4_NCC151 *1U/6.3V_4_NC

C150 *1U/6.3V_4_NCC150 *1U/6.3V_4_NC

08/11

For CPU cost down plan

C151, C150

Place resistor R175 close to CPU

R176 43_4R176 43_4

3

2

Sandy Bridge Processor (GRAPHIC POWER)

U25G

U25G

AA46

VAXG[1]

AB47

VAXG[2]

AB50

VAXG[3]

AB51

VAXG[4]

AB52

VAXG[5]

AB53

VAXG[6]

AB55

VAXG[7]

AB56

VAXG[8]

AB58

VAXG[9]

AB59

VAXG[10]

AC61

VAXG[11]

AD47

VAXG[12]

AD48

VAXG[13]

AD50

VAXG[14]

AD51

VAXG[15]

AD52

VAXG[16]

AD53

VAXG[17]

AD55

VAXG[18]

AD56

VAXG[19]

AD58

VAXG[20]

AD59

VAXG[21]

AE46

VAXG[22]

N45

VAXG[23]

P47

VAXG[24]

P48

VAXG[25]

P50

VAXG[26]

P51

VAXG[27]

P52

VAXG[28]

P53

VAXG[29]

P55

VAXG[30]

P56

VAXG[31]

P61

VAXG[32]

T48

VAXG[33]

T58

VAXG[34]

T59

VAXG[35]

T61

VAXG[36]

U46

VAXG[37]

V47

VAXG[38]

V48

VAXG[39]

V50

VAXG[40]

V51

VAXG[41]

V52

VAXG[42]

V53

VAXG[43]

V55

VAXG[44]

V56

VAXG[45]

V58

VAXG[46]

V59

VAXG[47]

W50

VAXG[48]

W51

VAXG[49]

W52

VAXG[50]

W53

VAXG[51]

W55

VAXG[52]

W56

VAXG[53]

W61

VAXG[54]

Y48

VAXG[55]

Y61

VAXG[56]

F45

VAXG_SENSE

G45

VSSAXG_SENSE

BB3

VCCPLL[1]

BC1

VCCPLL[2]

BC4

VCCPLL[3]

L17

VCCSA[1]

L21

VCCSA[2]

N16

VCCSA[3]

N20

VCCSA[4]

N22

VCCSA[5]

P17

VCCSA[6]

P20

VCCSA[7]

R16

VCCSA[8]

R18

VCCSA[9]

R21

VCCSA[10]

U15

VCCSA[11]

V16

VCCSA[12]

V17

VCCSA[13]

V18

VCCSA[14]

V21

VCCSA[15]

W20

VCCSA[16]

IC,SNB_2CBGA,1P0

IC,SNB_2CBGA,1P0

+1.5V_SUS +1.5V_CPU

R175

R175

75_4

75_4

GRAPHICS

GRAPHICS

LINES

LINES

1.8V RAIL

1.8V RAIL

SA RAIL

SA RAIL

C179 0.1U/16V_4C179 0.1U/16V_4

C182 0.1U/16V_4C182 0.1U/16V_4

C189 0.1U/16V_4C189 0.1U/16V_4

C193 0.1U/16V_4C193 0.1U/16V_4

2

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

POWER

POWER

SENSE

SENSE

QUIET RAILS

QUIET RAILS

VSS_SENSE_VDDQ

SENSE LINES

SENSE LINES

VR_SVID_ALERT# [37]

VDDQ_SENSE

VCCSA_SENSE

VCCSA_VID[0]

VCCSA_VID[1]

CPU is i7 in schematic

10mil

+VDDR_REF_CPU

AY43

SM_VREF

AJ28

VDDQ[1]

AJ33

VDDQ[2]

AJ36

VDDQ[3]

AJ40

VDDQ[4]

AL30

VDDQ[5]

AL34

VDDQ[6]

AL38

VDDQ[7]

AL42

VDDQ[8]

AM33

VDDQ[9]

AM36

VDDQ[10]

AM40

VDDQ[11]

AN30

VDDQ[12]

AN34

VDDQ[13]

AN38

VDDQ[14]

AR26

VDDQ[15]

AR28

VDDQ[16]

AR30

VDDQ[17]

AR32

VDDQ[18]

AR34

VDDQ[19]

AR36

VDDQ[20]

AR40

VDDQ[21]

AV41

VDDQ[22]

AW26

VDDQ[23]

BA40

VDDQ[24]

BB28

VDDQ[25]

BG33

VDDQ[26]

AM28

VCCDQ[1]

AN26

VCCDQ[2]

BC43

BA43

U10

D48

D49

Sandy Bridge only:

VCCSA_VID[0] should be pull down

VCCSA_VID[1] should connect to SA VR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

SNB:5A

C223 10U/6.3V_6C223 10U/6.3V_6

C176 10U/6.3V_6C176 10U/6.3V_6

C191 10U/6.3V_6C191 10U/6.3V_6

C213 10U/6.3V_6C213 10U/6.3V_6

C181 10U/6.3V_6C181 10U/6.3V_6

C207 10U/6.3V_6C207 10U/6.3V_6

C197 10U/6.3V_6C197 10U/6.3V_6

C192 *10U/6.3V_6_NCC192 *10U/6.3V_6_NC

C209 1U/6.3V_4C209 1U/6.3V_4

C195 *1U/6.3V_4_NCC195 *1U/6.3V_4_NC

C187 1U/6.3V_4C187 1U/6.3V_4

C169 *1U/6.3V_4_NCC169 *1U/6.3V_4_NC

C210 *1U/6.3V_4_NCC210 *1U/6.3V_4_NC

C228 *1U/6.3V_4_NCC228 *1U/6.3V_4_NC

C214 *1U/6.3V_4_NCC214 *1U/6.3V_4_NC

C177 *1U/6.3V_4_NCC177 *1U/6.3V_4_NC

C194 1U/6.3V_4C194 1U/6.3V_4

C198 *1U/6.3V_4_NCC198 *1U/6.3V_4_NC

C178 *1U/6.3V_4_NCC178 *1U/6.3V_4_NC

+1.5V_SUS +1.5V_CPU

8

7

6

5

PS_S3CNTRL_S[8]

C241

C241

*4700P/25V/X7R_4_NC

*4700P/25V/X7R_4_NC

C188 1U/6.3V_4C188 1U/6.3V_4

R126 100/F_4R126 100/F_4

VCCSA_VID0

1 2

VCCSA_VID1

Follow check list of Intel

Sandy Bridge 4/5

Sandy Bridge 4/5

Sandy Bridge 4/5

Thursday, October 13, 2011

Thursday, October 13, 2011

Thursday, October 13, 2011

1

+VDDR_REF_CPU

+1.5V_CPU

5A

Q26

Q26

AON7410

AON7410

3

2

1

4

check with power Andy

+1.5V_CPU

+VCCSA_CORE

R13910K_4R13910K_4

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

PROJECT :

+VDDR_REF_CPU

1K/F_4

1K/F_4

1

VCCSA_SENSE [36]

VCCSA_VID1 [36]

R137

R137

D13

D13

D13

6 41

6 41

6 41

+1.5V_CPU

R138

R138

1K/F_4

1K/F_4

C234

C234

0.1U/16V_4

0.1U/16V_4

1A

1A

1A

5

4

3

2

1

Sandy Bridge Processor (GND)

CPU is i7 in schematic CPU is i7 in schematic

U25H

U25H

A13

VSS[1]

D D

C C

B B

A A

A17

VSS[2]

A21

VSS[3]

A25

VSS[4]

A28

VSS[5]

A33

VSS[6]

A37

VSS[7]

A40

VSS[8]

A45

VSS[9]

A49

VSS[10]

A53

VSS[11]

A9

VSS[12]

AA1

VSS[13]

AA13

VSS[14]

AA50

VSS[15]

AA51

VSS[16]

AA52

VSS[17]

AA53

VSS[18]

AA55

VSS[19]

AA56

VSS[20]

AA8

VSS[21]

AB16

VSS[22]

AB18

VSS[23]

AB21

VSS[24]

AB48

VSS[25]

AB61

VSS[26]

AC10

VSS[27]

AC14

VSS[28]

AC46

VSS[29]

AC6

VSS[30]

AD17

VSS[31]

AD20

VSS[32]

AD4

VSS[33]

AD61

VSS[34]

AE13

VSS[35]

AE8

VSS[36]

AF1

VSS[37]

AF17

VSS[38]

AF21

VSS[39]

AF47

VSS[40]

AF48

VSS[41]

AF50

VSS[42]

AF51

VSS[43]

AF52

VSS[44]

AF53

VSS[45]

AF55

VSS[46]

AF56

VSS[47]

AF58

VSS[48]

AF59

VSS[49]

AG10

VSS[50]

AG14

VSS[51]

AG18

VSS[52]

AG47

VSS[53]

AG52

VSS[54]

AG61

VSS[55]

AG7

VSS[56]

AH4

VSS[57]

AH58

VSS[58]

AJ13

VSS[59]

AJ16

VSS[60]

AJ20

VSS[61]

AJ22

VSS[62]

AJ26

VSS[63]

AJ30

VSS[64]

AJ34

VSS[65]

AJ38

VSS[66]

AJ42

VSS[67]

AJ45

VSS[68]

AJ48

VSS[69]

AJ7

VSS[70]

AK1

VSS[71]

AK52

VSS[72]

AL10

VSS[73]

AL13

VSS[74]

AL17

VSS[75]

AL21

VSS[76]

AL25

VSS[77]

AL28

VSS[78]

AL33

VSS[79]

AL36

VSS[80]

AL40

VSS[81]

AL43

VSS[82]

AL47

VSS[83]

AL61

VSS[84]

AM13

VSS[85]

AM20

VSS[86]

AM22

VSS[87]

AM26

VSS[88]

AM30

VSS[89]

AM34

VSS[90]

IC,SNB_2CBGA,1P0

IC,SNB_2CBGA,1P0

VSS

VSS

5

VSS[91]

VSS[92]

VSS[93]

VSS[94]

VSS[95]

VSS[96]

VSS[97]

VSS[98]

VSS[99]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

VSS[163]

VSS[164]

VSS[165]

VSS[166]

VSS[167]

VSS[168]

VSS[169]

VSS[170]

VSS[171]

VSS[172]

VSS[173]

VSS[174]

VSS[175]

VSS[176]

VSS[177]

VSS[178]

VSS[179]

VSS[180]

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP10

AP51

AP55

AP7

AR13

AR17

AR21

AR41

AR48

AR61

AR7

AT14

AT19

AT36

AT4

AT45

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW13

AW43

AW61

AW7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

U25I

U25I

BG17

VSS[181]

BG21

VSS[182]

BG24

VSS[183]

BG28

VSS[184]

BG37

VSS[185]

BG41

VSS[186]

BG45

VSS[187]

BG49

VSS[188]

BG53

VSS[189]

BG9

VSS[190]

C29

VSS[191]

C35

VSS[192]

C40

VSS[193]

D10

VSS[194]

D14

VSS[195]

D18

VSS[196]

D22

VSS[197]

D26

VSS[198]

D29

VSS[199]

D35

VSS[200]

D4

VSS[201]

D40

VSS[202]

D43

VSS[203]

D46

VSS[204]

D50

VSS[205]

D54

VSS[206]

D58

VSS[207]

D6

VSS[208]

E25

VSS[209]

E29

VSS[210]

E3

VSS[211]

E35

VSS[212]

E40

VSS[213]

F13

VSS[214]

F15

VSS[215]

F19

VSS[216]

F29

VSS[217]

F35

VSS[218]

F40

VSS[219]

F55

VSS[220]

G48

VSS[221]

G51

VSS[222]

G6

VSS[223]

G61

VSS[224]

H10

VSS[225]

H14

VSS[226]

H17

VSS[227]

H21

VSS[228]

H4

VSS[229]

H53

VSS[230]

H58

VSS[231]

J1

VSS[232]

J49

VSS[233]

J55

VSS[234]

K11

VSS[235]

K21

VSS[236]

K51

VSS[237]

K8

VSS[238]

L16

VSS[239]

L20

VSS[240]

L22

VSS[241]

L26

VSS[242]

L30

VSS[243]

L34

VSS[244]

L38

VSS[245]

L43

VSS[246]

L48

VSS[247]

L61

VSS[248]

M11

VSS[249]

M15

VSS[250]

IC,SNB_2CBGA,1P0

IC,SNB_2CBGA,1P0

VSS

VSS

Processor Strapping

CFG2

(PCI-E Static x16 Lane Reversal)

CFG3

(PCI-E Static x4 Lane Reversal)

CFG4

(DP Presence Strap)

4

M4

VSS[251]

M58

VSS[252]

M6

VSS[253]

N1

VSS[254]

N17

VSS[255]

N21

VSS[256]

N25

VSS[257]

N28

VSS[258]

N33

VSS[259]

N36

VSS[260]

N40

VSS[261]

N43

VSS[262]

N47

VSS[263]

N48

VSS[264]

N51

VSS[265]

N52

VSS[266]

N56

VSS[267]

N61

VSS[268]

P14

VSS[269]

P16

VSS[270]

P18

VSS[271]

P21

VSS[272]

P58

VSS[273]

P59

VSS[274]

P9

VSS[275]

R17

VSS[276]

R20

VSS[277]

R4

VSS[278]

R46

VSS[279]

T1

VSS[280]

T47

VSS[281]

T50

VSS[282]

T51

VSS[283]

T52

VSS[284]

T53

VSS[285]

T55

VSS[286]

T56

VSS[287]

U13

VSS[288]

U8

VSS[289]

V20

VSS[290]

V61

VSS[291]

W13

VSS[292]

W15

VSS[293]

W18

VSS[294]

W21

VSS[295]

W46

VSS[296]

W8

VSS[297]

Y4

VSS[298]

Y47

VSS[299]

Y58

VSS[300]

Y59

VSS[301]

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

VSS_NCTF_10

NCTF

NCTF

VSS_NCTF_11

VSS_NCTF_12

VSS_NCTF_13

VSS_NCTF_14

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

VSS_NCTF_9

1 0

Normal Operation Lane Reversed

Normal Operation Lane Reversed

Disable; No physical DP attached to eDP

3

Enable; An ext DP device is connected to eDP

Sandy Bridge Processor (RESERVED, CFG)

CPU is i7 in schematic

U25E

U25E

B50

CFG[0]

C51

T72T72

T74T74

T76T76

T73T73

T71T71

CFG2

CFG3

CFG4CFG4

CFG5

CFG6

T55T55

T52T52

T54T54

T53T53

CFG[1]

B54

CFG[2]

D53

CFG[3]

A51

CFG[4]

C53

CFG[5]

C55

CFG[6]

H49

CFG[7]

A55

CFG[8]

H51

CFG[9]

K49

CFG[10]

K53

CFG[11]

F53

CFG[12]

G53

CFG[13]

L51

CFG[14]

F51

CFG[15]

D52

CFG[16]

L53

CFG[17]

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

IC,SNB_2CBGA,1P0

IC,SNB_2CBGA,1P0

RESERVED

RESERVED

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

PGB straping pin unused for UMA only

CFG[6:5] (PCIE Port Bifurcation Straps)

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2 disabled

01: Reserved - (Device 1 function 1 disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

2

Thursday, October 13, 2011

PROJECT :

Sandy Bridge 5/5

Sandy Bridge 5/5

Sandy Bridge 5/5

1

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

D13

D13

D13

7 41

7 41

7 41

BE7

BG7

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

1A

1A

1A

5

DMI_RXN0[3]

DMI_RXN1[3]

DMI_RXN2[3]

DMI_RXN3[3]

DMI_RXP0[3]

+1.05V_PCH

DMI_RXP1[3]

DMI_RXP2[3]

DMI_RXP3[3]

DMI_TXN0[3]

DMI_TXN1[3]

DMI_TXN2[3]

DMI_TXN3[3]

DMI_TXP0[3]

DMI_TXP1[3]

DMI_TXP2[3]

DMI_TXP3[3]

R203 49.9/F_4R203 49.9/F_4

R202 750/F_4R202 750/F_4

T90T90

W/O support

DMI_COMP

DMI2RBIAS

ME_SUS_PWR_ACK

XDP_DBRST#

SYS_PWROK

RSMRST#

ME_SUS_PWR_ACK

AC_PRESENT

PM_BATLOW#

PM_RI#

D D

C C

B B

XDP_DBRST#[4]

EC_PWROK[4,22]

HWPG[22,30]

PM_DRAM_PWRGD[4]

RSMRST#[22]

ME_SUS_PWR_ACK[22]

SIO_PWRBTN#[22]

AC_PRESENT[22]

4

3

Cougar Point (DMI,FDI,PM)

U31C

U31C

BL21

DMI0RXN

BL23

DMI1RXN

BJ19

DMI2RXN

BL17

DMI3RXN

BJ21

DMI0RXP

BJ23

DMI1RXP

BL19

DMI2RXP

BJ17

DMI3RXP

BD22

DMI0TXN

BB22

DMI1TXN

BB19

DMI2TXN

BB17

DMI3TXN

BF22

DMI0TXP

AY22

DMI1TXP

AY19

DMI2TXP

AY17

DMI3TXP

BF19

DMI_ZCOMP

BD19

DMI_IRCOMP

BK20

DMI2RBIAS

F15

SUSACK#

L1

SYS_RESET#

M10

SYS_PWROK

M22

PWROK

G3

APWROK

B12

DRAMPWROK

B20

RSMRST#

C13

SUSWARN#/SUSPWRDNACK/GPIO30

K19

PWRBTN#

H19

H10

F12

CougarPoint-H_SFF_Rev_1_0

CougarPoint-H_SFF_Rev_1_0

DSW

ACPRESENT / GPIO31

BATLOW# / GPIO72

RI#

+3V_S5

+3V_S5

+3V_S5

DSW

+3V_S5

+3V_S5

DMI

FDI

DMI

FDI

CLKRUN# / GPIO32

+3V

SUS_STAT# / GPIO61

SUSCLK / GPIO62

SLP_S5# / GPIO63

System Power Management

System Power Management

+3V_S5

SLP_LAN# / GPIO29

FDI_FSYNC0

FDI_FSYNC1

FDI_LSYNC0

FDI_LSYNC1

DSWVRMEN

FDI_RXN0

FDI_RXN1

FDI_RXN2

FDI_RXN3

FDI_RXN4

FDI_RXN5

FDI_RXN6

FDI_RXN7

FDI_RXP0

FDI_RXP1

FDI_RXP2

FDI_RXP3

FDI_RXP4

FDI_RXP5

FDI_RXP6

FDI_RXP7

FDI_INT

DPWROK

WAKE#

SLP_S4#

SLP_S3#

SLP_A#

SLP_SUS#

PMSYNCH

BL13

BJ15

BD12

BJ11

AY15

AY12

BJ9

BF10

BJ13

BL15

BF12

BL11

BB15

BB12

BL9

BD10

BB10

BH12

BK8

BK12

BH8

DSWVRMEN

F22

RSMRST#

A21

PCIE_WAKE#

D8

CLKRUN#

T2

G6

SUSCLK

D3

F6

SLP_S4#

K10

D4

C7

W/O support iAMT

A15

W/O support Deep Sx

BB8

SIO_SLP_LAN#

A7

FDI_TXN0 [3]

FDI_TXN1 [3]

FDI_TXN2 [3]

FDI_TXN3 [3]

FDI_TXN4 [3]

FDI_TXN5 [3]

FDI_TXN6 [3]

FDI_TXN7 [3]

FDI_TXP0 [3]

FDI_TXP1 [3]

FDI_TXP2 [3]

FDI_TXP3 [3]

FDI_TXP4 [3]

FDI_TXP5 [3]

FDI_TXP6 [3]

FDI_TXP7 [3]

FDI_INT [3]

FDI_FSYNC0 [3]

FDI_FSYNC1 [3]

FDI_LSYNC0 [3]

FDI_LSYNC1 [3]

PCIE_WAKE# [22]

CLKRUN# [22]

T19T19

SIO_SLP_S5# [22,34]

SLP_S4# [20,22,34]

SIO_SLP_S3# [22,34]

H_PM_SYNC [4]

T13T13

W/O support iAMT

W/O support

2

1

PCH Pull-high/low(CLG)

+3.3V_SUS

RN1

PM_BATLOW#

PCIE_WAKE#

PM_RI#

SIO_SLP_LAN#

ME_SUS_PWR_ACK

AC_PRESENT

CLKRUN#

XDP_DBRST#

RSMRST#

SYS_PWROK

DSWVRMEN

On Die DSW VR Enable

High = Enable (Default)

Low = Disable

RN1

1

2

3

4

5

6

7

8

10K

10K

RP10

RP10

1

3

10K

10K

R194 10K_4R194 10K_4

R213 1K_4R213 1K_4

R225 10K_4R225 10K_4

R214 100K_4R214 100K_4

+RTC_CELL

R217

R217

330K_4

330K_4

2

4

+3.3V_RUN

S3 Power reduce S3 Power reduce

A A

SIO_SLP_S3#

2

R74

R74

*10K_4_NC

*10K_4_NC

+5V_ALW

12

PS_S3CNTRL

31

R75

R75

10K_4

10K_4

Q19

Q19

PMF780SN

PMF780SN

5

PS_S3CNTRL [17]

PS_S3CNTRL

Q20

Q20

PMF780SN

PMF780SN

4

+15V_ALW

31

2

Copy From GM6

R73

R73

100K_4

100K_4

C72

C72

*0.01U/25V_4_NC

*0.01U/25V_4_NC

PS_S3CNTRL_S [6]

System PWR_OK(CLG)

SYS_PWROK[4]

3

SYS_PWROK

U7

U7

4

TC7SH08FU

TC7SH08FU

+3.3V_SUS

3 5

C71

C71

*0.1U/10V/X7R_4_NC

*0.1U/10V/X7R_4_NC

2

EC_PWROK

1

R66

R66

100K_4

100K_4

2

IMVP_PWRGD [22,28,37]

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

Thursday, October 13, 2011

PROJECT :

Cougar Point 1/7

Cougar Point 1/7

Cougar Point 1/7

1

D13

D13

D13

8 41

8 41

8 41

1A

1A

1A

5

Cougar Point (LVDS,DDI)

U31D

U31D

PANEL_BKEN[22]

ENVDD[19]

LCD_PW M[19]

LCD_DDCCLK[19]

D D

LCD_DDCDAT[19]

T36T36

R118 2.37K/F_4R118 2.37K/F_4

T37T37

T35T35

INT_TXLCLKOUTN[19]

INT_TXLCLKOUTP[19]

INT_TXLOUTN0[19]

INT_TXLOUTN1[19]

INT_TXLOUTN2[19]

INT_TXLOUTP0[19]

INT_TXLOUTP1[19]

INT_TXLOUTP2[19]

PANEL_BKEN

ENVDD

LCD_DDCCLK

LCD_DDCDAT

L_CTRL_CLK

L_CTRL_DATA

LVDS_IBG

LVDS_VBG

LCD

C C

T25T25

T29T29

T31T31

T84T84

T86T86

T87T87

T85T85

DAC_IREF

R102

R102

1K_4

B B

A A

INT_DP_HPD_R[18]

1K_4

If CRT hasn't used, it can changed to 5%

Follow R05 QT stage design

*365K/F_NC

*365K/F_NC

5

R195

R195

R129

R129

150K

150K

M44

L_BKLTEN

M42

L_VDD_EN

L49

L_BKLTCTL

L51

L_DDC_CLK

K46

L_DDC_DATA

R42

L_CTRL_CLK

M40

L_CTRL_DATA

AH42

LVD_IBG

AH40

LVD_VBG

AG51

LVD_VREFH

AG49

LVD_VREFL

AK44

LVDSA_CLK#

AK46

LVDSA_CLK

AR46

LVDSA_DATA#0

AN49

LVDSA_DATA#1

AN44

LVDSA_DATA#2

AK40

LVDSA_DATA#3

AR44

LVDSA_DATA0

AN51

LVDSA_DATA1

AN46

LVDSA_DATA2

AK42

LVDSA_DATA3

AH46

LVDSB_CLK#

AH44

LVDSB_CLK

AM50

LVDSB_DATA#0

AL49

LVDSB_DATA#1

AJ51

LVDSB_DATA#2

AH50

LVDSB_DATA#3

AM48

LVDSB_DATA0

AL51

LVDSB_DATA1

AJ49

LVDSB_DATA2

AH48

LVDSB_DATA3

M46

CRT_BLUE

R46

CRT_GREEN

U46

CRT_RED

R49

CRT_DDC_CLK

N49

CRT_DDC_DATA

M50

CRT_HSYNC

N51

CRT_VSYNC

R51

DAC_IREF

T48

CRT_IRTN

CougarPoint-H_SFF_Rev_1_0

CougarPoint-H_SFF_Rev_1_0

+5V_RUN

MMST3904-7-F

MMST3904-7-F

12

2

1 3

R191

R191

10K

10K

Q27

Q27

INT_DP_HPD

SDVO_TVCLKINN

SDVO_TVCLKINP

SDVO_CTRLCLK

SDVO_CTRLDATA

LVDS

LVDS

DDPC_CTRLCLK

DDPC_CTRLDATA

Digital Display Interface

Digital Display Interface

DDPD_CTRLCLK

DDPD_CTRLDATA

CRT

CRT

SDVO_STALLN

SDVO_STALLP

SDVO_INTN

SDVO_INTP

DDPB_AUXN

DDPB_AUXP

DDPB_HPD

DDPB_0N

DDPB_0P

DDPB_1N

DDPB_1P

DDPB_2N

DDPB_2P

DDPB_3N

DDPB_3P

DDPC_AUXN

DDPC_AUXP

DDPC_HPD

DDPC_0N

DDPC_0P

DDPC_1N

DDPC_1P

DDPC_2N

DDPC_2P

DDPC_3N

DDPC_3P

DDPD_AUXN

DDPD_AUXP

DDPD_HPD

DDPD_0N

DDPD_0P

DDPD_1N

DDPD_1P

DDPD_2N

DDPD_2P

DDPD_3N

DDPD_3P

LCD_DDCDAT

LCD_DDCCLK

INT_DP_SCL

INT_DP_SDA

L_CTRL_CLK

L_CTRL_DATA

ENVDD

4

AU40

AU42

AR51

AR49

AT50

AT48

W42

R44

AW51

AW49

AY42

AY48

AY50

AY44

AY46

BB44

BB46

BA49

BA51

INT_DP_SCL

T50

INT_DP_SDA

U44

AU51

AU49

INT_DP_HPD

BE46

BC49

BC51

BD48

BD50

BF46

BF45

BE49

BE51

M48

U42

AU46

AU44

BK44

BG51

BG49

BF42

BD42

BJ47

BL47

BL45

BJ45

RP5 2.2KX2RP5 2.2KX2

2

1

4

3

RP7 2.2KX2RP7 2.2KX2

2

1

4

3

RP6 2.2KX2RP6 2.2KX2

4

1

2

3

R78 *100K_4_NCR78 *100K_4_NC

4

12

INT_DP_SCL [18]

INT_DP_SDA [18]

INT_DP_AUXN_C [18]

INT_DP_AUXP_C [18]

INT_DP_TXN0_C [18]

INT_DP_TXP0_C [18]

INT_DP_TXN1_C [18]

INT_DP_TXP1_C [18]

INT_DP_TXN2_C [18]

INT_DP_TXP2_C [18]

INT_DP_TXN3_C [18]

INT_DP_TXP3_C [18]

+3.3V_RUN

3

Mini DP

3

Cougar Point (GND)

U31I

U31I

BA25

VSS[159]

BA27

VSS[160]

BA29

VSS[161]

BA31

VSS[162]

BA34

VSS[163]

BA36

VSS[164]

BA39

VSS[165]

BA41

VSS[166]

BA43

VSS[167]

BA45

VSS[168]

BA7

VSS[169]

BA9

VSS[170]

BB4

VSS[171]

F2

VSS[172]

BB48

VSS[173]

BB50

VSS[174]

BC11

VSS[175]

BC13

VSS[176]

BC16

VSS[177]

BC18

VSS[178]

BC21

VSS[179]

BC23

VSS[180]

BC25

VSS[181]

BC27

VSS[182]

BC29

VSS[183]

BC31

VSS[184]

BC34

VSS[185]

BC36

VSS[186]

BC39

VSS[187]

BC41

VSS[188]

BC43

VSS[189]

BC45

VSS[190]

BE11

VSS[191]

BE13

VSS[192]

BE16

VSS[193]

BE21

VSS[194]

BE23

VSS[195]

BE27

VSS[196]

BE29

VSS[197]

BE31

VSS[198]

BE34

VSS[199]

BE36

VSS[200]

BE39

VSS[201]

BE41

VSS[202]

BE43

VSS[203]

BE45

VSS[204]

BE7

VSS[205]

BE9

VSS[206]

BE18

VSS[207]

BF2

VSS[208]

BF4

VSS[209]

BF48

VSS[210]

BF50

VSS[211]

BH10

VSS[212]

BH14

VSS[213]

BH26

VSS[214]

BH32

VSS[215]

BH34

VSS[216]

BH38

VSS[217]

BH42

VSS[218]

BH44

VSS[219]

BH46

VSS[220]

G21

VSS[221]

BH48

VSS[222]

BH6

VSS[223]

BK10

VSS[224]

BK14

VSS[225]

BK18

VSS[226]

BK22

VSS[227]

BK26

VSS[228]

D14

VSS[229]

BK32

VSS[230]

BK34

VSS[231]

BK38

VSS[232]

BK42

VSS[233]

BK46

VSS[234]

D10

VSS[235]

D18

VSS[236]

D22

VSS[237]

D26

VSS[238]

D30

VSS[239]

D34

VSS[240]

D38

VSS[241]

D42

VSS[242]

D46

VSS[243]

F48

VSS[244]

F50

VSS[245]

G11

VSS[246]

G13

VSS[247]

G16

VSS[248]

G18

VSS[249]

G23

VSS[250]

G27

VSS[251]

G29

VSS[252]

G31

VSS[253]

G34

VSS[254]

G36

VSS[255]

G39

VSS[256]

G41

VSS[257]

D6

VSS[258]

G43

VSS[259]

G9

VSS[260]

J11

VSS[261]

J13

VSS[262]

J16

VSS[263]

CougarPoint-H_SFF_Rev_1_0

CougarPoint-H_SFF_Rev_1_0

2

VSS[264]

VSS[265]

VSS[266]

VSS[267]

VSS[268]

VSS[269]

VSS[270]

VSS[271]

VSS[272]

VSS[273]

VSS[274]

VSS[275]

VSS[276]

VSS[277]

VSS[278]

VSS[279]

VSS[280]

VSS[281]

VSS[282]

VSS[283]

VSS[284]

VSS[285]

VSS[286]

VSS[287]

VSS[288]

VSS[289]

VSS[290]

VSS[291]

VSS[292]

VSS[293]

VSS[294]

VSS[295]

VSS[296]

VSS[297]

VSS[298]

VSS[299]

VSS[300]

VSS[301]

VSS[302]

VSS[303]

VSS[304]

VSS[305]

VSS[306]

VSS[307]

VSS[308]

VSS[309]

VSS[310]

VSS[311]

VSS[312]

VSS[313]

VSS[314]

VSS[315]

VSS[316]

VSS[317]

VSS[318]

VSS[319]

VSS[320]

VSS[321]

VSS[322]

VSS[323]

VSS[324]

VSS[325]

VSS[328]

VSS[329]

VSS[330]

VSS[331]

VSS[333]

VSS[334]

VSS[335]

VSS[337]

VSS[338]

VSS[340]

VSS[342]

VSS[343]

VSS[344]

VSS[345]

VSS[346]

VSS[353]

VSS[354]

VSS[355]

VSS[356]

VSS[357]

VSS[358]

VSS[359]

VSS[360]

VSS[361]

VSS[362]

VSS[363]

VSS[364]

VSS[365]

VSS[366]

VSS[367]

VSS[368]

VSS[369]

VSS[370]

VSS[371]

VSS[372]

VSS[373]

VSS[374]

VSS[347]

VSS[348]

VSS[349]

VSS[350]

VSS[351]

VSS[352]

2

J18

J21

J23

J25

J27

J29

J31

J34

J36

L25

J41

J45

J7

J9

K2

K4

K48

K50

L11

L13

L16

L18

L29

L21

L23

L27

L9

L31

L34

L36

L39

L41

L43

L45

L7

N13

N21

R37

N23

N29

N31

N34

N39

N41

N43

N45

N7

N9

P2

P4

P48

P50

R17

R21

R31

T11

T13

T41

T43

T45

T7

T9

BH28

N25

AF8

AF35

BB2

BE25

BH30

F4

G25

N11

BH18

BH22

BK30

AR17

J39

U31

U49

V11

V15

V17

V2

V27

V29

V33

V35

V4

V41

V43

V45

V48

V7

V9

Y15

Y17

Y33

Y35

Y37

AR8

AR6

BF15

BD15

BF24

BD24

1

U31H

U31H

G7

VSS[0]

AA11

VSS[1]

AA39

VSS[2]

AA41

VSS[3]

AA43

VSS[4]

AA45

VSS[5]

AA7

VSS[6]

AA9

VSS[7]

AB17

VSS[8]

AB2

VSS[9]

AB25

VSS[10]

AB33

VSS[11]

AB35

VSS[12]

AB37

VSS[13]

AB4

VSS[14]

AB48

VSS[15]

AB50

VSS[16]

AC11

VSS[17]

AC17

VSS[18]

AC25

VSS[19]

AC41

VSS[20]

AC43

VSS[21]

AC45

VSS[22]

AC7

VSS[23]

AE13

VSS[24]

AE15

VSS[25]

AE17

VSS[26]

AE25

VSS[27]

AE35

VSS[28]

AE41

VSS[29]

AE43

VSS[30]

AE45

VSS[31]

AE7

VSS[32]

AE9

VSS[33]

AF19

VSS[34]

AF2

VSS[35]

AF25

VSS[36]

AF27

VSS[37]

AF29

VSS[38]

AF31

VSS[39]

AF4

VSS[40]

AF48

VSS[41]

AF50

VSS[42]

AG11

VSS[43]

AG17

VSS[44]

AC9

VSS[45]

AE11

VSS[46]

AG19

VSS[47]

AG29

VSS[48]

AG31

VSS[49]

AG35

VSS[50]

AG41

VSS[51]

AG43

VSS[52]

AG45

VSS[53]

AG7

VSS[54]

AG9

VSS[55]

AH2

VSS[56]

AJ11

VSS[57]

AJ19

VSS[58]

AJ33

VSS[59]

AJ35

VSS[60]

AJ39

VSS[61]

AJ41

VSS[62]

AJ43

VSS[63]

AJ45

VSS[64]

AJ7

VSS[65]

AJ9

VSS[66]

AK17

VSS[67]

AK19

VSS[68]

AK2

VSS[69]

AK23

VSS[70]

AK25

VSS[71]

AK27

VSS[72]

AK35

VSS[73]

AK37

VSS[74]

AK4

VSS[75]

AK48

VSS[76]

AK50

VSS[77]

AL11

VSS[78]

AL39

VSS[79]

CougarPoint-H_SFF_Rev_1_0

CougarPoint-H_SFF_Rev_1_0

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

PROJECT :

PROJECT :

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

Thursday, October 13, 2011

Date: Sheet of

Thursday, October 13, 2011

PROJECT :

Cougar Point 2/7

Cougar Point 2/7

Cougar Point 2/7

D13

D13

D13

1

AL41

VSS[80]

AL43

VSS[81]

AL45

VSS[82]

AL7

VSS[83]

AL9

VSS[84]

AM15

VSS[85]

AM19

VSS[86]

AM25

VSS[87]

AM29

VSS[88]

AM31

VSS[89]

AM37

VSS[90]

AP11

VSS[91]

AP17

VSS[92]

AP2

VSS[93]

AP21

VSS[94]

AP23

VSS[95]

AP25

VSS[96]

AP29

VSS[97]

AP31

VSS[98]

AP33

VSS[99]

AP35

VSS[100]

AP37

VSS[101]

AP4

VSS[102]

AP41

VSS[103]

AP43

VSS[104]

AP45

VSS[105]

AP48

VSS[106]

AP50

VSS[107]

AP7

VSS[108]

AP9

VSS[109]

AR19

VSS[110]

AR21

VSS[111]

AR31

VSS[112]

AR35

VSS[113]

AR37

VSS[114]

AT11

VSS[115]

AT39

VSS[116]

AT41

VSS[117]

AT43

VSS[118]

AT45

VSS[119]

AT7

VSS[120]

AT9

VSS[121]

AU17

VSS[122]

AU37

VSS[123]

AV2

VSS[124]

AV4

VSS[125]

AV48

VSS[126]

AV50

VSS[127]

AW11

VSS[128]

AW13

VSS[129]

AW23

VSS[130]

AW25

VSS[131]

AW27

VSS[132]

AW29

VSS[133]

AW36

VSS[134]

AW39

VSS[135]

AW43

VSS[136]

AW45

VSS[137]

AW7

VSS[138]

AW9

VSS[139]

AY10

VSS[140]

B10

VSS[141]

B14

VSS[142]

B18

VSS[143]

B22

VSS[144]

B26

VSS[145]

B30

VSS[146]

B34

VSS[147]

B38

VSS[148]

B42

VSS[149]

B46

VSS[150]

B6

VSS[151]

BA11

VSS[152]

BA13

VSS[153]

BA16

VSS[154]

AW41

VSS[155]

BA18

VSS[156]

BA21

VSS[157]

BA23

VSS[158]

9 41

9 41

9 41

1A

1A

1A

5

4

3

2

1

2

4

+3.3V_SUS

+3.3V_SUS

RTC_RST#

SRTC_RST#

C320

C320

1U/6.3V_4

1U/6.3V_4

+3.3V_RUN

C321 18P/50V/_4C321 18P/50V/_4

D D

ACZ_SPKR

EC17

EC17

*100P_NC

*100P_NC

C C

B B

C319 18P/50V/_4C319 18P/50V/_4

PCH_AZ_CODEC_BITCLK[29]

PCH_AZ_CODEC_RST#[22,29]

PCH_AZ_CODEC_SDIN0[29]

PCH_AZ_CODEC_SDOUT[29]

14

23

Y3

Y3

32.768KHZ

32.768KHZ

+RTC_CELL

ACZ_SPKR[29]

PCH_MELOCK[22]

10/04: NO.7

PCH_SPI_CLK[25]

PCH_SPI_CS0#[25]

PCH_SPI_SI[25]

PCH_SPI_SO[25]

R219

R219

10M_4

10M_4

R90 1M_4R90 1M_4

8/1 NO. 16

R223 47_4R223 47_4

C78447P/50V/NPO_4 C78447P/50V/NPO_4

R216 33_4R216 33_4

R227 1K_4R227 1K_4

R222 33_4R222 33_4

T26T26

T27T27

T33T33

T28T28

RTC_X1

RTC_X2

RTC_RST#

SRTC_RST#

SM_INTRUDER#

PCH_INTVRMEN

C317 22P/50V_4C317 22P/50V_4

R210 *SJ0402_NCR210 *SJ0402_NC

Cougar Point (HDA,JTAG,SATA)

U31A

U31A

A19

ACZ_BITCLK_R

ACZ_SYNC_R

ACZ_SPKR

ACZ_RST#_R

ACZ_SDOUT

PCH_JTAG_TCK

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_SPI_CLK_R

RTCX1

C19

RTCX2

F19

RTCRST#

A23

SRTCRST#

K22

INTRUDER#

C21

INTVRMEN

H35

HDA_BCLK

H37

HDA_SYNC

N1

SPKR

F35

HDA_RST#

D36

HDA_SDIN0

B36

HDA_SDIN1

C35

HDA_SDIN2

A35

HDA_SDIN3

K37

HDA_SDO

K35

HDA_DOCK_EN# / GPIO33

M35

HDA_DOCK_RST# / GPIO13

M17

JTAG_TCK

M15

JTAG_TMS

U12

JTAG_TDI

M12

JTAG_TDO

AD12

SPI_CLK

AB8

SPI_CS0#

AB6

SPI_CS1#

W8

SPI_MOSI

Y2

SPI_MISO

CougarPoint-H_SFF_Rev_1_0

CougarPoint-H_SFF_Rev_1_0

RTCIHDA

RTCIHDA

JTAG

JTAG

SPI

SPI

FWH4 / LFRAME#

LDRQ1# / GPIO23

LPC

LPC

+3V

SATA3

SATA3

SATA

SATA

+3V

+3V_S5

SATA3RCOMPO

SATA0GP / GPIO21

+3V

SATA1GP / GPIO19

+3V

FWH0 / LAD0

FWH1 / LAD1

FWH2 / LAD2

FWH3 / LAD3

LDRQ0#

SERIRQ

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA1RXP

SATA1TXN

SATA1TXP

SATA2RXN

SATA2RXP

SATA2TXN

SATA2TXP

SATA3RXN

SATA3RXP

SATA3TXN

SATA3TXP

SATA4RXN

SATA4RXP

SATA4TXN

SATA4TXP

SATA5RXN

SATA5RXP

SATA5TXN

SATA5TXP

SATAICOMPO

SATAICOMPI

SATA3COMPI

SATA3RBIAS

SATALED#

A37

A39

C39

C37

K40

H40

F37

IRQ_SERIRQ

Y4

AN3

AN1

AU3

AU1

AN6

AN8

AR3

AR1

AD4

AD2

AL3

AL1

AD8

AD6

AG3

AG1

AE3

AE1

AH8

AH6

AC3

AC1

AJ3

AJ1

AB10

SATA_COMP

AB12

AF10

SATA3_COMP

AF12

SATA3_RBIAS

AH4

Open-drain output

W10

SATA_DET0#

M2

BBS_BIT0

R1

mSATA

R211 37.4/F_4R211 37.4/F_4

R209 49.9/F_4R209 49.9/F_4

R208 750/F_4R208 750/F_4

T32T32

LPC_LAD0 [21,22,23]

LPC_LAD1 [21,22,23]

LPC_LAD2 [21,22,23]

LPC_LAD3 [21,22,23]

LPC_LFRAME# [21,22,23]

IRQ_SERIRQ [22,23]

SATA_RXN0 [23]

SATA_RXP0 [23]

SATA_TXN0 [23]

SATA_TXP0 [23]

+1.05V_PCH

IRQ_SERIRQ

SATA_DET0#

PCH JTAG Debug (CLG)

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TCK

PCH_JTAG_TDO

+RTC_CELL

R100 20K/F_4R100 20K/F_4

R224 20K/F_4R224 20K/F_4

RP14 10KRP14 10K

1

3

MP remove(Intel)

R98 200_4R98 200_4

R95 200_4R95 200_4

R104 100_4R104 100_4

1 2

R97 100_4R97 100_4

1 2

R107 51_4R107 51_4

R99 200_4R99 200_4

R105 100_4R105 100_4

1 2

C77

C77

1U/6.3V_4

1U/6.3V_4

PCH Strap Table

Pin Name Strap description

SPKR

HDA_SDO

Del 0510

A A

INTVRMEN

HDA_SYNC

No reboot mode setting PWROK

Integrated 1.05V VRM enable ALWAYS

On-Die PLL VR Volatge Select RSMRST

5

Sampled

PWROKFlash Descriptor Security

Configuration

0 = Default (weak pull-down 20K)

1 = Setting to No-Reboot mode

0 = Default (weak pull-down 20K)

1 = Override

Remove SPI_MOSI from PCH strapping, HR_C/L_v0.91

Should be always pull-up

0 = Support by 1.8V (weak PD)

1 = Support by 1.5V

4

+RTC_CELL

PCH_AZ_CODEC_SYNC[29]

note

R96 330K_4R96 330K_4

3

PCH_INTVRMEN

R85 33_4R85 33_4