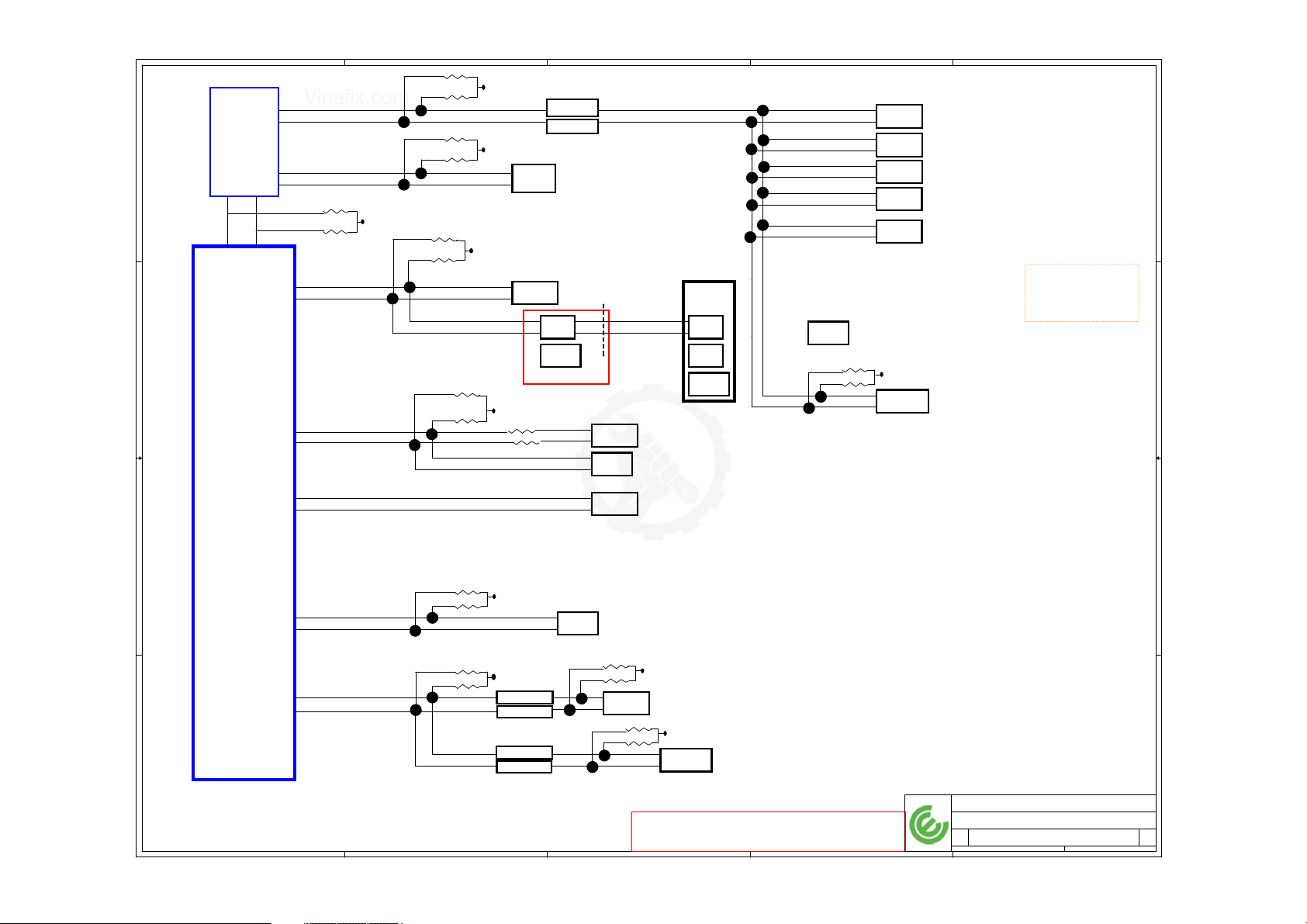

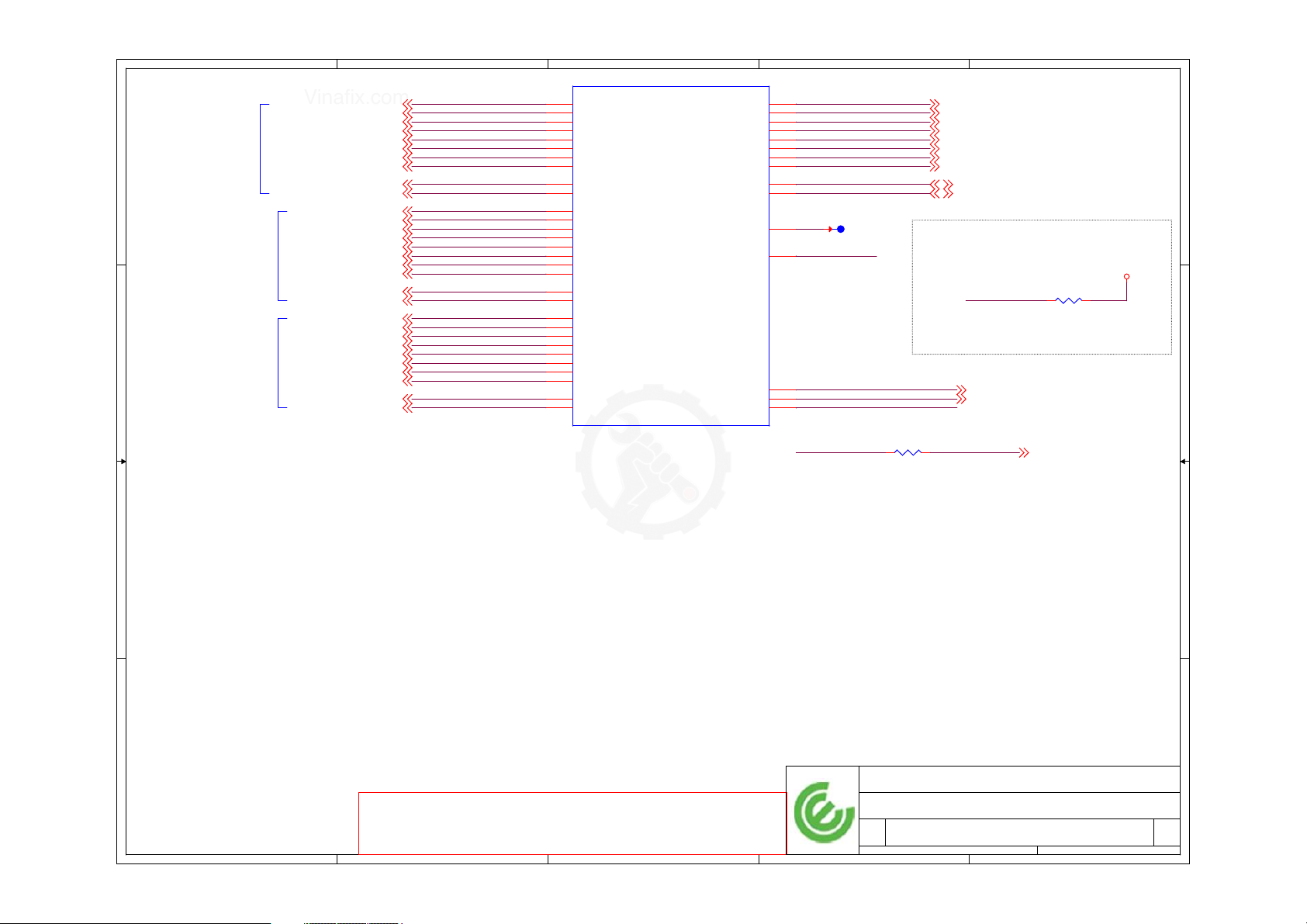

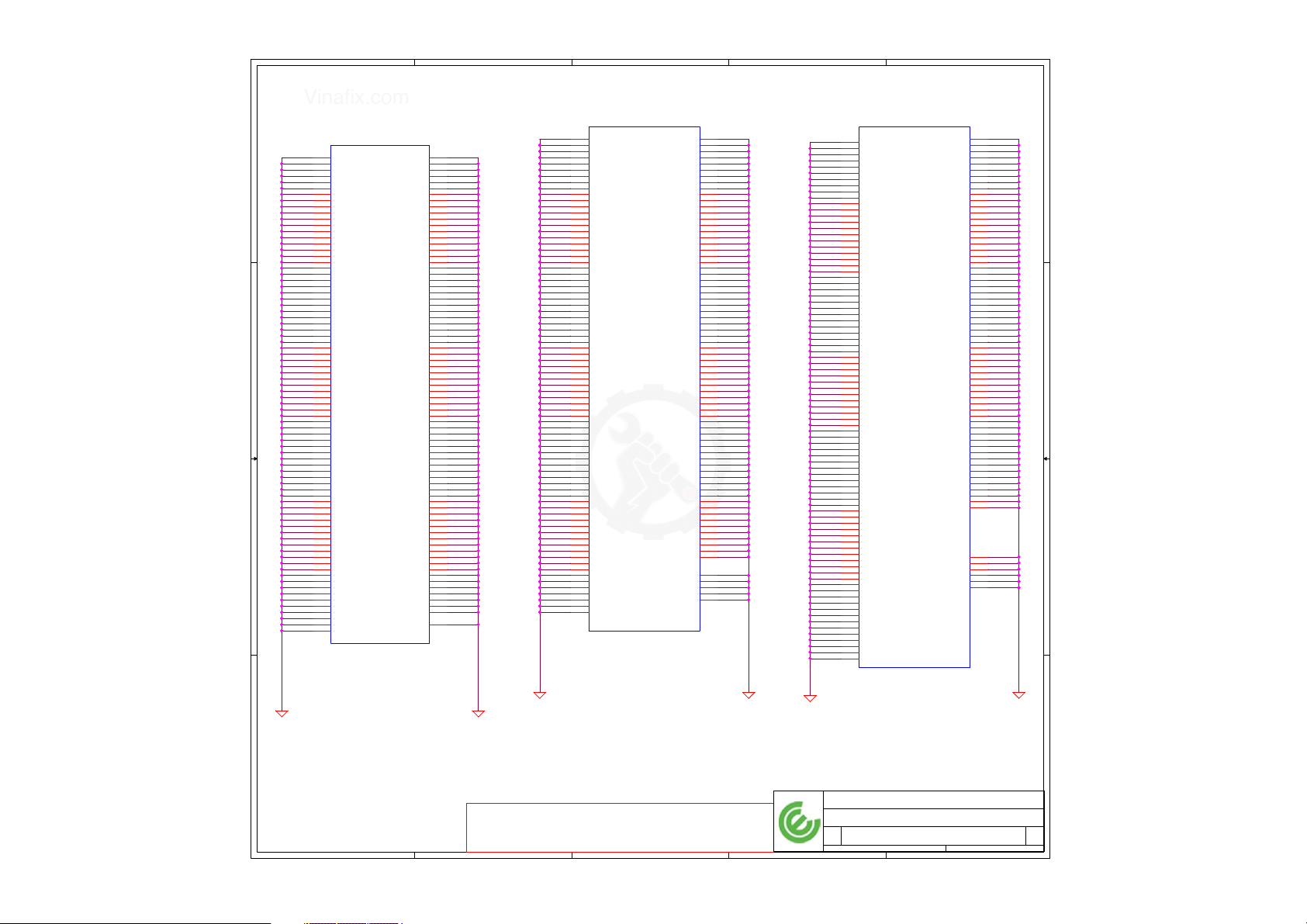

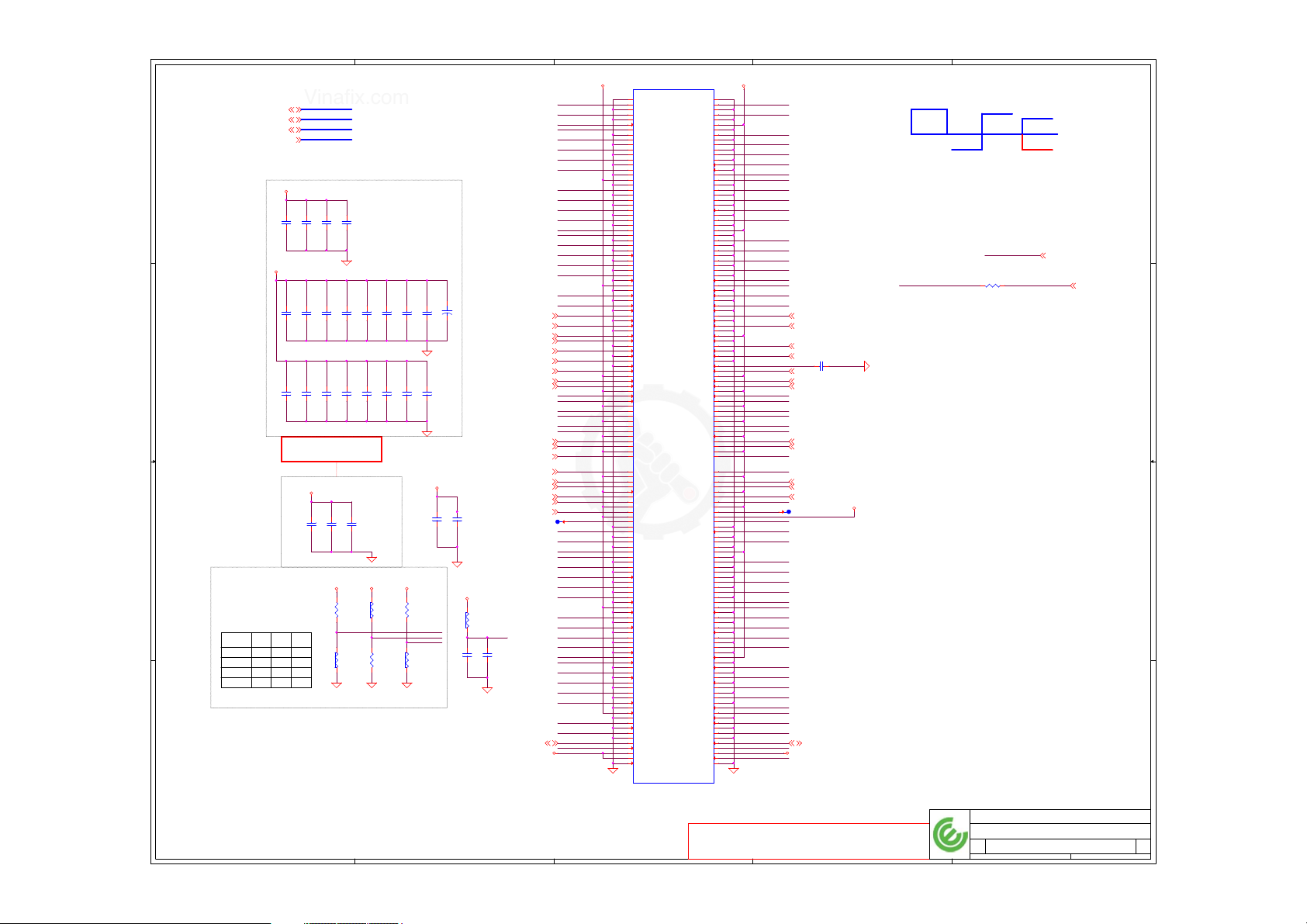

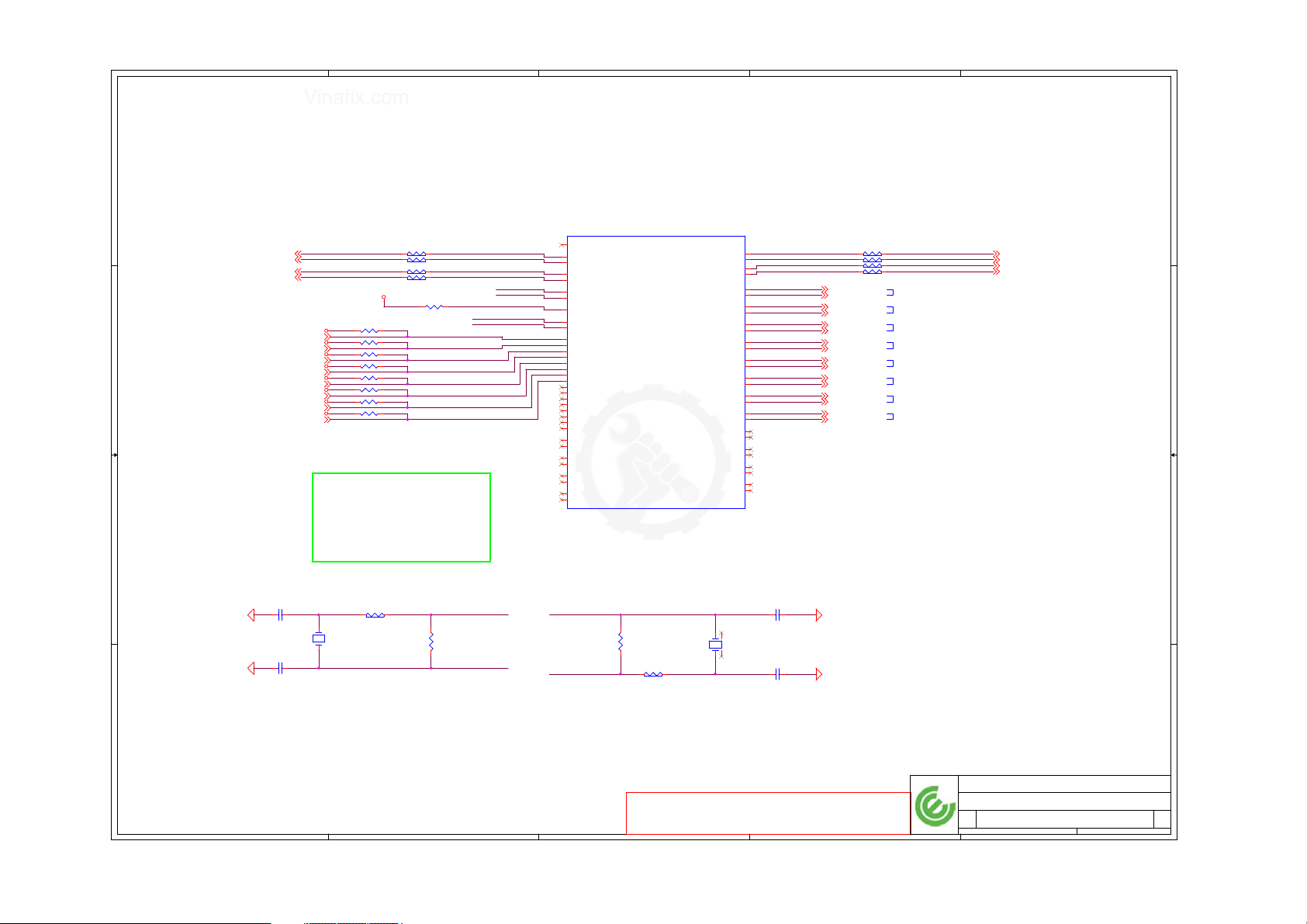

Dell precision 7520 Schematics

Vinafix.com

A

B

C

D

E

COMPAL

CONFIDENTIAL

1 1

MODEL NAME :

PCB NO :

BOM P/N :

GPIO MAP:

CAP00

LA-E311P

431A4X31L01

Gen7 GPIO Master_XXXX

CRANE15

2 2

REV : 1.0(A00)

2016.11.21

@ : Nopop Component

EMC@ : EMI/ESD/RF part

CONN@ : Connector Component

XDP@ : Total debug Component (pop them until ST)

3 3

Layout Dell logo

COPYRIGHT 2016

ALL RIGHT RESERVED

REV: X00

PWB: XXXXX

Kaby Lake H-type (2 chip)

4 4

DATE: 1403-06

PCB 1TS LA -E311P REV0 MB 1

Part

Description

Number

DAA000CS010

PCB 1TS LA-E311P REV1 MB 1

A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET O F ENGINEERING DRAWING AND SPEC IFICATIONS CONTAINS CONFIDENTI AL

TRADE SECRET AND OTHER PROPRIE TARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHO UT THE EXPRESS WRITTEN AUTHORI ZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INF ORMATION IT CONTAINS WAY BE US ED BY OR DISCLOSED TO ANY THIR D

PARTY WITHOUT DELL'S EXPRESS W RITTEN CONSENT.

B

C

D

Title

Title

Title

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Cover Sheet

Cover Sheet

Cover Sheet

LA-E311P

LA-E311P

LA-E311P

1 71Wednesday, N ovember 23, 2016

1 71Wednesday, N ovember 23, 2016

1 71Wednesday, N ovember 23, 2016

E

1.0

1.0

1.0

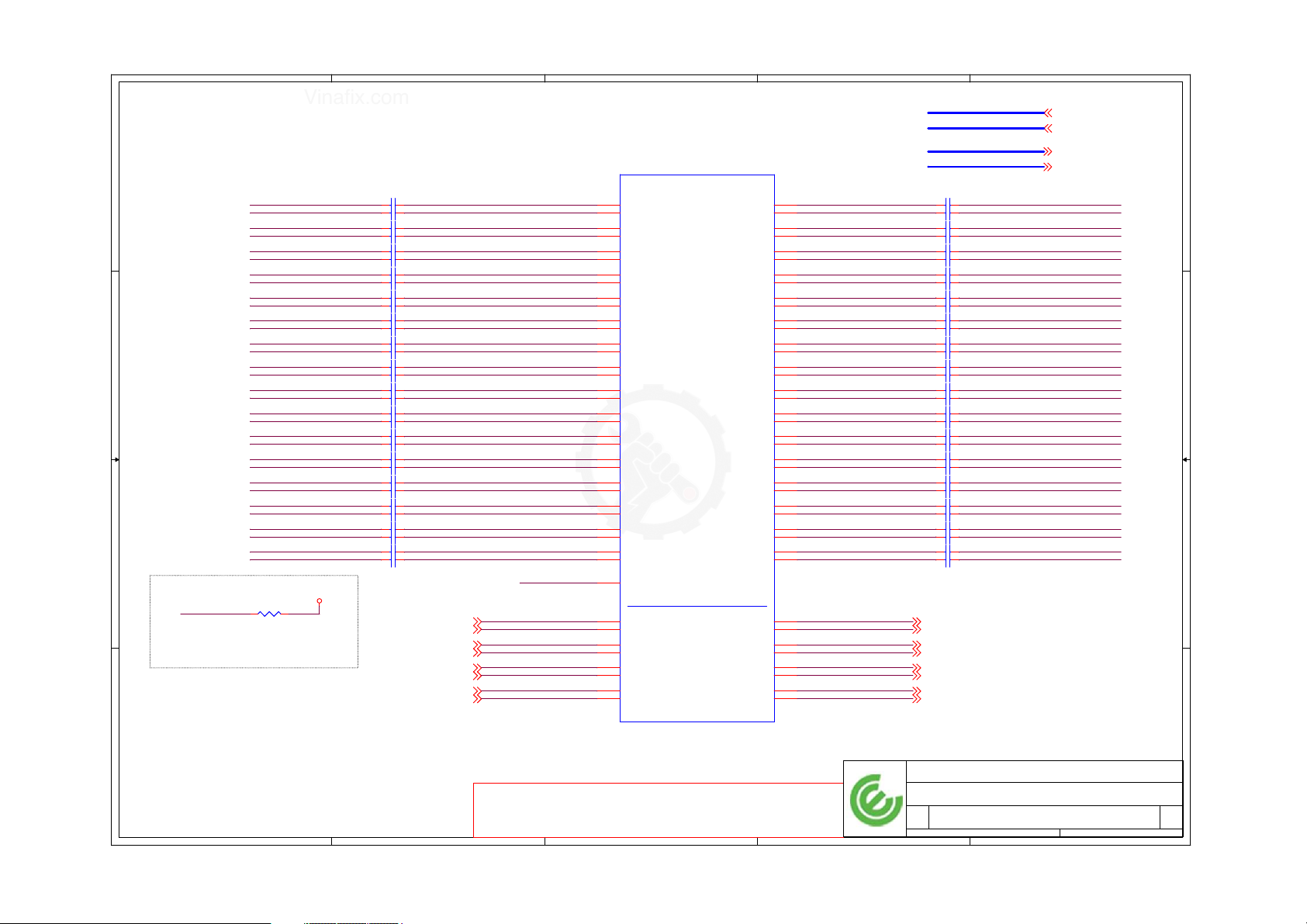

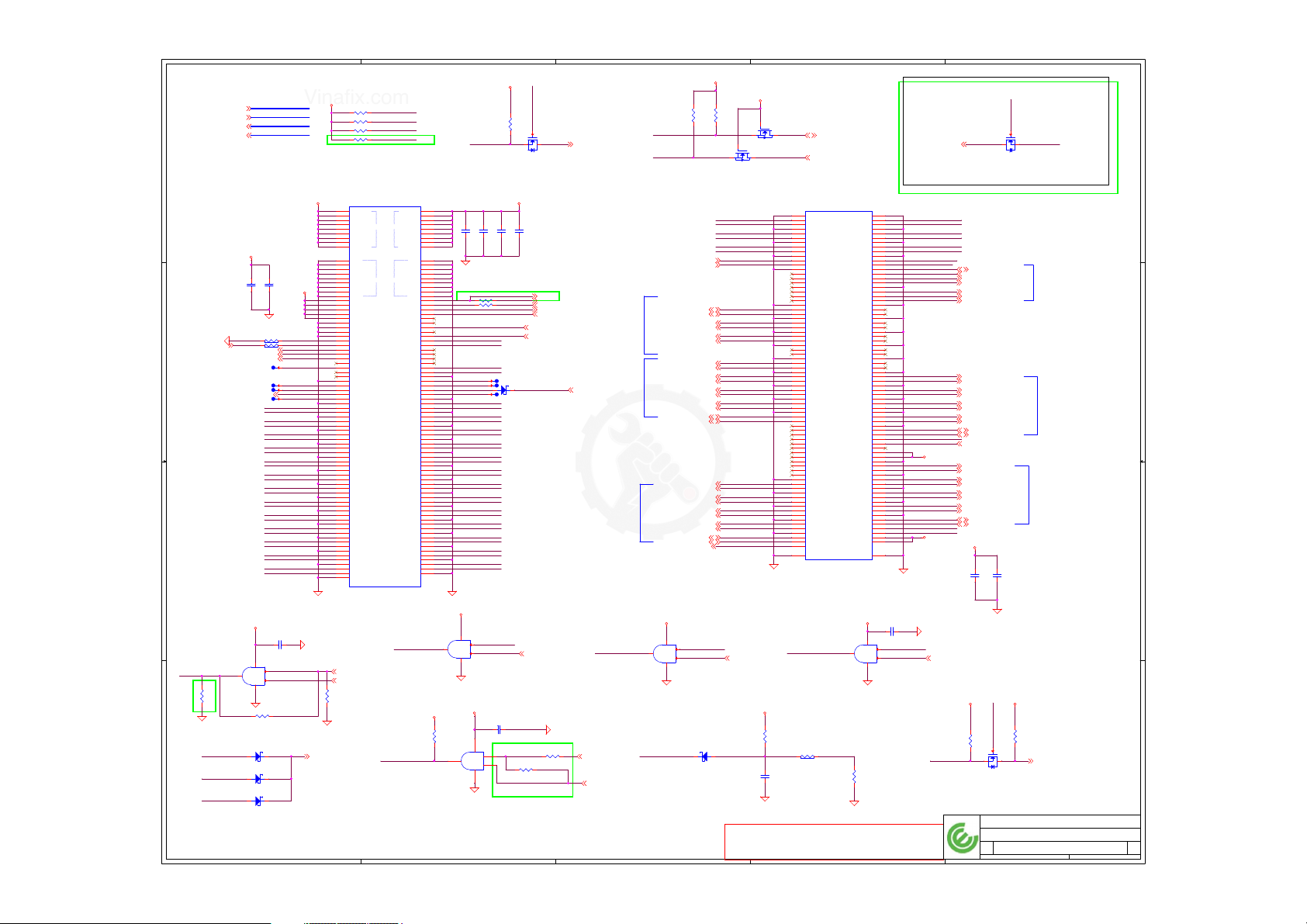

Vinafix.com

A

B

C

D

E

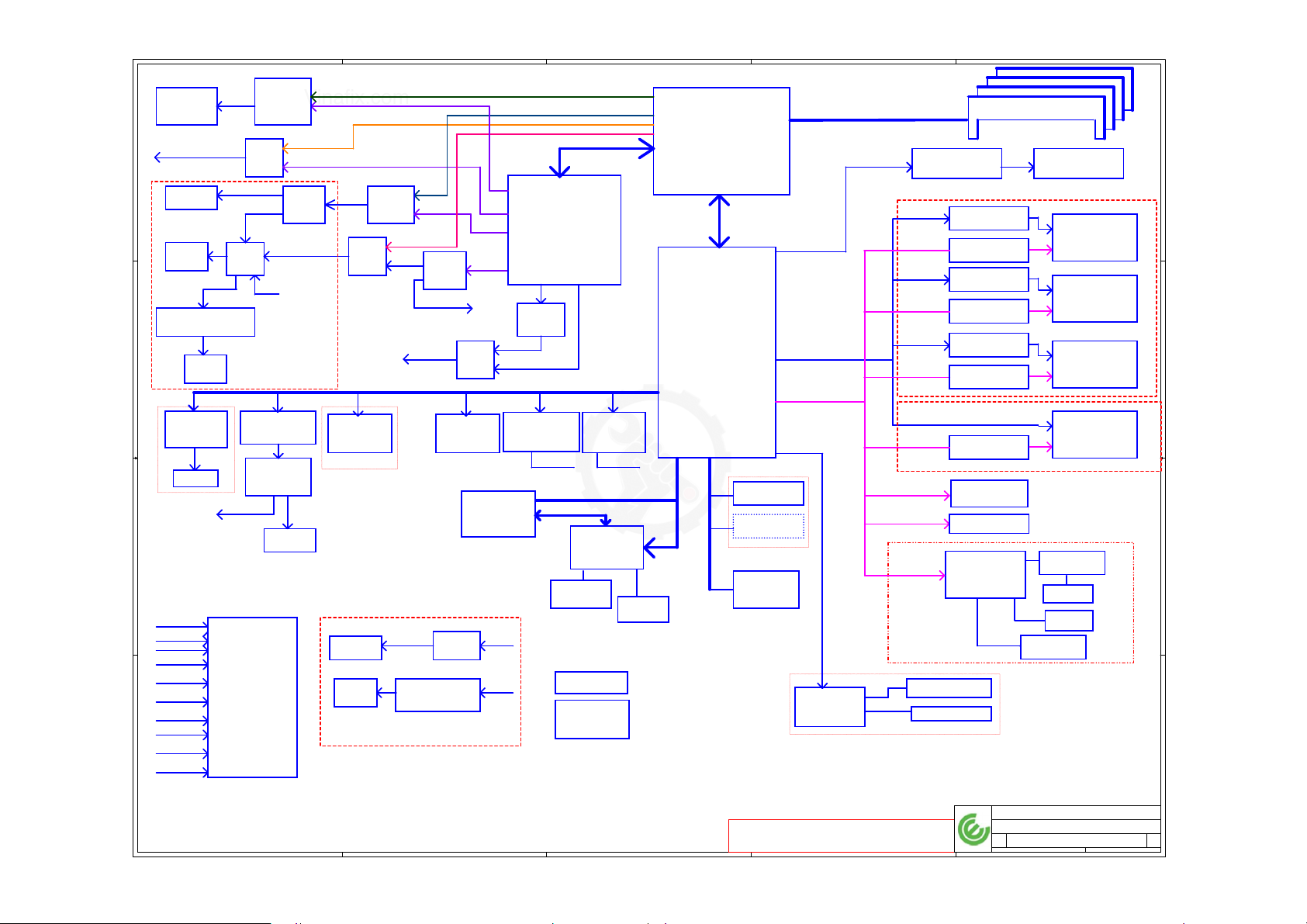

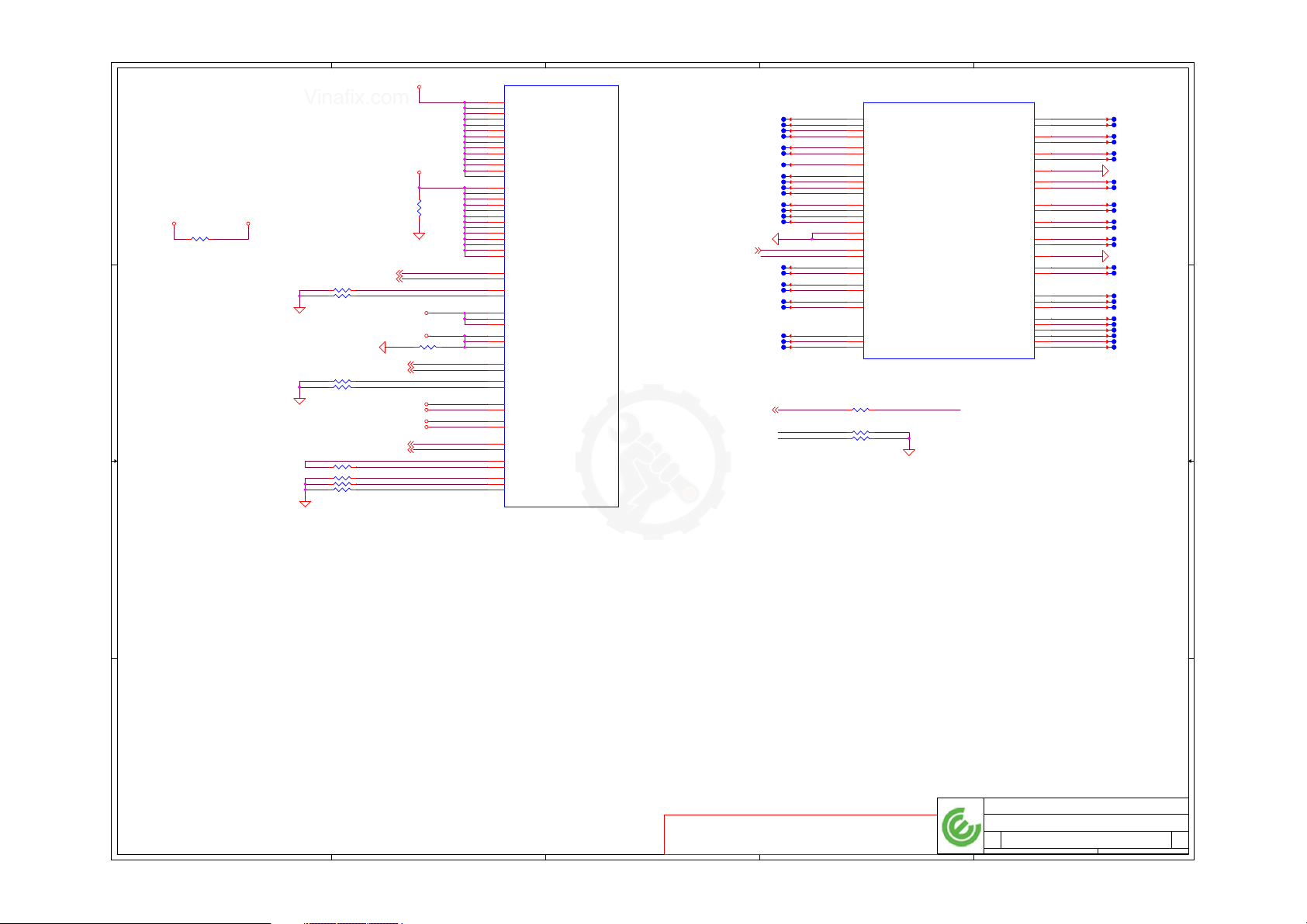

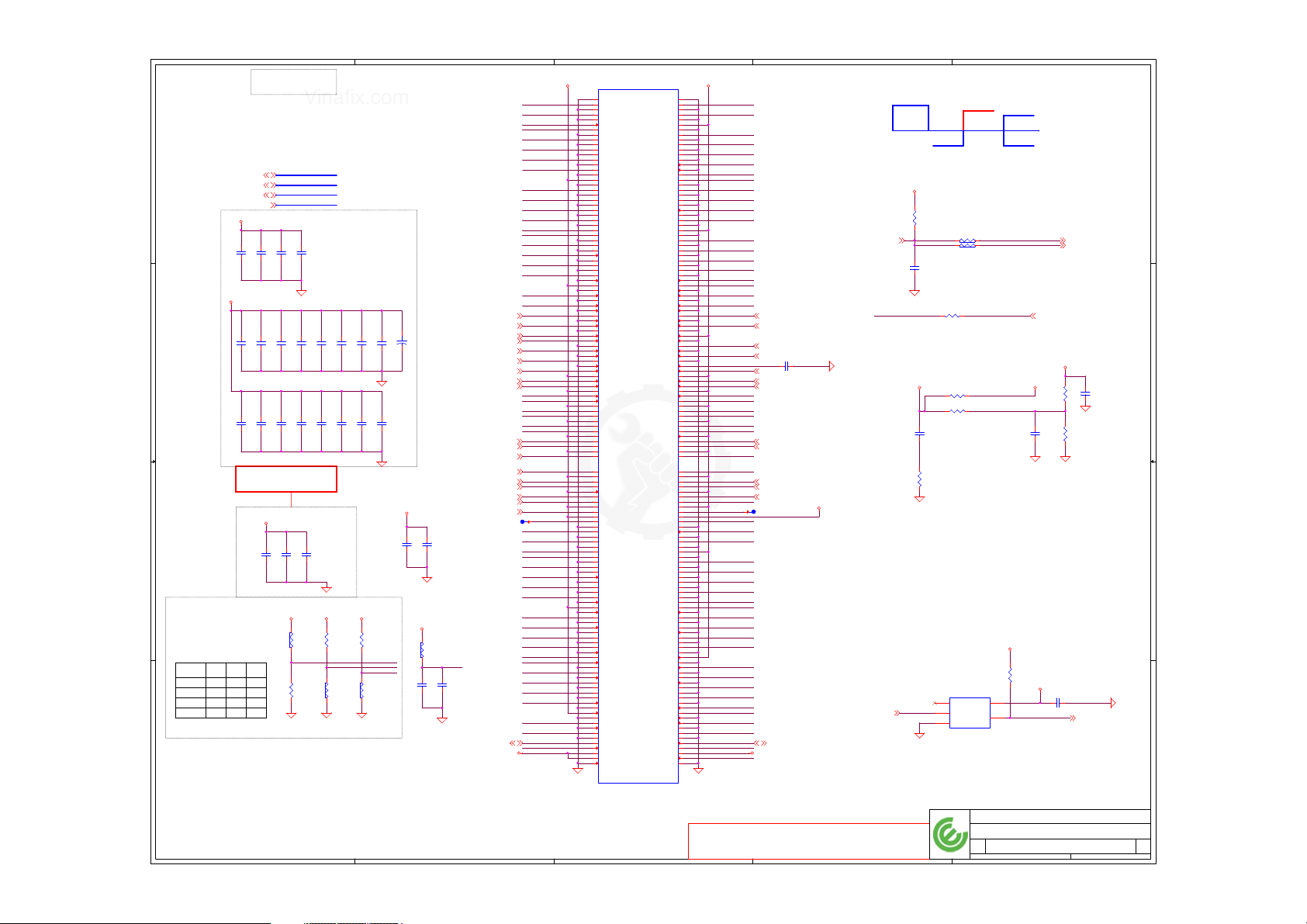

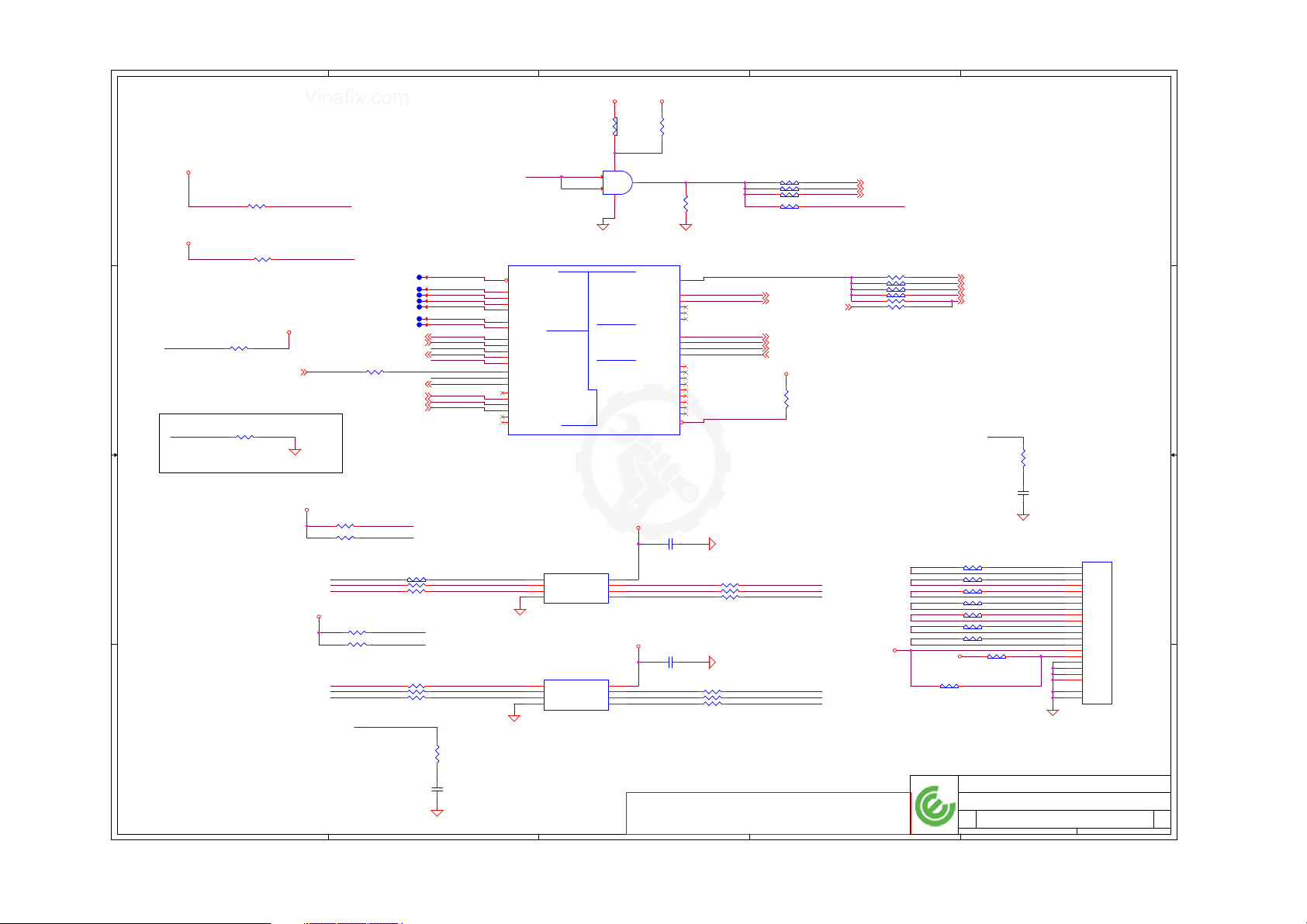

eDP Panel

Conn

P.30

Docking

DP Port1

1 1

2 2

On I/O

board

3 3

SATA Port 1

USB2 Port 7

USB2 Port 5

USB3.0 Port 6

Docking

4 4

DP1

Docking

DP2

mDP

1.3

Conn

HDMI1.4b

Conn

UPD

TPS65982D

Type-C

Conn

Port 3

RTS5242

SD4.0/MMC

SDXC

DAI

RGB

LAN

LPC

SW2 DP

P.6

P.6

SW1 DP

DP MUX

PS8331

mDP

SW6 DP2

TBT_DP1

SW6 DP1

TBT

AR-SP

Port 5~8

Intel Jacksonville

WGI219LM

LAN switch

PI3L720ZHEX

Docking

LAN

E-Dock

eDP MUX

PS8331

P.31

DP DEMUX

PS8468

TBT_DP0

PCIE

On Display

TBT board

Port 4

RJ45

P.43

P.29

DDI1

DPC

SW4 DP

P.37

P.37

P.37

Lane x4

Lane x4

P.33

DDI2

SW3 DP

Docking

CRT

DDI3

DPB

DP DEMUX

PS8338

P.32

Docking

DP Port2

M.2 Card slot_3

2280 SSD

TS3V712

VGA 2:1

SW

SW5 DP

DP1.3 MUX

HD3SS214

DP MUX

PS8331

P.34

Port 5~8 Port 2

TBT

AR-SP

P.5~8

On Display I/O board

DP_D

DP_C

MXM Conn.

TYPE A

DP_B

DPA

DP_A

DP_F

DP to VGA

RTD2166

P.35

P.36

PCIE BUS

Port 9~12

SATA Port 0 SATA Port 4

P.41

SMSC SIO

ECE5048

Port 17,18

M.2 Card slot_2

WWAN/LTE/HCA/

Cache

USB2 Port8 USB2 Port 6

BC BUS

P.47

FAN CONN

SW5 DP

DP redriver

mDP 1.3

Conn

HDMI1.4b

Conn

mDP

PS8460

DP to HDMI retimer

PS8407A

On Display Entry

board

SW4 DP

PEG x16

(Gen3)

P.18

VGA

M.2 Card slot_1

WLAN/BT

P.40

SMSC KBC

MEC5085

P.28

Micro SIM Card

Free Fall Sensor

LNG2DMTR

P.40

P.43

P.40

P.48

KB/TP

CONN

eDP

Intel

DDI3

KABYLAKE-H/

DDI1

DDI2

SKYLAKE-H 44e

PEG

BGA CPU

1440 Pins

Intel

SKYLAKE-H

BGA

837 Pins

LPC BUS

SPI

P.50

P.6~13

DMI x4

gen 2

P.18~26

W25Q128FVSIQ

128Mb 4K sector

W25Q32FVSSIQ

32Mb 4K sector

Discrete TPM

NPCT650JB2YX

(DDR4) Memory Bus

1.2V DDR4 2400/2667M Hz (Overclocking)

SATA Port 3

PCIE Port 15,16

SATA3.0

USB3.0

USB2.0

HD

Audio

P.22

P.22

P.39

Audio Codec

ALC3254

On I/O board

P.4

SATA/PCIE Repeater

PS8558B

USB3 Port 3

USB2 Port 2

USB3 Port 4

USB2 Port 3

USB3 Port 5

USB2 Port 4

USB3 Port 1

USB2 Port 1

USB2 Port 11

USB2 Port 9

USB Port 10

On USH/B

Universal Jack

Int. Speaker

DDR4 ECC-SO-DIMM X4

P.44

USB 3.0 Repeater

PS8713B

USB Power Share

SLGC55544CVTR

USB 3.0 Repeater

PS8713B

USB Power Share

SLGC55544CVTR

USB 3.0 Repeater

PS8713B

USB Power Share

SLGC55544CVTR

USB Power Share

SLGC55544CVTR

Digital Camera

Touch screen

LYNX(CV2)

BRCM58100

SPI

P.4

P.14~17BANK 0, 1, 2, 3, 4 ,5 ,6 ,7

SATA EXPRESS HDD

P.7

P.7 P.7

P.8

P.8 P.8

P.9

P.43

USB 3.0 Conn

Right Side

USB Charger

USB 3.0 Conn

Right Side

USB Charger

USB 3.0 Conn

Right Side

USB Charger

USB 3.0 Conn

Left Side

P.12

P.30

P.30

USB Charger

TDA8034HN

Smart Card

SPI

RFID/NFC

Fingerprint

CONN

P.9P.9

P.12

On Display

board

P.39

On I/O

board

A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

B

C

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

D

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Block Diagram

Block Diagram

Block Diagram

LA-E311P

LA-E311P

LA-E311P

E

2 71Wednesday, November 23, 2016

2 71Wednesday, November 23, 2016

2 71Wednesday, November 23, 2016

1.0

1.0

1.0

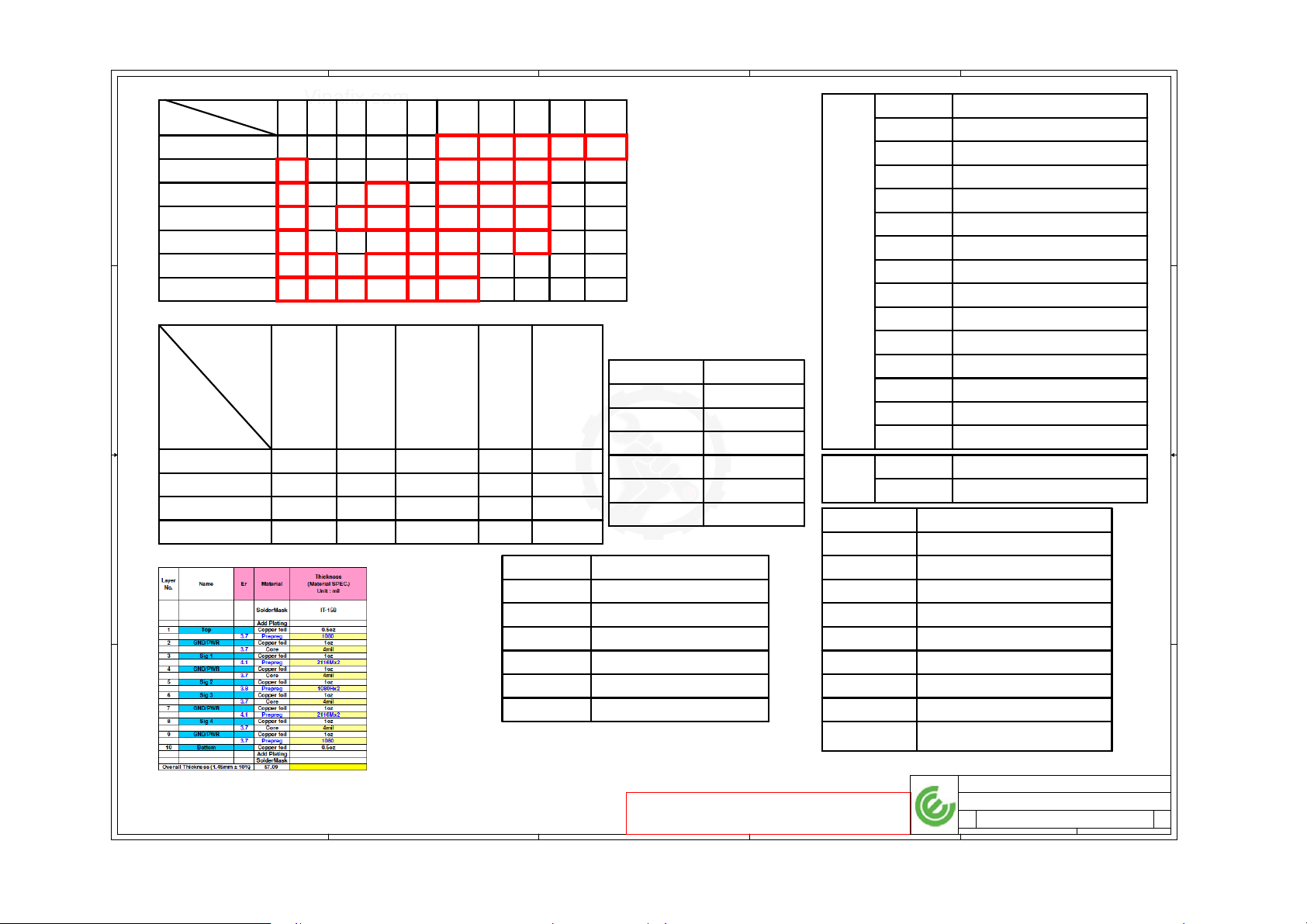

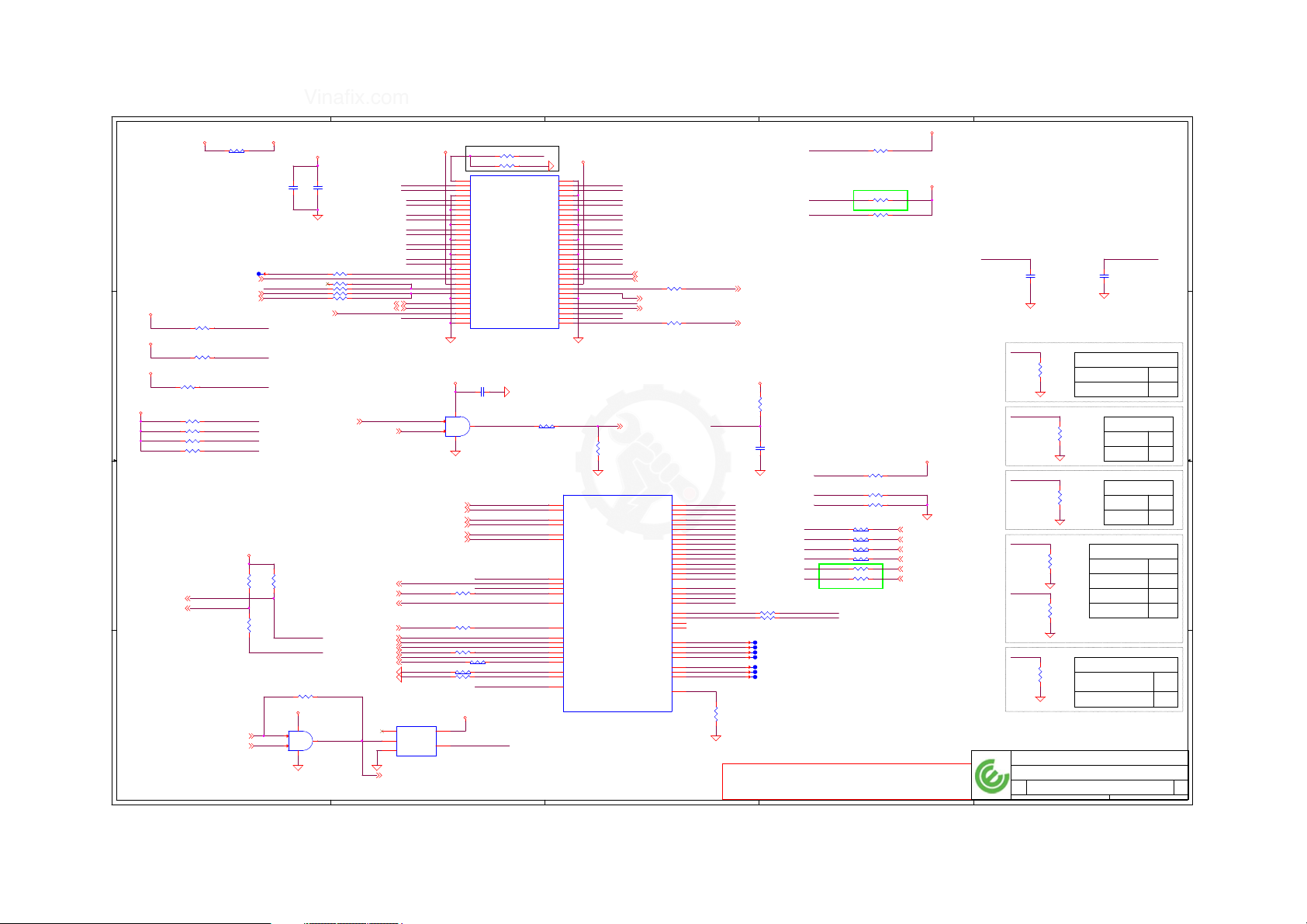

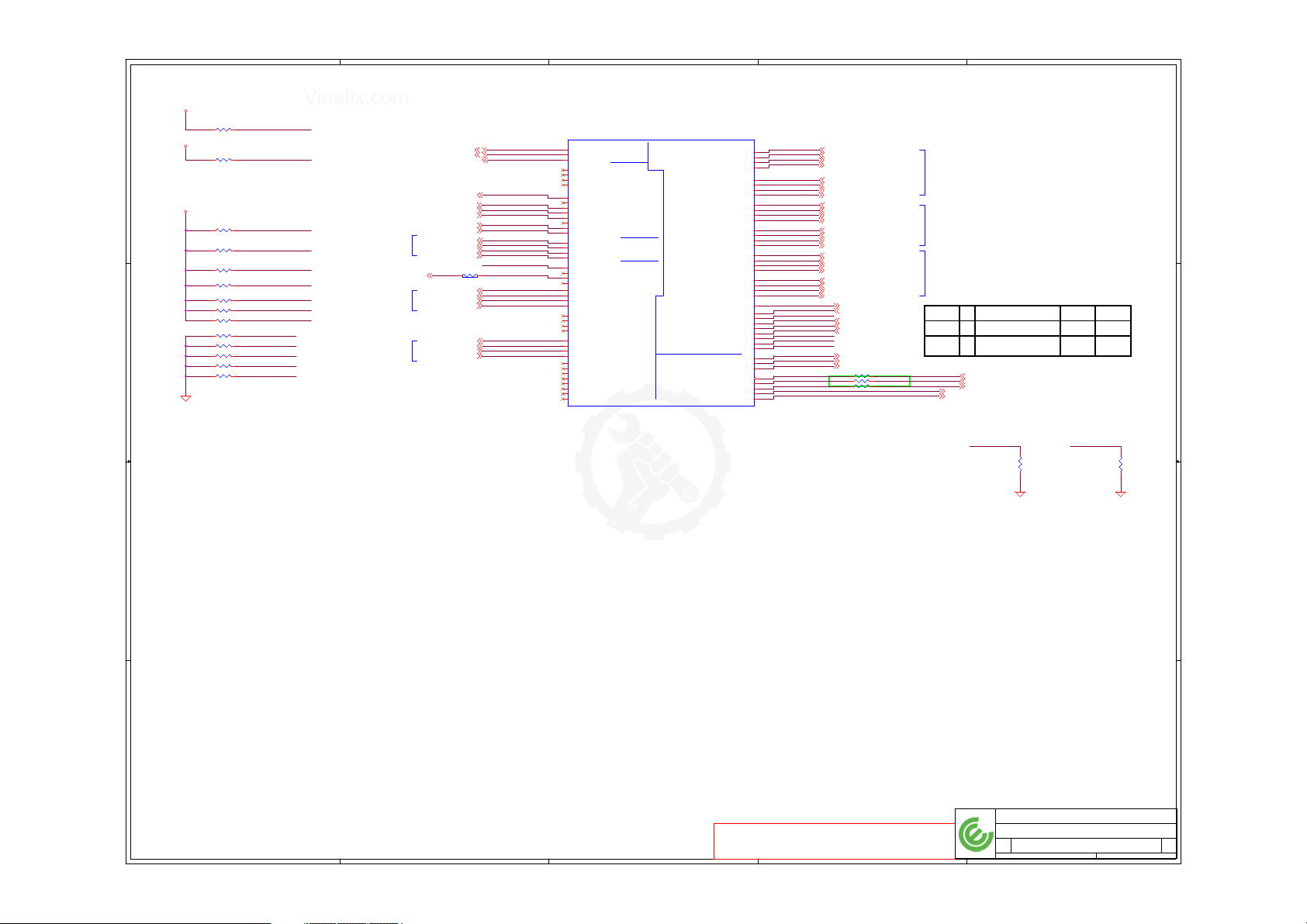

Vinafix.com

5

4

3

2

1

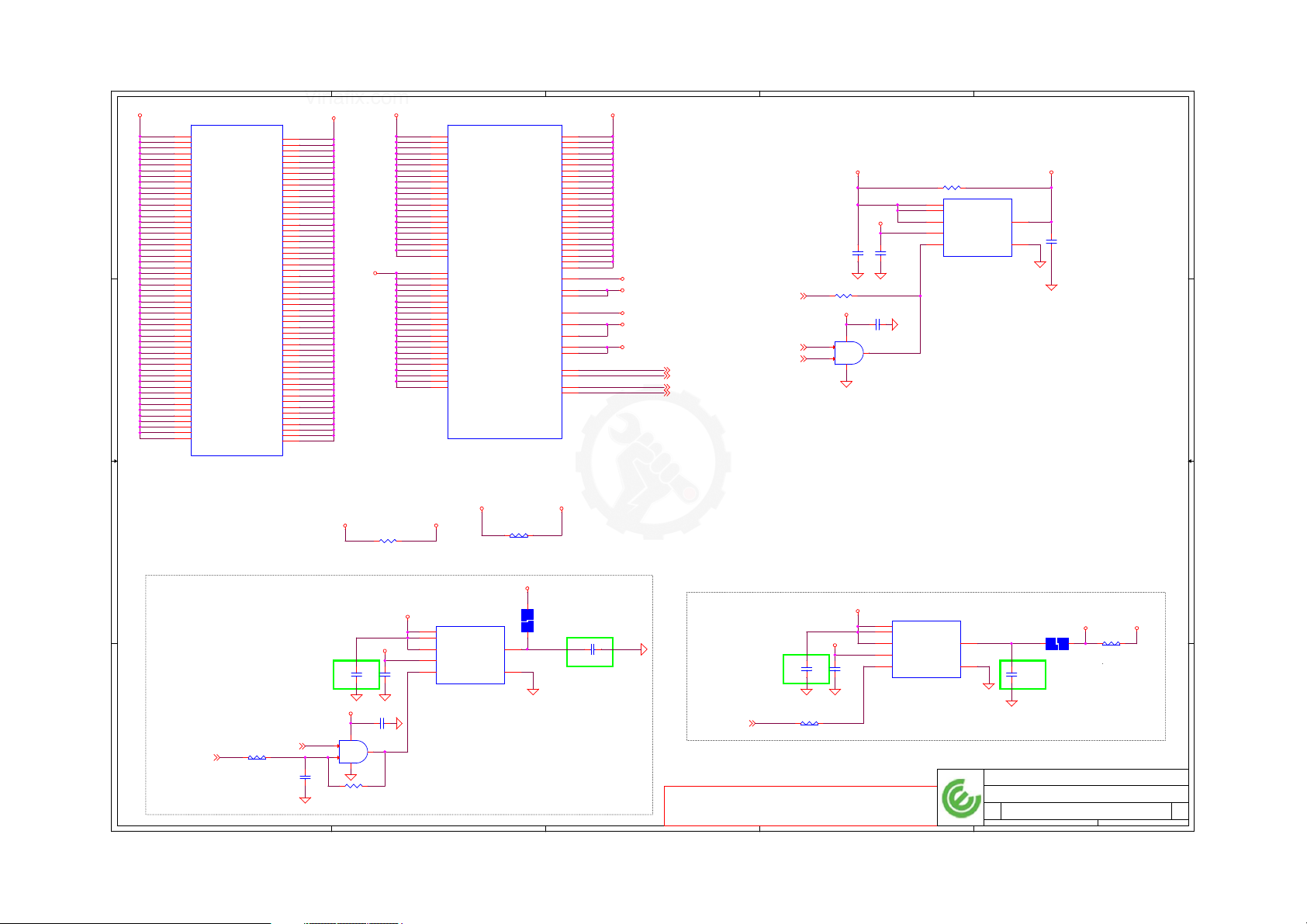

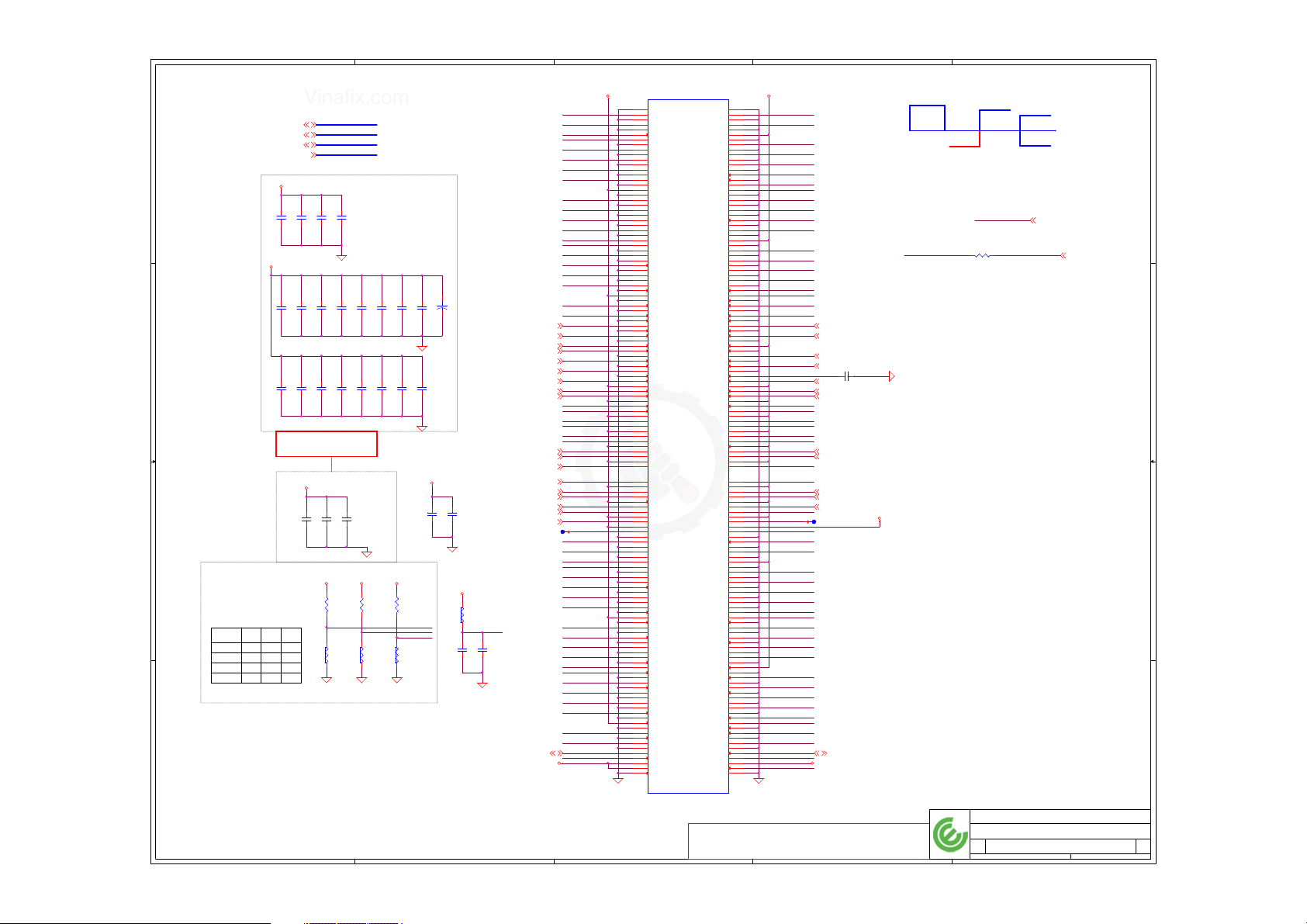

POWER STATES

Signal

State

S0 (Full ON) / M0

D D

S3 (Suspend to RAM) / M1 LOW HIGH HIGH HIGH ON ON ON OFF

S4 (Suspend to DISK) / M1 ON ON OFF

S5 (SOFT OFF) / M1 ON ON OFFLOW LOW HIGHLOW

S3 (Suspend to RAM) / M-OFF

S4 (Suspend to DISK) / M-OFF HIGH

S5 (SOFT OFF) / M-OFF

SLP

S3#

HIGH

LOW HIGH HIGHLOW

LOW HIGH HIGH HIGH LOW ON ONOFF OFF OFF

LOW LOW LOW LOW ON OFF OFF OFF OFF

LOW LOW LOW LOW LOW ON OFF OFF OFF OFF

SLP

SLP

S4#

HIGH HIGH HIGH

LOW

LOW

S5#

S4

STATE#

SLP

M#

HIGH

HIGH

ALWAYS

PLANE

ON ON

RUN

CLOCKS

PLANE

ON ON ON

OFF

OFF

OFF OFF

OFF

PCH

PM TABLE

+PWR_SRC

+5V_ALW

C C

State

S0

S3

S5 S4/AC

S5 S4/AC don't exist

B B

A A

power

plane

+3.3V_ALW

+3.3V_ALW2 +1.0V_VCCST

+3.3V_ALW_DSW

+3.3V_ALW_PCH

+3.3V_RTC_LDO

+1.8V_ALW

+1.0V_PRIM

ON

ON

Stack up

+3.3V_SUS

+1.2V_MEM

+2.5V_MEM

+5V_RUN

+3.3V_RUN

+1.5V_RUN +VCC_CORE

+0.675V_DDR_VTT

+3.3V_MXM

+5V_MXM

+MXM_PWR_SRC

ON ON

ON

OFF

OFFOFF

OFFON

OFF

OFF

(M-OFF)

+VCC_EDRAM

+VCC_EOPIO

+VCC_GTU

+VCC_GT

+1.0V_VCCSTG

+VCC_SA

ON

ON

ON

ON

OFF

OFF

OFFOFF

USB3.0 DESTINATION

Port 1

Port 2

Port 3

Port 4

Port 5

Port 6

Left Side JUSB1

M.2 Slot-2 (WWAN/LTE/HCA)

Right Side JUSB1

Right Side JUSB2

Right Side JUSB3

Docking

SATA

SATA 0

SATA 1

SATA 2

SATA 3

SATA 4

SATA 5

DESTINATION

2280 SSD

Dock ESATA

NA

SATAe HDD

M.2 Slot-2 (cache)

NA

USH

PCI EXPRESS

USB PORT# DESTINATION

1

Left Side JUSB1

2

Right Side JUSB1

3

Right Side JUSB2

4

Right Side JUSB3

5

Docking USB3.0

6

M.2 Slot-1 (BT)

7

Docking USB 2.0

M.2 Slot-2 (WWAN/LTE/HCA)8

9

Touch Screen

10

USH

11

Camera

12

NA

13

NA

14

NA

0

1

BIO

NA

DESTINATION

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5~8

Lane 9~12

Lane 13~14

Lane 15~16

Lane 17~18

NA

M.2 Slot-1 (WLAN)

MMI(Card reader)

10/100/1G LOM

TBT-Alpine Ridge

M.2 Slot-3(SSD 2280)

(Dock ESATA),NA(LANE reservsal)

SATA-Express HDD(LANE reservsal)

M.2 Slot-2(WWAN/LTE/Optane)

5

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Nu mber Rev

Size Document Nu mber Rev

Size Document Nu mber Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Index and Config.

Index and Config.

Index and Config.

LA-E311P

LA-E311P

LA-E311P

3 71Wednesday, N ovember 23, 2016

3 71Wednesday, N ovember 23, 2016

3 71Wednesday, N ovember 23, 2016

1

1.0

1.0

1.0

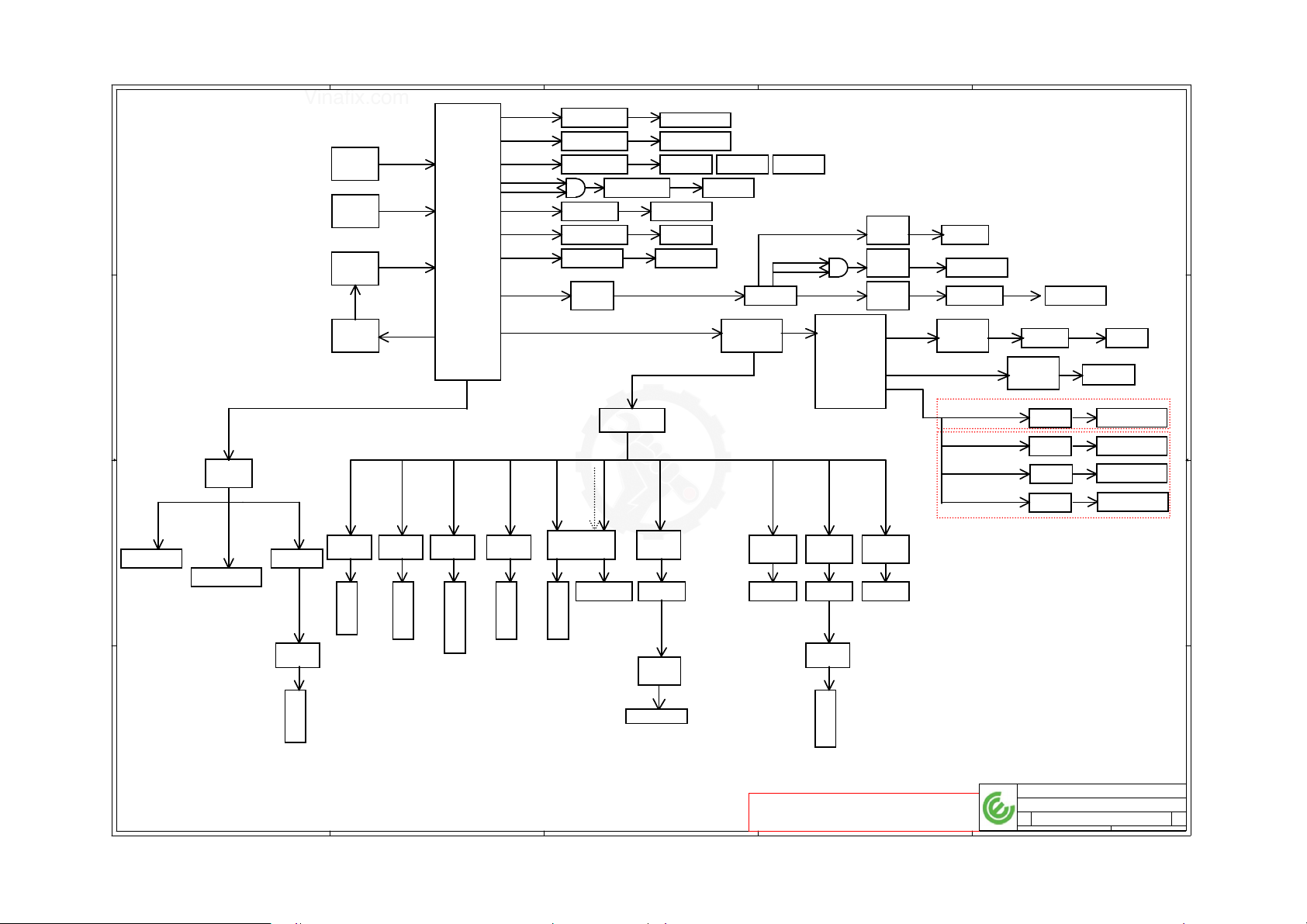

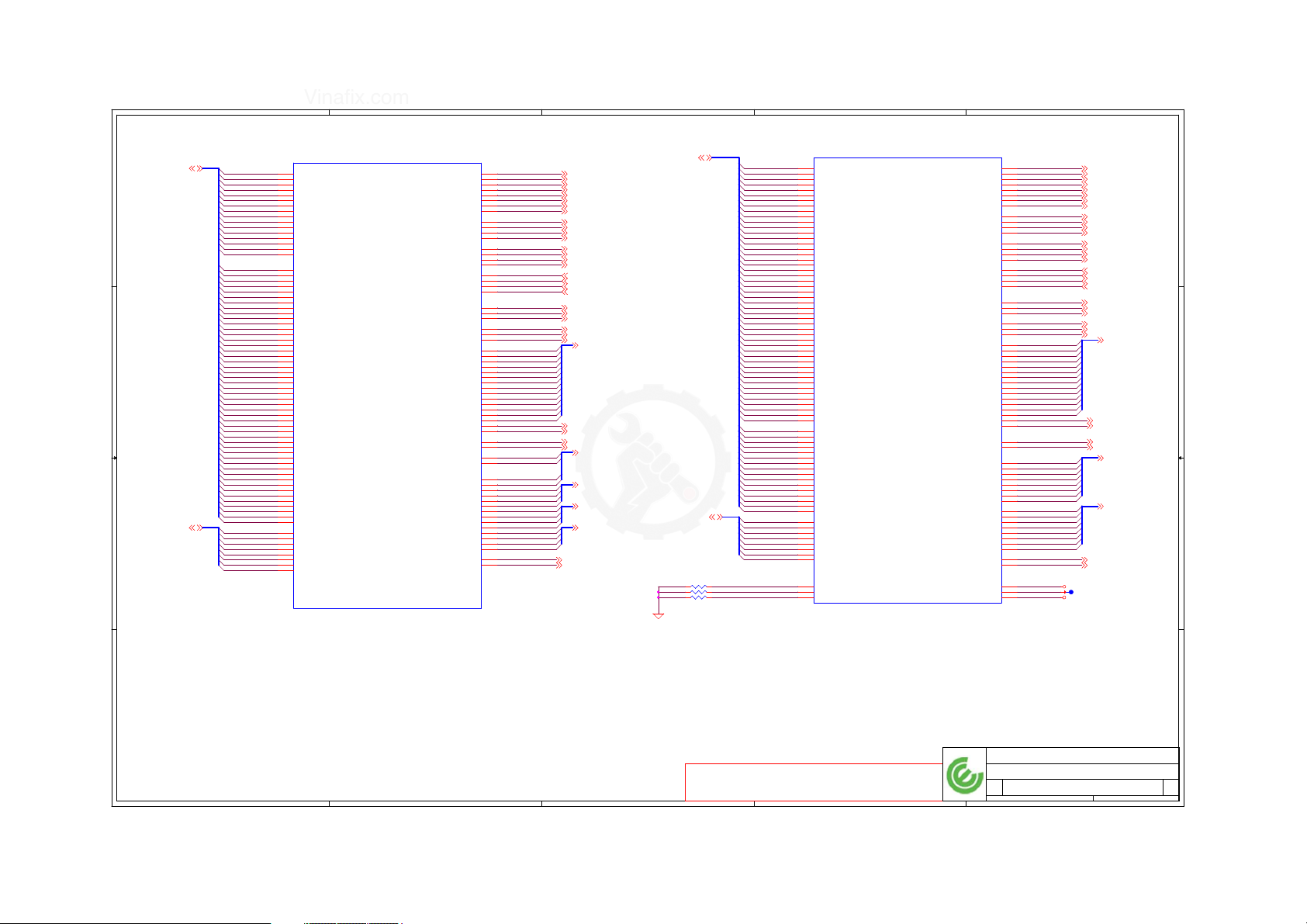

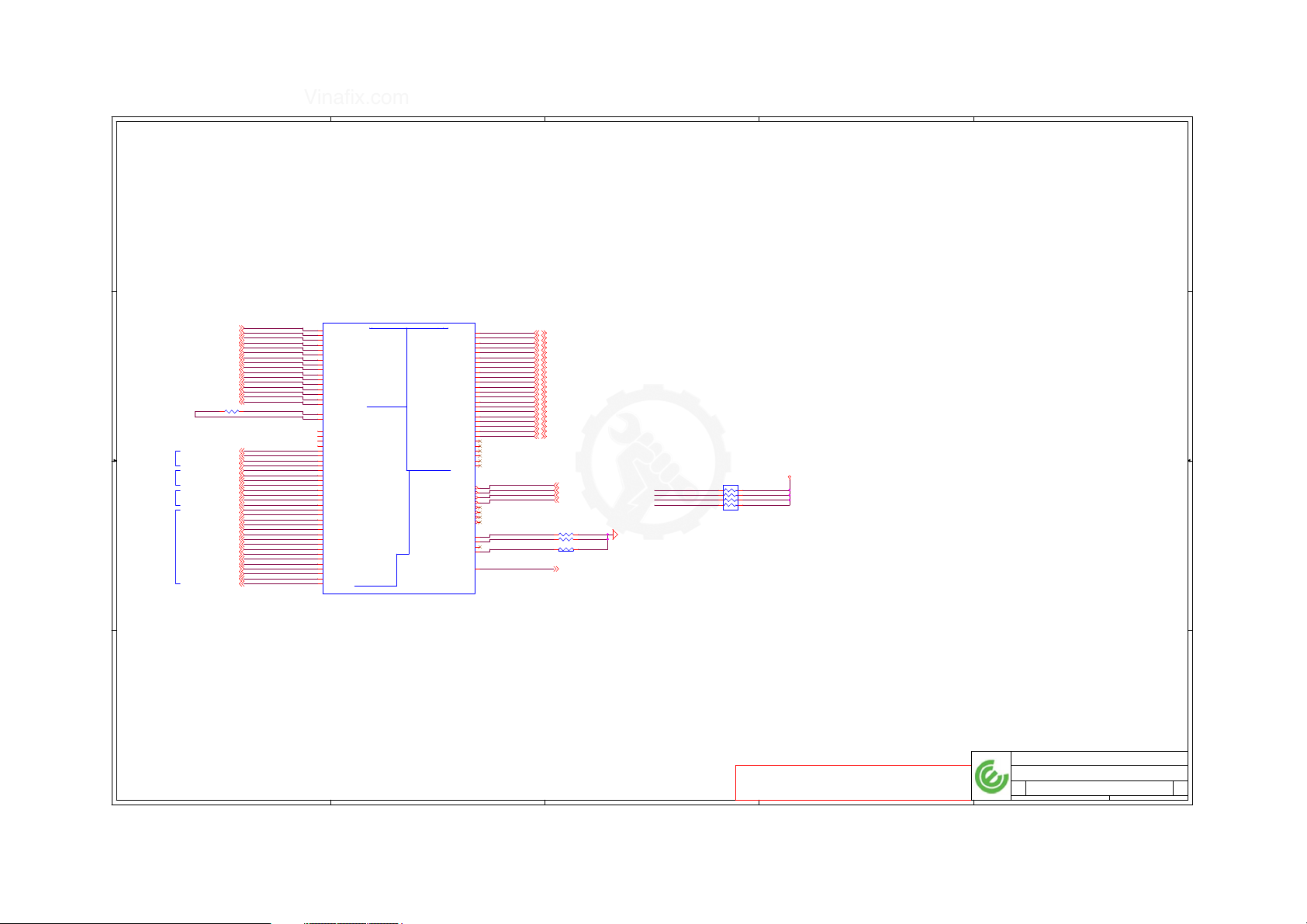

Vinafix.com

5

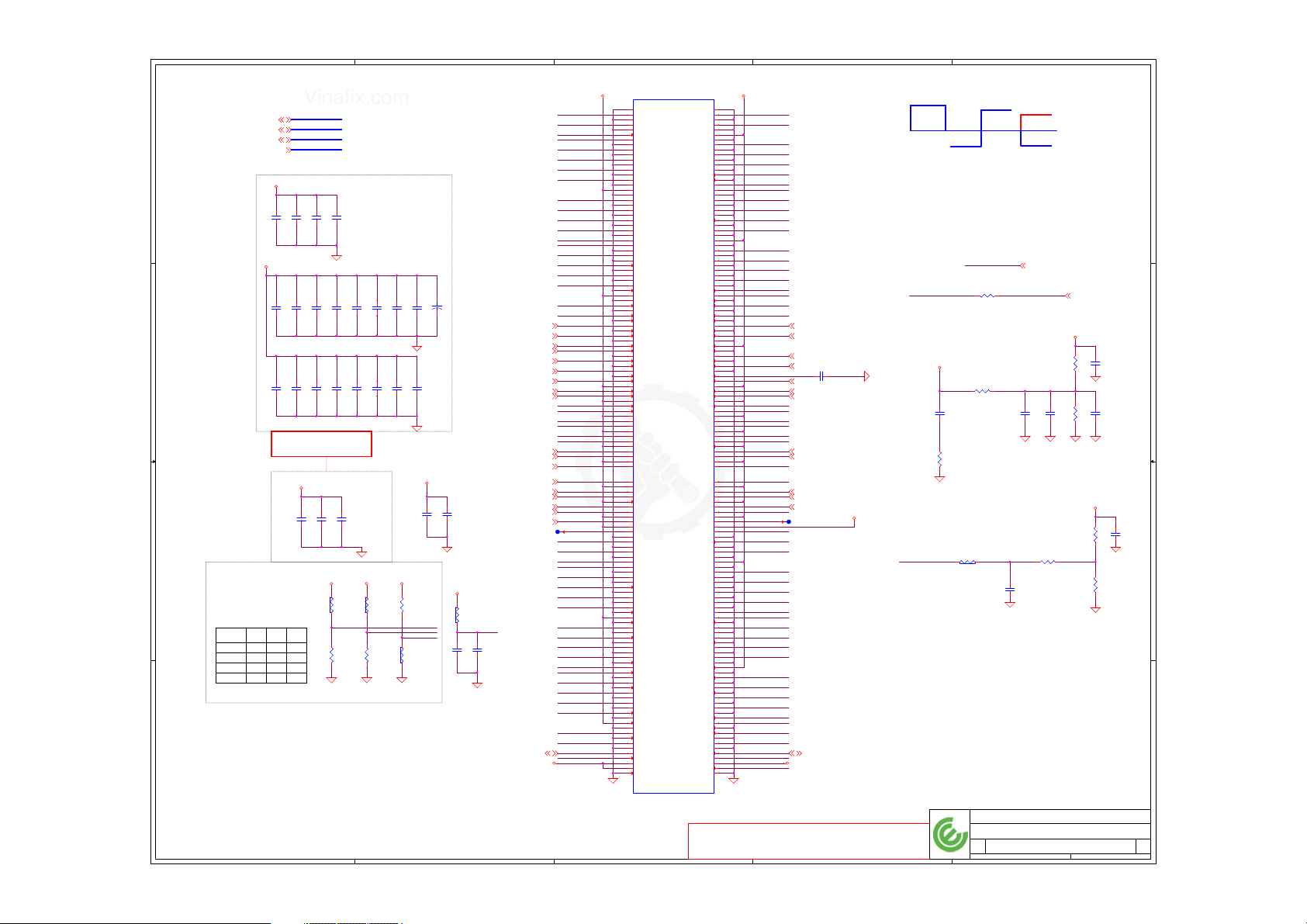

Docking

D D

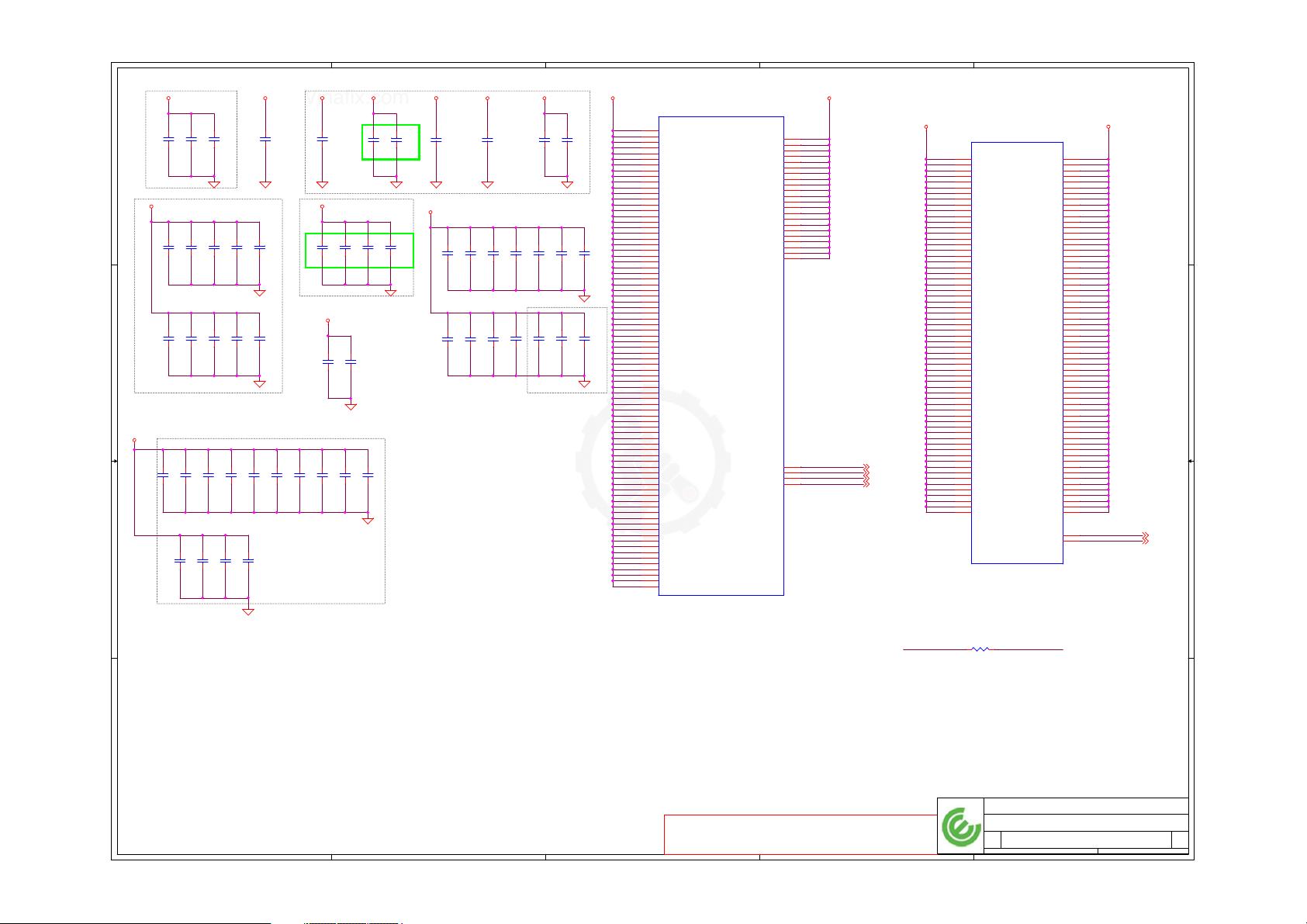

ADAPTER

BATTERY

CHARGER

C C

SIO_SLP_S4#

RT8207

(PU200)

NVRAM_PWR_EN

B B

+V_DDR_REF

0.6V_DDR_VTT_ON

+1.2V_MEM

AOZ1336

+0.6V_DDR_VTT

(UZ21)

+3.3V_SSD1

AOZ1336

(UZ24)

4

+PWR_SRC

EN_INVPWR

3.3V_RUN_GFX_ON

IMVP_VR_ON

SIO_SLP_S3#

1.2V_SUS_PWRGD

IMVP_VR_ON

IMVP_VR_ON

IMVP_VR_ON

SIO_SLP_SUS#

FDC654P

(Q21)

SI4835DDY

(Q186)

NCP81205MNTXG

(PU1100)

NB681GD

(PU1800)

NCP81210MNTWG

(PU1600)

TPS62134C

(PU500)

TPS51212

(PU800)

+3.3V_ALW

3.3V_WWAN_EN

+3.3V_WWAN

PCH_ALW_ON

AOZ1336

(UZ27)

+3.3V_ALW_PCH

3.3V_RUN_GFX_ON

EM5209VF

(UZ26)

+3.3V_MXM

SIO_SLP_LAN#

SIO_SLP_WLAN#

AUX_EN_WOWL

EM5209VF

(UZ25)

+3.3V_LAN

+3.3V_WLAN +LCDVDD

SYX198DQNC

(PU300)

EM5209VF

+3.3V_RUN

3

+BL_PWR_SRC

+MXM_PWR_SRC

+VCC_CORE

+VCC_EOPIO

+VCC_GTU

+VCC_EDRAM

RUN_ON

(UZ20)

ALWON

+VCC_GT

+VCC_IO

RUN_ON

+1.0V_PRIM

TPS51285B

(PU101)

ENVDD_PCH

G524B1T11U

MXM_ENVDD

(U33)

+VCC_SA

SIO_SLP_S0#

SIO_SLP_S3#

LCD_VCC_TEST_EN

SIO_SLP_S4#

+5V_ALW

SIO_SLP_SUS#

SY8032ABC

(PU900)

+1.8V_ALW

2

AOZ1336

(UZ23)

TPS22961

TPS22961

(UZ18)

SIO_SLP_S4#

SY8003DFC

(PU400)

+2.5V_MEM

RUN_ON

3.3V_RUN_GFX_ON

+1.0V_RUN

+1.0V_VCCSTG(UZ19)

+1.0V_VCCST

EM5209VF

(UZ20)

Left IO Board

USB_PWR_SHR_VBUS_EN

USB1_VBUS_EN

USB2_VBUS_EN

USB3_VBUS_EN

Right IO Board

+5V_RUN

EM5209VF

(UZ26)

SLGC55544CVTR

SLGC55544CVTR

SLGC55544CVTR

SLGC55544CVTR

+1.0V_VCCSFR

(UI1)

(UI1)

(UI3)

(UI5)

1

+5V_HDD

+5V_MXM

+5V_USB_PWR1

+5V_USB_PWR1

+5V_USB_PWR2

+5V_USB_PWR3

RUN_ON

AOZ1336

(UZ22)

+1.8V_RUN

AOZ1336

(UZ31)

+1.2V_RUN

+3.3V_CAM_EN#

LP2301

(Q24)

+CAMERA_VDD

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Power Rail

Power Rail

Power Rail

LA-E311P

LA-E311P

LA-E311P

1

4 71Wednesday, November 23, 2016

4 71Wednesday, November 23, 2016

4 71Wednesday, November 23, 2016

1.0

1.0

1.0

Vinafix.com

5

SMBUS Address [0x9a]

MEM_SMBCLK

AW44

BB43

MEM_SMBDATA

PCH

D D

1D

C C

KBC

AW42AW45

SML1_SMBDATA

SML1_SMBCLK

B6A5

1D

BB39

1A

1A

1C1CB59

1E

1E

AY44

B4

A3

A56

A50

B53

LAN_SMBCLK

LAN_SMBDATA

2.2K

2.2K

DOCK_TNY_SMB_CLK

DOCK_TNY_SMB_DAT

CHARGER_PBAT_SMBCLK

CHARGER_PBAT_SMBDAT

USH_SMBCLK

USH_SMBDAT

+3.3V_ALW_PCH

2.2K

2.2K

4

2.2K

2.2K

2.2K

2.2K

+3.3V_ALW_PCH

+3.3V_LAN

+3.3V_ALW

2.2K

2.2K

28

31

LOM

127

DOCKING

129

L2

K2

+3.3V_ALW

100 ohm

100 ohm

DMN66D0LDW

DMN66D0LDW

SMBUS Address [0xC8]

SMBUS Address

APR_EC: 0x48

SPR_EC: 0x70

MSLICE_EC: 0x72

USB: 0x59

AUDIO: 0x34

SLICE_BATTERY: 0x17

SLICE_CHARGER: 0x13

TYPE C connector

K7

TI PD

L7

AR Chip

TBT DP/B

7

6

12

11

5

6

B6

B7

BATTERY

CONN

Charger

LYNX(CV2)

3

IE/BME

EC

TI PD

AR Chip

SMBUS Address [0x16]

SMBUS Address [0xa4]

2

253

254

253

254

253

254

253

254

53

51

DIMM1

DIMM2

DIMM3

DIMM4

XDP1

SMBUS Address [A0h]

A0h --> 1010 0000

SMBUS Address [A0h]

A0h --> 1010 0000

SMBUS Address [A4h]

A4h --> 1010 0100

SMBUS Address [A4h]

A4h --> 1010 0100

SMBUS Address [TBD]

1

SMBUS Address

SMB_ADM1032: 0x98

SMB_DIAG_DUMP: 0x04

SMB_DIAG_DUMP2: 0x05

SMB_BLACKTOP: 0x60

JTHB1

2.2K

+3.3V_RUN

1

4

2.2K

LNG2DMTR

SMBUS Address [TBD]

MEC 5085

B B

4.7K

+3.3V_TP

B50

A47

B49

UPD_GPU_SMBCLK

B48

UPD_GPU_SMBDAT

I2C_1_SCL_EC

I2C_1_SDA_EC

1G

1G

1H

1H

A A

4.7K

2.2K

2.2K

+3.3V_RUN

DMN66D0LDW

DMN66D0LDW

DMN66D0LDW

DMN66D0LDW

19

18

TP

SMBUS Address [0xFF]

@4.7K

+3.3V_MXM

@4.7K

70

68

MXM

4.7K

4.7K

SMBUS Address [TBD]

+3.3V_TBT_SX

24

UPD

23

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

SMBUS Bolck Diagram

SMBUS Bolck Diagram

SMBUS Bolck Diagram

LA-E311P

LA-E311P

LA-E311P

5 71Wednesday, November 23, 2016

5 71Wednesday, November 23, 2016

5 71Wednesday, November 23, 2016

1

1.0

1.0

1.0

Vinafix.com

5

4

3

2

1

PEG_CRX _C_GTX_P[0..15]

PEG_CRX _C_GTX_N[0..15]

PEG_CTX _C_GRX_P[0..15]

SKYLAKE_HALO

E25

PEG_RXP[0]

D25

PEG_RXN[0]

E24

PEG_RXP[1]

F24

PEG_RXN[1]

E23

PEG_RXP[2]

D23

PEG_RXN[2]

E22

PEG_RXP[3]

F22

PEG_RXN[3]

E21

PEG_RXP[4]

D21

PEG_RXN[4]

E20

PEG_RXP[5]

F20

PEG_RXN[5]

E19

PEG_RXP[6]

D19

PEG_RXN[6]

E18

PEG_RXP[7]

F18

PEG_RXN[7]

D17

PEG_RXP[8]

E17

PEG_RXN[8]

F16

PEG_RXP[9]

E16

PEG_RXN[9]

D15

PEG_RXP[10]

E15

PEG_RXN[10]

F14

PEG_RXP[11]

E14

PEG_RXN[11]

D13

PEG_RXP[12]

E13

PEG_RXN[12]

F12

PEG_RXP[13]

E12

PEG_RXN[13]

D11

PEG_RXP[14]

E11

PEG_RXN[14]

F10

PEG_RXP[15]

E10

PEG_RXN[15]

G2

PEG_RCOMP

D8

DMI_RXP[0]

E8

DMI_RXN[0]

E6

DMI_RXP[1]

F6

DMI_RXN[1]

D5

DMI_RXP[2]

E5

DMI_RXN[2]

J8

DMI_RXP[3]

J9

DMI_RXN[3]

SKL-H_BG A1440

CPU1C

3 OF 14

3

D D

12

PEG_CRX _C_GTX_N15

PEG_CRX _C_GTX_N14

PEG_CRX _C_GTX_N13

PEG_CRX _C_GTX_N12

PEG_CRX _C_GTX_N11

PEG_CRX _C_GTX_P10

PEG_CRX _C_GTX_N10

PEG_CRX _C_GTX_P9

PEG_CRX _C_GTX_N9

5

PEG_CRX _C_GTX_P8

PEG_CRX _C_GTX_N8

PEG_CRX _C_GTX_P7

PEG_CRX _C_GTX_N7

PEG_CRX _C_GTX_P6

PEG_CRX _C_GTX_N6

PEG_CRX _C_GTX_P5

PEG_CRX _C_GTX_N5

PEG_CRX _C_GTX_N4

PEG_CRX _C_GTX_N3

PEG_CRX _C_GTX_N2

PEG_CRX _C_GTX_N1

PEG_CRX _C_GTX_P0

PEG_CRX _C_GTX_N0

+VCC_IO

12

RC224.9_040 2_1%

C C

B B

PEG_COM P

CAD Note:

Trace width=12 mils

,Spacing=15mil

Max length= 400 mils.

A A

CC32 0.22U_0402_10V 6K

12

CC16 0.22U_0402_10V 6K

12

CC31 0.22U_0402_10V 6K

12

CC15 0.22U_0402_10V 6K

12

CC30 0.22U_0402_10V 6K

12

CC14 0.22U_0402_10V 6K

12

CC29 0.22U_0402_10V 6K

12

CC13 0.22U_0402_10V 6K

12

CC28 0.22U_0402_10V 6K

12

CC12 0.22U_0402_10V 6K

12

CC27 0.22U_0402_10V 6K

12

CC11 0.22U_0402_10V 6K

12

CC26 0.22U_0402_10V 6K

12

CC10 0.22U_0402_10V 6K

12

CC25 0.22U_0402_10V 6K

12

CC9 0.22U_04 02_10V6K

12

CC24 0.22U_0402_10V 6K

12

CC8 0.22U_04 02_10V6K

12

CC23 0.22U_0402_10V 6K

12

CC7 0.22U_04 02_10V6K

12

CC22 0.22U_0402_10V 6K

12

CC6 0.22U_04 02_10V6K

12

CC21 0.22U_0402_10V 6K

12

CC5 0.22U_04 02_10V6K

12

CC20 0.22U_0402_10V 6K

12

CC4 0.22U_04 02_10V6K

12

CC19 0.22U_0402_10V 6K

12

CC3 0.22U_04 02_10V6K

12

CC18 0.22U_0402_10V 6K

12

CC2 0.22U_04 02_10V6K

12

CC17 0.22U_0402_10V 6K

12

CC1 0.22U_04 02_10V6K

DMI_CRX_P TX_P0<20>

DMI_CRX_P TX_N0<20>

DMI_CRX_P TX_P1<20>

DMI_CRX_P TX_N1<20>

DMI_CRX_P TX_P2<20>

DMI_CRX_P TX_N2<20>

DMI_CRX_P TX_P3<20>

DMI_CRX_P TX_N3<20>

4

PEG_CRX _GTX_P15PEG_CRX _C_GTX_P15

PEG_CRX _GTX_N15

PEG_CRX _GTX_P14PEG_CRX _C_GTX_P14

PEG_CRX _GTX_N14

PEG_CRX _GTX_P13PEG_CRX _C_GTX_P13

PEG_CRX _GTX_N13

PEG_CRX _GTX_P12PEG_CRX _C_GTX_P12

PEG_CRX _GTX_N12

PEG_CRX _GTX_P11PEG_CRX _C_GTX_P11

PEG_CRX _GTX_N11

PEG_CRX _GTX_P10

PEG_CRX _GTX_N10

PEG_CRX _GTX_P9

PEG_CRX _GTX_N9

PEG_CRX _GTX_P8

PEG_CRX _GTX_N8

PEG_CRX _GTX_P7

PEG_CRX _GTX_N7

PEG_CRX _GTX_P6

PEG_CRX _GTX_N6

PEG_CRX _GTX_P5

PEG_CRX _GTX_N5

PEG_CRX _GTX_P4PEG_C RX_C_GTX_P4

PEG_CRX _GTX_N4

PEG_CRX _GTX_P3PEG_C RX_C_GTX_P3

PEG_CRX _GTX_N3

PEG_CRX _GTX_P2PEG_C RX_C_GTX_P2

PEG_CRX _GTX_N2

PEG_CRX _GTX_P1PEG_C RX_C_GTX_P1

PEG_CRX _GTX_N1

PEG_CRX _GTX_P0

PEG_CRX _GTX_N0

PEG_COM P

DMI_CRX_P TX_P0

DMI_CRX_P TX_N0

DMI_CRX_P TX_P1

DMI_CRX_P TX_P2

DMI_CRX_P TX_N2

DMI_CRX_P TX_P3 DMI_CTX_P RX_P3

DMI_CRX_P TX_N3 DMI_CTX_P RX_N3

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Rev_1.0

PEG_TXP[0]

PEG_TXN[0]

PEG_TXP[1]

PEG_TXN[1]

PEG_TXP[2]

PEG_TXN[2]

PEG_TXP[3]

PEG_TXN[3]

PEG_TXP[4]

PEG_TXN[4]

PEG_TXP[5]

PEG_TXN[5]

PEG_TXP[6]

PEG_TXN[6]

PEG_TXP[7]

PEG_TXN[7]

PEG_TXP[8]

PEG_TXN[8]

PEG_TXP[9]

PEG_TXN[9]

PEG_TXP[10]

PEG_TXN[10]

PEG_TXP[11]

PEG_TXN[11]

PEG_TXP[12]

PEG_TXN[12]

PEG_TXP[13]

PEG_TXN[13]

PEG_TXP[14]

PEG_TXN[14]

PEG_TXP[15]

PEG_TXN[15]

DMI_TXP[0]

DMI_TXN[0]

DMI_TXP[1]

DMI_TXN[1]

DMI_TXP[2]

DMI_TXN[2]

DMI_TXP[3]

DMI_TXN[3]

PEG_CTX _GRX_P15

B25

PEG_CTX _GRX_N15

A25

PEG_CTX _GRX_P14

B24

PEG_CTX _GRX_N14

C24

PEG_CTX _GRX_P13

B23

PEG_CTX _GRX_N13

A23

PEG_CTX _GRX_P12

B22

PEG_CTX _GRX_N12

C22

PEG_CTX _GRX_P11

B21

PEG_CTX _GRX_N11

A21

PEG_CTX _GRX_P10

B20

PEG_CTX _GRX_N10

C20

PEG_CTX _GRX_P9 PEG_CTX _C_GRX_P9

B19

A19

PEG_CTX _GRX_P8

B18

PEG_CTX _GRX_N8

C18

PEG_CTX _GRX_P7

A17

PEG_CTX _GRX_N7

B17

PEG_CTX _GRX_P6

C16

PEG_CTX _GRX_N6

B16

PEG_CTX _GRX_P5 PEG_CTX _C_GRX_P5

A15

B15

PEG_CTX _GRX_P4

C14

PEG_CTX _GRX_N4

B14

PEG_CTX _GRX_P3 PEG_CTX _C_GRX_P3

A13

PEG_CTX _GRX_N3 PEG_CTX_C _GRX_N3

B13

PEG_CTX _GRX_P2

C12

PEG_CTX _GRX_N2

B12

PEG_CTX _GRX_P1

A11

PEG_CTX _GRX_N1

B11

PEG_CTX _GRX_P0

C10

PEG_CTX _GRX_N0

B10

B8

A8

C6

B6

B5

A5

D4

B4

DMI_CTX_P RX_P0

DMI_CTX_P RX_N0

DMI_CTX_P RX_P1

DMI_CTX_P RX_N1DMI_CRX_P TX_N1

DMI_CTX_P RX_P2

DMI_CTX_P RX_N2

2

PEG_CTX _C_GRX_N[0..15]

12

CC64 0.22U_0402_10V 6K

12

CC50 0.22U_0402_10V 6K

12

CC63 0.22U_0402_10V 6K

12

CC77 0.22U_0402_10V 6K

12

CC72 0.22U_0402_10V 6K

12

CC62 0.22U_0402_10V 6K

12

CC61 0.22U_0402_10V 6K

12

CC49 0.22U_0402_10V 6K

12

CC60 0.22U_0402_10V 6K

12

CC76 0.22U_0402_10V 6K

12

CC71 0.22U_0402_10V 6K

12

CC59 0.22U_0402_10V 6K

12

CC58 0.22U_0402_10V 6K

12

CC48 0.22U_0402_10V 6K

12

CC57 0.22U_0402_10V 6K

12

CC75 0.22U_0402_10V 6K

12

CC70 0.22U_0402_10V 6K

12

CC56 0.22U_0402_10V 6K

12

CC55 0.22U_0402_10V 6K

12

CC47 0.22U_0402_10V 6K

12

CC54 0.22U_0402_10V 6K

12

CC74 0.22U_0402_10V 6K

12

CC69 0.22U_0402_10V 6K

12

CC46 0.22U_0402_10V 6K

12

CC52 0.22U_0402_10V 6K

12

CC73 0.22U_0402_10V 6K

12

CC51 0.22U_0402_10V 6K

12

CC53 0.22U_0402_10V 6K

12

CC68 0.22U_0402_10V 6K

12

CC45 0.22U_0402_10V 6K

12

CC67 0.22U_0402_10V 6K

12

CC44 0.22U_0402_10V 6K

DMI_CTX_P RX_P0 <20>

DMI_CTX_P RX_N0 <20>

DMI_CTX_P RX_P1 <20>

DMI_CTX_P RX_N1 <20>

DMI_CTX_P RX_P2 <20>

DMI_CTX_P RX_N2 <20>

DMI_CTX_P RX_P3 <20>

DMI_CTX_P RX_N3 <20>

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Docu ment Number Rev

Size Docu ment Number Rev

Size Docu ment Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

SKYLAKE-H (1/8)

SKYLAKE-H (1/8)

SKYLAKE-H (1/8)

PEG_CRX _C_GTX_P[0..15] <18>

PEG_CRX _C_GTX_N[0..15] <18>

PEG_CTX _C_GRX_P[0..15] <18>

PEG_CTX _C_GRX_N[0..15] <18>

PEG_CTX _C_GRX_P15

PEG_CTX _C_GRX_N15

PEG_CTX _C_GRX_P14

PEG_CTX _C_GRX_N14

PEG_CTX _C_GRX_P13

PEG_CTX _C_GRX_N13

PEG_CTX _C_GRX_P12

PEG_CTX _C_GRX_N12

PEG_CTX _C_GRX_P11

PEG_CTX _C_GRX_N11

PEG_CTX _C_GRX_P10

PEG_CTX _C_GRX_N10

PEG_CTX _C_GRX_N9PEG_CTX _GRX_N9

PEG_CTX _C_GRX_P8

PEG_CTX _C_GRX_N8

PEG_CTX _C_GRX_P7

PEG_CTX _C_GRX_N7

PEG_CTX _C_GRX_P6

PEG_CTX _C_GRX_N6

PEG_CTX _C_GRX_N5PEG_CTX _GRX_N5

PEG_CTX _C_GRX_P4

PEG_CTX _C_GRX_N4

PEG_CTX _C_GRX_P2

PEG_CTX _C_GRX_N2

PEG_CTX _C_GRX_P1

PEG_CTX _C_GRX_N1

PEG_CTX _C_GRX_P0

PEG_CTX _C_GRX_N0

LA-E311P

LA-E311P

LA-E311P

1

1.0

1.0

6 71Wednesd ay, November 23, 201 6

6 71Wednesd ay, November 23, 201 6

6 71Wednesd ay, November 23, 201 6

1.0

Vinafix.com

5

+1.0V_PRIM

D D

RC216 0_0603_1%@

1 2

+1.0V_PRIM_XDP

0.1U_0402_25V6

12

+1.0V_PRIM_XDP

0.1U_0402_25V6

@

12

CC37

@

CC33

Place near JXDP1

XDP@

PCH_RSMRST#_R H_VCCST_PWRGD_XDP

@

T191

PAD~D

SIO_PWRBTN#<23,48>

RESET_OUT#<23,48>

H_PROCHOT#

PCH_THERMTRIP#

PCH_JTAGX

VCCST_PWRGD

H_CATERR#

+1.0V_VCCST

56.2_0402_1%

12

RC155

220_0402_5%

12

RC156

SN74AHC1G08DCKR _SC70-5

5

CFG0

12

VR_SVID_DATA

CPU_VIDALERT#

RC327 0 _0402_5%@

UC5

PCH_SPI_D0<22,39>

+1.0V_PRIM_XDP

+VCC_IO

+1.0V_VCCSTG

C C

RC180 1K_0402_5%

+1.0V_VCCST

B B

VR_SVID_DATA<63,66>

VR_SVID_ALERT#<63,66>

A A

1 2

CPU_XDP_PREQ#

12

RC13851_0402_ 5% @

FIVR_EN_R

12

RC132150_0402_5%

12

RC3261K_ 0402_5%

12

RC1661K_ 0402_5% @

12

RC1641K_0402_5%

12

RC17249.9_0402_1% @

VR_SVID_DATA

VR_SVID_ALERT#

IMVP_VR_ON_EC<48>

SIO_SLP_S3#<11,23,39,46,48>

100_0402_5%

RC157

+3.3V_ALW

1

2

PCH_JTAG_TCK<23>

1 2

5

P

IN1

IN2

G

3

1 2

RC124

1K_0402_5%

1 2

RC217 0 _0402_5%@

RC126 1 K_0402_5%XDP@

1 2

1 2

RC128 0 _0402_5%XDP@

1 2

RC129 0 _0402_5%@

DDR_XDP_WAN_SMBDAT<14,15,16,17,23,43>

DDR_XDP_WAN_SMBCLK<14,15,16,17,23,43>

PCH_RSMRST#

PCH_RSMRST#<48>

ALW_PWRGD_3V_5V<53>

VR_SVID_CLK<63,66>

H_PROCHOT#<48,59,63,66>

DDR_PG_CTRL<14>

VCCST_PWRGD<48>

H_PWRGD<23>

PLTRST_CPU#<19>

H_PM_SYNC<19>

H_PM_DOWN<19>

H_PECI<19,48>

PCH_THERMTRIP#<14,15,16,17,19,48>

IMVP_VR_ON

4

O

IMVP_VR_ON <57,58,63,66>

CPU_XDP_PREQ#

CPU_XDP_PRDY#

CFG0

CFG1

CFG2

CFG3

XDP_OBS0_R

XDP_OBS1_R

CFG4

CFG5

CFG6

CFG7

SIO_PWRBTN#

FIVR_EN_R

SYS_PWROK_R

PCH_JTAG_TCK

CPU_XDP_TCLK

PCH_CPU_BCLK_R_D<21>

PCH_CPU_BCLK_R_D#<21>

PCH_CPU_PCIBCLK_R_D<21>

PCH_CPU_PCIBCLK_R_D#<21>

CPU_24MHZ_R_D<21>

CPU_24MHZ_R_D#<21>

VR_SVID_CLK

DDR_PG_CTRL

H_PWRGD

PLTRST_CPU#

H_PECI

UC6

NC1VCC

2

A

3

GND

74AUP1G07GW_TSSO P5

4

+1.0V_PRIM_XDP

XDP_PRSNT_PIN1

JXDP1

1

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

OBSDATA_A09OBSDATA_C0

OBSDATA_A111OBSDATA_C1

13

GND4

OBSDATA_A215OBSDATA_C2

OBSDATA_A317OBSDATA_C3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

OBSDATA_B027OBSDATA_D0

OBSDATA_B129OBSDATA_D1

31

GND10

OBSDATA_B233OBSDATA_D2

OBSDATA_B335OBSDATA_D3

37

GND12

PWRGOOD/HOOK039ITPCLK/HOOK4

41

HOOK1

VCC_OBS_AB43VCC_OBS_CD

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

+3.3V_ALW

CC274

1 2

0.1U_0402_25V6K

UC4

5

SN74AHC1G08DCKR _SC70-5

1

P

IN1

4

O

2

IN2

G

3

PCH_CPU_BCLK_R_D

PCH_CPU_BCLK_R_D #

PCH_CPU_PCIBCLK_R_ D

PCH_CPU_PCIBCLK_R_ D#

CPU_24MHZ_R_D

CPU_24MHZ_R_D#

1 2

RC158 4 99_0402_1%

1 2

RC159 60.4_0 402_1%

1 2

RC168 2 0_0402_5%

1 2

RC169 0_0402_5%@

1 2

1 2

RC319 0 _0402_5%@

RC171 0 _0402_5%@

+3.3V_ALW

5

VCCST_PWRGD

4

Y

4

CPU XDP

XDP@

1 2

CFG3

GND1

OBSFN_C0

OBSFN_C1

GND3

GND5

GND7

OBSFN_D0

OBSFN_D1

GND9

GND11

GND13

ITPCLK#/HOOK5

RESET#/HOOK6

DBR#/HOOK7

GND15

TRST#

GND17

CONN@SAMTE_BSH-030-01-L-D -A

1 2

RC154 0_0402_5%@

TD0

TDI

TMS

BH31

BH32

BH29

BR30

BT13

BT31

BP35

BM34

BP31

BT34

BR33

BM30

B31

A32

D35

C36

E31

D31

H13

J31

BN1

+1.0V_PRIM_XDP

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

CPU1E

BCLKP

BCLKN

PCI_BCLKP

PCI_BCLKN

CLK24P

CLK24N

VIDALERT#

VIDSCK

VIDSOUT

PROCHOT#

DDR_VTT_CNTL

VCCST_PWRGD

PROCPWRGD

RESET#

PM_SYNC

PM_DOWN

PECI

THERMTRIP#

SKTOCC#

PROC_SELECT#

CATERR#

SKL-H_BGA1440

CFG17

CFG16

CFG8

CFG9

CFG10

CFG11

CFG19

CFG18

CFG12

CFG13

CFG14

CFG15

PCH_XDP_CLK_DP

PCH_XDP_CLK_DN

CPU_XDP_HOOK6

XDP_DBRESET#

CPU_XDP_TDO

CPU_XDP_TRST#

CPU_XDP_TDI

CPU_XDP_TMS

CPU_XDP_PRS

12

SKYLAKE_HALO

RC121 1K_0402_5%

1 2

RC122 0_0402_5%@

PM_RSMRST#_AND PCH_RSMRST#_R

CPU_VIDALERT#

VR_SVID_DATA

H_PROCHOT#_RH_PROCHOT#

VCCST_PWRGD_C PUVCC ST_PWRGD

H_PM_SYNC

H_PM_DOWN_RH_PM_DOWN

H_THERMTRIP#PCH_THERM TRIP#

H_SKTOCC#

SKL_CNL#

H_CATERR#

RC318

10K_0402_5%

5 OF 14

3

PCH_XDP_CLK_DP <21>

PCH_XDP_CLK_DN <21>

1 2

RC144 0 _0402_5%XDP@

XDP_DBRESET# <23>

CPU_XDP_TRST# <25>

1 2

RC127 1 K_0402_5%XDP@

PCH_RSMRST#_R <23>

Rev_1.0

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[17]

CFG[16]

CFG[19]

CFG[18]

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

PROC_TDO

PROC_TDI

PROC_TMS

PROC_TCK

PROC_TRST#

PROC_PREQ#

PROC_PRDY#

CFG_RCOMP

3

ITP_PMODE_CPU

PCH_SPI_D2_XDP

Place near JXDP1.41

BN25

BN27

BN26

BN28

BR20

BM20

BT20

BP20

BR23

BR22

BT23

BT22

BM19

BR19

BP19

BT19

BN23

BP23

BP22

BN22

BR27

BT27

BM31

BT30

BT28

BL32

BP28

BR28

BP30

BL30

BP27

BT25

2

CPU_XDP_HOOK6

XDP_DBRESET#

PCH_SPI_D0

ITP_PMODE_CPU <23>

PCH_SPI_D2_XDP <22>

+3.3V_ALW

1.5K_0402_5%

XDP@

12

RC241

SIO_PWRBTN#

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG17

CFG16

CFG19

CFG18

XDP_OBS0

XDP_OBS1

CPU_XDP_TDO

CPU_XDP_TDI

CPU_XDP_TMS

CPU_XDP_TCLK

CPU_XDP_TRST#

CPU_XDP_PREQ#

CPU_XDP_PRDY#

12

0.1U_0402_25V6

XDP@

12

CC269

CPU_XDP_TDO

CPU_XDP_TRST#

CPU_XDP_TCLK

CPU_XDP_TMS

CPU_XDP_TDI

CPU_XDP_TDO

CPU_XDP_TCLK

CPU_XDP_PREQ#

CPU_XDP_PRDY#

8/22

1 2

1 2

RC312 0_04 02_5%@

RC313 0_04 02_5%@

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

RC222

49.9_0402_1%

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

XDP_OBS0_R

XDP_OBS1_R

@

T184

@

T185

@

T180

@

T181

@

T179

@

T190

@

T189

RC307 0_0402_5%@

RC308 0_0402_5%@

RC309 0_0402_5%@

RC143 0_0402_5%@

RC315 0_0402_5%XDP@

RC314 0_0402_5%XDP@

RC6 2.2K_0 402_5%XDP@

RC316 3 K_0402_5%

RC133 1 .5K_0402_5%XDP@

1 2

1 2

1 2

1 2

1 2

1 2

1 2

8/24

1 2

1 2

2

12

12

12

+1.0V_PRIM_XDP

+3.3V_ALW_PCH

+1.0V_VCCSTG

RC13551_0402_5%

RC33051_0402_5% @

RC30651_0402_5%

PCH_JTAG_TMS <23>

PCH_JTAG_TDI <23>

PCH_JTAG_TDO <23>

PCH_JTAGX <23>

PCH_XDP_PREQ# <25>

PCH_XDP_PRDY# <25>

XDP_DBRESET#

RC143 for XDP debug

1

0.1U_0402_25V6

XDP@

CC35

12

SYS_PWROK_R

0.1U_0402_25V6

12

CC36@

Place near JXDP1.47

CFG0

CFG2

CFG4

CFG5

CFG6

CFG7

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Stall reset sequence after PCU

12

PLL lock until de-asserted

RC321

@

1K_0402_5%

No Stall

Stall

12

PEG LANE REVERSAL

RC181

1K_0402_5%

*

12

RC322

1K_0402_5%

PCI Express* Bifurcation

12

RC323

@

1K_0402_5%

1x8, 2x4

Reserved

2x8

RC324

@

1K_0402_5%

1x16

PEG Training

(default) PEG Train

immediately following

RESET# de-assertion

PEG Wait for BIOS for

training

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SKYLAKE-H (2/8)

SKYLAKE-H (2/8)

SKYLAKE-H (2/8)

LA-E311P

LA-E311P

LA-E311P

1

12

12

RC325

@

1K_0402_5%

NORMAL

LANE

REVERSED

eDP enable

Disabled

Enabled

1

0

1

0

1

0

[6:5]

00

01

10

11

1

0

7 71Wednesday, November 23, 2016

7 71Wednesday, November 23, 2016

7 71Wednesday, November 23, 2016

1.0

1.0

1.0

Vinafix.com

5

4

3

2

1

DDR_A_D[0..63]<14,15>

D D

C C

DDR_A_CB[0..7]<14,15>

B B

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_A_CB0

DDR_A_CB1

DDR_A_CB2

DDR_A_CB3

DDR_A_CB4

DDR_A_CB5

DDR_A_CB6

DDR_A_CB7

CPU1A

BR6

DDR0_DQ[0]

BT6

DDR0_DQ[1]

BP3

DDR0_DQ[2]

BR3

DDR0_DQ[3]

BN5

DDR0_DQ[4]

BP6

DDR0_DQ[5]

BP2

DDR0_DQ[6]

BN3

DDR0_DQ[7]

BL4

DDR0_DQ[8]

BL5

DDR0_DQ[9]

BL2

DDR0_DQ[10]

BM1

DDR0_DQ[11]

BK4

DDR0_DQ[12]

BK5

DDR0_DQ[13]

BK1

DDR0_DQ[14]

BK2

DDR0_DQ[15]

Interleave / Non-Interleaved

BG4

DDR0_DQ[16]/DDR0_DQ[32]

BG5

DDR0_DQ[17]/DDR0_DQ[33]

BF4

DDR0_DQ[18]/DDR0_DQ[34]

BF5

DDR0_DQ[19]/DDR0_DQ[35]

BG2

DDR0_DQ[20]/DDR0_DQ[36]

BG1

DDR0_DQ[21]/DDR0_DQ[37]

BF1

DDR0_DQ[22]/DDR0_DQ[38]

BF2

DDR0_DQ[23]/DDR0_DQ[39]

BD2

DDR0_DQ[24]/DDR0_DQ[40]

BD1

DDR0_DQ[25]/DDR0_DQ[41]

BC4

DDR0_DQ[26]/DDR0_DQ[42]

BC5

DDR0_DQ[27]/DDR0_DQ[43]

BD5

DDR0_DQ[28]/DDR0_DQ[44]

BD4

DDR0_DQ[29]/DDR0_DQ[45]

BC1

DDR0_DQ[30]/DDR0_DQ[46]

BC2

DDR0_DQ[31]/DDR0_DQ[47]

AB1

DDR0_DQ[32]/DDR1_DQ[0]

AB2

DDR0_DQ[33]/DDR1_DQ[1]

AA4

DDR0_DQ[34]/DDR1_DQ[2]

AA5

DDR0_DQ[35]/DDR1_DQ[3]

AB5

DDR0_DQ[36]/DDR1_DQ[4]

AB4

DDR0_DQ[37]/DDR1_DQ[5]

AA2

DDR0_DQ[38]/DDR1_DQ[6]

AA1

DDR0_DQ[39]/DDR1_DQ[7]

V5

DDR0_DQ[40]/DDR1_DQ[8]

V2

DDR0_DQ[41]/DDR1_DQ[9]

U1

DDR0_DQ[42]/DDR1_DQ[10]

U2

DDR0_DQ[43]/DDR1_DQ[11]

V1

DDR0_DQ[44]/DDR1_DQ[12]

V4

DDR0_DQ[45]/DDR1_DQ[13]

U5

DDR0_DQ[46]/DDR1_DQ[14]

U4

DDR0_DQ[47]/DDR1_DQ[15]

R2

DDR0_DQ[48]/DDR1_DQ[32]

P5

DDR0_DQ[49]/DDR1_DQ[33]

R4

DDR0_DQ[50]/DDR1_DQ[34]

P4

DDR0_DQ[51]/DDR1_DQ[35]

R5

DDR0_DQ[52]/DDR1_DQ[36]

P2

DDR0_DQ[53]/DDR1_DQ[37]

R1

DDR0_DQ[54]/DDR1_DQ[38]

P1

DDR0_DQ[55]/DDR1_DQ[39]

M4

DDR0_DQ[56]/DDR1_DQ[40]

M1

DDR0_DQ[57]/DDR1_DQ[41]

L4

DDR0_DQ[58]/DDR1_DQ[42]

L2

DDR0_DQ[59]/DDR1_DQ[43]

M5

DDR0_DQ[60]/DDR1_DQ[44]

M2

DDR0_DQ[61]/DDR1_DQ[45]

L5

DDR0_DQ[62]/DDR1_DQ[46]

L1

DDR0_DQ[63]/DDR1_DQ[47]

BA2

DDR0_ECC[0]

BA1

DDR0_ECC[1]

AY4

DDR0_ECC[2]

AY5

DDR0_ECC[3]

BA5

DDR0_ECC[4]

BA4

DDR0_ECC[5]

AY1

DDR0_ECC[6]

AY2

DDR0_ECC[7]

SKL-H_BGA1440

SKYLAKE_HALO

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[ 0]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[ 1]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[ 2]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[ 5]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[ 6]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[ 7]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[ 8]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[ 9]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[ 10]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[ 11]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[ 12]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[ 13]

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT #

DDR CH - A

1 OF 14

DDR0_CKP[0]

DDR0_CKN[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CLKP[2]

DDR0_CLKN[2]

DDR0_CLKP[3]

DDR0_CLKN[3]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_CS#[2]

DDR0_CS#[3]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_ODT[2]

DDR0_ODT[3]

DDR3L / LPDDR3 / DDR4

DDR0_MA[3]

DDR0_MA[4]

DDR0_ALERT#

DDR0_DQSN[0]

DDR0_DQSN[1]

Interleave / Non-Interleaved

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR0_DQSP[0]

DDR0_DQSP[1]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[8]

DDR0_DQSN[8]

Rev_1.0

DDR0_PAR

DDR_A_CLK0 DDR_B_CLK#0

AG1

DDR_A_CLK#0

AG2

DDR_A_CLK#1 DDR_B_CLK1

AK1

DDR_A_CLK1

AK2

DDR_A_CLK2

AL3

DDR_A_CLK#2

AK3

DDR_A_CLK3

AL2

DDR_A_CLK#3

AL1

DDR_A_CKE0

AT1

DDR_A_CKE1

AT2

DDR_A_CKE2

AT3

DDR_A_CKE3

AT5

DDR_A_CS#0

AD5

DDR_A_CS#1

AE2

DDR_A_CS#2

AD2

DDR_A_CS#3

AE5

DDR_A_ODT0

AD3

DDR_A_ODT1

AE4

DDR_A_ODT2

AE1

DDR_A_ODT3

AD4

DDR_A_BA0

AH5

DDR_A_BA1

AH1

DDR_A_BG0

AU1

DDR_A_MA16

AH4

DDR_A_MA14

AG4

DDR_A_MA15

AD1

DDR_A_MA0

AH3

DDR_A_MA1

AP4

DDR_A_MA2

AN4

DDR_A_MA3

AP5

DDR_A_MA4

AP2

DDR_A_MA5

AP1

DDR_A_MA6

AP3

DDR_A_MA7

AN1

DDR_A_MA8

AN3

DDR_A_MA9

AT4

DDR_A_MA10

AH2

DDR_A_MA11

AN2

DDR_A_MA12

AU4

DDR_A_MA13

AE3

DDR_A_BG1

AU2

DDR_A_ACT#

AU3

DDR_A_PARITY

AG3

DDR_A_ALERT#

AU5

DDR_A_DQS#0

BR5

DDR_A_DQS#1

BL3

DDR_A_DQS#2

BG3

DDR_A_DQS#3

BD3

DDR_A_DQS4

AB3

DDR_A_DQS5

V3

DDR_A_DQS6

R3

DDR_A_DQS7

M3

DDR_A_DQS0

BP5

DDR_A_DQS1

BK3

DDR_A_DQS2

BF3

DDR_A_DQS3

BC3

DDR_A_DQS#4

AA3

DDR_A_DQS#5

U3

DDR_A_DQS#6

P3

DDR_A_DQS#7

L3

DDR_A_DQS8

AY3

DDR_A_DQS#8

BA3

DDR_A_CLK0 <15>

DDR_A_CLK#0 <15>

DDR_A_CLK#1 <15>

DDR_A_CLK1 <15>

DDR_A_CLK2 <14>

DDR_A_CLK#2 <14>

DDR_A_CLK3 <14>

DDR_A_CLK#3 <14>

DDR_A_CKE0 <15>

DDR_A_CKE1 <15>

DDR_A_CKE2 <14>

DDR_A_CKE3 <14>

DDR_A_CS#0 <15>

DDR_A_CS#1 <15>

DDR_A_CS#2 <14>

DDR_A_CS#3 <14>

DDR_A_ODT0 <15>

DDR_A_ODT1 <15>

DDR_A_ODT2 <14>

DDR_A_ODT3 <14>

DDR_A_BA0 <14,15>

DDR_A_BA1 <14,15>

DDR_A_BG0 <14,15>

DDR_A_MA16 < 14,15>

DDR_A_MA14 < 14,15>

DDR_A_MA15 < 14,15>

DDR_A_MA[0..13] <14,15>

DDR_A_BG1 <14,15>

DDR_A_ACT# <14,15>

DDR_A_PARITY < 14,15>

DDR_A_ALERT# <14,15>

DDR_A_DQS#[0..3] <14,15>

DDR_A_DQS[4..7] <14,15>

DDR_A_DQS[0..3] <14,15>

DDR_A_DQS#[4..7] <14,15>

DDR_A_DQS8 <14,15>

DDR_A_DQS#8 <14,15>

DDR_B_D[0..63]<16,17>

DDR_B_CB[0..7]<16,17>

1 2

1 2

RD18 121_0402_1%

1 2

RD21 75_0402_1%

RD22 100_0402_1%

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_CB0

DDR_B_CB1

DDR_B_CB2

DDR_B_CB3

DDR_B_CB4

DDR_B_CB5

DDR_B_CB6

DDR_B_CB7

DDR_RCOMP0

DDR_RCOMP1

DDR_RCOMP2

CPU1B

Interleave / Non-Interleaved

BT11

DDR1_DQ[0]/DDR0_DQ[16]

BR11

DDR1_DQ[1]/DDR0_DQ[17]

BT8

DDR1_DQ[2]/DDR0_DQ[18]

BR8

DDR1_DQ[3]/DDR0_DQ[19]

BP11

DDR1_DQ[4]/DDR0_DQ[20]

BN11

DDR1_DQ[5]/DDR0_DQ[21]

BP8

DDR1_DQ[6]/DDR0_DQ[22]

BN8

DDR1_DQ[7]/DDR0_DQ[23]

BL12

DDR1_DQ[8]/DDR0_DQ[24]

BL11

DDR1_DQ[9]/DDR0_DQ[25]

BL8

DDR1_DQ[10]/DDR0_DQ[26]

BJ8

DDR1_DQ[11]/DDR0_DQ[27]

BJ11

DDR1_DQ[12]/DDR0_DQ[28]

BJ10

DDR1_DQ[13]/DDR0_DQ[29]

BL7

DDR1_DQ[14]/DDR0_DQ[30]

BJ7

DDR1_DQ[15]/DDR0_DQ[31]

BG11

DDR1_DQ[16]/DDR0_DQ[48]

BG10

DDR1_DQ[17]/DDR0_DQ[49]

BG8

DDR1_DQ[18]/DDR0_DQ[50]

BF8

DDR1_DQ[19]/DDR0_DQ[51]

BF11

DDR1_DQ[20]/DDR0_DQ[52]

BF10

DDR1_DQ[21]/DDR0_DQ[53]

BG7

DDR1_DQ[22]/DDR0_DQ[54]

BF7

DDR1_DQ[23]/DDR0_DQ[55]

BB11

DDR1_DQ[24]/DDR0_DQ[56]

BC11

DDR1_DQ[25]/DDR0_DQ[57]

BB8

DDR1_DQ[26]/DDR0_DQ[58]

BC8

DDR1_DQ[27]/DDR0_DQ[59]

BC10

DDR1_DQ[28]/DDR0_DQ[60]

BB10

DDR1_DQ[29]/DDR0_DQ[61]

BC7

DDR1_DQ[30]/DDR0_DQ[62]

BB7

DDR1_DQ[31]/DDR0_DQ[63]

AA11

DDR1_DQ[32]/DDR1_DQ[16]

AA10

DDR1_DQ[33]/DDR1_DQ[17]

AC11

DDR1_DQ[34]/DDR1_DQ[18]

AC10

DDR1_DQ[35]/DDR1_DQ[19]

AA7

DDR1_DQ[36]/DDR1_DQ[20]

AA8

DDR1_DQ[37]/DDR1_DQ[21]

AC8

DDR1_DQ[38]/DDR1_DQ[22]

AC7

DDR1_DQ[39]/DDR1_DQ[23]

W8

DDR1_DQ[40]/DDR1_DQ[24]

W7

DDR1_DQ[41]/DDR1_DQ[25]

V10

DDR1_DQ[42]/DDR1_DQ[26]

V11

DDR1_DQ[43]/DDR1_DQ[27]

W11

DDR1_DQ[44]/DDR1_DQ[28]

W10

DDR1_DQ[45]/DDR1_DQ[29]

V7

DDR1_DQ[46]/DDR1_DQ[30]

V8

DDR1_DQ[47]/DDR1_DQ[31]

R11

DDR1_DQ[48]

P11

DDR1_DQ[49]

P7

DDR1_DQ[50]

R8

DDR1_DQ[51]

R10

DDR1_DQ[52]

P10

DDR1_DQ[53]

R7

DDR1_DQ[54]

P8

DDR1_DQ[55]

L11

DDR1_DQ[56]

M11

DDR1_DQ[57]

L7

DDR1_DQ[58]

M8

DDR1_DQ[59]

L10

DDR1_DQ[60]

M10

DDR1_DQ[61]

M7

DDR1_DQ[62]

L8

DDR1_DQ[63]

AW11

DDR1_ECC[0]

AY11

DDR1_ECC[1]

AY8

DDR1_ECC[2]

AW8

DDR1_ECC[3]

AY10

DDR1_ECC[4]

AW10

DDR1_ECC[5]

AY7

DDR1_ECC[6]

AW7

DDR1_ECC[7]

G1

DDR_RCOMP[0]

H1

DDR_RCOMP[1]

J2

DDR_RCOMP[2]

SKL-H_BGA1440

SKYLAKE_HALO

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[ 0]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[ 1]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[ 2]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[ 5]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[ 6]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[ 7]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[ 8]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[ 9]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[ 10]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[ 11]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[ 12]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[ 13]

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT #

DDR CH - B

2 OF 14

DDR1_CKP[0]

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[1]

DDR1_CLKP[2]

DDR1_CLKN[2]

DDR1_CLKP[3]

DDR1_CLKN[3]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_CS#[2]

DDR1_CS#[3]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_ODT[2]

DDR1_ODT[3]

DDR3L / LPDDR3 / DDR4

DDR1_MA[3]

DDR1_MA[4]

DDR1_ALERT#

Interleave / Non-Interleaved

DDR1_DQSN[0]/DDR0_DQSN[2]

DDR1_DQSN[1]/DDR0_DQSN[3]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSN[6]

DDR1_DQSN[7]

DDR1_DQSP[0]/DDR0_DQSP[2]

DDR1_DQSP[1]/DDR0_DQSP[3]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR1_DQSP[6]

DDR1_DQSP[7]

DDR1_DQSP[8]

DDR1_DQSN[8]

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

Rev_1.0

DDR1_PAR

AM9

AN9

AM8

AM7

AM11

AM10

AJ10

AJ11

AT8

AT10

AT7

AT11

AF11

AE7

AF10

AE10

AF7

AE8

AE9

AE11

AH10

AH11

AF8

AH8

AH9

AR9

AJ9

AK6

AK5

AL5

AL6

AM6

AN7

AN10

AN8

AR11

AH7

AN11

AR10

AF9

AR7

AT9

AJ7

AR8

BP9

BL9

BG9

BC9

AC9

W9

R9

M9

BR9

BJ9

BF9

BB9

AA9

V9

P9

L9

AW9

AY9

BN13

BP13

BR13

DDR_B_CLK0

DDR_B_CLK#1

DDR_B_CLK2

DDR_B_CLK#2

DDR_B_CLK3

DDR_B_CLK#3

DDR_B_CKE0

DDR_B_CKE1

DDR_B_CKE2

DDR_B_CKE3

DDR_B_CS#0

DDR_B_CS#1

DDR_B_CS#2

DDR_B_CS#3

DDR_B_ODT0

DDR_B_ODT1

DDR_B_ODT2

DDR_B_ODT3

DDR_B_MA16

DDR_B_MA14

DDR_B_MA15

DDR_B_BA0

DDR_B_BA1

DDR_B_BG0

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_BG1

DDR_B_ACT#

DDR_B_PARITY

DDR_B_ALERT#

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS8

DDR_B_DQS#8

DDR_B_CLK0 <17>

DDR_B_CLK#0 <17>

DDR_B_CLK#1 <17>

DDR_B_CLK1 <17>

DDR_B_CLK2 <16>

DDR_B_CLK#2 <16>

DDR_B_CLK3 <16>

DDR_B_CLK#3 <16>

DDR_B_CKE0 <17>

DDR_B_CKE1 <17>

DDR_B_CKE2 <16>

DDR_B_CKE3 <16>

DDR_B_CS#0 <17>

DDR_B_CS#1 <17>

DDR_B_CS#2 <16>

DDR_B_CS#3 <16>

DDR_B_ODT0 <17>

DDR_B_ODT1 <17>

DDR_B_ODT2 <16>

DDR_B_ODT3 <16>

DDR_B_MA16 <16,17>

DDR_B_MA14 <16,17>

DDR_B_MA15 <16,17>

DDR_B_BA0 <16,17>

DDR_B_BA1 <16,17>

DDR_B_BG0 <16,17>

DDR_B_BG1 <16,17>

DDR_B_ACT# <16,17>

DDR_B_PARITY <16,17>

DDR_B_ALERT# <16,17>

DDR_B_DQS8 <16,17>

DDR_B_DQS#8 <16,17>

+DDR_VREF_CA

@

T199

PAD~D

+DDR_VREF_B_DQ

DDR_B_MA[0..13] <16,17>

DDR_B_DQS#[0..7] <16,17>

DDR_B_DQS[0..7] <16,17>

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

SKYLAKE-H (3/8)

SKYLAKE-H (3/8)

SKYLAKE-H (3/8)

LA-E311P

LA-E311P

LA-E311P

8 71Wednesday, November 23, 2016

8 71Wednesday, November 23, 2016

8 71Wednesday, November 23, 2016

1

1.0

1.0

1.0

Vinafix.com

5

CPU_DP1_P0<31>

CPU_DP1_N0<31>

CPU_DP1_P1<31>

Dock Port1

D D

TBT

C C

mDP/TBT

CPU_DP1_P2<31>

CPU_DP1_N2<31>

CPU_DP1_P3<31>

CPU_DP1_N3<31>

CPU_DP1_AUXP<31>

CPU_DP1_AUXN<31>

CPU_DP2_P0<34>

CPU_DP2_N0<34>

CPU_DP2_P1<34>

CPU_DP2_N1<34>

CPU_DP2_P2<34>

CPU_DP2_N2<34>

CPU_DP2_P3<34>

CPU_DP2_N3<34>

CPU_DP2_AUXP<34>

CPU_DP2_AUXN<34>

CPU_DP3_P0<33>

CPU_DP3_N0<33>

CPU_DP3_P1<33>

CPU_DP3_N1<33>

CPU_DP3_P2<33>

CPU_DP3_N2<33>

CPU_DP3_P3<33>

CPU_DP3_N3<33>

CPU_DP3_AUXP<33>

CPU_DP3_AUXN<33>

4

CPU_DP1_P0

CPU_DP1_N0

CPU_DP1_P1

CPU_DP1_P2

CPU_DP1_N2

CPU_DP1_P3

CPU_DP1_N3

CPU_DP1_AUXP

CPU_DP1_AUXN

CPU_DP2_P0

CPU_DP2_N0

CPU_DP2_P1

CPU_DP2_N1

CPU_DP2_P2

CPU_DP2_N2

CPU_DP2_P3

CPU_DP2_N3

CPU_DP2_AUXP

CPU_DP2_AUXN

CPU_DP3_P0

CPU_DP3_N0

CPU_DP3_P1

CPU_DP3_N1

CPU_DP3_P2

CPU_DP3_N2

CPU_DP3_P3

CPU_DP3_N3

CPU_DP3_AUXP

CPU_DP3_AUXN

K36

DDI1_TXP[0]

K37

DDI1_TXN[0]

J35

DDI1_TXP[1]

J34

DDI1_TXN[1]

H37

DDI1_TXP[2]

H36

DDI1_TXN[2]

J37

DDI1_TXP[3]

J38

DDI1_TXN[3]

D27

DDI1_AUXP

E27

DDI1_AUXN

H34

DDI2_TXP[0]

H33

DDI2_TXN[0]

F37

DDI2_TXP[1]

G38

DDI2_TXN[1]

F34

DDI2_TXP[2]

F35

DDI2_TXN[2]

E37

DDI2_TXP[3]

E36

DDI2_TXN[3]

F26

DDI2_AUXP

E26

DDI2_AUXN

C34

DDI3_TXP[0]

D34

DDI3_TXN[0]

B36

DDI3_TXP[1]

B34

DDI3_TXN[1]

F33

DDI3_TXP[2]

E33

DDI3_TXN[2]

C33

DDI3_TXP[3]

B33

DDI3_TXN[3]

A27

DDI3_AUXP

B27

DDI3_AUXN

SKL-H_BGA1440

CPU1D

3

SKYLAKE_HALO

4 OF 14

Rev_1.0

EDP_TXP[0]

EDP_TXN[0]

EDP_TXP[1]

EDP_TXN[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP_AUXP

EDP_AUXN

EDP_DISP_UTIL

EDP_RCOMP

PROC_AUDIO_CLK

PROC_AUDIO_SDI

PROC_AUDIO_SDO

2

D29

E29

F28

E28

B29

A29

B28

C28

C26

B26

A33

D37

G27

G25

G29

EDP_TXP0

EDP_TXN0

EDP_TXP1

EDP_TXN1CPU_DP1_N1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXP

EDP_AUXN

@

T194

PAD~D

EDP_COMP

AUD_AZACPU_SCLK

AUD_AZACPU_SDO

AUD_AZACPU_SDI

AUD_AZACPU_SDI AUD_AZACPU_SDI_R

1 2

RC66 20_0402_5%

EDP_TXP0 <29>

EDP_TXN0 <29>

EDP_TXP1 <29>

EDP_TXN1 <29>CPU_DP1_N1<31>

EDP_TXN2 <29>

EDP_TXP2 <29>

EDP_TXN3 <29>

EDP_TXP3 <29>

EDP_AUXP <29>

EDP_AUXN <29>

COMPENSATION PU FOR

eDP

CAD Note:Trace width=20 mils

,Spacing=25mil,

Max length=100 mils.

EDP_COMP

AUD_AZACPU_SCLK <23>

AUD_AZACPU_SDO <23>

AUD_AZACPU_SDI_R <23>

1

+VCC_IO

12

RC124.9_0402_1%

B B

A A

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

Compal Electronics, Inc.

SKYLAKE-H (4/8)

SKYLAKE-H (4/8)

SKYLAKE-H (4/8)

LA-E311P

LA-E311P

LA-E311P

9 71Wednesday, November 23, 2016

9 71Wednesday, November 23, 2016

9 71Wednesday, November 23, 2016

1

1.0

1.0

1.0

Vinafix.com

5

D D

+VCC_EDRAM_FUSEPRG_ED2 +1.8V_RUN_EDRAM_ED2

1 2

RC226 100_0603_1%@

VCC_EDRAM_SENSE<57>

VSS_EDRAM_SENSE<57>

1 2

1 2

RC223 0_0603_5%@

C C

1 2

1 2

RC176 100_0603_1%@

RC224 0_0603_5%@

1 2

RC230 100_0603_1%@

1 2

1 2

RC227 49.9_0402_1%

1 2

RC228 49.9_0402_1%

RC229 49.9_0402_1%

+VCC_EOPIO

+VCC_EOPIO_ED2

VCC_EOPIO_SENSE<58>

VSS_EOPIO_SENSE<58>

+1.8V_RUN_EDRAM

+VCC_EDRAM_FUSEPRG

+1.8V_RUN_EDRAM_ED2

+VCC_EDRAM_FUSEPRG_ED2

CPU_ZVM#<57,58>

CPU_MSM#<58>

4

+VCC_EDRAM

3.3A

+VCC_EDRAM_ED2

100_0603_1%~D

12

@

RC173

VCC_EDRAM_SENSE

VSS_EDRAM_SENSE

VCC_EDRAM_SENSE_ED2

VSS_EDRAM_SENSE_ED2

3.2A

1 2

RC175 100_0603_1%@

VCC_EOPIO_SENSE_ED3

VSS_EOPIO_SENSE_ED3

CPU_ZVM#_ED2

CPU_MSM#_ED2

CPU_EOPIO_RCOMP

EDRAM_OPIO_RCOMP

EDRAM_OPIO_RCOMP_ED2

BK17

BK19

BM17

BN17

BK23

BK26

BK27

BM24

BM16

BM22

BP15

BR15

BP16

BR16

BN15

BM15

BP17

BN16

BM14

AW13

AU13

AY13

BR25

BP25

BJ17

BJ19

BJ20

BK20

BL16

BL17

BL18

BL19

BL20

BL21

BJ23

BJ26

BJ27

BL23

BL24

BL25

BL26

BL27

BL28

BL15

BL22

BT15

BT16

BL14

BJ35

BJ36

AT13

BT29

CPU1J

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

VCCOPC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCOPC_S ENSE

VSSOPC_ SENSE

RSVD

RSVD

VCCEOPIO

VCCEOPIO

VCCEOPIO

RSVD

RSVD

RSVD

VCCEOPIO _SENSE

VSSEOPI O_SENSE

RSVD

RSVD

VCC_OPC_ 1P8

VCC_OPC_ 1P8

RSVD

RSVD

ZVM#

MSM#

ZVM2#

MSM2#

OPC_RCOMP

OPCE_RCO MP

OPCE_RCO MP2

SKL-H_BGA1440

SKYLAKE_HALO

10 OF 14

Rev_1.0

3

T1PAD~D @

T2PAD~D @

T3PAD~D @

T4PAD~D @

T5PAD~D @

T6PAD~D @

T7PAD~D @

T9PAD~D @

T10PAD~D @

T11PAD~D @

T8PAD~D @

T14PAD~D @

T13PAD~D @

T15PAD~D @

T12PAD~D @

PCH_2_CPU_TRIGGER<25>

CPU_2_PCH_TRIGGER<25>

PCH_2_CPU_TRIGGER

CPU_2_PCH_TRIGGER_R

TP_SKL_F30

TP_SKL_E30

T18PAD~D @

T19PAD~D @

T21PAD~D @

T20PAD~D @

T23PAD~D @

T24PAD~D @

T22PAD~D @

TP_SKL_F30

TP_SKL_E30

2

CPU1K

D1

RSVD_TP

E1

RSVD_TP

E3

RSVD_TP

E2

RSVD_TP

BR1

RSVD_TP

BT2

RSVD_TP

BN35

RSVD

J24

RSVD

H24

RSVD

BN33

RSVD

BL34

RSVD

N29

RSVD

R14

RSVD

AE29

RSVD

AA14

RSVD

A36

RSVD

A37

RSVD

H23

PROC_TRIGIN

J23

PROC_TRIGOU T

F30

RSVD

E30

RSVD

B30

RSVD

C30

RSVD

G3

RSVD

J3

RSVD

BR35

RSVD

BR31

RSVD

BH30

RSVD

SKL-H_BGA1440

CPU_2_PCH_TRIGGER_RCPU_2_PCH_TRIGGER

1 2

RC177 30_0402_5%

1 2

1 2

RC178 0_0402_5%@

RC179 0_0402_5%@

SKYLAKE_HALO

11 OF 14

Rev_1.0

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

NCTF

NCTF

NCTF

NCTF

NCTF

NCTF

1

BM33

BL33

BJ14

BJ13

BK28

BJ28

BJ18

VSS

BJ16

BK16

BK24

BJ24

BK21

BJ21

BT17

BR17

BK18

VSS

BJ34

BJ33

G13

AJ8

BL31

B2

B38

BP1

BR2

C1

C38

T26 PAD~D@

T25 PAD~D@

T28 PAD~D@

T27 PAD~D@

T29 PAD~D@

T30 PAD~D@

T31 PAD~D@

T32 PAD~D@

T34 PAD~D@

T33 PAD~D@

T36 PAD~D@

T35 PAD~D@

T37 PAD~D@

T38 PAD~D@

T39 PAD~D@T16PAD~D @

T40 PAD~D@T17PAD~D @

T42 PAD~D@RC174 100_0603_1%@

T41 PAD~D@

T44 PAD~D@

T43 PAD~D@

T45 PAD~D@

T46 PAD~D@

T47 PAD~D@

T48 PAD~D@

T49 PAD~D@

B B

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

SKYLAKE-H (5/8)

SKYLAKE-H (5/8)

SKYLAKE-H (5/8)

LA-E311P

LA-E311P

LA-E311P

10 71Wednesday, November 23, 2016

10 71Wednesday, November 23, 2016

10 71Wednesday, November 23, 2016

1

1.0

1.0

1.0

Vinafix.com

5

+VCC_GT +VCC_SA

D D

C C

B B

BG34

BG35

BG36

BH33

BH34

BH35

BH36

BH37

BH38

BJ37

BJ38

BL36

BL37

BM36

BM37

BN36

BN37

BN38

BP37

BP38

BR37

BT37

BE38

BF13

BF14

BF29

BF30

BF31

BF32

BF35

BF36

BF37

BF38

BG29

BG30

BG31

BG32

BG33

BC36

BC37

BC38

BD13

BD14

BD29

BD30

BD31

BD32

BD33

BD34

BD35

BD36

BE31

BE32

BE37

CPU1H

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

SKL-H_BGA1440

SKYLAKE_HALO

8 OF 14

Rev_1.0

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

+VCC_GT

AV29

AV30

AV31

AV32

AV33

AV34

AV35

AV36

AW14

AW31

AW32

AW33

AW34

AW35

AW36

AW37

AW38

AY29

AY30

AY31

AY32

AY35

AY36

AY37

AY38

BA13

BA14

BA29

BA30

BA31

BA32

BA33

BA34

BA35

BA36

BB13

BB14

BB31

BB32

BB33

BB34

BB35

BB36

BB37

BB38

BC29

BC30

BC31

BC32

BC35

BE33

BE34

BE35

BE36

+VCC_IO

+1.0V_VCCSTG +1.0V_VCCST

RC317 0_0402_5%@

1 2

4

SKYLAKE_HALO

CPU1I

J30

VCCSA

K29

VCCSA

K30

VCCSA

K31

VCCSA

K32

VCCSA

K33

VCCSA

K34

VCCSA

K35

VCCSA

L31

VCCSA

L32

VCCSA

L35

VCCSA

L36

VCCSA

L37

VCCSA

L38

VCCSA

M29

VCCSA

M30

VCCSA

M31

VCCSA

M32

VCCSA

M33

VCCSA

M34

VCCSA

M35

VCCSA

M36

VCCSA

AG12

VCCIO

G15

VCCIO

G17

VCCIO

G19

VCCIO

G21

VCCIO

H15

VCCIO

H16

VCCIO

H17

VCCIO

H19

VCCIO

H20

VCCIO

H21

VCCIO

H26

VCCIO

H27

VCCIO

J15

VCCIO

J16

VCCIO

J17

VCCIO

J19

VCCIO

J20

VCCIO

J21

VCCIO

J26

VCCIO

J27

VCCIO

SKL-H_BGA1440

9 OF 14

+VCC_VDDQ_CLK +1.2V_MEM

1 2

RC220 0_0402_5%@

Rev_1.0

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQC

VCCPLL_O C

VCCPLL_O C

VCCST

VCCSTG

VCCSTG

VCCPLL

VCCPLL

VCCSA_SE NSE

VSSSA_S ENSE

VCCIO_SE NSE

VSSIO_S ENSE

AA6

AE12

AF5

AF6

AG5

AG9

AJ12

AL11

AP6

AP7

AR12

AR6

AT12

AW6

AY6

J5

J6

K12

K6

L12

L6

R6

T6

W6

Y12

BH13

G11

H30

H29

G30

H28

J28

M38

M37

H14

J14

+1.2V_MEM

12A

+VCC_VDDQ_CLK

+VCC_SFR_OC

+1.0V_VCCST

+1.0V_VCCSTG

+1.0V_VCCSFR

VCC_SA_SENSE

VSS_SA_SENSE

VCC_IO_SENSE

VSS_IO_SENSE

3

VCC_SA_SENSE <63>

VSS_SA_SENSE <63>

VCC_IO_SENSE <55>

VSS_IO_SENSE < 55>

2

+1.2V_MEM

PDDG page19, if don`t support DS3, contact to VDDQ directly

+5V_ALW

0.1U_0402_10V7K

@

1U_0402_6.3V6K

1

12

CZ96

CZ97

2

SIO_SLP_S3#_UZ30

SIO_SLP_S3#<7,11,23, 39,46,48>

SIO_SLP_SUS#<48,60,61>

SIO_SLP_S4#<11,23,39,48,54,56>

RC332 0_0402_5%@

1 2

+3.3V_ALW

5

1

IN1

2

IN2

3

P

O

G

C1471

@

1 2

0.1U_0402_10V7K

4

UC7

SN74AHC1G08DCKR_SC70-5

RC302 0_0402_5%@

UZ30

1

VIN1

2

VIN2

7

VIN thermal

3

VBIAS

4

ON

TPS22961DNYR_WSON8

12

6

VOUT

5

GND

+VCC_SFR_OC

0.1U_0402_10V7K

12

1

CZ95

VOUT

GND

+1.0V_VCCSTG

12

+1.0V_VCCSTG_C

6

5

@

PJP7

PAD-OPEN1x3m

9/8

1 2

CZ82 10U_0402_6.3V6M

+1.0V_PRIM

+5V_ALW

9/8

10U_0402_6.3V6M

0.1U_0402_10V7K

@

1

12

CZ90

CZ89

2

SIO_SLP_S4#<11,23,39,48,54,56>

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

RC303 0_0402_5%@

1 2

2

+1.0V_VCCST source

UZ18

1

VIN1

2

VIN2

7

VIN thermal

3

VBIAS

4

ON

TPS22961DNYR_WSON8

4.4mohm/6A

TR=12.5us@Vin=1.05V

+1.0V_VCCST_UZ18

6

VOUT

5

GND

DELL CONFIDENTIAL/PROPRIETARY

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PJP6

@

PAD-OPEN1x1m

9/8

12

CZ63

10U_0402_6.3V6M

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SKYLAKE-H (6/8)

SKYLAKE-H (6/8)

SKYLAKE-H (6/8)

+1.0V_VCCST +1.0V_VCCSFR

12

1 2

RC304 0_0603_5%@

LA-E311P

LA-E311P

LA-E311P

11 71W ednesday, November 23, 2016

11 71W ednesday, November 23, 2016

11 71W ednesday, November 23, 2016

1

1.0

1.0

1.0

+1.0V_VCCSTG source

+1.0V_PRIM

UZ19

1

VIN1

2

0.1U_0402_10V7K

@

CZ86

VIN2

7

VIN thermal

3

VBIAS

4

ON

TPS22961DNYR_WSON8

4.4mohm/6A

TR=12.5us@Vin=1.05V

4

+5V_ALW

10U_0402_6.3V6M

9/8

1

12

CZ88

2

+3.3V_ALW

C1421

@

1 2

0.1U_0402_10V7K

A A

SIO_SLP_S3#<7,11,23, 39,46,48>

5

RC331 0_0402_5%@

1 2

220P_0402_25V8J

SIO_SLP_S0#<23, 39>

CC273

@

5

1

P

IN1

4

O

2

IN2

G

UC1

RC320 0_0402_5%@

1 2

SN74AHC1G08DCKR_SC70-5

3

1

2

Vinafix.com

5

PLACE CAP IN

+VCC_EOPIO

PLACE CAP BACKSIDE

10U_0603_6.3V6M~D

1

1

CC173

2

2

D D

+VCC_EDRAM

PLACE CAP BACKSIDE

10U_0603_6.3V6M~D

1

1

CC177

2

2

10U_0603_6.3V6M~D

1

1

CC182

2

2

C C

+1.2V_MEM

+1.2V_MEM DECOUPLING

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

1

CC161

2

2

22U_0603_6.3V6M

B B

12

CC81

SOCKET EDGE TOP

+1.8V_RUN_EDRAM

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

CC174

CC169

2

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

CC170