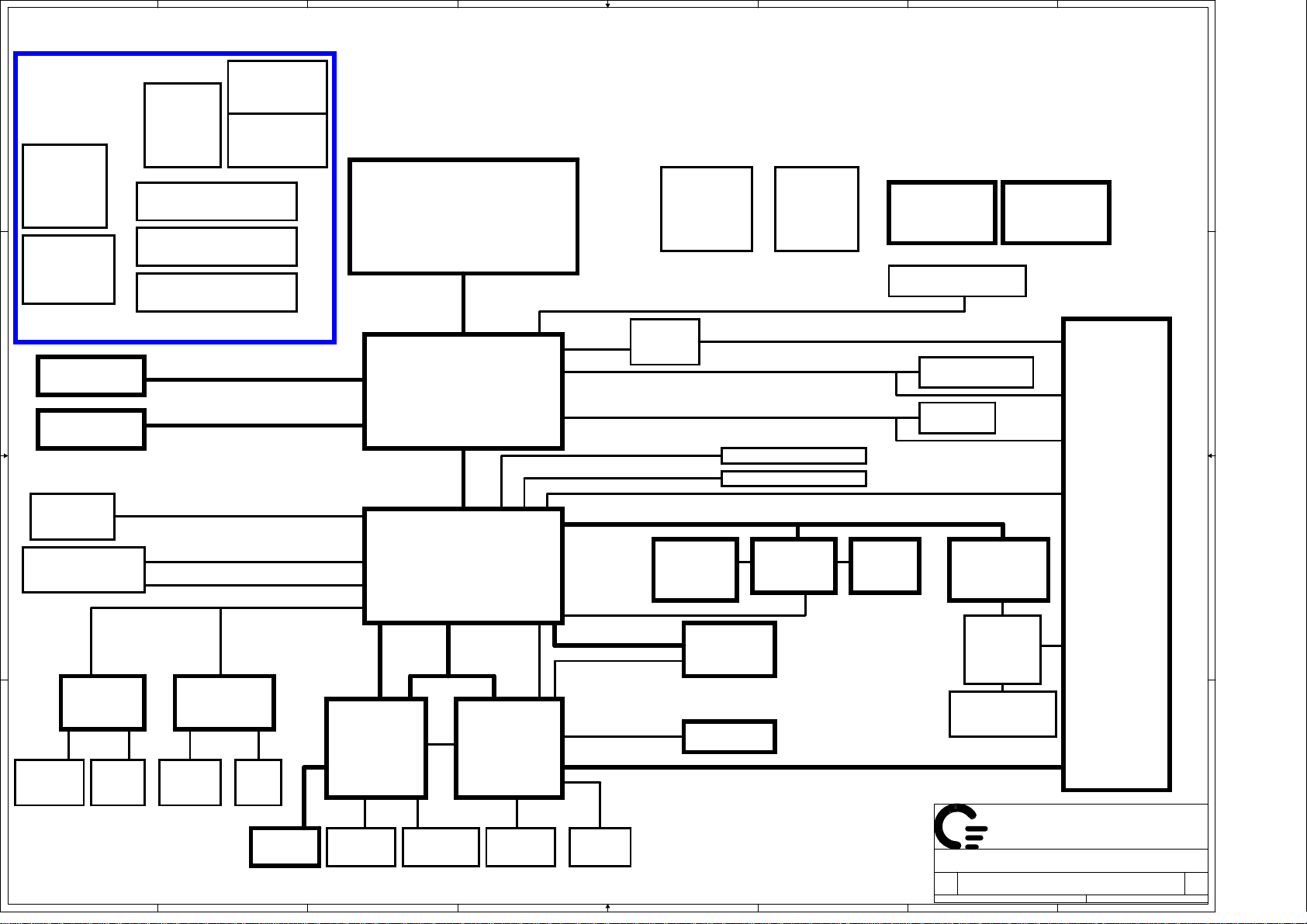

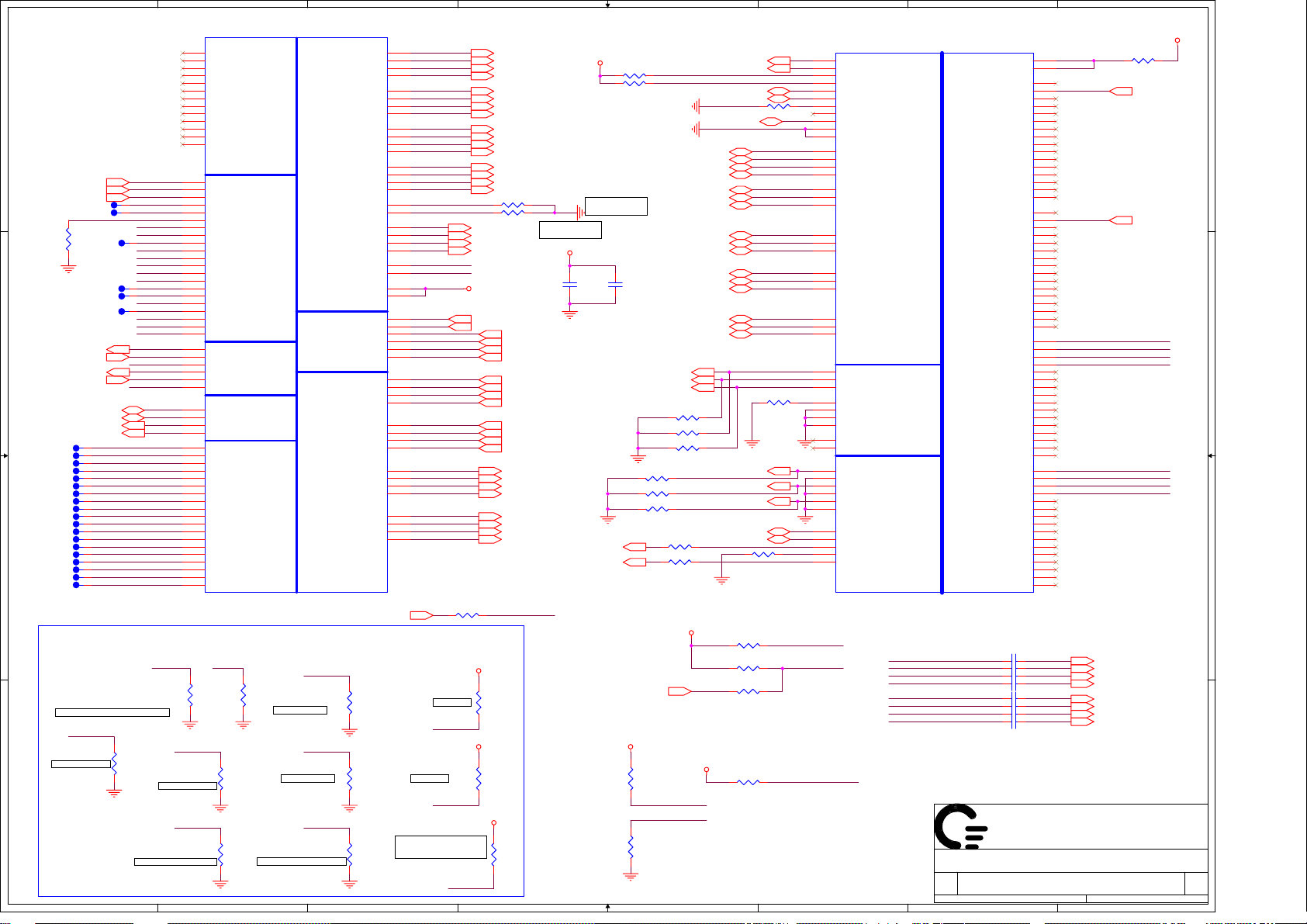

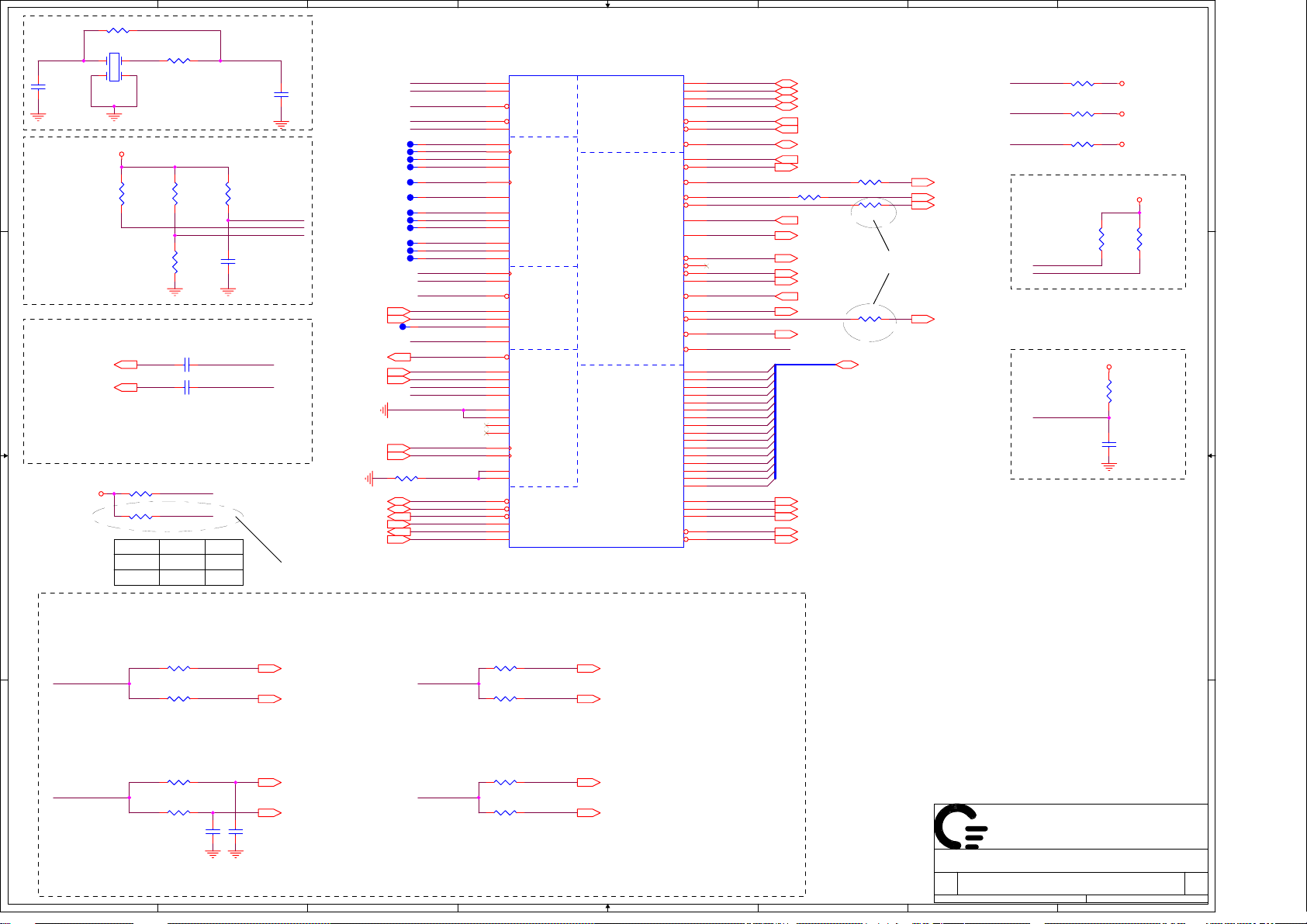

Page 1

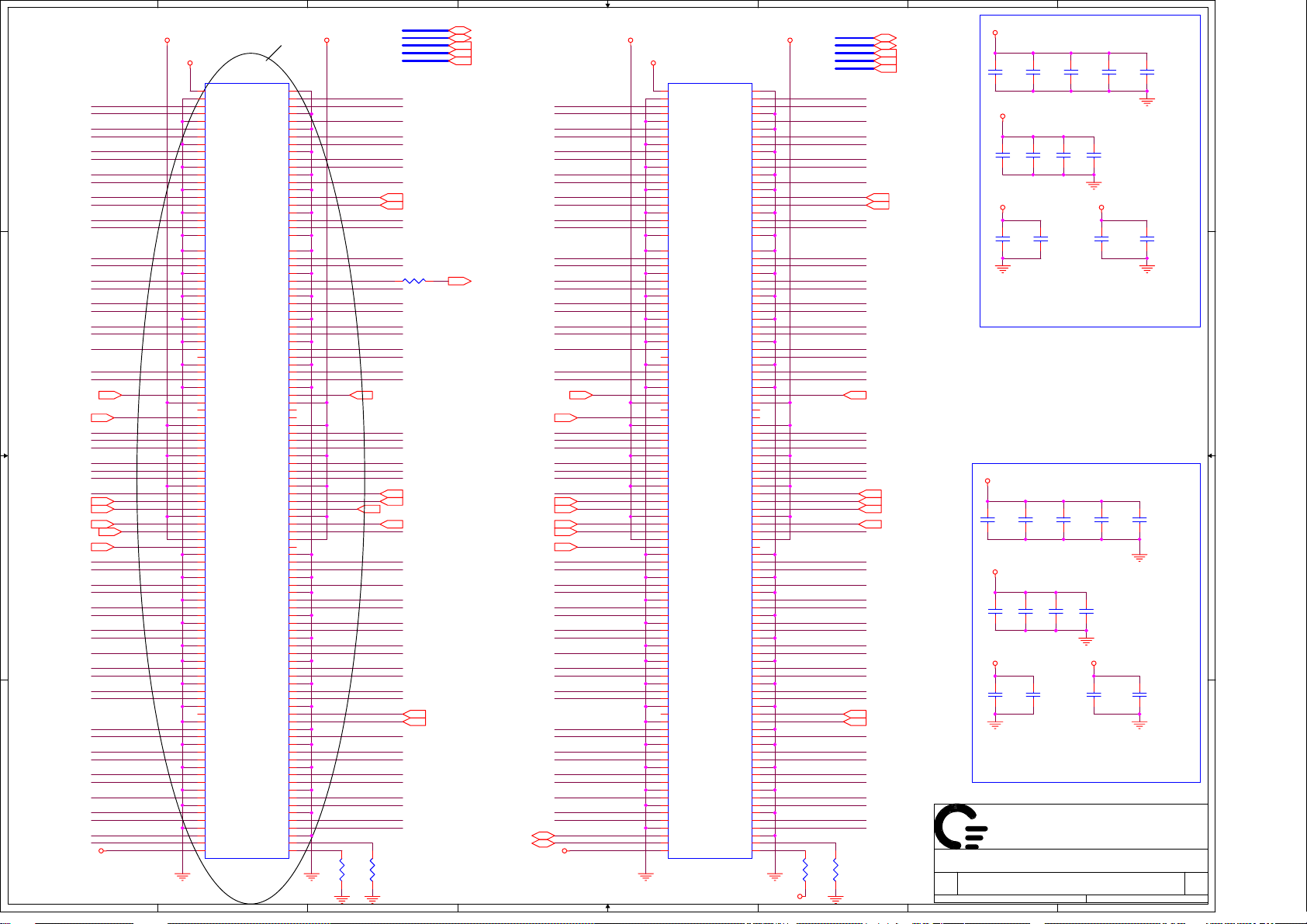

1

2

3

4

5

6

7

8

DRAM Power

DC/DC

A A

+3V_SRC

+5VSUS

PG 46

IMVP-6

CPU VR

PG 45

RUN POWER

SW

PG 47

POWER DC/DC

B B

DDR2-SODIMM1

AC/BATT

CONNECTOR

BATT

SELECTOR

BATT

CHARGER

400/533/667 MHZ DDR II

1.8V, 0.9V

PG 43

1.5VSUS, 1.05V

PG 44

PG 48

PG 41

PG 42

PG 15,16

400/533/667 MHZ DDR II

DDR2-SODIMM2

PG 15,16

SATA - HDD

SATA

PG 21

Internal Media Bay

C C

CD-ROM

PG 21

ATA 66/100

USB2.0(P2)

AC97/Azalia

AUDIO

STAC9200

PG 34,35

MDC

PG 26

SPI

S/PDIF to

DOCK

D D

PG 39

Audio

Jacks

PG 35

RJ11 to

DOCK

PG 39

Tip

Ring

PG 26

Flash

PG 30

1

2

SHELBY-INTEGRATED

DMI X4 Interface

SPI

SIO MEC5004

128KB Flash

TMKBC

128 Pins VTQFP

PG 27

Keyboard

PG 27

Touchpad

PG 31

3

Yonah

(478 Micro-FCPGA)

PG 3,4

533/667

MHz FSB

Calistoga

1466 uFCBGA

PG 5,6,7,8,9,10

ICH7-M

652 BGA

PG 11,12,13,14

LPC

USB2.0 (P1)

SIO ECE5018

Expander

BC

USB 2.0 Hub(4)

128 Pins VTQFP

PG 28

PS/2

IrDA

PG 38

sDVO

USB2.0 (P5,P6)

USB2.0 (P3,P4)

USB2.0 (P7)

PCIE

ECE_USB2.0(P1)

ECE_USB2.0(P2)

Serial

PG 29

4

CLOCKS

ICS954301

PG 17

SI1362

PG 18

1394 CONN

PG 25

USB2.0 (P0)

MINI-PCIE

Wireless LAN

PG 23

Bluetooth

PG 31

5

2 Rear Ports

2 right Side

SYSTEM

RESET CKT

PG 40

LVDS

DVI

TVOUT

VGA

33MHz PCI

CARDBUS

OZ711

PG 24

PG 33

PG 33

PCMCIA

CON.

PG 24

DOCK LPC

6

SWTICH & LED &

IO CONN

PG 33

FAN & THERMAL

PG 32

Panel Connector

PG 19

S-Video

PG 20

CRT

PG 20

DOCKING

CONNECTOR

LAN (100/10)

BCM4401

PG 36

E-Switch

PI3L110Q

PG 37

I/O Board CONN

PG 33

PG 39

QUANTA

Title

Size Document Number Rev

Date: Sheet

COMPUTER

Schematic Block Diagram1

DM5 1A

星期二

27, 2005

十二月

7

of

159,

8

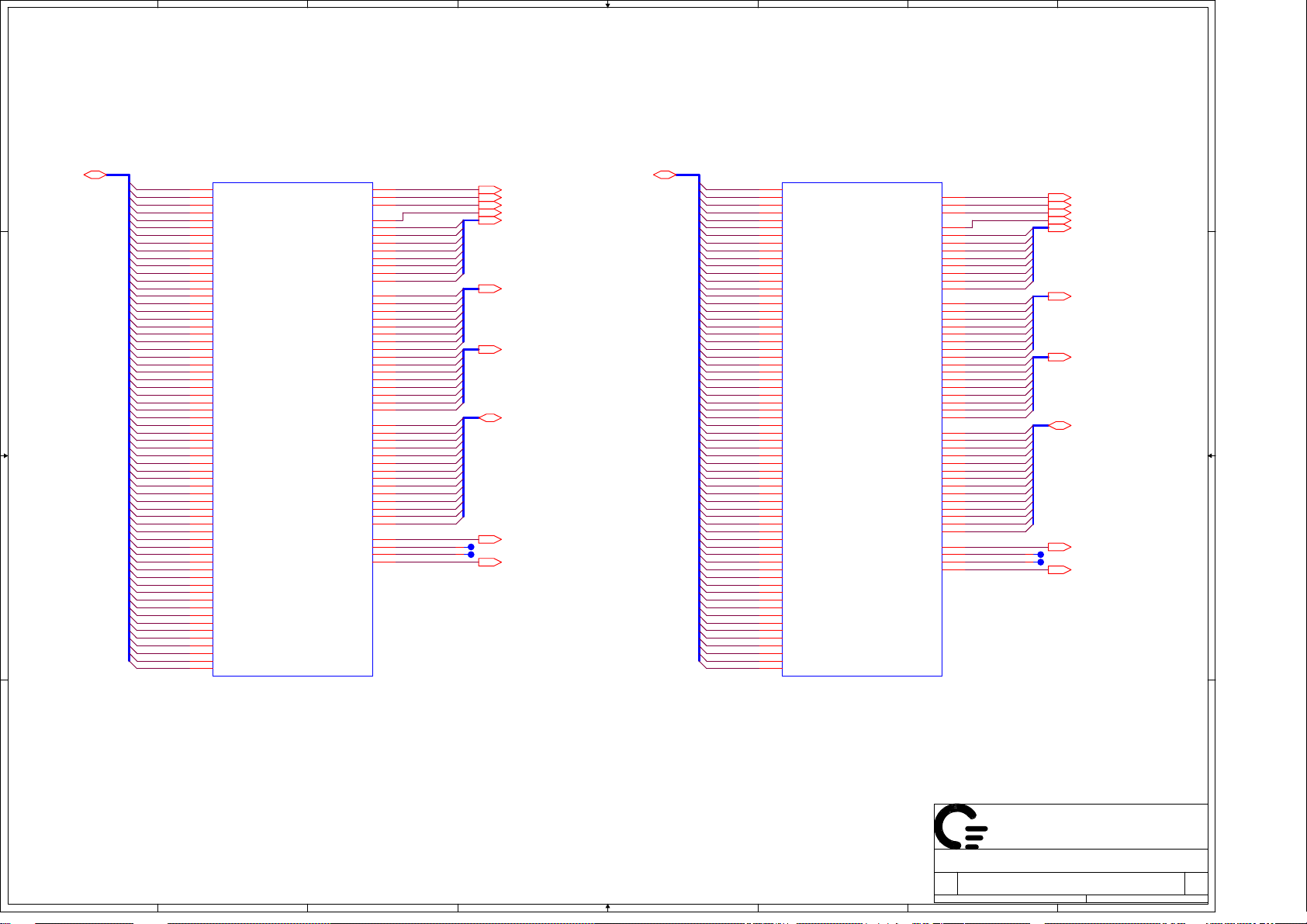

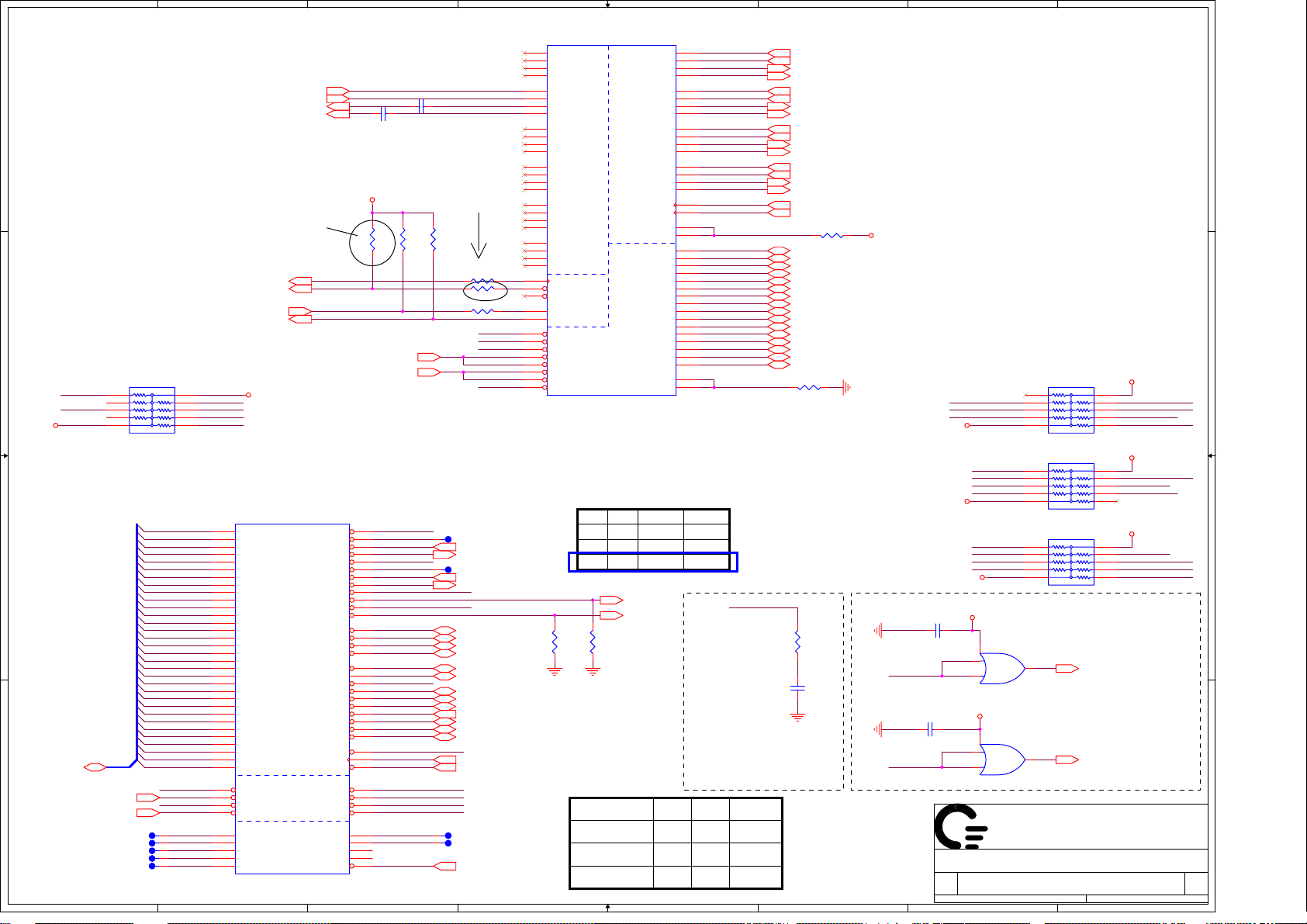

Page 2

1

Pg# Description

1

Schematic Block Diagram 1

2

Front Page

3-4

A A

B B

C C

Yonah

5-10

Calistoga

11-14

ICH7

15-16

DDRII SO-DIMM(200P)

17

Clock Generator

18

SI1362

19

LCD Conn. & SSP

20

CRT & TV Conn.

21

SATA & IDE Conn.

22

PAD & Screw Hole

23

MiniCard

24

PCCARD&CONN

25

1394

26

MDC Conn.

27-28

SIO (MEC5004 & ECE5018)

29

Serial Port

30

Flash ROM

31

Touch Pad CONN.& Bluetooth CONN

FAN & Thermal

32

33

Switch Board Conn. & LED & IO Board

34-35

Azelia CODEC (STAC9751) & Phone Jack

LAN BCM4401 10/100

36

LAN SWITCH / LAN POWER

37

38

FIR

2

INDEX

3

DNI LIST

4

5

6

Power & Ground

Label Description

DC_IN+

PBATT+

PWR_SRC

VHCORE

1.05V AGTL+ POWER (1.05V) I/O

+3VRUN

+3VSUS

+5VALW

+5VRUN

+5VSUS

+5VHDD

+5VMOD

STRB#/5V

+5VRUN

VDDA

1_8VSUS

1_8VRUN

+3VALW 8051 POWER (3V)

V1_5RUN

GND ALL PAGES DIGIT AL GROUND

Pg#

AC ADAPTER (20V)

MAIN BATTERY + (10~17V)

MAIN POWER (10~20V)

CPU CORE POWER (1.25/1.15V)

SLP_S3# CTRLD POWER

SLP_S5# CTRLD POWER

8051 POWER (5V)

SLP_S3# CTRLD POWER

SLP_S5# CTRLD POWER

HDD POWER (5V)

MODULE POWER (5V)

EXTERNAL FDD POWER (5V)

FAN POWER (5V)

AUDIO ANALOG POWER (5V)

RESUME WELL IN ICH

SLP_S3# CTRLD POWER

ALVISO POWE R Non -CPU I/O

COMBO CONN GND

7

8

Control Signal

RUNPWROK

RUNPWROK

RUN_ON

SUS_ON

RUN_ON

SUS_ON

HDDC_EN#

MODC_EN#

FDD/LPT#

FAN_OFF/ON#

RUN_ON

39 Docking Conn.

40

SYSTEM RESET/POWER GOOD

41-42

Battery Selector & Charger

43

1.8VSUS/0.9V

44

1.5V/1.05V

45

CPU Power

D D

46

D/D Power

47

RUN Power Switch

48

DCIN , Batt

49

Power Block Diagram

50

SMBUS Block Diagram

1

QUANTA

Title

Size Document Number Rev

2

3

4

5

6

Date: Sheet

COMPUTER

Index, DNI, Power & Ground

DM5 3A

星期二

27, 2005

十二月

7

of

259,

8

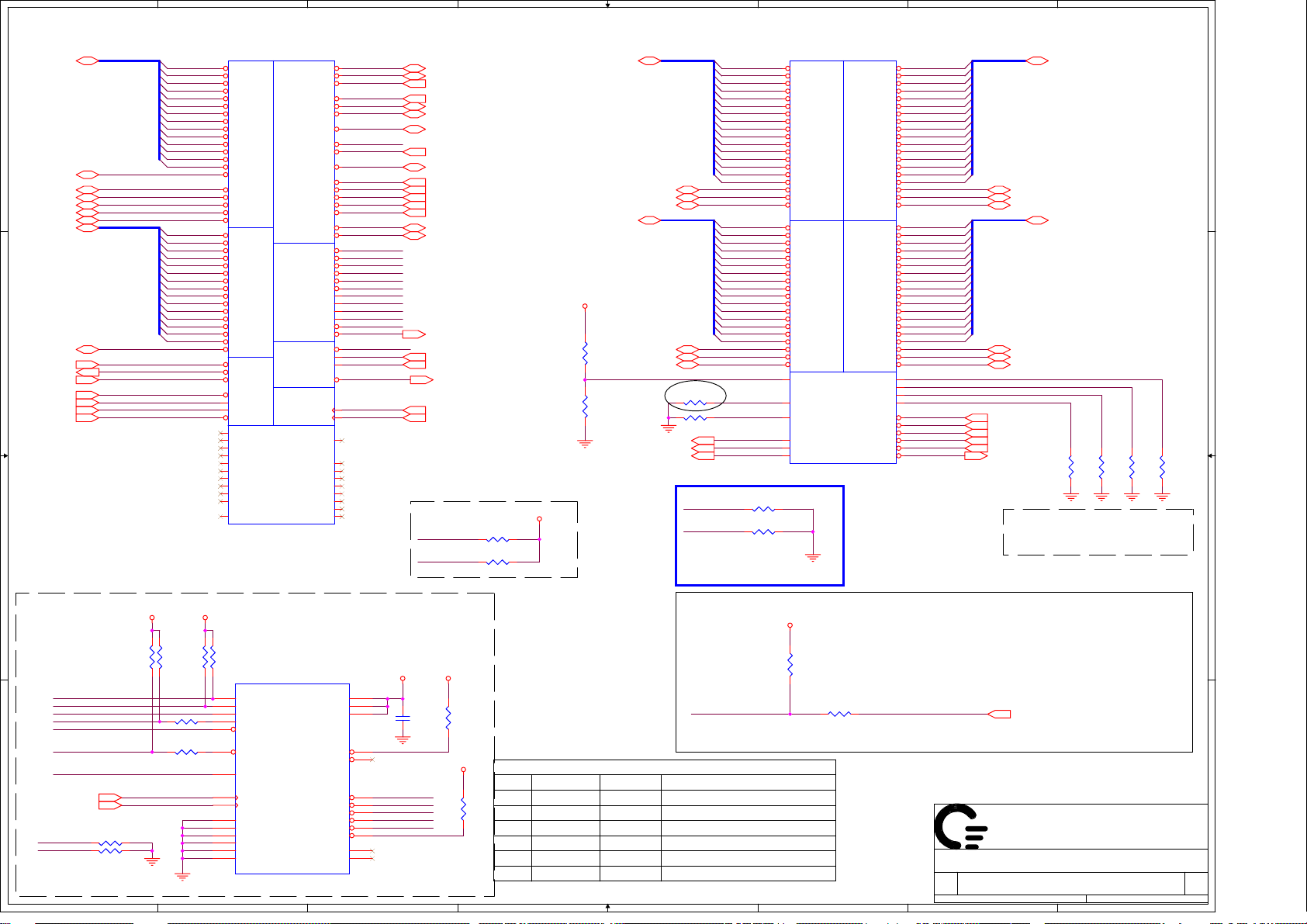

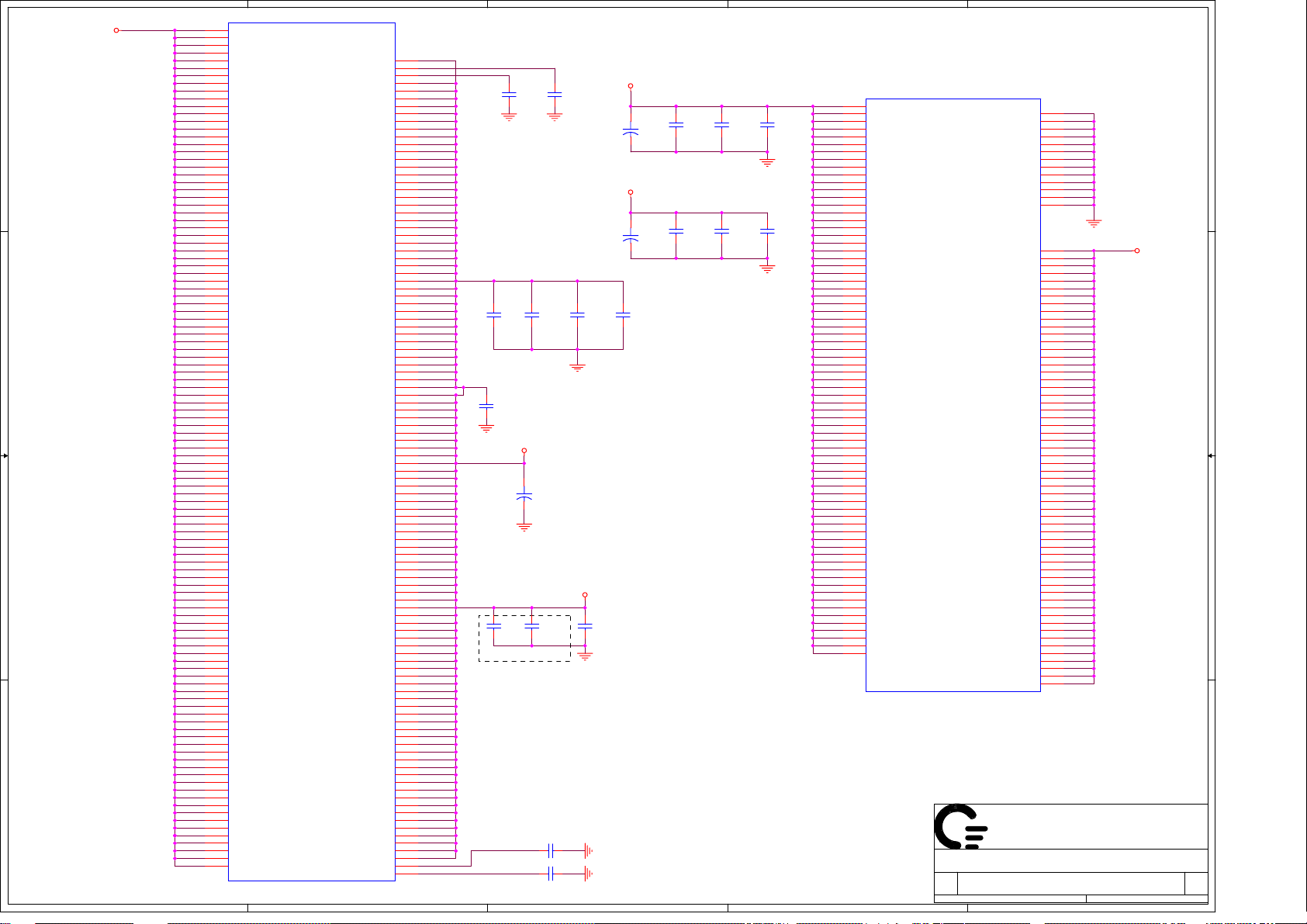

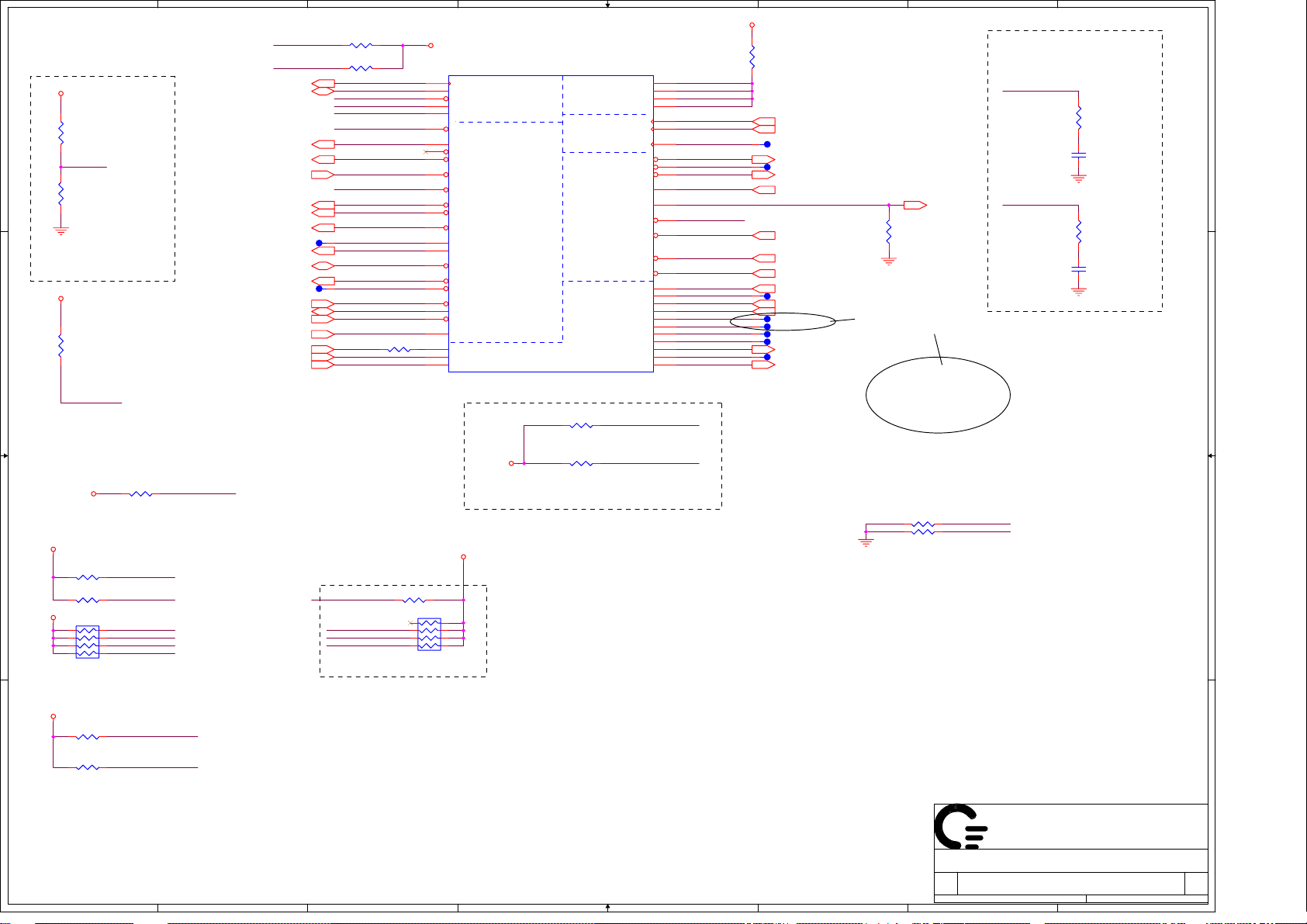

Page 3

1

2

3

4

5

6

7

8

M23

R24

N24

M24

N25

M26

AD26

C26

D25

C21

E22

F24

E26

H22

F23

G25

E25

E23

K24

G24

H26

F26

K22

H25

H23

G22

N22

K25

P26

R23

L25

L22

L23

P25

P22

P23

T24

L26

T25

B22

B23

J24

J23

J26

U6B

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

Yonah

DATA GRP 0 DATA GRP 1

MISC

PWRGOOD

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

DATA GRP 2

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

DATA GRP 3

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

SLP#

PSI#

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0V_CPU_BTLREF

COMP1

COMP2

COMP3

H_D#[0..63]

H_D#[0..63]

H_DPRSTP# 11,45

H_DPSLP# 11

H_DPWR# 5

H_PWRGOOD 11

H_CPUSLP# 5,11

H_PSI# 45

H_D#[0..63] 5

H_DSTBN#2 5

H_DSTBP#2 5

H_DINV#2 5

H_D#[0..63] 5

H_DSTBN#3 5

H_DSTBP#3 5

H_DINV#3 5

R156

R154

54.9/F

Comp0,2 connect with Zo=27.4ohm.

Comp1,3 connect with Zo=55ohm,

make these t race length shorter than 0.5".

27.4/F

1 2

54.9/F

1 2

R155

27.4/F

1 2

R158

1 2

AA1

AA4

AB2

AA3

B25

M3

K5

M1

N2

N3

P5

P2

L1

P4

P1

R1

L2

K3

H2

K2

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

M4

N5

T2

V3

B2

C3

J4

L4

J1

J3

U6A

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]#

RSVD[02]#

RSVD[03]#

RSVD[04]#

RSVD[05]#

RSVD[06]#

RSVD[07]#

RSVD[08]#

RSVD[09]#

RSVD[10]#

RSVD[11]#

Yonah

ADDR GROUP 0

DEFER#

CONTROL

RESET#

XDP/ITP SIGNALS

PROCHOT

THERMDA

THERMDC

THERMTRIP#

THERMH CLK

RSVD[12]#

RSVD[13]#

RSVD[14]#

RSVD[15]#

RSVD[16]#

RESERVED

RSVD[17]#

RSVD[18]#

RSVD[19]#

RSVD[20]#

ADS#

BNR#

BPRI#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDO

TMS

TRST#

DBR#

BCLK[0]

BCLK[1]

TDI

H1

E2

G5

H5

F21

E1

F1

H_IERR#

D20

H_INIT#

B3

H4

H_RESET#

B1

F3

F4

G3

G2

G6

E4

AD4

ITP_BPM#1

AD3

ITP_BPM#2

AD1

ITP_BPM#3

AC4

ITP_BPM#4

AC2

ITP_BPM#5

AC1

ITP_TCK

AC5

ITP_TDIH_A#26

AA6

ITP_TDO

AB3

ITP_TMS

AB5

ITP_TRST#

AB6

C20

H_PROCHOT#

D21

H_THERMDA

A24

H_THERMDC

A25

H_THERMTRIP#

C7

A22

A21

T22

D2

F6

D3

C1

AF1

D22

C23

C24

H_ADS# 5

H_BNR# 5

H_BPRI# 5

H_DEFER# 5

H_DRDY# 5

H_DBSY# 5

H_BR0# 5

H_INIT# 11

H_LOCK# 5

H_RESET# 5

H_RS#0 5

H_RS#1 5

H_RS#2 5

H_TRDY# 5

H_HIT# 5

H_HITM# 5

ITP_DBRESET# 13,27

H_THERMDA 32

H_THERMDC 32

H_THERMTRIP# 32

CLK_CPU_BCLK 17

CLK_CPU_BCLK# 17

H_THERMTRIP#

H_IERR#

Routing together

Trace width/Spacing

=10/10 mil

R31 56

1 2

R165 56

1 2

+1.05V_VCCP

H_D#[0..63]5

H_D#[0..63]5

Place voltage

divider within

0.5" of GTLREF

pin

+1.05V_VCCP

R146

1K/F

CT_1214:Change R29

from 51_NC to 1K_NC

R142

2K/F

H_D#[0..63]

H_DSTBN#05

H_DSTBP#05

H_DINV#05

H_D#[0..63]

H_DSTBN#15

H_DSTBP#15

H_DINV#15

R29 *1K_NC

1 2

51

1 2

R28

Pop R28 for Yonah B0 & forward

CPU_MCH_BSEL06,17

CPU_MCH_BSEL16,17

CPU_MCH_BSEL26,17

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

TEST1

TEST2

H_DPRSTP#

H_DPSLP#

Populate for Yonah A0,

de-pop for Yonah A1

R30 *56_NC

1 2

R32 *56_NC

1 2

H_A#[3..31]5

A A

H_ADSTB#05

H_REQ#05

H_REQ#15

H_REQ#25

H_REQ#35

H_REQ#45

H_A#[17..31]5

B B

H_ADSTB#15

H_A20M#11

H_FERR#11

H_IGNNE#11

H_STPCLK#11

H_INTR11

H_NMI11

H_SMI#11

C C

H_A#[3..16]

H_A#[17..31]

H_A20M#

H_FERR#

H_IGNNE#

H_STPCLK#

H_SMI#

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19 ITP_BPM#0

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

+1.05V_VCCP +1.05V_VCCP

R220

R221

39.2/F

51

R219 22.6/F

R217 22.6/F

12

12

R222

150

1

2

5

7

3

12

11

8

9

10

14

16

18

20

22

JITP1

TDI

TMS

TCK

TDO

TRST#

RESET#

FBO

BCLKN

BCLKP

GND0

GND1

GND2

GND3

GND4

GND5

*ITP700_NC

2

VTT0

VTT1

VTAP

DBR#

DBA#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

NC0

NC1

+1.05V_VCCP +3.3V_SUS

27

28

26

1 2

25

24

ITP_BPM#0

23

ITP_BPM#1

21

ITP_BPM#2

19

ITP_BPM#3

17

ITP_BPM#4

15

ITP_BPM#5

13

4

6

3

C337

0.1U_10V

12

R215

150

+1.05V_VCCP

12

R216

*54.9/F_NC

H_PROCHOT# CPU_PROCHOT#

ITP disable guidelines

Signal Resistor Value Connect To Resistor Placement

150 ohm +/- 5%

TDI

39 ohm +/- 5%

TMS

680 ohm +/- 5%

TRST#

27 ohm +/- 5%

TCK

Open

TDO

ITP_EN R268 Depop +3VRUN Close to CK410M Pin8

Note: Populate R214, R216, C366, and R268 when ITP connector is populated.

4

VTT

VTT

GND

GND

VTT

Within 2.0" of the CPU

Within 2.0" of the CPU

Within 2.0" of the CPU

Within 2.0" of the CPU

Within 2.0" of the CPU

5

12

R218

51/F

1 2

ITP_TDI

ITP_TMS

ITP_TCK

ITP_TDO

ITP_TRST#

H_RESET# ITP_DBRESET#

ITP_TCK

D D

CLK_CPU_ITP#17

CLK_CPU_ITP17

R150 27.4/F

ITP_TCK

1 2

ITP_TRST#

1 2

R153 680

1

1 2

1 2

+1.05V_VCCP

R168

75/F

1 2

0_0402

R448

6

CPU_PROCHOT# 28

QUANTA

Title

Size Document Number Rev

Date: Sheet

COMPUTER

Yonah Processor (HOST)

DM5 1A

星期二

27, 2005

十二月

7

of

359,

8

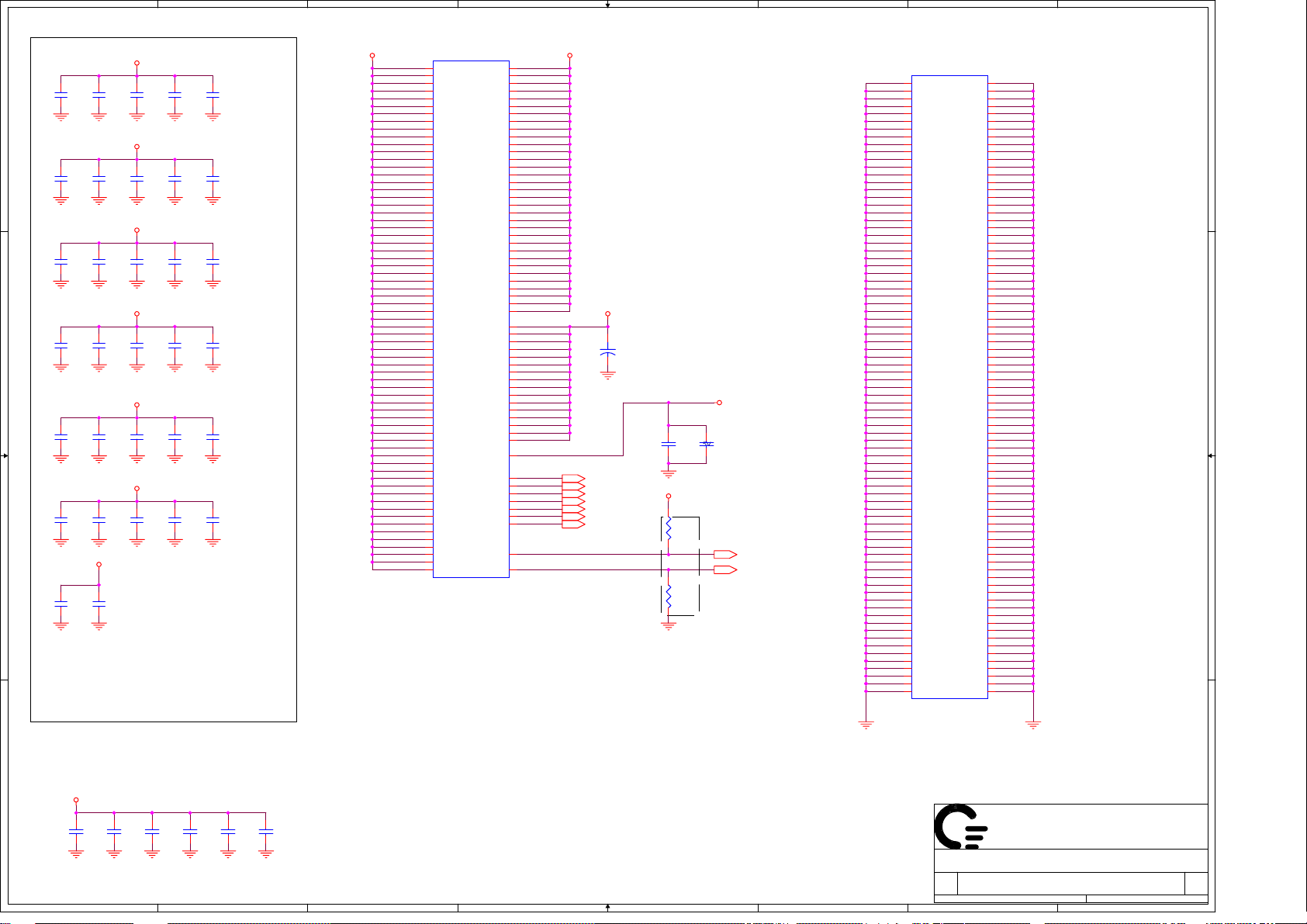

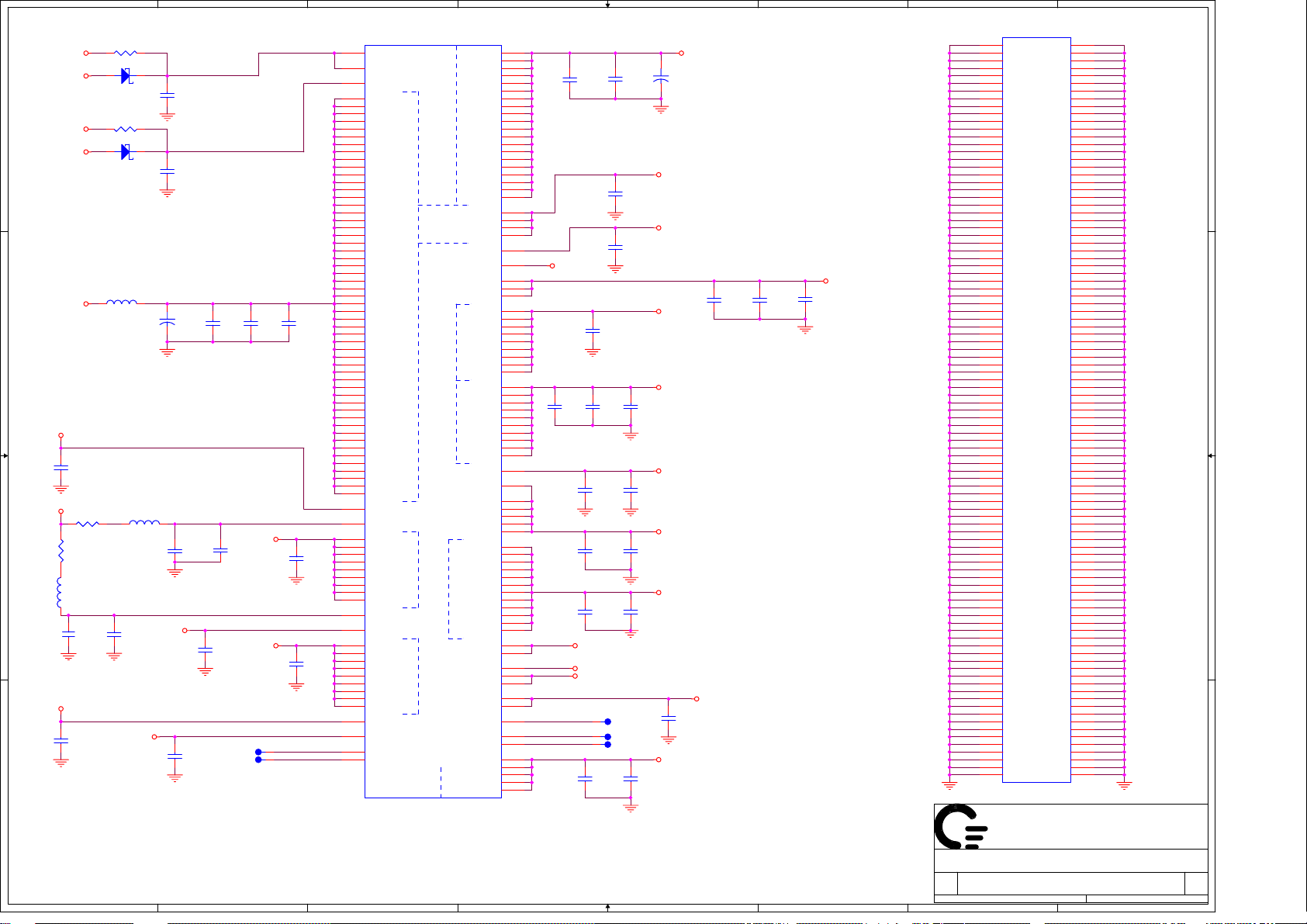

Page 4

1

2

3

4

5

6

7

8

+VCC_CORE

C266

10U_4V

A A

C64

10U_4V

C60

10U_4V

B B

C C

C272

10U_4V

C62

10U_4V

C247

10U_4V

+VCC_CORE

C229

10U_4V

22uF 0805 X6S->105 degree C

8 inside ca vity north s i de secondary layer, 8 inside cavity

south side secondary layer, 6 inside cavity north side

primary lay er, 6 inside cavity south side primary layer.

C248

10U_4V

C63

10U_4V

C59

10U_4V

C271

10U_4V

C252

10U_4V

C246

10U_4V

C215

10U_4V

C67

10U_4V

+VCC_CORE

C61

10U_4V

+VCC_CORE

C58

10U_4V

+VCC_CORE

C270

10U_4V

+VCC_CORE

C251

10U_4V

+VCC_CORE

C245

10U_4V

C66

10U_4V

C269

10U_4V

C57

10U_4V

C268

10U_4V

C250

10U_4V

C281

10U_4V

C65

10U_4V

C267

10U_4V

C273

10U_4V

C283

10U_4V

C249

10U_4V

C282

10U_4V

+VCC_CORE

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AC10

AB10

AB12

AB14

AB15

AB17

AB18

A10

A12

A13

A15

A17

A18

A20

B10

B12

B14

B15

B17

B18

B20

C10

C12

C13

C15

C17

C18

D10

D12

D14

D15

D17

D18

E10

E12

E13

E15

E17

E18

E20

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AB9

U6C

A7

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

Yonah

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

VCC[77]

VCC[78]

VCC[79]

VCC[80]

VCC[81]

VCC[82]

VCC[83]

VCC[84]

VCC[85]

VCC[86]

VCC[87]

VCC[88]

VCC[89]

VCC[90]

VCC[91]

VCC[92]

VCC[93]

VCC[94]

VCC[95]

VCC[96]

VCC[97]

VCC[98]

VCC[99]

VCC[100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

A9

B7

B9

C9

D9

E7

E9

F7

F9

+VCC_CORE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

Route VCCSENSE and VSSSENSE

traces at 27.4ohms with 50mil

spacing. Place PU and PD

within 0.5 inch of CPU.

+1.05V_VCCP

+

C261

*330U_2.5V_NC

CT_0530: Modify

netname.

CPU_VID0 45

CPU_VID1 45

CPU_VID2 45

CPU_VID3 45

CPU_VID4 45

CPU_VID5 45

CPU_VID6 45

VCCSENSE

VSSSENSE

12

C68

0.01U_25V

+VCC_CORE

R138

100/F

R139

100/F

+1.5V_RUN

12

C69

10U_4V

Place C28

near PIN B26

VCCSENSE 45

VSSSENSE 45

Place PU & PD within

1 inch of CPU

M22

M25

N23

N26

A11

A14

A16

A19

A23

A26

B11

B13

B16

B19

B21

B24

C11

C14

C16

C19

C22

C25

D11

D13

D16

D19

D23

D26

E11

E14

E16

E19

E21

E24

F11

F13

F16

F19

F22

F25

G23

G26

H21

H24

K23

K26

L21

L24

U6D

A4

VSS[001]

A8

VSS[002]

VSS[003]

VSS[004]

VSS[005]

VSS[006]

VSS[007]

VSS[008]

B6

VSS[009]

B8

VSS[010]

VSS[011]

VSS[012]

VSS[013]

VSS[014]

VSS[015]

VSS[016]

C5

VSS[017]

C8

VSS[018]

VSS[019]

VSS[020]

VSS[021]

VSS[022]

C2

VSS[023]

VSS[024]

VSS[025]

D1

VSS[026]

D4

VSS[027]

D8

VSS[028]

VSS[029]

VSS[030]

VSS[031]

VSS[032]

VSS[033]

VSS[034]

E3

VSS[035]

E6

VSS[036]

E8

VSS[037]

VSS[038]

VSS[039]

VSS[040]

VSS[041]

VSS[042]

VSS[043]

F5

VSS[044]

F8

VSS[045]

VSS[046]

VSS[047]

VSS[048]

VSS[049]

F2

VSS[050]

VSS[051]

VSS[052]

G4

VSS[053]

G1

VSS[054]

VSS[055]

VSS[056]

H3

VSS[057]

H6

VSS[058]

VSS[059]

VSS[060]

J2

VSS[061]

J5

VSS[062]

J22

VSS[063]

J25

VSS[064]

K1

VSS[065]

K4

VSS[066]

VSS[067]

VSS[068]

L3

VSS[069]

L6

VSS[070]

VSS[071]

VSS[072]

M2

VSS[073]

M5

VSS[074]

VSS[075]

VSS[076]

N1

VSS[077]

N4

VSS[078]

VSS[079]

VSS[080]

P3

VSS[081]

Yonah

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

D D

+1.05V_VCCP

12

C264

0.1U_10V

1

12

C254

0.1U_10V

12

C255

0.1U_10V

12

C256

0.1U_10V

12

C263

0.1U_10V

2

12

C262

0.1U_10V

QUANTA

Title

Size Document Number Rev

3

4

5

6

Date: Sheet

COMPUTER

Yonah Processor (POWER)

DM5 1A

星期二

27, 2005

十二月

7

of

459,

8

Page 5

1

Layout note: H_XRCOMP & H_YRCOMP

trace width and spcaing is 10/20 mil

H_XRCOMP

12

R50

24.9/F

A A

Layout note: H_YSCOMP & H_XSCOMP

resistor should be less than 0.5" inch.

+1.05V_VCCP

12

R48

54.9/F

H_XSCOMP

B B

C C

H_SWING 0 ,H _SWING1 should be 10mil

wide & 20mil spacing.

H_SWING 0, H _ S WING1 Resistors & Caps

should be placed within 0.5"

12

R47

221/F

H_SWNG0 H_SWNG1

12

R46

100/F

C321

0.1U_10V

1 2

+1.05V_VCCP

+1.05V_VCCP+1.05V_VCCP

R55

100/F

12

12

12

12

H_YRCOMP

R57

24.9/F

R52

54.9/F

H_YSCOMP

R54

221/F

1 2

2

C84

0.1U_10V

3

H_D#[0..63]3

CLK_MCH_BCLK17

CLK_MCH_BCLK#17

H_D#[0..63]

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_XRCOMP

H_XSCOMP

H_SWNG0

H_YRCOMP

H_YSCOMP

H_SWNG1

W11

AB7

AA9

AB8

AA4

AA7

AA2

AA6

AA10

AA1

AB4

AC9

AB11

AC11

AB3

AC2

AD1

AD9

AC1

AD7

AC6

AB5

AD10

AD4

AC8

AG2

AG1

K11

T10

U11

T11

Y10

F1

H1

H3

K2

G1

G2

K9

K1

K7

H4

G4

T3

U7

U9

W9

T1

T8

T4

W7

U5

T9

W6

T5

W4

W3

Y3

Y7

W5

W2

Y8

E1

E2

E4

Y1

U1

W1

J1

J6

J8

J3

4

U7A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

H_CLKIN

H_CLKIN#

Calistoga

H_ADSTB#_0

H_ADSTB#_1

HOST

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_ADS#

H_VREF_0

H_BNR#

H_BPRI#

H_BREQ#0

H_CPURST#

H_DBSY#

H_DEFER#

H_DPWR#

H_DRDY#

H_VREF_1

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_SLPCPU#

H_TRDY#

5

H_A#3

H9

H_A#4

C9

H_A#5

E11

H_A#6

G11

H_A#7

F11

H_A#8

G12

H_A#9

F9

H_A#10

H11

H_A#11

J12

H_A#12

G14

H_A#13

D9

H_A#14

J14

H_A#15

H13

H_A#16

J15

H_A#17

F14

H_A#18

D12

H_A#19

A11

H_A#20

C11

H_A#21

A12

H_A#22

A13

H_A#23

E13

H_A#24

G13

H_A#25

F12

H_A#26

B12

H_A#27

B14

H_A#28

C12

H_A#29

A14

H_A#30

C14

H_A#31

D14

E8

B9

C13

J13

C6

F6

C7

B7

A7

C3

J9

H8

K13

J7

W8

U3

AB10

K4

T7

Y5

AC4

K3

T6

AA5

AC5

D3

D4

B3

D8

G8

B8

F8

A8

B4

E6

D6

E3

E7

6

H_A#[3..31]

H_A#[3..31] 3

H_VREF decoupling cap should be

placed within 100mils

H_ADS# 3

H_ADSTB#0 3

H_ADSTB#1 3

H_BNR# 3

H_BPRI# 3

H_BR0# 3

H_RESET# 3

H_DBSY# 3

H_DEFER# 3

H_DPWR# 3

H_DRDY# 3

H_DINV#0 3

H_DINV#1 3

H_DINV#2 3

H_DINV#3 3

H_DSTBN#0 3

H_DSTBN#1 3

H_DSTBN#2 3

H_DSTBN#3 3

H_DSTBP#0 3

H_DSTBP#1 3

H_DSTBP#2 3

H_DSTBP#3 3

H_HIT# 3

H_HITM# 3

H_LOCK# 3

H_REQ#0 3

H_REQ#1 3

H_REQ#2 3

H_REQ#3 3

H_REQ#4 3

H_RS#0 3

H_RS#1 3

H_RS#2 3

H_CPUSLP# 3,11

H_TRDY# 3

12

C336

0.1U_10V

H_VREF

7

+1.05V_VCCP

R212

100/F

1 2

12

R213

200/F

8

D D

QUANTA

Title

Size Document Number Rev

Custom

1

2

3

4

5

6

Date: Sheet

COMPUTER

Calistoga (Host)

DM5 1A

星期二

27, 2005

十二月

7

of

559,

8

Page 6

1

2

3

4

5

6

7

8

U7B

T32

RSVD_1

R32

RSVD_2

F3

RSVD_3

F7

RSVD_4

AG11

RSVD_5

AF11

RSVD_6

H7

RSVD_7

J19

RSVD_8

A41

AH33

AH34

BA41

BA40

BA39

AY41

AW41

AW1

CFG7

CFG9

A35

A34

D28

D27

K16

K18

F18

E15

F15

E18

D19

D16

G16

E16

D15

G15

K15

C15

H16

G18

H15

K27

G28

F25

H26

H28

H27

K28

H32

C41

BA3

BA2

BA1

B41

AY1

A40

A39

J18

J25

J26

G6

D1

C1

B2

A4

A3

12

R223

*2.2K_NC

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_BMBUSY#

PM_EXTTS#_0

PM_EXTTS#_1

PM_THRMTRIP#

PWROK

RSTIN#

SDVO_CTRLCLK

SDVO_CTRLDATA

ICH_SYNC#

CLK_REQ#

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

12

R205

*2.2K_NC

12

R195

*2.2K_NC

12

R207

*2.2K_NC

2

SM_OCDCOMP_0

SM_OCDCOMP_1

CFGRSVD

DDR MUXINGCLKDMI

D_REFSSCLKIN#

PM

D_REFSSCLKIN

MISC

NC

Calistoga

CFG10

Host PLL VCC Select

Low=Reserved

High=Mobility

CFG11

PSB 4X CLK Enable

Low=Calistoga

High=Reserved

CFG16

FSB Dynamic ODT

Low=Dynamic ODT Disable

High=Dynamic ODT Enable

SM_RCOMP#

SM_RCOMP

SM_VREF_0

SM_VREF_1

D_REFCLKIN#

D_REFCLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

CFG[2:0]

A A

001=FSB533

011=FSB667

Others = Reserved

CPU_MCH_BSEL03,17

CPU_MCH_BSEL13,17

CPU_MCH_BSEL23,17

R200

*2.2K_NC

Low=DMIx2

High=DMIx4

B B

THERMTRIP_MCH#32

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

PAD

C C

PAD

PAD

Note: CFG3:17 has internal pullup

CFG18:19 has internal pulldown

D D

T62

PAD

T5

PAD

12

PAD

PAD

PAD

PAD

PM_BMBUSY#13

PM_EXTTS#015

ICH_PWRGD13,40

SDVO_CTRLCLK18

SDVO_CTRLDATA18

MCH_ICH_SYNC#12

CLK_3GPLLREQ#17

T12

T60

T11

T33

T24

T32

T27

T35

T28

T8

T10

T25

T34

T22

T26

T4

T9

T7

T3

CFG[13:12]

00 = Reserved

01 = XOR Mode Enabled

10 = All Z Mode Enabled

11 = Normal Operation(Default)

CFG6

Low= Moby

High=Calistoga

1

T61

T6

T59

T63

PM_EXTTS#0

PM_EXTTS#1

TP_NC0

TP_NC1

TP_NC2

TP_NC3

TP_NC4

TP_NC5

TP_NC6

TP_NC7

TP_NC8

TP_NC9

TP_NC10

TP_NC11

TP_NC12

TP_NC13

TP_NC14

TP_NC15

TP_NC16

TP_NC17

TP_NC18

12

R184

*2.2K_NC

PCIE Graphics Lane

Low= Reverse Lane

High=Normal operation

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

PLTRST#_R

CFG13 CFG12

CPU_Strap

Low=RSVD

High=Mobile CPU

SM_CK_0

SM_CK_1

SM_CK_2

SM_CK_3

SM_CK#_0

SM_CK#_1

SM_CK#_2

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

G_CLKIN#

G_CLKIN

12

R196

*2.2K_NC

12

R192

*2.2K_NC

12

R204

*2.2K_NC

AY35

AR1

AW7

AW40

AW35

AT1

AY7

AY40

AU20

AT20

BA29

AY29

AW13

AW12

AY21

AW21

M_OCDOCMP0

AL20

M_OCDOCMP1

AF10

BA13

BA12

AY20

AU21

SMRCOMPN

AV9

SMRCOMPP

AT9

AK1

AK41

AF33

AG33

A27

A26

C40

D41

AE35

AF39

AG35

AH39

AC35

AE39

AF35

AG39

AE37

AF41

AG37

AH41

AC37

AE41

AF37

AG41

PLTRST#12,13,18,23,27,28

DMI Lane Reversal

Low=Normal

High=Lane Reversed

PCIe Backward

Interpoerability mode

Low=Only SDVO or PCIEx1

is operational

(defaults)

High=SDVO and PCIEx1 are

operating simultaneously

via PEG port

3

VCC Select

Low=1.05V

High=1.5V

CFG18

CFG19

CFG20

M_CLK_DDR0 15

M_CLK_DDR1 15

M_CLK_DDR2 15

M_CLK_DDR3 15

M_CLK_DDR#0 15

M_CLK_DDR#1 15

M_CLK_DDR#2 15

M_CLK_DDR#3 15

DDR_CKE0_DIMMA 15,16

DDR_CKE1_DIMMA 15,16

DDR_CKE2_DIMMB 15,16

DDR_CKE3_DIMMB 15,16

DDR_CS0_DIMMA# 15,16

DDR_CS1_DIMMA# 15,16

DDR_CS2_DIMMB# 15,16

DDR_CS3_DIMMB# 15,16

R255 *40.2/F_NC

R247 *40.2/F_NC

M_ODT0 15,16

M_ODT1 15,16

M_ODT2 15,16

M_ODT3 15,16

V_DDR_MCH_REF

CLK_MCH_3GPLL# 17

CLK_MCH_3GPLL 17

MCH_DREFCLK# 17

MCH_DREFCLK 17

DREF_SSCLK# 17

DREF_SSCLK 17

DMI_MRX_ITX_N0 12

DMI_MRX_ITX_N1 12

DMI_MRX_ITX_N2 12

DMI_MRX_ITX_N3 12

DMI_MRX_ITX_P0 12

DMI_MRX_ITX_P1 12

DMI_MRX_ITX_P2 12

DMI_MRX_ITX_P3 12

DMI_MTX_IRX_N0 12

DMI_MTX_IRX_N1 12

DMI_MTX_IRX_N2 12

DMI_MTX_IRX_N3 12

DMI_MTX_IRX_P0 12

DMI_MTX_IRX_P1 12

DMI_MTX_IRX_P2 12

DMI_MTX_IRX_P3 12

PLTRST#_R

12

R62100

+3.3V_RUN

R225

*1K_NC

1 2

+3.3V_RUN

R232

*1K_NC

1 2

+3.3V_RUN

R224

*1K_NC

1 2

+3.3V_RUN

Stuff R255,R247

for A1 Calistoga

V_DDR_MCH_REF

12

4

R202 10K

1 2

1 2

R203 10K

Place R255,R247

close to MCH.

12

C93

.1U_10V

VGA_HSYNC20

VGA_VSYNC20

+1.8V_SUS

LCTLA_CLK

LCTLB_DAT

C559

.1U_10V

TV_CVBS20,39

TV_Y20,39

TV_C20,39

R190 150/F

1 2

R185 150/F

1 2

R187 150/F

1 2

R194 *150/F_NC

1 2

R193 *150/F_NC

1 2

R186 *150/F_NC

1 2

1 2

R35 39

1 2

R36 39

+3.3V_RUN

DPRSLPVR13,45

12

R263

80.6/F

SMRCOMPN

SMRCOMPP

12

R261

80.6/F

5

PANEL_BKEN19

LCD_ACLK-19

LCD_ACLK+19

LCD_BCLK-19

LCD_BCLK+19

LCD_A0-19

LCD_A1-19

LCD_A2-19

LCD_A0+19

LCD_A1+19

LCD_A2+19

LCD_B0-19

LCD_B1-19

LCD_B2-19

LCD_B0+19

LCD_B1+19

LCD_B2+19

+1.05V_VCCP

BIA_PWM19,27

LCD_DDCCLK19

LCD_DDCDAT19

1 2

R183 1.5K/F

ENVDD19

1 2

R208

4.99K/F

VGA_BLU20,39

VGA_GRN20,39

VGA_RED20,39

CLK_DDC220

DAT_DDC220

1 2

R214 255/F

R206 10K

1 2

R201 *10K_NC

1 2

R227 0

1 2

R226 75

1 2

THERMTRIP_MCH#

U7C

D32

L_BKLTCTL

J30

L_BKLTEN

H30

L_CLKCTLA

H29

L_CLKCTLB

G26

L_DDC_CLK

G25

L_DDC_DATA

B38

L_IBG

C35

L_VBG

F32

L_VDDEN

C33

L_VREFH

C32

L_VREFL

A33

LA_CLK#

A32

LA_CLK

E27

LB_CLK#

E26

LB_CLK

C37

LA_DATA#_0

B35

LA_DATA#_1

A37

LA_DATA#_2

B37

LA_DATA_0

B34

LA_DATA_1

A36

LA_DATA_2

G30

LB_DATA#_0

D30

LB_DATA#_1

F29

LB_DATA#_2

F30

LB_DATA_0

D29

LB_DATA_1

F28

LB_DATA_2

A16

TV_DACA_OUT

C18

TV_DACB_OUT

A19

TV_DACC_OUT

J20

TV_IREF

B16

TV_IRTNA

B18

TV_IRTNB

B19

TV_IRTNC

K30

TV_DCONSEL0

J29

TV_DCONSEL1

E23

CRT_BLUE

D23

CRT_BLUE#

C22

CRT_GREEN

B22

CRT_GREEN#

A21

CRT_RED

B21

CRT_RED#

C26

CRT_DDC_CLK

C25

CRT_DDC_DATA

G23

CRT_HSYNC

J22

CRT_IREF

H23

CRT_VSYNC

Calistoga

PM_EXTTS#0

PM_EXTTS#1 DVO_GREEN#_C

6

LVDS

TV

VGA

DVO_RED#_C

DVO_BLUE#_C

DVO_CLK#_C

DVO_RED_C

DVO_GREEN_C

DVO_BLUE_C

DVO_CLK_C

Title

Size Document Number Rev

Date: Sheet

VCC3G_PCIE_R

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

D40

D38

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

DVO_RED#_C

DVO_GREEN#_C

DVO_BLUE#_C

DVO_CLK#_C

DVO_RED_C

DVO_GREEN_C

DVO_BLUE_C

DVO_CLK_C

SDVOB_RED- 18

SDVOB_GREEN- 18

SDVOB_BLUE- 18

SDVOB_CLK- 18

SDVOB_RED+ 18

SDVOB_GREEN+ 18

SDVOB_BLUE+ 18

SDVOB_CLK+ 18

EXP_A_COMPI

EXP_A_COMPO

EXP_A_RXN_0

EXP_A_RXN_1

EXP_A_RXN_2

EXP_A_RXN_3

EXP_A_RXN_4

EXP_A_RXN_5

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXN_8

EXP_A_RXN_9

EXP_A_RXN_10

EXP_A_RXN_11

EXP_A_RXN_12

EXP_A_RXN_13

EXP_A_RXN_14

EXP_A_RXN_15

EXP_A_RXP_0

EXP_A_RXP_1

EXP_A_RXP_2

EXP_A_RXP_3

EXP_A_RXP_4

EXP_A_RXP_5

EXP_A_RXP_6

EXP_A_RXP_7

EXP_A_RXP_8

EXP_A_RXP_9

EXP_A_RXP_10

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_TXN_0

EXP_A_TXN_1

EXP_A_TXN_2

EXP_A_TXN_3

EXP_A_TXN_4

EXP_A_TXN_5

EXP_A_TXN_6

EXP_A_TXN_7

EXP_A_TXN_8

EXP_A_TXN_9

EXP_A_TXN_10

EXP_A_TXN_11

EXP_A_TXN_12

EXP_A_TXN_13

PCI-EXPRESS GRAPHICS

EXP_A_TXN_14

EXP_A_TXN_15

EXP_A_TXP_0

EXP_A_TXP_1

EXP_A_TXP_2

EXP_A_TXP_3

EXP_A_TXP_4

EXP_A_TXP_5

EXP_A_TXP_6

EXP_A_TXP_7

EXP_A_TXP_8

EXP_A_TXP_9

EXP_A_TXP_10

EXP_A_TXP_11

EXP_A_TXP_12

EXP_A_TXP_13

EXP_A_TXP_14

EXP_A_TXP_15

C326 .1U_10V

C325 .1U_10V

C335 .1U_10V

C339 .1U_10V

C323 .1U_10V

C322 .1U_10V

C330 .1U_10V

C334 .1U_10V

QUANTA

COMPUTER

Calistoga (VGA,DMI)

DM5 1A

星期二

27, 2005

十二月

7

VCC3G_PCIE

R188 24.9/F

1 2

SDVOB_INT- 18

SDVOB_INT+ 18

of

659,

8

Page 7

1

A A

2

3

4

5

6

7

8

AJ35

AJ34

AM31

AM33

AJ36

AK35

AJ32

AH31

AN35

AP33

AR31

AP31

AN38

AM36

AM34

AN33

AK26

AL27

AM26

AN24

AK28

AL28

AM24

AP26

AP23

AL22

AP21

AN20

AL23

AP24

AP20

AT21

AR12

AR14

AP13

AP12

AT13

AT12

AL14

AL12

AW2

AK9

AN7

AK8

AK7

AP9

AN9

AT5

AL5

AY2

AP1

AN2

AV2

AT3

AN1

AL2

AG7

AF9

AG4

AF6

AG9

AH6

AF4

AF8

U7D

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

Calistoga

DDR_A_BS0

AU12

SA_BS_0

SA_BS_1

SA_BS_2

SA_CAS#

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

DDR SYSTEM MEMORY A

SA_WE#

AV14

BA20

AY13

AJ33

AM35

AL26

AN22

AM14

AL9

AR3

AH4

AK33

AT33

AN28

AM22

AN12

AN8

AP3

AG5

AK32

AU33

AN27

AM21

AM12

AL8

AN3

AH5

AY16

AU14

AW16

BA16

BA17

AU16

AV17

AU17

AW17

AT16

AU13

AT17

AV20

AV12

AW14

AK23

AK24

AY14

DDR_A_BS1

DDR_A_BS2

DDR_A_CAS#

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_RAS#

DDR_A_WE#

DDR_A_BS0 15,16

DDR_A_BS1 15,16

DDR_A_BS2 15,16

DDR_A_CAS# 15,16

DDR_A_DM[0..7] 15

DDR_A_DQS[0..7] 15

DDR_A_DQS#[0..7] 15

DDR_A_MA[0..13] 15,16

DDR_A_RAS# 15,16

T70 PAD

T69 PAD

DDR_A_WE# 15,16

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

B B

C C

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_D[0..63]15DDR_A_D[0..63]15

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

AK39

AJ37

AP39

AR41

AJ38

AK38

AN41

AP41

AT40

AV41

AU38

AV38

AP38

AR40

AW38

AY38

BA38

AV36

AR36

AP36

BA36

AU36

AP35

AP34

AY33

BA33

AT31

AU29

AU31

AW31

AV29

AW29

AM19

AL19

AP14

AN14

AN17

AM16

AP15

AL15

AJ11

AH10

AN10

AK13

AH11

AK10

BA10

AW10

BA4

AW4

AY10

AY9

AW5

AY5

AV4

AR5

AK4

AK3

AT4

AK5

AJ9

AJ8

AJ5

AJ3

U7E

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

Calistoga

DDR_B_BS0

AT24

SB_BS_0

SB_BS_1

SB_BS_2

SB_CAS#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

DDR SYSTEM MEMORY B

SB_WE#

AV23

AY28

AR24

AK36

AR38

AT36

BA31

AL17

AH8

BA5

AN4

AM39

AT39

AU35

AR29

AR16

AR10

AR7

AN5

AM40

AU39

AT35

AP29

AP16

AT10

AT7

AP5

AY23

AW24

AY24

AR28

AT27

AT28

AU27

AV28

AV27

AW27

AV24

BA27

AY27

AR23

AU23

AK16

AK18

AR27

DDR_B_BS1

DDR_B_BS2

DDR_B_CAS#

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_RAS#

DDR_B_WE#

DDR_B_BS0 15,16

DDR_B_BS1 15,16

DDR_B_BS2 15,16

DDR_B_CAS# 15,16

DDR_B_DM[0..7] 15

DDR_B_DQS[0..7] 15

DDR_B_DQS#[0..7] 15

DDR_B_MA[0..13] 15,16

DDR_B_RAS# 15,16

T71 PAD

T68 PAD

DDR_B_WE# 15,16

D D

QUANTA

Title

Size Document Number Rev

Custom

1

2

3

4

5

6

Date: Sheet

COMPUTER

Calistoga (DDR2)

DM5 1A

星期二

27, 2005

十二月

7

of

759,

8

Page 8

5

U7G

+1.05V_VCCP

D D

C C

B B

A A

5

AA33

W33

P33

N33

AA32

Y32

W32

V32

P32

N32

M32

AA31

W31

V31

R31

P31

N31

M31

AA30

Y30

W30

V30

U30

R30

P30

N30

M30

AA29

Y29

W29

V29

U29

R29

P29

M29

AB28

AA28

Y28

V28

U28

R28

P28

N28

M28

P27

N27

M27

P26

N26

N25

M25

P24

N24

M24

AB23

AA23

Y23

P23

N23

M23

AC22

AB22

Y22

W22

P22

N22

M22

AC21

AA21

W21

N21

M21

AC20

AB20

Y20

W20

P20

N20

M20

AB19

AA19

Y19

N19

M19

N18

M18

P17

N17

M17

N16

M16

VCC_0

VCC_1

VCC_2

VCC_3

L33

VCC_4

J33

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

L32

VCC_13

J32

VCC_14

VCC_15

VCC_16

VCC_17

T31

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

T30

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

L30

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

L29

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

T28

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

L28

VCC_53

VCC_54

VCC_55

VCC_56

L27

VCC_57

VCC_58

VCC_59

L26

VCC_60

VCC_61

VCC_62

L25

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

L23

VCC_73

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

L22

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

L21

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

L20

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

L19

VCC_101

VCC_102

VCC_103

L18

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

L16

VCC_110

VCC

Calistoga

4

VCC_SM_0

VCC_SM_1

VCC_SM_2

VCC_SM_3

VCC_SM_4

VCC_SM_5

VCC_SM_6

VCC_SM_7

VCC_SM_8

VCC_SM_9

VCC_SM_10

VCC_SM_11

VCC_SM_12

VCC_SM_13

VCC_SM_14

VCC_SM_15

VCC_SM_16

VCC_SM_17

VCC_SM_18

VCC_SM_19

VCC_SM_20

VCC_SM_21

VCC_SM_22

VCC_SM_23

VCC_SM_24

VCC_SM_25

VCC_SM_26

VCC_SM_27

VCC_SM_28

VCC_SM_29

VCC_SM_30

VCC_SM_31

VCC_SM_32

VCC_SM_33

VCC_SM_34

VCC_SM_35

VCC_SM_36

VCC_SM_37

VCC_SM_38

VCC_SM_39

VCC_SM_40

VCC_SM_41

VCC_SM_42

VCC_SM_43

VCC_SM_44

VCC_SM_45

VCC_SM_46

VCC_SM_47

VCC_SM_48

VCC_SM_49

VCC_SM_50

VCC_SM_51

VCC_SM_52

VCC_SM_53

VCC_SM_54

VCC_SM_55

VCC_SM_56

VCC_SM_57

VCC_SM_58

VCC_SM_59

VCC_SM_60

VCC_SM_61

VCC_SM_62

VCC_SM_63

VCC_SM_64

VCC_SM_65

VCC_SM_66

VCC_SM_67

VCC_SM_68

VCC_SM_69

VCC_SM_70

VCC_SM_71

VCC_SM_72

VCC_SM_73

VCC_SM_74

VCC_SM_75

VCC_SM_76

VCC_SM_77

VCC_SM_78

VCC_SM_79

VCC_SM_80

VCC_SM_81

VCC_SM_82

VCC_SM_83

VCC_SM_84

VCC_SM_85

VCC_SM_86

VCC_SM_87

VCC_SM_88

VCC_SM_89

VCC_SM_90

VCC_SM_91

VCC_SM_92

VCC_SM_93

VCC_SM_94

VCC_SM_95

VCC_SM_96

VCC_SM_97

VCC_SM_98

VCC_SM_99

VCC_SM_100

VCC_SM_101

VCC_SM_102

VCC_SM_103

VCC_SM_104

VCC_SM_105

VCC_SM_106

VCC_SM_107

4

AU41

AT41

AM41

AU40

BA34

AY34

AW34

AV34

AU34

AT34

AR34

BA30

AY30

AW30

AV30

AU30

AT30

AR30

AP30

AN30

AM30

AM29

AL29

AK29

AJ29

AH29

AJ28

AH28

AJ27

AH27

BA26

AY26

AW26

AV26

AU26

AT26

AR26

AJ26

AH26

AJ25

AH25

AJ24

AH24

BA23

AJ23

BA22

AY22

AW22

AV22

AU22

AT22

AR22

AP22

AK22

AJ22

AK21

AK20

BA19

AY19

AW19

AV19

AU19

AT19

AR19

AP19

AK19

AJ19

AJ18

AJ17

AH17

AJ16

AH16

BA15

AY15

AW15

AV15

AU15

AT15

AR15

AJ15

AJ14

AJ13

AH13

AK12

AJ12

AH12

AG12

AK11

BA8

AY8

AW8

AV8

AT8

AR8

AP8

BA6

AY6

AW6

AV6

AT6

AR6

AP6

AN6

AL6

AK6

AJ6

AV1

AJ1

Place near C94 close to U2.AT41

Place near C92 close to U2.AM41

VCCSM_LF4

VCCSM_LF5

12

.1U_10V

C107

12

C92

0.47U_10V

12

.1U_10V

C106

12

C94

0.47U_10V

Place C104 close to U3.BA23

12

C104

0.47U_10V

+1.8V_SUS

+

C88

*330U_2.5V_NC

+1.8V_SUS

12

12

C373

C374

10U_4V

10U_4V

Place In Cavity

Place near U2.AV1 & AJ1

C97 0.47U_10V

VCCSM_LF2

VCCSM_LF1

1 2

C91 0.47U_10V

1 2

3

+1.05V_VCCP

C344

C345

C108

C103

0.47U_10V

+

+1.05V_VCCP

+

12

C105

.1U_10V

330U_2.5V

330U_2.5V

12

.1U_10V

12

Place C103 near pin U2.BA15

3

12

12

C342

10U_4V

C364

10U_4V

12

C360

1U_10V

12

C355

0.22U_10V

12

C350

0.22U_10V

12

C343

0.22U_10V

2

AD27

AC27

AB27

AA27

Y27

W27

V27

U27

T27

R27

AD26

AC26

AB26

AA26

Y26

W26

V26

U26

T26

R26

AD25

AC25

AB25

AA25

Y25

W25

V25

U25

T25

R25

AD24

AC24

AB24

AA24

Y24

W24

V24

U24

T24

R24

AD23

V23

U23

T23

R23

AD22

V22

U22

T22

R22

AD21

V21

U21

T21

R21

AD20

V20

U20

T20

R20

AD19

V19

U19

T19

AD18

AC18

AB18

AA18

Y18

W18

V18

U18

T18

2

U7F

VCC_NCTF0

VCC_NCTF1

VCC_NCTF2

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VCC_NCTF65

VCC_NCTF66

VCC_NCTF67

VCC_NCTF68

VCC_NCTF69

VCC_NCTF70

VCC_NCTF71

VCC_NCTF72

1

AE27

AE26

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AC17

Y17

U17

AG27

AF27

AG26

AF26

AG25

AF25

AG24

AF24

AG23

AF23

AG22

AF22

AG21

AF21

AG20

AF20

AG19

AF19

R19

AG18

AF18

R18

AG17

AF17

AE17

AD17

AB17

AA17

W17

V17

T17

R17

AG16

AF16

AE16

AD16

AC16

AB16

AA16

Y16

W16

V16

U16

T16

R16

AG15

AF15

AE15

AD15

AC15

AB15

AA15

Y15

W15

V15

U15

T15

R15

+1.5V_RUN

NCTF

Calistoga

VSS_NCTF0

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VCCAUX_NCTF0

VCCAUX_NCTF1

VCCAUX_NCTF2

VCCAUX_NCTF3

VCCAUX_NCTF4

VCCAUX_NCTF5

VCCAUX_NCTF6

VCCAUX_NCTF7

VCCAUX_NCTF8

VCCAUX_NCTF9

VCCAUX_NCTF10

VCCAUX_NCTF11

VCCAUX_NCTF12

VCCAUX_NCTF13

VCCAUX_NCTF14

VCCAUX_NCTF15

VCCAUX_NCTF16

VCCAUX_NCTF17

VCCAUX_NCTF18

VCCAUX_NCTF19

VCCAUX_NCTF20

VCCAUX_NCTF21

VCCAUX_NCTF22

VCCAUX_NCTF23

VCCAUX_NCTF24

VCCAUX_NCTF25

VCCAUX_NCTF26

VCCAUX_NCTF27

VCCAUX_NCTF28

VCCAUX_NCTF29

VCCAUX_NCTF30

VCCAUX_NCTF31

VCCAUX_NCTF32

VCCAUX_NCTF33

VCCAUX_NCTF34

VCCAUX_NCTF35

VCCAUX_NCTF36

VCCAUX_NCTF37

VCCAUX_NCTF38

VCCAUX_NCTF39

VCCAUX_NCTF40

VCCAUX_NCTF41

VCCAUX_NCTF42

VCCAUX_NCTF43

VCCAUX_NCTF44

VCCAUX_NCTF45

VCCAUX_NCTF46

VCCAUX_NCTF47

VCCAUX_NCTF48

VCCAUX_NCTF49

VCCAUX_NCTF50

VCCAUX_NCTF51

VCCAUX_NCTF52

VCCAUX_NCTF53

VCCAUX_NCTF54

VCCAUX_NCTF55

VCCAUX_NCTF56

VCCAUX_NCTF57

QUANTA

Title

Size Document Number Rev

Custom

Date: Sheet

COMPUTER

Calistoga (VCC, NCTF)

DM5 1A

星期二

27, 2005

十二月

1

of

859,

Page 9

5

L17

1 2

1 2

BLM18PG330SN1

L46

1 2

BLM18PG181SN1

+2.5V_RUN

VCCA_3GPLL_R

L41

1 2

BLM18PG181SN1

+1.5V_RUN

CT_1214: Removed

R49 0_0805 ohm.

+1.5V_RUN

D D

D18

R171 10

2 1

+1.05V_VCCP

RB751V

Route Caps within 250mil or

VCC3G_PCIE

C79

150U_2V_L

R249

0.5/F

VCCA_CRTDAC

12

C293

.1U_10V

12

+

C87

10U_4V

12

C354

10U_4V

R178 0

1 2

Calistoga. Route FB within

3" of Calistoga.

Route VSSACRTDAC gnd from GMCH to decoupling cap

ground lead and then connect to gnd plane.

+1.5V_RUN

C C

B B

A A

+3.3V_RUN

+1.5V_RUN

L42

10uH

L16

10uH

D17

2 1

RB751V

12

12

12

12

R163

10

1 2

+1.5V_RUN

12

C319

+

.1U_10V

12

C316

+

.1U_10V

L40

1 2

BLM18PG181SN1

5

VCCA_DPLLA

C71

470U_4V

C76

470U_4V

C278

10U_4V

2.2U_6.3V

L15

1 2

BLM18PG181SN1

C296

+1.5V_RUN

12

.1U_10V

.1U_10V

.1U_10V

12

.1U_10V

.1U_10V

.1U_10V

C284

C313

C279

C294

C280

C70

L45

BLM11A121S

L47

BLM11A121S

VCC_TVDACA

12

VCC_TVDACB

12

VCC_TVDACC

12

VCC_TVBG

12

VCCD_TVDAC

12

VCCQ_TVDAC

12

C306 *22NF_3P_NC

C285 *22NF_3P_NC

C295 *22NF_3P_NC

C307 *22NF_3P_NC

C286 *22NF_3P_NC

C72 *22NF_3P_NC

12

C90

10U_4V

12

C365

.1U_10V

1

3

C298

2

*22NF_3P_NC

12

12

C367

.1U_10V

12

12

C375

.1U_10V

R180 0

1 2

123

R172 0

1 2

123

R177 0

1 2

123

R181 0

1 2

123

R170 0

1 2

123

R33 0

1 2

123

4

VCC3G_PCIE

12

Place C79 and C87 on

same side as

Calostoga. No Vias.

VCCA_3GPLL

12

12

C324

.022U

VCCA_HPLL

12

C362

22U

VCCA_MPLLVCCA_DPLLB

12

C378

22U

VCC_TVDACA_R

12

C314

.022U

VCC_TVDACB_R

12

C320

.022U

VCC_TVDACC_R

12

C297

.022U

VCC_TVBG_R

12

C327

.022U

VSS_TVBG

VCCD_TVDAC_R

12

C289

.022U

VCCQ_TVDAC_R

12

C74

.022U

4

+2.5V_RUN

C328

.01U

12

+2.5V_RUN

3

12

C305

.1U_10V

4.7U

C329 .1U_10V

12

C312

+2.5V_RUN

12

VCC3G_PCIE

VCCA_3GPLL

C329 should be place within 200mils

+2.5V_CRTDAC

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

+1.5V_RUN

10U_4V

+2.5V_RUN

C304

.1U_10V

12

.1U_10V

C310

C311

+3.3V_RUN

12

12

C308

10U_4V

C301

.01U

12

12

.1U_10V

C303

+1.5V_RUN

12

+1.5V_RUN

VCCA_MPLL

VCC_TVBG_R

VSS_TVBG

VCC_TVDACA_R

VCC_TVDACB_R

VCC_TVDACC_R

VCCD_TVDAC_R

VCCQ_TVDAC_R

12

C369

.1U_10V

Route VSSA_TVBG_GND from GMCH to

decoupling cap ground lead and then connect

to the GND plane.

4.7U, 10U and 22U should be placed <500mils with

in its pins.

0.1U should be placed <200mils with in its pins.

22n should be placed with in its pins.

3

H22

C30

AJ41

AB41

R41

N41

AC33

G41

H41

G21

C39

AF1

AF2

H20

G20

C20

D20

AH1

AH2

C28

D21

H19

AK31

AF31

AE31

AC31

AL30

AK30

AJ30

AH30

AG30

AF30

AE30

AD30

AC30

AG29

AF29

AE29

AD29

AC29

AG28

AF28

AE28

AH22

AJ21

AH21

AJ20

AH20

AH19

AH15

AH14

AG14

AF14

AE14

AF13

AE13

AF12

AE12

AD12

B30

A30

Y41

V41

L41

F21

E21

B26

A38

B39

E19

F19

E20

F20

A28

B28

A23

B23

B25

P19

P16

P15

Y14

U7H

VCCSYNC

VCC_TXLVDS0

VCC_TXLVDS1

VCC_TXLVDS2

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GPLL

VCCA_3GBG

VSSA_3GBG

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_LVDS

VSSA_LVDS

VCCA_MPLL

VCCA_TVBG

VSSA_TVBG

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCD_HMPLL0

VCCD_HMPLL1

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCD_TVDAC

VCC_HV0

VCC_HV1

VCC_HV2

VCCD_QTVDAC

VCCAUX0

VCCAUX1

VCCAUX2

VCCAUX3

VCCAUX4

VCCAUX5

VCCAUX6

VCCAUX7

VCCAUX8

VCCAUX9

VCCAUX10

VCCAUX11

VCCAUX12

VCCAUX13

VCCAUX14

VCCAUX15

VCCAUX16

VCCAUX17

VCCAUX18

VCCAUX19

VCCAUX20

VCCAUX21

VCCAUX22

VCCAUX23

VCCAUX24

VCCAUX25

VCCAUX26

VCCAUX27

VCCAUX28

VCCAUX29

VCCAUX30

VCCAUX31

VCCAUX32

VCCAUX33

VCCAUX34

VCCAUX35

VCCAUX36

VCCAUX37

VCCAUX38

VCCAUX39

VCCAUX40

2

POWER

Calistoga

2

1

VTT_0

VTT_1

VTT_2

VTT_3

VTT_4

VTT_5

VTT_6

VTT_7

VTT_8

VTT_9

VTT_10

VTT_11

VTT_12

VTT_13

VTT_14

VTT_15

VTT_16

VTT_17

VTT_18

VTT_19

VTT_20

VTT_21

VTT_22

VTT_23

VTT_24

VTT_25

VTT_26

VTT_27

VTT_28

VTT_29

VTT_30

VTT_31

VTT_32

VTT_33

VTT_34

VTT_35

VTT_36

VTT_37

VTT_38

VTT_39

VTT_40

VTT_41

VTT_42

VTT_43

VTT_44

VTT_45

VTT_46

VTT_47

VTT_48

VTT_49

VTT_50

VTT_51

VTT_52

VTT_53

VTT_54

VTT_55

VTT_56

VTT_57

VTT_58

VTT_59

VTT_60

VTT_61

VTT_62

VTT_63

VTT_64

VTT_65

VTT_66

VTT_67

VTT_68

VTT_69

VTT_70

VTT_71

VTT_72

VTT_73

VTT_74

VTT_75

VTT_76

AC14

AB14

W14

V14

T14

R14

P14

N14

M14

L14

AD13

AC13

AB13

AA13

Y13

W13

V13

U13

T13

R13

N13

M13

L13

AB12

AA12

Y12

W12

V12

U12

T12

R12

P12

N12

M12

L12

R11

P11

N11

M11

R10

P10

N10

M10

P9

N9

M9

R8

P8

N8

M8

P7

N7

M7

R6

P6

M6

A6

R5

P5

N5

M5

P4

N4

M4

R3

P3

N3

M3

R2

P2

M2

D2

AB1

R1

P1

N1

M1

+1.05V_VCCP

+1.05V_VCCP

12

C346

2.2U_6.3V

Place in Cavity.

+1.05V_VCCP

C78

330U_2.5V

+

Place on the edge.

Place close to pin A6

VTTLF_CAP3

VTTLF_CAP2

VTTLF_CAP1

C73 .47U_10V

Place close to pin D2

1 2

12

C86

.47U_10V

12

C358

4.7U

12

C82

.22U

12

C75

.22U

Place close to pin AB1

QUANTA

Title

Size Document Number Rev

Custom

Date: Sheet

COMPUTER

Calistoga (Power)

DM5 1A

星期二

27, 2005

十二月

1

of

959,

Page 10

5

U7I

AC41

VSS_0

AA41

VSS_1

W41

VSS_2

T41

VSS_3

P41

VSS_4

M41

VSS_5

J41

VSS_6

F41

VSS_7

AV40

VSS_8

AP40

VSS_9

AN40

VSS_10

D D

C C

B B

A A

AK40

AJ40

AH40

AG40

AF40

AE40

AY39

AW39

AV39

AR39

AN39

AJ39

AC39

AB39

AA39

W39

M39

G39

D39

AT38

AM38

AH38

AG38

AF38

AE38

C38

AK37

AH37

AB37

AA37

Y37

W37

V37

R37

P37

N37

M37

H37

G37

D37

AY36

AW36

AN36

AH36

AG36

AF36

AE36

AC36

C36

B36

BA35

AV35

AR35

AH35

AB35

AA35

Y35

W35

V35

R35

P35

N35

M35

H35

G35

D35

AN34

B40

Y39

V39

T39

R39

P39

N39

L39

J39

H39

F39

T37

L37

J37

F37

T35

L35

J35

F35

VSS_11