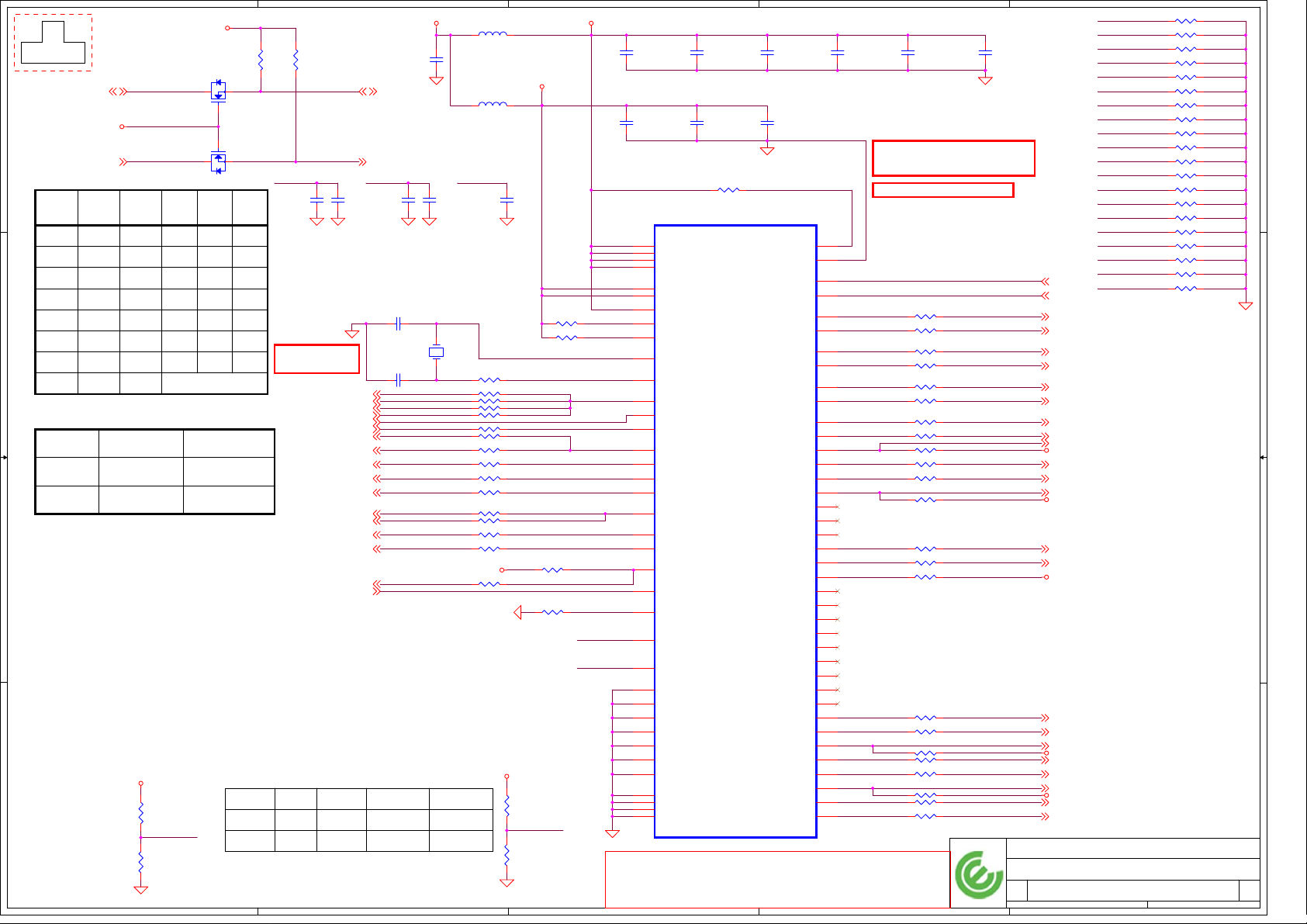

Page 1

A

COMPAL CONFIDENTIAL

B

C

D

E

MODEL NAME :

PCB NO :

1 1

COMPAL P/N :

LA-3741P

JAU00

DA800008W0L

Carson Schematics Document

uFCBGA Mobile Merom-ULV

Intel Calistoga-GMS + ICH7M

2007-01-24

REV : 0.1 (DELL: X00)

HW POP option control table

2 2

BOM No.

CPU P/N

CPU Type

Speed/power

01 BOM 02 BOM

45148731L01 45148731L02 4514873 1L03 45148731L04

SA00001ND0L

Dual core

SA00001MA1L SA00001ND0L

Dual core

1.06G , 9W1.2G ,9W

C41,C44 220 uf 220 uf

C42,C43

3 3

C21,C26,C29,C31

C34,C36,C28,C23

Pop Pop

10 uf

10 uf

C694,C697,C37,C39,C22

C698,C693,C25,C40,C35

C699,C700,C30,C33,C27

Pop Pop

C703,C704,C38

03 BOM 04 BOM

SA00001MA1L

Dual core Dual core

1.06G , 9W1.2G ,9W

220 uf 220 uf

Pop Pop

10 uf 10 uf

Pop Pop

Location: U2

330 uf Poly Cap ; P/N : SGA00001P0L

220 uf Poly Cap ; P/N : SGA00002D0L

POP 2@ ; 220 uf for Dual core

220 uf Poly Cap ; ( P/N : SGA00002D0L)

10 uf MLCC Cap ; P / N ( S E 00000110L)

22 uf MLCC Cap ; P / N ( S E 1 6 0 106M8L)

POP 2@ ; 10 uf for Dual core

10 uf MLCC Cap ; P / N ( S E 1 6 0 106M8L)

JP3

U50

4 4

Depop

Pop

Depop

Pop Pop

Depop DepopPop

POP 4@ ; For with TAA Board

POP 1@ ; For without TAA Board

DELL CONFIDENTIAL/PROPRIETARY

MB PCB

Part Number Description

DA800008W0L

PCB 02F LA-3741P REV0 M/B

A

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

B

C

D

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

LA-3741P

153Friday, January 26, 2007

E

0.1

of

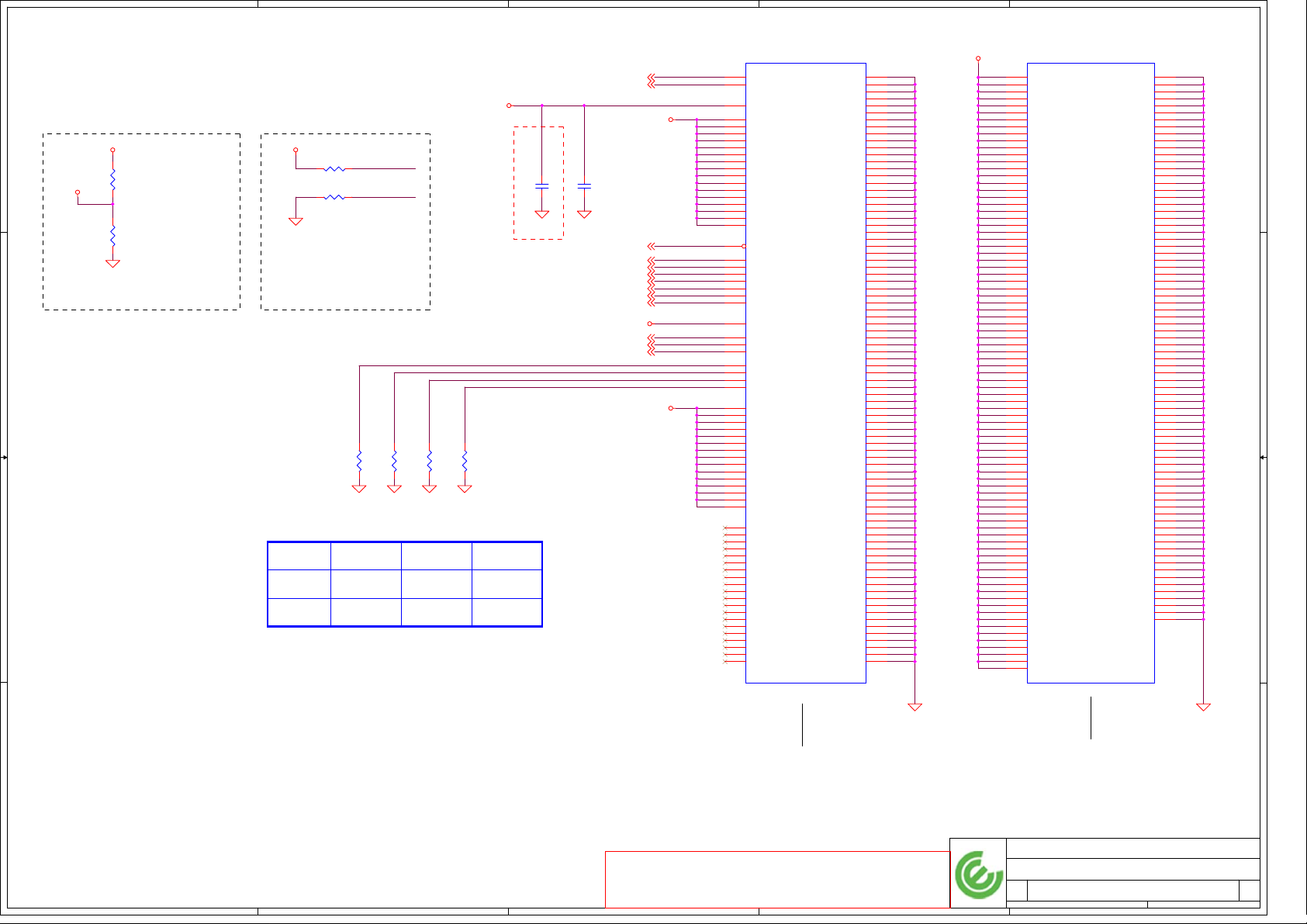

Page 2

A

Compal confidential

Model : HAU30

B

C

D

E

Block Diagram

FAN

+FAN1_VOUT

1 1

pg 18

+2.5V_RUN

pg 18

DVI

2 2

PCI BUS

IDSEL:AD24

(PIRQA#,GNT0#,REQ0#)

DOCKING PORT

+DOCK_PWR_SRC

+3.3V_RUN

+2.5V_LOM

pg 38

USB[7]

Mini Card2

WLAN

3 3

+3.3V_RUN

pg 36

DOCKING

BUFFER

+5V_RUN

Mini Card 1

+3.3V_RUN

+3.3V_LAN+3.3V_LAN

+1.5V_RUN+1.5V_RUN

SIM Card

+SIM_PWR

CardBus & 1394 & SD

R5C843 CSP208

pg 37

+3.3V_RUN/ +1.5V_RUN 100MHz

+3.3V_RUN

+3.3V_SUS

GIGA Enthernet

WWAN

pg 36

HUB USB[2]USB[0]

pg 36

+3.3V_LAN

Thermal

GUARDIAN

EMC4000

+3.3V_SUS

CRT CONN

+5V_RUN

LVDS CONN

+LCDVDD

+GFX_PWR_SRC

DVI Bridge SI1362

+3.3V_RUN

+1.8V_RUN

+3.3V_RUN 33MHz

IDSEL:AD17

(PIRQB,C,D#,GNT2#,REQ2#)

pg 31,32

BCM5752

pg 29

LAN SWITCH

PI3L500E

+3.3V_LAN

pg 30

pg 18

pg 21

RGB

pg 19

LVDS

DVO

pg 20

HUB USB[1]

TV

SD card SLOT

+SD_VCC

1394 CONNCard Bus SLOT

PCI Express BUS

LPC BUS

USB[1]

HUB USB[4]

HUB_USB[3]

pg 32

pg 31pg 32

+1.05V_VCCP

+VCC_CORE

+1.5V_RUN

+1.8V_SUS

+1.05V_VCCP

+3.3V_RUN

+2.5V_RUN

+1.5V_RUN

100MHz

+3.3V_RUN

+3.3V_SUS

+1.5V_RUN

+1.05V_VCCP

+3.3V_RUN

33MHz

SMSC SIO

ECE5018

+3.3V_ALW

Pentium-M

Merom-2M ULV

uFCBGA CPU

479pin

System Bus

FSB 400/533 MHz

INTEL

Calistoga-GMS

998pin BGA

pg 10,11,12,13,14

DMI

INTEL

ICH7-M

652pin BGA

pg 22,23,24,25

HUB USB[1]

HUB USB[2]

pg 39

H_D#(0..63)H_A#(3..31)

pg 7,8

SPI

Memory BUS

(DDR2)

48MHz

Azalia I/F

ATA100

+1.05V_VCCP

+1.8V_SUS 400/533MHz

USB[4] REAR

USB[6] REAR

USB[5] REAR

PATA HDD

+3.3V_HDD

pg 26 pg 27

Azalia Codec

STAC9200

+3.3V_RUN

+VDDA

CPU ITP Port

Clock Generator

SLG84450VTR

+3.3V_RUN

DDRII 1GB on Board

+0.9V_DDR_VTT

+1.8V_SUS

DDRII-DIMM X1

BANK 2, 3

+0.9V_DDR_VTT

+1.8V_SUS

USB Ports X1

+5V_SUS

pg 33

USB Ports X1

+5V_SUS

PWR USB X1

+5V_SUS

DH_PORT_PWRSRC

pg 33

pg 33

MDC

+3.3V_SUS

RJ11

pg 30

pg 6pg 7

pg 16,17

pg 15

pg 34

Cable

RJ45

pg 30

Power Sequence

DC IN

4 4

BATT IN

CHARGER

pg 45

pg 46

pg 51

3V/5V/15V

1.5V/1.05V

1.8V/0.9V

VCORE (IMVP-6)

A

pg 47pg 42,43

pg 48

pg 49

pg 50

Transformer

+2.5V_LOM

pg 30

Power On/Off

SW & LED

pg 44

DC/DC Interface

pg 45

B

Bluetooth

+3.3V_RUN

USB_BIO

Fingerprint

+3.3V_RUN

pg 34

Smart Card

+5V_RUN

pg 41

+3.3V_RUN

OZ77C6

pg 35

SLOT

pg 35

FIR

pg 37

Int.KBD &

Stick

Stick

C

pg 41

+RTC_CELL

+3.3V_ALW

SMSC KBC

MEC5004

Touch Pad

+5V_RUN

pg 40

+3.3V_ALW

pg 41

SPI

ST M25P80

pg 40

AMP & INT.

Speaker

+5V_SUS +3.3V_RUN

INT MIC

+5V_SUS

pg 28 pg 28

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

D

Date: Sheet

HeadPhone &

MIC Jack

Compal Electronics, Inc.

Block Diagram

LA-3741P

253Friday, January 26, 2007

E

0.1

of

Page 3

5

Ceramic Capacitors :

4

3

TABLE

PCI

2

1

0.1U_0402_6.3VXX

D D

Tolerance

Temperatur e Characteristics

Rated Voltage

PCI DEVICE

CARD BUS

DOCKING

IDSEL

AD17

AD24 0

REQ#/GNT#

2

PIRQ

B,C,D

A

Package Size

Value

PM TABLE

+5V_RUN

Tantalum or Polymer Capacitors :

power

plane

+3.3V_ALW

10U_D2_10VX_R45

C C

Low ESR Mark : 45 m ohm

Tolerance

Rated Voltage

Package Size

Value

State

S0

S1

S3

S5 S4/AC

S5 S4/AC don't exist

ON

ON

ON

ON

+3.3V_SRC

+3.3V_SUS

+5V_SUS+5V_ALW

+1.8V_SUS

+15V_SUS

ON

ON

ON

OFF

OFF

+3.3V_RUN

+1.8V_RUN

+0.9V_DDR_VTT

+1.5V_RUN

+VCC_CORE

+1.05V_VCCP

+2.5V_RUN

ON

ON

OFF

OFF

OFFOFF

Capacitor Spec Guide:

Temperature Characteristics:

B B

A A

Symbol

CODE

Tolerance:

Symbol

CODE

Z5U

8

9

COG SJ

HI J

UK

UJ

A

+-0.1PF

+-0.05PF

M

K

+-20%

+-10%

+-30%

Z5V

X6SNPO

SL

N

A

1

B

2

Z5P

B

BJ

K

X5S

C

+-0.25PF

P

+100,-0%

4

5

G

X

6

X5R

SH

H

+-3%

Z

+80,-20%

30

Y5U X7R

C

CH

D

+-0.5PF +-1PF

Q

+20,-10%

+30,-10%

Y5P

Y5V

DEFG

CJ

CK

F

+-2%

V

+40,-20%

7

J

+-5%

NOTE1:

@XX : Depop component

USB

TABLE

USB PORT#

0

1

2

3

4,6

5

7

DESTINATION

Mini 2(WLAN)

USB Hub (5018)

N/A

N/A

REAR

PWR USB

Docking

USB H U B DESTINATION

1

2

3

4

USB HUB on

OZ77C6LN

DP_HUB

PC Card Bay

Mini 1(WWAN)

SMART CARD

Blue tooth

DESTINATION

Fingerprint

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Index and Config.

LA-3741P

353Friday, January 26, 2007

1

0.1

of

Page 4

5

4

3

2

1

ALWON

D D

ALWON

ADAPTER

+5V_ALW

+3.3V_ALW

+PWR_SRC

FDS4435 +GFX_PWR_SRC

RUN_ON

BATTERY

TPS51120

C C

SUS_ON

+5V_SUS

SUS_ON

+3.3V_SRC

AD3207 SC480

RUNPWROK

+VCC_CORE

SC483

RUNPWROK

+1.5V_RUN

RUNPWROK

+VCCP

SUSPWROK_5V

+1.8V_SUS

RUN_ON

+0.9V_DDR_VTT

B B

SI4800

RUN_ON

+5V_RUN

PL8

+15V_SUS

793475

VDDA

SI4800

RUN_ON

(Option)

AUDIO_AVDD_ON

+3.3V_RUN

SI3456

ENAB_3VLAN

+3.3V_LAN

SI3456

RUN_ON

+1.8V_RUN

L47

EMC4000

A A

+2.5V_RUN

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Power Rail

LA-3741P

453Friday, January 26, 2007

1

of

0.1

Page 5

5

4

3

2

1

+3.3V_SUS

2.2K 2.2K 2.2K 2. 2K

ICH_SMBCLK

C22

D D

C C

ICH7-M

SIO

ICH_SMBDATA

B22

+3.3V_ALW

10K

CLK_SMB

6

DAT_SMB +3.3V_ALW

5

+5V_ALW

10K 10K

DOCK_SMB_CLK

10

DOCK_SMB_DAT

9

+3.3V_ALW

+3.3V_SUS

10K

SMBUS Address [TBD]

+5V_ALW

WWAN

2N7002

2N7002

3032

C8C7

5752M

LOM

SMBUS Address [C8]

SMBUS Address [TBD]

8

GUARDIAN

7

Power USB

DOG house

39

DOCKING

40

3032

WLAN

SMBUS Address [2F]

SMBUS Address [5A]

SMBUS Address [C4, 72, 70, 48]

CLK_SCLK

CLK_SDATA

+3.3V_RUN

16

CLK GEN.

17

SMBUS Address [D2]

DDR II 1G

ON Board

SMBUS Address [A0]

197

DIMM1

195

SMBUS Address [A2]

8.2K 8. 2K

112

Macallan IV

B B

A A

111

8

7

SBAT_SMBCLK

SBAT_SMBDAT

+3.3V_ALW

+3.3V_ALW

8.2K8.2K

PBAT_SMBCLK

PBAT_SMBDAT +3.3V_ALW

100

100

6

INV

5

3

BATTERY

4

CONN

9

CHARGER

10

Inverter

SMBUS Address [58]

SMBUS Address [16]

SMBUS Address [12]

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

SMBUS TOPOLOGY

LA-3741P

553Friday, January 26, 2007

1

0.1

of

Page 6

5

D

1

3

G S

2

2N7002

ICH_SMBDATA<24,29,36> CLK_SDATA <15,17>

D D

+3.3V_RUN

ICH_SMBCLK<24,29,36>

FSC FSB FSA CPU

CLKSEL2 CLKSEL0CLKSEL1

ICH_SMBDATA

ICH_SMBCLK

000

1

*

C C

00

1

0

11

0

1

1

0

1

1

11

0

00

1

0

1

CPU_BSEL CPU_BSEL2(FSC) CPU_BSEL1(FSB)

133

166

B B

A A

0

0

+3.3V_RUN

5

1 2

12

2N7002W-7-F_SOT323~D

MHz

266

133

200

166

333

100

400

R69

10K_0402_5%~D

FSA

R72

@

10K_0402_5%~D

+3.3V_RUN

Q1

D

1 3

1 3

D

SRC

MHz

100

100

100

100

100

100

100

Reserve

12

S

G

2

2

G

Q2

S

2N7002W-7-F_SOT323~D

PCI

MHz

33.3

33.3

33.3

33.3

33.3

33.3

33.3

0

1

12

R5

R4

2.2K_0402_5%~D

2.2K_0402_5%~D

CLK_SDATA

CLK_SCLK

1

2

C10

4.7U_0603_6.3V6M~D

Place crystal within

500 mils of CK410

CLK_SD_48M<31>

CLK_ICH_48M<24>

CLK_SMCARD_48M<35>

CPU_MCH_BSEL0<8,10>

CPU_MCH_BSEL1<8,10>

CPU_MCH_BSEL2<8,10>

CLK_PCI_5004<40>

CLK_PCI_SIO<39>

CLK_PCI_PCCARD<31>

CLK_PCI_DOCK<38>

CLK_PCI_LOM<29>

CLK_ICH_14M<24>

CLK_SIO_14M<39>

MCH_DREFCLK<10>

MCH_DREFCLK#<10>

CLK_PCI_ICH<22>

CLK_ENABLE#<50>

FCTSEL1 PIN43 PIN44 PIN47 PIN48

01DOT96T DOT96C 96/100M_T 96/100M_C

27M_out 27M SSout SRCT0 SRCC0

4

+3.3V_RUN

C6

0.1U_0402_16V4Z~D

CLK_SCLK <15,17>

+CK_VDD_48+CK_VDD_A +CK_VDD_REF

1

2

C11

0.047U_0402_16V7K~D

1

2

C12

4.7U_0603_6.3V6M~D

C15

27P_0402_50V8J~D

12

C16

27P_0402_50V8J~D

12

CLK_SD_48M

CLK_ICH_48M FSA

CLK_SMCARD_48M

CLK_PCI_5004

CLK_PCI_SIO

CLK_PCI_PCCARD PCI_PCCARD

CLK_PCI_LOM PCI_LOM

CLK_SIO_14M

MCH_DREFCLK# DOT96#

CLK_PCI_ICH PCI_ICH

CLK_ENABLE#

4

1 2

L1

BLM18PG600SN1_0603~D

1

60ohm,500mA,0.1ohm

2

1

2

12

L2

BLM18PG600SN1_0603~D

C13

0.047U_0402_16V7K~D

X1

14.31818MHz_20P_1BX14318CC1A~D

R30 0_0402_5%~D

R605 39_0402_5%~D

R32 39_0402_5%~D

R34 39_0402_5%~D

R561 8.2K_0402_5%~D@

R56 8.2K_0402_5%~D

R35 39_0402_5%~D

R36 39_0402_5%~D

R38 56_0402_5%~D

R39 56_0402_5%~D

R37 56_0402_5%~D

R40 15_0402_5%~D

R41 15_0402_5%~D

R42 33_0402_5%~D

R43 33_0402_5%~D

+3.3V_RUN

R48 56_0402_5%~D

+CK_VDD_MAIN2

1 2

60ohm,500mA,0.1ohm

1

2

1 2

12

12

1 2

12

12

12

12

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

+3.3V_RUN

@

10K_0402_5%~D

1 2

12

R71

10K_0402_5%~D

+CK_VDD_MAIN

C14

0.047U_0402_16V7K~D

1 2

R25 1_0603_5%~D

1 2

R27 2.2_0603_5%~D

1 2

R46 10K_0402_5%~D

1 2

R51 475_0402_1%~D

R67

FCTSEL1

3

+CK_VDD_MAIN

1

C1

10U_0805_10V4Z~D

2

1

C7

10U_0805_10V4Z~D

2

1

C2

0.1U_0402_16V4Z~D

2

1

C8

0.1U_0402_16V4Z~D

2

1

C3

0.1U_0402_16V4Z~D

2

1

C9

0.1U_0402_16V4Z~D

2

2

1

C4

0.1U_0402_16V4Z~D

2

Place near each pin

W>40 mil

1 2

R15 2.2_0603_5%~D

U1

1

VDDSRC

49

VDDSRC

54

VDDSRC

65

VDDSRC

30

VDDPCI

36

VDDPCI

12

+CK_VDD_REF

+CK_VDD_48

CLK_XTAL_IN

CLK_XTAL_OUT

FSC

FCTSEL1

PCI_DOCKCLK_PCI_DOCK

CLK14M_REFCLK_ICH_14M

DOT96MCH_DREFCLK

CLKIREF

CLK_SCLK

CLK_SDATA

VDDCPU

18

VDDREF

40

VDD48

20

X1

19

X2

41

USB_48MHz/FSLA

45

FSLB/TEST_MODE

23

REF0/FSLC/TEST_SEL

34

PCICLK4/FCTSEL1

33

PCICLK3

32

PCICLK2

27

PCICLK1

22

REF1

43

DOTT_96MHz/27MHz

44

DOTC_96MHz/27MHz(SS)

37

ITP_EN/PCICLK_F0

39

Vtt_PwrGd#/PD

9

IREF

16

SMBCLK

17

SMBDAT

4

GNDSRC

15

GNDCPU

21

GNDREF

31

GNDPCI

35

GNDPCI

42

GND48

68

GNDSRC

73

THRM_PAD

74

THRM_PAD

75

THRM_PAD

76

THRM_PAD

SLG84450VTR_QFN72~D

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

+CK_VDD_A

VDDA

GNDA

PCI_SRC_STOP#

CPU_STOP#

CPUT1

CPUC1

CPUT0

CPUC0

CPUT_ITP/SRCT10

CPUC_ITP/SRCC10

SRCT9

SRCC9

CLKREQ9#

SRCT8

SRCC8

CLKREQ8#

SRCT7

SRCC7

CLKREQ7#

SRCT6

SRCC6

CLKREQ6#

SRCT5

SRCC5

CLKREQ5#

SRCT4

SRCC4

CLKREQ4#

SRCT3

SRCC3

CLKREQ3#

SRCT2

SRCC2

CLKREQ2#

SRCT1

SRCC1

CLKREQ1#

LCD100/96/SRC0_T

LCD100/96/SRC0_C

Place near CK410+

7

8

H_STP_PCI#

25

H_STP_CPU#

24

11

10

CPU_BCLK

14

13

CPU_ITP

6

CPU_ITP#

5

3

2

72

MCH_3GPLL CLK_MCH_3GPLL

70

69

71

66

67

38

PCIE_ICH

63

PCIE_ICH#

64

62

60

61

29

58

59

57

55

56

28

PCIE_MINI2

52

PCIE_MINI2#

53

26

PCIE_MINI1

50

PCIE_MINI1#

51

46

DOT96_SSC

47

DOT96_SSC#

48

2

1

2

CLK_MCH_BCLKMCH_BCLK

CLK_MCH_BCLK#MCH_BCLK#

CLK_CPU_BCLK

CLK_CPU_BCLK#CPU_BCLK#

CLK_CPU_ITP

CLK_CPU_ITP#

CLK_PCIE_LOMPCIE_LOM

CLK_PCIE_LOM#PCIE_LOM#

CLK_MCH_3GPLL#MCH_3GPLL#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_PCIE_MINI2

CLK_PCIE_MINI2#

CLK_PCIE_MINI1

CLK_PCIE_MINI1#

1

C5

0.1U_0402_16V4Z~D

2

1 2

R24 33_0402_5%~D

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

R26 33_0402_5%~D

R28 33_0402_5%~D

R29 33_0402_5%~D

R31 33_0402_5%~D

R33 33_0402_5%~D

R53 33_0402_5%~D

R54 33_0402_5%~D

R55 10K_0402_5%~D

R49 33_0402_5%~D

R50 33_0402_5%~D

R52 10K_0402_5%~D

R44 33_0402_5%~D

R45 33_0402_5%~D

R47 10K_0402_5%~D

R61 33_0402_5%~D

R62 33_0402_5%~D

R63 10K_0402_5%~D

R64 33_0402_5%~D

R65 33_0402_5%~D

R66 10K_0402_5%~D

R68 33_0402_5%~D

R70 33_0402_5%~D

1

C643

0.1U_0402_16V4Z~D

H_STP_PCI# <24>

+3.3V_RUN

+3.3V_RUN

+3.3V_RUN

+3.3V_RUN

+3.3V_RUN

CLK_CPU_ITP

CLK_CPU_ITP#

CLK_MCH_BCLK

CLK_MCH_BCLK#

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_PCIE_LOM

CLK_PCIE_LOM#

CLK_PCIE_MINI2

CLK_PCIE_MINI2#

CLK_PCIE_MINI1

CLK_PCIE_MINI1#

MCH_DREFCLK

MCH_DREFCLK#

DREF_SSCLK

H_STP_CPU# <24>

CLK_MCH_BCLK <10>

CLK_MCH_BCLK# <10>

CLK_CPU_BCLK <7>

CLK_CPU_BCLK# <7>

CLK_CPU_ITP <7>

CLK_CPU_ITP# <7>

CLK_PCIE_LOM <29>

CLK_PCIE_LOM# <29>

LOM_CLKREQ# <29>

CLK_MCH_3GPLL <12>

CLK_MCH_3GPLL# <12>

CLK_3GPLLREQ# <10>

CLK_PCIE_ICH <24>

CLK_PCIE_ICH# <24>

CLK_PCIE_MINI2 <36>

CLK_PCIE_MINI2# <36>

MINI2CLK_REQ# <36>

CLK_PCIE_MINI1 <36>

CLK_PCIE_MINI1# <36>

MINI1CLK_REQ# <36>

DREF_SSCLK <10>

DREF_SSCLK# <10>

DREF_SSCLK#

R1 49.9_0402_1%~D

R2 49.9_0402_1%~D

R3 49.9_0402_1%~D

R6 49.9_0402_1%~D

R7 49.9_0402_1%~D

R8 49.9_0402_1%~D

R9 49.9_0402_1%~D

R10 49.9_0402_1%~D

R11 49.9_0402_1%~D

R12 49.9_0402_1%~D

R13 49.9_0402_1%~D

R14 49.9_0402_1%~D

R16 49.9_0402_1%~D

R17 49.9_0402_1%~D

R18 49.9_0402_1%~D

R19 49.9_0402_1%~D

R20 49.9_0402_1%~D

R21 49.9_0402_1%~D

R22 49.9_0402_1%~D

R23 49.9_0402_1%~D

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

12

12

12

12

12

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Clock Generator

LA-3741P

653Friday, January 26, 2007

1

of

0.1

Page 7

5

4

3

2

1

H_A#[3..31]<10>

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

D D

H_REQ#[0..4]<10>

H_ADSTB#0<10>

C C

R82

56_0402_5%~D

@

1 2

C18

+1.05V_VCCP

B B

H_THERMDA<18>

2200P_0402_50V7K~D

H_THERMDC<18>

H_THERMDA, H_THERMDC routing together.

Trace width / Spacing = 10 / 10 mil

A A

H_ADSTB#1<10>

CLK_CPU_BCLK<6>

CLK_CPU_BCLK#<6>

H_ADS#<10>

H_BNR#<10>

H_BPRI#<10>

H_BR0#<10>

H_DEFER#<10>

H_DRDY#<10>

H_HIT#<10>

H_HITM#<10>

H_LOCK#<10>

H_RESET#<10>

H_RS#[0..2]<10>

H_TRDY#<10>

ITP_DBRESET#<24,40>

H_DBSY#<10>

H_DPSLP#<23>

H_DPRSTP#<23,50>

H_DPWR#<10>

CPU_PROCHOT#<39>

H_PWRGOOD<23>

H_CPUSLP#<10,23>

1

2

H_THERMTRIP#<18>

5

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_DBRESET#

H_DBSY#

H_DPSLP#

H_DPRSTP#

H_DPWR#

ITP_BPM#4

ITP_BPM#5

CPU_PROCHOT#

H_CPUSLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

H_THERMDA

H_THERMDC

H_THERMTRIP#

TEST2

R84 51_0402_5%~D

R579 1K_0402_5%~D@

1 2

1 2

U2A

J4

A3#

L4

M3

K5

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

K3

H2

K2

J3

L5

L2

V4

A22

A21

H1

E2

G5

F1

H5

F21

G6

E4

D20

H4

B1

F3

F4

G3

G2

AD4

AD3

AD1

AC4

C20

E1

B5

E5

D24

AC2

AC1

D21

D6

D7

AC5

AA6

AB3

C26

D25

AB5

AB6

A24

A25

C7

YONAH-ULV

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

ADDR GROUP

A25#

A26#

A27#

A28#

A29#

A30#

A31#

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

ADSTB0#

ADSTB1#

BCLK0

HOST CLK

BCLK1

ADS#

BNR#

BPRI#

BR0#

DEFER#

DRDY#

HIT#

CONTROL

HITM#

IERR#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

BPM0#

BPM1#

BPM2#

BPM3#

DBR#

DBSY#

DPSLP#

DPRSTP#

DPWR#

PRDY#

PREQ#

PROCHOT#

PWRGOOD

SLP#

TCK

TDI

TDO

TEST1

TEST2

TMS

TRST#

THERMDA

THERMDC

THERMTRIP#

MISC

THERMAL

DIODE

Yonah-ULV_1.06G SC_UFCBGA479~D

DATA GROUP

LEGACY CPU

For Yonah B0

4

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

LINT0

LINT1

STPCLK#

+1.05V_VCCP

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

INIT#

SMI#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

1 2

R83 56_0402_5%~D

1 2

R468 75_0402_5%~D

F24

E26

H22

F23

G25

E25

E23

K24

G24

J24

J23

H26

F26

K22

H25

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

J26

M26

V23

AC20

H23

M24

W24

AD23

G22

N25

Y25

AE24

A6

A5

C4

B3

C6

B4

D5

A3

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_A20M#

H_FERR#

H_IGNNE#

H_INIT#

H_INTR

H_NMI

H_STPCLK#

H_SMI#

H_THERMTRIP#

CPU_PROCHOT#TEST1

H_D#0

E22

H_STPCLK# <23>

Link CIS

H_DINV#0 <10>

H_DINV#1 <10>

H_DINV#2 <10>

H_DINV#3 <10>

H_A20M# <23>

H_FERR# <23>

H_IGNNE# <23>

H_INIT# <23>

H_INTR <23>

H_NMI <23>

H_SMI# <23>

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

H_D#[0..63] <10>

ITP_TDO

1 2

R80 22.6_0402_1%~D

H_DSTBN#[0..3] <10>

H_DSTBP#[0..3] <10>

+1.05V_VCCP

1

2

+3.3V_SUS

+1.05V_VCCP

1

C17

2

0.1U_0402_16V4Z~D

C633

1 2

R73 150_0402_1%~D

1 2

R74 51_0402_5%~D

1 2

R75 54.9_0402_1%~D

1 2

R76 39_0402_5%~D

1 2

R78 150_0402_1%~D

1 2

R575 54.9_0402_1%~D@

1 2

R79 680_0402_5%~D

1 2

R81 27.4_0402_1%~D

0.1U_0402_16V4Z~D

ITP_DBRESET#

ITP_TDO

H_RESET#

ITP_TMS

ITP_TDI

ITP_BPM#5

ITP_TRST#

ITP_TCK

This shall place near CPU

+1.05V_VCCP

J2

28

VTT1

27

VTT0

26

ITP_DBRESET#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

R77

22.6_0402_1%~D

H_RESET#

1 2

CLK_CPU_ITP<6>

CLK_CPU_ITP#<6>

ITP_BPM#4

ITP_BPM#5

ITP_TCK

CLK_CPU_ITP

CLK_CPU_ITP#

ITP_TCK

ITP_TRST#

ITP_TMS

ITP_TDI

VTAP

25

DBR#

24

DBA#

23

BPM0#

22

GND5

21

BPM1#

20

GND4

19

BPM2#

18

GND3

17

BPM3#

16

GND2

15

BPM4#

14

GND1

13

BPM5#

12

RESET#

11

FBO

10

GND0

9

BCLKP

8

BCLKN

7

TDO

6

NC2

5

TCK

4

NC1

3

TRST#

2

TMS

1

TDI

GND7

MOLEX_52435-2891_28P~D@

30

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

2

Date: Sheet

Compal Electronics, Inc.

Yonah-ULV in mFCPGA479

LA-3741P

753Friday, January 26, 2007

1

of

0.1

Page 8

5

4

3

2

1

Length match within 25 mils

VCCSENSE<50>

VSSSENSE<50>

+1.5V_RUN

D D

+VCC_CORE

1 2

R88 100_0402_1%~D

1 2

R89 100_0402_1%~D

Layout close CPU

VCCSENSE

VSSSENSE

1

C20

C19

2

0.01U_0402_16V7K~D

Close to U2.B26

10U_0805_6.3V6M~D

V_CPU_GTLREF

+1.05V_VCCP

R_A

12

R87

1K_0402_1%~D

R_B

12

R90

2K_0402_1%~D

VCCSENSE/VSSSENSE

Layout close CPU PIN AD26

0.5 inch (max)

C C

B B

trace width 18mil,

space 7mil, for

other signal 15mil

12

R91

R92

27.4_0402_1%~D

CPU_BSEL CPU_BSEL2 CPU_BSEL1

133

166

00

0

12

12

R93

27.4_0402_1%~D

54.9_0402_1%~D

1

Resistor placed within

0.5" of CPU pin.Trace

should be at least 25

12

mils away from any

other toggling signal.

R94

54.9_0402_1%~D

CPU_BSEL0

1

1

1

2

V_CPU_GTLREF

CPU_MCH_BSEL0<6,10>

CPU_MCH_BSEL1<6,10>

CPU_MCH_BSEL2<6,10>

+1.05V_VCCP

H_PSI#<50>

VID0<50>

VID1<50>

VID2<50>

VID3<50>

VID4<50>

VID5<50>

VID6<50>

+VCC_CORE

VCCSENSE

VSSSENSE

H_PSI#

VID0

VID1

VID2

VID3

VID4

VID5

VID6

COMP0

COMP1

COMP2

COMP3

U2B

AF7

VCCSENSE

AE7

VSSSENSE

B26

VCCA

K6

VCCP

J6

VCCP

M6

VCCP

N6

VCCP

YONAH-ULV

T6

VCCP

R6

VCCP

K21

VCCP

J21

VCCP

M21

VCCP

N21

VCCP

T21

VCCP

R21

VCCP

V21

VCCP

W21

VCCP

V6

VCCP

G21

VCCP

AE6

PSI#

AD6

VID0

AF5

VID1

AE5

VID2

AF4

VID3

AE3

VID4

AF2

VID5

AE2

VID6

AD26

GTLREF

B22

BSEL0

B23

BSEL1

C21

BSEL2

R26

COMP0

U26

COMP1

U1

COMP2

V1

COMP3

E7

VCC

AB20

VCC

AA20

VCC

AF20

VCC

AE20

VCC

AB18

VCC

AB17

VCC

AA18

VCC

AA17

VCC

AD18

VCC

AD17

VCC

AC18

VCC

AC17

VCC

AF18

VCC

AF17

VCC

D2

RSVD

F6

RSVD

D3

RSVD

C1

RSVD

AF1

RSVD

D22

RSVD

C23

RSVD

C24

RSVD

AA1

RSVD

AA4

RSVD

AB2

RSVD

AA3

RSVD

M4

RSVD

N5

RSVD

T2

RSVD

V3

RSVD

B2

RSVD

C3

RSVD

T22

RSVD

B25

RSVD

Yonah-ULV_1.06G SC_UFCBGA479~D

AB26

VSS

AA25

VSS

AD25

VSS

AE26

VSS

AB23

VSS

AC24

VSS

AF24

VSS

AE23

VSS

AA22

VSS

AD22

VSS

AC21

VSS

AF21

VSS

AB19

VSS

AA19

VSS

AD19

VSS

AC19

VSS

AF19

VSS

AE19

VSS

AB16

VSS

AA16

VSS

AD16

VSS

AC16

VSS

AF16

VSS

AE16

VSS

AB13

VSS

AA14

VSS

AD13

VSS

AC14

VSS

AF13

VSS

AE14

VSS

AB11

VSS

AA11

VSS

AD11

VSS

AC11

VSS

AF11

VSS

AE11

VSS

AB8

VSS

AA8

VSS

AD8

VSS

AC8

VSS

AF8

VSS

AE8

VSS

AA5

VSS

AD5

VSS

AC6

VSS

AF6

VSS

AB4

VSS

AC3

VSS

AF3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE4

AB1

AA2

AD2

AE1

B6

C5

F5

E6

H6

J5

M5

L6

P6

R5

V5

U6

Y6

A4

D4

E3

H3

G4

K4

L3

P3

N4

T4

U3

Y3

W4

D1

C2

F2

G1

POWER, GROUNG, RESERVED SIGNALS AND NC

+VCC_CORE

U2C

AE18

VCC

AE17

VCC

AB15

VCC

AA15

VCC

AD15

VCC

AC15

VCC

AF15

VCC

AE15

VCC

AB14

VCC

AA13

VCC

AD14

VCC

AC13

VCC

AF14

VCC

AE13

VCC

AB12

VCC

AA12

VCC

YONAH-ULV

AD12

VCC

AC12

VCC

AF12

VCC

AE12

VCC

AB10

VCC

AB9

VCC

AA10

VCC

AA9

VCC

AD10

VCC

AD9

VCC

AC10

VCC

AC9

VCC

AF10

VCC

AF9

VCC

AE10

POWER, GROUND

VCC

AE9

VCC

AB7

VCC

AA7

VCC

AD7

VCC

AC7

VCC

B20

VCC

A20

VCC

F20

VCC

E20

VCC

B18

VCC

B17

VCC

A18

VCC

A17

VCC

D18

VCC

D17

VCC

C18

VCC

C17

VCC

F18

VCC

F17

VCC

E18

VCC

E17

VCC

B15

VCC

A15

VCC

D15

VCC

C15

VCC

F15

VCC

E15

VCC

B14

VCC

A13

VCC

D14

VCC

C13

VCC

F14

VCC

E13

VCC

B12

VCC

A12

VCC

D12

VCC

C12

VCC

F12

VCC

E12

VCC

B10

VCC

B9

VCC

A10

VCC

A9

VCC

D10

VCC

D9

VCC

C10

VCC

C9

VCC

F10

VCC

F9

VCC

E10

VCC

E9

VCC

B7

VCC

A7

VCC

F7

VCC

Yonah-ULV_1.06G SC_UFCBGA479~D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K1

J2

M2

N1

T1

R2

V2

W1

A26

D26

C25

F25

B24

A23

D23

E24

B21

C22

F22

E21

B19

A19

D19

C19

F19

E19

B16

A16

D16

C16

F16

E16

B13

A14

D13

C14

F13

E14

B11

A11

D11

C11

F11

E11

B8

A8

D8

C8

F8

E8

G26

K26

J25

M25

N26

T26

R25

V25

W26

H24

G23

K23

L24

P24

N23

T23

U24

Y24

W23

H21

J22

M22

L21

P21

R22

V22

U21

Y21

Link CIS

Link CIS

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Yonah-ULV in mFCBGA479

LA-3741P

853Friday, January 26, 2007

1

0.1

of

Page 9

5

+VCC_CORE

Place these inside

socket cavity on L8

(North side

Secondary)

D D

Place these inside

socket cavity on L8

(Sorth side

Secondary)

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

C21

22U_0805_6.3V6M~D

C31

22U_0805_6.3V6M~D

<BOM Structure>

C693

2@

10U_0805_4VAM~D

1

C22

2@

10U_0805_4VAM~D

2

1

C32

@

10U_0805_4VAM~D

2

1

C694

2@

10U_0805_4VAM~D

2

1

C23

22U_0805_6.3V6M~D

2

1

C33

2@

10U_0805_4VAM~D

2

1

C695

@

10U_0805_4VAM~D

2

4

1

C24

@

10U_0805_4VAM~D

2

1

C34

22U_0805_6.3V6M~D

2

1

C696

@

10U_0805_4VAM~D

2

1

C25

2@

10U_0805_4VAM~D

2

1

C35

2@

10U_0805_4VAM~D

2

1

C697

2@

10U_0805_4VAM~D

2

1

C26

22U_0805_6.3V6M~D

2

1

C36

22U_0805_6.3V6M~D

2

1

C698

2@

10U_0805_4VAM~D

2

1

C27

2@

10U_0805_4VAM~D

2

1

C37

2@

10U_0805_4VAM~D

2

1

C699

2@

10U_0805_4VAM~D

2

3

1

C28

22U_0805_6.3V6M~D

2

1

C38

2@

10U_0805_4VAM~D

2

1

C700

2@

10U_0805_4VAM~D

2

1

C29

22U_0805_6.3V6M~D

2

1

C39

2@

10U_0805_4VAM~D

2

1

C701

@

10U_0805_4VAM~D

2

1

2

1

2

1

2

C30

2@

10U_0805_4VAM~D

C40

2@

10U_0805_4VAM~D

C702

@

10U_0805_4VAM~D

2

1

+VCC_CORE

1

C703

2@

10U_0805_4VAM~D

2

C C

1

C704

2@

10U_0805_4VAM~D

2

Note:

C21,C23,C26,C28,C29,C31,C34,C36

use 22U on Single Core CPU and

use 10U on Dual Core CPU.

High Frequence Decoupling

Temp. characteristics: X5R

Operating range: -55~+85degree

Near VCORE regulator.

+VCC_CORE

Note: C41,C44

will change to

220U 2.5V 6M on

South Side Secondary

1

+

C43

C42

2@

2@

2

220U_D_2VM_R7M~D

+

C705

+

@

2

2

330U_D_2.5VM_R6M~D

220U_D_2VM_R7M~D

1

+

C44

C41

2

330U_D_2.5VM_R6M~D

330U_D_2.5VM_R6M~D

1

1

North Side Secondary

1

1

+

+

C706

@

2

2

330U_D_2.5VM_R6M~D

Dual Core CPU for

CPU transition

noise

ESR <= 1.5m ohm

Capacitor = 1320uF

7mOhm

7mOhm

6mOhm

6/7mOhm

6/7mOhm

B B

+1.05V_VCCP

1

+

C45

@

2

330U_D2E_2.5VM_R9~D

PS CAP

1

C46

0.1U_0402_10V7K~D

2

PS CAP

PS CAP

1

C47

0.1U_0402_10V7K~D

2

PS CAP

1

2

CRB was 270uF

6mOhm

PS CAP

PS CAP

C48

0.1U_0402_16V4Z~D

1

C49

0.1U_0402_16V4Z~D

2

1

C50

0.1U_0402_10V7K~D

2

1

C51

0.1U_0402_10V7K~D

2

Place these inside

socket cavity on L8

(North side

Secondary)

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

CPU Bypass

LA-3741P

953Friday, January 26, 2007

1

0.1

of

Page 10

5

4

3

2

1

AF33

AG1

AM30

AG33

AF1

AK1

AN30

AN21

AN22

AF26

AF25

AG14

AF12

AK14

AH12

AJ21

AF11

AE12

AF14

AJ14

AJ12

AN12

AN14

AA33

AE1

Y29

Y32

Y28

Y31

V28

V31

V29

V32

AJ1

U3B

DMI_RXN_0

DMI_RXN_1

DMI_RXP_0

DMI_RXP_1

DMI_TXN_0

DMI_TXN_1

DMI_TXP_0

DMI_TXP_1

SM_CK_0

SM_CK_1

SM_CK_2

SM_CK_3

SM_CK#_0

SM_CK#_1

SM_CK#_2

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_OCDCOMP_0

SM_OCDCOMP_1

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMPN

SM_RCOMPP

SM_VREF_0

SM_VREF_1

Calistoga-GMS_FCBGA998~D

CFG_0

CFG_1

CFG_2

CFG_3

CFG_5

CFG_6

DMI

RESERVED1

RESERVED2

RESERVED7

RESERVED8

RESERVED9

CFG/RSVD

DDR2 MUXING

PM_ICHSYNC#

PM_BMBUSY#

PM_EXTTS#_0

PM

PM_EXTTS#_1

THRMTRIP#

PWROK

RSTIN#

D_REFCLKN

D_REFCLKP

CLK

D_REFSSCLKN

D_REFSSCLKP

CLKREQ#

C18

E18

G20

G18

J20

J18

K32

K31

C17

F18

A3

E31

G21

F26

H26

J15

AB29

W27

A27

A26

J33

H33

J22

CPU_MCH_BSEL0

CPU_MCH_BSEL1

CPU_MCH_BSEL2

CFG3

CFG5

CFG6

PM_EXTTS#0

PM_EXTTS#1

ICH_PWRGD

PLTRST_R#

1 2

MCH_ICH_SYNC# <22>

PM_BMBUSY# <24>

PM_EX TTS#0 <15>

PM_EX TTS#1 <24>

THERMTRIP_MCH# <18>

ICH_PWRGD <24,43>

MCH_DREFCLK# <6>

MCH_DREFCLK <6>

DREF_SSCLK# <6>

DREF_SSCLK <6>

CLK_3GPLLREQ# <6>

Strap Pin Table

CFG5

CFG19

(DMI Lane Reversal)

Calistoga-GM S n ot ha ve CFG4,CFG[7..18],CFG[20]

Need to double check

CFG19<13>

Low = DMI x 2

High = DMI x 4

Low = Normal

Operation (Default):

Lane number in Order

High = Reverse Lane

PM_EXTTS#0

PM_EXTTS#1

CPU_MCH_BSEL0

THERMTRIP_MCH#

CFG5

R108 10K_0402_5%~D

R109 10K_0402_5%~D@

1 2

R110 1K_0402_5%~D @

1 2

R113 1K_0402_5%~D @

1 2

R114 75_0402_5%~D

1 2

R115 2.2K_0402_5%~D

12

12

CPU_MCH_BSEL0 <6,8>DMI_MRX_ITX_N0<24>

CPU_MCH_BSEL1 <6,8>

CPU_MCH_BSEL2 <6,8>

T2PAD~D

T3PAD~D

PLTRST# <20,22,24,29,36>

R100100_0402_1%~D

*

+3.3V_RUN

+1.05V_VCCP

H_D#[0..63]<7>

D D

C C

+1.05V_VCCP

12

12

R103

R104

54.9_0402_1%~D

54.9_0402_1%~D

B B

12

R106

24.9_0402_1%~D

Layout Note:

H_XRCOMP & H_YRCOMP trace width

A A

and spacing is 10/20

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_XRCOMP

H_XSCOMP

H_SWNG0

H_YRCOMP

H_YSCOMP

H_SWNG1

12

R107

24.9_0402_1%~D

C4

F6

H9

H6

F7

E3

C2

C3

K9

F5

J7

K7

H8

E5

K8

J8

J2

J3

N1

M5

K5

J5

H3

J4

N3

M4

M3

N8

N6

K3

N9

M1

V8

V9

R6

T8

R2

N5

N2

R5

U7

R8

T4

T7

R3

T5

V6

V3

W2

W1

V2

W4

W7

W5

V5

AB4

AB8

W8

AA9

AA8

AB1

AB7

AA2

AB5

A10

A6

C15

J1

K1

H1

U3A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

V_DDR_MCH_REF<15,16,17,49>

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_VREF0

H_BNR#

H_BPRI#

H_BREQ0#

H_CPURST#

H_VREF1

HCLKN

HOST

HCLKP

H_DBSY#

H_DEFER#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DPWR#

H_DRDY#

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_HIT#

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_SLPCPU#

H_TRDY#

Calistoga-GMS_FCBGA998~D

V_DDR_MCH_REF

C55

@

0.1U_0402_10V6K~D

H_A#3

F8

H_A#4

D12

H_A#5

C13

H_A#6

A8

H_A#7

E13

H_A#8

E12

H_A#9

J12

H_A#10

B13

H_A#11

A13

H_A#12

G13

H_A#13

A12

H_A#14

D14

H_A#15

F14

H_A#16

J13

H_A#17

E17

H_A#18

H15

H_A#19

G15

H_A#20

G14

H_A#21

A15

H_A#22

B18

H_A#23

B15

H_A#24

E14

H_A#25

H13

H_A#26

C14

H_A#27

A17

H_A#28

E15

H_A#29

H17

H_A#30

D17

H_A#31

G17

H_ADS#

F10

H_ADSTB#0

C12

H_ADSTB#1

H16

H_VREF

E2

H_BNR#

B9

H_BPRI#

C7

H_BR0#

G8

H_RESET#

B10

H_VREF

E1

AA6

AA5

H_DBSY#

C10

H_DEFER#

C6

H5

J6

T9

U6

H_DPWR#

G7

H_DRDY#

E6

H_DSTBN#0

F3

H_DSTBN#1

M8

H_DSTBN#2

T1

H_DSTBN#3

AA3

H_DSTBP#0

F4

H_DSTBP#1

M7

H_DSTBP#2

T2

H_DSTBP#3

AB3

H_HIT#

C8

H_HITM#

B4

H_LOCK#

C5

H_REQ#0

G9

H_REQ#1

E9

H_REQ#2

G12

H_REQ#3

B8

H_REQ#4

F12

H_RS#0

A5

H_RS#1

B6

H_RS#2

G10

H_CPUSLP#

E8

H_TRDY#

E10

1

2

H_A#[3..31] <7>

+1.05V_VCCP

12

R95

221_0402_1%~D

12

R96

100_0402_1%~D

+1.05V_VCCP

12

H_ADS# <7>

H_ADSTB#0 <7>

H_ADSTB#1 <7>

H_BNR# <7>

H_BPRI# <7>

H_BR0# <7>

H_RESET# <7>

CLK_MCH_BCLK# <6>

CLK_MCH_BCLK <6>

H_DBSY# <7>

H_DEFER# <7>

H_DINV#0 <7>

H_DINV#1 <7>

H_DINV#2 <7>

H_DINV#3 <7>

H_DPWR# <7>

H_DRDY# <7>

H_DSTBN#[0..3] <7>

H_DSTBP#[0..3] <7>

H_HIT# <7>

H_HITM# <7>

H_LOCK# <7>

H_REQ#[0..4] <7>

H_RS#[0..2] <7>

H_CPUSLP# <7,23>

H_TRDY# <7>

12

+1.05V_VCCP

12

12

R105

R97

221_0402_1%~D

R98

100_0402_1%~D

R102

100_0402_1%~D

200_0402_1%~D

Stuff R111 & R112 for A1 Calistoga

1

2

1

2

1

C54

2

H_SWNG1

C52

0.1U_0402_10V6K~D

H_SWNG0

0.1U_0402_10V6K~D

H_VREF

0.1U_0402_10V6K~D

+1.8V_SUS

C53

R99 80.6_0402_1%~D

R101 80.6_0402_1%~D

DMI_MRX_ITX_N1<24>

DMI_MRX_ITX_P0<24>

DMI_MRX_ITX_P1<24>

DMI_MTX_IRX_N0<24>

DMI_MTX_IRX_N1<24>

DMI_MTX_IRX_P0<24>

DMI_MTX_IRX_P1<24>

T13 PAD~D

DDR_CKE2_DIMMA<15>

DDR_CKE3_DIMMA<15>

T14 PAD~D

DDR_CS2_DIMMA#<15>

DDR_CS3_DIMMA#<15>

T15 PAD~D

1 2

1 2

V_DDR_MCH_REF

Layout Note:

Route as short

as possible

12

R111

@

40.2_0402_1%~D

DMI_MRX_ITX_N0

DMI_MRX_ITX_N1

DMI_MRX_ITX_P0

DMI_MRX_ITX_P1

DMI_MTX_IRX_N0

DMI_MTX_IRX_N1

DMI_MTX_IRX_P0

DMI_MTX_IRX_P1

12

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR2

M_CLK_DDR3

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#2

M_CLK_DDR#3

DDR_CKE0

DDR_CKE1

DDR_CKE2_DIMMA

DDR_CKE3_DIMMA

DDR_CS0#

DDR_CS1#

DDR_CS2_DIMMA#

DDR_CS3_DIMMA#

M_OCDOCMP0

M_OCDOCMP1

M_ODT0

M_ODT1

M_ODT2

M_ODT3

SMRCOMPN

SMRCOMPP

M_OCDOCMP0

M_OCDOCMP1

M_CLK_DDR0<16,17>

M_CLK_DDR1<16,17>

M_CLK_DDR2<15>

M_CLK_DDR3<15>

M_CLK_DDR#0<16,17>

M_CLK_DDR#1<16,17>

M_CLK_DDR#2<15>

M_CLK_DDR#3<15>

DDR_CKE0<16,17>

DDR_CS0#<16,17>

M_ODT0<16,17>

M_ODT2<15>

M_ODT3<15>

R112

@

40.2_0402_1%~D

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Calistoga(1 of 5)

LA-3741P

1

10 53Friday, January 26, 2007

0.1

of

Page 11

5

4

3

2

1

D D

DDR_A_BS0<16,17>

DDR_A_BS1<16,17>

DDR_A_BS2<16,17>

DDR_A_DM[0..7]<15,16>

DDR_A_DQS[0..7]<15,16>

DDR_A_DQS#[0..7]<15,16>

C C

B B

DDR_A_MA[0..13]<16,17>

DDR_B_MA[0..13]<15>

DDR_A_CAS#<16,17>

DDR_A_RAS#<16,17>

DDR_A_WE#<16,17>

DDR_B_BS0<15>

DDR_B_BS1<15>

DDR_B_BS2<15>

T4 PAD~D

T5 PAD~D

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_CAS#

DDR_A_RAS#

SA_RCVENIN#

SA_RCVENOUT#

DDR_A_WE#

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7 DDR_A_D63

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

AK12

AH11

AG17

AB30

AL31

AF30

AK26

AC28

AJ30

AK33

AL25

AM2

AC29

AK30

AJ33

AM25

AM3

AJ15

AM17

AM15

AH15

AK15

AN15

AJ18

AF19

AN17

AL17

AG16

AL18

AG18

AL14

AJ17

AK18

AN28

AM28

AH17

AH21

AJ20

AE27

AN20

AL21

AK21

AK22

AL22

AH22

AG22

AF21

AM21

AE21

AL20

AE22

AE26

AE20

AG7

AK5

AH3

AN9

AH8

AE3

AN8

AE2

AL9

AJ8

U3C

SA_BS_0

SA_BS_1

SA_BS_2

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

SB_BS_0

SB_BS_1

SB_BS_2

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

DDR2 SYSTEM MEMORY

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SB_CAS#

SB_RAS#

SB_WE#

Calistoga-GMS_FCBGA998~D

AC31

AB28

AE33

AF32

AC33

AB32

AB31

AE31

AH31

AK31

AL28

AK27

AH30

AL32

AJ28

AJ27

AH32

AF31

AH27

AF28

AJ32

AG31

AG28

AG27

AN27

AM26

AJ26

AJ25

AL27

AN26

AH25

AG26

AM12

AL11

AH9

AK9

AM11

AK11

AM8

AK8

AG9

AF9

AF8

AK6

AF7

AG11

AJ6

AH6

AN6

AM6

AK3

AL2

AM5

AL5

AJ3

AJ2

AG2

AF3

AE7

AF6

AH5

AG3

AG5

AF5

AG19

AG21

AG20

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_B_CAS#

DDR_B_RAS#

DDR_B_WE#

DDR_A_D[0..63] <15,16>

DDR_B_CAS# <15>

DDR_B_RAS# <15>

DDR_B_WE# <15>

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Calistogo(2 of 5)

LA-3741P

11 53Friday, January 26, 2007

1

0.1

of

Page 12

5

D D

4

3

2

1

R116

24.9_0402_1%~D

1 2

C56 0.1U_0402_10V6K~D

C57 0.1U_0402_10V6K~D

C58 0.1U_0402_10V6K~D

C59 0.1U_0402_10V6K~D

C60 0.1U_0402_10V6K~D

C61 0.1U_0402_10V6K~D

C62 0.1U_0402_10V6K~D

C63 0.1U_0402_10V6K~D

12

AA26

H27

J27

Y26

H20

H22

A24

A23

E25

F25

C25

D25

F27

D27

H25

H30

G29

F28

E28

G28

H28

K30

K27

J29

J30

K29

D30

C30

A30

A29

G31

F32

D31

H31

G32

C31

F33

D33

F30

E33

D32

F29

U3F

SDVO_CTRLDATA

SDVO_CTRLCLK

G_CLKN

G_CLKP

CRT_DDC_CLK

CRT_DDC_DATA

CRT_BLUE

CRT_BLUE#

CRT_GREEN

CRT_GREEN#

CRT_RED

CRT_RED#

CRT_VSYNC

CRT_HSYNC

CRT_IREF

L_BKLTCTL

L_BKLTEN

L_CLKCTLA

L_CTLBDATA

L_DDC_CLK

L_DDC_DATA

L_VDDEN

L_IBG

L_VBG

L_VREFH

L_VREFL

LA_CLKN

LA_CLKP

LB_CLKN

LB_CLKP

LA_DATAN_0

LA_DATAN_1

LA_DATAN_2

LA_DATAP_0

LA_DATAP_1

LA_DATAP_2

LB_DATAN_0

LB_DATAN_1

LB_DATAN_2

LB_DATAP_0

LB_DATAP_1

LB_DATAP_2

EXP_A_COMPI

EXP_A_ICOMPO

SDVO_TVCLKIN#

SDVO_INT#

SDVO_FLDSTALL#

MISC

SDVO_TVCLKIN

SDVO_INT

SDVO_FLDSTALL

SDVO

SDVO_RED#

SDVO_GREEN#

SDVO_BLUE#

SDVO_CLKN

SDVO_RED

SDVO_GREEN

SDVO_BLUE

SDVO_CLKP

TV_DACA

TV_DACB

TV_DACC

TV_IREF

TV_IRTNA

TV

TV_IRTNB

LVDS VGA

TV_IRTNC

TV_DCONSEL0

TV_DCONSEL1

Calistoga-GMS_FCBGA998~D

R28

M28

N30

R30

T29

M30

P30

T30

DVO_RED#_C

P28

DVO_GREEN#_C

N32

DVO_BLUE#_C

P32

DVO_CLK#_C

T32

DVO_RED_C

N28

DVO_GREEN_C

M32

DVO_BLUE_C

P33

DVO_CLK_C

R32

A21

C20

E20

G23

B21

C21

D21

G26

J26

+PEGCOMP

TVIREF

VGA_BLU<21,38>

VGA_GRN<21,38>

VGA_RED<21,38>

BIA_PWM<19,40>

ENVDD<19>

12

LCD_A0-<19>

LCD_A1-<19>

LCD_A2-<19>

LCD_A0+<19>

LCD_A1+<19>

LCD_A2+<19>

LCD_ACLK-

LCD_ACLK+

LCD_A1-

LCD_A1+

LCD_A0-

LCD_A0+

LCD_A2-

LCD_A2+

SDVO_CTRLDATA

SDVO_CTRLCLK

G_CLK_DDC2

G_DAT_DDC2

CRT_IREF

BIA_PWM

PANEL_BKEN

LCTLA_CLK

LCTLB_DATA

LCD_DDCCLK

LCD_DDCDATA

L_IBG

LCD_ACLKLCD_ACLK+

LCD_A0LCD_A1LCD_A2-

LCD_A0+

LCD_A1+

LCD_A2+

C711

C712

C713

C714

2

1

1

2

1

2

1

2

SDVO_CTRLDATA<20>

SDVO_CTRLCLK<20>

CLK_MCH_3GPLL#<6>

CLK_MCH_3GPLL<6>

Close to U3.H25

C C

+3.3V_RUN

B B

A A

1 2

R580 2.2K_0402_5%~D

1 2

R581 2.2K_0402_5%~D

1 2

R123 10K_0402_5%~D

1 2

R124 10K_0402_5%~D

R126 150_0402_1%~D

R127 150_0402_1%~D

R128 150_0402_1%~D

12

12

12

LCD_DDCCLK

LCD_DDCDATA

LCTLA_CLK

LCTLB_DATA

VGA_RED

VGA_GRN

VGA_BLU

R117 255_0402_1%~D

VGA_VSYNC<21>

VGA_HSYNC<21>

12

PANEL_BKEN<19>

LCD_DDCCLK<19>

LCD_DDCDATA<19>

R118 1.5K_0402_1%~D

LCD_ACLK-<19>

LCD_ACLK+<19>

8.2P_0402_50V8J~D

3.3P_0402_50VJ~D

3.3P_0402_50VJ~D

3.3P_0402_50VJ~D

+1.5VRUN_PCIE

SDVOB_INT- <20>

SDVOB_INT+ <20>

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

R119

R122

150_0402_1%~D

4.99K_0402_1%~D

Close to U3.G23

12

R120

SDVOB_RED- <20>

SDVOB_GREEN- <20>

SDVOB_BLUE- <20>

SDVOB_CLK- <20>

SDVOB_RED+ <20>

SDVOB_GREEN+ <20>

SDVOB_BLUE+ <20>

SDVOB_CLK+ <20>

TV_CVBS <38>

TV_Y <38>

TV_C <38>

12

R121

150_0402_1%~D

150_0402_1%~D

G_CLK_DDC2

G_DAT_DDC2

+3.3V_RUN

12

12

R129

2.2K_0402_5%~D

R130

+3.3V_RUN

2.2K_0402_5%~D

13

Q3

G

2N7002W-7-F_SOT323~D

2

G

2

13

D

S

Q4

2N7002W-7-F_SOT323~D

CLK_DDC2

DAT_DDC2

CLK_DDC2 <21,38>

DAT_DDC2 <21,38>

D

S

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

Calistoga(3 of 5)

LA-3741P

12 53Friday, January 26, 2007

1

0.1

of

Page 13

5

4

3

2

1

+1.05V_VCCP

D D

1

C65

10U_0805_6.3V6M~D

1

+

2

1

C66

2

2

0.1U_0402_10V6K~D

0.1U_0402_10V6K~D

1

1

C68

2

2

10U_0805_6.3V6M~D

1

C64

2

0.1U_0402_10V6K~D

C67

C C

C70

220U_D2_4M_R45~D

CRB 270uF

+1.05V_VCCP

1

+

C71

B B

A A

2

220U_D2_4M_R45~D

5

U3H

T25

VCC_NCTF1

R25

VCC_NCTF2

P25

VCC_NCTF3

N25

VCC_NCTF4

M25

VCC_NCTF5

P24

VCC_NCTF6

N24

VCC_NCTF7

M24

VCC_NCTF8

Y22

VCC_NCTF9

W22

VCC_NCTF10

V22

AB10

AA10

U22

R22

N22

M22

W21

U21

R21

N21

M21

W20

U20

R20

N20

M20

N19

M19

N18

M18

N17

M17

N16

M16

N15

M15

W14

U14

R14

N14

M14

R10

N10

M10

T22

P22

Y21

V21

T21

P21

Y20

V20

T20

P20

Y19

P19

Y18

P18

Y17

P17

Y16

P16

Y15

P15

Y14

V14

T14

P14

T10

P10

L10

D1

A18

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VTT_NCTF1

VTT_NCTF2

VTT_NCTF3

VTT_NCTF4

VTT_NCTF5

VTT_NCTF6

RSVD_3

RSVD_4

RSVD_5

RSVD_6

NCTF

VCCAUX_NCTF1

VCCAUX_NCTF2

VCCAUX_NCTF3

VCCAUX_NCTF4

VCCAUX_NCTF5

VCCAUX_NCTF6

VCCAUX_NCTF7

VCCAUX_NCTF8

VCCAUX_NCTF9

VCCAUX_NCTF10

VCCAUX_NCTF11

VCCAUX_NCTF12

VCCAUX_NCTF13

VCCAUX_NCTF14

VCCAUX_NCTF15

VCCAUX_NCTF16

VCCAUX_NCTF17

VCCAUX_NCTF18

VCCAUX_NCTF19

VCCAUX_NCTF20

VCCAUX_NCTF21

VCCAUX_NCTF22

VCCAUX_NCTF23

VCCAUX_NCTF24

VCCAUX_NCTF25

VCCAUX_NCTF26

VCCAUX_NCTF27

VCCAUX_NCTF28

VCCAUX_NCTF29

VCCAUX_NCTF30

VCCAUX_NCTF31

VCCAUX_NCTF32

VCCAUX_NCTF33

VCCAUX_NCTF34

VCCAUX_NCTF35

VCCAUX_NCTF36

VCCAUX_NCTF37

VCCAUX_NCTF38

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VSS_NCTF13

VSS_NCTF14

VSS_NCTF15

VSS_NCTF16

VSS_NCTF17

VSS_NCTF18

VSS_NCTF19

CFG_19

RESERVED10

RESERVED11

RESERVED12

RESERVED13

RESERVED14

RESERVED15

RESERVED16

RESERVED17

RESERVED18

RESERVED19

RESERVED20

RESERVED21

RESERVED22

RESERVED23

RESERVED24

RESERVED25

Calistoga-GMS_FCBGA998~D

+1.5V_RUN

AD25

AC25

AB25

AD24

AC24

AD22

AD21

AD20

AD19

AD18

AD17

AD16

AD15

AD14

K14

AD13

Y13

W13

V13

U13

T13

R13

P13

N13

M13

AD12

Y12

W12

V12

U12

T12

R12

P12

N12

M12

AD11

AD10

K10

AN33

AA25

V25

U25

AA22

AA21

AA20

AA19

AA18

AA17

AA16

AA15

AA14

AA13

A4

A33

B2

AN1

C1

CFG19

K28

K25

K26

R24

T24

K21

K19

K20

K24

K22

J17

K23

K17

K12

K13

K16

K15

4

CFG19 <10>

U3E

AH33

VSS_1

Y33

VSS_2

V33

VSS_3

R33

VSS_4

G33

VSS_5

AK32

VSS_6

AG32

VSS_7

AE32

VSS_8

AC32

VSS_9

AA32

VSS_10

U32

VSS_11

H32

VSS_12

E32

VSS_13

C32

VSS_14

AM31

VSS_15

AJ31

VSS_16

AA31

VSS_17

U31

VSS_18

T31

VSS_19

R31

VSS_20

P31

VSS_21

N31

VSS_22

M31

VSS_23

J31

VSS_24

F31

VSS_25

AL30

VSS_26

AG30

VSS_27

AE30

VSS_28

AC30

VSS_29

AA30

VSS_30

Y30

VSS_31

V30

VSS_32

U30

VSS_33

G30

VSS_34

E30

VSS_35

B30

VSS_36

AA29

VSS_37

U29

VSS_38

R29

VSS_39

P29

VSS_40

N29

VSS_41

M29

VSS_42

H29

VSS_43

E29

VSS_44

B29

VSS_45

AK28

VSS_46

AH28

VSS_47

AE28

VSS_48

AA28

VSS_49

U28

VSS_50

T28

VSS_51

J28

VSS_52

D28

VSS_53

AM27

VSS_54

AF27

VSS_55

AB27

VSS_56

AA27

VSS_57

Y27

VSS_58

U27

VSS_59

T27

VSS_60

R27

VSS_61

P27

VSS_62

N27

VSS_63

M27

VSS_64

G27

VSS_65

E27

VSS_66

C27

VSS_67

B27

VSS_68

AL26

VSS_69

AH26