5

IPPSB-FA

PAGE

D D

C C

B B

01

03

04~09

1002DDR3 CHANNEL A_G/F

11

12

13 PLTRST_CPU# & SMbus

14

15~16

17~25

27~28

29~30

31~32

33~35

36

37~38

39

40

41

42

43~44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59~61

62

63~64

65

66~67

68

69

70~71

72

73

74

75

76

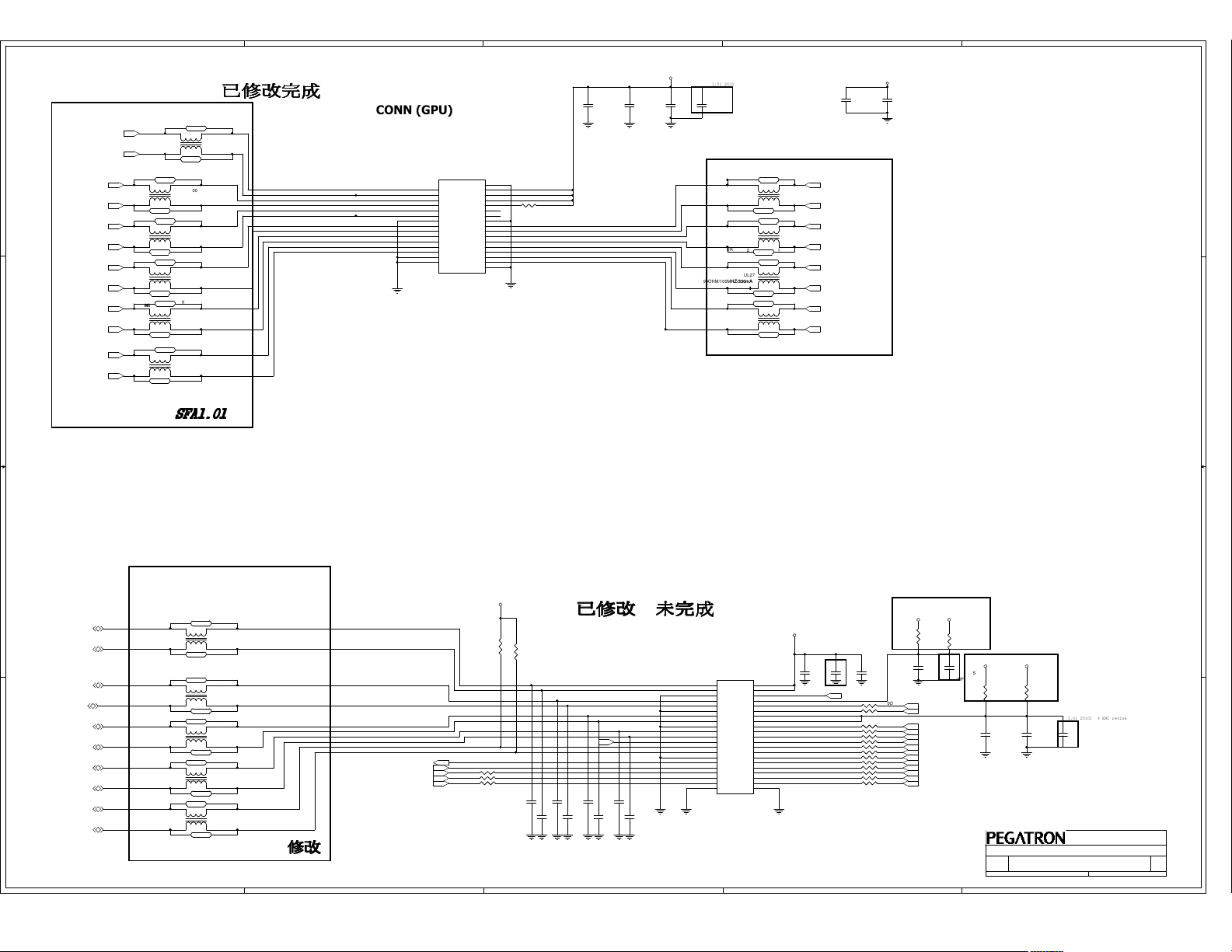

77 MXM.NVVDD

78 Card Reader RTS5139-GR

TITLE

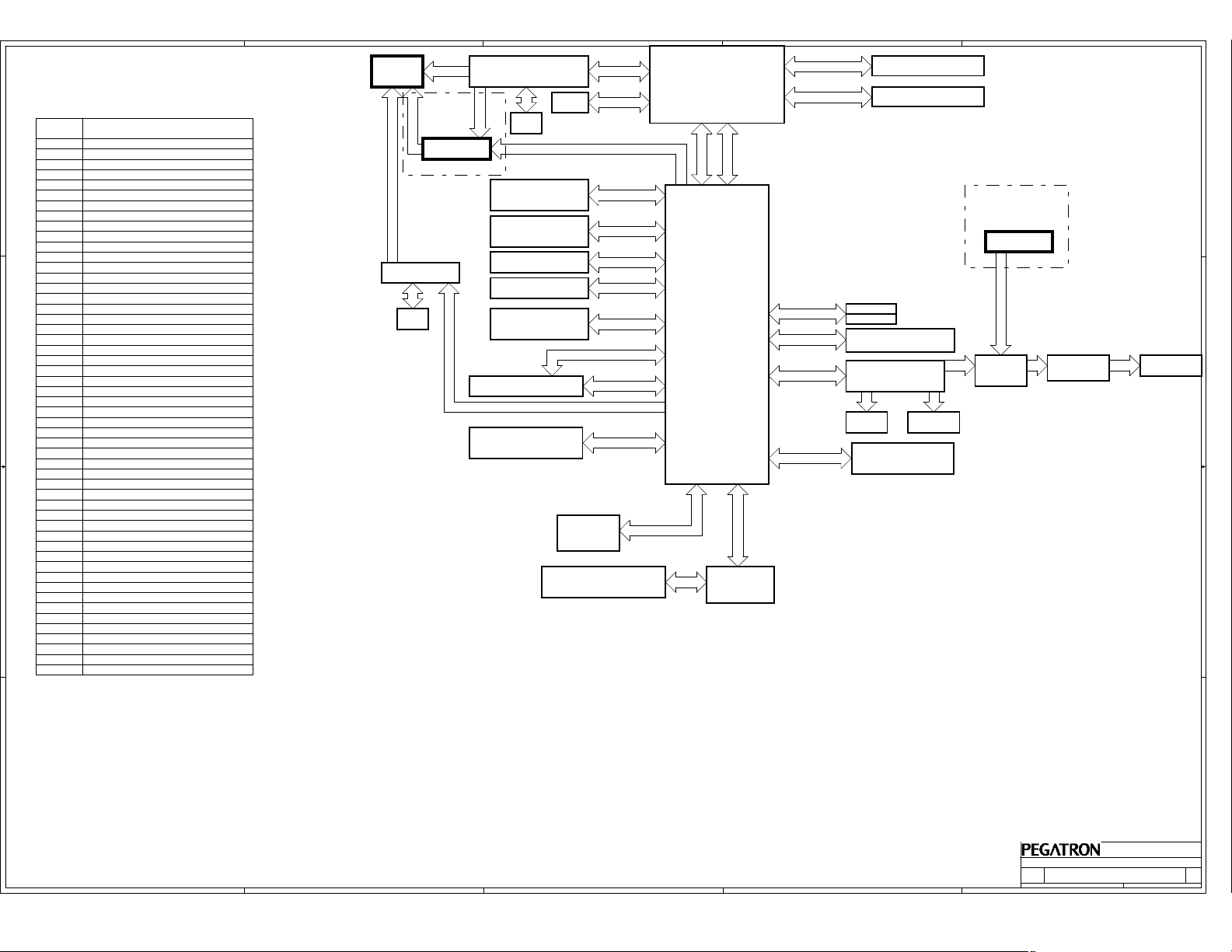

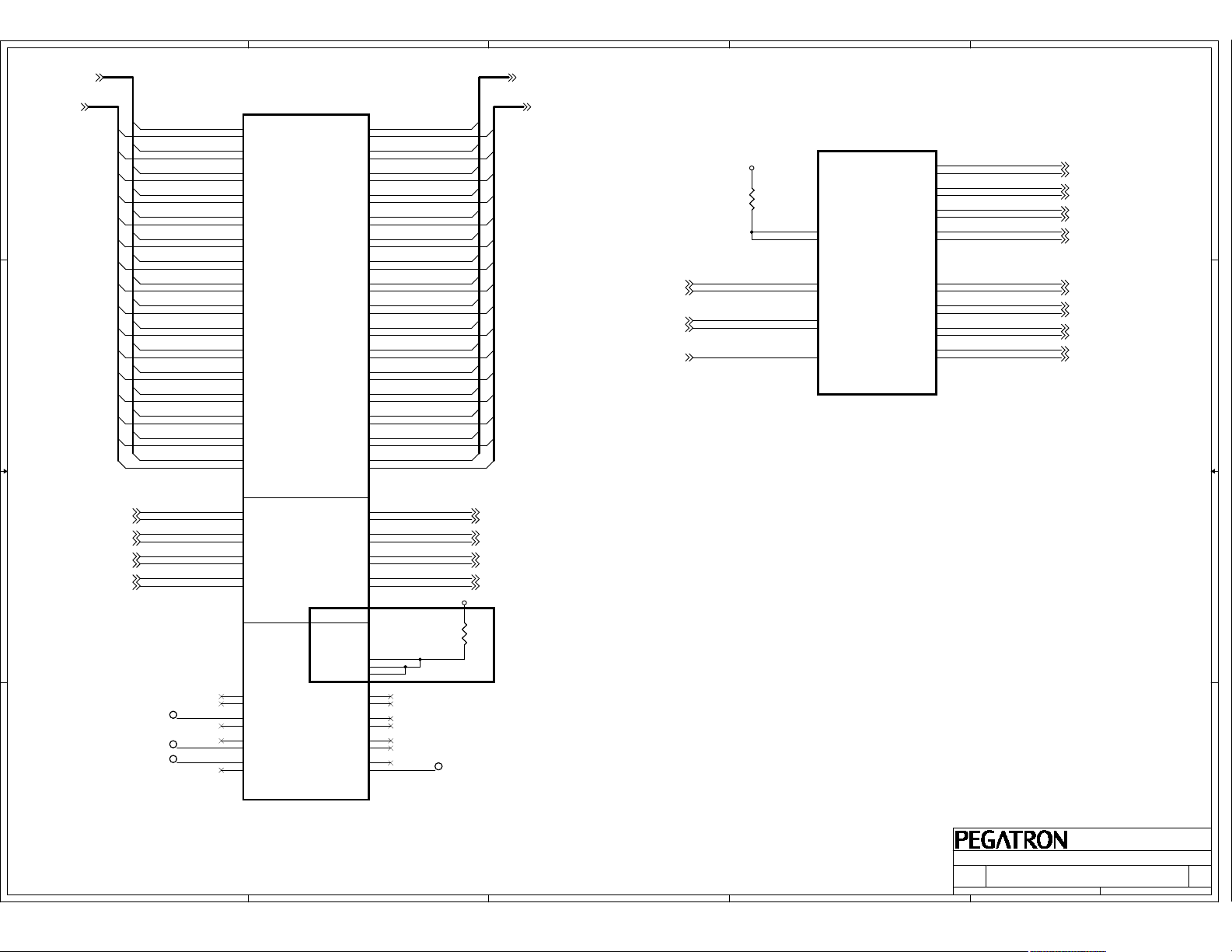

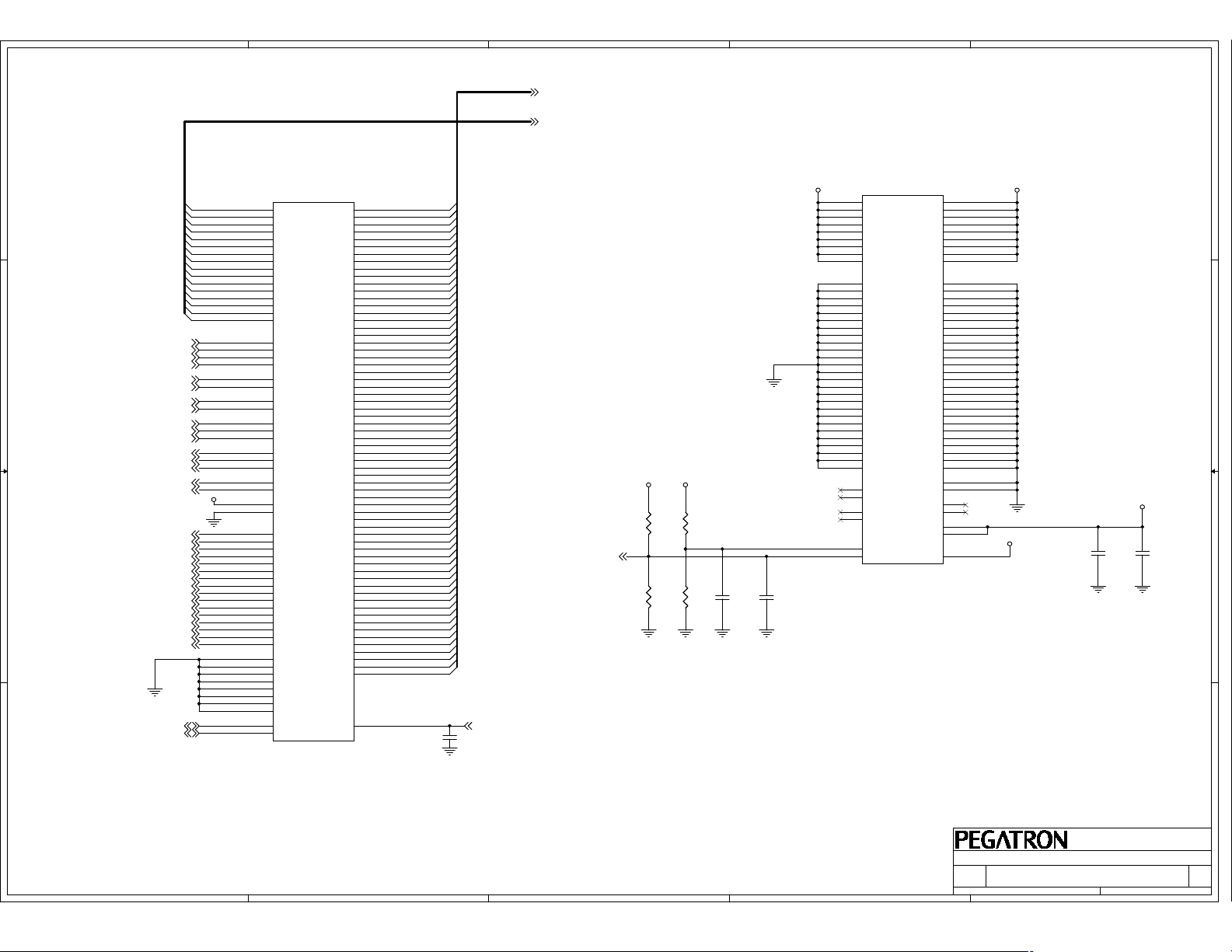

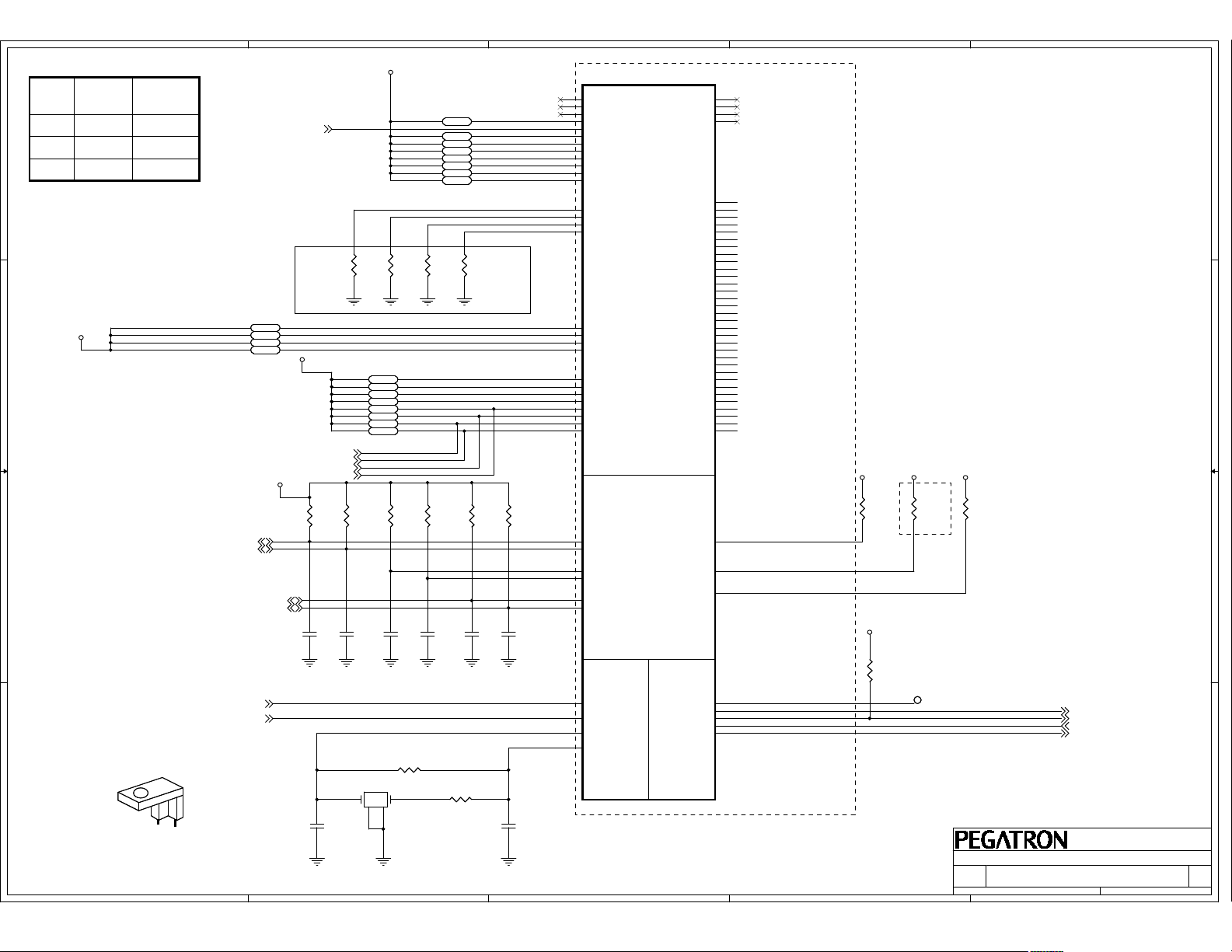

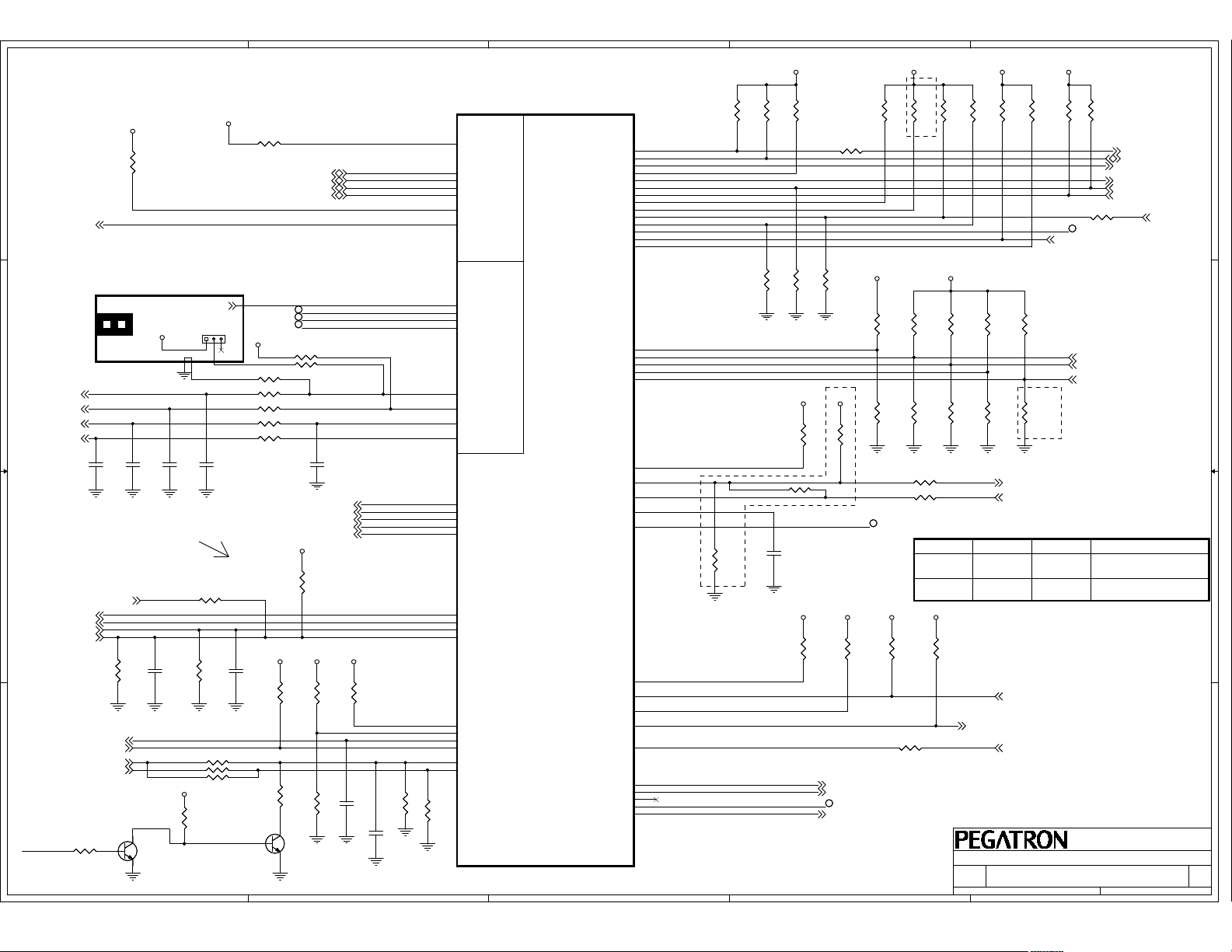

BLOCK DIAGRAM

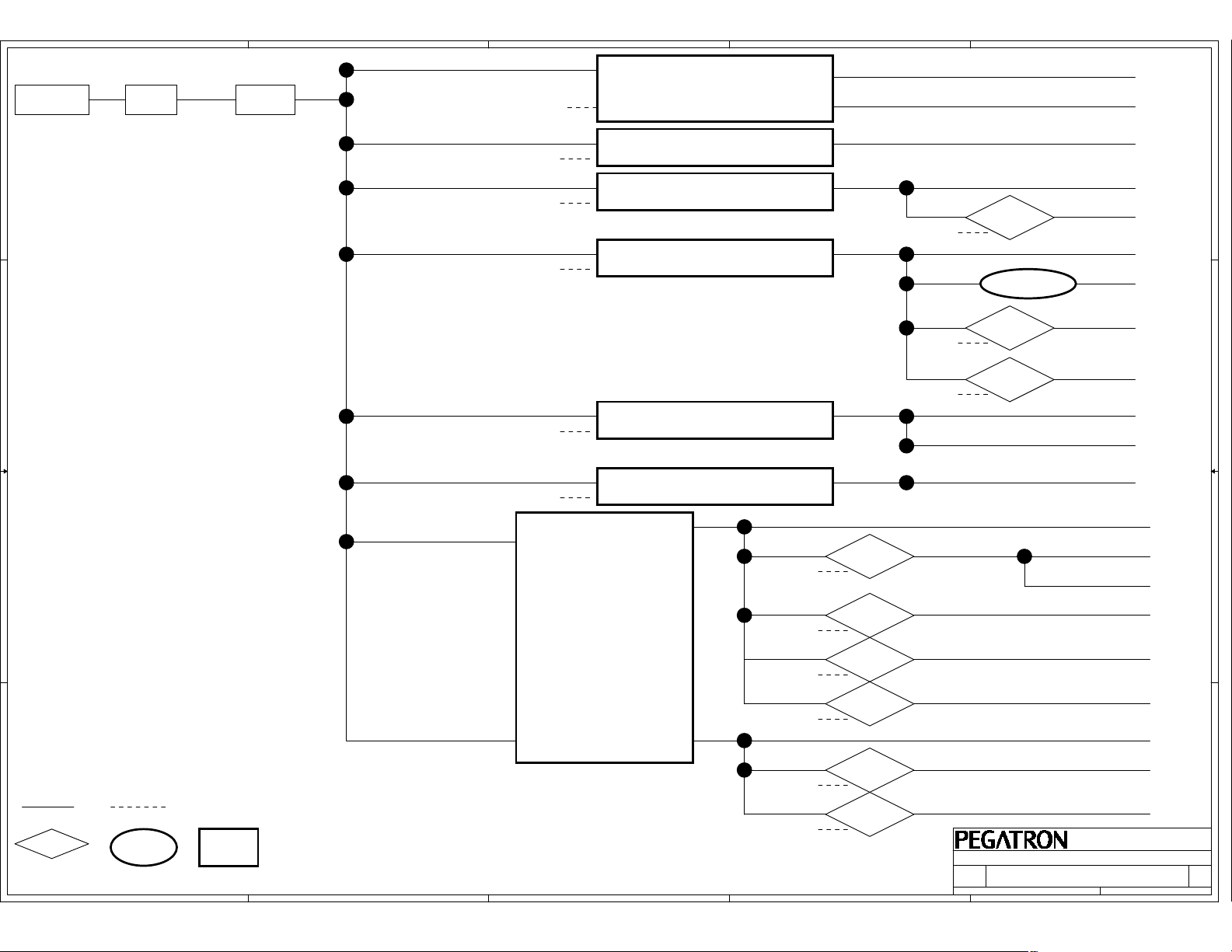

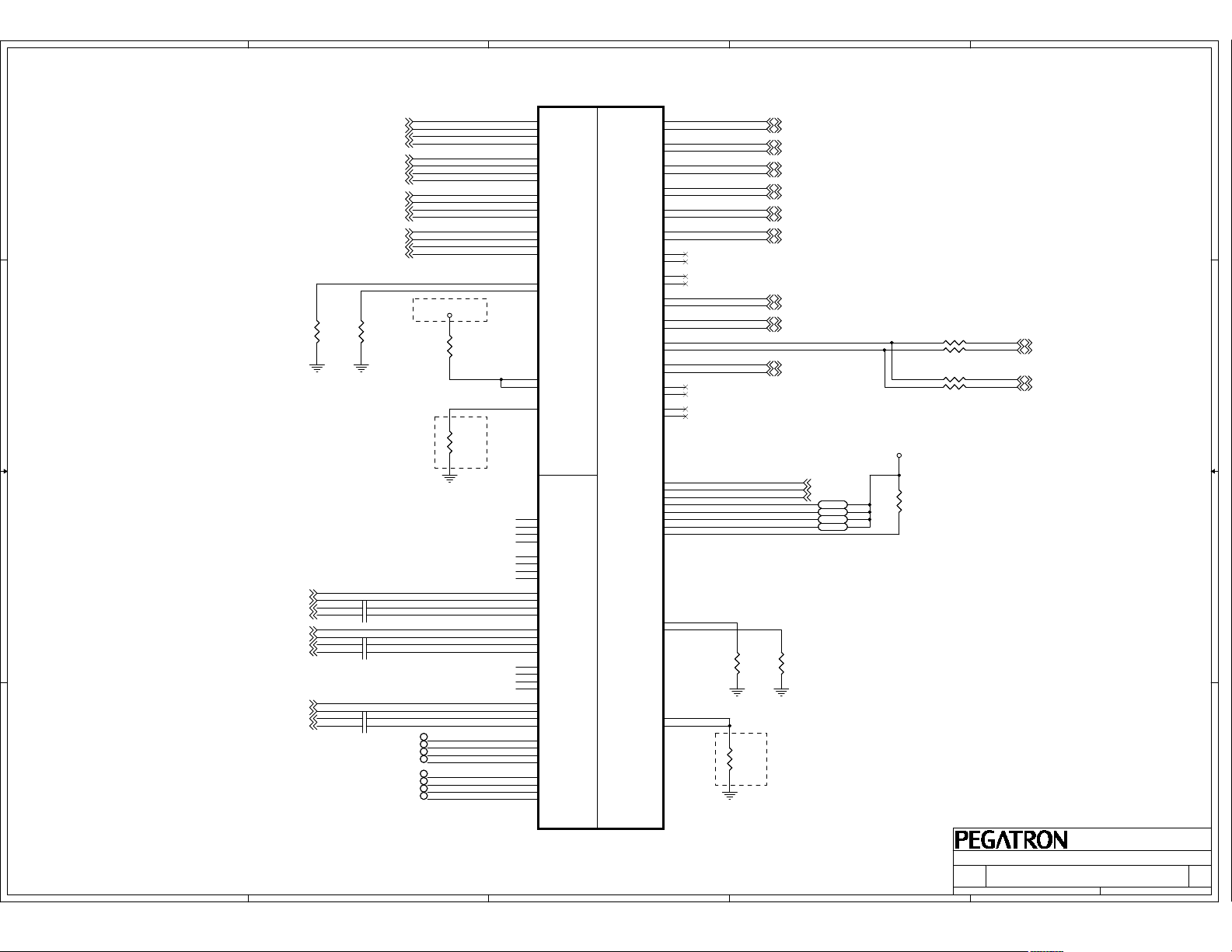

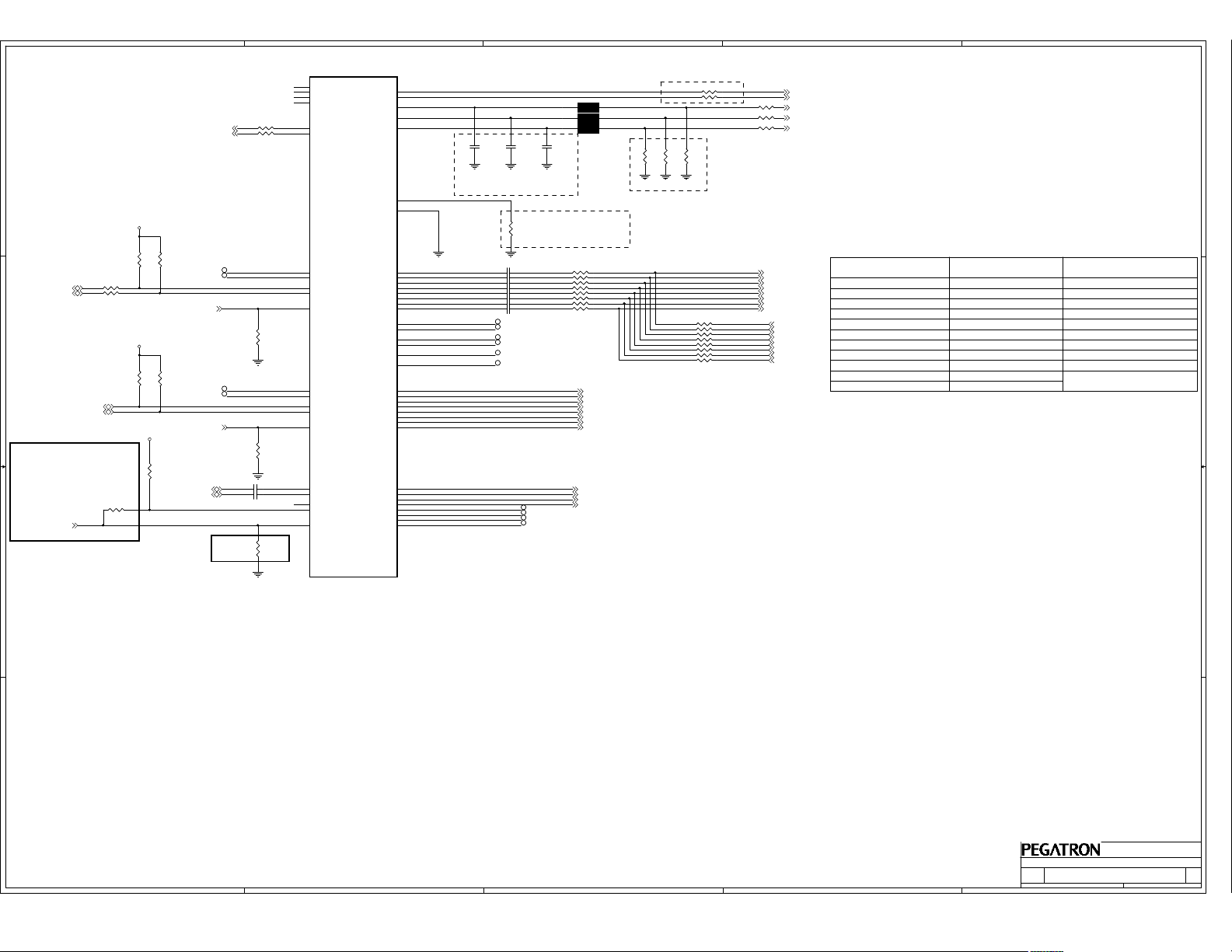

POWER FLOW

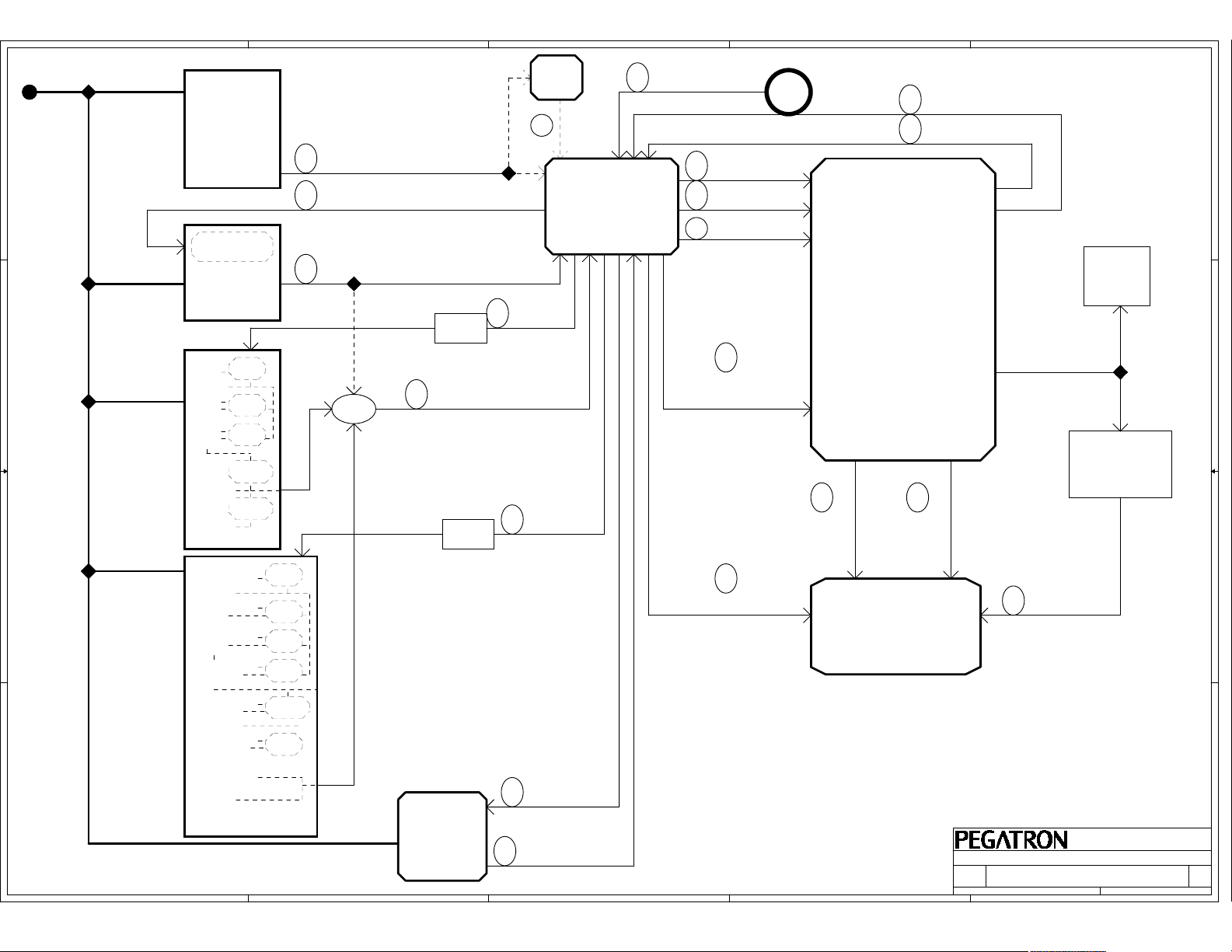

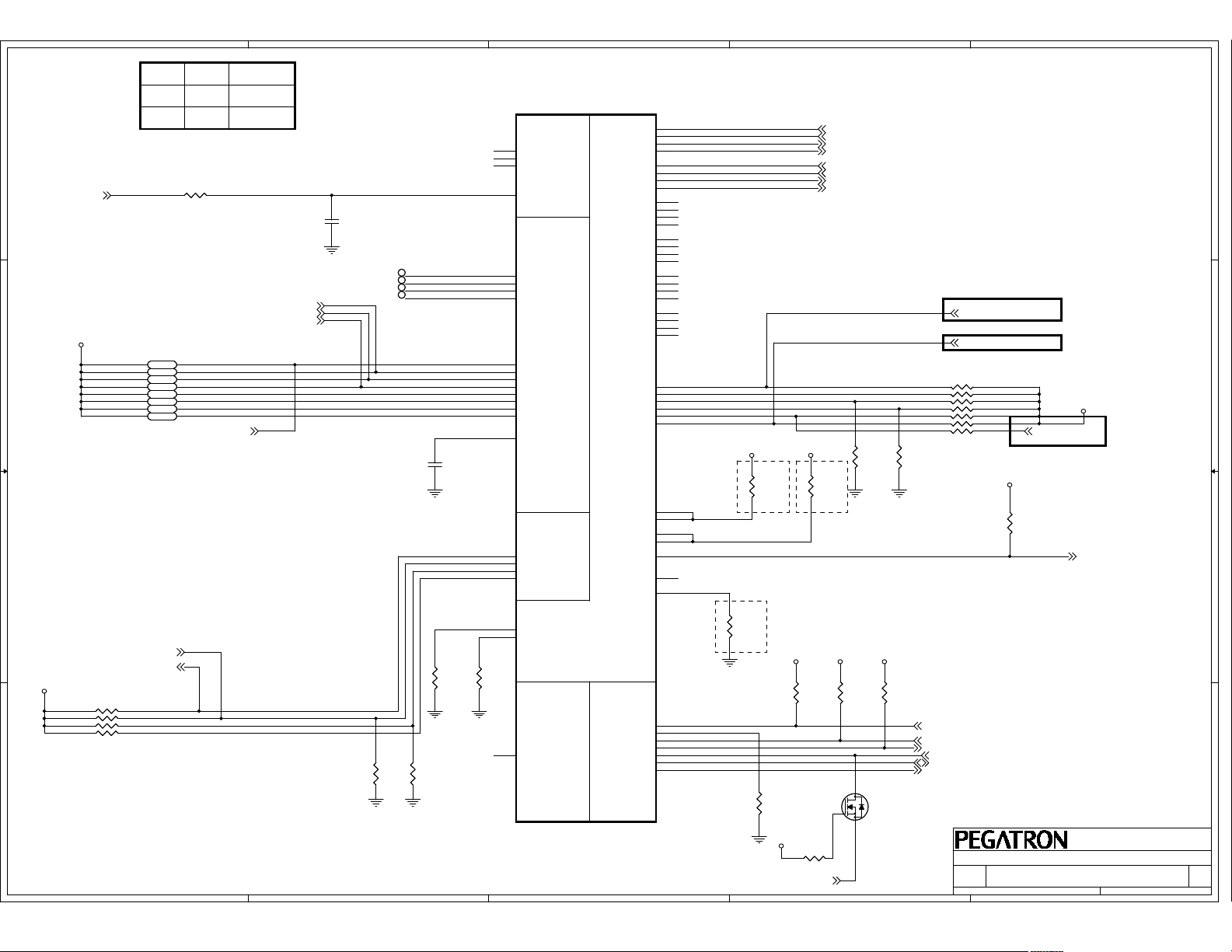

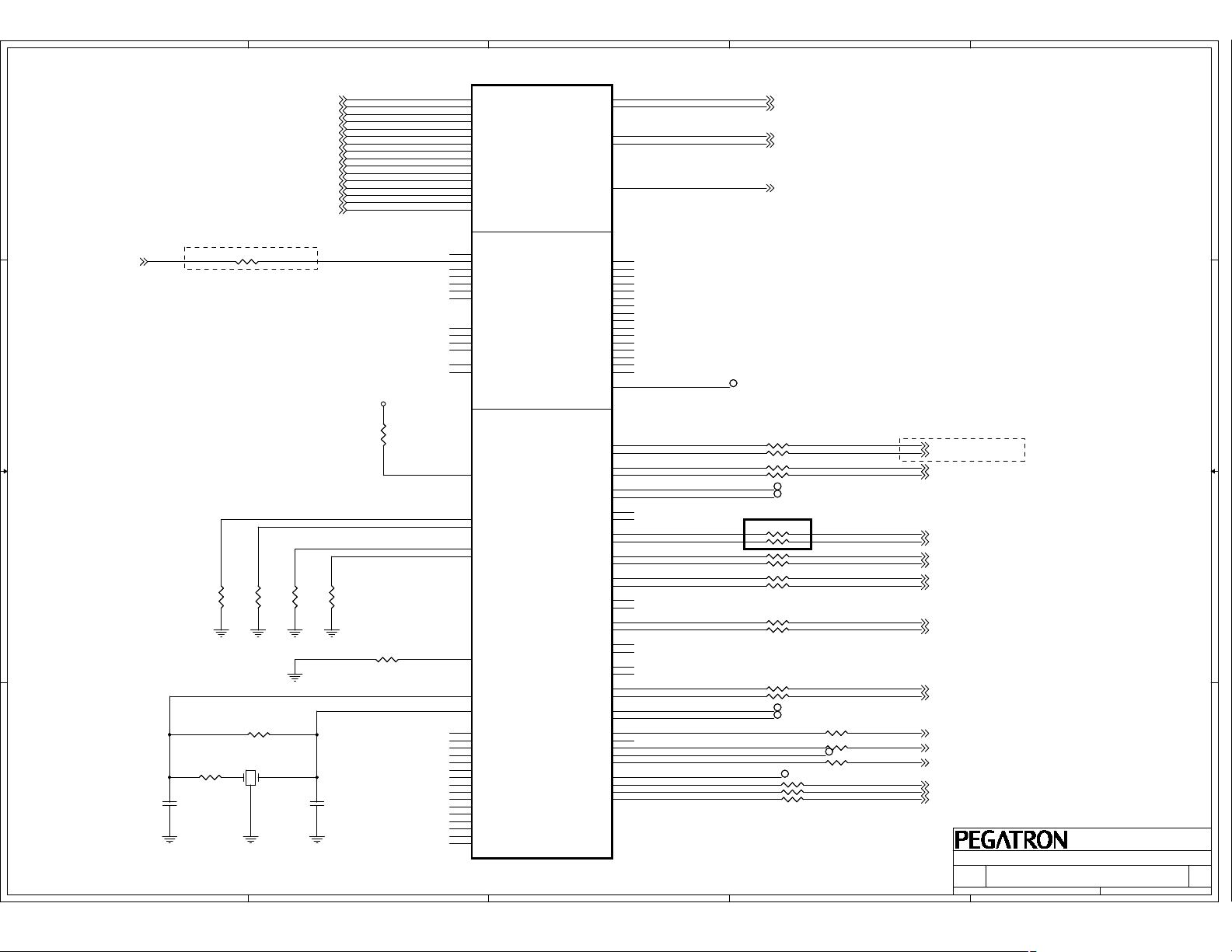

POWER SEQUENCE

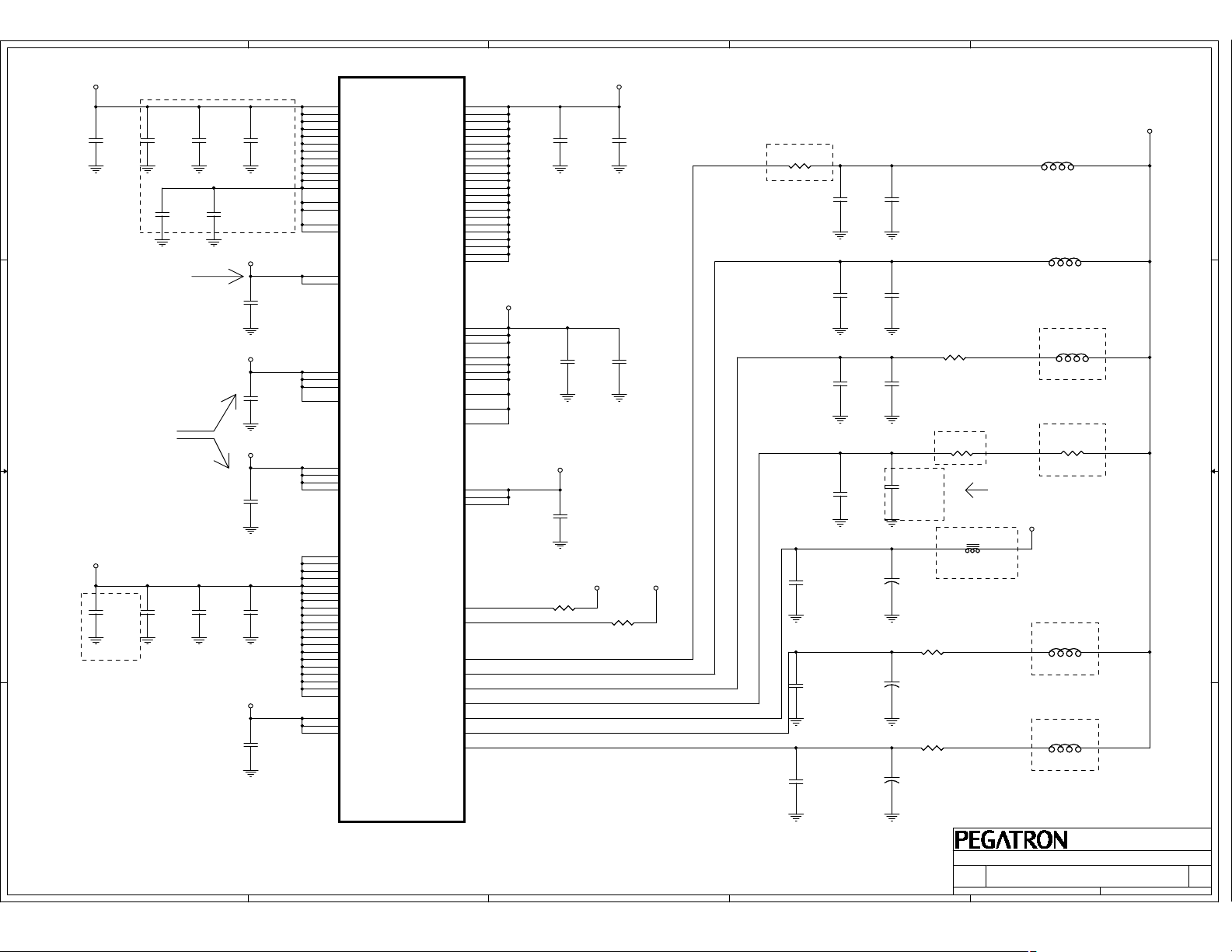

CPU_LGA1155_DDR3_A 1-6

DDR3 CHANNEL B_G/F

DDR3 TERMINATION A&B

Converter Controllor

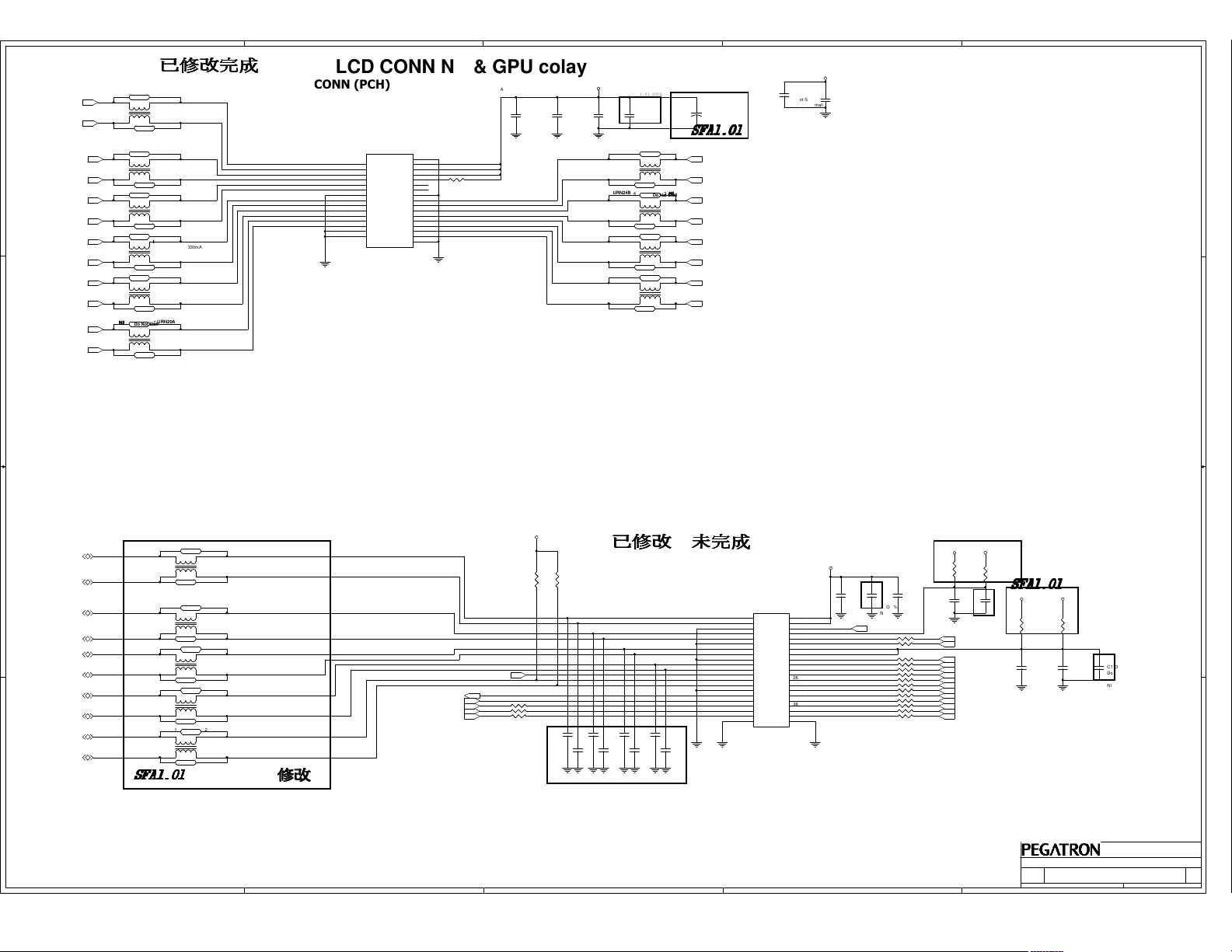

LVDS&AV CONN

INTEL_PCH 1-9

LAN

CODEC&CONN

AMP&SWITCH

USB&HUB&BT

HPD_DET

MINI CARD(WL&TVT&DMC)

Misc. conn&Touch&Wcam&RTC

FAN

PWR LED & Button*

IR LEDs

EC 8519

SM BUS & SPI ROM

SCREW HOLE

UVP, OVP & +19VSB

LOAD_SWITCH

+3P3VSB&+5VSB

+1P5V_DUAL & +1P2V

Current Monitor

+12V & +1P8V

+1P05V_CPUIO&+0P925V_SA

POWER_PROTECT

+1P05V_CPUIO CAP

+VTT_DDR

+V_AXG DRIVER

+VCORE CONTROLLER

+VCORE CAP

+1P05V&+1P05V_PCH

CPU&PCH XDP DEBUG CONNECTOR

VGA CONN

GPU DDR3

VGA-N12P_STRAPPING+EEPROM

MXM.VGA-N12P_Xtal/Thermal

GPU HDMI(DMC&AV)

GPU CTRL

GPU.VGA_N12P_PCI-E I/F

GPU PCI-E_LVDS_VGA

MXM.GPU Discharge

GPU_POWER&GND

EDP CH751179

4

LVDSpanel

Nvidia N12P/N12M

HDMI

LVDS

LVDS

AV Board

Option

EDID

rom

HDMI

Real USB

4 rear PORTS

Side USB

2 side PORTS

webcam + Dmic

PS8615

Touch

EDID

rom

Card reader

Realtek/RTS5139

WLAN SLOT + BT

Realtek 8111E

GBE

IR learning/receiver

/blaster

XDP

Debug

port

3

100MHz

PCI-E BUS

USB 2.0

480Mb/s

USB 2.0

480Mb/s

USB 2.0

480Mb/s

USB 2.0

480Mb/s

USB 2.0

480Mb/s

USB 2.0

480Mb/s

PCIE BUS

100MHz

eDP

PCIE BUS

100MHz

Intel Processor

Sandy Bridge

LGA-1155 Pin Socket

FDI LINK

,17(/

Cougar Point

PCH

H61

942 Pin

27mm X 27mm

33MHz

LPC BUS

45W/65W

DMI

LPC BUS

33MHz

EC

IT8519E

Channel A

Channel B

3Gbps

SATA BUS

SPI

HDA

PCIE BUS

100MHz

2

Dual-Channel Memory x 2 Slots

DDR3 1066/1333

DDR3 1066/1333

SATA0

SATA1

SPI FLASH

AUDIO CODEC

ALC269Q-VA6

Mic

MINI SOLT(TVT)

Line-out

32MB

Option

AV Board

Audio

Switch

1

AMP

TPA3110D2

SPK

A A

PEGATRON DT-MB RESTRICTED SECRET

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

IPPSB-FA

IPPSB-FA

IPPSB-FA

A2

A2

A2

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

%/29.',$*5$0

%/29.',$*5$0

%/29.',$*5$0

Jerry Chung

Jerry Chung

Jerry Chung

179Tuesday, April 26, 2011

179Tuesday, April 26, 2011

179Tuesday, April 26, 2011

of

of

of

Rev

Rev

Rev

1.01

1.01

1.01

5

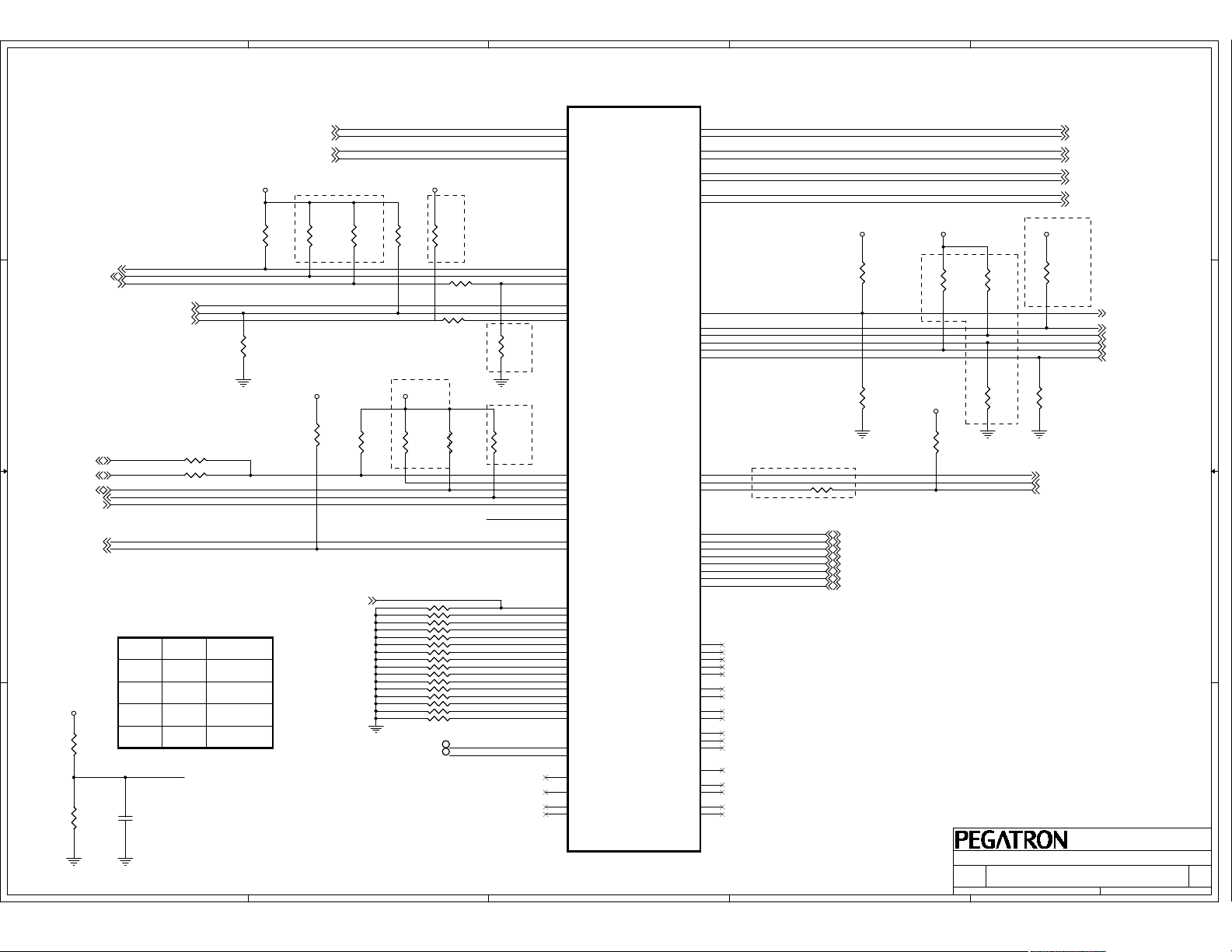

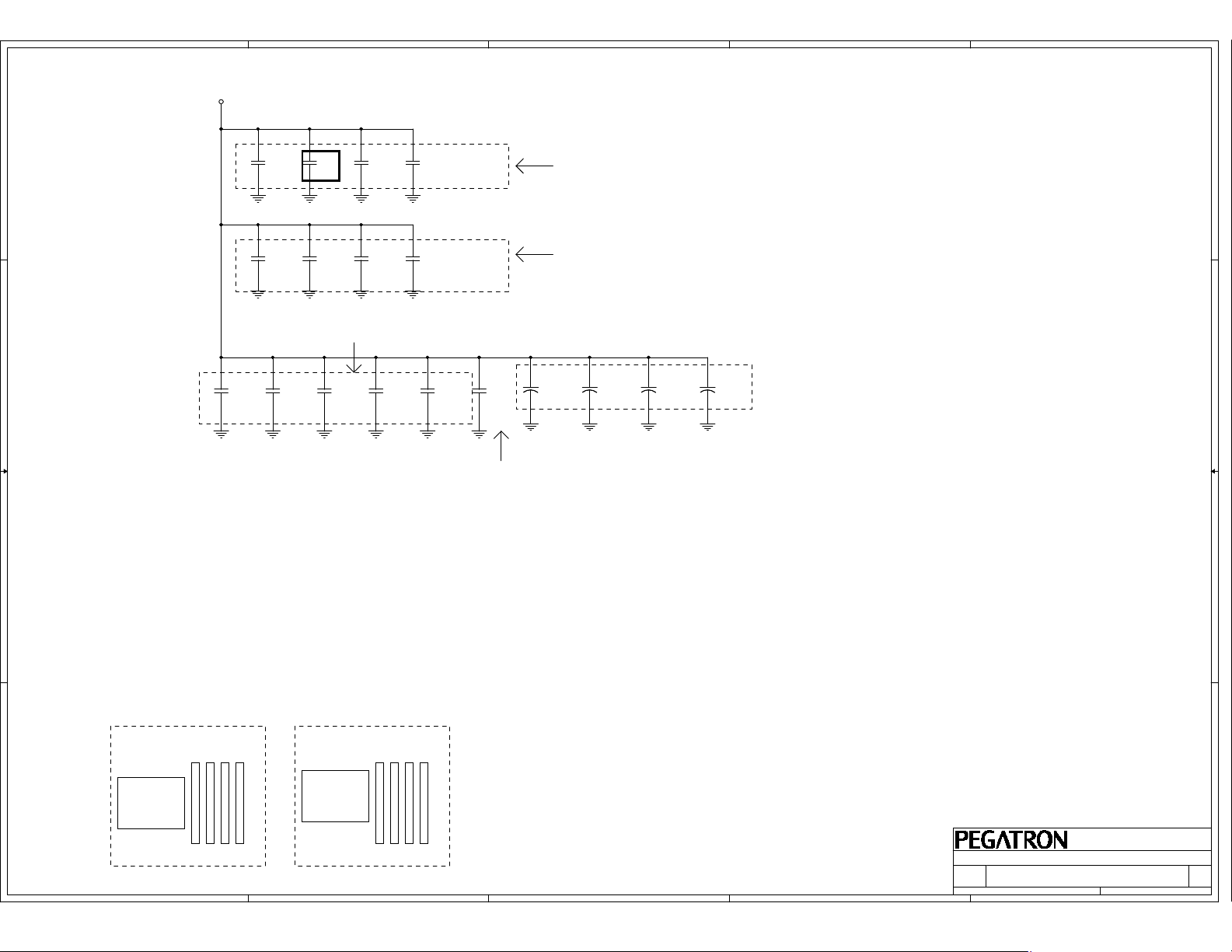

Adapter

+19VA

+19VA_VIN

D D

OVP/UVP

+19VSB_R

INA199A3

Current Monitor

+19VSB

4

+1P05V_CPUIO

SUSB#_PWR

+1P05V_PCH_PWRGD

+5V_DUAL

3

NCP6121S52MNR2G

IRFH7914PBF*1+NTMFS4839NHT1G*2 (3-phase)

IRFH7914PBF*2+NTMFS4839NHT1G*2 (1-phase)

RT8204LGQW

IRF8707PBF*1+IRF8707PBF*1

RT8204LGQW

IRF8707PBF*1+IRFH7914*2

RT8204LGQW

IRF8707PBF*1+IRFH7914*2

2

18.3A

+1P05V_CPUIO_PWRGD

22.66A

IPDH6N03LAG

RT9045GSP

1

+VCORE

S0/S1

75A

+V_AXG

S0/S1

35A

+12V

S0/S1

3.3A

+1P05V_CPUIO

9.5A

+0P925V_SA

8.8A

+1P5V_DUAL

13.75A

+VTTDDR

1.5A

S0/S1

S0/S1

S0/S1/S3

S0/S1/S3

SUSB#_PWR

IRF8707PBF

C C

IRF8707PBF

+1P05V

10.03A

NVVDD_PWRGD

RT8204LGQW

IRF8707PBF*1+IRF8707PBF*2

+1P5V

1.5A

+1P5V_GPU

5.91A

+1P05_PCH

6.2A

+1P05V

S0/S1

S0/S1

S0/S1

S0/S1

3.83A

+5V

6.5A

32:(5)/2:

32:(5)/2:

32:(5)/2:

XXXX-XX

XXXX-XX

XXXX-XX

279Tuesday, April 26, 2011

279Tuesday, April 26, 2011

279Tuesday, April 26, 2011

S0/S1

S0 ~ S5

S0/S1

S0/S1

S0/S1

S0/S1

S0/S1/S3

S0 ~ S5

S0/S1/S3

S0/S1

of

of

of

Rev

Rev

Rev

1.01

1.01

1.01

31.56A

+3P3V_GPU

TPS51125ARGER

IRFH7914PBF*1+NTMFS4839NHT1G*1

RT8208AGQW

IRFH7914PBF*1+NTMFS4839NHT1G*2

IPDH6N03LAG

B B

+1P5V_GPU

NVVDD

31.56A

+3P3VSB16.63A

5.67A

+1P8V_FSR

2.5A

+1P8V

0.3A

SUSB#_PWR

IRF8707PBF

IRF8707PBF

SUSB#_PWR

IRF8707PBF

SUSC#_PWR

IRFH7914PBF*1+NTMFS4839NHT1G*1

IRF8707PBF*2

A A

Power Rail

SPDT Linear

Control signal

5

Switching

4

3

SUSC#_PWR

SUSB#_PWR

IRF8707PBF

2

0413

0413

0413

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,336%)$

,336%)$

,336%)$

+3P3V

4.43A

+3P3V_GPU

1.38A

+3P3V_DUAL

2.35A

+5VSB18.07A

1.57A

+5V_DUAL

10A

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

5

4

3

2

1

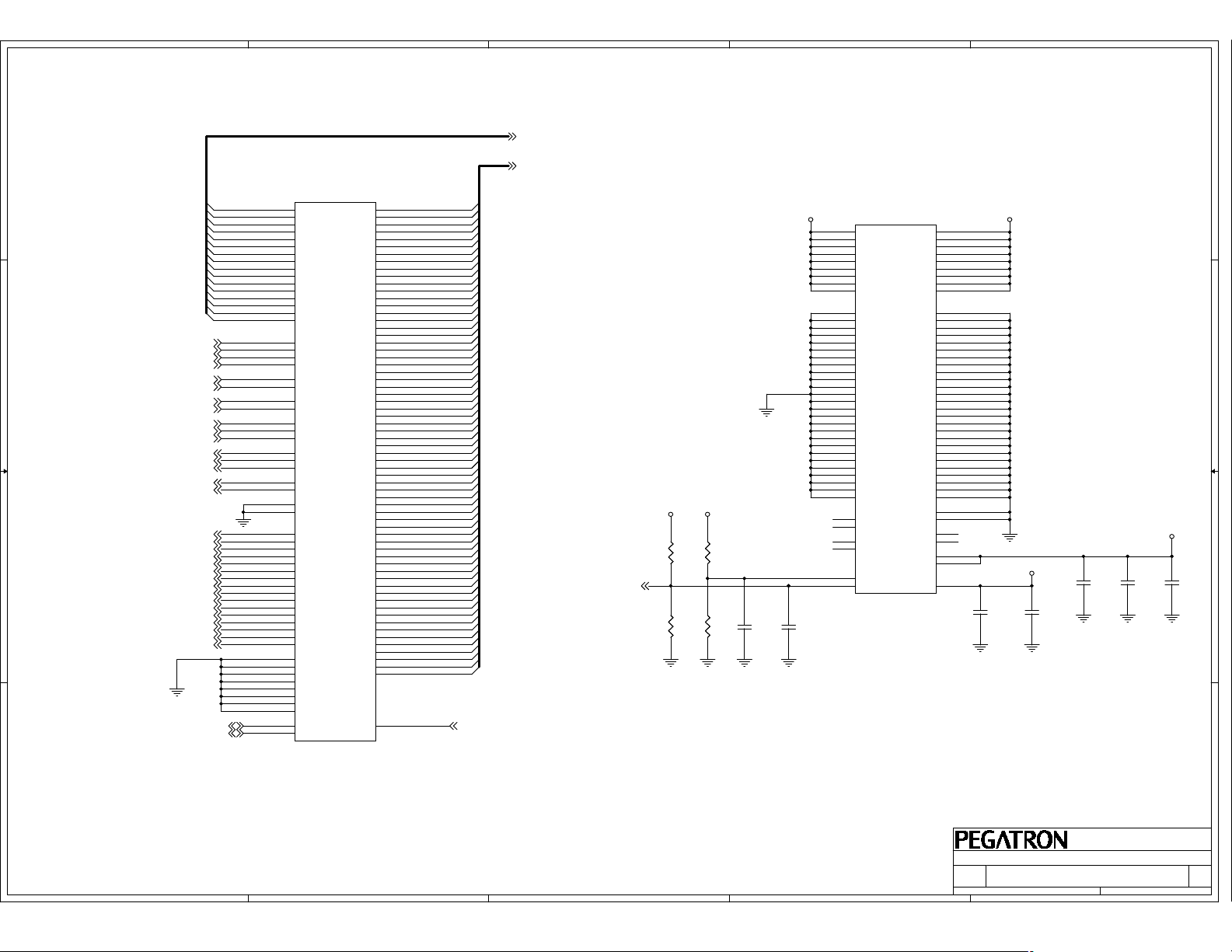

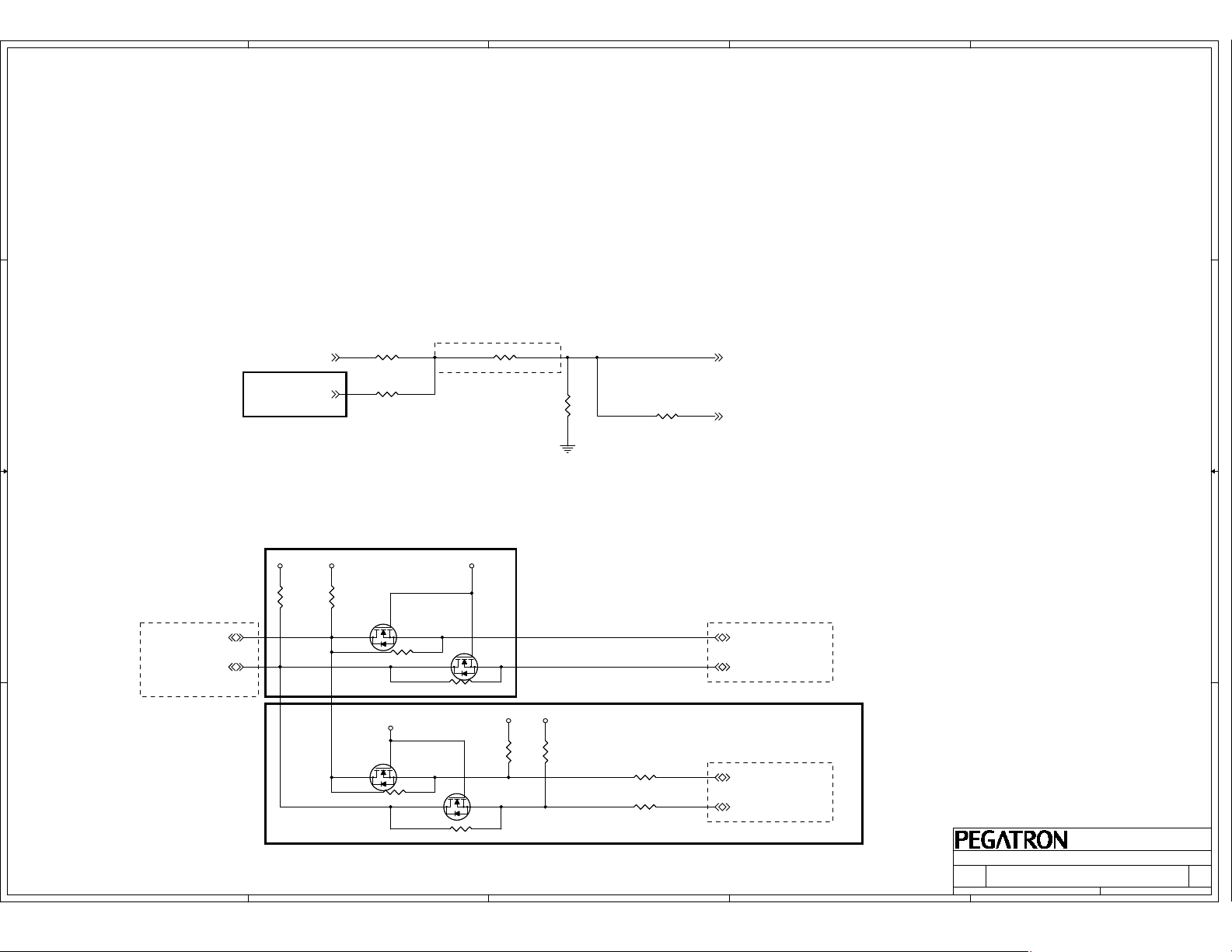

+19VSB

TPS51125

+5VA

+3VA

D D

+3VA_EC

ENTRIP1

TPS51125

ENTRIP2

+3P3VSB

+3VA_EC

1

VSUS_ON

3

SUS_PWRGD

4

+5VSB

SUSC#_PWR

C C

+12VSUS

UMC4N

+5V_DUAL

+5VO

5903

NMOS

+3P3V_DUAL

+3VO

5903

NMOS

+1P5V_DUAL

8202

LIN REG.

+VTT_DDR

+1P1VSB_USB

RT9045

AND

+1P5V_DUAL_PWRGD

SUSB#_PWR

1Kohm

11

ALL_SYSTEM_PWRGD

1Kohm

Reset

circuit

SUSC_EC#

9

SUSB_EC#

10

1-1

WRST#

PWR_SW#

2

(&

,7(

ALL_SYSTEM_PWRGD

PM_PWRBTN#

6

PM_RSMRST#

5

DPWROK

1-2

14

PWROK

PCH_PWROK

Power

Button

PWRBTN#

RSMRST#

DPWROK

&RXJDU

3RLQW

APWROK

PWROK

SYS_PWROK

DRAMPWROK

15

7

8

,QWHO

3&+

16

SLP_S4#

SLP_S3#

SLP_S3#

SLP_S4#

PLTRST#

PROCPWRGD

CPUPWRGD

LAN

XDP

EC etc.

PLTRST#

3.3V TO 1.1V

SHIFTER

DRAM_PWROK

+12V

+12VSUS

+5VO

+3VO

+1.8V

+1.8V

+1.8V

4502

5903

NMOS

5903

NMOS

2304

NMOS

9024

LIN REG.

9026

LDO

+1P05V_PCH_PWRGD

+1P05V_CPUIO_PWRGD

VR_ON

9FRUH

PGOOD

4

12

VRM_PWRGD

13

CPU_VRON

17

SYS_PWROK

SM_DRAMPWROK

UNCOREPWRGOOD

RESET#

PLTRST_CPU#

18

6DQG\

%ULGJH

0413

0413

0413

Title :

32:(56(48(1&(

Title :

32:(56(48(1&(

Title :

32:(56(48(1&(

Mike Yen

Mike Yen

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

3

2

Date: Sheet

,336%)$

,336%)$

,336%)$

Engineer:

Mike Yen

379Tuesday, April 26, 2011

379Tuesday, April 26, 2011

1

379Tuesday, April 26, 2011

Rev

Rev

Rev

1.01

1.01

1.01

of

of

of

B B

+5V

+3P3V

+1P8V_SFR

+1P5V

+10P5V_PCH

+10P5V_CPUIO

+0P925V_SA

A A

+V_AXG

5

5

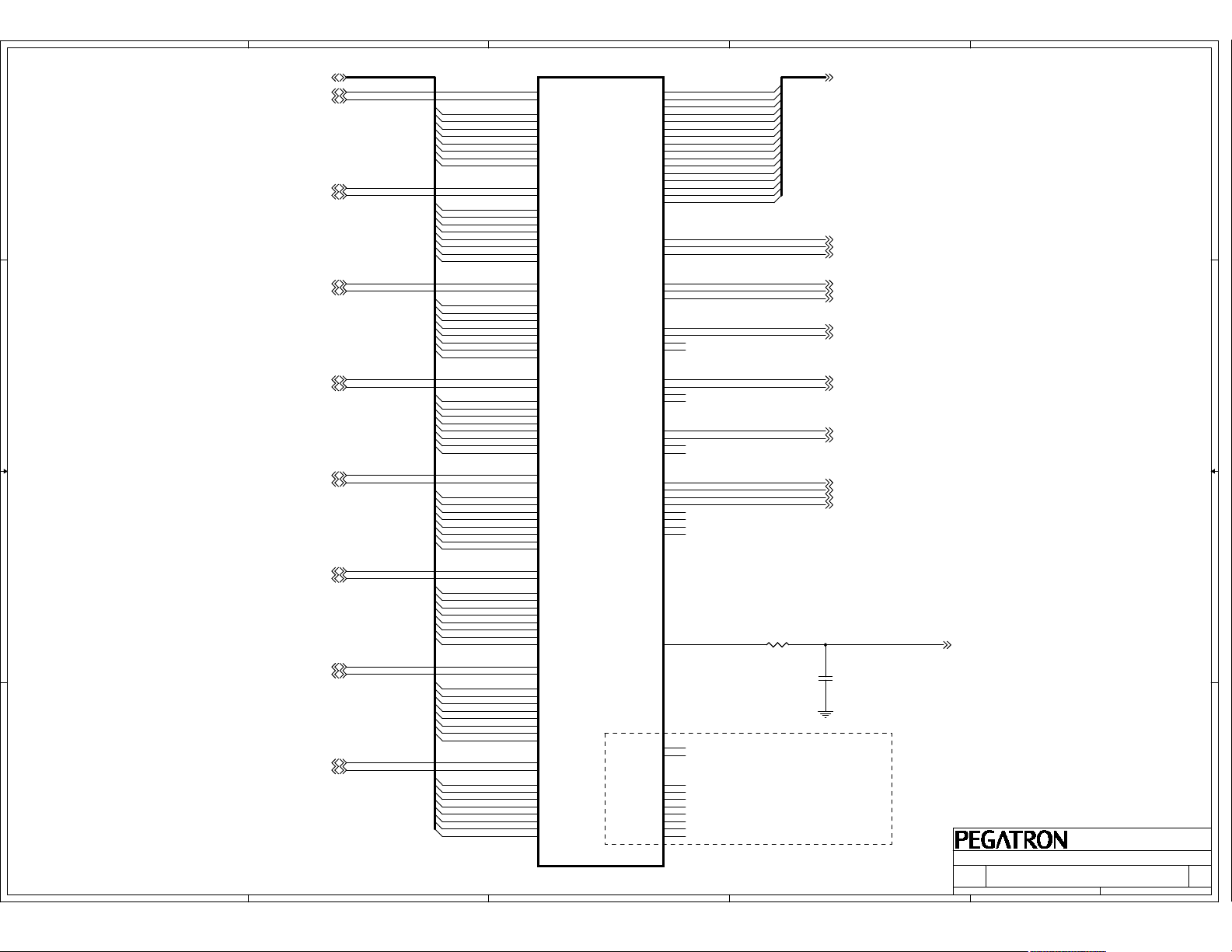

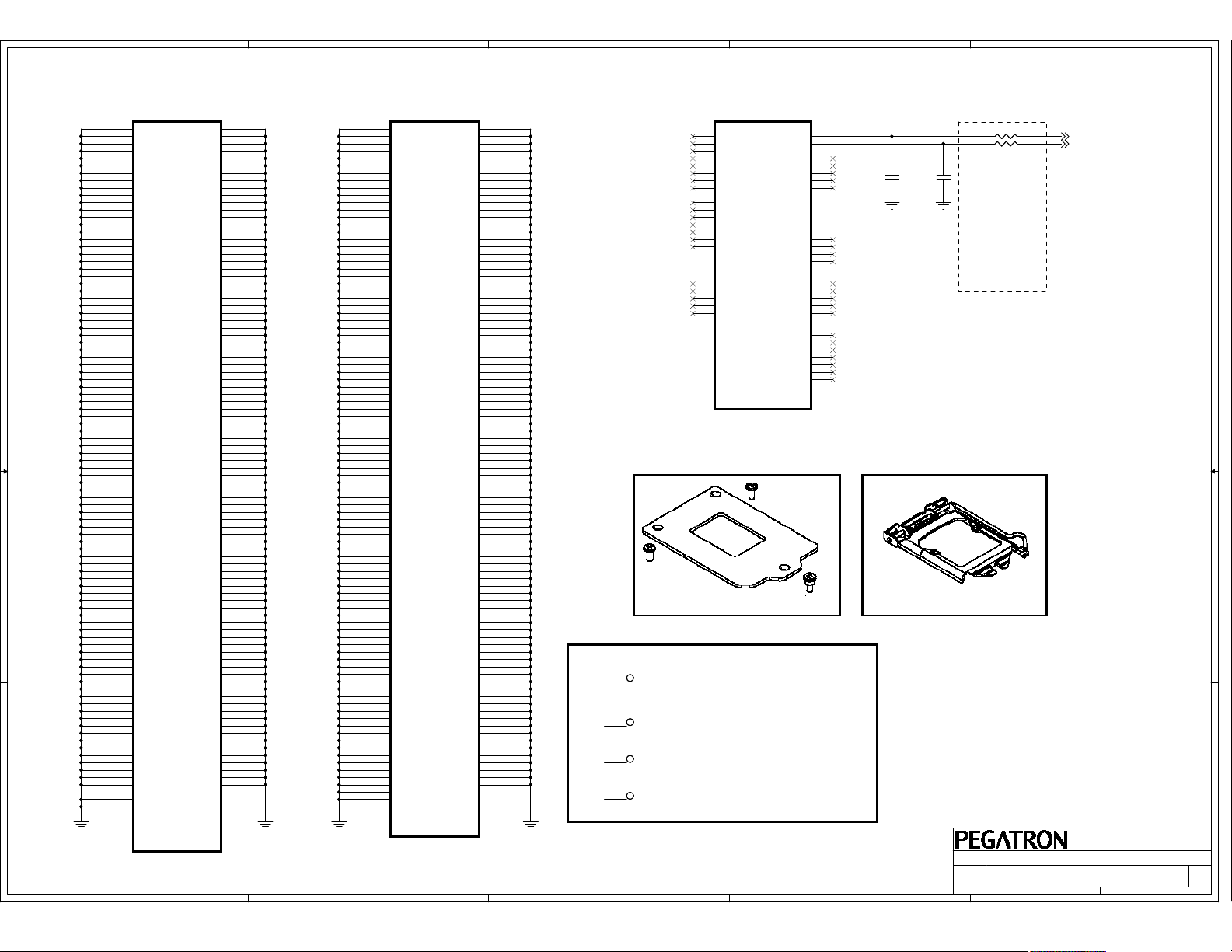

M_CHA_DQ[0..63][10]

M_CHA_DQS0[10]

M_CHA_DQS0#[10]

D D

M_CHA_DQS1[10]

M_CHA_DQS1#[10]

M_CHA_DQS2[10]

M_CHA_DQS2#[10]

C C

B B

A A

5

M_CHA_DQS3[10]

M_CHA_DQS3#[10]

M_CHA_DQS4[10]

M_CHA_DQS4#[10]

M_CHA_DQS5[10]

M_CHA_DQS5#[10]

M_CHA_DQS6[10]

M_CHA_DQS6#[10]

M_CHA_DQS7[10]

M_CHA_DQS7#[10]

4

XU1A

AW4

AW3

AW5

AW8

AW7

AW9

AV37

AV36

AU35

AW37

AU39

AU36

AW35

AY36

AU38

AU37

AP38

AP39

AR40

AR37

AN38

AN37

AR39

AR38

AN39

AN40

AK38

AK39

AL40

AL37

AJ38

AJ37

AL39

AL38

AJ39

AJ40

AF38

AF39

AG40

AG37

AE38

AE37

AG39

AG38

AE39

AE40

AK3

AK2

AJ3

AJ4

AL3

AL4

AJ2

AJ1

AL2

AL1

AP3

AP2

AN1

AN4

AR3

AR4

AN2

AN3

AR2

AR1

AV4

AV2

AV5

AU2

AU3

AU5

AY5

AV8

AY7

AU7

AV9

AU9

AV7

AY9

XU1A

SA_DQS_0

SA_DQS#_0

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQS_1

SA_DQS#_1

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQS_2

SA_DQS#_2

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQS_3

SA_DQS#_3

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQS_4

SA_DQS#_4

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQS_5

SA_DQS#_5

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQS_6

SA_DQS#_6

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQS_7

SA_DQS#_7

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SOCKET_1155P

SOCKET_1155P

I

I

M_CHA_DQS0

M_CHA_DQS0#

M_CHA_DQ0

M_CHA_DQ1

M_CHA_DQ2

M_CHA_DQ3

M_CHA_DQ4

M_CHA_DQ5

M_CHA_DQ6

M_CHA_DQ7

M_CHA_DQS1

M_CHA_DQS1#

M_CHA_DQ8

M_CHA_DQ9

M_CHA_DQ10

M_CHA_DQ11

M_CHA_DQ12

M_CHA_DQ13

M_CHA_DQ14

M_CHA_DQ15

M_CHA_DQS2

M_CHA_DQS2#

M_CHA_DQ16

M_CHA_DQ17

M_CHA_DQ18

M_CHA_DQ19

M_CHA_DQ20

M_CHA_DQ21

M_CHA_DQ22

M_CHA_DQ23

M_CHA_DQS3

M_CHA_DQS3#

M_CHA_DQ24

M_CHA_DQ25

M_CHA_DQ26

M_CHA_DQ27

M_CHA_DQ28

M_CHA_DQ29

M_CHA_DQ30

M_CHA_DQ31

M_CHA_DQS4

M_CHA_DQS4#

M_CHA_DQ32

M_CHA_DQ33

M_CHA_DQ34

M_CHA_DQ35

M_CHA_DQ36

M_CHA_DQ37

M_CHA_DQ38

M_CHA_DQ39

M_CHA_DQS5

M_CHA_DQS5#

M_CHA_DQ40

M_CHA_DQ41

M_CHA_DQ42

M_CHA_DQ43

M_CHA_DQ44

M_CHA_DQ45

M_CHA_DQ46

M_CHA_DQ47

M_CHA_DQS6

M_CHA_DQS6#

M_CHA_DQ48

M_CHA_DQ49

M_CHA_DQ50

M_CHA_DQ51

M_CHA_DQ52

M_CHA_DQ53

M_CHA_DQ54

M_CHA_DQ55

M_CHA_DQS7

M_CHA_DQS7#

M_CHA_DQ56

M_CHA_DQ57

M_CHA_DQ58

M_CHA_DQ59

M_CHA_DQ60

M_CHA_DQ61

M_CHA_DQ62

M_CHA_DQ63

4

3

SM_DRAMRST#

DDR3_A

DDR3_A

3

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_WE#

SA_CAS#

SA_RAS#

SA_BS_0

SA_BS_1

SA_BS_2

SA_CS#_0

SA_CS#_1

SA_CS#_2

SA_CS#_3

SA_CKE_0

SA_CKE_1

SA_CKE_2

SA_CKE_3

SA_ODT_0

SA_ODT_1

SA_ODT_2

SA_ODT_3

SA_CK_0

SA_CK#_0

SA_CK_1

SA_CK#_1

SA_CK_2

SA_CK#_2

SA_CK_3

SA_CK#_3

SA_DQS_8

SA_DQS#_8

SA_ECC_CB_0

SA_ECC_CB_1

SA_ECC_CB_2

SA_ECC_CB_3

SA_ECC_CB_4

SA_ECC_CB_5

SA_ECC_CB_6

SA_ECC_CB_7

M_CHA_MAA0

AV27

M_CHA_MAA1

AY24

M_CHA_MAA2

AW24

M_CHA_MAA3

AW23

M_CHA_MAA4

AV23

M_CHA_MAA5

AT24

M_CHA_MAA6

AT23

M_CHA_MAA7

AU22

M_CHA_MAA8

AV22

M_CHA_MAA9

AT22

M_CHA_MAA10

AV28

M_CHA_MAA11

AU21

M_CHA_MAA12

AT21

M_CHA_MAA13

AW32

M_CHA_MAA14

AU20

M_CHA_MAA15

AT20

AW29

AV30

AU28

AY29

AW28

AV20

AU29

AV32

AW30

AU33

AV19

AT19

AU18

AV18

AV31

AU32

AU30

AW33

AY25

AW25

AU24

AU25

AW27

AY27

AV26

AW26

93

93

HR1

SM_DRAMRST#

AW18

AV13

AV12

AU12

127(

AU14

AW13

Sugar Bay platform does not support ECC

AY13

AU13

AU11

AY12

AW12

HR1

1 2

0

0

2

M_CHA_MAA[0..15] [10]

M_CHA_WE# [10]

M_CHA_CAS# [10]

M_CHA_RAS# [10]

M_CHA_BA0 [10]

M_CHA_BA1 [10]

M_CHA_BA2 [10]

M_CHA_CS#0 [10]

M_CHA_CS#1 [10]

M_CHA_CKE0 [10]

M_CHA_CKE1 [10]

M_CHA_ODT0 [10]

M_CHA_ODT1 [10]

M_CHA_CLK0 [10]

M_CHA_CLK0# [10]

M_CHA_CLK1 [10]

M_CHA_CLK1# [10]

12

1,

1,

HC1

HC1

Do Not Stuff

Do Not Stuff

X7R 10%

X7R 10%

GND

2

1

DDR3_DRAMRST# [10,11]

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Engineer:

,336%)$

,336%)$

,336%)$

1

''5B$

''5B$

''5B$

Mike Yen

Mike Yen

Mike Yen

of

of

of

479Wednesday, April 27, 2011

479Wednesday, April 27, 2011

479Wednesday, April 27, 2011

Rev

Rev

Rev

1.01

1.01

1.01

5

M_CHB_DQ[0..63][11]

M_CHB_DQS0[11]

M_CHB_DQS0#[11]

D D

M_CHB_DQS1[11]

M_CHB_DQS1#[11]

M_CHB_DQS2[11]

M_CHB_DQS2#[11]

C C

M_CHB_DQS3[11]

M_CHB_DQS3#[11]

M_CHB_DQS4[11]

M_CHB_DQS4#[11]

B B

A A

5

M_CHB_DQS5[11]

M_CHB_DQS5#[11]

M_CHB_DQS6[11]

M_CHB_DQS6#[11]

M_CHB_DQS7[11]

M_CHB_DQS7#[11]

4

XU1B

XU1B

M_CHB_DQS0

M_CHB_DQS0#

M_CHB_DQ0

M_CHB_DQ1

M_CHB_DQ2

M_CHB_DQ3

M_CHB_DQ4

M_CHB_DQ5

M_CHB_DQ6

M_CHB_DQ7

M_CHB_DQS1

M_CHB_DQS1#

M_CHB_DQ13

M_CHB_DQ9

M_CHB_DQ11

M_CHB_DQ15

M_CHB_DQ12

M_CHB_DQ8

M_CHB_DQ14

M_CHB_DQ10

M_CHB_DQS2

M_CHB_DQS2#

M_CHB_DQ16

M_CHB_DQ17

M_CHB_DQ18

M_CHB_DQ19

M_CHB_DQ20

M_CHB_DQ21

M_CHB_DQ22

M_CHB_DQ23

M_CHB_DQS3

M_CHB_DQS3#

M_CHB_DQ24

M_CHB_DQ25

M_CHB_DQ26

M_CHB_DQ27

M_CHB_DQ28

M_CHB_DQ29

M_CHB_DQ30

M_CHB_DQ31

M_CHB_DQS4

M_CHB_DQS4#

M_CHB_DQ32

M_CHB_DQ33

M_CHB_DQ34

M_CHB_DQ35

M_CHB_DQ36

M_CHB_DQ37

M_CHB_DQ38

M_CHB_DQ39

M_CHB_DQS5

M_CHB_DQS5#

M_CHB_DQ40

M_CHB_DQ41

M_CHB_DQ42

M_CHB_DQ43

M_CHB_DQ44

M_CHB_DQ45

M_CHB_DQ46

M_CHB_DQ47

M_CHB_DQS6

M_CHB_DQS6#

M_CHB_DQ48

M_CHB_DQ52

M_CHB_DQ55

M_CHB_DQ51

M_CHB_DQ54

M_CHB_DQ49

M_CHB_DQ53

M_CHB_DQ50

M_CHB_DQS7

M_CHB_DQS7#

M_CHB_DQ56

M_CHB_DQ57

M_CHB_DQ58

M_CHB_DQ59

M_CHB_DQ60

M_CHB_DQ61

M_CHB_DQ62

M_CHB_DQ63

4

AM10

AL10

AP10

AR10

AN13

AN12

AM12

AM13

AR13

AP13

AL12

AL13

AR12

AP12

AN29

AN28

AR28

AR29

AL28

AL29

AP28

AP29

AM28

AM29

AP33

AR33

AP32

AP31

AP35

AP34

AR32

AR31

AR35

AR34

AL33

AM33

AM32

AM31

AL35

AL32

AM34

AL31

AM35

AL34

AG35

AG34

AH35

AH34

AE34

AE35

AJ35

AJ34

AF33

AF35

AH7

AH6

AG7

AG8

AG5

AG6

AM8

AL8

AL7

AM7

AL6

AM6

AL9

AM9

AR8

AP8

AP7

AR7

AP6

AR6

AP9

AR9

AJ9

AJ8

AJ6

AJ7

SB_DQS_0

SB_DQS#_0

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQS_1

SB_DQS#_1

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQS_2

SB_DQS#_2

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQS_3

SB_DQS#_3

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQS_4

SB_DQS#_4

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQS_5

SB_DQS#_5

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQS_6

SB_DQS#_6

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQS_7

SB_DQS#_7

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

DDR3_B

DDR3_B

SOCKET_1155P

SOCKET_1155P

I

I

3

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SA_CK[2]

SA_CK[1]

SA_ODT[2]

SB_BS_0

SB_BS_1

SB_BS_2

SB_CS#_0

SB_CS#_1

SB_CS#_2

SB_CS#_3

SB_CKE_0

SB_CKE_1

SB_CKE_2

SB_CKE_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_CK_0

SB_CK#_0

SB_CK_1

SB_CK#_1

SB_CK_2

SB_CK#_2

SB_CK_3

SB_CK#_3

SB_DQS_8

SB_DQS#_8

SB_ECC_CB_0

SB_ECC_CB_1

SB_ECC_CB_2

SB_ECC_CB_3

SB_ECC_CB_4

SB_ECC_CB_5

SB_ECC_CB_6

SB_ECC_CB_7

3

M_CHB_MAA0

AK24

M_CHB_MAA1

AM20

M_CHB_MAA2

AM19

M_CHB_MAA3

AK18

M_CHB_MAA4

AP19

M_CHB_MAA5

AP18

M_CHB_MAA6

AM18

M_CHB_MAA7

AL18

M_CHB_MAA8

AN18

M_CHB_MAA9

AY17

M_CHB_MAA10

AN23

M_CHB_MAA11

AU17

M_CHB_MAA12

AT18

M_CHB_MAA13

AR26

M_CHB_MAA14

AY16

M_CHB_MAA15

AV16

AR25

AK25

AP24

AP23

AM24

AW17

AN25

AN26

AL25

AT26

AU16

AY15

AW15

AV15

AL26

AP26

AM26

AK26

AL21

AL22

AL20

AK20

AL23

AM22

AP21

AN21

AN16

AN15

AL16

127(

AM16

AP16

Sugar Bay platform does not support ECC

AR16

AL15

AM15

AR15

AP15

2

M_CHB_MAA[0..15] [11]

M_CHB_WE# [11]

M_CHB_CAS# [11]

M_CHB_RAS# [11]

M_CHB_BA0 [11]

M_CHB_BA1 [11]

M_CHB_BA2 [11]

M_CHB_CS#0 [11]

M_CHB_CS#1 [11]

M_CHB_CKE0 [11]

M_CHB_CKE1 [11]

M_CHB_ODT0 [11]

M_CHB_ODT1 [11]

M_CHB_CLK0 [11]

M_CHB_CLK0# [11]

M_CHB_CLK1 [11]

M_CHB_CLK1# [11]

2

1

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Engineer:

,336%)$

,336%)$

,336%)$

1

''5B%

''5B%

''5B%

Mike Yen

Mike Yen

Mike Yen

of

of

of

579Wednesday, April 27, 2011

579Wednesday, April 27, 2011

579Wednesday, April 27, 2011

Rev

Rev

Rev

1.01

1.01

1.01

5

4

3

2

1

PEG_RXP[0..15][73]

PEG_RXN[0..15][73]

PEG_RXP0 PEG_TXP0

PEG_RXP0

PEG_RXN0

PEG_RXN0

PEG_RXP1

PEG_RXP1

PEG_RXN1

D D

C C

DMI_RXP0[18]

DMI_RXN0[18]

DMI_RXP1[18]

DMI_RXN1[18]

DMI_RXP2[18]

DMI_RXN2[18]

B B

A A

DMI_RXP3[18]

DMI_RXN3[18]

12%20

12%20

12%20

12%20

12%20

12%20

PEG_RXN1

PEG_RXP2

PEG_RXP2

PEG_RXN2

PEG_RXN2

PEG_RXP3

PEG_RXP3

PEG_RXN3

PEG_RXN3

PEG_RXP4

PEG_RXP4

PEG_RXN4

PEG_RXN4

PEG_RXP5

PEG_RXP5

PEG_RXN5

PEG_RXN5

PEG_RXP6

PEG_RXP6

PEG_RXN6

PEG_RXN6

PEG_RXP7

PEG_RXP7

PEG_RXN7

PEG_RXN7

PEG_RXP8

PEG_RXP8

PEG_RXN8

PEG_RXN8

PEG_RXP9

PEG_RXP9

PEG_RXN9

PEG_RXN9

PEG_RXP10

PEG_RXP10

PEG_RXN10

PEG_RXN10

PEG_RXP11

PEG_RXP11

PEG_RXN11

PEG_RXN11

PEG_RXP12

PEG_RXP12

PEG_RXN12

PEG_RXN12

PEG_RXP13

PEG_RXP13

PEG_RXN13

PEG_RXN13

PEG_RXP14

PEG_RXP14

PEG_RXN14

PEG_RXN14

PEG_RXP15

PEG_RXP15

PEG_RXN15

PEG_RXN15

HT26

HT26

1

HT27

HT27

1

HT28

HT28

1

5

XU1C

XU1C

B11

PEG_RX_0

B12

PEG_RX#_0

D12

PEG_RX_1

D11

PEG_RX#_1

C10

PEG_RX_2

C9

PEG_RX#_2

E10

PEG_RX_3

E9

PEG_RX#_3

B8

PEG_RX_4

B7

PEG_RX#_4

C6

PEG_RX_5

C5

PEG_RX#_5

A5

PEG_RX_6

A6

PEG_RX#_6

E2

PEG_RX_7

E1

PEG_RX#_7

F4

PEG_RX_8

F3

PEG_RX#_8

G2

PEG_RX_9

G1

PEG_RX#_9

H3

PEG_RX_10

H4

PEG_RX#_10

J1

PEG_RX_11

J2

PEG_RX#_11

K3

PEG_RX_12

K4

PEG_RX#_12

L1

PEG_RX_13

L2

PEG_RX#_13

M3

PEG_RX_14

M4

PEG_RX#_14

N1

PEG_RX_15

N2

PEG_RX#_15

W5

DMI_RX_0

W4

DMI_RX#_0

V3

DMI_RX_1

V4

DMI_RX#_1

Y3

DMI_RX_2

Y4

DMI_RX#_2

AA4

DMI_RX_3

AA5

DMI_RX#_3

P3

PE_RX_0

P4

PE_RX#_0

R2

PE_RX_1

R1

PE_RX#_1

T4

PE_RX_2

T3

PE_RX#_2

U2

PE_RX_3

U1

PE_RX#_3

SOCKET_1155P

SOCKET_1155P

I

I

Processor PCI Express*

Receive/ Transmit

Differential Pair. These

signals are available for

Workstation only.

PEG

PEG

DMI

DMI

GEN

GEN

PEG_TX_0

PEG_TX#_0

PEG_TX_1

PEG_TX#_1

PEG_TX_2

PEG_TX#_2

PEG_TX_3

PEG_TX#_3

PEG_TX_4

PEG_TX#_4

PEG_TX_5

PEG_TX#_5

PEG_TX_6

PEG_TX#_6

PEG_TX_7

PEG_TX#_7

PEG_TX_8

PEG_TX#_8

PEG_TX_9

PEG_TX#_9

PEG_TX_10

PEG_TX#_10

PEG_TX_11

PEG_TX#_11

PEG_TX_12

PEG_TX#_12

PEG_TX_13

PEG_TX#_13

PEG_TX_14

PEG_TX#_14

PEG_TX_15

PEG_TX#_15

DMI_TX_0

DMI_TX#_0

DMI_TX_1

DMI_TX#_1

DMI_TX_2

DMI_TX#_2

DMI_TX_3

DMI_TX#_3

PEG_ICOMPO

PEG_RCOMPO

PEG_COMPI

PE_TX_0

PE_TX#_0

PE_TX_1

PE_TX#_1

PE_TX_2

PE_TX#_2

PE_TX_3

PE_TX#_3

C13

C14

E14

E13

G14

G13

F12

F11

J14

J13

D8

D7

D3

C3

E6

E5

F8

F7

G10

G9

G5

G6

K7

K8

J5

J6

M8

M7

L6

L5

N5

N6

V7

V6

W7

W8

Y6

Y7

AA7

AA8

B5

C4

B4

P8

P7

T7

T8

R6

R5

U5

U6

4

PEG_TXP0

PEG_TXN0

PEG_TXN0

PEG_TXP1

PEG_TXP1

PEG_TXN1

PEG_TXN1

PEG_TXP2

PEG_TXP2

PEG_TXN2

PEG_TXN2

PEG_TXP3

PEG_TXP3

PEG_TXN3

PEG_TXN3

PEG_TXP4

PEG_TXP4

PEG_TXN4

PEG_TXN4

PEG_TXP5

PEG_TXP5

PEG_TXN5

PEG_TXN5

PEG_TXP6

PEG_TXP6

PEG_TXN6

PEG_TXN6

PEG_TXP7

PEG_TXP7

PEG_TXN7

PEG_TXN7

PEG_TXP8

PEG_TXP8

PEG_TXN8

PEG_TXN8

PEG_TXP9

PEG_TXP9

PEG_TXN9

PEG_TXN9

PEG_TXP10

PEG_TXP10

PEG_TXN10

PEG_TXN10

PEG_TXP11

PEG_TXP11

PEG_TXN11

PEG_TXN11

PEG_TXP12

PEG_TXP12

PEG_TXN12

PEG_TXN12

PEG_TXP13

PEG_TXP13

PEG_TXN13

PEG_TXN13

PEG_TXP14

PEG_TXP14

PEG_TXN14

PEG_TXN14

PEG_TXP15

PEG_TXP15

PEG_TXN15

PEG_TXN15

+1P05V_CPUIO

12

PEG_COMP

SHORT B4 & C4 TOGETHER, ROUTE AS A SINGLE 4 MIL TRACE TO HR3.2

ROUTE B5 TO HR3.2 AS A SEPERATE 10 MIL TRACE

HT39

HT39

1

12%20

12%20

DMI_TXP0 [18]

DMI_TXN0 [18]

DMI_TXP1 [18]

DMI_TXN1 [18]

DMI_TXP2 [18]

DMI_TXN2 [18]

DMI_TXP3 [18]

DMI_TXN3 [18]

,

,

HR3

HR3

24.9

24.9

1%

1%

PEG_TXP[0..15] [73]

PEG_TXN[0..15] [73]

XU1D

+1P05V_CPUIO

12

,

,

HR2

HR2

24.9

24.9

1%

1%

FDI_COMP

FDI_FSYNC_0[22]

FDI_LSYNC_0[22]

FDI_FSYNC_1[22]

FDI_LSYNC_1[22]

FDI_IN T[22]

XU1D

AE2

FDI_COMPIO

AE1

FDI_ICOMPO

AC5

FDI_FSYNC_0

AC4

FDI_LSYNC_0

AE5

FDI_FSYNC_1

AE4

FDI_LSYNC_1

AG3

FDI_INT

SOCKET_1155P

SOCKET_1155P

I

I

FDI

FDI

FDI_TX_0

FDI_TX#_0

FDI_TX_1

FDI_TX#_1

FDI_TX_2

FDI_TX#_2

FDI_TX_3

FDI_TX#_3

FDI_TX_4

FDI_TX#_4

FDI_TX_5

FDI_TX#_5

FDI_TX_6

FDI_TX#_6

FDI_TX_7

FDI_TX#_7

AC8

AC7

AC2

AC3

AD2

AD1

AD4

AD3

AD7

AD6

AE7

AE8

AF3

AF2

AG2

AG1

FDI_TXP0 [22]

FDI_TXN0 [22]

FDI_TXP1 [22]

FDI_TXN1 [22]

FDI_TXP2 [22]

FDI_TXN2 [22]

FDI_TXP3 [22]

FDI_TXN3 [22]

FDI_TXP4 [22]

FDI_TXN4 [22]

FDI_TXP5 [22]

FDI_TXN5 [22]

FDI_TXP6 [22]

FDI_TXN6 [22]

FDI_TXP7 [22]

FDI_TXN7 [22]

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

3

2

Date: Sheet

Engineer:

,336%)$

,336%)$

,336%)$

1

3&,('0,)',

3&,('0,)',

3&,('0,)',

Mike Yen

Mike Yen

Mike Yen

of

of

of

679Wednesday, April 27, 2011

679Wednesday, April 27, 2011

679Wednesday, April 27, 2011

Rev

Rev

Rev

1.01

1.01

1.01

5

CK_100M_DMI[22]

CK_100M_DMI#[22]

+1P05V_CPUIO

12

,

,

HR58

HR58

1K

1K

Description

X16(Default)

2X8

Reserved

X8, X4/X4

CK_100M_CPU_XDP[64]

CK_100M_CPU_XDP#[64]

12

1,

1,

HR5

HR5

Do Not Stuff

Do Not Stuff

1%

1%

127(

12

HR6

HR6

110

110

1%

1%

12

CPU_CFG0[64]

D D

VIDSCLK[58]

VIDSOUT[58]

VIDALERT#[58]

PLTRST_CPU#[13]

CPUPWRGD[20,64]

DRAM_PWROK[20]

C C

HR21 Do Not Stuff

HR21 Do Not Stuff

1 2

1,

PECI_PCH[19]

H_PECI[43]

PROCHOT#[58]

H_THMTRIP#[19,54]

PM_SYNC[19]

SKTOCC#[20]

PROC_SEL[22]

B B

1,

HR20 0

HR20 0

1 2

93

93

CFG[2]: PCI Express* Static x16 Lane Numbering Reversal.

- 1 = Normal operation

- 0 = Lane numbers reversed

CFG[0~15] is IPU

127(

CFG6 CFG5

11

,

,

,

,

10

01

00

H_DDR_VREF

12

,

,

D3CB17

D3CB17

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

5

+1P5V_DUAL

12

D3R39

D3R39

100

100

1%

1%

A A

12

D3R40

D3R40

100

100

1%

1%

GND GND

Place near CPU

12

,

,

,

,

12

HR14

HR14

2.2K

2.2K

4

127(

+1P5V_DUAL

12

,

,

1,

1,

HR7

HR7

HR4

HR4

75

75

Do Not Stuff

Do Not Stuff

1%

1%

HR11

HR11

,

,

HR70

HR70

,

,

127(

For VR Debug

TBD: CRB 0.7 is NI

+1P05V_CPUIO+1P8V_SFR

12

1,

1,

1,

1,

HR16

HR16

HR17

HR17

Do Not Stuff

Do Not Stuff

Do Not Stuff

Do Not Stuff

GND

4

12%20

12%20

12%20

12%20

ST29

ST29

ST48

ST48

Place HR57 near CPU 2"~3"

12

,

,

HR57

HR57

200

200

1%

1%

1 2

44.2

44.2

1%

1%

1 2

120

120

1%

1%

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

1

1

H_VIDALERT#

SM_DPWROK

12

1,

1,

HR59

HR59

Do Not Stuff

Do Not Stuff

GNDGND

127(

CRB UN-STUFF

12

1,

1,

,

,

HR19

HR19

HR18

HR18

Do Not Stuff

Do Not Stuff

51

51

H_PECI_R

CATERR_R#

H_DDR_VREF

PROC_SEL

HR24Do Not Stuff1,HR24Do Not Stuff

1,

H_CFG1

HR25Do Not Stuff1,HR25Do Not Stuff

1,

H_CFG2

HR27Do Not Stuff1,HR27Do Not Stuff

1,

H_CFG3

HR26Do Not Stuff1,HR26Do Not Stuff

1,

H_CFG4

HR28Do Not Stuff1,HR28Do Not Stuff

1,

H_CFG5

HR29Do Not Stuff1,HR29Do Not Stuff

1,

H_CFG6

HR30Do Not Stuff1,HR30Do Not Stuff

1,

H_CFG7

HR32Do Not Stuff1,HR32Do Not Stuff

1,

H_CFG8

HR31Do Not Stuff1,HR31Do Not Stuff

1,

H_CFG9

HR33Do Not Stuff1,HR33Do Not Stuff

1,

H_CFG10

HR34Do Not Stuff1,HR34Do Not Stuff

1,

H_CFG11

HR35Do Not Stuff1,HR35Do Not Stuff

1,

H_CFG12

HR37Do Not Stuff1,HR37Do Not Stuff

1,

H_CFG13

HR36Do Not Stuff1,HR36Do Not Stuff

1,

H_CFG14

HR39Do Not Stuff1,HR39Do Not Stuff

1,

H_CFG15

HR38Do Not Stuff1,HR38Do Not Stuff

1,

H_CFG16_SNB_PCUSTB0

H_CFG17_SNB_PCUSTB1

XU1E

XU1E

W2

BCLK_0

W1

BCLK#_0

C40

RSVD_001

D40

RSVD_002

C37

VIDSCLK

B37

VIDSOUT

A37

VIDALERT#

F36

RESET#

J40

UNCOREPWRGOOD

AJ19

SM_DRAMPWROK

J35

PECI

E37

CATERR#

H34

PROCHOT#

G35

THERMTRIP#

E38

PM_SYNC

AJ22

SM_VREF

AJ33

SKTOCC#

K32

PROC_SEL

H36

CFG_0

J36

CFG_1

J37

CFG_2

K36

CFG_3

L36

CFG_4

N35

CFG_5

L37

CFG_6

M36

CFG_7

J38

CFG_8

L35

CFG_9

M38

CFG_10

N36

CFG_11

N38

CFG_12

N39

CFG_13

N37

CFG_14

N40

CFG_15

G37

CFG_16

G36

CFG_17

AT14

RSVD_016

AY3

RSVD_023

H7

RSVD_028

H8

RSVD_029

SOCKET_1155P

SOCKET_1155P

I

I

3

3

MISC

MISC

VCCSA_VID

VCCSA_SENSE

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSSIO_SENSE

VCCAXG_SENSE

VSSAXG_SENSE

VCCP_SELECT

TDO

TCK

TMS

TRST#

PRDY#

PREQ#

DBR#

BPM#_0

BPM#_1

BPM#_2

BPM#_3

BPM#_4

BPM#_5

BPM#_6

BPM#_7

RSVD_024

RSVD_030

RSVD_037

RSVD_036

RSVD_033

RSVD_040

RSVD_039

RSVD_018

RSVD_020

RSVD_038

RSVD_032

RSVD_034

RSVD_035

RSVD_050

RSVD_053

RSVD_051

RSVD_052

2

P34

T2

A36

B36

AB4

AB3

L32

M32

+5V

12

,

,

HR52

HR52

10K

10K

P33

L39

L40

TDI

M40

L38

J39

12

,

,

HR53

HR53

4.7K

4.7K

127(

TBD: CRB is NI

K38

K40

E39

H40

H38

G38

G40

G39

F38

E40

F40

B39

J33

L34

L33

K34

N33

M34

AV1

AW2

L9

J9

K9

L31

J31

K31

AD34

AD35

HR54 0

HR54 0

1 2

93

93

BPM0# [64]

BPM1# [64]

BPM2# [64]

BPM3# [64]

BPM4# [64]

BPM5# [64]

BPM6# [64]

BPM7# [64]

2

+1P05V_CPUIO +1P05V_CPUIO

12

12

,

,

HR8

HR8

51

51

127(

Place near CPU

+3P3VSB

12

1,

1,

HR15

HR15

Do Not Stuff

Do Not Stuff

12

GNDGND

PEGATRON DT-MB RESTRICTED SECRET

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

,

,

HR9

HR9

51

51

,

,

HR12

HR12

51

51

12

GND

1

VCCSA_VID [53]

VCCSA_SENSE [53]

VCC_SENSE [58]

VSS_SENSE [58]

VCCIO_SENSE [53]

VSSIO_SENSE [53]

VCCAXG_SENSE [58]

VSSAXG_SENSE [58]

12

127(

,

,

HR10

HR10

Place near XDP connector

51

51

VCCIO_SEL [53]

TDO [64]

TDI [64]

TCK [64]

TMS [64]

TRST# [64]

,

,

HR13

HR13

51

51

H_PRDY# [64]

H_PREQ# [64]

SYS_RESET_DBR# [20,63,64]

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

,336%)$

,336%)$

,336%)$

1

0,6&

0,6&

0,6&

Mike Yen

Mike Yen

Mike Yen

779Wednesday, April 27, 2011

779Wednesday, April 27, 2011

779Wednesday, April 27, 2011

Rev

Rev

Rev

1.01

1.01

1.01

of

of

of

5

4

3

2

1

D D

C C

B B

A A

XU1F

XU1F

A12

VCC_001

A13

VCC_002

A14

VCC_003

A15

VCC_004

A16

VCC_005

A18

VCC_006

A24

VCC_007

A25

VCC_008

A27

VCC_009

A28

VCC_010

B15

VCC_011

B16

VCC_012

B18

VCC_013

B24

VCC_014

B25

VCC_015

B27

VCC_016

B28

VCC_017

B30

VCC_018

B31

VCC_019

B33

VCC_020

B34

VCC_021

C15

VCC_022

C16

VCC_023

C18

VCC_024

C19

VCC_025

C21

VCC_026

C22

VCC_027

C24

VCC_028

C25

VCC_029

C27

VCC_030

C28

VCC_031

C30

VCC_032

C31

VCC_033

C33

VCC_034

C34

VCC_035

C36

VCC_036

D13

VCC_037

D14

VCC_038

D15

VCC_039

D16

VCC_040

D18

VCC_041

D19

VCC_042

D21

VCC_043

D22

VCC_044

D24

VCC_045

D25

VCC_046

D27

VCC_047

D28

VCC_048

D30

VCC_049

D31

VCC_050

D33

VCC_051

D34

VCC_052

D35

VCC_053

D36

VCC_054

E15

VCC_055

E16

VCC_056

E18

VCC_057

E19

VCC_058

E21

VCC_059

E22

VCC_060

E24

VCC_061

E25

VCC_062

E27

VCC_063

E28

VCC_064

E30

VCC_065

E31

VCC_066

E33

VCC_067

E34

VCC_068

E35

VCC_069

F15

VCC_070

F16

VCC_071

F18

VCC_072

F19

VCC_073

F21

VCC_074

F22

VCC_075

F24

VCC_076

F25

VCC_077

F27

VCC_078

F28

VCC_079

F30

VCC_080

F31

VCC_081

VCC_082

VCC_083

VCC_084

VCC_085

VCC_086

VCC_087

VCC_088

VCC_089

VCC_090

VCC_091

VCC_092

VCC_093

VCC_094

VCC_095

VCC_096

VCC_097

VCC_098

VCC_099

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

VCC_123

VCC_124

VCC_125

VCC_126

VCC_127

VCC_128

VCC_129

VCC_130

VCC_131

VCC_132

VCC_133

VCC_134

VCC_135

VCC_136

VCC_137

VCC_138

VCC_139

VCC_140

VCC_141

VCC_142

VCC_143

VCC_144

VCC_145

VCC_146

VCC_147

VCC_148

VCC_149

VCC_150

VCC_151

VCC_152

VCC_153

VCC_154

VCC_155

VCC_156

VCC_157

VCC_158

VCC_159

VCC_160

VCC_161

F32

F33

F34

G15

G16

G18

G19

G21

G22

G24

G25

G27

G28

G30

G31

G32

G33

H13

H14

H15

H16

H18

H19

H21

H22

H24

H25

H27

H28

H30

H31

H32

J12

J15

J16

J18

J19

J21

J22

J24

J25

J27

J28

J30

K15

K16

K18

K19

K21

K22

K24

K25

K27

K28

K30

L13

L14

L15

L16

L18

L19

L21

L22

L24

L25

L27

L28

L30

M14

M15

M16

M18

M19

M21

M22

M24

M25

M27

M28

M30

+VCORE+VCORE

+1P05V_CPUIO

+0P925V_SA

+1P8V_SFR

AC24

AC24

4.7UF/6.3V

4.7UF/6.3V

1 2

X5R 10%

X5R 10%

,

,

mx_c0805

mx_c0805

GND

M13

AA3

AB8

AF8

AG33

AJ16

AJ17

AJ26

AJ28

AJ32

AK15

AK17

AK19

AK21

AK23

AK27

AK29

AK30

D10

H10

H11

H12

M10

M11

M12

AK11

AK12

A11

A7

B9

D6

E3

E4

G3

G4

J3

J4

J7

J8

L3

L4

L7

N3

N4

N7

R3

R4

R7

U3

U4

U7

V8

W3

J10

K10

K11

L11

L12

XU1H

XU1H

VCCIO_34

VCCIO_01

VCCIO_02

VCCIO_03

VCCIO_04

VCCIO_05

VCCIO_06

VCCIO_07

VCCIO_08

VCCIO_09

VCCIO_10

VCCIO_11

VCCIO_12

VCCIO_13

VCCIO_14

VCCIO_15

VCCIO_16

VCCIO_17

VCCIO_18

VCCIO_19

VCCIO_20

VCCIO_21

VCCIO_22

VCCIO_23

VCCIO_24

VCCIO_25

VCCIO_26

VCCIO_27

VCCIO_28

VCCIO_29

VCCIO_30

VCCIO_31

VCCIO_32

VCCIO_33

VCCIO_35

VCCIO_36

VCCIO_37

VCCIO_38

VCCIO_39

VCCIO_40

VCCIO_41

VCCIO_42

VCCIO_43

VCCIO_44

VCCIO_45

VCCSA_01

VCCSA_02

VCCSA_03

VCCSA_04

VCCSA_05

VCCSA_06

VCCSA_07

VCCSA_08

VCCSA_09

VCCSA_10

VCCSA_11

VCCPLL_01

VCCPLL_02

SOCKET_1155P

SOCKET_1155P

I

I

VDDQ_01

VDDQ_02

VDDQ_04

VDDQ_05

VDDQ_06

VDDQ_07

VDDQ_08

VDDQ_09

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

VDDQ_20

VDDQ_21

VDDQ_22

VDDQ_23

VDDQ_03

AJ13

AJ14

AJ23

AJ24

AR20

AR21

AR22

AR23

AR24

AU19

AU23

AU27

AU31

AV21

AV24

AV25

AV29

AV33

AW31

AY23

AY26

AY28

AJ20

+1P5V_DUAL

Place on the bottom under XU1

12

GND GND GND

,

,

HCB1

HCB1

22UF/6.3V

22UF/6.3V

X5R 20%

X5R 20%

mx_c0805_small

mx_c0805_small

12

,

,

HCB6

HCB6

22UF/6.3V

22UF/6.3V

X5R 20%

X5R 20%

mx_c0805_small

mx_c0805_small

12

,

,

HCB3

HCB3

22UF/6.3V

22UF/6.3V

X5R 20%

X5R 20%

mx_c0805_small

mx_c0805_small

+V_AXG

AB33

AB34

AB35

AB36

AB37

AB38

AB39

AB40

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

W33

W34

W35

W36

W37

W38

T33

T34

T35

T36

T37

T38

T39

T40

U33

U34

U35

U36

U37

U38

U39

U40

Y33

Y34

Y35

Y36

Y37

Y38

XU1G

XU1G

VCCAXG_01

VCCAXG_02

VCCAXG_03

VCCAXG_04

VCCAXG_05

VCCAXG_06

VCCAXG_07

VCCAXG_08

VCCAXG_09

VCCAXG_10

VCCAXG_11

VCCAXG_12

VCCAXG_13

VCCAXG_14

VCCAXG_15

VCCAXG_16

VCCAXG_17

VCCAXG_18

VCCAXG_19

VCCAXG_20

VCCAXG_21

VCCAXG_22

VCCAXG_23

VCCAXG_24

VCCAXG_25

VCCAXG_26

VCCAXG_27

VCCAXG_28

VCCAXG_29

VCCAXG_30

VCCAXG_31

VCCAXG_32

VCCAXG_33

VCCAXG_34

VCCAXG_35

VCCAXG_36

VCCAXG_37

VCCAXG_38

VCCAXG_39

VCCAXG_40

VCCAXG_41

VCCAXG_42

VCCAXG_43

VCCAXG_44

SOCKET_1155P

SOCKET_1155P

I

I

5

SOCKET_1155P

SOCKET_1155P

I

I

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

Engineer:

,336%)$

,336%)$

,336%)$

9&&

9&&

9&&

Mike Yen

Mike Yen

Mike Yen

879Tuesday, April 26, 2011

879Tuesday, April 26, 2011

1

879Tuesday, April 26, 2011

Rev

Rev

Rev

1.01

1.01

1.01

of

of

of

5

XU1I

XU1I

A17

VSS_001

A23

VSS_002

A26

VSS_003

A29

VSS_004

D D

C C

B B

A A

A35

VSS_005

AA33

VSS_006

AA34

VSS_007

AA35

VSS_008

AA36

VSS_009

AA37

VSS_010

AA38

VSS_011

AA6

VSS_012

AB5

VSS_013

AC1

VSS_014

AC6

VSS_015

AD33

VSS_016

AD36

VSS_017

AD38

VSS_018

AD39

VSS_019

AD40

VSS_020

AD5

VSS_021

AD8

VSS_022

AE3

VSS_023

AE33

VSS_024

AE36

VSS_025

AF1

VSS_026

AF34

VSS_027

AF36

VSS_028

AF37

VSS_029

AF40

VSS_030

AF5

VSS_031

AF6

VSS_032

AF7

VSS_033

AG36

VSS_034

AH2

VSS_035

AH3

VSS_036

AH33

VSS_037

AH36

VSS_038

AH37

VSS_039

AH38

VSS_040

AH39

VSS_041

AH40

VSS_042

AH5

VSS_043

AH8

VSS_044

AJ12

VSS_045

AJ15

VSS_046

AJ18

VSS_047

AJ21

VSS_048

AJ25

VSS_049

AJ27

VSS_050

AJ36

VSS_051

AJ5

VSS_052

AK1

VSS_053

AK10

VSS_054

AK13

VSS_055

AK14

VSS_056

AK16

VSS_057

AK22

VSS_058

AK28

VSS_059

AK31

VSS_060

AK32

VSS_061

AK33

VSS_062

AK34

VSS_063

AK35

VSS_064

AK36

VSS_065

AK37

VSS_066

AK4

VSS_067

AK40

VSS_068

AK5

VSS_069

AK6

VSS_070

AK7

VSS_071

AK8

VSS_072

AK9

VSS_073

AL11

VSS_074

AL14

VSS_075

AL17

VSS_076

AL19

VSS_077

AL24

VSS_078

AL27

VSS_079

AL30

VSS_080

AL36

VSS_081

AL5

VSS_082

AM1

VSS_083

AM11

VSS_084

AM14

VSS_085

AM17

VSS_086

AM2

VSS_087

AM21

VSS_088

AM23

VSS_089

AM25

VSS_090

A4

VSS_NCTF_01

AV39

VSS_NCTF_02

GND GND GND GND

SOCKET_1155P

SOCKET_1155P

I

I

5

GND

GND

VSS_091

VSS_092

VSS_093

VSS_094

VSS_095

VSS_096

VSS_097

VSS_098

VSS_099

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

AM27

AM3

AM30

AM36

AM37

AM38

AM39

AM4

AM40

AM5

AN10

AN11

AN14

AN17

AN19

AN22

AN24

AN27

AN30

AN31

AN32

AN33

AN34

AN35

AN36

AN5

AN6

AN7

AN8

AN9

AP1

AP11

AP14

AP17

AP22

AP25

AP27

AP30

AP36

AP37

AP4

AP40

AP5

AR11

AR14

AR17

AR18

AR19

AR27

AR30

AR36

AR5

AT1

AT10

AT12

AT13

AT15

AT16

AT17

AT2

AT25

AT27

AT28

AT29

AT3

AT30

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AT39

AT4

AT40

AT5

AT6

AT7

AT8

AT9

AU1

AU15

AU26

AU34

AU4

AU6

AU8

AV10

4

AV11

AV14

AV17

AV35

AV38

AW10

AW11

AW14

AW16

AW36

AW6

AY11

AY14

AY18

AY35

AY37

4

AV3

AV6

AY4

AY6

AY8

B10

B13

B14

B17

B23

B26

B29

B32

B35

B38

C11

C12

C17

C20

C23

C26

C29

C32

C35

D17

D20

D23

D26

D29

D32

D37

D39

E11

E12

E17

E20

E23

E26

E29

E32

E36

F10

F13

F14

F17

F20

F23

F26

F29

F35

F37

F39

G11

G12

G17

G20

G23

G26

G29

G34

B6

C7

C8

D2

D4

D5

D9

E7

E8

F1

F2

F5

F6

F9

G7

B3

XU1J

XU1J

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_NCTF_03

VSS_NCTF_04

GND

GND

SOCKET_1155P

SOCKET_1155P

I

I

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_355

VSS_356

VSS_357

VSS_358

VSS_359

VSS_360

G8

H1

H17

H2

H20

H23

H26

H29

H33

H35

H37

H39

H5

H6

H9

J11

J17

J20

J23

J26

J29

J32

K1

K12

K13

K14

K17

K2

K20

K23

K26

K29

K33

K35

K37

K39

K5

K6

L10

L17

L20

L23

L26

L29

L8

M1

M17

M2

M20

M23

M26

M29

M33

M35

M37

M39

M5

M6

M9

N8

P1

P2

P36

P38

P40

P5

P6

R33

R35

R37

R39

R8

T1

T5

T6

U8

V1

V2

V33

V34

V35

V36

V37

V38

V39

V40

V5

W6

Y5

Y8

3

XU1K

XU1K

AB7

RSVD_04

AD37

RSVD_05

AG4

RSVD_08

AJ29

RSVD_10

AJ30

RSVD_11

AJ31

RSVD_12

AV34

RSVD_19

AW34

RSVD_21

P35

RSVD_43

P37

RSVD_44

P39

RSVD_45

R34

RSVD_46

R36

RSVD_47

R38

RSVD_48

R40

RSVD_49

A38

NCTF_01

AU40

NCTF_02

AW38

NCTF_03

C2

NCTF_04

D1

NCTF_05

SOCKET_1155P

SOCKET_1155P

I

I

,

,

%$&.3/$7(

%$&.3/$7(

INTEL LGA 1156P BACK PLATE,3 SCREW

INTEL LGA 1156P BACK PLATE,3 SCREW

PT44P11-6401

PT44P11-6401

H28

H28

1

Do Not Stuff

Do Not Stuff

12%20

12%20

H29

H29

1

Do Not Stuff

Do Not Stuff

12%20

12%20

H30

H30

1

Do Not Stuff

Do Not Stuff

12%20

12%20

H31

H31

1

Do Not Stuff

Do Not Stuff

12%20

12%20

3

2

SA_DIMM_VR

AH1

FC_AH1

FC_AH4

RSVD_15

RSVD_14

RSVD_13

RSVD_17

RSVD_22

RSVD_07

RSVD_03

RSVD_06

RSVD_09

RSVD_27

RSVD_26

RSVD_25

RSVD_31

RSVD_41

NP_NC1

NP_NC2

NP_NC3

NP_NC4

NP_NC5

NP_NC6

NP_NC7

AH4

AT11

AP20

AN20

AU10

AY10

AF4

AB6

AE6

AJ11

D38

C39

C38

J34

N34

1

2

3

4

5

6

7

SB_DIMM_VR

SFA 1.01

2

12

,

,

HC2

HC2

0.1UF/16V

0.1UF/16V

GND GND

,

,

,/0

,/0

INTEL LGA1156 SOCKET ILM

INTEL LGA1156 SOCKET ILM

SOCKET1156_ILM

SOCKET1156_ILM

1

HR42 0

HR42 0

1 2

,9%

,9%

HR43 0

HR43 0

1 2

,9%

,9%

12

,

,

HC3

HC3

0.1UF/16V

0.1UF/16V

DIMM_VREF_A [10]

DIMM_VREF_B [11]

Stuff

resistors

HR42/HR43

for future

IVB VREF

capability

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Engineer:

,336%)$

,336%)$

,336%)$

966

966

966

Mike Yen

Mike Yen

Mike Yen

979Wednesday, April 27, 2011

979Wednesday, April 27, 2011

1

979Wednesday, April 27, 2011

Rev

Rev

Rev

1.01

1.01

1.01

of

of

of

5

4

3

2

1

ઃઃઃઃޏޏޏޏ

D D

M_CHA_MAA0

M_CHA_MAA1

M_CHA_MAA2

M_CHA_MAA3

M_CHA_MAA4

M_CHA_MAA5

M_CHA_MAA6

M_CHA_MAA7

M_CHA_MAA8

M_CHA_MAA9

M_CHA_MAA10

M_CHA_MAA11

M_CHA_MAA12

M_CHA_MAA13

M_CHA_MAA14

M_CHA_MAA15

M_CHA_CLK1[4]

M_CHA_CLK1#[4]

M_CHA_CLK0[4]

C C

B B

M_CHA_CLK0#[4]

M_CHA_CS#1[4]

M_CHA_CS#0[4]

M_CHA_ODT1[4]

M_CHA_ODT0[4]

M_CHA_WE#[4]

M_CHA_RAS#[4]

M_CHA_CAS#[4]

M_CHA_BA2[4]

M_CHA_BA1[4]

M_CHA_BA0[4]

M_CHA_CKE1[4]

M_CHA_CKE0[4]

M_CHA_DQS7[4]

M_CHA_DQS7#[4]

M_CHA_DQS6[4]

M_CHA_DQS6#[4]

M_CHA_DQS5[4]

M_CHA_DQS5#[4]

M_CHA_DQS4[4]

M_CHA_DQS4#[4]

M_CHA_DQS3[4]

M_CHA_DQS3#[4]

M_CHA_DQS2[4]

M_CHA_DQS2#[4]

M_CHA_DQS1[4]

M_CHA_DQS1#[4]

M_CHA_DQS0[4]

M_CHA_DQS0#[4]

GND

SMB_CLK_M[11,37,38,45,63,64,79]

SMB_DATA_M[11,37,38,45,63,64,79]

GND

5.2H

DIMMA0A

DIMMA0A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

102

CK1

104

CK1#

101

CK0

103

CK0#

121

S1#

114

S0#

120

ODT1

116

ODT0

113

WE#

110

RAS#

115

CAS#

79

BA2

108

BA1

109

BA0

74

CKE1

73

CKE0

201

SA1

197

SA0

188

DQS7

186

DQS#7

171

DQS6

169

DQS#6

154

DQS5

152

DQS#5

137

DQS4

135

DQS#4

64

DQS3

62

DQS#3

47

DQS2

45

DQS#2

29

DQS1

27

DQS#1

12

DQS0

10

DQS#0

187

DM7

170

DM6

153

DM5

136

DM4

63

DM3

46

DM2

28

DM1

11

DM0

202

SCL

200

SDA

DDR3_DIMM_204P

DDR3_DIMM_204P

I

I

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

RESET#

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

30

M_CHA_DQ1

M_CHA_DQ5

M_CHA_DQ2

M_CHA_DQ3

M_CHA_DQ0

M_CHA_DQ4

M_CHA_DQ7

M_CHA_DQ6

M_CHA_DQ13

M_CHA_DQ12

M_CHA_DQ15

M_CHA_DQ14

M_CHA_DQ8

M_CHA_DQ9

M_CHA_DQ11

M_CHA_DQ10

M_CHA_DQ17

M_CHA_DQ20

M_CHA_DQ23

M_CHA_DQ18

M_CHA_DQ16

M_CHA_DQ21

M_CHA_DQ19

M_CHA_DQ22

M_CHA_DQ29

M_CHA_DQ28

M_CHA_DQ31

M_CHA_DQ30

M_CHA_DQ24

M_CHA_DQ25

M_CHA_DQ27

M_CHA_DQ26

M_CHA_DQ33

M_CHA_DQ36

M_CHA_DQ38

M_CHA_DQ39

M_CHA_DQ32

M_CHA_DQ37

M_CHA_DQ34

M_CHA_DQ35

M_CHA_DQ41

M_CHA_DQ45

M_CHA_DQ47

M_CHA_DQ42

M_CHA_DQ44

M_CHA_DQ40

M_CHA_DQ46

M_CHA_DQ43

M_CHA_DQ53

M_CHA_DQ52

M_CHA_DQ51

M_CHA_DQ50

M_CHA_DQ48

M_CHA_DQ49

M_CHA_DQ54

M_CHA_DQ55

M_CHA_DQ57

M_CHA_DQ56

M_CHA_DQ63

M_CHA_DQ62

M_CHA_DQ61

M_CHA_DQ60

M_CHA_DQ59

M_CHA_DQ58

M_CHA_MAA[0..15] [4]

M_CHA_DQ[0..63] [4]

DDR3_DRAMRST# [4,11]

I

+1P5V_DUAL

GND

+1P5V_DUAL +1P5V_DUAL

12

12

,

,

,

,

D3R30

D3R30

D3R31

D3R31

1K

1K

1K

1K

1%

1%

1%

1%

DIMM_VREF_A[9]

12

12

,

,

,

,

D3R32

D3R32

D3R22

D3R22

1K

1K

1K

1K

1%

1%

1%

1%

GND GND GND GND

12

,

,

D3CB48

D3CB48

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

DIMM_CA_VREF_A

DIMM_VREF_A

12

,

,

D3CB15

D3CB15

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

I

DIMMA0B

DIMMA0B

75

VDD1

81

VDD3

87

VDD5

93

VDD7

99

VDD9

105

VDD11

111

VDD13

117

VDD15

123

VDD17

2

VSS1

8

VSS3

13

VSS5

19

VSS7

25

VSS9

31

VSS11

37

VSS13

43

VSS15

48

VSS17

54

VSS19

60

VSS21

65

VSS23

71

VSS25

127

VSS27

133

VSS29

138

VSS31

144

VSS33

150

VSS35

155

VSS37

161

VSS39

167

VSS41

172

VSS43

178

VSS45

184

VSS47

189

VSS49

195

VSS51

198

EVENT#

125

TEST

77

NC1

122

NC2

126

VREFCA

1

VREFDQ

DDR3_DIMM_204P

DDR3_DIMM_204P

VDD2

VDD4

VDD6

VDD8

VDD10

VDD12

VDD14

VDD16

VDD18

VSS2

VSS4

VSS6

VSS8

VSS10

VSS12

VSS14

VSS16

VSS18

VSS20

VSS22

VSS24

VSS26

VSS28

VSS30

VSS32

VSS34

VSS36

VSS38

VSS40

VSS42

VSS44

VSS46

VSS48

VSS50

VSS52

GND1

GND2

NP_NC1

NP_NC2

VTT1

VTT2

VDDSPD

76

82

88

94

100

106

112

118

124

3

9

14

20

26

32

38

44

49

55

61

66

72

128

134

139

145

151

156

162

168

173

179

185

190

196

207

208

205

206

203

204

199

1UF/6.3V

1UF/6.3V

X5R 10%

X5R 10%

C9351

C9351

I

I

+1P5V_DUAL

12

C9350

C9350

1UF/6.3V

1UF/6.3V

X5R 10%

X5R 10%

GND

I

I

+3P3V

GNDGND

12

D3CB1

D3CB1

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

,

,

GND

12

D3CB49

D3CB49

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

12

,

,

4.7UF/6.3V

4.7UF/6.3V

mx_c0805_small

mx_c0805_small

D3CB16

D3CB16

X5R 10%

X5R 10%

+VTT_DDR

12

,

,

GNDGND

A A

''5&+$11(/$

''5&+$11(/$

''5&+$11(/$

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Engineer:

,336%)$

,336%)$

,336%)$

1

Mike Yen

Mike Yen

Mike Yen

10 79Wednesday, April 27, 2011

10 79Wednesday, April 27, 2011

10 79Wednesday, April 27, 2011

Rev

Rev

Rev

1.01

1.01

1.01

of

of

of

5

4

3

2

1

ઃઃઃઃޏޏޏޏ

D D

M_CHB_MAA0

M_CHB_MAA1

M_CHB_MAA2

M_CHB_MAA3

M_CHB_MAA4

M_CHB_MAA5

M_CHB_MAA6

M_CHB_MAA7

M_CHB_MAA8

M_CHB_MAA9

M_CHB_MAA10

M_CHB_MAA11

M_CHB_MAA12

M_CHB_MAA13

M_CHB_MAA14

M_CHB_MAA15

M_CHB_CLK1[5]

M_CHB_CLK1#[5]

M_CHB_CLK0[5]

C C

B B

M_CHB_CLK0#[5]

M_CHB_CS#1[5]

M_CHB_CS#0[5]

M_CHB_ODT1[5]

M_CHB_ODT0[5]

M_CHB_WE#[5]

M_CHB_RAS#[5]

M_CHB_CAS#[5]

M_CHB_BA2[5]

M_CHB_BA1[5]

M_CHB_BA0[5]

M_CHB_CKE1[5]

M_CHB_CKE0[5]

M_CHB_DQS7[5]

M_CHB_DQS7#[5]

M_CHB_DQS6[5]

M_CHB_DQS6#[5]

M_CHB_DQS5[5]

M_CHB_DQS5#[5]

M_CHB_DQS4[5]

M_CHB_DQS4#[5]

M_CHB_DQS3[5]

M_CHB_DQS3#[5]

M_CHB_DQS2[5]

M_CHB_DQS2#[5]

M_CHB_DQS1[5]

M_CHB_DQS1#[5]

M_CHB_DQS0[5]

M_CHB_DQS0#[5]

GND

SMB_CLK_M[10,37,38,45,63,64,79]

SMB_DATA_M[10,37,38,45,63,64,79]

+3P3V

GND

5.2H

+

',00%$

',00%$

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

102

CK1

104

CK1#

101

CK0

103

CK0#

121

S1#

114

S0#

120

ODT1

116

ODT0

113

WE#

110

RAS#

115

CAS#

79

BA2

108

BA1

109

BA0

74

CKE1

73

CKE0

201

SA1

197

SA0

188

DQS7

186

DQS#7

171

DQS6

169

DQS#6

154

DQS5

152

DQS#5

137

DQS4

135

DQS#4

64

DQS3

62

DQS#3

47

DQS2

45

DQS#2

29

DQS1

27

DQS#1

12

DQS0

10

DQS#0

187

DM7

170

DM6

153

DM5

136

DM4

63

DM3

46

DM2

28

DM1

11

DM0

202

SCL

200

SDA

DDR3_DIMM_204P

DDR3_DIMM_204P

I

I

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

RESET#

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

30

M_CHB_DQ0

M_CHB_DQ4

M_CHB_DQ7

M_CHB_DQ6

M_CHB_DQ1

M_CHB_DQ5

M_CHB_DQ2

M_CHB_DQ3

M_CHB_DQ13

M_CHB_DQ12

M_CHB_DQ15

M_CHB_DQ14

M_CHB_DQ8

M_CHB_DQ9

M_CHB_DQ10

M_CHB_DQ11

M_CHB_DQ20

M_CHB_DQ21

M_CHB_DQ23

M_CHB_DQ22

M_CHB_DQ16

M_CHB_DQ17

M_CHB_DQ18

M_CHB_DQ19

M_CHB_DQ24

M_CHB_DQ25

M_CHB_DQ27

M_CHB_DQ26

M_CHB_DQ28

M_CHB_DQ29

M_CHB_DQ30

M_CHB_DQ31

M_CHB_DQ32

M_CHB_DQ33

M_CHB_DQ38

M_CHB_DQ39

M_CHB_DQ36

M_CHB_DQ37

M_CHB_DQ34

M_CHB_DQ35

M_CHB_DQ40

M_CHB_DQ41

M_CHB_DQ47

M_CHB_DQ46

M_CHB_DQ44

M_CHB_DQ45

M_CHB_DQ42

M_CHB_DQ43

M_CHB_DQ52

M_CHB_DQ53

M_CHB_DQ51

M_CHB_DQ50

M_CHB_DQ49

M_CHB_DQ48

M_CHB_DQ54

M_CHB_DQ55

M_CHB_DQ61

M_CHB_DQ60

M_CHB_DQ62

M_CHB_DQ63

M_CHB_DQ57

M_CHB_DQ56

M_CHB_DQ59

M_CHB_DQ58

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

D3C4

D3C4

,

,

GND

12

DDR3_DRAMRST# [4,10]

M_CHB_DQ[0..63] [5]

M_CHB_MAA[0..15] [5]

DIMM_VREF_B[9]

+1P5V_DUAL +1P5V_DUAL

12

12

,

,

,

,

D3R33

D3R33

D3R36

D3R36

1K

1K

1K

1K

1%

1%

1%

1%

12

12

,

,

D3R35

D3R35

1K

1K

1%

1%

GND GND GND GND

,

,

D3R37

D3R37

1K

1K

1%

1%

12

,

,

D3CB51

D3CB51

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

+1P5V_DUAL

GND

DIMM_CA_VREF_B

DIMM_VREF_B

12

,

,

D3CB50

D3CB50

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

',00%%

',00%%

75

VDD1

81

VDD3

87

VDD5

93

VDD7

99

VDD9

105

VDD11

111

VDD13

117

VDD15

123

VDD17

2

VSS1

8

VSS3

13

VSS5

19

VSS7

25

VSS9

31

VSS11

37

VSS13

43

VSS15

48

VSS17

54

VSS19

60

VSS21

65

VSS23

71

VSS25

127

VSS27

133

VSS29

138

VSS31

144

VSS33

150

VSS35

155

VSS37

161

VSS39

167

VSS41

172

VSS43

178

VSS45

184

VSS47

189

VSS49

195

VSS51

198

EVENT#

125

TEST

77

NC1

122

NC2

126

VREFCA

1

VREFDQ

DDR3_DIMM_204P

DDR3_DIMM_204P

I

I

VDD2

VDD4

VDD6

VDD8

VDD10

VDD12

VDD14

VDD16

VDD18

VSS2

VSS4

VSS6

VSS8

VSS10

VSS12

VSS14

VSS16

VSS18

VSS20

VSS22

VSS24

VSS26

VSS28

VSS30

VSS32

VSS34

VSS36

VSS38

VSS40

VSS42

VSS44

VSS46

VSS48

VSS50

VSS52

GND1

GND2

NP_NC1