Page 1

C

VT83201

3.3V Low Phase Noise VCXO

(Voltage-Controlled Crystal Oscillator)

and PLL Clock Synthesizer

Applications

•= DSL clock source

•= Set-top boxes

•= Telecom switching

General Description

The Vaishali VT83201 is a single-c hip, integrated VCXO and Phase Locked Loop (PLL) clock synthesizer.

The device uses the VCXO and an analog Phase-Loc ked Loop (PLL) to ac cept a 10 MHz to 20 MHz, 30pF

(pull range of 200 ppm ) crystal input, in order to produce either one or two output clock s. A 0 to 3V c ontrol

signal is used to fine tune the output clock frequency in the ±100ppm range. Select inputs S0 and S1 ar e

used for frequency and output selection.

Features

•= 3.3V supply operation

•= Packaged in 16-pin SOIC package

•= Replaces separate VCXO and multiplier

•= Uses inexpensive pullable crystal

•= On-chip VCXO with 200 ppm pull range (±100 ppm)

•= MPEG Video clock source

•= HDTV

•= 5V-tolerant control inputs

•= Zero ppm synthesis error in both

clocks

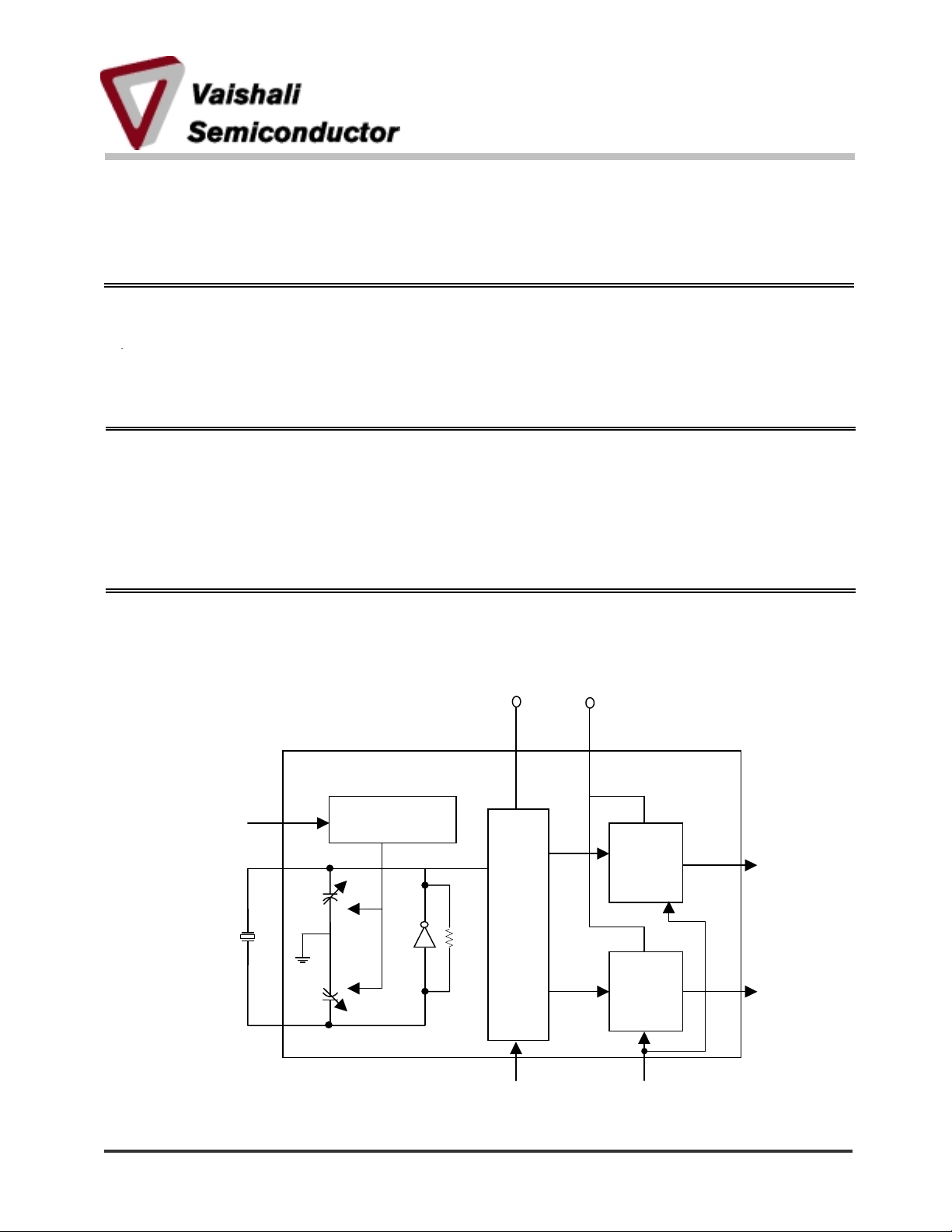

Figure 1. Functional Block Diagram

VIN

10-20 MHz

Pullable

Crystal

X2

X1

Load Cap Control

Load

Caps

VDD1 VDD2

Low

Phase

osc

Noise

PLL

Output

Buffer

Output

Buffer

LK1

CLK2

2001-04-12 Page 1 MDST-0011-01

Vaishali Semic onductor 747 Camden Avenue, Suite C Cam pbel l CA 95008 P h. 408.377.6060 Fax 408.377.6063

S1:S0

www.vaishali.com

OE

Page 2

VT83201

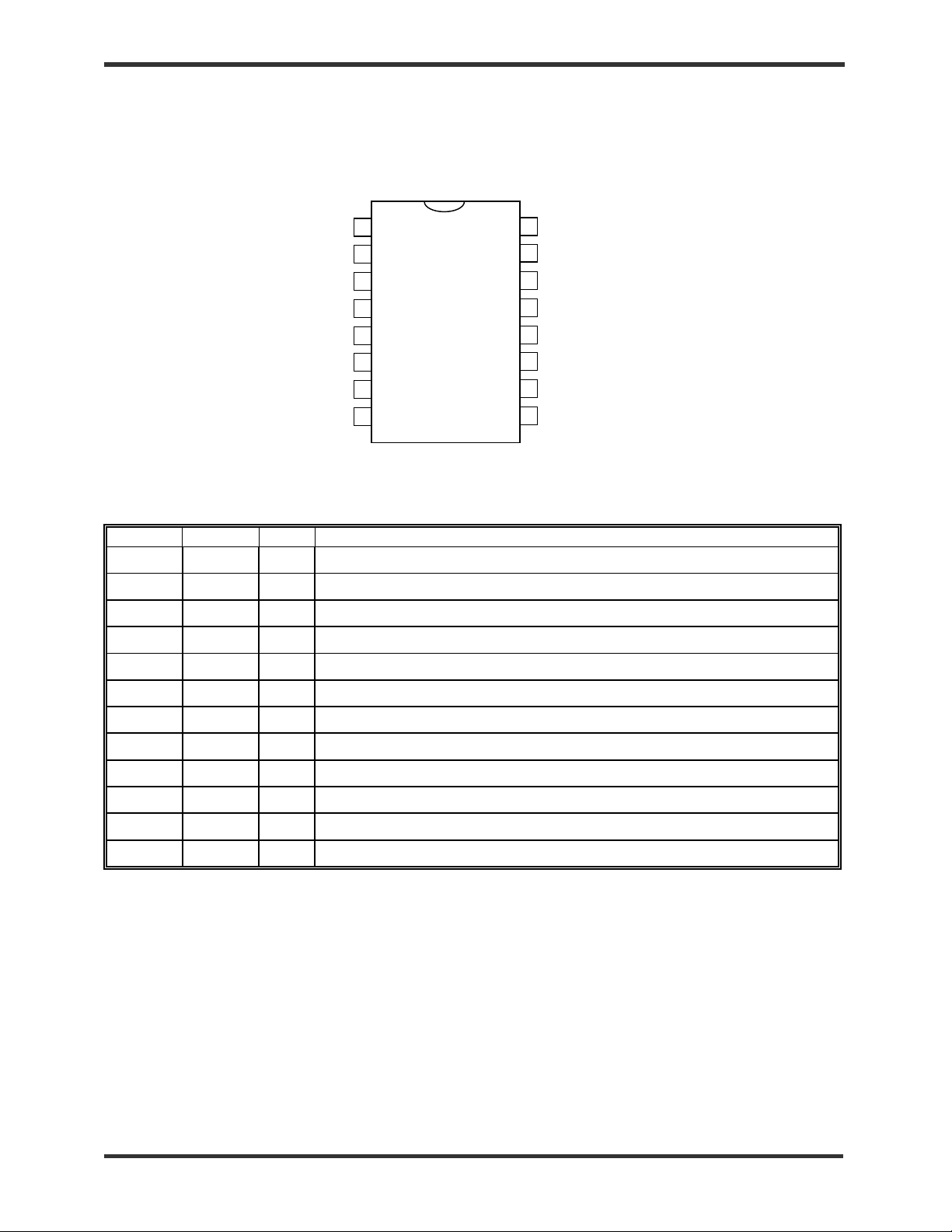

Figure 2. Pin Configuration

VT83201

16 pin SOIC

X1

V

DD

V

DD

VIN

GND

GND

GND

OE

1

1

2

3

1

4

5

6

7

8

16

15

14

13

12

11

10

X2

NC

S1

GND

CLK2

VDD2

S0

9

CLK1

Table 1. Pin Description

Name Pin # Type Description

X1 1 XI Crystal connection. Connect to a pullable crystal of 10–20 MHz

VDD1 2,3 P Core VDD. Connect to 3.3V

VIN 4 I Voltage input to VCXO. Zero to 3V signal controls the frequency of the VCXO.

GND 5,6, 7,13 P Connect to ground.

OE 8 I Active HIGH Output enable . Outputs in Hi-Z state when LOW

CLK1 9 O Clock output #1 per Table 2.

S0 10 I Select input #0. Selects output per Table 2

VDD2 11 P Output VDD. Connect to 3.3V

CLK2 12 O Clock output #2 per Table 2

S1 14 I Select input #1. Selects outputs per Table 2

NC 15 - There is no internal connection to this pin.

X2 16 XO Crystal connection. Connect to a pullable crystal of 10 MHz – 20 MHz.

Legend: I = Input

O = Output

P = Power supply connection

XI, XO = Crystal connections.

2001-04-12 Page 2 MDST-0011-01

www.Vaishali.com

Vaishali Semic onductor 747 Camden Avenue, Suite C Cam pbel l CA 95008 P h. 408.377.6060 Fax 408.377.6063

Page 3

VT83201

Table 2. Clock Selection Table (OE = High)

S1 S0 CLK1 CLK2

0 0 REF/4 REF/2

0 M

0 1 OFF X 2.6666

1 0 OFF X 4

1 1 OFF X 1.3333

Note:

1. SO has three valid states: 0 (LOW) = VIN ≤ 0.5V

1 (HIGH) = V

M (MID) = 0.5V

(1)

OFF X 0.666

≥ VDD – 0.5

IN

< VIN < VDD – 0.5V

Table 3. Absolute Maximum Ratings

Parameter Conditions Min Typ Max Units

Supply voltage, VDD Referenced to GND 4.6 V

Inputs and Clock Outputs Referenced to GND -0.5 VDD+0.5 V

Soldering Temperature Max of 10 seconds 260 °C

Storage temperature -65 150 °C

Stresses above those li st ed under Abs olute Maxim um Ratings may caus e permanent dam age to the device. These ratings are stress

specifications onl y and c orrect f unct ional operat ion of t he device at thes e or any other c ondit ions above t hos e lis ted in t he operational

sections of t he specifications is not i mplied. Exposure to absolute maxim um rating conditions for extended periods may affect product

reliability.

Table 4. Operating Conditions

Parameter Conditions Min Typ Max Units

Operating Voltage, VDD 3.15 3.3 3.45 V

Input High Voltage, VIH, X1 pin only 2.5 V

Input Low Voltage, VIL, X1 pin only 0.4 V

Input High Voltage, VIH, binary inputs S1, OE 2 V

Input Low Voltage, VIL, binary inputs S1, OE 0.8 V

Input High Voltage, VIH, trinary input S0 VDD-0.5 V

Input Low Voltage, VIL, trinary input S0 0.5 V

Operating Temperature 0 70 °C

VCXO control voltage, VIN 0 3 V

Table 5. DC Electrical Characteristics

TA = 0°C to +70°C, VDD = 3.15 V to 3.45 V

Parameter Condition Min Typ

Output High Voltage, VOH I

Output Low Voltage, VOL I

Operating Supply Current, IDD No Load 38 mA

=-25mA 2.4 V

OH

=25mA 0.4 V

OL

(1)

Max Units

Short Circuit Current Each output ±85 mA

Input Capacitance S0, S1, OE 7 pF

Note:

1. Typical values are at V

2001-04-12 Page 3 MDST-0011-01

Vaishali Semic onductor 747 Camden Avenue, Suite C Cam pbel l CA 95008 P h. 408.377.6060 Fax 408.377.6063

= 3.3V and 25°C

DD

www.Vaishali.com

Page 4

VT83201

Table 6. AC Electrical Characteristics

TA = 0°C to +70°C, VDD = 3.15 V to 3.45 V

Symbol Parameter Condition Min Typ Max Units

Fosc Input Crystal Frequency 10 20 MHz

tr Output Clock Rise Time 0.8 to 2.0V 1.5 ns

tf Output Clock Fall Time 2.0 to 0.8V 1.5 ns

tod Output Cloc k Duty Cycle At VDD/2 40 60 %

tpZL, tpZH Enable Time. OE to CLK CL = 50pf 5 6.5 ns

tpLZ, tpHZ Disable Time. OE to CLK CL = 50pf 4 5.5 ns

t

(pk – pk) Maximum Absolute Jitter

jit

(Peak to Peak)

Phase Noise, relative to

carrier

Output pullability 0V <VIN <3V ±100 ppm

Note:

1. Typical values are at V

= 3.3V and 25°C

DD

±100 ps

10 KHz offset -115 dBc/Hz

Table 7 Pullable Crystal Specifications

Parameter Value

Correlation (load) capacitance 30 pF

C0/C1 240 max

ESR

Operating Temperature

Initial Accuracy ±20 ppm

Temperature + Aging Stability ±50 ppm

35 Ω max

0°C to +70°C

Figure 3. External Crystal Connection Block Diagram

10-20 MHz

Pullable Crystal

X2

X1

XTAL OSC

XTAL OSC

PLL

PLL

CLOCK

CLOCK

GEN

Clk 1

Clk 2

OE

Ordering Information

Part Number Marking Shipping/Packaging No. of Pins Package Temperature

VT83201S1 VT83201S1 Tubes 16 SOIC

VT83201S1X VT83201S1 Tape & Reel 16 SOIC

VT83201/D Dice in waffle packe

VT83201/DW Dice in wafer form

2001-04-12 Page 4 MDST-0011-01

www.Vaishali.com

Vaishali Semic onductor 747 Camden Avenue, Suite C Cam pbel l CA 95008 P h. 408.377.6060 Fax 408.377.6063

0°C to +70°C

0°C to +70°C

0°C to +70°C

0°C to +70°C

Loading...

Loading...