Page 1

STV9432TAP

100MHz OSD FOR MONITOR INCLUDING

BEAM CURRENTS, VIDEO TIMING ANALYZER AND PWMs

■ MULTIFUNCTION OSD FOR MONITOR

■ INCLUDES FACILITIES FOR CUT-OFF VOLT-

AGE MONITORING:

- THREE 8 BITS ADC INPUTS

- ADC TRIGGER DURING RETRACE TIME OFA

PROGRAMMED LINE

■ INCLUDES FACILITIES FOR SCREEN SIZE &

CENTERING AUTO SETUP

- HS, VS, VIDEO TIMING MEASUREMENTS

■ 100MHz MAX. PIXEL CLOCK, AVAILABLE FOR

ANY LINE FREQUENCY BETWEEN 15 AND 140

kHz

■ 12 x 18 CHARACTER ROM FONT INCLUDES:

- 240 MONOCOLOR CHARACTERS

- 16 MULTICOLOR CHARACTERS

■ CHARACTER FLASHING

■ UP TO 1K CHARACTERS TEXT DISPLAY

■ ULTRAHIGH FREQUENCY PLL FOR

■ JITTER-FREE DISPLAY

■ FLEXIBLE DISPLAY:

- ANY CHARACTER WIDTH AND HEIGHT

- ANYWHERE IN THE SCREEN

■ SINGLE BYTE CHARACTER CODES AND

COLOR LOOK-UP TABLE FOR EASY PROGRAMMING AND FAST ACCESS

■ CHARACTER FLIP OPERATIONS

■ WIDE DISPLAY WINDOW ALLOWS PATTERN

GENERATION FORFACTORY ADJUSTMENTS

2

■ I

C BUS MCU INTERFACE

■ FIVE 8 BITS PWM DAC OUTPUTS

DESCRIPTION

Connected to a host MCU via its serial I2C Bus, the

STV9432TAP is a multifunction slave peripheral

device integrating the following blocks:

- On-screen Display. It includes a MASK PROGRAMMABLE ROM that holds the CUSTOM

CHARACTER FONT, a 1Kbytes RAM that stores

the code strings of the different lines of text to be

displayed, and a set of registers to program character sizes and colors. A built-in digital PLL, oper-

ating at very high frequency, gives an accurrate

display without visible jitter for a wide line frequency range from 15 to 140 kHz.

- Cut-off Monitoring Circuitry includes: 5 x 8 bits

PWM DACs, 3 x 8 bits ADCs and a programmable

ADC sampling trigger. It gives the possibility to

measure the three beam currents, during the horizontal flyback, at a given line in the frame, provided that the three ADC inputs are connected to a

beam current sensing circuitry. The values are

stored in three BEAM CURRENT REGISTERS,

and available for MCU read.

- Video Timing Analyzer. Using the HorizontalSync,

Vertical Sync, Horizontal Flyback, and ”Video

Active” inputs, a set of counters give the different

timing measurements necessary to analyze the

current Video timing characteristics in order to

make the automaticset-up of screen size and centering. The measurements are initialized on the

same programmable trigger line than in the above

cut-offmonitoring circuitry.

.

SO28

(Plastic Micropackage)

ORDER CODE:STV9432TAP

Version 4.0

February 2000 1/25

This ispreliminary information on a new product indevelopment orundergoing evaluation. Details are subject tochange without notice.

1

Page 2

STV9432TAP

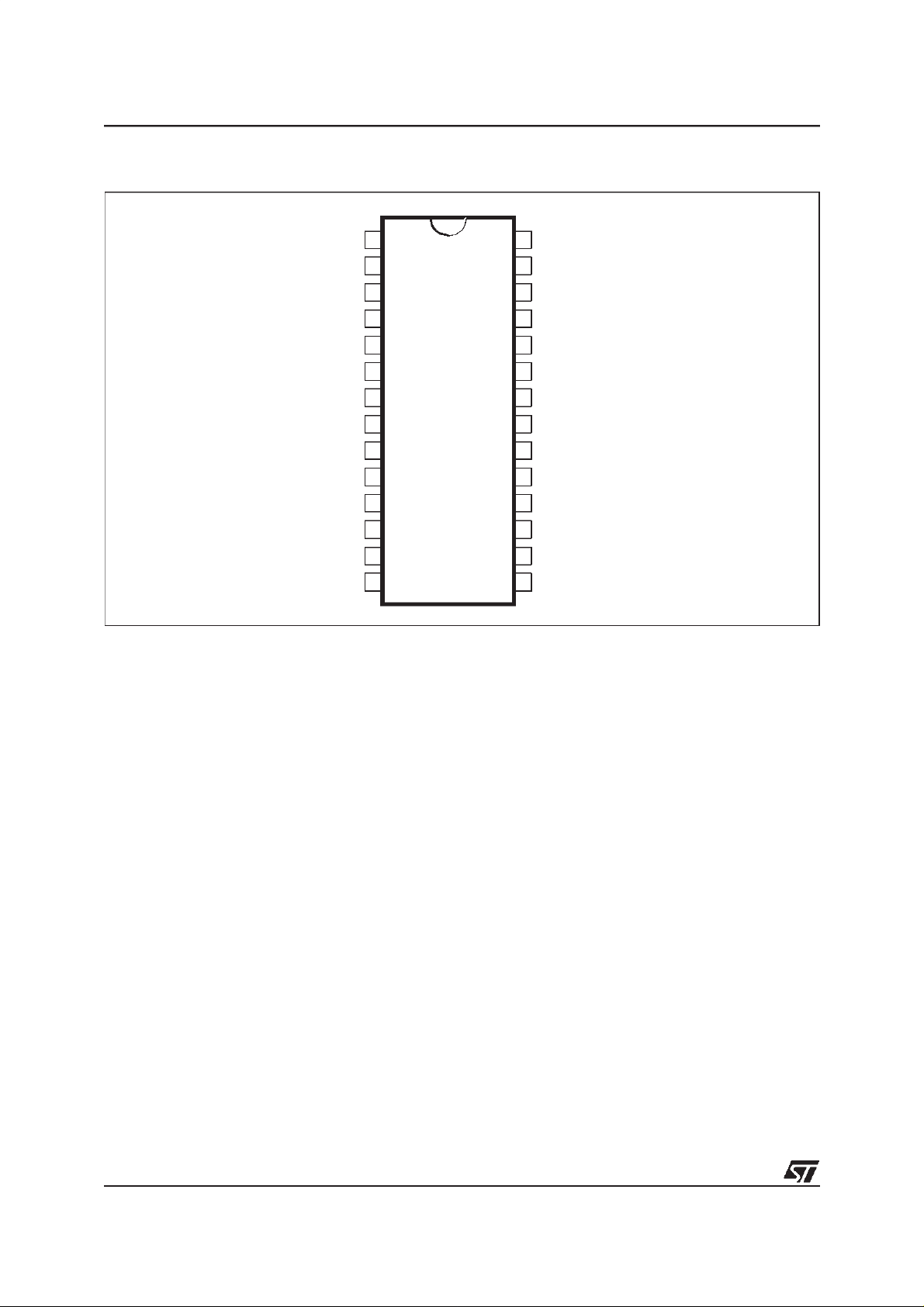

1 - PIN CONNECTIONS

FILTER

AGND

SDA

SCL

HFLY

DV

DVSS/OV

XTO

PWM1

PWM2

HS

VS

AV

XTI

1

2

3

4

5

6

7

8

9

DD

10

SS

11

12

13

14 PWM3

28

27

26

25

24

23

22

21

20

19

18

17

16

15

TEST

ADCREF

RCI

GCI

BCI

AV

DD

OV

DD

FBLK

BOUT

GOUT

ROUT

PWM5

PWM4

2/25

2

Page 3

2 - PIN DESCRIPTION

Pin Number Symbol Type Description

1 FILTER I/O PLL Filter

2 AGND Power Analog Ground

3SDAI/O

4SCLI

5 HS I Horizontal Sync Input

6 VS I Vertical Sync Input

7 HFLY I Horizontal Flyback Input

8 AV I Active Video Input

9DV

10 DV

SS

DD

/OV

SS

Power Digital +5V Power Supply

Power Digital and RGB Output Ground

11 XTI I Crystal Oscillator Input

12 XTO O Crystal Oscillator Output

13 PWM1 O PWM DAC Output 1

14 PWM2 O PWM DAC Output 2

15 PWM3 O PWM DAC Output 3

16 PWM4 O PWM DAC Output 4

17 PWM5 O PWM DAC Output 5

18 ROUT O Red Output

19 GOUT O Green Output

20 BOUT O Blue Output

21 FBLK O Fast Blanking Output

22 OV

23 AV

DD

DD

Power +5V Supply for the RGB Outputs

Power Analog +5V Power Supply

24 BCI I Blue Beam Current Input

25 GCI I Green Beam Current Input

26 RCI I Red Beam Current Input

27 ADCREF I/O ADC Reference Voltage Pin

28 TEST I/O Pin to be connected to ground

2

C Bus Serial Data

I

2

C Bus Serial Clock

I

STV9432TAP

3/25

Page 4

STV9432TAP

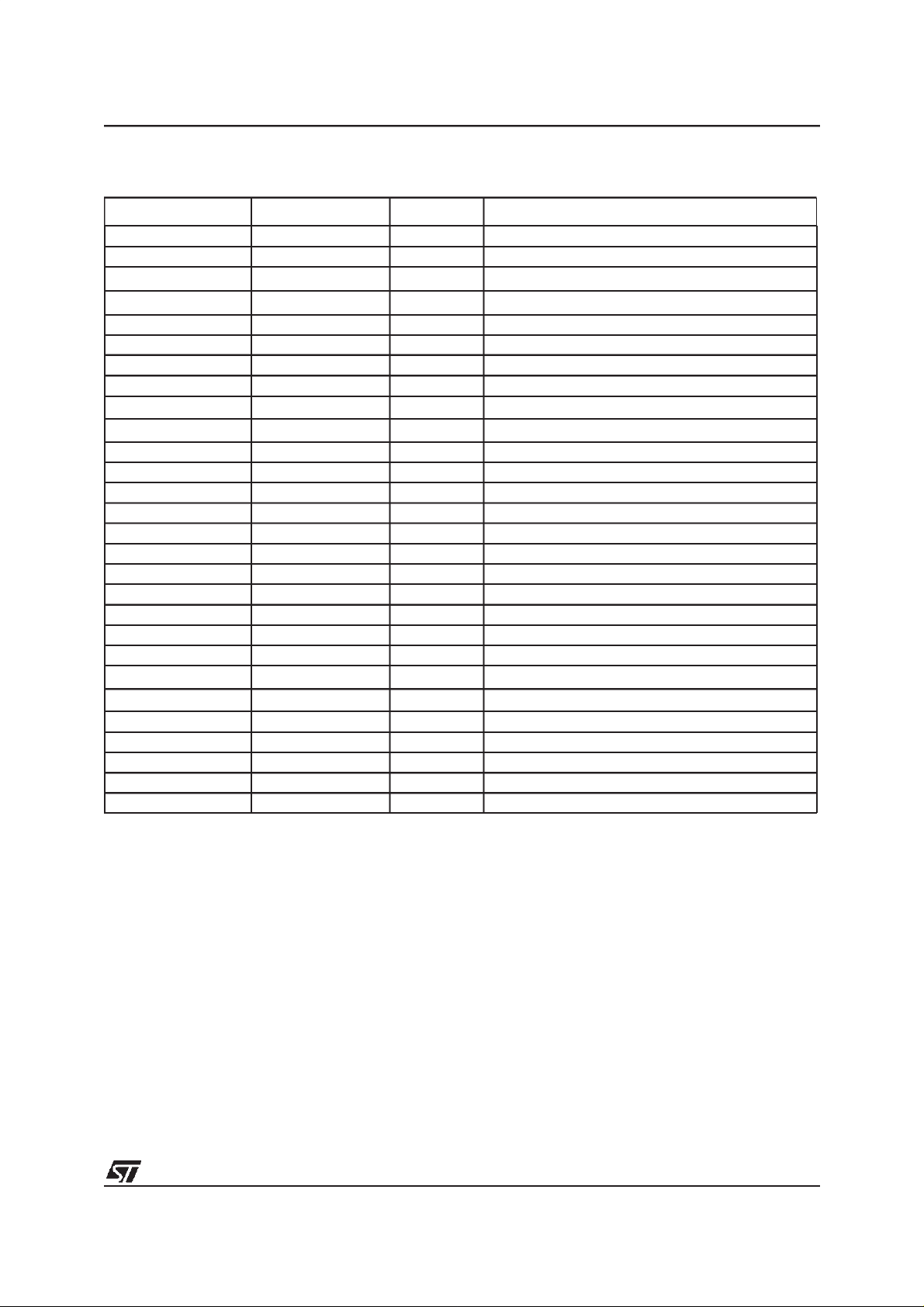

3 - BLOCK DIAGRAM

11

XTI

XTO

12

OSCILLATOR

8BITS

PWMs

13

14

15

16

17

PWM1

PWM2

PWM3

PWM4

PWM5

FILTER

HFLY

VS

HS

AV

RCI

GCI

BCI

ADCREF

AV

DD

DV

DD

5

26

25

24

27

23

1

7

6

8

PLL

TIMINGS

ANALYZER

BEAM

CURRENT

DISPLAY

CONTROLLER

1k BYTES RAM

CHARACTER

FONT ROM

22

18

19

20

21

10

2

OV

DD

ROUT

GOUT

BOUT

FBLK

DV

SS

AGND

/OV

SS

MEASURE-

MENT

2

C BUS

I

INTERFACE

3.3V

VOLTAGE REGULATOR

9

POWER-ON RESET

28

SDA

3

SCL

4

TEST

STV9432TAP

4 - ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

4/25

AV

DD

,DVDD,OV

V

IN

T

oper

T

stg

Supply Voltage -0.3, +6.0 V

DD

Input Voltage VSS-0.3, VDD+0.3 V

Operating Temperature 0, +70

Storage Temperature -40, +125

o

C

o

C

Page 5

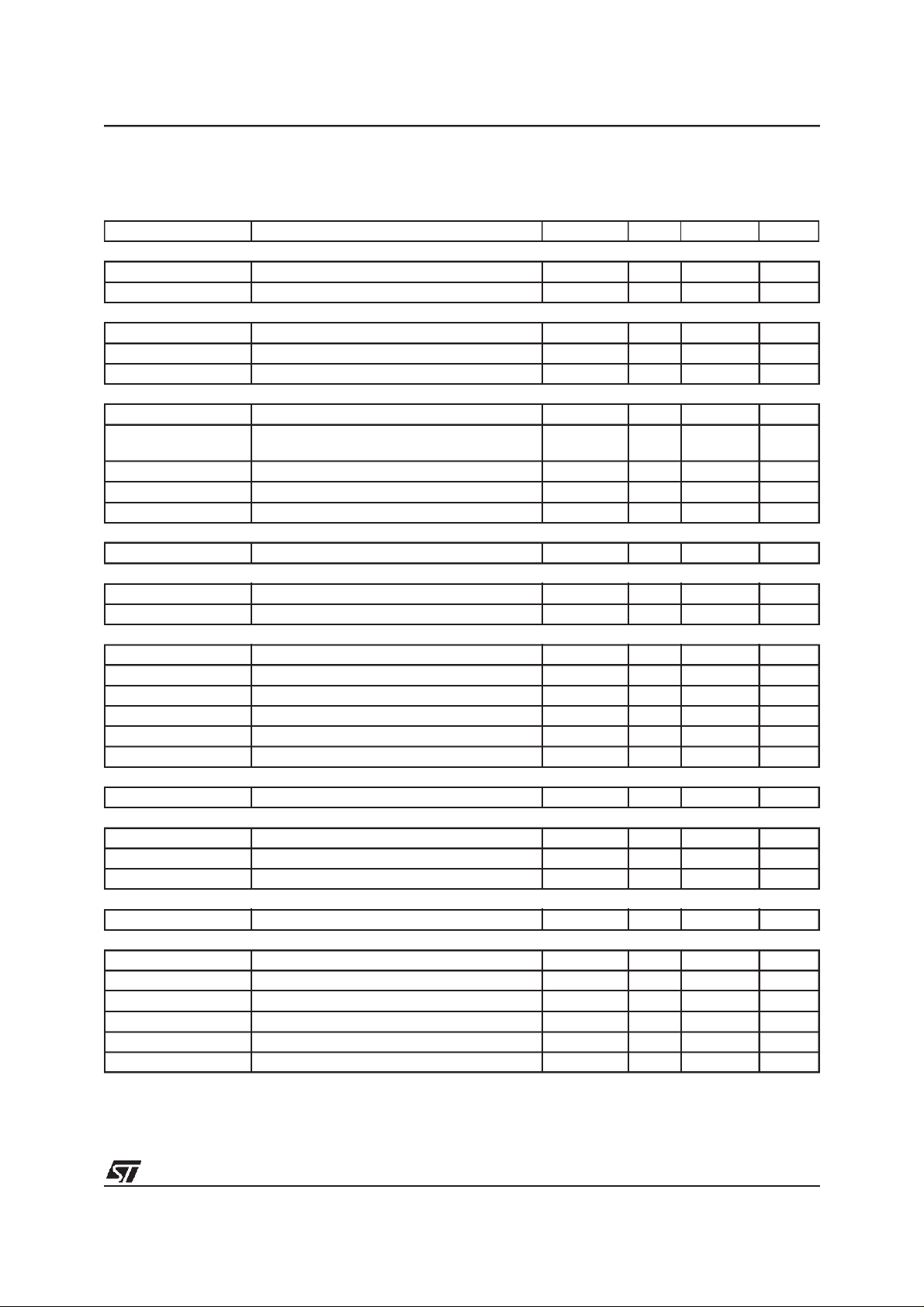

5 - ELECTRICAL CHARACTERISTICS

(VDD= 5V, VSS= 0V, GND =0V, TA=0to70o, unless otherwise specified)

Symbol Parameter Min. Typ. Max. Unit

SUPPLY

AVDD,DVDD,OV

+DIDD+OI

AI

DD

INPUTS (SCL, SDA)

V

IL

V

IH

I

IL

INPUTS (HS, VS, AV, HFLY)

V

IL

V

IH

V

HYST

I

PU

H

SIN

OUTPUTS (SDA open drain)

V

OL

OUTPUTS (R, G, B, FBLK)

V

OL

V

OH

OSCILLATOR (XTI, XTO)

I

IL

I

IH

V

IL

V

IH

V

OL

V

OH

ADCREF

V

REF

8 BITS PWM DACs 1,2,3,4,5

V

OL

V

OH

t

PWM

POWER-ON RESET

DV

DDTH

8 BITS ADC INPUTS (RCI, GCI, BCI)

V

IN

Z

IN

V

OFF

I

LEAK

ILE

DLE

Supply Voltage

DD

Analog and DigitalSupply Current

DD

Input Low Voltage

Input High Voltage

Input Leakage Current

Input Low Voltage

Input High Voltage HS, VS, AV

Schmidt Trigger Hysteresis

Pull-up Source Current (VIN= 0V)

Horinzontal Synchro Input Range

Output Low Voltage (IOL= 3mA)

Output Low Voltage (IOL= 3mA)

Output High Voltage (IOH= 3mA)

XTI Input Source Current (VIN= 0V)

XTI Input Sink Current (VIN=VDD)

XTI Input Low Voltage

XTI Input High Voltage

XTI Output Low Voltage (IOL= 3mA)

XTI Output High Voltage (IOH= 3mA)

Output Voltage Reference

Output Low Voltage (IOL= 1.6mA)

Output High Voltage (IOH= -0.8mA)

PWM Period

Supply Threshold Level

Input Voltage

Input Impedance

Input Offset Voltage

Input Leakage Current

Integral Linearity Error (Note 2)

Differential Linearity Error (Note 2)

HFLY

4.75 5 5.25 V

- - 150 mA

2.4 V

-1 +1 µA

2.4

3.6

15 - 140 kHz

00.4V

00.4V

0.8V

DD

315µA

315µA

0.7V

DD

00.4V

0.8V

DD

00.4V

VCC- 0.5 V

0V

-2 +2 LSB

-0.5 +0.5 LSB

STV9432TAP

0.8 V

0.8 V

V

0.4 V

100 µA

V

DD

1.4 V

V

DD

3.3 V

256 t

3.6 V

ADCREF

100 k

3LSB

050µA

V

V

V

OSC

V

Ω

5/25

Page 6

STV9432TAP

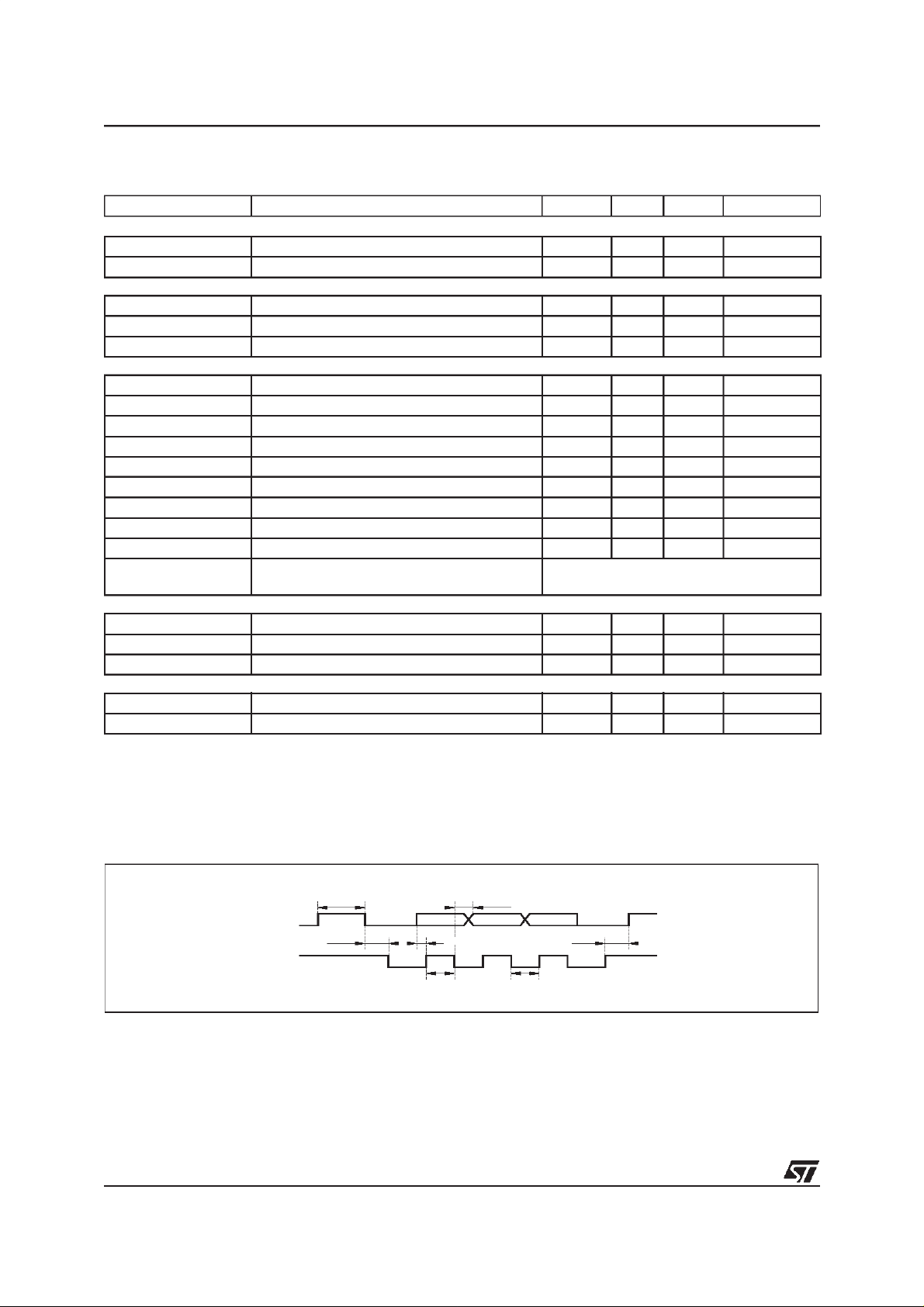

6 - TIMINGS

Symbol Parameter Min. Typ. Max. Unit

OSCILLATOR

f

OSC

f

PXL

R, G, B, FBLK (C

2

I

C INTERFACE: SDAAND SCL (see Figure 1)

t

ANALYZER (HS, HFLY,AV)

t

LOAD

t

R

t

F

t

SKEW

f

SCL

t

BUF

t

HDS

t

SUP

t

LOW

t

HIGH

t

HDAT

SUDAT

t

F

t

R

t

HLOW

HHIGH

Hs

ANALYZER (VS)

t

VLOW

t

VHIGH

Clock Frequency

Maximum PixelFrequency

= 30pF)

Rise Time (see Note 1)

Fall Time (see Note 1)

Skew between R, G, B, FBLK

SCL Clock Frequency

Time the bus must be free between 2 access

Hold Time for Start Condition

Set up Time for Stop Condition

The Low Period of Clock

The High Period of Clock

Hold Time Data

Set up Time Data

Fall Time of SDA

Rise Time of both SCL and SDA

Low Pulse Width(see Note 3)

High Pulse Width

Hs Frequency

Low Pulse Width

High Pulse Width

0 400 kHz

500 ns

500 ns

500 ns

400 ns

400 ns

0ns

500 ns

Depend on the pull-up resistor and the

2 4091 t

2 4091 t

2 4091 Lines

2 4091 Lines

Notes:

- These parameters are not tested on each unit. They are measured during our internal qualification procedure which

includes characterization on batches coming from corners of our processes and also temperature characterization.

- The ADC measurements are dependant on the noise. The test is done by correlation in order to screen out marginal

devices.

-t

HTIM

=3t

OSC

: 40.

Figure 1.

8 MHz

100 MHz

5ns

5ns

5ns

20 ns

load capacitance

HTIM

HTIM

Hfly

6/25

STOP START DATA

t

BUF

SDA

t

HDS

SCL

t

HIGH

t

SUDAT

t

HDAT

t

LOW

t

SUP

STOP

Page 7

7 - SERIAL INTERFACE

The 2-wires serial interface is an I2C interface. To be

connected to the I

address; the slave addressof the STV9432TAP is BA

(in hexadecimal).

A6 A5 A4 A3 A2 A1 A0 RW

1011101

7.1 - Data Transfer in Write Mode

The host MCU can write data into the STV9432TAP

registers or RAM.

To write data into the STV9432TAP, after a start, the

MCU must send (Figure2):

- First, the I

the R/W bit,

- The two bytes of the internal address where the

MCU wants to write data,

Figure 2. I2C Write Operation

SCL

SDA

2

C bus, a device must own its slave

2

C address slave byte with a lowlevel for

R/W

A7 A6 A5 A4 A3 A2 A1 A0 - - A13 A12 A11 A10 A9 A8

I2C Slave Address

ACK LSB Address ACK MSB Address ACKStart

STV9432TAP

- The successivebytes of data.

All bytes are sent MSB bit first and the write data

transfer is closed by a stop.

7.2 - Data Transfer in ReadMode

The host MCU can read data from the STV9432TAP

register, RAM or ROM.

To read data from the STV9432TAP (Figure 3), the

MCU must send 2 different I

one is made of I

2

C slave address byte with R/W bit at

low level and the 2 internal address bytes.

The second one is made of I

with R/W bit at high level and all the successive data

bytes read at successive addresses starting from the

initial address given by the first sequence.

2

C sequences. The first

2

C slave address byte

SCL

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

SDA

Figure 3. I2C Read Operation

SCL

SDA

2

I

C SlaveAddress

SCL

SDA R/W

I2C SlaveAddress

ACK ACKDataByte 1 DataByte2 ACK DataByte n Stop

R/W

A7 A6 A5 A4 A3 A2 A1 A0

ACK LSB Address ACK MSB Address ACKStart

D7 D6 D5 D4 D3 D2 D1 D0

*

ACK ACK DataByte n ACKStart

Data Byte1

- - A13 A12

D7 D6 D5 D4 D3 D2 D1 D0

A10 A10 A9 A8

Stop

Stop

7/25

Page 8

STV9432TAP

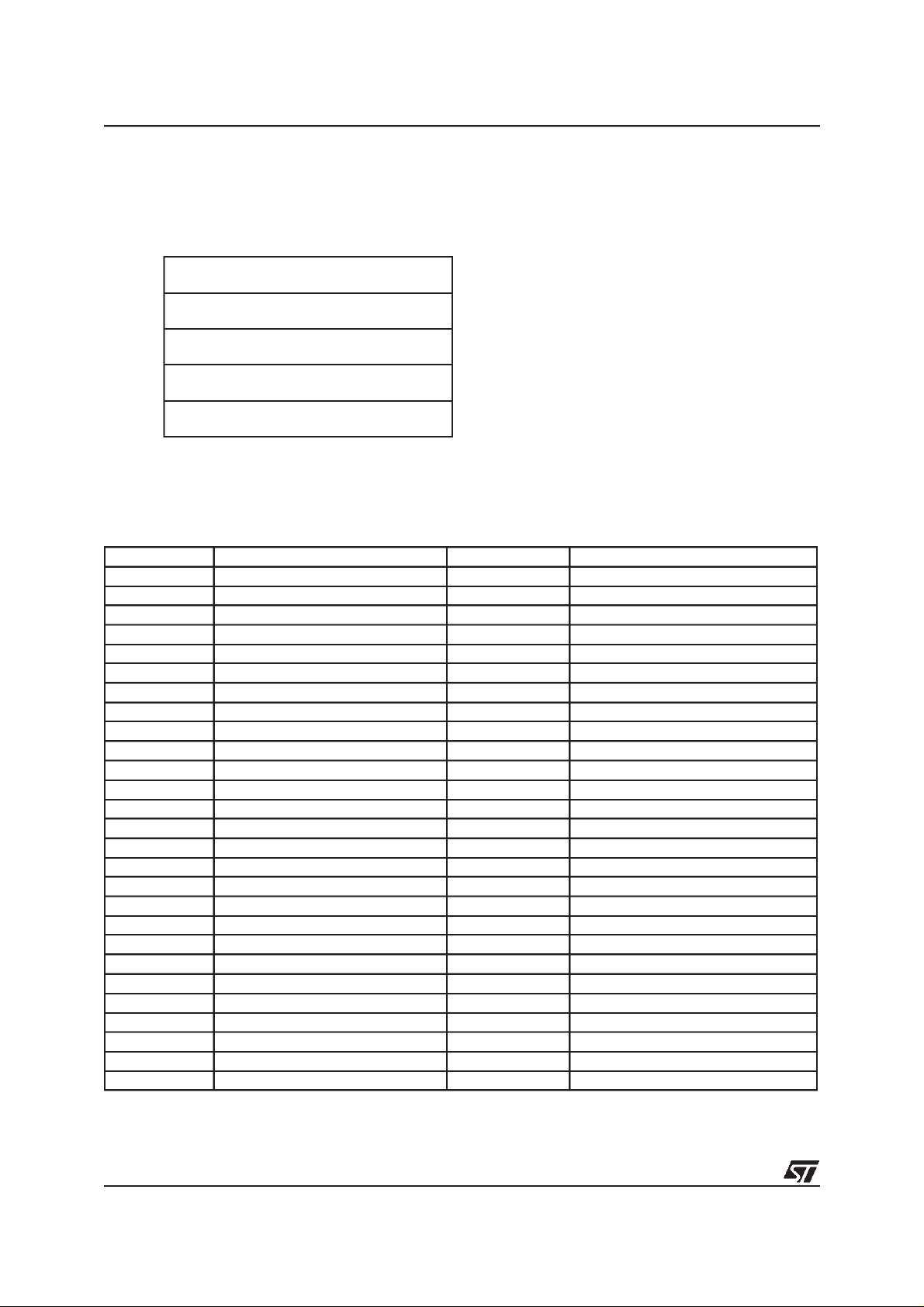

7.3 - ADDRESSING SPACE

7.3.1 - General Mapping

STV9432TAP registers, RAM and ROM are mapped in a 32Kbytes addressing space.

The mapping is the following:

0000

03FF

0400

07FF

0800

3FFF

4000

403F

4040

7FFF

1024 bytes RAM

Empty Space

Character Generator ROM

Internal Registers

Empty Space

Descriptors and character codes

Important Notice:

All 16 bits datas are mapped LSB byte at lower address and MSB byte at higher address.

- Example: H1 12 bits register: @4000: 8 LSB bits - @4001: 4 MSB bits.

- Descriptors must also be written to RAM LSB byte first.

7.3.2 - I2C Registers Mapping

4000 H1 LSB 4024 Color 4

4001 H1 MSB 4025 Color 5

4002 H2 LSB 4026 Color 6

4003 H2 MSB 4027 Color 7

4004 H3 LSB 4028 Color 8

4005 H3 MSB 4029 Color 9

4006 H4 LSB 402A Color 10

4007 H4 MSB 402B Color 11

4008 H5 LSB 402C Color 12

4009 H5 MSB 402D Color 13

400A H6 LSB 402E Color 14

400B H6 MSB 402F Color 15

400C V1 LSB 4030 Line Duration

400D V1 MSB 4031 Top Margin

400E V2 LSB 4032 Horizontal Delay

400F V2 MSB 4033 Character Height

4010 V3 LSB 4034 Display Control

4011 V3 MSB 4035 Locking Time Constant

4012 RCI 4036 Capture Time Constant

4013 GCI 4037 Initial Pixel Period

4014 BCI 4038 PWM1

4015 SBN 4039 PWM2

4016 TIMG 403A PWM3

4017-401F Reserved 403B PWM4

4020 Color 0 403C PWM5

4021 Color 1 403D-403E Reserved

4022 Color 2 403F RST

4023 Color 3 4040-7FFF Reserved

8/25

Page 9

STV9432TAP

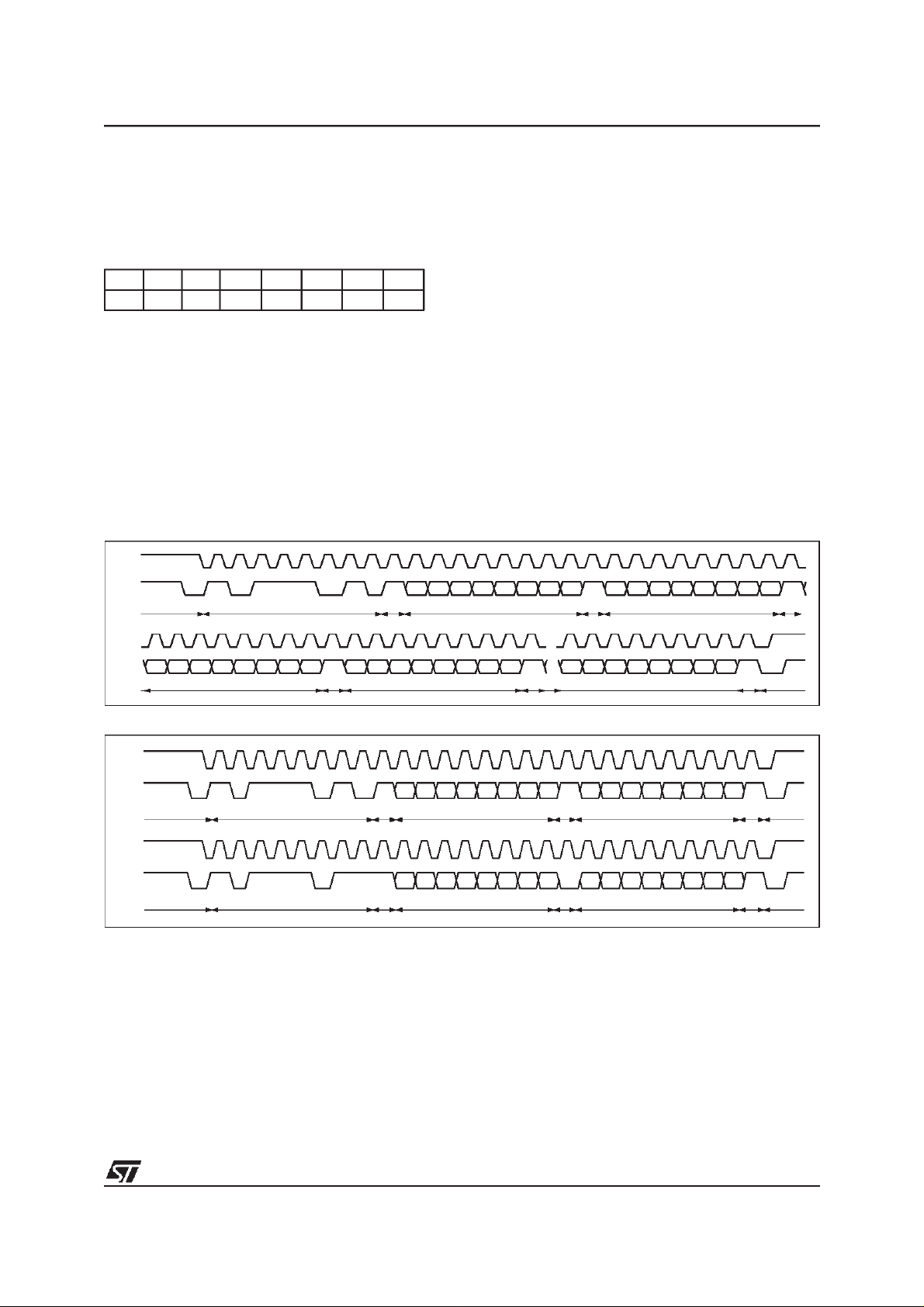

8 - TIMING ANALYZER

8.1 - VIDEO HORIZONTAL TIMINGS

All horizontal timing measurements use a 106.7MHz clock. This clock is made from theinternal oscillator:

= 40f

f

HTIM

They hold the value of the last measurement that was initiated by I

Figure 4.

: 3. These twelve bits read-onlyregisters read time measurements, given in t

OSC

2

C command (seeTIMG Register).

HTIM

units.

AV

HS

EE’

HFLY

AA’

D

F

B

C’C

D’

F’

H1 Register: H sync to Active video, min of C to A

4000 H1.7 H1.6 H1.5 H1.4 H1.3 H1.2 H1.1 H1.0

4001 - - - - H1.11 H1.10 H1.9 H1.8

H2 Register: Active video to H sync,min of B to C’

4002 H2.7 H2.6 H2.5 H2.4 H2.3 H2.2 H2.1 H2.0

4003 - - - - H2.11 H2.10 H2.9 H2.8

H3 Register: Line period, C to C’

4004 H3.7 H3.6 H3.5 H3.4 H3.3 H3.2 H3.1 H3.0

4005 - - - - H3.11 H3.10 H3.9 H3.8

H4 Register: H Fly to H sync, E to C

4006 H4.7 H4.6 H4.5 H4.4 H4.3 H4.2 H4.1 H4.0

4007 - - - - H4.11 H4.10 H4.9 H4.8

H5 Register: H sync to H Fly, C to E’

4008 H5.7 H5.6 H5.5 H5.4 H5.3 H5.2 H5.1 H5.0

4009 - - - - H5.11 H5.10 H5.9 H5.8

H6 Register: H fly pulse, E to F

400A H6.7 H6.6 H6.5 H6.4 H6.3 H6.2 H6.1 H6.0

400B - - - - H6.11 H6.10 H6.9 H6.8

8.2 - VIDEO VERTICAL TIMINGS

These twelve bits read-only registers read time measurements, given in number of scan lines. They hold the

2

value of the last measurement that was initiated by I

C command (seeTIMG Register).

Figure 5.

AV

VS

AA’

B

K’K

L’L

9/25

3

Page 10

STV9432TAP

V1 Register: V sync to Active video, min. of K to A

400C V1.7 V1.6 V1.5 V1.4 V1.3 V1.2 V1.1 V1.0

400D - - - - V1.11 V1.10 V1.9 V1.8

V2 Register: Active video to V sync, min. of B to K’

400E V2.7 V2.6 V2.5 V2.4 V2.3 V2.2 V2.1 V2.0

400F - - - - V2.11 V2.10 V2.9 V2.8

V3 Register: Number of lines per frame,K to K’ ’

4010 V3.7 V3.6 V3.5 V3.4 V3.3 V3.2 V3.1 V3.0

4011 - - - - V3.11 V3.10 V3.9 V3.8

8.3 - TIMING ANALYSIS TRIGGER

The Timing Analysis is performedaccording to the setting of SBN and TIMG registers:

8.3.1 - SBN Register

This 8 bits register holds the ”sampling bloc” number.

The sampling bloc is a set of 4 consecutive scan lines, the first of which is used for sampling the video timings or

Beam currents.

The reset value of this register is 0.

4015 SBN7 SBN6 SBN5 SBN4 SBN3 SBN2 SBN1 SBN0

8.3.2 - TIMG Register

4016 STM NFR1 NFR0 ADCDLY3 ADCDLY2 ADCDLY1 ADCDLY0 SELECT

This 8 bits register holds the following parameters:

STM : Start Measurement Bit. This bit has to be forced to 1 by I2C to start themeasure-

ment sequence, depending on the measurement selection bit. When measure-

ment is completed the IC will reset this bit to 0.

NFR [1:0] : NFR number ofmeasurement frames, 1 to 4 frames

ADCDLY[3:0] : Cut-off Beam current ADCsampling delay time: 0 to15 x t

OSC

,byt

OSC

steps

SELECT : Selection of Beam current measurement (0) or Timingmeasurement (1)

To initiatea TimingAnalysis cycle:

- program the Sampling Bloc Number in the SBN Register,

- program the TIMG Register, with: ”SELECT” bit =1, ”NFR” bits specify the number of measurement frames

(H1, H2, V1, V2), ”STM” bit = 1 (Start Measurement).

As soon as the measurement cycle is finished, the ”STM” bit is automatically reset by the device.

After a Timing Analysis cycle, reading a zero in STM bit of TIMG register means that the measurement is com-

pleted and the mcu may read the results in Hi and Vi registers.

10/25

Page 11

STV9432TAP

Figure 6. Video Timing Measurement sequence - “Select bit = 1” (TIMG register, bit 0)

I2C SET STM BIT (TIMG register)

WAIT FOR ACKNOWLEDGEBIT

WAIT FORRISING EDGE OF VS

MEASURESH1 AT EVERY LINE

DURING NFR+1 FRAMES.

AFTER NFR+1 FRAMES,

H1 HOLDS THE MIN.VALUE

MEASURESH2 AT EVERY LINE

DURING NFR+1 FRAMES.

AFTER NFR+1 FRAMES,

H2 HOLDS THE MIN.VALUE

AFTER NFR+1 FRAMES, RESET STM BIT

MEASURES V3

MEASURES V1 DURING NFR+1

AND KEEPS THE MIN.VALUE

MEASURES V2 DURING NFR+1

AND KEEPS THE MIN.VALUE

WAIT FOR 4*SBN RISING EDGES OF HS

ACQUISITION OF H3, H4,H5, H6

11/25

Page 12

9 - BEAM CURRENTS MEASUREMENT

9.1 - BEAM CURRENT MEASUREMENT REGISTERS

STV9432TAP

The Beam Current Measurement circuitry uses threeA to D converters, sampled at f

OSC

frequency.

These three 8 bits registers read the valuesof the last Beam currents measurement, initiated by I2C command (see TIMG register).

RCI Register: Red BeamCurrent Input

4012 RCI7 RCI6 RCI5 RCII4 RCI3 RCI2 RCI1 RCI0

GCI Register: Green Beam Current Input

4013 GCI7 GCI6 GCI5 GCI4 GCI3 GCI2 GCI1 GCI0

BCI Register: Blue Beam Current Input

4014 BCI7 BCI6 BCI5 BCI4 BCI3 BCI2 BCI1 BCI0

9.2 - BEAM CURRENT MEASUREMENT TRIGGER

The Beam Currents Measurement is performed according to the setting of SBNand TIMG registers :

9.2.1 - SBN Register

This 8 bits register holds the ”sampling bloc” number. The sampling bloc is a set of 4 consecutive scan

lines, the first of which is used for sampling the video timings or Beam currents. The reset value of this

register is 0.

4015 SBN7 SBN6 SBN5 SBN4 SBN3 SBN2 SBN1 SBN0

9.2.2 - TIMG Register

4016 STM NFR1 NFR0 ADCDLY3 ADCDLY2 ADCDLY1 0 SELECT

This 8 bits register holds the following parameters: When measurement is completedthe IC will reset

STM : Start Measurement Bit. This bit has

to be forced to 1 by I2C to start the

measurement sequence, depending

on the measurement selection bit.

When measurement is completed

the IC will reset this bit to 0.

NFR

[1:0]

ADCDLY

[3:0]

: NFR number of measurement

frames, 1 to 4 frames

: Cut-off Beam current ADC sampling

delay time: 0 to 15 x t

OSC

,byt

OSC

steps

SELECT : Selection of Beam current measure-

ment (0) orTimingmeasurement (1)

this bit to 0. The reset value ofthis register is 0.

To initiate a BeamCurrents Measurement cycle:

- program the Sampling BlocNumber in the SBN

Register,

- program the TIMG Register, with: ”SELECT”

bit = 0, ”ADCDLY” bits specify the sampling

time during HFly, ”STM” bit = 1 (Start Measurement).

As soon asthe measurement cycle is finished, the

”STM” bit is automatically reset by the device.

After a Beam Currents Measurement cycle, reading a zero in STM bit of TIMG register means that

the measurementis completed and the MCU may

read the results in RCI, GCI, and BCI registers.

15/29

4

Page 13

STV9432TAP

Figure 7. Beam Currents Measurement Sequence - “Select bit = 0” (TIMG register, bit 0)

I2C SET STM BIT (TIMG register)

WAIT FOR ACKNOWLEDGE BIT

WAITFOR RISING EDGEOF VS

WAITFOR 4*SBN RISINGEDGES OF HS

WAIT FOR RISING EDGE OF HFLY

WAITFOR ADC DLY

ACQUISITIONOF RBC, GBC, BBC

RESETSTM BIT

16/29

Page 14

STV9432TAP

10 - DIGITAL TO ANALOG PWM OUTPUTS

The five to A outputs PWM1 toc5 of the STV9432TAP are pulse width modulatortype converter outputs.

The frequency of the output signal is f

low pass filter,the voltage value of the output is: Value [7:0] x VDD: 256.

Figure 8.

PWM1 Signal

V1[7:0]

0

1

128

255

10.1 - PWM REGISTERS

Pulse Width Modulator 1

4038 V17 V16 V15 V14 V13 V12 V11 V10

: 256 and the duty cycle is: Value [7:0]: 256. After an external

OSC

256 x t

OSC

t

OSC

V1[7:0] : Digital value of the 1stPWM D to A converter (Pin 13)

Pulse Width Modulator 2

4039 V27 V26 V25 V24 V23 V22 V21 V20

V2[7:0] : Digital value of the 2ndPWM D to A converter (Pin 14)

Pulse Width Modulator 3

403A V37 V36 V35 V34 V33 V32 V31 V30

V3[7:0] : Digital value of the 3rdPWM D to A converter (Pin 15)

Pulse Width Modulator 4

403B V47 V46 V45 V44 V43 V42 V41 V40

V4[7:0] : Digital value of the 4thPWM D to A converter(Pin 16)

Pulse Width Modulator 5

403C V57 V56 V55 V54 V53 V52 V51 V50

V5[7:0] : Digital value of the 5thPWM D to A converter(Pin 17)

Note: Power-on reset default value of PWM register is OOH.

14/25

5

Page 15

STV9432TAP

11 - SOFTWARE RESET REGISTER

403F - - - - - - - RST

To perform a software I2C reset of the device, set the RST bit to ONE.

This bit willbe automatically reset by the device.

Software Reset will put all Write registers at their default power-on value, and reset all internal logic

blocks except the I2C bus interface itself. It will not change the RAM contents.

12 - ON-SCREEN DISPLAY

The STV9432TAP on-screen display is able to display any line of characters (character strip) anywhere in the screen.

Character strings are programmed bythe MCU in

RAM via I2C bus. Character shapes are coded in

the internal ROM font. Character strips may be

12.1 - RAM PROGRAMMING

adjacent or separated by verticalspaces (Spacing

strips)

Consequently, one display page is made of a list

of Character strips and Spacing strips.

A TopMargin and a Left Margin are programmable

in dedicated registers.

12.1.1 - Two kinds of Data

Strip Descriptorsand Character Codes

An OSD screen is made of a number of Character

and Spacing strips.

There are two groups of Data that make one OSD

screen:

- a Strip Descriptors list,

- Textstrings - one per Character strip.

Each Strip is associated with a 2 bytes Strip

Descriptor.

There are two kinds of Strip Descriptors:

- Character Strip Descriptors: they contain the

Text string Ram address of the Character Strip,

- Spacing Strip Descriptors: they specify the vertical space height.

In the example shown in Figure 9, the OSD

screen, is made of 9 strips.

In RAM, there is:

- one list of 9 Strip descriptors

(size = 9 x 2 bytes = 18 bytes),

- 6 Text strings, each of them is made of the

character codes of the line of text.

Text strings can be programmed anywhere in

RAM. The Descriptor list can be located at 16 different addresses in RAM, this address is defined

in the Display Control Register.

It is consequently possible to store up to 16 different pages in RAM.

The current Displayed page is specified in the Display Control Register. It refers to a given Page

Descriptor list.

Figure 9. Display Page: list of Character and Spacing strips

TOP MARGIN

Text line number one

Text line number two

Text line number three

Strip 1 : CharacterStrip

Strip 2 : CharacterStrip

Strip 3 : SpacingStrip

Strip 4 : CharacterStrip

Strip 5 : SpacingStrip

Text line number four

LEFT MARGIN

Text line number five

Text line number six

Strip 6 : CharacterStrip

Strip 7 : CharacterStrip

Strip 8 : CharacterStrip

Strip 9 : SpacingStrip (Bottom Margin)

15/25

Page 16

STV9432TAP

12.1.2 - Descriptors

Spacing

MSB 0

LSB SL7 SL6 SL5 SL4 SL3 SL2 SL1 SL0

L/ : LINE or CHARACTER spacing:

C

L/

C

= 0, spacing descriptor defined as character height (SL[7:0] = 1 to 255 character).

= 1, spacing descriptor defined as scanline height (SL[7:0] = 1 to 255 scan lines).

------

SL[7:0] : Number of selected height (character or scan lines according L/ ).

C

Character

MSB 1 DE CLU3 CLU2 CLU1 CLU0 C9 C8

LSB C7 C6 C5 C4 C3 C2 C1 C0

DE : Display enable:

= 0, R = G = B =0 and FBLK = FBK bit of display control register on the whole strip,

= 1, display of the characters.

CLU[3:0] : Active color selection at the begining of the strip.

C[9:1] : Address of the first character code of the strip.

C0 : Address 0 must be 0.

12.1.3 - Code Format

There are basically3 kindsof code:

- the control codes from 0 to 15 (00H to 0FH),

- the ROM monochrome character codes from16 to 255 (10H to FFH),

- the two bytes multicolor character codes from 08F0 to 08FF (Hex).

For code definitions see Table 1.

Table 1 Character and Command Codes

0 123456789ABCDEF

0 col 0

1 col 1

2 col 2

3 col 3

4 col 4

5 col 5

6 col 6

7 col 7

8 multicol

9nop

A vflip

B hflip

C dflip

D call

E rtn

F eof

Single byte codes 00 to 0f are command codes. Single byte codes 10 to ff are monochrome character codes. Double

byte codes 08F0 to 08FF are multicolor character codes.

240 Monochrome Characters

16/25

Page 17

Figure 10. Character Font for the STV9432TAP

STV9432TAP

17/25

Page 18

STV9432TAP

Control Codes

Control codes must be followed by a displayable

code, except for RTN & EOL. They must not be

used twice consecutively without a displayable

code between them.

The control code CALL is preceded by an address

byte. Thecontrol codes are not displayed except if

mentioned.

Codes 0 to 7 (0h to 7h):

COL0 to COL7 codes select 1 byte among 8

within the CLUT in RAM. The block selection is

fixed byCLU3 bit of the active character descriptor

(see Table 1 and Table 2).

Code 8 (08h):

Multicolor character precode, must be followed by

a multicolor character number from F0h to FFh.

Code 9 (09h):

NOP: no operation is performed, can be used to

spare a location in RAM for an active control code.

Codes 10 to 12 (0Ah to 0Ch):

FLIPS:

HFLIP(0Bh)

Horizontal Flip code flips horizontaly

the following displayable code.

VFLIP(0Ah)

Vertical Flip code flips verticaly the

following displayable code.

DFLIP(0Ch)

Horizontal & Vertical Flip code flips

horizontaly and verticaly the following displayable

code.

Code 13 (0Dh):

CALL, this control code switch the display of the

next character to the code address given by the

next byte as following:

CALL CODE

@) MSB

(odd

ADDRESS BYTE

@)LSB

(even

00001101

A8 A7 A6 A5 A4 A3 A2 A1

A[9:1] : Address of the next code to be

used (A0 = 0 only even

addresses), in low half part of

RAM.

Notes:

CALL and RTNcode must be used simultaneously.

CALL and RTN codes are displayed as a SPACE

character.

CALL and RTN codes must be placed at odd addresses. They may be preceed by a NOP in order to

place them at the right position.

Code 14 (0Eh):

RTN: return to the CALL + 1 code location (see

Note).

Code 15 (0Fh):

EOL, end ofline terminates the display of the cur-

rent row.

ROM Character Codes

Codes 16 to 255 (10h to FFh):

ROM monochrome character codes. The characters shapes are 12x18 pixel matrix described in

Figure 11.

Codes 256 to 272 (F0h to FFh):

ROM multicolor character codes. They must be

preceded by the multicolor pre-code 08h. The

characters shapes are 12x18 pixel matrix

described in Figure 11.

12.1.4 - OSD Look-up Table

Color look-up table [CLUT] is read/write RAM

table. Mapping address is described above in the

section ROM Character Codes.

The CLUT is splitted in 2 blocks of 8 bytes. Each

byte contains foreground and background informations as described below:

TRA BR BG BB FL FR FG FB

TRA

FL

BR,BG, BB

FR,FG,FB

:

Transparent background

:

Flashing foreground

:

Background color

:

Foreground color

Each block may store a different set of colors. One

block of colors may be used for the normal items

of the menu while the second block, with brighter

colors, may be used for selected items of the

menu.

The block selection is done by programming bit

CLU3 of CLU[3:0] of the character descriptor (see

Table 2). It remains selected all the row long.

Bit CLU2, CLU1 and CLU0 of CLU[3:0] of the

character descriptor select the active color at the

beginning of the row.

The active color can be changed along the row,

using 8 control codes COL0 to COL7.

Each control code (COL0to COL7) activate a dedicated color byte in the CLUT as described in

Table 2.

18/25

Page 19

STV9432TAP

Table 2 CLUT Block Selection

CLU3 CLU[2:0] Code Name Command Code

(hex)

0 Col 0 00 @4020 07

1 Col 1 01 @4021 16

0 2 Col 2 02 @4022 25

3 Col 3 03 @4023 34

4 Col 4 04 @4024 43

5 Col 5 05 @4025 52

6 Col 6 06 @4026 61

7 Col 7 07 @4027 70

0 Col 0 00 @4028 70

1 Col 1 01 @4029 61

2 Col 2 02 @402A 52

1 3 Col 3 03 @402B 43

4 Col 4 04 @402C 34

5 Col 5 05 @402D 25

6 Col 6 06 @402E 16

7 Col 7 07 @402F 07

12.2 - OSD CONTROL REGISTERS

Line Duration (reset value: 20H)

4030 VSP HSP LD6 LD5 LD4 LD3 LD2 LD1

Ram @(hex) Reset Value (hex)

VSP : V-SYNC active edge selection

HSP : HFLY active edge selection

LD[6:1] : LINE DURATION

= 0, falling egde,

= 1, rising edge.

= 0, rising egde,

= 1, falling edge.

LD0 = 0

LD1 = 2 periods ofcharacter

One character period is 12 pixels long.

Top Margin (reset value: 30H)

4031 M9 M8 M7 M6 M5 M4 M3 M2

M[9:2] : TOP MARGIN height from the VSYNC reference edge.

M0 = 0, M1 = 0

M2 = 4 scan lines

Note: The top margin is displayed before the first strip of descriptor list. It can be black if FBK of DISPLAY CONTROL

register is set or transparent if FBKis clear.

Horizontal Delay (reset value: 20H)

4032 DD7 DD6 DD5 DD4 DD3 DD2 DD1 DD0

DD[7:0] :

HORIZONTALDISPLAYDELAY from the HSYNC reference edge to the 1

ter strips.

Unit = 6 pixel periods. Minimum value is 08H. Firstpixel position = [DD[7:0] - 6] x 6 + 54 with

DD[7:0] = 0,2,4,6 delay is 54 pixel and with DD[7:0] = 1,3,5 delay is 60 pixel

st

pixel position of the charac-

19/25

Page 20

STV9432TAP

Character Height (reset value: 24H)

4033 - - CH5 CH4 CH3 CH2 CH1 CH0

CH[5:0] : HEIGHT of the character strips in scan lines. For each scan line, the number of the slice which is displayed is

given by:

SLICE-NUMBER =

SCAN-LINE-NUMBER = Number ofthe current scan line of the strip.

round

(

SCAN-LINE-NUMBER x 18

CH[5:0]

)

Display Control (reset Value: 00H)

4034 OSD FBK FL1 FL0 P9 P8 P7 P6

OSD : ON/OFF (if 0, R, G, B and FBLK outputsare 0).

FBK : Fast blanking control:

= 1, forces FBLK pin at ”1” outside and inside the OSD area.

This leads to blank video RGB and to only display OSD RGB.

= 0, FBLK pin is driven according character code for normal display of OSD data.

FL[1:0] : Flashing mode :

- 00: No flashing. The character attribute is ignored,

- 01: Flashing at f

- 10: Flashing at 2 f

- 11: Flashing at 4 f

(50% duty cycle),

F

F

F

Note: fFis 128 time vertical frequency.

P[9:6] :

Address of the 1

st

descriptor of the current displayed pages.

P[13:10] and P[5:0] = 0; up to 16 different pages can be stored in the RAM.

Locking Condition TimeConstant (reset value: 01H)

4035 FR AS2 AS1 AS0 LUK BS2 BS1 BS0

FR : Free Running; if = 1 PLL is disabled and the pixelfrequency keeps its last value.

AS[2:0] : Phase constant during locking conditions.

BS[2:0] : Frequency constant during locking conditions.

LUK : Lock unlock status bit

0 = unlocked PLL

1 = Locked PLL

Capture Process Time Constant (reset value: 24H)

4036 LEN AF2 AF1 AF0 - BF2 BF1 BF0

LEN : Lock enable

0 = R,G,B,FBLK are always enabled,

1 = R,G,B,,FBLK are enabled only when PLL is locked.

AF[2:0] : Phase constant during the capture process.

BF[2:0] : Frequency constant during the capture process.

Initial Pixel Period (reset value: 06H)

4037 PP7 PP6 PP5 PP4 PP3 PP2 PP1 PP0

PP[7:0] : Value to initialize the pixel period of the PLL.

20/25

Page 21

STV9432TAP

12.3 - OSD TIMINGS

The number of pixel periods is given by the LINE

DURATION register and is equal to:

[LD[6:1] x 2 + 1 ] x 12.

(LD[6:1]: value of the LINE DURATIONregister).

This value allows to define the horizontal size of

the characters.

The horizontal left margin is given by the HORIZONTALDELAY register and is equal to:

(DD[7:0] -6) x 6 + 54

(DD[7:0]: value of the DISPLAYDELAY register).

This value allows to define the horizontal position

of the characters on the screen. Due to internal

logic, minimum horizontal delay is fixed at 4.5

characters (54 pixel) when DD is even and lower

or equal to 6, and it is fixed at 5 characters (60

pixel) when DD is odd and lower orequal to 7.

12.4 - PLL

The PLL function of the STV9432TAP provides

the internal pixel clock locked on the horizontal

synchro signal and used by the display processor

to generate the R, G, B and fast blanking signals.

It ismade of 2 PLLs. The first one analog (see Figure 11) provides a high frequency that is 40 times

the internal oscillator frequency, or 320MHz. This

high frequency clock is used by the Display controller.

The 320MHz frequency is then divided by three.

The resulting 106.7MHz clock is used by the

Video timings analysis block.

The second PLL, full digital (see Figure 12), provides a pixel frequency locked on the horizontal

synchro signal. The ratio between the frequencies

of these 2 signals is:

M = 12 x (LD[6:1] x 2 + 1) where LD[6:1] is the

value of the LINE DURATIONregister.

Figure 11. Analog PLL

N •f

OSC

VCO 40

FILTER

f

OSC

Figure 12. Digital PLL

M •f

H-SYNC

40 •f

OSC

%D %M

ALGO

f

H-SYNC

err(n)D(n)

12.4.1 - Programming of the PLL Registers

Initial Pixel Period (@4037)

This register allows to increase the speed of the

convergence of the PLL when the horizontal frequency changes (new graphic standard). The

relationship between PP[7:0], LD[6:1], f

f

is:

OSC

PP[7:0] = round

(

40 . f

OSC

6. (2.LD + 1).f

HSYNC

HSYNC

and

)

Locking Condition Time Constant (@ 4035)

This register provides the AS[2:0] and BS[2:0]

constants used by the algo part of the PLL (see

Figure 11). These two constants as well as the

phase error err(n) give the new value D(n) of the

high frequency signal division. AS[2:0] and

BS[2:0] fix the pixel clock frequency. These two

constants are used only in locking condition, if the

phase error is inferior to a fixed value during at

least 4 scan lines. If the phase error becomes

greater than this fixed value, the PLL is not in locking condition but in capture process. In this case,

the algo part of the PLL used the other constants,

AF[2:0] and BF[2:0], given by the next register.

Capture Process Time Constant (@ 4036)

The choice between these two time constants

(locking condition or capture process) allows to

decrease the capture process time by changing

the time response of the PLL.

12.4.2 - How to choose the time constant value

The time response of the PLL is given by its characteristic equation which is:

(x - 1)2+( ).(x - 1) + = 0

αβ+ β

Where:

α 3LD⋅= β

[6:1].2

A-11

and = 3.LD[6:1].2

B-19

(LD[6:1] = value of the LINE DURATION register,

A = valueof the 1st time constant, AFor AS and

B = valueof the 2dtime constant, BF or BS).

As you can see, the solution depends only on the

LINE DURATION and the TIME CONSTANTS

given by the I2C registers.

If ( )2- 4 and2 < 4, the PLL is sta-

αβ+ β0≥ αβ–

ble and its response is like that presented in Figure 14.

If ( )2- 4 , the response of the PLL is

αβ+ β0≤

like that presented in Figure 15. In this case the

PLL is stable if > 0.7 damping coefficient). Table

τ

3 gives some good values for A and B constants

for different values of the LINE DURATION.

21/25

Page 22

STV9432TAP

Figure 13. Time Response of the PLL/

Characteristic equation solutions (with real

solutions)

PLL Frequency

f

1

f

0

Input Frequency

f

1

f

0

t

t

Figure 14. Time Response of the PLL/

Characteristic equation solutions (with

complex solutions)

PLL Frequency

f

1

f

0

Input Frequency

f

1

f

0

t

t

Table 3 ValidTimeConstants Examples

B\A0 123 4 5 6

0 YYYY YYYY YYYY YYYN YNNN NNNN NNNN

1 YYYY YYYY YYYY YYYN YNNN NNNN NNNN

2 NYYY YYYY YYYY YYYN YNNN NNNN NNNN

3 NNNY YYYY YYYY YYYN YNNN NNNN NNNN

4 NNNN

NYYY

(1)

5 NNNN NNNY YYYY YYYN YNNN NNNN NNNN

6 NNNN NNNN NYYY YYYN YNNN NNNN NNNN

7 NNNN NNNN NNNY YYYN YNNN NNNN NNNN

YYYY YYYN YNNN NNNN NNNN

Note : Case of A[2:0] = 1 (001) and B[2:0] = 4 (100):

LD[6:1] 8 16 24 32

ValidTime Constants N Y Y Y

Table meaning: N = No possible capture - No stability, Y = PLL can lock.

22/25

Page 23

13 - APPLICATION DIAGRAM

Figure 15.

47µF

C16

STV9432TAP

µH

100

VDD +5VGND

Beam current inputs

Ω

1k

Ω

1k

Separate path for digitlal GND

L3

C15

100nF

100pF

Ω

1k

C14 C14

Fast blanking ouput

100pF

R2 R3 R4

C12

100pF

µF

100nF

22

Ω

2.2k

C11

R1

1nF

TEST28

ADCREF27

1 FILTER

2 AGND

C8

C10

RCI26

3SDA

GCI25

4SCL

µH

L2

100

C9

100nF

BCI24

FBLK21

AVdd23

OVdd22

7HFLY

5HS

6VS

ROUT18

GOUT19

BOUT20

PWM517

PWM315

PWM416

8AV

11XTi

12XTO

9 DVdd

10DVss/OVss

13PWM1

14PWM2

R8

10kΩ10kΩ

R8

10kΩ

R6

RGB outputs

µF4.7µF4.7µF4.7µF

4.7

PWM outputs

100nF

R5

22pF

100µH

L1

Xtal

8 Mhz

C5 C6

22pF

10kΩ

PWM outputs

I2C bus

Horizontal sync

Vertival sync

Fly back pulse

Active video

C2 C3 C4

C1

100pF 100pF 100pF

100pF

23/25

Page 24

STV9432TAP

PACKAGE MECHANICAL DATA

28 PINS - PLASTICMICROPACKAGE(SO)

Dimensions

A 2.65 0.104

a1 0.1 0.3 0.004 0.012

b 0.35 0.49 0.014 0.019

b1 0.23 0.32 0.009 0.013

C 0.5 0.020

c1 45

D 17.7 18.1 0.697 0.713

E 10 10.65 0.394 0.419

e 1.27 0.050

e3 16.51 0.65

F 7.4 7.6 0.291

L 0.4 1.27 0.016 0.299

S8°(Max.) 0.050

Min. Typ. Max. Min. Typ. Max.

Millimeters Inches

24/25

6

Page 25

STV9432TAP

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no

responsibility for the consequences of use of such information nor for any infringement of patents or other

rights ofthird parties which may result from its use. No license is granted by implication or otherwise under any

patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change

without notice. This publication supersedes and replaces all information previously supplied.

STMicroelectronics products are not authorized for use as critical components in life support devices or

systems without express written approval of STMicroelectronics.

The ST logo is a trademark of STMicroelectronics.

2000 STMicroelectronics - All Rights Reserved

Purchase of I

Rights to use these components in a I

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan -Malaysia - Malta - Morocco -

2

C Components ofSTMicroelectronics, conveys a license under the Philips I2C Patent.

Standard Specifications as defined by Philips.

STMicroelectronics GROUP OF COMPANIES

Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

2

C system, is granted provided that the system conforms to the I2C

http://www.st.com

25/25

7

Loading...

Loading...