Page 1

STV7801S

PLASMA DATA POWER SWITCH

PRELIMINARY DATA

FEATURES

■ High Voltage - Low Power Pulse Generator

■ 100V Absolute Maximu m Supply

■ High Load Drive Capability (25nF)

■ 5V Compatible Input Logic

■ Very Low Stand-by Current

■ Power Recovery High Current (±7A)

■ Totem Pole High Output Current (±5A)

■ Built-in Timing Control & Thermal Protection

■ BCD Technology

■ Packaging: Multiwatt 15, Power SO20

DESCRIPTION

STV7801 is a m onolithic integrated circuit implemented in STMicroelectronics BCD proprietary

technology designed as a switched power supply

generator for data drivers in a Plasma Display

Panel (P.D.P.) application.

The high load drive capabil ity of the STV7 801 reduces the number of devices necessary to drive a

complete PDP (4 to 6 devices for a 42” VGA 16/9

PDP monitor).

The STV7801 high current drive capability provides a high power recovery efficiency coefficient

superior to 85% on constant capacitive load.

To limit the numbe r of external components, the

device integrates level shifters driven with 5V

CMOS compatible levels.

To increase the reliability of the system, the device

integrates several protections such as output

over-voltage, over-temperature, power-ON protection.

.

MULTIWATT 15 (Plastic Package)

ORDER CODE: STV7801S

Customer samples will be available

by september 2000

POWERSO20 (Plast ic Package)

20 leads

ORDER CODE: STV7801SP

Revision 3.3

June 2000 1/18

This is preliminary information on a new product in development or undergoing evaluation. Details are subject to change without notice.

1

Page 2

STV7801S

1 - PIN CONNE CT ION

Multiwatt 15

PowerSO20

15

14

13

12

11

10

Vpp

Vpp

CBoot

Out

Vssp

Vdd

9

8

7

6

5

4

3

2

1

DM-LH

Vsslog

PR

DM-HL

PR-FPS

LH-Tr

L-Clmp

H-Clmp

HL-Tr

2/18

Vsssub

HL-Tr

H-Clmp

L-Clmp

LH-Tr

PR-FPS

PR-FPS

DM-HL

PR

Vsssub

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

Vsssub

Vpp

Vpp

CBoot

Out

Vssp

Vssp

Vdd

DM-LH

Vsslog

2

Page 3

2 - BLOC DIAGRAM

MULTIWATT 15

Vdd

10

Protection

Control

Voltage Control

CBoot Vpp

13 15 14

Bootstrap

control

STV7801S

H-Clmp

LH-Tr

HL-Tr

L-Clmp

Vsslog

2

4

1

3

8

STV7801S

Timing

Control

LH Transistor

HL Transistor

DM-HLPR-FPS

DM-LH

H-Clmp

Transistor

L-Clmp

Transistor

11965

Vssp

7

12

PR

Out

3/18

Page 4

STV7801S

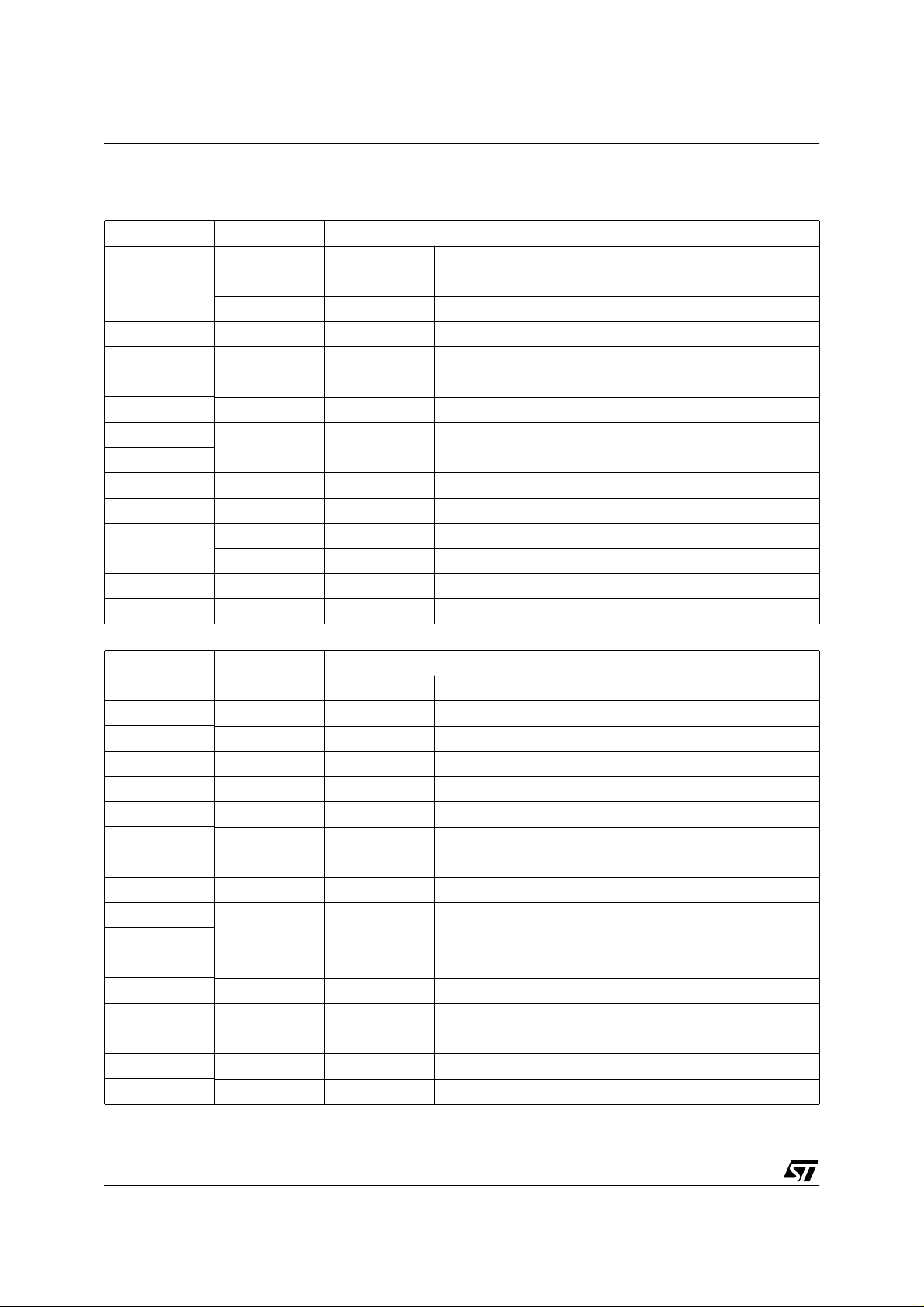

3 - PIN DESCRIPTION

Multiwatt 15

Pin Number Pin Name Function Description

1 HL-Tr Input Power Recovery High Level/Low Level Transition

2 H-Clmp Input Main Switch High-Side Clamp Input

3 L-Clmp Input Main Switch Low-Side Clamp Input

4 LH-Tr Input Power Recovery Low Level/High Level Transition

5 PR-FPS Input Power Recovery Floating Supply

6 DM-HL Input Current Recirculation- Input Pin - High/Low Transition

7 PR Output Power Recirculation Output Stage

8 Vsslog Ground Logic Ground/Substrate Ground

9 DM-LH Output Current Recirculation- Output Pin - Low/High Transition

10 Vdd Supply Logic Supply

11 Vssp Ground Power Ground

12 Out Output Main Switch Output

13 CBoot Input Bootstrap Capacitor Input Pin

14 Vpp Supply High Voltage Supply

15 Vpp Supply High Voltage Supply

PowerSO20

Pin Number Pin Name Function Description

1 Vssub Ground Substrate Ground

2 HL-Tr Input Power Recovery High Level/Low Level Transition

3 H-Clmp Input Main Switch High-Side Clamp Input

4 L-Clmp Input Main Switch Low-Side Clamp Input

5 LH-Tr Input Power Recovery Low Level/High Level Transition

6 PR-FPS Input Power Recovery Floating Supply

7 PR-FPS Input Power Recovery Floating Supply

8

DM-HL

9 PR Output Power Recirculation Output Stage

10

11

Vssub

Vsslog

12 DM-LH Output Current Recirculation- Output Pin - Low/High Transition

13

14

15

Vdd

Vssp

Vssp

16 Out Output Main Switch Output

17 CBoot Input Bootstrap Capacitor Input Pin

Input Current Recirculation- Input Pin - High/Low Transition

Ground Substrate Ground

Ground Logic Ground/Substrate Ground

Supply Logic Supply

Ground Power Ground

Ground Power Ground

4/18

Page 5

Pin Number Pin Name Function Description

18 Vpp Supply High Voltage Supply

19 Vpp Supply High Voltage Supply

20 Vssub Ground Substrate Ground

4 - CIRCUIT DESCRIPTION

STV7801S

STV7801 is a monol ithic integrated circuit implemented in ST Microelectronics BCD proprietary

technology designed as a switched power supp ly

generator for data drivers in a Plasma Display

Panel (P.D.P.) application.

The high load drive capability of STV7801 reduces

the number of devices n ecessary to drive a com plete PDP (4 to 6 devices for a 42" VGA 16/9 PDP

monitor).

STV7801 high current drive capability provides a

high power recovery efficiency coefficient superior

to 85% on constant capacitive load. The structure

of the output stage is implemented with 2 DMOS

transistors to minimise the die size. External components like bootstrap capacitor can also be implemented to increase the performances of the circuit.

STV7801 integrates level s hifters driven with 5V

CMOS compatible levels. This feature reduces the

number of discrete components such as voltage

trans lator s.

STV7801 integrates several protections like output

over-voltage, timing control and over-tem perature

to increase the reliability of the system.

Over-voltage protection consists in clamping diodes connected between Vpp, Vssp and critical

nodes of the devices.

Timing control consists in a m onitoring of the ou tput stage control signals to avoid any cross-conduction.

Over-temperature protection is activated when

junction temperature reaches the threshold values

fixed internally and sets the device in tri-state

mode.

STV7801 can drive several data drivers connected

to column electrodes of the panel. The maximum

amount of data drivers is given by the Power Recovery Current of the device and then the maximum rise/fall time of the signal. The rise and fall

time of the AC supply signal is adjusted by the value of the inductance connected to the panel capacitance through the data drivers. The amount of

STV7801 needed to gene rate the AC supply can

be reduced by increasing the rise/fall time of the

generated AC supply.

5 - CONTROL SIGN ALS TR UTH TABLE

HL-Tr LH-Tr L-Clmp H-Clmp Device Output Comments

L H L L Low to High Transition Power Saving Mode

H L L L High to Low Transition Power Saving Mode

LXLH

XLHL

X X H H Tri-State Protection Mode

XHHXTri-State Protection Mode

H X X H Tri-State Protection Mode

L L L L Tri-State Protection Mode

Vpp Power Supply Clamp

Vssp Power Ground Clamp

5/18

Page 6

STV7801S

6 - POWER ON SEQUENCE

If Vpp is switched ON before Vdd, the circuit remains in Tri-State mode until Vdd reaches Vdd threshold.

If Vddis switched ON before Vpp, the circuit remains in Tri-State mode until Vpp reaches Vpp threshold.

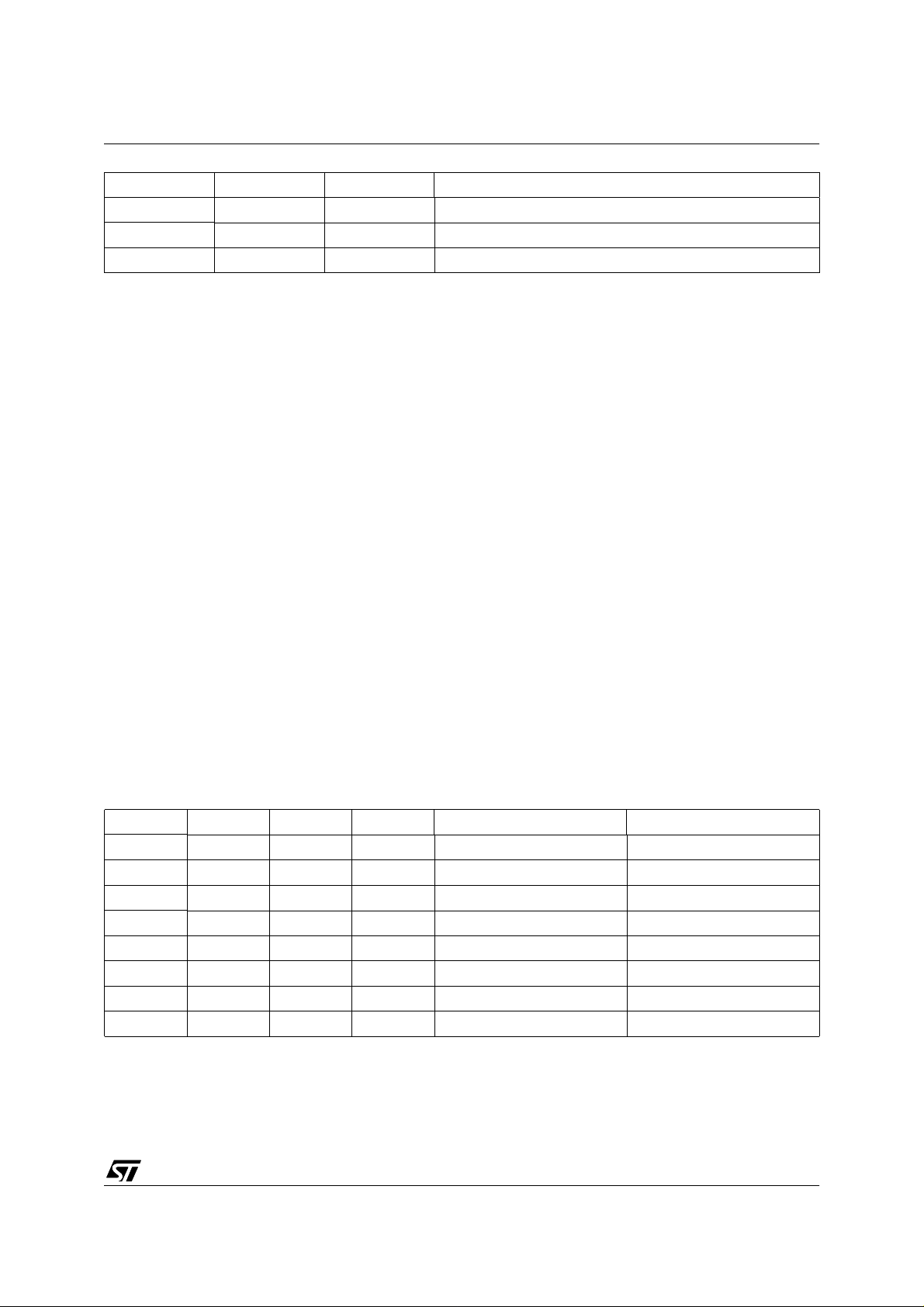

7 - ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

Vdd Logic Supply Range -0.3,+14 V

Vpp Driver Supply Range -0.3 , + 100 V

VIn Logic Input Voltage Range -0.3, Vdd+0.3 °C

Ih-Out Main Switch High Side Current -5 A

Il-Out Main Switch Low Side Current 5 A

Ipr-Hi Power Recovery Current (note1)-7A

Ipr-Lo Power Recovery current (note1)7A

V

CBoot-Vout

Tjmax Maximum Junction Temperature (note2)

Top Operating Temperature Range -20, +70 °C

Tstg Storage Temperature Range -50, +150 °C

Difference between Boot voltage and output voltage 14 V

Internally

protected

°C

Note 1 Peak current as defined in Figure 1 on page 9

Note 2 T hese parame ters are meas ured during ST ’s internal qua lification whi ch includes tem perature ch aracterizat ion

on standard and corner batches of the process. These parameters are not tested on the parts.

Remark: ESD susceptibility

Human body Model: 100pF, 1.5kΩ

Vpp pin (14-15: Multiwatt 15) V

DM-LH pin (9: Multiwatt 15) V

By connecting a 1nF decoupling capacitor, the circuit withstands V

ESD

ESD

= 200V

=400V

=2.2kV on all pins.

ESD

8 - THERMAL DAT A

Symbol Parameter

R

th(j-a)

R

th(j-c)

Note 3 Multilayer PCB.

Note 4 Package floating in the air.

Junction - Ambient Thermal Resistance 40(note3) 35 (note4)°C/W

Junction - Case Thermal Resistance +0.6, +2.5 -0.6, +2.4

PowerSO20 MW15

Value

Unit

6/18

Page 7

STV7801S

9 - ELECTRIC AL CHARACTERISTI CS

(T

= 25°C, Vdd=12 V, Vpp=90 V, Vsslog=Vssub=0 V, Vssp=0 V, unless otherwise specified)

amb

Symbol Parameter Test Conditions Min Typ Max Unit

SUPPLY

Vdd Logic Supply Voltage 11 12 13 V

Vpp Power Output Supply Voltage 20 - 100 V

Idd

Ipp

BOOTSTRAPPED SUPPLY VOLTAGE

V

CBoot-Vout

I

lkg1Boot

I

lkg2Boot

OUTPUTS

V

satH

V

satL

V

satHL

V

satLH

PROTECTION

Tth

Vdd

t

hreshold

Vpp

threshold

INPUTS

Vih Input high level (CMOS compatible) 4 V

Vil

Iih High level inut current (Vih=

Iil Low level input current (Vil=0)

Logic Biasing Current without Transition

(Stand-by-mode)

Power Biasing Current without

Transition (Stand-by-mode)

-5-mA

-6-mA

Bootstrap supply voltage 12 V

Hiz mode

Boot leakage current Hiz mode

Vpp=100V,

-5 0 5 µA

VCBoot-Vout = 10V

HClmp = high

Boot leakage current HClmp

Vpp=100V,

15 30 50 µA

VCBoot-Vout = 10V

Output Saturation Voltage (high level)

Voltage Drop vs

Vpp

iH@-1A

iH@-3A

iH@-4A

1.5

4.5

6.5

Output Saturation Voltage (low level)

iL@1A

iL@3A

iL@4A

1.5

4.5

6.5

Power recirculation - Voltage drop (high

to low level)

iL@1A

iL@3A

iL@6A

V

PR-FPS

=Vpp/2

0.8

2.5

5

Power recirculation - Voltage drop (low

to high level)

iL@-1A

iL@-3A

iL@-6A

Thermal protection temperature threshold

Power ON threshold voltage on

Vdd

V

PR-FPS

=Vpp/2

0.8

2

5

- 170 - °C

7.5 V

Power ON threshold voltage on Vpp 13.3 V

dd

Input low level (CMOS compatible) 0 .9 V

Vdd

)

Vih=Vdd=12V 80 120 150 µA

-2 0 +2 µA

V

V

V

V

V

V

V

V

V

V

V

V

V

7/18

Page 8

STV7801S

10 - AC TIME REQUIREMENTS

(T

= 25°C, Vdd=12 V, Vpp=90 V, Vsslog=Vssub=0 V, Vssp=0 V, unless otherwise specified)

amb

Symbol Parameter Test Conditions Min Typ Max Unit

t

LH

t

HL

t

H

tL

t

Hsetup

t

Lsetup

t

Hhold

t

Lhold

Low/High transition high level control

pulse

High/Low transition high level control

pulse

Duration of high voltage clamp control

pulse at high level

Duration of low voltage clamp control

pulse at low level

Set-up time of Vpp voltage clamp after

low to high transition

Set-up time of Vssp voltage clamp

after high to low transition

Hold time Vout low before high voltage clamp control pulse

Hold time Vout high before low voltage clamp control pulse

10 - - ns

10 - - ns

10 - - ns

10 - - ns

10 - - ns

100 - - ns

TBD

TBD

11 - AC TIMING CHARACTERISTICS

(T

= 25°C, Vdd=12 V, Vpp=90 V, Vsslog=Vssub=0 V, Vssp=0 V, unless otherwise specified)

amb

Symbol Parameter Test Conditions Min Typ Max Unit

t

ON-LH

t

ON-HClmp

t

ON-HL

t

ON-LClmp

Delay of power output change after

recirculation low to high transition

Delay of power output clamp at Vpp

after output stage high side ON

Delay of power output change after

recirculation high to low transition

Delay of power output clamp at GND

after output stage low side ON

Vpp=40V - 140 - ns

- 160 - ns

- 140 - ns

-60-ns

8/18

Page 9

12 - AC CHARAC TERISTIC WAVEFOR MS

Figure 1.

STV7801S

Power output

Current in the inductance

Figure 2.

Power output

HClmp

LH-tr

t

ON-LH

tON-HClmp

tLH

t

H

9/18

Page 10

STV7801S

Figure 3.

ton_HL

Power output

L-Clmp

HL-tr

tON-LClmp

tL

tHL

10/18

Page 11

13 - APPLICATION DIAGRAM

STV7801S

10K

HL-Tr

100pF

10K

H-Clmp

100pF

10K

L-Clmp

100pF

10K

LH-Tr

100pF

47µF/160V 1µF/160V

Vpp

1

2

3

STV7801

4

5

15

14

13

12

11

10

Vpp

CBoot

Out

Vssp

Vdd

+90V

100

µ

F/160V

1nF

to Vpp pins

of data d r iv er I Cs

1µH

(eg pins 1, 2, 42, 66,

107,108 of STV7610A)

DM-HL

6

PR

7

The diodes for the recirculation current directly impact the device performances. High Voltage diodes with recovery time inferior to 50ns are recommended. Shorter recovery times will improve the

power efficiency of the application.

The rise and fall time of the output signal is adjusted by the value of the inductance for a given capacitive load.

trise (tfall) is calculated by the following formula :

DM-LH

9

Vsslog

8

t

rise

πxLxCload=

A 1nF bootstrap capacitor is recommended.

The bootstrap capacitor allows the output signal to

reach the

Vpp value. For a given output level, the

power efficiency will be increased.

A 47µF capacitor is recommended. The ripple on

the tank capacitor is reduced by increasing the

tank capacitor value.

Decoupling capacitors on the power supplies will

minimise the overshoots.

11/18

Page 12

STV7801S

The timing of the control signals will be adjusted by

the trimmers of the RC cells. It is recommended to

the rising (falling) edge of the output signal has

reached its maximum (minimum) value.

enable the clamp signals (H-Clmp, L-Clmp) after

14 - RECOVERY FACTOR MEASUREM ENT CONDITIONS

An idealised schematic of the Power Recovery application is defined below. The inductance (power saving mode) and the 2 capacitors (load, floating_supply) are external components for the D.P.S. device.

Figure 4. DPS Device : Functional Diagram

Vpp

A

S3

Cfloating_supply

S4

The Power Recovery Factor (PRF) in % is given

by the formula :

PRF = 100 x (Pc - Pr) / Pc.

– Pc is the theoretical capacitive power dissipated

in the switches S1, S2 of the Data Power Switch

device when S3, S4 are not activated. Pc is calculated by the formula :

2

P

Cload Vpp

C

xF×=

Inductance

(Power Saving Mode)

with F=switching frequency.

Cload = equivalent panel capacitance

– Pr is the power dissipated in the Data Power

Switch device when it is configured in a power recovery mode (S1, S2, S3, S4 activated). Pr is

calculated by multiplying the average current given by the current sensor A and the value of the

supply voltage

PRF is affected by the external components of the

DPS device such as the inductance and the decoupling capacitors, also the layout of the application.

S1

Cload

S2

Vssp

Vpp.

12/18

Page 13

15 - RESULTS OF POWER EFFICIE NCY

15.1 Power recovery factor for different inductance values

Figure 5. STV7801- Power Recovery Factor, L=1.1µH, T=3.3µs, BYW80-200 diodes

90

85

80

PRF (in %)

75

STV7801S

Cload=4.7nF, Trise=220ns

Cload=9.4nF, Trise=310ns

70

30 40 50 60 70 80 90 100 110

Cload=14.1nF, Trise=380ns

Cload=18.8nF, Trise=430ns

VPP (in V)

Cload=23.5nF, Trise=480ns

Figure 6. STV7801- Power Recovery Factor. L=0.66µH, T=3.3µs, BYW80-200 diodes

85

80

PRF (in %)

75

Cload=4.7nF, Trise=170ns

Cload=9.4nF, Trise=245ns

70

30 40 50 60 70 80 90 100 110

VPP (in V)

Cload=14.1nF, Trise=290ns

Cload=18.8nF, Trise=340ns

13/18

Page 14

STV7801S

Figure 7. STV7801- Power Recovery Factor - L=0.36µH, T=3.3µs, BYW80-200 diodes

85

80

75

PRF (in %)

70

Cload=4.7nF, Trise=140ns

Cload=9.4nF, Trise=200ns

65

30 40 50 60 70 80 90 100 110

Cload=14.1nF, Trise=245ns Cload=18.8nF, Trise=265ns

VPP (in V)

15.2 Power recovery factor (PRF) versus time and Cload

Figure 8. STV7801- PRF versus rise time and Cload - Vpp=70V, T=3. 3µs, BYW80-20 0 diodes

87

86

85

84

83

82

PRF (in %)

81

80

Cload=9.4nF

Cload=14.1nF

Cload=18.8nF

14/18

79

78

150 200 250 300 350 400 450

trise (tfall) in ns

Page 15

STV7801S

15.3 Power recovery factor (PRF) for fixed rise (fall) time

Figure 9. PRF versus Cload and L values - Trise (fall) = 260ns, T=3.3µs, BYW 80-200 diod es

85

84

83

82

81

PRF (in %)

80

79

78

30 40 50 60 70 80 90 100 110

Cload=18.8nF, L=0.4uH

Cload=10.4nF, L=0.66uH

Cload=6.7nF , L=1.1uH Cload=17nF, L=0.5uH

Vpp (in V)

Figure 10. PRF versus Cload and L values - Trise (fall) = 330ns, T=3.3µs, BYW 80-200 diodes

86

85

84

83

PRF (in %)

82

81

Cload=18.8nF, L=0.66uH Cload=11nF, L=1.0uH Cload=8.7nF , L=1.3uH

80

30 40 50 60 70 80 90 100 110

Vpp (in V)

15/18

Page 16

STV7801S

16 - PACKAGE M ECHANICAL DAT A

Multiwatt 15 horizontal, shortleads

H2

V

R

R

B

L5

F

G1

G

V

E

N

V V

C

L1L2

L3

L4

R1 P

L7

Diam 1

S1

V

A

H2

H1

S

MW15HME

Dimensions Millimeters Inches

Min. Typ. Max. Min. Typ. Max.

A 5 0.197

B 2.65 0.104

C 1.6 0.063

E 0.49 0.55 0.019 0.022

F 0.66 0.75 0.026 0.030

G 1.02 1.27 1.52 0.040 0.050 0.060

G1 17.53 17.78 18.03 0.690 0.700 0.709

H1 19.6 20.2 0.772 0.795

H2 19.6 20.2 0.772 0.795

L1 17.8 18 18.2 0.701 0.709 0.717

L2 2.3 2.5 2.8 0.091 0.098 0.110

L3 17.25 17.5 17.75 0.679 0.689 0.699

L4 10.3 10.7 10.9 0.406 0.421 0.429

L5 2.7 3 3.3 0.106 0.118 0.130

L7 2.65 2.9 0.104 0.114

R 1.5 0.059

S 1.9 2.6 0.075 0.102

S1 1.9 2.6 0.075 0.102

Dia1 3.65 3.85 0.144 0.152

16/18

3

Page 17

STV7801S

PowerSO20

NN

A

a2

a3

GAGE

PLANE

0.033

0.083

DETAIL B

be

20

E2

1

Dimensions Millimeters Inches

Min. Typ. Max. Min. Typ. Max.

A 3.50 0.138

a1 0.20 0.275 0.008 0.011

a2 3.10 3.20 0.122 0.126

a3 0 0.075 0 0.003

b 0.42 0.50 0.0165 0.020

c 0.24 0.28 0.009 0.011

D(1) 15.85 15.95 0.624 0.628

D1 9.45 9.75 0.372 0.384

E 14.10 14.20 14.35 0.555 0.559 0.565

e 1.27 0.050

e3 11.43 0.450

E1(1) 10.85 11.05 0.431 0.435

E2 2.85 0.112

E3 5.85 6.15 0.230 0.242

G 0 0.075 0 0.003

H 15.55 15.85 0.612 0.624

h 0.039

L 0.85 1.05

M 2.10 2.30

N 9d. 9d.

R 0.30 0.012

S 3d. 5d. 7d. 3d. 5d. 7d.

T 10.00 0.394

Note 5 “D” and “E1” do not include mold flash or protrusions

-Mold flash or protrusions shall not exceed 0.15mm (0.006inc.)

-Critical dimensions: “E”, “G” and “a3”

e3DETA IL A

H

D

M

11

10

E1

lead

DETA IL B

s

L

R

0.041

0.090

17/18

Page 18

STV7801S

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the con sequences of use of suc h informatio n nor for any infringeme nt of patents or other right s of

third parties whi ch ma y res ult fro m its u se. N o licen se is grant ed by implic ation or oth erwi se und er an y patent

or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supe rsedes and repl aces all informa tion previously s upplied. STMicr oelectronics

products are not auth orized for use as critical componen ts in lif e support devices or syst ems with out the e xpress written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

2000 STMicroelectronics - All Rights Reserved.

Purchase of I

components in an I

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco -

18/18

2

C Components by STMicroelectronics conveys a license under the Philips I2C Patent. Rights to use these

2

C system is granted provided that the system conforms to the I2C Standard Specification as defined

by Philips.

STMicroelectronics Group of Companies

Singapore - Spain Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com

4

Loading...

Loading...