Page 1

STV6886

LOW-COST I2C CONTROLLED DEFLECTION PROCESSOR

FOR MULTISYNC MONITOR

FEATURES

General

■ SYNC PROCESSOR (separate or composite)

■ 12V SUPPLY VOLTAGE

■ 8V REFERENCE VOLTAGE

■ HOR. LOCK/UNLOCK OUTPUT

■ HOR. & VERT. LOCK/UNLOCK INDICATION

■ READ/WRITE I

■ HORIZONTAL AND VERTICAL MOIRE

■ B+ REGULATOR

2

C INTERFACE

- Internal PWM generator for B+ current mode

step-up converter

- Switchable to step-down converter

-I2C-adjustable B+ reference voltage

- Output pulses synchronized on horizontal

frequency

- Internal maximum current limitation.

Horizontal

■ Self-adaptative

■ Dual PLL concept

■ 80kHz maximum frequency

■ X-ray protection input

2

■ I

C controls: Horizontal duty-cycle, H-position,

horizontal size amplitude

DESCRIPTION

The STV6886 is a monolithic integrated circuit assembled in a 32-pin shrink dual-in-line plastic

package. This IC controls all the functions related

to horizontal and vertical deflection in multimode

or multi-frequency computer display monitors.

The internal sync processor, combined with the

powerful geometry correction block, makes the

STV6886 suitable for very high performance monitors, using few external components.

Combined with other ST components dedicated

for CRT monitors (microcontroller, video preamplifier, video amplifier, OSD controller) the STV6886

allows fully I2C bus-controlled computer display

monitors to be built with a reduced number of external components.

SHRINK32 (Plastic Package)

ORDER CODE: STV6886

PIN CONNECTIONS

Vertical

■ Vertical ramp generator

■ 50 to 120 Hz agc loop

■ Geometry tracking with VPOS & VAMP

2

■ I

C controls:VAMP, VPOS, S-CORR, C-CORR

■ Vertical breathing compensation

I2C Geometry Corrections

■ Vertical parabolagenerator (Pin Cushion - E/W,

Keystone, Corner Correction)

■ Horizontal dynamic phase

(Side Pin Balance & Parallelogram)

■ Horizontal and vertical dynamic focus

(Horizontal Focus Amplitude, Horizontal Focus

Symmetry, Vertical Focus Amplitude)

HMOIRE/HLOCK

H/HVIN

VSYNCIN

PLL2C

C0

R0

PLL1F

HPOSITION

HFOCUSCAP

FOCUS-OUT

HGND

HFLY

HREF

COMP

REGIN

I

SENSE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16 17

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

5V

SDA

SCL

V

CC

BOUT

GND

HOUT

XRAY

EWOUT

VOUT

VCAP

V

REF

VAGCCAP

VGND

VBREATH

B + GND

Version 4.2

April 2000 1/43

1

Page 2

TABLE OF CONTENTS

PIN CONNECTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . .................................. 3

QUICK REFERENCE DATA . . . . . . . . . . . ............................................ 4

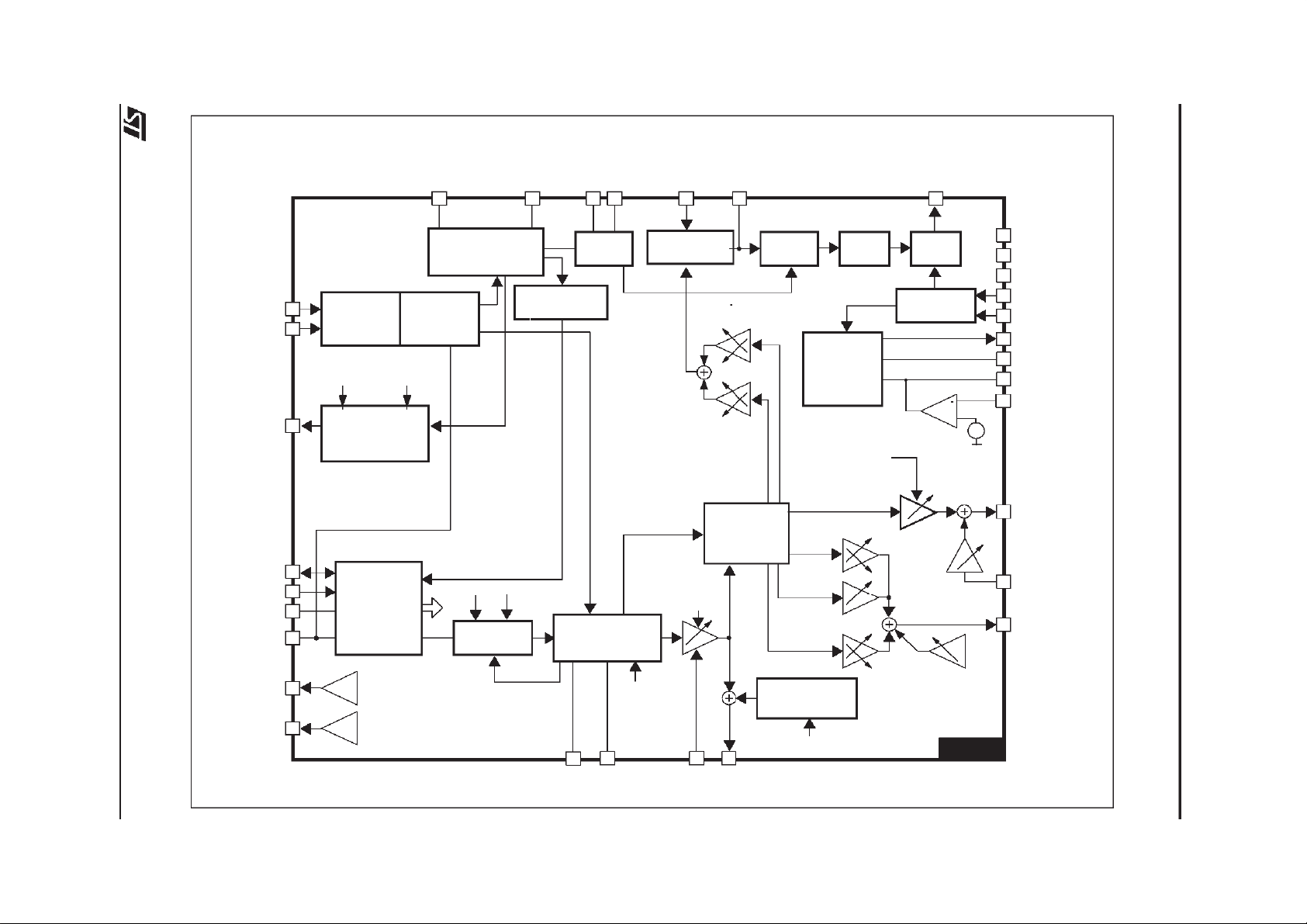

BLOCK DIAGRAM . . . . . . . . . ..................................................... 5

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

THERMAL DATA . . . . . . . . . . . . . . . . . . . ............................................6

Supply and reference voltages ..................................................... 6

I2C READ/WRITE . . . . . . . . . . . . . . . . . . . . . . ......................................... 7

SYNC PROCESSOR . . . . . . . . . . . . ................................................7

HORIZONTAL SECTION . . . . . . . . . . . . . ............................................ 8

VERTICAL SECTION . . . . . ...................................................... 10

DYNAMIC FOCUS SECTION . . . . . . ...............................................11

GEOMETRY CONTROL SECTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

MOIRE CANCELLATION SECTION . . . . . . . . . . . . . . . ................................. 13

B+ SECTION . .................................................................14

TYPICAL OUTPUTWAVEFORMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ........ 16

I2C BUS ADDRESS TABLE . . . . . . . ............................................... 20

OPERATING DESCRIPTION . . . . . . ...............................................23

1 GENERAL CONSIDERATIONS . . . . . ......................................... 23

1.1 Power Supply . . . . . . . ............................................... 23

1.2 I2C Control . . . . . . . . . . . . . . . . . . . . . . . ................................. 23

1.3 Write Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ........ 23

1.4 Read Mode ....................................................... 23

1.5 Sync Processor . . . . . ............................................... 23

1.6 Sync Identification Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . 23

1.7 IC status . . . . . . . . . . . . . . . . . . . . .. . . . . . . .............................. 24

1.8 Sync Inputs . . . .................................................... 24

1.9 Sync Processor Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2 HORIZONTAL PART . . . . . . . . . . . . . . . . . . . . . . . . ..............................24

2.1 Internal Input Conditions . . ...........................................24

2.2 PLL1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . ................................. 25

2.3 PLL2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . ................................. 26

2.4 Output Section . . . . . . . . . . . . . ........................................ 27

2.5 X-RAY Protection . . . . . . . . . . . . . . . . . .................................. 27

2.6 Horizontal and Vertical Dynamic Focus . . . . . . . . . . . . . . . . . . . . . . . ...........27

2.7 Horizontal Moiré Output . . . . . . . . . . . . .................................. 29

3 VERTICAL PART . . . . . . . . . . ............................................... 29

3.1 Function . . . . . . .................................................... 29

3.2 I2C Control Adjustments . . . . . . . . . .................................... 29

3.3 Vertical Moiré . . . . . . . ............................................... 29

3.4 Basic Equations .................................................... 30

3.5 Geometric Corrections . . . . ........................................... 30

3.6 E/W ............................................................. 31

3.7 Dynamic Horizontal Phase Control . . . . . ................................ 32

4 DC/DC CONVERTER PART . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

4.1 Step-up Configuration . . . . . . . . . . . . . .................................. 32

4.2 Step-down Configuration . . . . .. . . . . . .................................. 32

4.3 Step-up and Step-down Configuration Comparison . . . . . . . . . . . . . . . . . . . . . . . . 32

INTERNAL SCHEMATICS . . . ....................................................34

PACKAGE MECHANICAL DATA . . . ...............................................41

2

2/43

Page 3

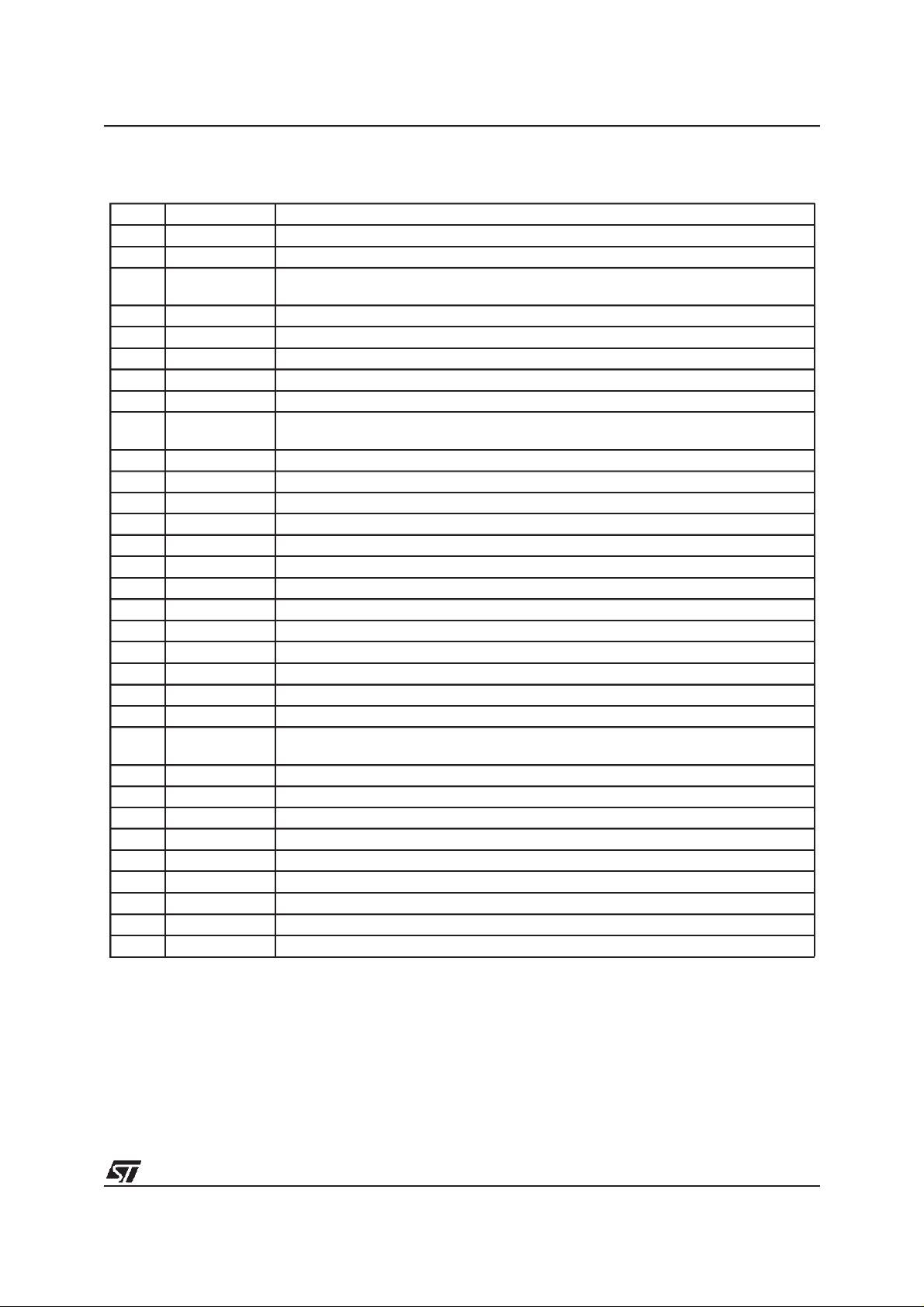

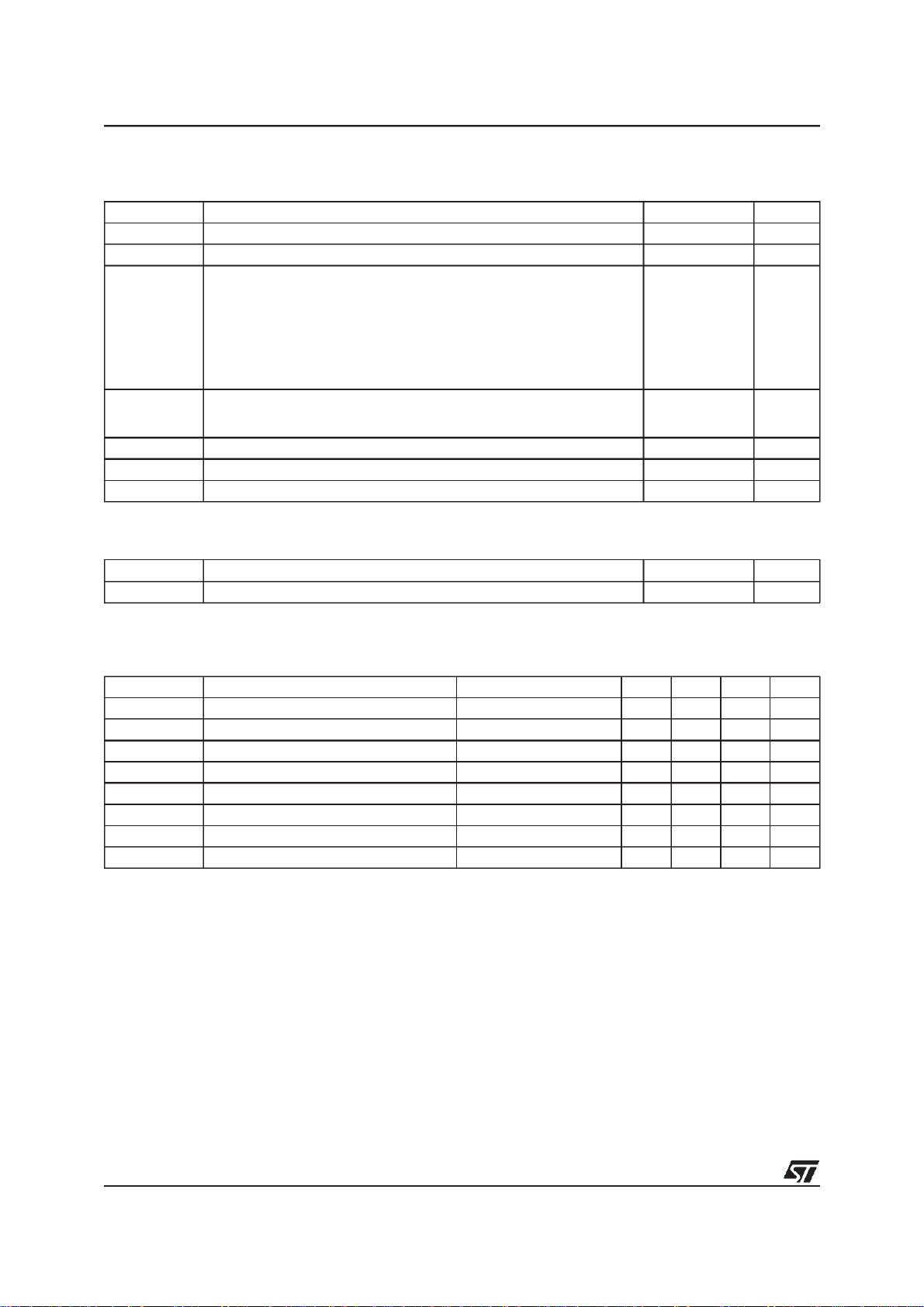

PIN CONNECTIONS

Pin Name Function

1 H/HVIN TTL-compatible Horizontal sync Input (separate or composite)

2 VSYNCIN TTL-compatible Vertical sync Input (for separated H&V)

3 HMOIRE/

HLOCK

4 PLL2C Second PLL Loop Filter

5 C0 Horizontal Oscillator Capacitor

6 R0 Horizontal Oscillator Resistor

7 PLL1F First PLL Loop Filter

8 HPOSITION Horizontal Position Filter (capacitor to be connected to HGND)

9

HFOCUS-

CAP

10 FOCUS OUT Mixed Horizontal and Vertical Dynamic Focus Output

11 HGND Horizontal Section Ground

12 HFLY Horizontal Flyback Input (positive polarity)

13 HREF Horizontal Section Reference Voltage (to be filtered)

14 COMP B+ Error Amplifier Output for frequency compensation and gain setting

15 REGIN Feedback Input of B+ control loop

16 I

SENSE

17 B+GND Ground (related to B+reference)

18 VBREATH V Breathing Input Control (compensation of vertical amplitude against EHV variation)

19 VGND Vertical Section Ground

20 VAGCCAP Memory Capacitor for Automatic Gain Control in Vertical Ramp Generator

21 V

REF

22 VCAP Vertical Sawtooth Generator Capacitor

23 VOUT Vertical Ramp Output (with frequency-independent amplitude and S or C Corrections

24 EWOUT Pin Cushion (E/W)Correction Parabola Output

25 XRAY X-RAY protection input (with internal latch)

26 HOUT Horizontal Drive Output(NPN open collector)

27 GND General Ground

28 BOUT B+ PWM Regulator Output (NPN open collector)

29 V

CC

30 SCL I

31 SDA I

32 5V 5V Supply Voltage

Horizontal Moiré Output (to be connected to PLL2C through a resistor divider), HLock

Output

Horizontal Dynamic Focus Oscillator Capacitor

Sensing of external B+ switching transistor current, or switch for step-down converter

Vertical Section Reference Voltage (to be filtered to pin 19)

if any). It includes vertical position and vertical moiré voltages.

Supply Voltage(12V typ) (referenced to Pin 27)

2

C Clock Input

2

C Data Input

STV6886

3/43

Page 4

STV6886

QUICK REFERENCE DATA

Parameter Value Unit

Any polarity on H Sync & V Sync inputs YES

TTL or composite Syncs YES

Sync on Green NO

Horizontal Frequency 15 to 80 kHz

Horizontal Autosync Range (for given R0 and C0. Can be easily increased by application) 1 to 3.5 f0

Control of free-running frequency NO

Frequency Generator for Burn-in NO

2

Control of H-Position through I

Control for H-Duty Cycle through I

PLL1 Inhibition Possibility NO

Output for Horizontal Lock/Unlock YES

Dual Polarity H-Drive Outputs NO

Vertical Frequency 35 to 150 Hz

Vertical Autosync Range (for 150nF on Pin 22 and 470nF on Pin 20) 50 to 120 Hz

Vertical S-Correction (adapted to normal or super flat tube), controlled through I

Vertical C-Correction, controlled through I

Control of Vertical Amplitude through I

Control of Vertical Position through I

Input for Vertical Amplitude compensation versus EHV YES

E/W Correction Output(also known as Pin Cushion Output) YES

Horizontal Size Adjustment through I

Control of E/W (Pincushion) Adjustment through I

Control of Keystone (Trapezoïd) Adjustment through I

Control of Corner Adjustment through I

Fully integrated Dynamic Horizontal Phase Control YES

Control of Side Pin Balance through I

Control of Parallelogram through I

H/V composite Dynamic Focus Output YES

Control of Horizontal Dynamic Focus Amplitude through I

Control of Horizontal Dynamic Focus Symmetry through I

Control of Vertical Dynamic Focus Amplitude through I

Tracking of Geometric Corrections and ofVertical focus withVertical Amplitude and Position YES

Control of Horizontal and Vertical Moiré cancellations through I

Optimisation of HMoiré frequency through I

B+ Regulation, adjustable through I

Stand-by function, disabling H and V scanning and B+ YES

X-Ray protection, disabling H scanning and B+ YES

Blanking Outputs NO

2

C Read/Write 400 kHz

Fast I

2

C indication of the presence of Syncs (biased from 5V alone) YES

I

2

C indication of the polarity and Type of Syncs YES

I

2

C indication of Lock/Unlock, for bothHorizontal and Vertical sections YES

I

CYES

2

C30to65%

2

CYES

2

CYES

2

CYES

2

CYES

2

C control of E/W Output DC level YES

2

CYES

2

CYES

2

CYES

2

CYES

2

CYES

2

CYES

2

CYES

2

CYES

2

CYES

2

CYES

2

CYES

4/43

Page 5

H/HVIN

V

SYNCIN

HMOIRE

/HLOCK

SDA

SCL

GND

5V

SyncInput

1

2

VSYNC HFLY

HorizontalMoire

3

7 bits+ON/OFF

31

30

27

32

Select

(1bit)

Generator

+Frequency

2

I

C Interface

PLL1F POSITION R0 C0 HFLY PLL2C HOUT

7 8 6 5 12 4 26

Phase/Frequency

Comparator

H-Phase(7bits)

Sync

Processor

VCO

Lock/Unlock

Identification

Phase

Comparator

SPinbal

7bits

2

x

Phase

Shifter

H-Duty

(7bits)

Safety

Processor

B+

Controller

x

Keybal

7bits

VDFAMP

7bits

2

4

2

x

Amp

Symmetry

2x7bits

7 bits

S andC

Correction

7 bits

Vertical

Oscillator

RampGenerator

VAMP

7bits

Geometry

Tracking

E/Wpcc

7bits

Keyst.

7 bits

Corner

7bits

x

x

x

Hout

Buffer

+

5V

Internal

reference

(7bits)

2

x

HSize

DC

7 bits

11

19

17

29

25

28

16

14

15

10

9

24

BLOCK DIAGRAM

HGND

VGND

GND

VCC

XRAY

+OUT

ISENSE

COMP

REGIN

FOCUS

HFOCUSCAP

EWOUT

5/43

HREF

VREF

13

21

OUT

VerticalMoire

Cancel

7bits+ON/OFF

VSYNC

STV6886

STV6886

H

ref

V

ref

VPOS

7bits

23182022

V

CAP

AGCCAP

VBREATHV

V

Page 6

STV6886

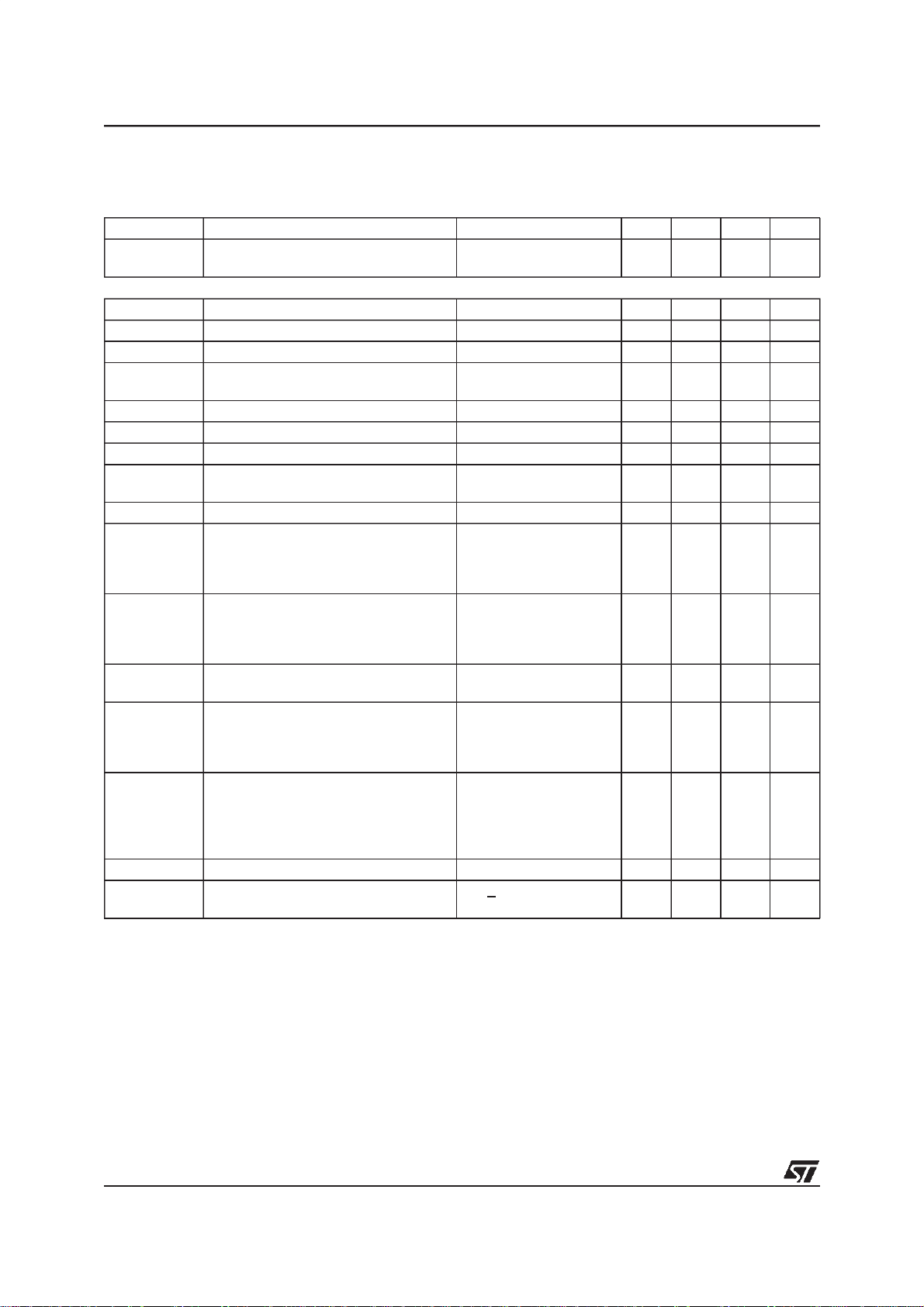

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

CC

V

DD

V

IN

VESD

T

stg

T

j

T

oper

Supply Voltage (Pin 29) 13.5 V

Supply Voltage (Pin 32) 5.7 V

Max Voltage on Pin 4

Pin 9

Pin 5

Pins 6, 7, 8, 14, 15, 16, 20, 22

Pins 3, 10, 18, 23, 24, 25, 26, 28

Pins 1, 2

Pins 30, 31

ESD susceptibility Human Body Model, 100pF Discharge

through 1.5kΩ

EIAJ Norm, 200pF Discharge through 0Ω

4.0

5.5

6.4

8.0

V

V

300

CC

DD

5

2

Storage Temperature -40, +150 °C

Junction Temperature +150 °C

Operating Temperature 0, +70 °C

THERMAL DATA

V

V

V

V

V

V

V

kV

V

Symbol Parameter Value Unit

R

th(j-a)

Max. Junction-Ambient Thermal Resistance 65 °C/W

SUPPLY AND REFERENCE VOLTAGES

Electrical Characteristics (VCC= 12V, T

Symbol Parameter Test Conditions Min. Typ. Max. Units

V

V

I

CC

I

DD

V

REF-H

V

REF-V

I

REF-H

I

REF-V

CC

DD

Supply Voltage Pin 29 10.8 12 13.2 V

Supply Voltage Pin 32 4.5 5 5.5 V

Supply Current Pin 29 50 mA

Supply Current Pin 32 5 mA

Horizontal Reference Voltage Pin 13, I = -2mA 7.6 8.2 8.8 V

Vertical Reference Voltage Pin 21, I = -2mA 7.6 8.2 8.8 V

Max. Sourced Current on V

Max. Sourced Current on V

=25°C unless otherwise indicated)

amb

REF-H

REF-V

Pin 13 5 mA

Pin 21 5 mA

6/43

Page 7

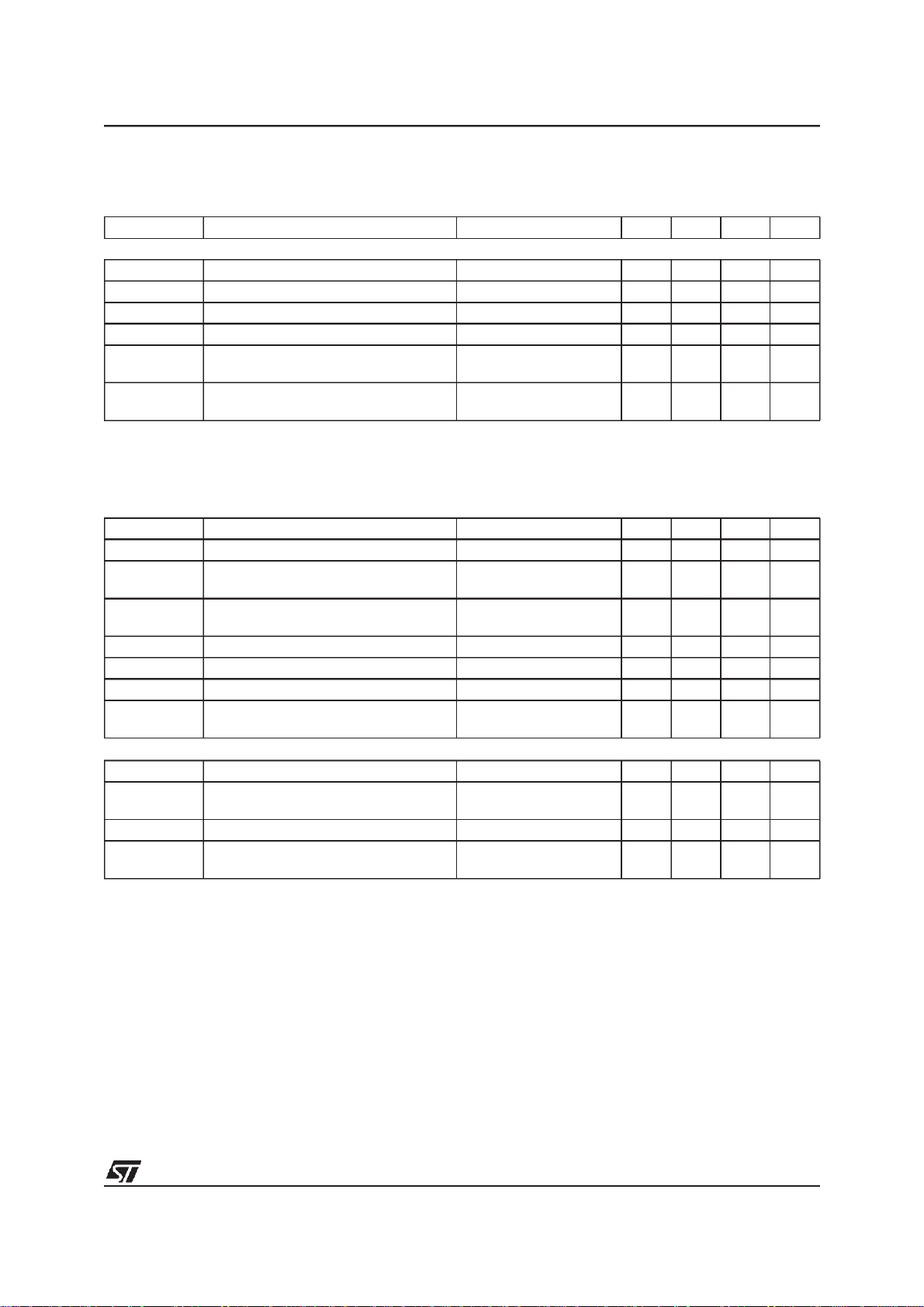

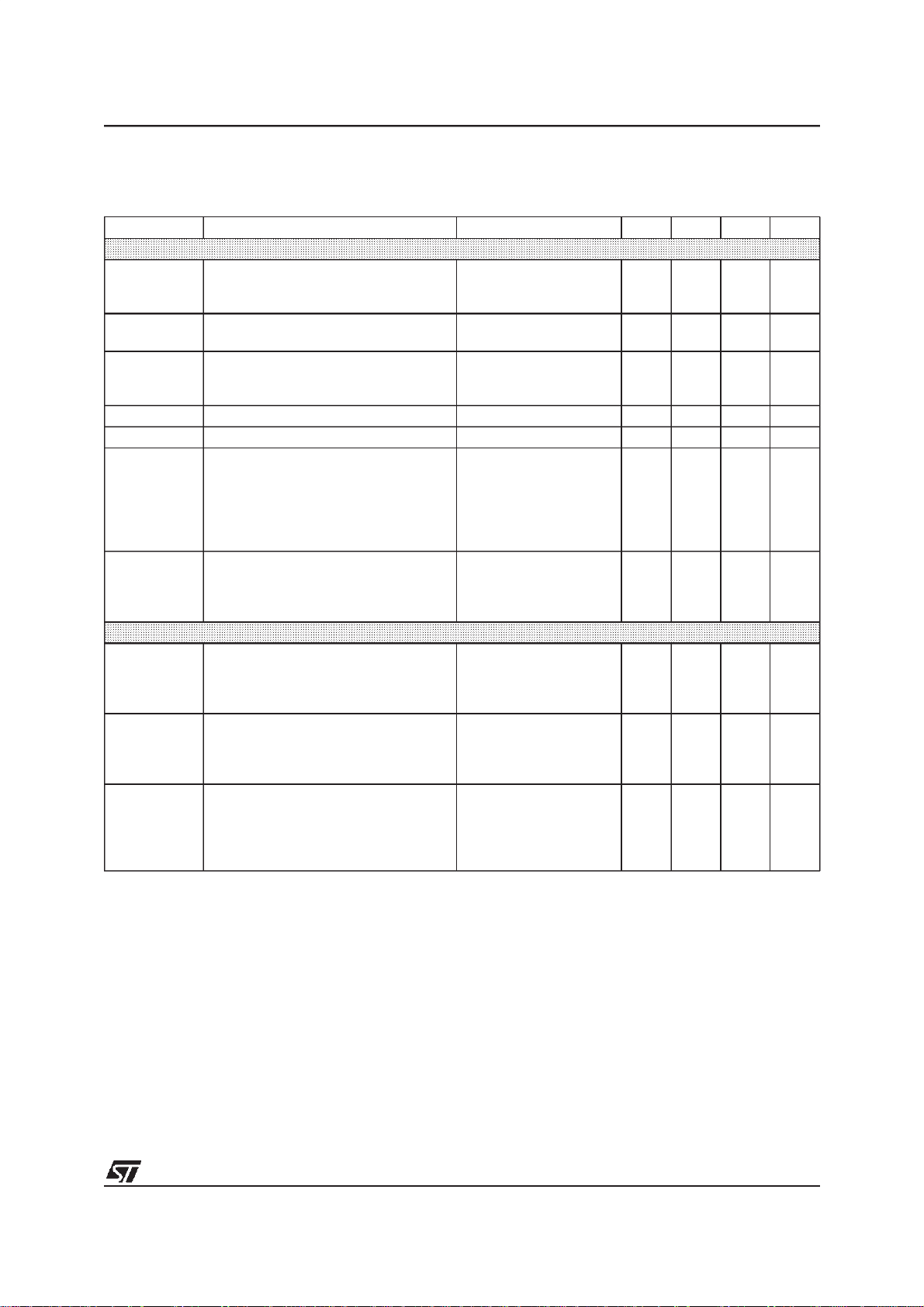

STV6886

I2C READ/WRITE

Electrical Characteristics (VDD= 5V, T

Symbol Parameter Test Conditions Min. Typ. Max. Units

2

C PROCESSOR

I

Fscl Maximum Clock Frequency Pin 30 400 kHz

Tlow Low period of the SCL Clock Pin 30 1.3 µs

Thigh High period of the SCL Clock Pin 30 0.6 µs

Vinth SDA and SCL Input Threshold Pins 30, 31 2.2 V

VACK

2

C leak

I

Note: 1 See also I2C Bus Address Table.

(1)

Acknowledged Output Voltage on SDA

input with 3mA

Leakage current into SDA and SCL with

no logic supply

amb

=25°C)

Pin 31 0.4 V

=0

V

DD

Pins 30, 31 = 5 V

20 µA

SYNC PROCESSOR

Operating Conditions (VDD= 5V, VCC= 12V, T

Symbol Parameter Test Conditions Min. Typ. Max. Units

HSVR Voltage on H/HVIN Input Pin 1 0 5 V

MinD

Mduty

VSVR Voltage on VSYNCIN Pin 2 0 5 V

VSW Minimum Vertical Sync Pulse Width Pin 2 5 µs

VSmD Maximum Vertical Sync Input Duty Cycle Pin 2 15 %

VextM

Minimum Horizontal Input Pulses Duration

Maximum Horizontal Input Signal Duty

Cycle

Maximum Vertical Sync Width on TTL H/

Vcomposite

Electrical Characteristics (VDD= 5V, VCC= 12V, T

Symbol Parameter Test Conditions Min. Typ. Max. Units

VINTH

RIN Horizontal and Vertical Pull-Up Resistor Pins 1, 2 250 kΩ

VoutT

Note: 2 THis the horizontal period.

Horizontal and Vertical Input Logic Level

(Pins 1, 2)

Extracted Vsync Integration Time (% of

) on H/VComposite

T

H

(2)

=25°C)

amb

Pin 1 0.7 µs

Pin 1 25 %

Pin 1 750 µs

=25°C)

amb

High Level

Low Level

C0 = 820pF 26 35 %

2.2

0.8

V

V

7/43

Page 8

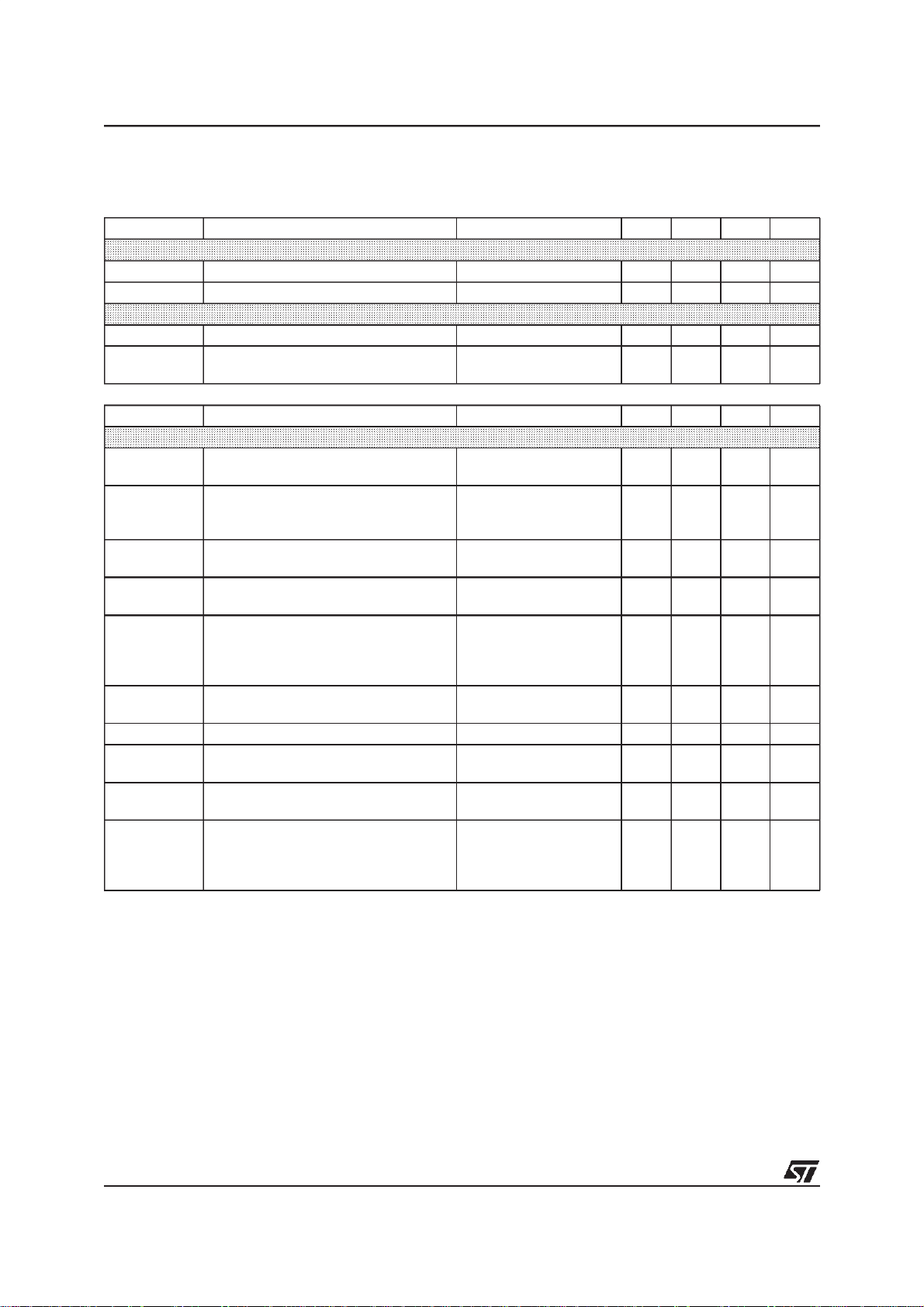

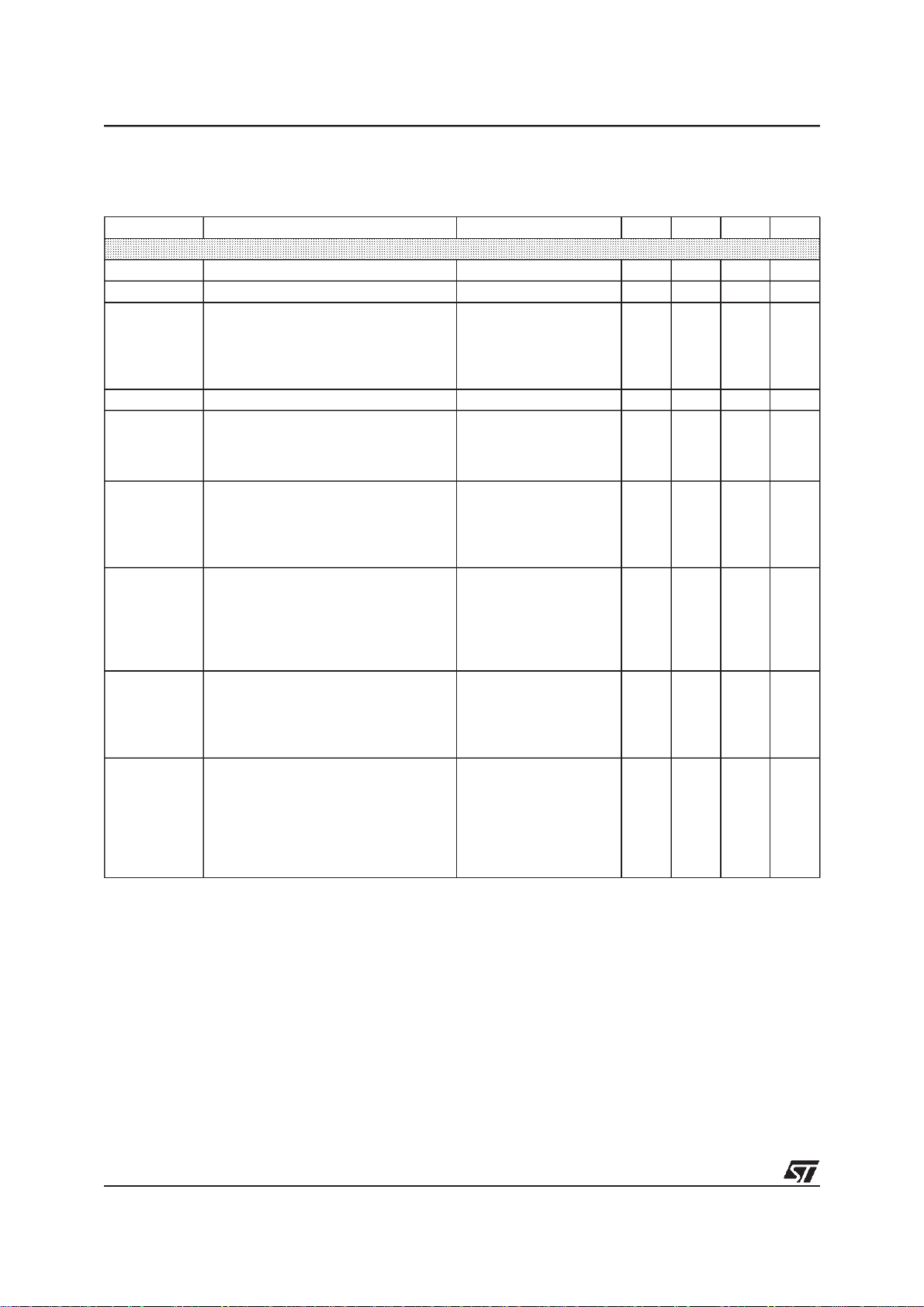

STV6886

HORIZONTAL SECTION

Operating Conditions

Symbol Parameter Test Conditions Min. Typ. Max. Units

VCO

I

0max

F(max.) Maximum Oscillator Frequency 80 kHz

OUTPUT SECTION

I12m Maximum Input Peak Current Pin 12 5 mA

HOI

Electrical Characteristics (VCC= 12V, T

Symbol Parameter Test Conditions Min. Typ. Max. Units

1st PLL SECTION

HpoIT

Vvco VCO Control Voltage (Pin 7)

Vcog VCO Gain (Pin 7)

Hph Horizontal Phase Adjustment

Vbmi

Vbtyp

Vbmax

IPII1U

IPII1L

f

o

dfo/dT Free Running Frequency Thermal Drift

CR PLL1 Capture Range

HUnlock

Max Current from Pin 6 Pin 6 1.5 mA

Horizontal Drive Output Maximum Current

amb

Delay Time for detecting polarity

(3)

change

(4)

Horizontal Phase Setting Value (Pin 8)

Minimum Value

Typical Value

Maximum Value

PLL1 Filter Charge Current

Pin 26, Sunk current 30 mA

=25°C)

Pin 1 0.75 ms

V

= 8.2V

REF-H

f

H=f0

fH=fH(Max.)

= 6.49kΩ,

R

0

= 820pF

C

0

% of Horizontal

Period

(4)

Sub-Address 01

Byte x1111111

Byte x1000000

Byte x0000000

PLL1 Unlocked

PLL1 Locked

Tbd 15.9 Tbd kHz/V

1.4

4.9

±10 %

2.9

3.5

4.2

±140

±1

Free Running Frequency R0= 6.49kΩ,C0= 820pF Tbd 22.8 Tbd kHz

Not including external

(5)

componant drift

fH(Min.)

fH(Max.)

(6)

-150 ppm/C

fo+0.5

3.5f

o

Sub-address 02

DC level pin 3 when PLL1 is

unlocked

(7)

1xxx xxxx

0000 0000

0111 1111

6

0.3

2.75 3

V

V

V

V

V

µA

mA

kHz

kHz

V

V

V

8/43

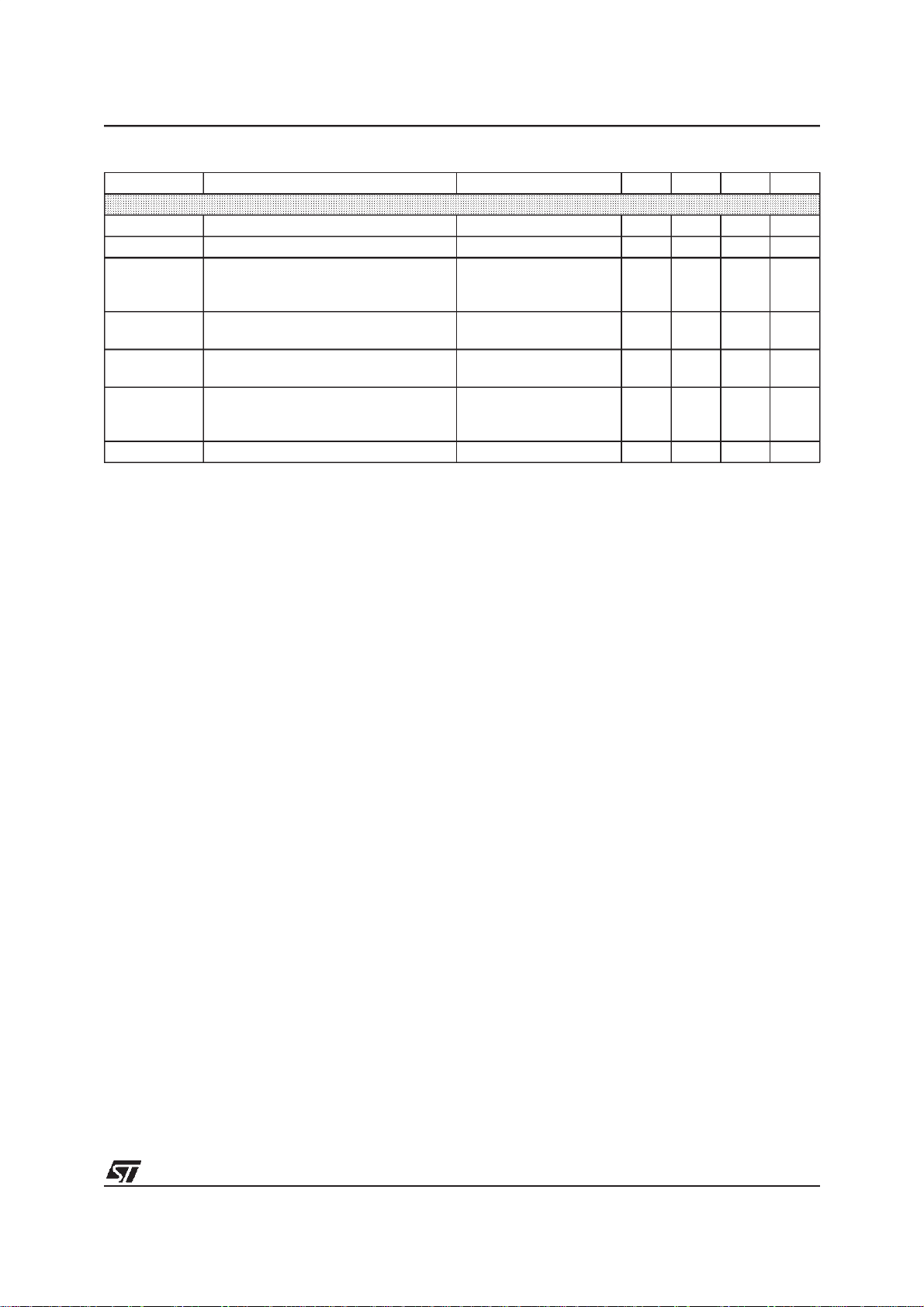

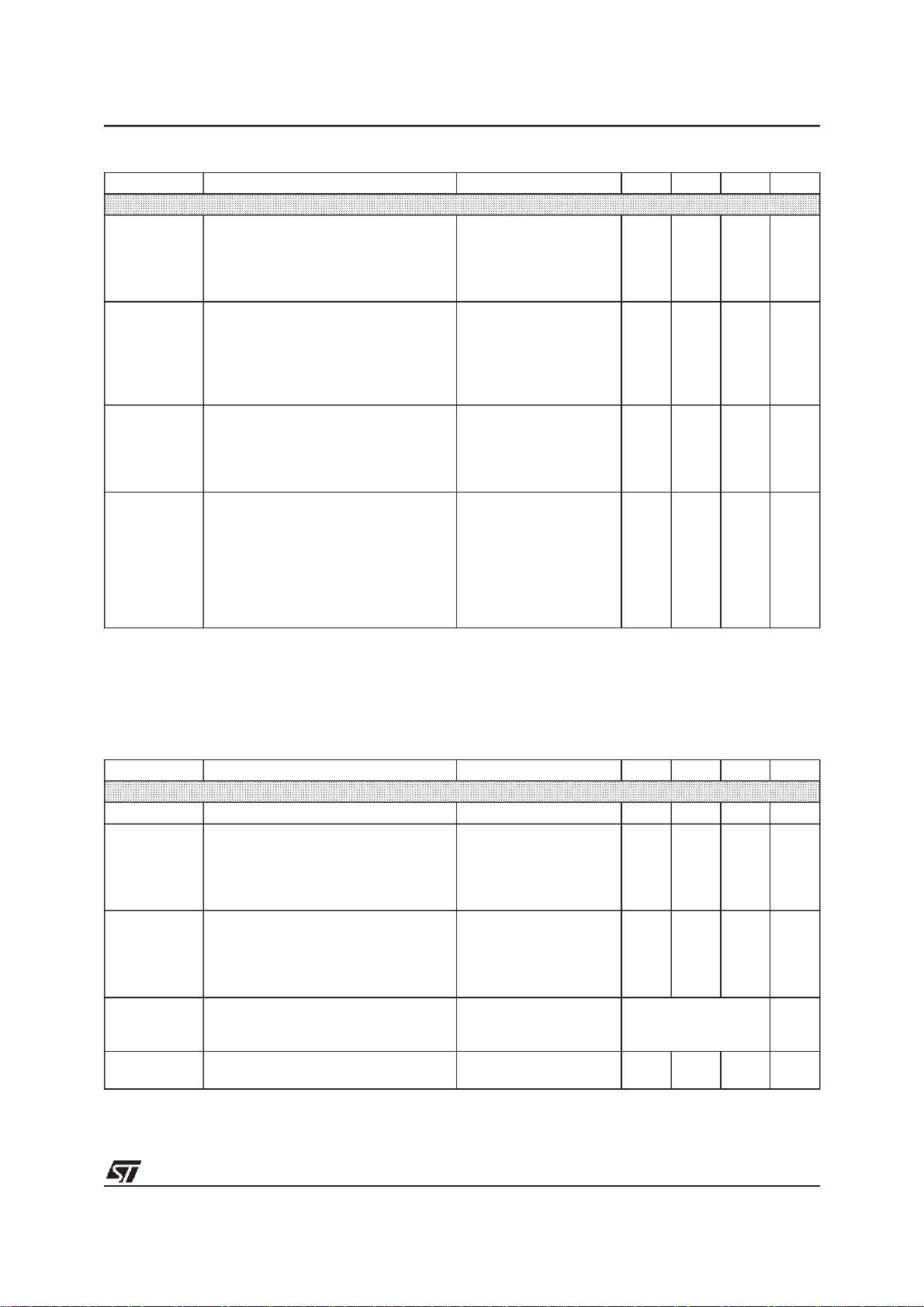

Page 9

STV6886

Symbol Parameter Test Conditions Min. Typ. Max. Units

2nd PLL SECTION AND HORIZONTAL OUTPUT SECTION

FBth Flyback Input Threshold Voltage (Pin 12) 0.65 0.75 V

Hjit Horizontal Jitter

HDmin

HDmax

XRAYth

Vphi2

Horizontal Drive Output Duty-Cycle (Pin

(9)

26)

X-RAY Protection Input Threshold Voltage,

Internal Clamping Levels on 2nd PLL

Loop Filter (Pin 4)

(8)

Inhibition threshold (The condition V

VSCinh

VSCinh willstop H-Out, V-Out, B-Out and

reset X-RAY)

HDvd Horizontal Drive Output (low level) Pin 26, I

Note: 3 This delay is necessary to avoid a wrong detection of polarity change in the case of a composite sync.

4 See Figure 10 for explanation of reference phase.

5 These parameters are not tested on each unit. They are measured during our internal qualification.

6 A larger range may be obtained by application.

7 When at 0xxx xxxx, (HMoiré/HLock not selected), Pin 3 is a DAC with 0.3...2.75V range. When at 1xxx xxxx

(HMoiré/HLock selected) and PLL1 is locked, Pin 3 provides the waveform for HMoiré. See also Moiré

section.

8 Hjit = 10

6

x(Standard deviation/Horizontal period).

9 Duty Cycle is the ratio between the output transistor OFF time and the period. The scanning transistor is

controlled OFF when the output transistor is OFF.

10 Initial Condition for Safe Start Up.

At 31.4kHz 70 ppm

Sub-Address 00

Byte x1111111

Byte x0000000

(10)

30

65

Pin 25, (see fig. 14) 7.6 8.2 8.8 V

CC

Low Level

High Level

<

1.6

4.2

Pin 29 7.5 V

= 30mA 0.4 V

OUT

%

%

V

V

9/43

Page 10

STV6886

VERTICAL SECTION

Operating Conditions

Symbol Parameter Test Conditions Min. Typ. Max. Units

R

LOAD

Electrical Characteristics (VCC= 12V, T

Symbol Parameter Test Conditions Min. Typ. Max. Units

VRB Voltage at Ramp Bottom Point Pin 22 2.1 V

VRT Voltage at Ramp Top Point (with Sync) Pin 22 5.1 V

VRTF

VSTD Vertical Sawtooth Discharge Time Pin 22, C

VFRF Vertical Free Running Frequency

ASFR AUTO-SYNC Frequency

RAFD

Rlin Ramp Linearity on Pin 22

VPOS

VOR

VOI

dVS

Ccorr

BRRANG DC Breathing Control Range

BRADj

Note: 11 These parameters are not tested on each unit. They aremeasured during ourinternal qualification procedure.

Note: 12 Set Register 07 at Byte 0xxxxxxx (S correction inhibited) and Register 08 at Byte 0xxxxxxx (C correction

Note: 13 This is the frequency range for which the vertical oscillator will automatically synchronize, using a single

Note: 14 When not used, the DC breathing control pin must be connected to 12V.

Minimum Load for less than 1% Vertical

Amplitude Drift

amb

Voltage at Ramp Top Point (without

Sync)

(12)

(13)

Ramp Amplitude Drift Versus Frequency

at Maximum Vertical Amplitude

(11)

(12)

Pin 20 65 MΩ

=25°C)

Pin 22

= 150nF 70 µs

22

Pin 22, C22= 150nF 100 Hz

C22= 150nF ±5% 50 120 Hz

C22= 150nF

50Hz< f < 120Hz

2.5V < V27< 4.5V 0.5 %

Sub Address 06

Vertical Position Adjustment Voltage (Pin

23 - VOUT mean value)

Byte 00000000

Byte 01000000

Byte 01111111 Tbd

Sub Address 05

Vertical Output Voltage

(peak-to-peak on Pin 23)

Byte 10000000

Byte 11000000

Byte 11111111 Tbd

Vertical Output Maximum Current

(Pin 23)

Max Vertical S-Correction Amplitude (TV

is the vertical period)

(0xxxxxxx inhibits S-CORR

11111111 gives max S-CORR)

Sub Address 07

Byte 11111111

∆V/V

∆V/V

at TV/4

PP

at 3TV/4

PP

Sub Address 08

Vertical C-Corr Amplitude

(0xxxxxxx inhibits C-CORR)

∆V/V

Byte 10000000

Byte 11000000

PP

at TV/2

Byte 11111111

(14)

Vertical Output Variation versus DC

Breathing Control (Pin 23)

V

18

V

18>VREF-V

1V<V18< V

REF-V

inhibited), to obtain a vertical sawtooth with linear shape.

capacitor value on Pin22 and Pin 20, and with a constant ramp amplitude.

VRT-

0.1

200

3.2

3.6

4.0

2.15

3.0

3.9

Tbd V

Tbd V

V

ppm/

Hz

V

V

V

V

±5mA

-3.5

+3.5

-3

0

+3

%

%

%

%

%

112V

0

-2.5

%/V

%/V

10/43

Page 11

STV6886

DYNAMIC FOCUS SECTION

Electrical Characteristics (VCC= 12V, T

Symbol Parameter Test Conditions Min. Typ. Max. Units

HORIZONTAL DYNAMIC FOCUS FUNCTION (seeFigure 15 on page 28)

Horizontal Dynamic Focus Sawtooth

HDFst

HDFdis

HDFstart

HDFDC Bottom DC Output Level R

TDFHD DC Output Voltage Thermal Drift

HDFamp

HDFKeyst

VERTICAL DYNAMIC FOCUS FUNCTION (see Figure 1)

AMPVDF

VDFAMP

VHDFKeyt

Note: 15 S and C correction are inhibited to obtain a linear vertical sawtooth.

Minimum Level

Maximum Level

Horizontal Dynamic Focus Sawtooth

Discharge Width

Internal Phase Advance versus HFLY

middle

(Independent of frequency)

Horizontal Dynamic Focus

Amplitude

Max Byte

Typ Byte

Max Byte

Horizontal Dynamic FocusSymmetry

(For time reference, see Figure 15)

Max Phase Advance

Max Phase Delay

Vertical Dynamic Focus Parabola (added

to horizontal) Amplitude with VAMP and

VPOS Typical

Parabola Amplitude Function of VAMP

(tracking between VAMP and VDF) with

VPOS Typ. (see Figure 1 on page 15,

(15)

)

and

Parabola Asymmetry Function of VPOS

Control (tracking between VPOSand

VDF) with VAMP Max.

B/A Ratio

A/B Ratio

amb

=25°C)

(11)

Pin 9, capacitor on HFOCUSCAP and

C0 = 820pF, T

=20µs

H

2.2

4.9

Triggered by HDFstart 400 ns

1 µs

= 10kΩ, Pin 10 2.1 V

LOAD

200 ppm/C

Sub-Address 03,

Pin 10, fH = 50kHz,

Symmetric Wave Form

x1111111

x1000000

x0000000

1

1.5

3.5

Subaddress 04

x1111111 (decimal 127)

x0000000 (decimal 0)

16

16

Sub-Address 0F

Min Byte x0000000

Typ Byte x1000000

Max Byte x1111111

0

0.5

1

Sub-Address 05

Byte x0000000

Byte x1000000

Byte x1111111

0.6

1

1.5

Sub-Address 06

Byte x0000000

Byte x1111111

0.52

0.52

V

V

V

PP

V

PP

V

PP

%

%

V

PP

V

PP

V

PP

V

PP

V

PP

V

PP

11/43

Page 12

STV6886

GEOMETRY CONTROL SECTION

Electrical Characteristics (VCC= 12V, T

Symbol Parameter Test Conditions Min. Typ. Max. Units

SYMMETRIC CONTROL THROUGH E/W OUTPUT (see Figure 2 on page 15 and Figure 4 on page 15)

VEWM Maximum E/W Output Voltage Pin 24 6.5 V

VEWm Minimum E/W Output Voltage Pin 24 1.8 V

For control of Horizontal size.

DC Output Voltage with:

EW

DC

TDEW

EWpara

EWtrack

KeyAdj

EW Corner

KeyTrack

-E/W Corner inhibited

-Keystone inhibited

DC Output Voltage Thermal Drift See

DC

Parabola Amplitude with:

-VAMP max,

-VPOS typ.,

-Keystone and Corner inhibited

Parabola Amplitude Function of VAMP

Control (tracking between VAMP & E/W):

-VPOS typ.

-E/W Amplitude, Corner & Keystone in-

(17)

hibited

Keystone Adjustment Capability with: -

VPOS typ.

-E/W inhibited,

-Corner inhibited

-Vert. Amplitude max

(17)

(see

and Figure 4)

Corner Adjustment Capability with:

-VPOS typ,

-E/W inhibited

-Keystone inhibited

-Vertical Amplitude max.

Intrinsic Keystone Function of VPOS

Control (tracking between VPOS & E/W):

- E/W Amplitude

-Vertical Amplitude max

-Corner inhibited

B/A Ratio

A/B Ratio

amb

=25°C)

Pin 24, see Figure 2

Subaddress 11

Byte x0000000

Byte x1000000

Byte x1111111

Subaddress 0A

Byte 11111111

Byte 11000000

Byte 10000000

Subaddress 05

Byte 10000000

Byte 11000000

Byte 11111111

Subaddress 09

Byte 10000000

Byte 11111111

Subaddress 10

Byte 11111111

Byte 11000000

Byte 10000000

Subaddress 06

Byte 00000000

Byte 01111111

(16)

2

3.25

4.2

100 ppm/C

1.4

0.7

0

0.2

0.4

0.7

0.4

0.4

+1.25

0

−1.25

0.52

0.52

V

V

V

V

PP

V

PP

V

PP

V

PP

V

PP

V

PP

V

PP

V

PP

V

PP

V

PP

V

PP

12/43

Page 13

STV6886

Symbol Parameter Test Conditions Min. Typ. Max. Units

ASYMMETRIC CONTROL THROUGH INTERNAL DYNAMIC HORIZONTAL PHASE MODULATION (see Figure 3)

Side Pin Balance Parabola Amplitude

(Figure 3) with :

SPBpara

-VAMP max.,

-VPOS typ.

-Parallelogram inhibited

(17 & 18)

Side Pin Balance Parabola Amplitude

function of VAMP Control (tracking be-

SPBtrack

tween VAMP and SPB) with:

-SPB max.,

-VPOS typ.

-Parallelogram inhibited

(17 & 18)

Parallelogram Adjustment Capability

with:

ParAdj

-VAMP max.,

-VPOS typ.

-SPB inhibited

(17 & 18)

Intrinsic Parallelogram Function of VPOS

Control (tracking between VPOSand

DHPC) with :

Partrack

-VAMP max.,

-SPB max.

-Parallelogram inhibited

(17 & 18)

B/A Ratio

A/B Ratio

Note: 16 These parameters arenot tested on each unit. They are measured during our internal qualification procedure.

Note: 17 With Register 07 at Byte 0xxxxxxx (S correction inhibited) and Register 08 at Byte 0xxxxxxx (C correction

inhibited), the sawtooth has a linear shape.

Subaddress 0D

Byte 11111111

Byte 10000000

Subaddress 05

Byte 10000000

Byte 11000000

Byte 11111111

Subaddress 0E

Byte 11111111

Byte 11000000

Subaddress 06

Byte x0000000

Byte x1111111

+2.8

-2.8

1

1.8

2.8

+2.8

-2.8

0.52

0.52

%T

%T

%T

%T

%T

%T

%T

H

H

H

H

H

H

H

MOIRE CANCELLATION SECTION

Electrical Characteristics (VCC= 12V, T

Symbol Parameter Test Conditions Min. Typ. Max. Units

HORIZONTAL AND VERTICAL MOIRE

R

MOIRE

DacOut

HMOIRE

T

HMOIRE

VMOIRE

Note: 18 THis the horizontal period.

Minimum Output Resistor to GND Pin 3 4.7 kΩ

DC Voltage pin 3

DAC configuration

Moiré pulse

(See also Hunlock in 1st PLL section)

H Frequency: Locked

Preferred Scanning/EHT structure

Vertical Moiré

(measured on VOUT: Pin 23)

amb

=25°C)

R

sub-address 02

Byte 00000000

Byte 01000000

Byte 01111111

R

Sub-address 02

Byte 10000000

Byte 11000000

Byte 11111111

Sub-address II:

0xxx xxxx

1xxx xxxx

Sub-address 0C

Byte 11111111 3 mV

MOIRE

MOIRE

=4.7kΩ

0.3

1.1

2.75 3

=4.7kΩ

0

0.8

2.2

Separate

Combined

V

V

V

V

PP

V

PP

V

PP

13/43

Page 14

STV6886

B+ SECTION

Operating Conditions

Symbol Parameter Test Conditions Min. Typ. Max. Units

FeedRes Minimum Feedback Resistor

Electrical Characteristics (VCC= 12V, T

amb

Symbol Parameter Test Conditions Min. Typ. Max. Units

OLG Error Amplifier Open Loop Gain At low frequency

UGBW Unity Gain Bandwidth See

IRI Feedback Input Bias Current

EAOI Error Amplifier Output Current

CSG Current Sense Input Voltage Gain Pin 16 3

MCEth

Max Current Sense Input Threshold Volt-

age

ISI Current Sense Input Bias Current

Tonmax

Maximum ONTimeof the external power

transistor

B+OSV B+Output Saturation Voltage V

IV

REF

V

REFADJ

Internal Reference Voltage

Internal Reference Voltage Adjustment

Range

Threshold for step-up/step-down selec-

PWMSEL

tion (step-up configuration if V

< PWM-

16

SEL)

t

FB+

Fall Time Pin 28 100 ns

Note: 19 These parameters arenot tested on each unit. Theyare measured during our internal qualification procedure

which includes characterization on batches coming from corners of our process and also temperature

characterization.

Note: 20 Tomake soft start possible, 0.5mA are sunk when B+ is disabled.

Note: 21 The external power transistor is OFF during 400ns of the HFOCUSCAP discharge

Resistor between Pins 15

and 14

5kΩ

=25°C)

(19)

(19)

Current sourced by Pin 15

(PNP base)

Current sourced by Pin 14

Current sunk by

(20)

Pin 14

Pin 16 1.3 V

Current sunk by Pin 16

(PNP base)

% of horizontal period,

= 27kHz)

f

o

with I28= 10mA 0.25 V

28

(21)

On error amp (+)

input Subaddress OB:

Byte 1000000

Byte 01111111

Byte 00000000

Pin 16 6 V

85 dB

6MHz

0.2 µA

1.4 mA

2

1 µA

100 %

5V

+20

-20

mA

%

%

14/43

Page 15

Figure 1. Vertical Dynamic Focus Function

Figure 2. E/W Output

STV6886

Figure 3. Dynamic Horizontal Phase Control

Figure 4. Keystone Effect on E/W Output (PCC Inhibited)

15/43

Page 16

STV6886

TYPICAL OUTPUT WAVEFORMS

Function

Sub

Address

Pin Byte Specification Effect on Screen

Vertical Size 05 23

Vertical

Position

06 23

DC Control

V

OUTDC

10000000

V

OUTDC

11111111

00000000 V

01000000 V

01111111 V

0xxxxxxx:

Inhibited

OUTDC

OUTDC

OUTDC

2.15V

3.9V

= 3.2V

= 3.6V

= 4.0V

Vertical

S

Linearity

07 23

11111111

∆V

V

PP

∆V

V

PP

=

3.5%

16/43

Page 17

STV6886

Function

Vertical

C

Linearity

Horizontal

Size

Sub

Address

08 23

11 24

Pin Byte Specification Effect on Screen

0xxxxxxx :

Inhibited

∆V

10000000

11111111

V

PP

DV

=-3%

V

PP

V

PP

DV

=+3%

V

PP

x1111111

4.2V

x0000000

2V

Horizontal

Dynamic

Focus with:

Amplitude

Horizontal

Dynamic

Focus with:

Symmetry

03 10

04 10

X000 0000 —

X111 1111 ---

X000 0000 —

X111 1111 ---

17/43

Page 18

STV6886

Function

Keystone

(Trapezoid)

Control

E/W

(Pin

Cushion)

Control

Sub

Address

09 24

0A 24

Pin Byte Specification Effect on Screen

(E/W + Corner Inhibited)

10000000

11111111

0.4V

0.4V EW

EW

DC

DC

(Keystone + Corner Inhibited)

10000000

11111111

EW

EW

DC

DC

0V

1.4V

(Keystone+ E/W Inhibited)

Corner

Control

Parallel-

ogram

Control

10 24

0E

Internal

11111111

10000000

(SPB

Inhibited)

10000000

11111111

1.25V

EW

EW

1.25V

2.8%T

2.8%T

DC

DC

H

H

18/43

Page 19

STV6886

Function

Side Pin

Balance

Control

Vertical

Dynamic

Focus with

Horizontal

Sub

Address

0D

0F 10

Pin Byte Specification Effect on Screen

(Parallelogram

Inhibited)

2.8%T

2.8%T

H

H

10000000

11111111

X111 1111

2.1V

T

V

X000 0000

2.1V

T

V

0V

19/43

Page 20

STV6886

I2C BUS ADDRESS TABLE

Slave Address (8C): Write Mode

Sub Address Definition

D8 D7 D6 D5 D4 D3 D2 D1

0 0 0 0 0 0 0 0 0 Horizontal Drive Selection/Horizontal Duty Cycle

1 0 0 0 0 0 0 0 1 X-ray Reset/Horizontal Position

2 0 0 0 0 0 0 1 0 Horizontal Moiré/H Lock

3 0 0 0 0 0 0 1 1 Sync. Priority/Horizontal Focus Amplitude

4 0 0 0 0 0 1 0 0 Refresh/Horizontal Focus Symmetry

5 0 0 0 0 0 1 0 1 Vertical Ramp Amplitude

6 0 0 0 0 0 1 1 0 Vertical Position Adjustment

7 0 0 0 0 0 1 1 1 S Correction

8 0 0 0 0 1 0 0 0 C Correction

9 0 0 0 0 1 0 0 1 E/W Keystone

A 0 0 0 0 1 0 1 0 E/W Amplitude

B 0 0 0 0 1 0 1 1 B+ Reference Adjustment

C 0 0 0 0 1 0 0 0 Vertical Moiré

D 0 0 0 0 1 0 0 1 Side Pin Balance

E 0 0 0 0 1 0 1 0 Parallelogram

F 0 0 0 0 1 0 1 1 Vertical Dynamic Focus Amplitude

10 0 0 0 1 0 0 0 0 E/W Corner

11 0 0 0 1 0 0 0 1 H. Moiré Frequency/Horizontal Size Amplitude

Slave Address (8D): Read Mode: No sub address needed.

20/43

Page 21

I2C BUS ADDRESS TABLE (continued)

D8 D7 D6 D5 D4 D3 D2 D1

WRITE MODE

HDrive

00

01

02

03

04

05

06

07

08

09

0A

0B

0C

0D

0E

0, off

[1], on

Xray

1, reset

[0]

HMoiré/HLock

1, on

[0], off

Sync

0, Comp

[1], Sep

Detect

Refresh

[0], off

Vramp

0, off

[1], on

Test V

1, on

[0], off

S Select

1, on

[0]

C Select

1, on

[0]

E/W Key

0, off

[1]

E/W Sel

0, off

[1]

Test H

1, on

[0], off

V. Moiré

1, on

[0]

SPB Sel

0, off

[1]

Parallelo

0, off

[1]

[0] [0] [0] [0] [0] [0] [0]

Horizontal Phase Adjustment

[1] [0] [0] [0] [0] [0] [0]

[0] [0] [0] [0] [0] [0] [0]

[1] [0] [0] [0] [0] [0] [0]

[1] [0] [0] [0] [0] [0] [0]

Vertical Ramp Amplitude Adjustment

[1] [0] [0] [0] [0] [0] [0]

[1] [0] [0] [0] [0] [0] [0]

[1] [0] [0] [0] [0] [0] [0]

[1] [0] [0] [0] [0] [0] [0]

[1] [0] [0] [0] [0] [0] [0]

[1] [0] [0] [0] [0] [0] [0]

[1] [0] [0] [0] [0] [0] [0]

[0] [0] [0] [0] [0] [0] [0]

[1] [0] [0] [0] [0] [0] [0]

[1] [0] [0] [0] [0] [0] [0]

STV6886

Horizontal Duty Cycle

Horizontal Moiré Amplitude

Horizontal Focus Amplitude

Horizontal Focus Symmetry

Vertical Position Adjustment

S Correction

C Correction

E/W Keystone

E/W Amplitude

B + Reference Adjustment

Vertical Moiré Amplitude

Side Pin Balance

Parallelogram

21/43

Page 22

STV6886

D8 D7 D6 D5 D4 D3 D2 D1

Vertical Dynamic Focus Amplitude

E/W Corner

Horizontal Size Amplitude

Polarity Detection Sync Detection

H/V pol

[1], negative

V pol

[1], negative

Vext det

[0], no det

H/V det

[0], no det

1, ignore T

[0], accept all

10

11

scanning/EHT

Hlock

0, on

[1], no

Eq. Pulse

Corner Sel

[0], off

H. Moiré

suited to

1 Combined

[0] Separate

0F

READ MODE

[x] at Power-on Reset value

Data is transferred with vertical sawtooth retrace.

We recommend setting the unspecified bits to [0] in order to ensure compatibility with future devices.

1, on

/2

H

[1] [0] [0] [0] [0] [0] [0]

[1] [0] [0] [0] [0] [0] [0]

[1] [0] [0] [0] [0] [0] [0]

Vlock

0, on

[1], no

Xray

1, on

[0], off

Vdet

[0], no det

22/43

Page 23

OPERATING DESCRIPTION

1 GENERAL CONSIDERATIONS

STV6886

1.1 Power Supply

The typical values of the power supply voltages

VCCand VDDare 12 V and 5 V respectively. Optimum operation is obtained for VCCbetween 10.8

and 13.2 V and VDDbetween 4.5 and 5.5 V.

In order to avoid erratic operation of the circuit during the transientphase of VCC switching on,oroff,

the value of VCCis monitored: if VCCis less than

7.5 V typ.,the outputs of the circuit are inhibited.

Similarly, before VDDreaches 4 V, all the I2C reg-

ister are reset to their default value (see I2CBus

Address Table).

In order to have verygood power supply rejection,

the circuit is internally supplied by several voltage

references (typ. value: 8.2 V). Two of these voltage references are externally accessible, one for

the vertical and one for the horizontal part. They

can be used to bias external circuitry (if I

less than5 mA). It is necessary to filter the voltage

references by externalcapacitorsconnectedtothe

respective grounds, in order to minimize the noise

and consequently the “jitter” on vertical and horizontal output signals.

1.2 I2C Control

STV6886 belongs to the I2C-controlled device

family. Instead of being controlled by DC voltages

on dedicated control pins, each adjustment can be

done via the I2C Interface.

The I2C bus is a serial bus with a clock and a data

input. The general function and the bus protocol

are specified in the Philips-bus data sheets.

The inputs (Data and Clock) are comparators with

a 2.2 V threshold at 5 V supply. Spikes of up to 50

ns are filtered by an integrator and the maximum

clock speed is limited to 400 kHz.

The data line (SDA) can receive or transmit data.

In read-mode the IC sends reply information

(1 byte) to the micro-processor.

The bus protocol prescribes a full-byte transmission in all cases. The first byte after the start condition is used to transmit the IC-address (hexa 8C

for write, 8D for read).

1.3 Write Mode

In write modethesecond byte is thesubaddress of

the selected function to adjust (or controls to affect) and the third byte the corresponding data

byte. Itis possible to send more thanone data byte

to the IC.If after the third byte no stop or start con-

LOAD

is

dition is detected, the circuit increments automatically by one the momentary subaddress in the

subaddress counter (auto-increment mode). So it

is possible to transmit immediately the following

data bytes without sending the IC address or subaddress. This can be useful to reinitialize all the

controls very quickly (flash manner). This procedure can be finished by a stop condition.

The circuit has18adjustmentcapabilities:3for the

horizontal part, 4 for the vertical, 3 for the E/W correction, 2 for the dynamic horizontal phase control,

2 for the vertical and horizontalMoiréoptions,3for

the horizontal andthe verticaldynamicfocus and 1

for the B+ reference adjustment.

18 bits are also dedicated to several controls (ON/

OFF, Horizontal Forced Frequency, Sync Priority,

Detection Refresh and XRAY reset).

1.4 Read Mode

During the read mode the second byte transmits

the reply information.

The reply byte contains the horizontal and vertical

lock/unlock status, the XRAY activation status,

and the horizontalandverticalpolarity detection. It

also contains the sync detection status which is

used by the MCU to assign the sync priority. A

stop condition always stops all the activities of the

bus decoder and switches to high impedance both

the data and clock line (SDA and SCL).

See I2C Bus Address Table.

1.5 Sync Processor

The internal sync processor allows the STV6886

to accept:

– separated horizontal & vertical TTL-compatible

sync signal

– composite horizontal & vertical TTL-compatible

sync signal

1.6 Sync Identification Status

The MCU can read (address read mode: 8D) the

status register via the I2C bus, and then select the

sync priority depending on this status.

Among other data this register indicates the presence of sync pulses on H/HVIN, VSYNCIN and

(when 12 V is supplied) whether a Vext has been

extracted from H/HVIN. Both horizontal and vertical sync are detected even if only 5 V is supplied.

23/43

Page 24

STV6886

In order to choose the right sync priority the MCU

may proceed as follows (see I2C Bus Address Table):

– refresh the status register,

– wait at least for 20ms (Max. vertical period),

– read the status register.

Sync priority choice should be :

Sync

VextdetH/V

detVdet

No Yes Yes 1 Separated H&V

Yes Yes No 0

priority

Subaddress

03 (D8)

Comment

Sync type

Composite TTL

H&V

Of course, when the choice is made, we can refresh the sync detections and verify that the extracted Vsync is present and that no sync type

change has occurred. The sync processor also

gives sync polarity information.

1.7 IC status

The IC can inform the MCU about the 1st horizontal PLL and vertical section status (locked or not)

and about the XRAY protection (activated or

not).Resetting the XRAY internal latch can be

done either by decreasing the VCCsupply or directly resetting it via the I2C interface.

1.8 Sync Inputs

Both H/HVIN and VSYNCIN inputs are TTL compatible triggers with hysteresis to avoid erratic detection. Both inputs include a pull up resistor connected to VDD.

1.9 Sync Processor Output

The sync processor indicates on bit D8 of the status register whether 1st PLL is locked toan incom-

ing horizontal sync. Its level goes to low when

locked. This information is also available onpin 3if

sub-address 02 D8is equal to1.When PLL1 is unlocked, pin 3 output voltage becomes higher than

6V. When it is locked, the HMoiré waveform is

available on pin 3 (max voltage: 3V).

2 HORIZONTAL PART

2.1 Internal Input Conditions

A digital signal (horizontal sync pulse or TTL composite) is sent by the sync processor to the horizontal input. It may be positive or negative (see

Figure 5).

Using internal integration, both signals are recognized if Z/T < 25%.Synchronizationtakes place on

the leading edge of the internal sync signal.

The minimum value of Z is 0.7 µs.

Another integration is able to extract the vertical

pulse from composite syncifthe dutycycleis higher than 25% (typically d = 35%),

(see Figure 6).

Figure 5.

Figure 6.

CSync

Integ.

d

VSyn

The last feature performed is the removal of these

equalization pulses which fall in the middle of a

line, to avoid parasitic pulses on the phase comparator (which would be disturbed by missing or ex-

24/43

traneous pulses). This last feature is switched on/

off by sub-address 0F D8. By default [0], equalization pulses will not be removed.

Page 25

STV6886

2.2 PLL1

The PLL1 consists of a phase comparator, an external filter and a voltage-controlled oscillator

(VCO).The phase comparator is a“phase/frequency” type designed in CMOS technology. This kind

of phase detector avoids locking on wrong frequencies. It is followed by a “charge pump”, composed of two current sources : sunk and sourced

(typically I =1 mA when locked and I = 140 µA

when unlocked). This difference between lock/unlock allows smooth catching of the horizontal frequency by PLL1. This effect is reinforced by an internal original slow down system when PLL1 is

locked, avoiding the horizontal frequency changing too quickly. The dynamic behavior of PLL1 is

fixed byan external filter which integrates the current of the charge pump. A “CRC” filter is generally

used (see Figure 7 on page 25).

Figure 8.

LOCKDET

High

H/HVIN

1

INPUT

INTERFACE

Extracted

VSync

COMP1

Low

Figure 7.

PLL1F

7

1.8kΩ

10nF

The PLL1 is internally inhibited during extracted

vertical sync (if any) to avoid taking in account

missing pulses or wrong pulses on phase comparator. Inhibition is obtained by stopping high and

low signals at the input of the charge pump block

(see Figure 8 on page 25).

ExtractedLock/Unlock

Status VSync

PLL

INHIBITION

CHARGE

PUMP

HPOSITION

PHASE

ADJUST

PLL1F R0 C0

765

VCO

OSC

2

C

I

HPOS

Adj.

Figure 9.

PLL1F

(Loop Filter)

(1.4V<V

7

<4.9V)

7

I

0

I

2

0

R0

4I

0

6

6.4V

1.6V

5

C0

6.4V

1.6V

RS

FLIP FLOP

0 0.875T

H

25/43

Page 26

STV6886

The VCO uses an external RC network. It delivers

a linear sawtooth obtained by the charge and the

discharge of the capacitor, with a current proportional to the current in the resistor. The typical

thresholds of the sawtooth are 1.6 V and 6.4 V.

The control voltage of the VCO is between 1.4 V

and 4.9 V (see Figure 9). The theoretical frequency range of this VCO is in the ratio of 1 to 3.5. The

effective frequency range has to be smaller due to

clamp intervention on the filter lowest value.

The sync frequency must always be higher than

the freerunning frequency. For example, whenusing a sync range between 25 kHz and 80 kHz, the

suggested free running frequency is 22 kHz.

PLL1 ensures the coincidence between the leading edge of the sync signal and a phase reference

REF1 obtained by comparison between the sawtooth of the VCO and an internal DC voltage Vb.

Vb isI2C adjustablebetween 2.9 V and 4.2V (corresponding to ±10 %) (see Figure 10).

The STV6886 also includesa Lock/Unlock identification block which senses in real time whether

PLL1 is locked or not on the incoming horizontal

sync signal. This information is available through

I2C, and also on pin 3 if HLock/Unlock option has

been set through Subaddress 02,D8.

Figure 10. PLL1 Timing Diagram

HO

SC

Sawtooth

7/8 TH

1/8 TH

6.4V

Figure 11. PLL2 Timing Diagram

HOsc

Sawtooth

Flyback

Internally

shaped Flyback

HDrive

7/8T

Ts

Duty Cycle

H

1/8 T

H

6.4V

4.0V

1.6V

The phase comparator of PLL2 is followed by a

charge pump (typical output current: 0.5 mA).

The flyback input consists of an NPN transistor.

The input current mustbe limitedto less than 5 mA

(see Figure 12).

Figure 12. Flyback Input Electrical Diagram

Ref. for H Position

Vb

(2.9V<Vb<4.2V)

1.6V

REF1

HSync

Phase REF1 is obtained by comparison between

the sawtooth and a DC voltage adjustable between

2.9 V and 4.2 V.

The PLL1 ensures the exact coincidence between the

signal phase REF and HSYNC. A ±10% T

adjustment is possible around the 3.5V point.

phase

H

2.3 PLL2

PLL2 ensures a constant position of the shaped

flyback signal in comparison with the sawtooth of

the VCO, taking into account the saturation time

Ts (see Figure 11 on page 26)

26/43

500Ω

HFLY

12

Q1

20kΩ

GND 0V

The duty cycleisadjustable throughI2C from 30 %

to 65 %. For a safe start-up operation, the initial

duty cycle (after power-on reset) is 65% in order to

avoid having too long a conduction period of the

horizontal scanning transistor.

The maximum storage time (Ts Max.) is (0.44THT

/2). Typically, T

FLY

FLY/TH

is around 20 %, at

maximum frequency, which means that Ts max is

around 34 % of TH.

Page 27

STV6886

2.4 Output Section

The H-drive signal is sent to the output through a

shaping stage which also controls the H-drive duty

cycle (I2C adjustable) (see Figure 11). In order to

secure thescanningpower part operation, the output is inhibited in the following cases:

– when VCCor VDDare too low

– when the XRAY protection is activated

– during the Horizontal flyback

– when the HDrive I2C bit control is off.

The output stage consists of a NPN bipolar tran-

sistor. Only the collector is accessible (see

Figure 13).

Figure 13.

This output stage is intended for “reverse” base

control, where setting the output NPN in off-state

will control the power scanning transistor in offstate.

The maximum output current is 30mA, and the

corresponding voltage drop of the output V

0.4V Max.

CEsat

Obviously the powerscanningtransistorcannot be

directly driven by the integrated circuit. An interface has to be added between the circuit and the

power transistor either of bipolar or MOS type.

2.5 X-RAY Protection

The X-Ray protectionis activated by application of

a high level on the X-Rayinput (more than 8.2V on

Pin 25). It inhibits the H-Drive and B+ outputs.

This activation is internally delayed by 2 lines to

avoid erratic detection when short parasitics are

present .

This protection is latched; it may be reset either by

VCCswitch-off or by I2C (see Figure 14 on

page 28).

2.6 Horizontal and Vertical Dynamic Focus

For dynamic focusadjustment,the STV6886 delivers the sum of two signals on pin 10:

– a parabolic waveform at horizontal frequency,

– a parabolic waveform at vertical frequency.

The horizontal parabola comes from a sawtooth in

phase advance with flyback pulse middle. The

phase advance versus horizontal flyback middle is

kept constant versus frequency(about 1µs). Symmetry and amplitude are I2C adjustable (see

Figure 15 on page 28).

The vertical parabola is tracked with VPOS and

VAMP. Its amplitude can be adjusted. It is also affected by S and C corrections.

This positive signal once amplified is to be sent to

the CRT focusing grids.

Because the DC/DC converter is triggered by the

HFocus sawtooth, it is recommended toconnect a

is

capacitor to pin 9, even if HFocus is not needed.

The capacitor value is critical only if Focus is used.

27/43

Page 28

STV6886

Figure 14. Safety Functions Block Diagram

Figure 15. Phase of HFocus Parabola

Flyback pulse

H Focus sawtooth

H Focus parabola

1 µs

0.4 µs

0.6 µs

0.16T

H 0.16T

0.6 µs

0.475T

H

127

2

I

C Code

(decimal)

64

45

0

H

28/43

127

64

45

0

Page 29

STV6886

2.7 Horizontal Moiré Output

The Horizontal Moiré output is intended to correct

a beat between the horizontal video pixel period

and the CRT pixel width.

The Moiré signal is a combination of the horizontal

and vertical frequency signals.

To achieve a Moiré cancellation, the Moiré output

has to be connected so as to modulate the horizontal position. We recommend introducing this

“Horizontal Controlled Jitter” on the ground side of

PLL2 capacitor where this “controlled jitter” will directly affect the horizontal position.

The amplitude of the signal is I2C adjustable. The

H-Moiré frequency can be chosen via the I2C.

If H Scanning and EHT are separated, bit D8 in

subaddress 11 should be set to 0. If H Scanning

and EHT are combined, setting this bit to 1 will provide a better screen aspect.

The H-Moiré output is combined with the PLL1

horizontal unlock output.

If HMoiré/HLock is selected(bit 02D8 to 1):

– when PLL1 is unlocked, pin 3 output voltage

goes above 6V.

– when PLL1 is locked, the HMoiré signal (up to

2.2V peak) is present on pin 3.

If HMoiré/HLockis not selected, pin 3 can be used

as a 0....2.5V DAC.

3 VERTICAL PART

3.1 Function

When the synchronization pulse is not present, an

internal current source sets the free-running frequency. For an external capacitor C

the typical free running frequency is 100Hz.

The typical free running frequency can be calculated by:

fo(Hz) = 1.5.10

-5 .

C

1

OSC

A negative or positive TTL level pulse applied on

Pin 2 (VSYNC) as well as a TTL composite sync

on Pin 1 can synchronize the ramp in the range

[fmin, fmax] (See Figure 16 on page 30). This frequency range depends on the external capacitor

connected on Pin 22. A 150nF (± 5%) capacitor is

recommended for 50Hz to 120Hz applications.

OSC

= 150nF,

If a synchronization pulse is applied, the internal

oscillator is synchronized immediately but with

wrong amplitude. An internal correction then adjusts it in less than half a second. The top value of

the ramp (Pin 22) is sampled on the AGC capacitor (Pin 20) at each clock pulse and a transconductance amplifier modifies the charge current of

the capacitor so as to adjust the amplitude to the

right value.

The Read Status register provides the vertical

Lock-Unlock and the verticalsync polarity information.

We recommend to use an AGC capacitor with low

leakage current. A value lower than 100nA is mandatory.

A good stability of the internal closed loop is

reached with a 470nF ± 5% capacitor value on Pin

20 (VAGC).

3.2 I2C Control Adjustments

S and C correction shapes can then be added to

this ramp. These frequency-independent S and C

corrections are generated internally. Their amplitudes are adjustable by their respective I2C registers. They can also be inhibitedby their select bits.

Finally, the amplitude of this S and C corrected

ramp can be adjusted by the vertical ramp amplitude control register.

The adjusted rampis available onPin 23 (V

drive an external power stage.

OUT

)to

The gain of this stage can be adjusted (± 25%) depending on its register value.

The mean value of this ramp is driven by its own

I2C register (vertical position). Its value is

VPOS = 7/16.V

Usually V

is sent through a resistive divider to

OUT

REF-V

± 400mV.

the inverting input of the booster. Since VPOS derives from V

,the bias voltage sent to thenon-

REF-V

inverting input of the booster should also derive

from V

cation Diagram).

to optimize the accuracy (see Appli-

REF-V

3.3 Vertical Moiré

By using the verticalMoiré,VPOScanbe modulated from frame to frame. This function is intended

to cancel the fringes which appear whenthe line to

line interval is very close to the CRT vertical pitch.

The amplitude of the modulation is controlled by

register VMOIRE on sub-address 0C and can be

switched-off via the control bit D8.

29/43

Page 30

STV6886

Figure 16. AGC Loop Block Diagram

3.4 Basic Equations

In first approximation, the amplitude of the ramp

on Pin 23 (VOUT) is:

V

- VPOS= (V

OUT

OSC-VDCMID

).(1 + 0.3 (V

AMP

where:

V

DCMID

on Pin 22, typically 3.6V)

V

OSC=V22

V

AMP

= 7/16 V

(middle value of the ramp

REF

(ramp with fixed amplitude)

= -1 for minimum vertical amplitude regis-

ter value and +1 for maximum

VPOS is calculated by:

VPOS = V

DCMID

+ 0.4 V

P

where VP= -1 for minimum vertical position register value and +1 for maximum.

The current available on Pin 22 is:

3

I

OSC

where C

.

=

V

REFxCOSC

8

= capacitor connected on Pin 22 and

OSC

xf

f = synchronization frequency.

3.5 Geometric Corrections

The principle is represented in Figure 17 on

page 31.

))

Starting from the vertical ramp, a parabola-shaped

current is generated for E/W correction (also

known as Pin Cushion correction), dynamic horizontal phase control correction, and vertical dynamic focus correction.

The parabola generator ismade byananalogmultiplier, the output current of which is equal to:

DI = k.(V

where V

OUT-VDCMID

is the vertical output ramp (typically

OUT

between 2 and 5V) and V

(for V

=8.2V). TheVOUTsawtoothistypical-

REF-V

2

)

DCMID

is 3.6V

ly centered on 3.6V. By changing the vertical position, the sawtooth shifts by ±0.4V.

To provide good screen geometry for any enduser adjustment, the STV6886 has the “geometry

tracking” feature which automatically adapts the

parabola shape, depending on the vertical position

and size.

30/43

Page 31

STV6886

Due to the large output stage voltage range (E/W

Pin Cushion, Keystone, E/W Corner), the combination of the tracking function, maximum vertical

amplitude, maximum or minimum vertical position

and maximum gain on the DAC control may lead

to output stage saturation. This must be avoided

by limiting the output voltage with appropriate I2C

register values.

For the E/W part and the dynamic horizontal

phase control part, a sawtooth-shaped differential

current in the following form is generated:

∆I’ = k’.(V

OUT

- V

DCMID

)

Then ∆I and ∆I’ are added and converted intovoltage for the E/W part.

Figure 17. Geometric Corrections Principle

Each of the three E/W components or the two dynamic horizontal phase control components may

be inhibited by their own I2C select bit.

The E/W parabola is available on Pin 24 via an

emitter follower output stage which has to be biased by an external resistor (10kΩ to ground). Being stable in temperature, the device can be DC

coupled with external circuitry (mandatory to obtain H Size control).

The vertical dynamic focus is combined with the

horizontal focus on Pin 10.

The dynamic horizontal phase control drives internally the H-position, moving the HFLY position on

the horizontal sawtooth in the range of ± 2.8 %T

both for side pin balance and parallelogram.

H

3.6 E/W

EWOUT = EWDC+K1(V

K2 (V

OUT

- V

DCMID

)2+K3(V

OUT

OUT

- V

DCMID

- V

DCMID

)+

K1 is adjustable by the keystone I2C register.

4

)

K2 is adjustable by the E/W amplitudeI2C register.

K3 is adjustable by the E/W corner I2C register.

31/43

Page 32

STV6886

3.7 Dynamic Horizontal Phase Control

I

OUT

=K4(V

OUT

- V

DCMID

) + K5 (V

OUT

- V

DCMID

2

)

K4 is adjustable by the parallelogram I2C register.

K5 is adjustable by the side pin balance I2C regis-

ter.

4 DC/DC CONVERTER PART

This unit controls the switch-mode DC/DC converter. It converts a DC constant voltage into the

B+ voltage (roughly proportional to the horizontal

frequency) necessary for the horizontal scanning.

This DC/DC converter can be configured either in

step-up or step-down mode. In both cases it operates very similarly to the well known UC3842.

4.1 Step-up Configuration

Operating Description

– The power MOS is switched ON during the fly-

back (at thebeginningof the positiveslope of the

horizontal focus sawtooth).

– The power MOS is switched OFF when its cur-

rent reaches apredetermined value. For this purpose, a sense resistor is inserted in its source.

The voltage on this resistor is sent to Pin16

(I

– The feedback (coming either from the EHV or

from the flyback) is divided to a voltage close to

5.0V and compared to the internal 5.0V reference (I

error amplifier,the output of which controls the

power MOS switch-off current.

Main Features

– Switching synchronized on the horizontal fre-

quency,

– B+ voltage always higher than the DC source,

– Current limited on a pulse-by-pulse basis.

The DC/DC converter is disabled:

– when VCCor VDDare too low,

– when X-Ray protection is latched,

– directly through I2C bus.

When disabled, BOUT is driven to GND by a

0.5mA current source. This feature allows to implement externally a soft start circuit.

SENSE

).

). The difference is amplified by an

VREF

4.2 Step-down Configuration

In step-down configuration, the I

SENSE

information

is not used any more and therefore not sent to the

Pin16. This configuration is selected by connecting this Pin16 to a DC voltage higher than 6V (for

example V

Instead of I

REF-V

SENSE

).

waveform the H-Focus Sawtooth is used for comparison with the amplified error voltage. For that reason, the Step-down configuration can operate only if the H-Focus capacitor

is connected.

Operating Description

– The power MOS is switched ON as for the step-

up configuration.

– Thefeedback tothe error amplifier is done asfor

the step-up configuration.

– ThepowerMOS is switched OFF when the HFO-

CUSCAP voltage gets higher than the error amplifier output voltage.

Main Features

– Switching synchronized on the horizontal fre-

quency,

– B+ voltage always lower than the DC source,

– No current limitation.

4.3 Step-up and Step-down Configuration

Comparison

In step-down configuration the control signal is inverted compared with the step-up mode.This, for

the following reason:

– Instep-up mode, the switch is a N-channel MOS

referenced to ground and made conductive by a

high level on its gate.

– In step-down, a high-side switch is necessary. It

can be either a P- or a N-channel MOS.

• For a P-channel MOS, the gate is controlled

directly from Pin 28 through a capacitor (this

allows to spare a Transformer). In this case,

a negative-going pulse is needed to make

the MOS conductive. Therefore it is

necessary to invert the control signal.

• For a N-channel MOS, a transformer is

needed to control the gate. The polarity of

the transformer can be easily adapted to the

negative-going control pulse.

32/43

Page 33

Figure 18. DC/DC Converter (represented: Step-Up configuration)

DAC

7bits

STV6886

8.2V

EHV

Feedback

± I

adjust

5V ±20%

+

85 dB

-

A

REGIN COMP

15

22kΩ

1MΩ

10nF

Horizontal Dynamic

Focus Sawtooth

V

B+

1.3V

L

1.3V

I

SENSE

1/3

HDF Discharge

400ns

+

C1

-

+

C2

-

+

C3

6V

down

S

Q

R

up

B+Inhibit.

+

-

Command step-up/down

C4

down

up

12V

BOUT

28

STV6886

1614

33/43

Page 34

STV6886

INTERNAL SCHEMATICS

Figure 19.

Pins 1-2

H/HVIN

VSYNCIN

Figure 20.

5V

200Ω

12V

Figure 22.

12V

20 kΩ

CO

5

HREF

13

Figure 23.

R0

HREF

13

12V

6

HREF

13

HMOIRE/HLOCK

Figure 21.

PLL2 4

12V

3

Figure 24.

HREF

13

PLL1F

7

34/43

Page 35

STV6886

Figure 25.

HPOSITION

Figure 26.

HFOCUS

CAP

9

12V

8

HREF

12V

13

HREF

Figure 28.

HFLY

Figure 29.

COMP

HREF

13

12V

12

14

Figure 27.

HFOCUS

10

12V

12V

Figure 30.

REGIN

12V

15

35/43

Page 36

STV6886

Figure 31.

I

16

SENSE

Figure 32.

BREATH

12V

18

12V

Figure 34.

22

VCAP

Figure 35.

VOUT 23

12V

12V

Figure 33.

VAGCCAP

36/43

20

12V

Figure 36.

EWOUT

12V

24

Page 37

Figure 37.

Figure 38.

STV6886

12V

XRAY 25

V12

HOUT-BOUT

Pins 26-28

Figure 39.

Pins 30-31

SDA-SCL

37/43

Page 38

STV6886

Figure 40. Demonstration Board

+12V

CC2

10µF

CC3

47pF

CC1

100nF

VCCTB1

TA1

TA2

1 234 5678

CC4

47pF

+12V

PC2

47kΩ

R35

+12V

10kΩ

C22

J8

33pFR810kΩ

HFLY

J9

DYN

FOCUS

J19

1

2

3

4

CON4

REGIN

I

SENSE

GND

B+OUT

TP8

EHT

COMP

TB2

CDA

10kΩ

PC1

47kΩ

-12V

CDBIBQBQBIB

IA

IA

R10

10kΩ

R25

1kΩ

R24

10kΩ

R73

1MΩR75

R76

47kΩ

QA

C16 (*)

QA

C25

33pF

P1

10kΩ

910111213141516

GND

HOUT

L

47µH

C27

47µF

R51

1kΩ

TP13

TP17

J12

ICC1

MC1 4528

R23

6.49k

C31 4.7µF R36 1.8kΩ

100nF

JP1

C51

R50

100nF

1MΩ

R57

82kΩ

+12V

R74

10kΩ

C60

R77

100nF

15kΩ

J11

C7 22nF

820pF 5%

Ω

C13 10nF

C17 1µF

820pF 5%

HREFC33

TP1

TP16

TP10

C28

1%

C34

C46

1nF

C47

100pF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

IC4

STV6886

H/HVIN

VSYNCIN

SDA

HMOIRE/

SCL

HLOCK

PLL2C

V

C0

B+OUT

GND

R0

PLL1F

HOUT

H

XRAY

POSITION

HFOCUS-

EWOUT

CAP

FOCUS

VOUT

OUT

HGND

V

CAP

HFLY

V

HREF

VAGCCAP

COMP

VGND

REGIN

BREATH

I

B+GND

SENSE

R58

10Ω

J16 J15

+5V

+5V

L1

R39

22µH

C30

100µF

C6

100nF

150nF

470nF

4.7kΩ

C32

100nF

C5

100µF

+12V

R53

1kΩ

C48

10µF

HOUT

C49

100nF

R7 10kΩ

R45 33kΩ

+12V

C12

R52

3.9kΩ

C3

47µF

C15

C2

100nF

Q4

BC557

Q5

BC547

L3

22µH

C50

10µF

32

+5V

31

30

29

CC

28

27

26

25

24

23

22

21

REF

20

19

18

17

J14

12 34

C39

22pF

R29

R42

4.7kΩ

100Ω

C40

22pFR41

100Ω

SCL

SDA

+12V

R56

560kΩ

D2

1N4148

R40

36kΩ

R1

12kΩ

R2

5.6Ω

IC1

TDA817 2

C41

470pF

C4

100nF

C38

C36

1µF

VERTIC AL DEFL ECTION STAGE

13 14 15 16 17 18 19 20 21 22 23 24

PWM4

PWM5

SCL

SDA

RST

GNDRGBTEST

XTALOUT

CKOUT

PXCK

C37

33pF

R15

1kΩ

Q1

BC557Q2BC557

R33

4.7kΩ

C14

470µF

C10

100µF

35V

HSYNC

V

DD

47µF

R17

43kΩ

C1

220nFR31.5Ω

C9

100nF

TP6

TP7

VSYNC

FBLK

+5VC43

R5

5.6Ω

C11220pF

R18

10kΩ

33pF

PWM3

PWM2

+12V

R34

1kΩ

R9

470Ω

D1

1n400 1

-12V

XTALIN

X1

8MHz

R37

27kΩ

C10

470µFC8100nF

C45

10µF

PWM6

PWM7

IC3-STV9422

PWM1

PWM0

123456789101112

R43

10kΩ

C42

1µF

R30

10kΩ

E/W POWER STAGE

R38

R19

2.2Ω

270kΩ

3W

Q3

TIP122

+12V

-12V

TP3

TP4

R11

VYOKE

220Ω

0.5W

R4

1Ω

0.5W

+5V

HOUT

TILT

J13

E/W

J6

J18

J17

R49

22kΩ

J1

J2

J3

1

2

3

38/43

Page 39

Figure 41.

STV6886

39/43

Page 40

STV6886

Figure 42.

40/43

Page 41

PACKAGE MECHANICAL DATA

STV6886

41/43

Page 42

STV6886

PACKAGE MECHANICAL DATA

32 PINS - PLASTIC SHRINK

E

E1

A2

B1B

D

32 17

1

Dimensions

A 3.556 3.759 5.080 0.140 0.148 0.200

A1 0.508 0.020

A2 3.048 3.556 4.572 0.120 0.140 0.180

B 0.356 0.457 0.584 0.014 0.018 0.023

B1 0.762 1.016 1.397 0.030 0.040 0.055

C .203 0.254 0.356 0.008 0.010 0.014

D 27.43 27.94 28.45 1.080 1.100 1.120

E 9.906 10.41 11.05 0.390 0.410 0.435

E1 7.620 8.890 9.398 0.300 0.350 0.370

e 1.778 0.070

eA 10.16 0.400

eB 12.70 0.500

L 2.540 3.048 3.810 0.100 0.120 0.150

Min. Typ. Max. Min. Typ. Max.

Millimeters Inches

e

16

A

A1

L

Stand-off

C

eA

eB

42/43

Page 43

STV6886

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no

responsibility for the consequences of use of such information nor for any infringement of patents or other

rights of third parties which may result from its use. No license is granted by implication or otherwise under any

patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change

without notice. This publication supersedes and replaces all information previously supplied.

STMicroelectronics products are not authorized for use as critical components in life support devices or

systems without express written approval of STMicroelectronics.

The ST logo is a trademark of STMicroelectronics.

2000 STMicroelectronics - All Rights Reserved

Purchase of I

Rights to use these components in a I

2

C Components ofSTMicroelectronics, conveys a license under the Philips I2C Patent.

2

C system, is granted provided that the system conforms to the I2C

Standard Specifications as defined by Philips.

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - FInland - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco The

Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

http://www.st.com

43/43

Loading...

Loading...