Page 1

STU13NB60

N-CHANNEL ENHANCEMENT MODE

PowerMESH MOSFET

PRELIMINARY DATA

TYPE V

DSS

R

DS(on)

I

D

ST U1 3NB60 600 V < 0.45 Ω 12.6 A

■ TYPICALR

■ EXTREMELY HIGH dv/dt CAPABILITY

■ 100% AVALANCHETESTED

■ VERYLOW INTRINSICCAPACITANCES

■ GATECHARGEMINIMIZED

■ ± 30V GATE TO SOURCE VOLTAGERATING

DS(on)

=0.4 Ω

DESCRIPTION

Using the latest high voltage MESH OVERLAY

process, SGS-Thomson has designed an

advanced family of power MOSFETs with

outstanding performances. The new patent

pending strip layout coupled with the Company’s

proprietary edge termination structure, gives the

lowest R

per area, exceptional avalanche

DS(on)

and dv/dt capabilities and unrivalled gate charge

and switching characteristics.

APPLICATIONS

■ SWITCHMODEPOWER SUPPLIES(SMPS)

■ DC-ACCONVERTERS FOR WELDING

EQUIPMENTAND UNINTERRUPTIBLE

POWERSUPPLIESAND MOTORDRIVE

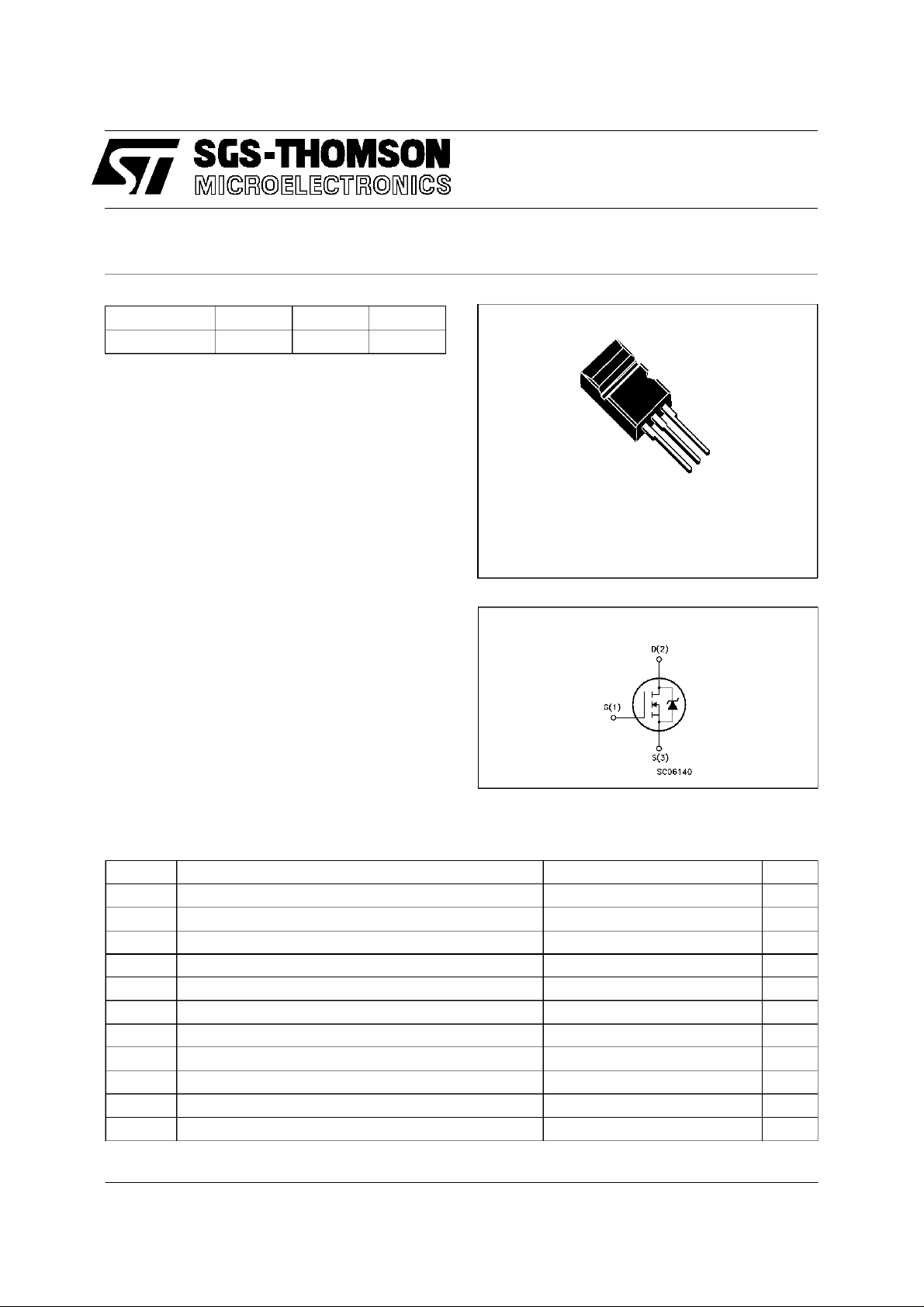

3

2

1

Max220

INTERNAL SCHEMATIC DIAGRAM

ABSOLUTE MAXIMUM RATINGS

Symb o l Para meter Value Uni t

V

V

V

I

DM

P

dv/dt(

T

(•) Pulse width limited by safe operating area (1)ISD≤13A, di/dt ≤ 200 A/µs,VDD≤ V

October 1997

This ispreliminary information on a new productnow in development or undergoing evaluation. Details are subject to changewithout notice.

Drain-source Voltage (VGS=0) 600 V

DS

Drain- gate Voltage (RGS=20kΩ)

DGR

Gat e- source Vo lt age ± 30 V

GS

I

Drain Cur rent (c on t inuous) at Tc=25oC12.6A

D

I

Drain Cur rent (c on t inuous) at Tc=100oC7.9A

D

600 V

(•) Drain Current (pul sed) 50.4 A

Tot al Dissip at ion at Tc=25oC160W

tot

Derating F actor 1.28 W/

1) Peak Diode Rec ov er y vo lt age s l ope 4.5 V/ns

Sto rage Temper ature -65 to 150

stg

T

Max. Operating Ju nct ion T e m peratur e 150

j

,Tj≤T

(BR)DSS

JMAX

o

C

o

C

o

C

1/6

Page 2

STU13NB60

THERMAL DATA

R

thj-case

Rthj-a mb

R

thc-sin k

T

AVALANCHE CHARACTERISTICS

Symbol Para met e r Max Value Uni t

I

AR

E

Ther mal Resist ance Junction- case Max

Ther mal Resist ance Junction- ambient Max

Ther mal Resist ance Case-sink T y p

Maximum Lead Tem per a t u re F o r Soldering Purpos e

l

Avalanche Cur re nt , Repetiti v e or Not-Re petitive

(pulse width limited by T

Single Pulse Avalanche Energy

AS

(starting T

=25oC, ID=IAR,VDD=50V)

j

max, δ <1%)

j

0.78

62.5

0.5

300

12.6 A

800 mJ

o

C/W

oC/W

o

C/W

o

C

ELECTRICAL CHARACTERISTICS (T

=25oC unlessotherwise specified)

case

OFF

Symbol Parameter Test Cond itions Min. Typ . Max. Unit

V

(BR)DSS

I

DSS

I

GSS

Drain-sourc e

Breakdown V oltage

Zer o Gat e V o lt age

Drain Current (V

GS

Gat e-body Leaka ge

Current (V

DS

=0)

=0)

=250µAVGS=0

I

D

o

@100

V

V

V

C

=MaxRating

DS

=MaxRating Tc=125oC

DS

= ± 30 V

GS

600 V

1

50

± 100 nA

ON (∗)

Symbol Parameter Test Cond itions Min. Typ. Max. Unit

V

GS(th )

Gate Threshold

V

DS=VGSID

=250µA

345V

Voltage

R

DS(on)

Stati c D rain-source On

VGS=10V ID=6.3 A 0.4 0.45 Ω

Resistance

I

D(on)

On State Drain Curre nt VDS>I

D(on)xRDS(on)max

12.6 A

VGS=10V

DYNAMIC

Symbol Parameter Test Cond itions Min. Typ. Max. Unit

g

(∗)Forward

fs

Tr ansconductanc e

C

C

C

Input Capac i t an c e

iss

Out put C apa c itance

oss

Reverse Transf er

rss

Capa cit an c e

VDS>I

D(on)xRDS(on)maxID

=6.3 A 6 9 S

VDS=25V f=1MHz VGS= 0 2950

370

33

3840

480

43

µA

µA

pF

pF

pF

2/6

Page 3

STU13NB60

ELECTRICAL CHARACTERISTICS (continued)

SWITCHINGON

Symbol Parameter Test Cond itions Min. Typ. Max. Unit

t

d(on)

Turn-on Time

r

Rise Tim e

t

VDD=300V ID=6.3A

=4.7 Ω VGS=10V

R

G

30

14

(see test circuit, figure 3)

Q

Q

Q

Total Gate Charge

g

Gat e-Sour ce Char ge

gs

Gate-Drain Charge

gd

VDD=480V ID=12. 6 A VGS=10V 65

18

27

SWITCHINGOFF

Symbol Parameter Test Cond itions Min. Typ. Max. Unit

t

r(Voff)

t

t

Of f - voltage Rise Time

Fall Time

f

Cross-ov er Time

c

VDD=480V ID=12.6A

=4.7 Ω VGS=10V

R

G

(see test circuit, figure 5)

21

18

32

SOURCE DRAIN DIODE

Symbol Parameter Test Cond itions Min. Typ. Max. Unit

I

SD

I

SDM

V

SD

t

Q

I

RRM

(∗) Pulsed: Pulse duration =300 µs, duty cycle1.5 %

(•) Pulse width limited by safe operating area

Source-drain Curre nt

(•)

Source-drain Curre nt

(pulsed)

(∗) For ward On Volt age ISD=12.6A VGS=0 1.6 V

Reverse Recov er y

rr

Time

Reverse Recov er y

rr

= 1 2.6 A di/d t = 100 A/µs

I

SD

=100V Tj=150oC

V

DD

(see test circuit, figure 5)

820

9.6

Charge

Reverse Recov er y

23.5

Current

42

20

91 nC

29

25

45

12.6 A

ns

ns

nC

nC

ns

ns

ns

A

ns

µC

A

3/6

Page 4

STU13NB60

Fig. 1: Unclamped InductiveLoad TestCircuit Fig. 2: Unclamped Inductive Waveform

Fig. 3: SwitchingTimesTest CircuitsFor

ResistiveLoad

Fig. 5: Test Circuit For Inductive Load Switching

And Diode RecoveryTimes

Fig. 4: Gate Charge test Circuit

4/6

Page 5

Max220MECHANICAL DATA

STU13NB60

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

A 4.3 4.6 0.169 0.181

A1 2.2 2.4 0.087 0.094

A2 2.9 3.1 0.114 0.122

b 0.7 0.93 0.027 0.036

b1 1.25 1.4 0.049 0.055

b2 1.2 1.38 0.047 0.054

c 0.45 0.6 0.18 0.023

D 15.9 16.3 0.626 0.641

D1 9 9.35 0.354 0.368

D2 0.8 1.2 0.031 0.047

D3 2.8 3.2 0.110 0.126

e 2.44 2.64 0.096 0.104

E 10.05 10.35 0.396 0.407

L 13.2 13.6 0.520 0.535

L1 3 3.4 0.118 0.133

mm inch

D3 D1

D2

C

A

E

A2

A1

D

b1

b2

L1

L

b

e

P011R

5/6

Page 6

STU13NB60

Informationfurnished is believed to be accurate and reliable.However, SGS-THOMSONMicroelectronics assumesno responsabilityfor the

consequencesof use of such informationnor for any infringementof patents or other rightsof third parties which may results fromits use. No

license is granted byimplicationor otherwiseunder anypatentor patentrights ofSGS-THOMSONMicroelectronics.Specificationsmentioned

in this publication are subject tochange without notice.This publicationsupersedesand replaces all informationpreviously supplied.

SGS-THOMSON Microelectronicsproducts arenotauthorizedforuseas criticalcomponentsinlifesupportdevices or systemswithout express

written approvalof SGS-THOMSONMicroelectonics.

1997 SGS-THOMSON Microelectronics -Printed in Italy - All RightsReserved

Australia- Brazil - Canada- China- France - Germany- Hong Kong - Italy- Japan- Korea -Malaysia - Malta - Morocco - The Netherlands-

Singapore - Spain- Sweden - Switzerland- Taiwan - Thailand- UnitedKingdom- U.S.A

SGS-THOMSON MicroelectronicsGROUP OF COMPANIES

...

6/6

Loading...

Loading...