Page 1

INTEGRATED CIRCUITS

74F50729

Synchronizing dual D-type flip-flop with

edge-triggered set and reset with

metastable immune characteristics

Product specification

IC15 Data Handbook

1990 Sep 14

Page 2

Philips Semiconductors Product specification

Synchronizing dual D-type flip-flop with edge-triggered

set and reset and metastable immune characteristics

FEA TURES

•Metastable immune characteristics

•Output skew less than 1.5ns

•High source current (I

applications

= 15mA) ideal for clock driver

OH

•See 74F5074 for synchronizing dual D–type flip–flop

•See 74F50109 for synchronizing dual J–K positive

edge–triggered flip–flop

•See 74F50728 for synchronizing cascaded dual D–type flip–flop

•Industrial temperature range available (–40°C to +85°C)

DESCRIPTION

The 74F50729 is a dual positive edge–triggered D–type featuring

individual data, clock, set and reset inputs; also true and

complementary outputs.

The 74F50729 is designed so that the outputs can never display a

metastable state due to setup and hold time violations. If setup time

and hold time are violated the propagation delays may be extended

beyond the specifications but the outputs will not glitch or display a

metastable state. Typical metastability parameters for the 74F50729

are: τ ≅ 135ps and τ ≅ 9.8 X 10

of the rate at which a latch in a metastable state resolves that

condition and T

represents a function of the measurement of the

o

propensity of a latch to enter a metastable state.

Set (SDn) and reset (RDn) are asynchronous positive–edge

triggered inputs and operate independently of the clock (CPn) input.

Data must be stable just one setup time prior to the low–to–high

transition of the clock for guaranteed propagation delays.

Clock triggering occurs at a voltage level and is not directly related

to the transition time of the positive–going pulse. Following the hold

time interval, data at the Dn input may be changed without affecting

the levels of the output.

6

sec where τ represents a function

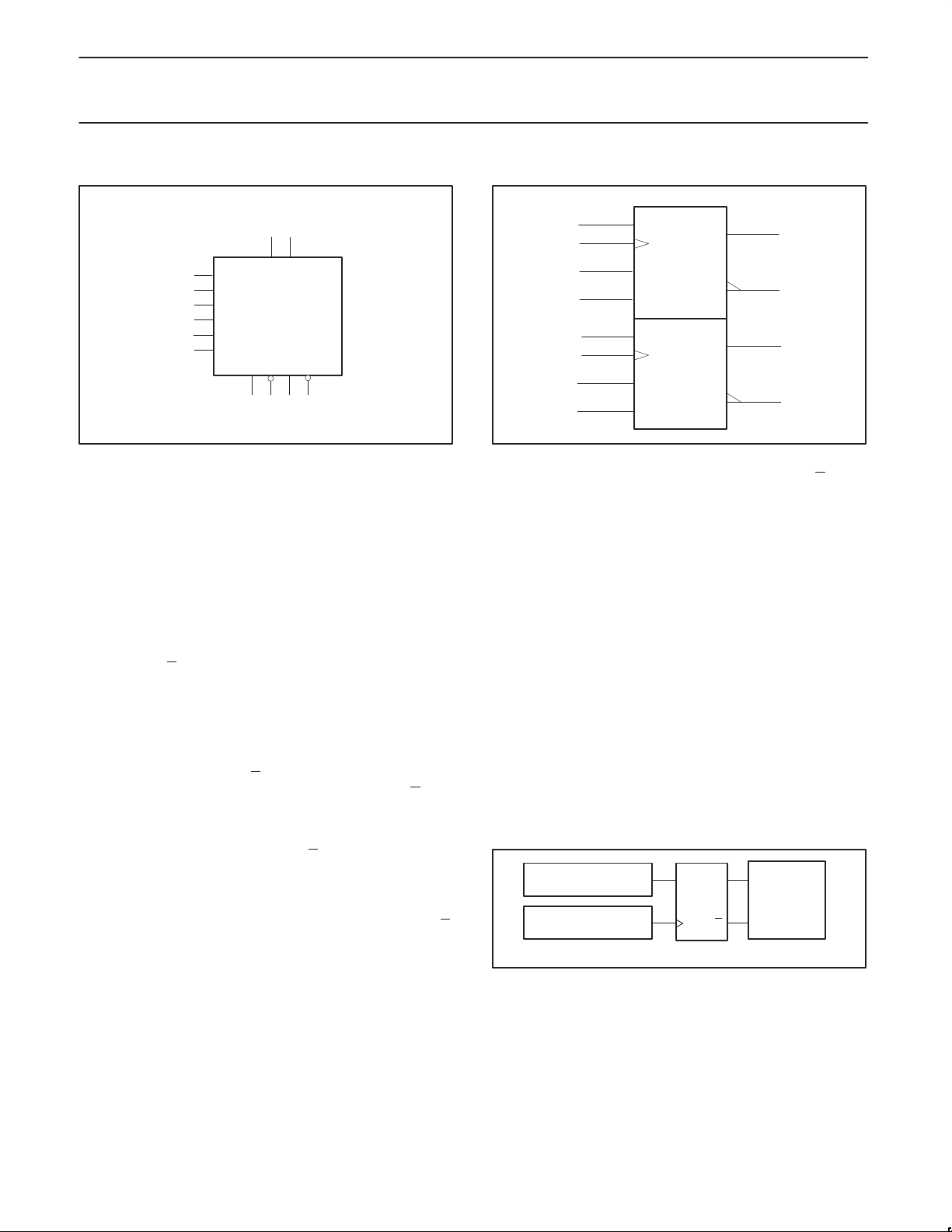

PIN CONFIGURATION

RD0

D0

CP0

SD0

Q0

Q

GND

TYPE TYPICAL f

74F50729 120 MHz 19mA

74F50729

V

MAX

14

CC

13

RD1

D1

12

11

CP1

10

SD1

9

Q1

87

Q1

SF00611

TYPICAL SUPPL Y

CURRENT (TOTAL)

1

2

3

4

5

0

6

ORDERING INFORMATION

ORDER CODE

COMMERCIAL RANGE INDUSTRIAL RANGE

DESCRIPTION

VCC = 5V ±10%, VCC = 5V ±10%,

T

= 0°C to +70°C T

amb

= –40°C to +85°C

amb

PKG DWG #

14–pin plastic DIP N74F50729N I74F50729N SOT27-1

14–pin plastic SO N74F50729D I74F50729D SOT108-1

INPUT AND OUTPUT LOADING AND FAN OUT TABLE

PINS DESCRIPTION

74F (U.L.) HIGH/

LOW

D0, D1 Data inputs 1.0/0.417 20µA/250µA

CP0, CP1 Clock inputs (active rising edge) 1.0/1.0 20µA/20µA

SD0, SD1 Set inputs (active rising edge) 1.0/1.0 20µA/20µA

RD0, RD1 Reset inputs (active rising edge) 1.0/1.0 20µA/20µA

Q0, Q1, Q0, Q1 Data outputs 750/33 15mA/20mA

NOTE: One (1.0) FAST unit load is defined as: 20µA in the high state and 0.6mA in the low state.

1990 Sep 14 853-1390 00420

2

LOAD VALUE HIGH/

LOW

Page 3

Philips Semiconductors Product specification

Synchronizing dual D-type flip-flop with edge-triggered

set and reset and metastable immune characteristics

LOGIC SYMBOL

212

D1D0

Q0 Q0 Q1 Q1

56 98

SF00612

VCC = Pin 14

GND = Pin 7

3

CP0

4

SD0

RD0

1

11

CP1

10

SD1

13

RD1

MET ASTABLE IMMUNE CHARACTERISTICS

Philips Semiconductors uses the term ‘metastable immune’ to

describe characteristics of some of the products in its family.

Specifically the 74F50XXX family presently consist of 4 products

which will not glitch or display metastable immune characteristics.

This term means that the outputs will not glitch or display an output

anomaly under any circumstances including setup and hold time

violations. This claim is easily verified on the 74F5074. By running

two independent signal generators (see Fig. 1) at nearly the same

frequency (in this case 10MHz clock and 10.02 MHz data) the

device–under–test can be often be driven into metastable state. If

the Q output is then used to trigger a digital scope set to infinite

persistence the Q

run by continuously operating the devices in the region where

metastability will occur.

When the device–under–test is a 74F74 (which was not designed

with metastable immune characteristics) the waveform will appear

as in Fig. 2.

Figure 2 shows clearly that the Q

respect to the Q trigger point. This also implies that the Q or Q

output waveshapes may be distorted. This can be verified on an

analog scope with a charge plate CRT. Perhaps of even greater

interest are the dots running along the 3.5V volt line in the upper

right hand quadrant. These show that the Q

state even though the Q output glitched to at least 1.5 volt, the

trigger point of the scope.

When the device–under–test is a metastable immune part, such as

the 74F5074, the waveform will appear as in Fig. 3. The 74F5074 Q

output will appear as in Fig. 3. The 74F5074 Q output will not vary

with respect to the Q trigger point even when the a part is driven into

a metastable state. Any tendency towards internal metastability is

resolved by Philips Semiconductors patented circuitry. If a

metastable event occurs within the flop the only outward

output will build a waveform. An experiment was

output can vary in time with

output did not change

IEC/IEEE SYMBOL

manifestation of the event will be an increased clock–to–Q/Q

propagation delay. This propagation delay is, of course, a function of

the metastability characteristics of the part defined by τ and T

The metastability characteristics of the 74F5074 and related part

types represent state–of–the–art TTL technology.

After determining the T

between failures (MTBF) is simple. Suppose a designer wants to

use the 74F50729 for synchronizing asynchronous data that is

arriving at 10MHz (as measured by a frequency counter), has a

clock frequency of 50MHz, and has decided that he would like to

sample the output of the 74F50729 10 nanoseconds after the clock

edge. He simply plugs his number into the equation below:

MTBF = e

In this formula, fC is the frequency of the clock, fI is the average

input event frequency , and t’ is the time after the clock pulse that the

output is sampled (t’ < h, h being the normal propagation delay). In

this situation the f

because input events consist of both of low and high transitions.

Multiplying f

clear that the MTBF is greater than 10

formula the actual MTBF is 1.51 X 10

(t’/t)

/ TofCf

by fC gives an answer of 10

I

SIGNAL GENERATOR

SIGNAL GENERATOR

74F50729

4

3

2

1

10

11

12

13

and t of the flop, calculating the mean time

0

I

will be twice the data frequency of 20 MHz

I

Figure 1. Test Setup

S

1D

R

S

2D

R

&

C1

C2

DQ

3

6

9

8

SF00613

15

Hz2. From Fig. 3. it is

10

seconds. Using the above

10

seconds or about 480 years.

TRIGGER

DIGITAL

SCOPE

INPUT

SF00586

CP

Q

0.

1990 Sep 14

3

Page 4

Philips Semiconductors Product specification

Synchronizing dual D-type flip-flop with edge-triggered

set and reset and metastable immune characteristics

COMP ARISON OF METASTABLE IMMUNE AND NON–IMMUNE CHARACTERISTICS

4

3

2

1

0

Time base = 2.00ns/div Trigger level = 1.5 Volts Trigger slope = positive

Figure 2. 74F74 Q output triggered by Q output, setup and hold times violated

74F50729

SF00587

3

2

1

0

Time base = 2.00ns/div Trigger level = 1.5 Volts Trigger slope = positive

Figure 3. 74F74 Q output triggered by Q output, setup and hold times violated

SF00588

1990 Sep 14

4

Page 5

Philips Semiconductors Product specification

Synchronizing dual D-type flip-flop with edge-triggered

set and reset and metastable immune characteristics

MEAN TIME BETWEEN FAILURES (MTBF) VERSUS t’

6

MTBF in seconds

10,000 years

100 years

one year

one week

10

10

10

10

10

10

10

8

10

10

12

11

10

9

8

7

6

10

10

10

12

14

10

1015 = fCf

74F50729

I

78910

t’ in nanoseconds

NOTE: VCC = 5V, T

= 25°C, τ =135ps, To = 9.8 X 106 sec

amb

Figure 4.

TYPICAL VALUES FOR τ AND T0 AT VARIOUS VCCS AND TEMPERA TURES

T

= 0°C

amb

V

CC

τ T

0

5.5V 125ps 1.0 X 109 sec 138ps 5.4 X 106 sec 160ps 1.7 X 105 sec

5.0V 115ps 1.3 X 1010 sec 135ps 9.8 X 106 sec 167ps 3.9 X 104 sec

4.5V 115ps 3.4 X 1013 sec 132ps 5.1 X 108 sec 175ps 7.3 X 104 sec

FUNCTION TABLE

INPUTS OUTPUTS OPERATING

SD RD CP D Q Q MODE

↑ ↑ X X H L Asynchronous set

↑ ↑ X X L H Asynchronous reset

↑ ↑ ↑ h H L Load ”1”

↑ ↑ ↑ l L H Load ”0”

↑ ↑ ↑ X NC NC Hold

NOTES:

1. H = High–voltage level

2. h = High–voltage level one setup time prior to low–to–high clock

transition

3. L = Low–voltage level

4. l = Low–voltage level one setup time prior to low–to–high clock

transition

5. NC= No change from the previous setup

6. X = Don’t care

7. ↑ = Low–to–high clock transition

8. ↑

= Not low–to–high clock transition

T

= 25°C

amb

τ T

LOGIC DIAGRAM

4, 10

SD

1, 13

RD

3, 11

CP

2, 12

D

VCC = Pin 14

GND = Pin 7

0

SF00589

τ T

T

= 70°C

amb

0

5, 9

Q

6, 8

Q

SF00614

1990 Sep 14

5

Page 6

Philips Semiconductors Product specification

Synchronizing dual D-type flip-flop with edge-triggered

set and reset and metastable immune characteristics

ABSOLUTE MAXIMUM RATINGS

(Operation beyond the limit set forth in this table may impair the useful life of the device. Unless otherwise noted these limits are over the

operating free air temperature range.)

SYMBOL

V

V

I

IN

V

I

OUT

T

T

CC

IH

OUT

amb

stg

Supply voltage –0.5 to +7.0 V

Input voltage –0.5 to +7.0 V

Input current –30 to +5 mA

Voltage applied to output in high output state –0.5 to V

Current applied to output in low output state 40 mA

Operating free air temperature range Commercial range 0 to +70

Storage temperature range –65 to +150

RECOMMENDED OPERATING CONDITIONS

SYMBOL PARAMETER MIN NOM MAX UNIT

V

V

V

I

I

I

T

CC

IH

IL

Ik

OH

OL

amb

Supply voltage 4.5 5.0 5.5 V

High–level input voltage 2.0 V

Low–level input voltage 0.8 V

Input clamp current –18 mA

High–level output current VCC ± 10% –12 mA

Low–level output current 20 mA

Operating free air temperature range Commercial range 0 +70

PARAMETER RATING UNIT

Industrial range –40 to +85

LIMITS

VCC ± 5% –15 mA

Industrial range –40 +85

74F50729

CC

V

°C

°C

°C

°C

°C

1990 Sep 14

6

Page 7

Philips Semiconductors Product specification

Synchronizing dual D-type flip-flop with edge-triggered

set and reset and metastable immune characteristics

DC ELECTRICAL CHARACTERISTICS

(Over recommended operating free-air temperature range unless otherwise noted.)

SYMBOL

V

OH

V

OL

V

IK

I

I

I

IH

I

IL

I

OS

I

CC

High-level output voltage VCC = MIN, VIH = MIN I

Low-level output voltage

Input clamp voltage VCC = MIN, II = I

Input current at maximum input voltage VCC = MAX, VI = 7.0V 100 µA

High–level input current VCC = MAX, VI = 2.7V 20 µA

Low–level input current Dn VCC = MAX, VI = 0.5V -250 µA

Short–circuit output current

Supply current4 (total) VCC = MAX 19 27 mA

NOTES:

1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type

and function table for operating mode.

2. All typical values are at V

3. Not more than one output should be shorted at a time. For testing I

techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting

of a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any

sequence of parameter tests, I

4. Measure I

with the clock input grounded and all outputs open, then with Q and Q outputs high in turn.

CC

PARAMETER TEST LIMITS UNIT

OH

–15mA

I

OL

1

= MAX

I

=

OH

= MAX

±10%V

±5%V

±5%V

±10%V

±5%V

MIN TY.2MAX

2.5 V

CC

2.7 3.4 V

CC

2.0 V

CC

CC

CC

CONDITIONS

VIL = MAX,

VCC = MIN, VIL =

MAX,

VIH = MIN

IK

CPn, SDn, RDn –20 µA

3

= 5V, T

CC

OS

= 25°C.

amb

tests should be performed last.

VCC = MAX, VO = 2.25V -60 -150 mA

, the use of high-speed test apparatus and/or sample-and-hold

OS

74F50729

0.30 0.50 V

0.30 0.50 V

-0.73 -1.2 V

AC ELECTRICAL CHARACTERISTICS

T

= +25°C T

amb

SYMBOL PARAMETER TEST VCC = +5.0V

CONDITION CL = 50pF,

= 500Ω

R

L

MIN TYP MAX MIN MAX MIN MAX

f

max

t

PLH

t

PHL

t

PLH

t

PHL

t

ok(o)

NOTES:

1. | t

PLH

2. Skew lines are valid only under same conditions (temperature, V

Maximum clock frequency Waveform 1 105 120 85 75 ns

Propagation delay

CPn to Qn or Qn

Propagation delay

SDn RDn to Qn or Qn

Output skew

actual –t

actual | for any one output compared to any other output where N and M are either LH or HL.

PHL

1, 2

Waveform 1

Waveform 2

Waveform 4 1.5 1.5 1.5 ns

2.0

2.0

2.0

3.0

, loading, etc.,).

CC

3.9

3.9

4.0

5.0

LIMITS

amb

+70

= 0°C to

°C

T

amb

VCC = +5.0V ± 10% VCC = +5.0V ± 10%

CL = 50pF,

= 500Ω

R

L

6.0

6.0

6.5

7.5

1.5

2.0

1.5

2.0

6.5

6.5

7.5

8.0

1.5

2.0

1.5

2.0

= –40°C to +85°C

CL = 50pF,

= 500Ω

R

L

7.0

6.5

7.5

8.0

UNIT

ns

ns

1990 Sep 14

7

Page 8

Philips Semiconductors Product specification

Synchronizing dual D-type flip-flop with edge-triggered

set and reset and metastable immune characteristics

AC SETUP REQUIREMENTS

LIMITS

T

= +25°C T

amb

SYMBOL PARAMETER TEST VCC = +5.0V

CONDITION CL = 50pF,

= 500Ω

R

L

MIN TYP MAX MIN MAX MIN MAX

t

(H)

su

t

(L)

su

t

(H)

h

t

(L)

h

t

(H)

w

t

(L)

w

t

(L) SDn, RDn pulse width, low Waveform 3 3.5 4.0 4.0 ns

w

t

rec

t

rec

Setup time, high or low

Dn to CPn

Hold time, high or low

Dn to CPn

CPn pulse width,

high or low

Recovery time

SDn, RDn to CPn

Recovery time

SDn to RDn or RDn to SDn

Waveform 1

Waveform 1

Waveform 2

1.5

1.5

1.0

1.0

3.0

4.0

Waveform 3 6.0 6.5 6.5 ns

Waveform 3 6.0 1.0 1.0 ns

= 0°C to +70°C T

amb

VCC = +5.0V ± 10%

CL = 50pF,

= 500Ω

R

L

2.0

2.0

1.5

1.5

3.5

6.0

amb

VCC = +5.0V ± 10% UNIT

74F50729

= –40°C to +85°C

CL = 50pF,

RL = 500Ω

2.0

2.0

1.5

1.5

3.5

6.0

ns

ns

ns

AC WAVEFORMS

For all waveforms, VM = 1.5V.

The shaded areas indicate when the input is permitted to change for predictable output performance.

Dn

CPn

Qn

Qn

V

M

tsu(L) th(L)

V

M

V

t

t

M

PLH

PHL

tw(H)

V

tsu(H) th(H)

1/f

max

(L)

t

V

M

V

M

V

M

w

V

M

M

V

M

t

PHL

V

M

t

PLH

V

M

SF00049

Waveform 1. Propagation delay for data to output, data setup

time and hold times, and clock width, and

maximum clock frequency

SDn or RDn

CPn

V

M

t

rec

V

M

SF00603

Waveform 3. Recovery time for set or reset to output

SDn

V

M

RDn

Qn

Qn

Waveform 2. Propagation delay for set and reset to output,

Qn, Qn

Qn, Qn

Waveform 4. Output skew

tw(L)

t

PLH

t

PHL

set and reset pulse width

V

M

t

(L)

V

M

w

t

PHL

V

M

t

PLH

V

SF00590

V

M

M

SF00050

V

M

V

M

V

M

V

M

t

sk(o)

1990 Sep 14

8

Page 9

Philips Semiconductors Product specification

Synchronizing dual D-type flip-flop with edge-triggered

set and reset and metastable immune characteristics

TEST CIRCUIT AND WAVEFORMS

V

CC

PULSE

GENERATOR

V

IN

R

T

D.U.T.

V

OUT

R

C

L

L

Test Circuit for Totem-Pole Outputs

DEFINITIONS:

= Load resistor;

R

L

see AC ELECTRICAL CHARACTERISTICS for value.

C

= Load capacitance includes jig and probe capacitance;

L

see AC ELECTRICAL CHARACTERISTICS for value.

R

= Termination resistance should be equal to Z

T

pulse generators.

OUT

of

NEGATIVE

PULSE

POSITIVE

PULSE

family

74F

90%

10%

amplitude

3.0V 1.5V

V

M

10%

90%

V

M

INPUT PULSE REQUIREMENTS

t

w

)

t

THL (tf

t

TLH (tr

)

t

TLH (tr

t

THL (tf

t

w

Input Pulse Definition

V

rep. rate

M

1MHz 500ns

10%

)

)

90%

t

w

V

M

V

M

74F50729

90%

10%

t

TLHtTHL

2.5ns 2.5ns

AMP (V)

0V

AMP (V)

0V

SF00006

1990 Sep 14

9

Page 10

Philips Semiconductors Product specification

Synchronizing dual D-type flip-flop with edge-triggered

set and reset and metastable immune characteristics

DIP14: plastic dual in-line package; 14 leads (300 mil) SOT27-1

74F50729

1990 Sep 14

10

Page 11

Philips Semiconductors Product specification

Synchronizing dual D-type flip-flop with edge-triggered

set and reset and metastable immune characteristics

SO14: plastic small outline package; 14 leads; body width 3.9 mm SOT108-1

74F50729

1990 Sep 14

11

Page 12

Philips Semiconductors Product specification

Synchronizing dual D-type flip-flop with edge-triggered

set and reset and metastable immune characteristics

Data sheet status

Data sheet

status

Objective

specification

Preliminary

specification

Product

specification

Product

status

Development

Qualification

Production

Definition

This data sheet contains the design target or goal specifications for product development.

Specification may change in any manner without notice.

This data sheet contains preliminary data, and supplementary data will be published at a later date.

Philips Semiconductors reserves the right to make chages at any time without notice in order to

improve design and supply the best possible product.

This data sheet contains final specifications. Philips Semiconductors reserves the right to make

changes at any time without notice in order to improve design and supply the best possible product.

[1]

74F50729

[1] Please consult the most recently issued datasheet before initiating or completing a design.

Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For

detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or

at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended

periods may affect device reliability.

Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips

Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or

modification.

Disclaimers

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can

reasonably be expected to result in personal injury . Philips Semiconductors customers using or selling these products for use in such applications

do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard

cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no

responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these

products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless

otherwise specified.

Philips Semiconductors

811 East Arques Avenue

P.O. Box 3409

Sunnyvale, California 94088–3409

Telephone 800-234-7381

Copyright Philips Electronics North America Corporation 1998

All rights reserved. Printed in U.S.A.

print code Date of release: 10-98

Document order number: 9397-750-05216

yyyy mmm dd

12

Loading...

Loading...