CMOS ST-BUS FAMILY

MT8931C

Subscriber Network Interface Circuit

Preliminary Information

Features

• ETS 300-012, CCITT I.430 and ANSI T1.605

S/T interface

• Full-du plex 2B+ D, 19 2 kbi t/s tra nsmi ssio n

• Link acti vation/ deac tivat ion

• D-chann el acce ss cont entio n res olutio n

• Point-to-p oint, point-to- mu ltipo int and st ar

configurat ions

• Master (NT) /Slave (TE) mo des of operati on

• Exceeds lo op len gth re quire ments

• Comple te loopb ack t es ting capa bi lities

• On chip HDLC D-c han nel pro tocol ler

• 8 bit Motorola/Intel microprocessor interface

• Microproc essor-c ontrol led op eration

• Mitel ST-BUS interface

• Low power CM OS tech nolog y

• Single 5 vol t pow er su pply

Applications

• ISDN NT1

• ISDN S or T interf ace

• ISDN Terminal Adaptor (TA)

• Digital sets (TE1) - 4 wire ISDN interface

• Digital PABXs, Digital Line Cards (NT2)

ISSUE 1 May 1995

Ordering Information

MT8931CC 28 Pin Ceramic DIP

MT8931CE 28 Pin Plastic DIP

MT8931CP 44 Pin PLCC

-40°C to +85°C

Description

The MT8931C Subscriber Network Interface Circuit

(SNIC) implements the ETSI ETS 300-012, CCITT

I.430 and ANSI T1.605 Recommendations for the

ISDN S and T reference points. Providing point-topoint and point-to-multipoint digital transmission, the

SNIC may be used at either end of the subscriber

line (NT or TE).

An HDLC D-channel protocoller is included and

controlled through a Motorola/Intel microprocessor

port.

The MT8931C is fabricated in Mitel’s CMOS

process.

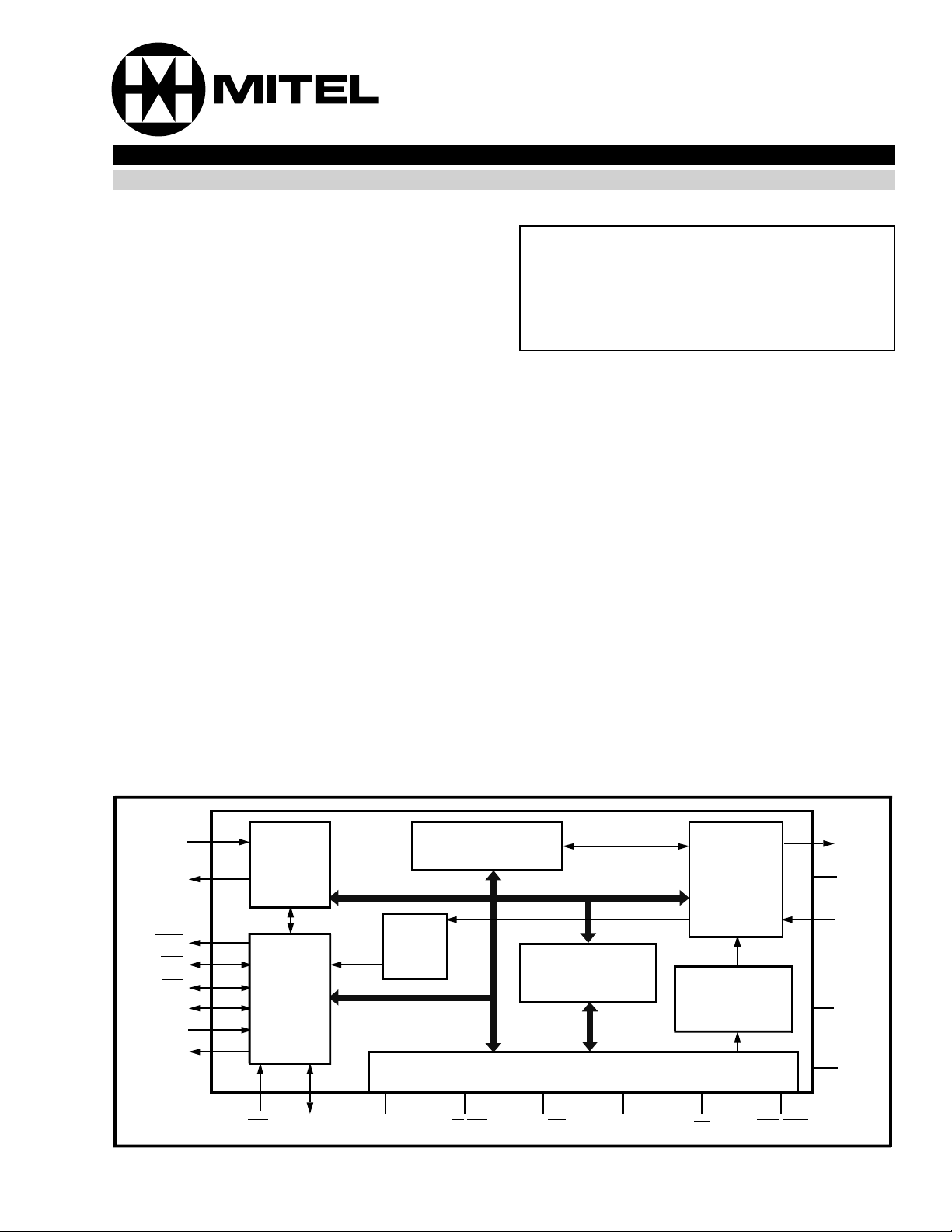

DSTi

DSTo

F0od

C4b

F0b

STAR/Rsto

XTAL1/NT

XTAL2/NC

Rsti

ST-BUS

Interface

Timing

and

Control

HALF AD0-7 R/W/WR DS/RD

D-channel Priority

Mechanism

PLL

Figure 1 - Functional Block Diagram

HDLC

Transceiver

Microprocessor Interface

AS/ALE CS

S-Bus

Link

Interface

Link

Activation

Controller

LTx

VBias

LRx

VDD

VSS

IRQ/NDA

9-73

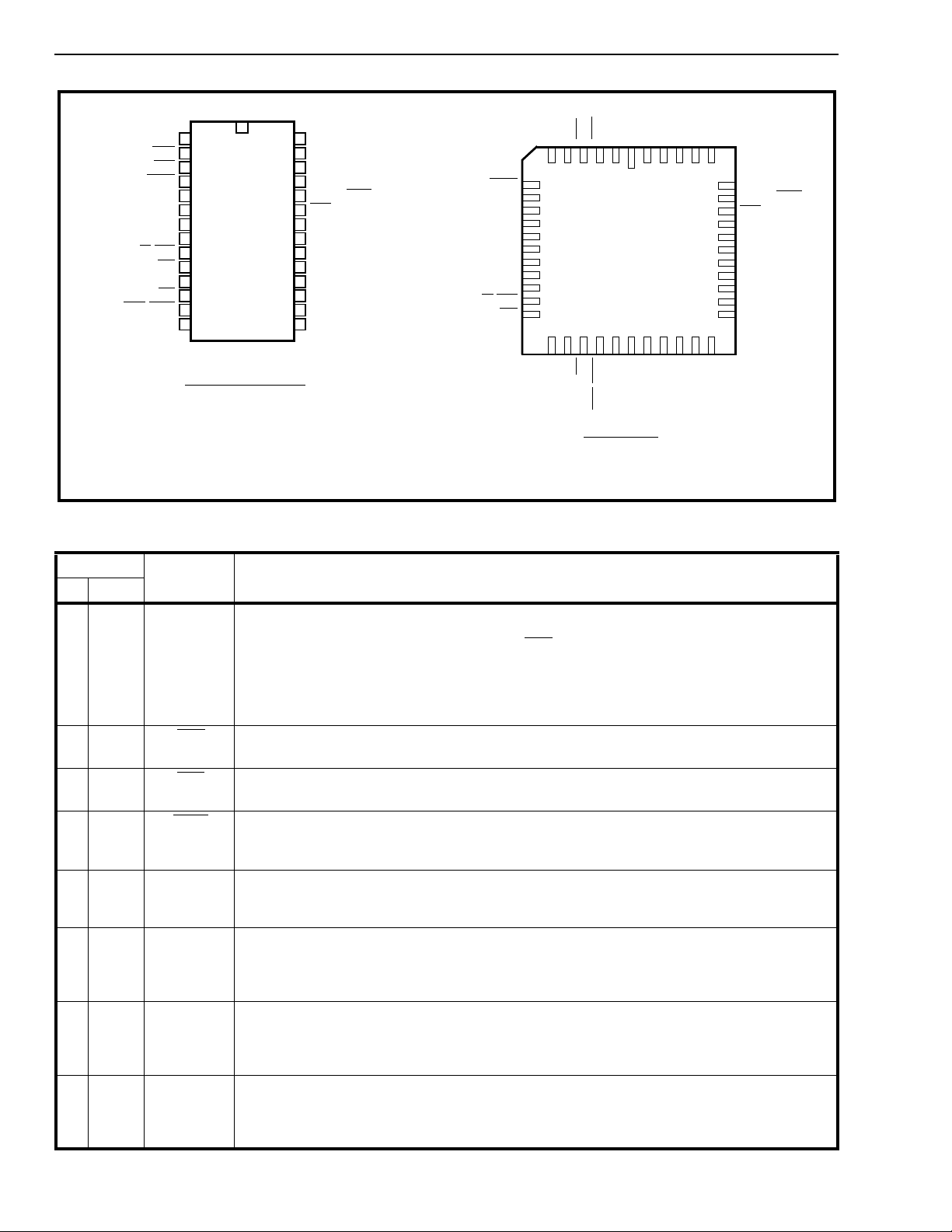

MT8931C Preliminary Information

HALF

C4b

F0b

F0od

DSTi

DSTo

XTAL2/ NC

XTAL1/ N T

/WR

R/W

DS/RD

AS/ALE

CS

IRQ/NDA

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28 PIN PDIP/CERDIP

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VDD

VBias

LTx

LRx

STAR/Rsto

Rsti

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

F0od

DSTi

DSTo

NC

NC

NC

XTAL2/NC

XTAL1/NT

NC

/WR

R/W

DS/RD

NCNCC4b

F0b

65432 44434241

7

8

9

10

11

12

13

14

15

16

17

CS

NC

AS/ALE

44 PIN PLCC

NC

HALF

VDD

1

231819202122 24 25 262728

NC

AD0

VSS

IRQ/NDA

VBias

AD1

LTx

NC

LRx

40

NC

39

STAR/Rsto

38

37

Rsti

NC

36

35

AD7

34

AD6

33

NC

32

AD5

31

AD4

30

AD3

29

NC

NC

NC

AD2

Figure 2 - Pin Connections

Pin Description

Pin #

DIP PLCC

12 HALFHALF Input/O utpu t : this is an input in NT mode and an out put in TE mode ident ifying

Name Description

which half of the S-interface fram e is currently being written/rea d over the ST-BUS

(HALF = 0 sampled on the falling edge of C4b

within the frame pulse low window,

identifies the informa tio n to be transmitted/ received in the first half of the S-Bus frame

while HALF= 1 identifi es the informa tion to be transmitted/ received into the second half

of the S-Bus frame). Tying this pin to V

or VDD in NT mode will allow the device to free

SS

run. This signal can also be accessed from the ST-BUS C-channel.

23 C4b

4.096 MHz Clock: a 4.096 MHz ST-BUS Data Clock input in NT mode.

In TE mode an output 4.096 MHz clock phase-locked to the line data signal.

34 F0b

Frame Pulse: an active low frame pulse inp ut indicating the beginni ng of active STBUS channel time s in NT mode. Fram e pulse outp ut in TE mo de.

47 F0od

Delayed Fram e Pulse Ou tput: an active low delayed frame pulse out put indicat ing

the end of active ST-BUS channels for this device. Can be used to daisy chain

to other ST-BUS devices to share an ST-BUS stream.

58 DSTiData ST-BUS Input: a 2048 kbit/s serial PCM/data ST-BUS input with D, C, B1, and B2

channels assigned to the first four timeslots. These channe ls contain dat a to be

transmitted on the line and chip control informat ion.

69 DSToData ST -BUS Output: a 2048 kbit/s serial PCM/dat a ST-BUS output with D, C, B1 and

B2 channels assigned to the first four timeslots, respectivel y. The remaining timeslots

are placed into high impedance. These channels contain data received from the line

and chip status informati on.

7 13 XTAL2/IC Crystal 2/Internal Connection: in TE mode, XTAL1 and XTAL2 are to be connected to

an external 4.096 MHz parallel resonant crystal for the on-chip oscillator.

If XTAL1 is connected directly to a 4.096 MHz clock, this pin must be left unconnected.

In NT mode, this pin must be left unconnecte d.

8 14 XTAL1/NT Crystal 1/Netwo rk Termination Mode Select Inpu t: for TE mode mode selection, a

4.096 MHz crystal is to be connected between the XTAL1 and XTAL2 pins, or a 4.096

MHz clock can be connected directly to XTAL1. For NT mode selection, this pin must

be tied to VDD. A pull-up resistor is needed when driven by a TTL device.

9-74

Preliminary Information MT8931C

Pin Description (continued)

Pin #

DIP PLCC

916 R/W/WR Read/Write or Write Input: defines the data bus transfer as a read (R/W=1) or a write

10 17 DS/RD

11 19 AS/ALE Address Strobe/Address Latch Enable Input: in Motorola bus mode the falling edge

12 20 CS

13 21 IRQ

14 22 V

15-2224-26,

30-32,

34-35

Name Description

(R/W

=0) in Motorola bus mode. Redefined to WR in Intel bus mode.

Data Strobe/Read Input: active high input indicat es to the SNIC that valid data is on

the bus during a write operatio n or that th e SNIC must output data during a read

operation in Motorola bus mode. Redefined to RD

in Intel bus mode.

is used to strobe the address into the SNIC during microprocessor access. Redefined

to ALE in Intel bus mod e.

Chip Select Input: active low, used to select the SNIC for microprocessor access.

Interrupt Reques t (Open Drai n Outpu t): an outp ut indicati ng an unmasked HDLC

interrupt. The interrupt remains active unti l the microprocessor clears it by reading the

HDLC Interrupt Status Regist er. This interrupt source is enabled with B2=0 of Master

Control Register.

NDA

New Data Available (Open Drain Output): an active low output signal indicating

availabilit y of new data from the S-Bus. This signal is selecte d with B2=1 of Master

Control Register. This pin must be tied to V

SS

Ground .

with a 10kΩ resistor.

DD

AD0-7 Bidirectional Address/Data Bus: electrically and logically compatible to either Intel or

Motorola micro-bus specificat ions. If DS/RD

the chip operates to Motorola specs. If DS/RD

mode is selected. Taking Rsti

low sets Motorola mo de.

is low on the rising edge of AS/ALE then

is high on the rising edge of AS/ALE Intel

23 37 Rsti

Reset Input: Schmitt trigger reset input. If ’0’, sets all control registers to the default

conditions, resets activation stat e machines to the deactivat ed stat e, resets HDLC,

clears the HDLC FIFO‘ s. Sets the micropo rt to M otorol a bus m ode.

24 38 STAR/Rsto

Star/Reset (Open Drain Output): 192kb it/s Rx data outp ut fixed relati ve to the STBUS timebase. A group of NTs, in fixed timing mode, can be wire or’ed toget her to

create a Star configuratio n. Active low rese t output in TE mode indicat ing 128

consecutive marks have been received. Can be connected directly to Rsti

to reset all TEs on the bus. This pin must be tied to V

with a 10 kΩ resistor.

DD

to allow NT

25 40 LRx Receive Line Signal Input: this is a high impedance input for the pseudoternary line

signal to be connected to the line through a 2:1 ratio transformer. See Figures 20 and

21. A DC bias level on this input equal to V

must be maintained.

Bias

26 42 LTx Transmit Line Signal Output: this is a current source output designed to drive a

nominal 50 ohm line through a 2:1 ratio transformer. See Figures 20 and 21.

27 43 V

28 44 V

1,5-6,10-

12,1 5,18,

23,27-

29, 33,

36, 39,

41

Bias

DD

NC No Connection.

Bias Voltage: analog ground for Tx and Rx transformers. This pin must be decoupled

to V

through a 10µF capacitor with good high frequency characteristic s.

DD

Power Sup pl y Input.

9-75

MT8931C Preliminary Information

Functional Description

The MT8931C Subscriber Network Interface Circuit

(SNIC) is a multifunction transceiver providing a

complete interface to the S/T Reference Point as

specified in ETS 300-012, CCITT Recommendation

I.430 and ANSI T1.605. Implementing both

point-to-point and point-to-multipoint voice/data

transmission, the SNIC may be used at either end of

the digital subscriber loop. A programmable digital

interface allows the MT8931C to be configured as a

Network Termination (NT) or as a Terminal

Equipment (TE) device.

The SNIC supports 192 kbit/s (2B+D + overhead) full

duplex data transmission on a 4-wire balanced

transmission line. Transmission capability for both B

and D channels, as well as related timing and

synchronization functions, are provided on chip. The

signalling capability and procedures necessary to

enable customer terminals (TEs) to be activated and

deactivated, form part of the MT8931C’s

functionality. The SNIC handles D-channel resource

allocation and prioritization for access contention

resolution and signalling requirements in passive bus

line configurations. Control and status information

allows implementation of mainten-ance functions

and monitor ing of the dev ice and the subscr iber loop .

An HDLC transceiver is included on the SNIC for link

access protocol handling via the D-channel.

Depacketized data is passed to and from the

transceiver via the microprocessor port. Two 19 byte

deep FIFOs, one for transmit and one for receive,

are provided to buffer the data. The HDLC block can

be set up to transmit or receive to/from either the

S-interface port or the ST-BUS port. Further, the

transmit destination and receive source can be

independently selected, e.g., transmit to S-interface

while receiving from ST-BUS. The transmit and

receive paths can be separately enabled or disabled.

Both, one and two byte address recognition is

supported by the SNIC. A transparent mode allows

data to be passed directly to the D channel without

being packetized.

A block diagram of the MT8931C is shown in Figure

1. The SNIC has three interface ports: a 4-wire

CCITT compatible S/T interface (subscriber loop

interface), a 2048 kbit/s ST-BUS serial port, and a

general purpose parallel microprocessor port. This

8-bit parallel port is compatible with both Motorola or

Intel microprocessor bus signals and timing.

The three major blocks of the MT8931C, consisting

of the system serial interface (ST-BUS), HDLC

transceiver, and the digital subscriber loop interface

(S-interface) are interconnected by high speed data

busses. Data sent to and received from the

S-interface port (B1, B2 and D channels) can be

accessed from either the parallel microprocessor

port or the serial ST-BUS port. This is also true for

SNIC control and status information (C-channel).

Depacketized D-channel information to and from the

HDLC section can only be accessed through the

parallel microprocessor port.

S-Bus Interface

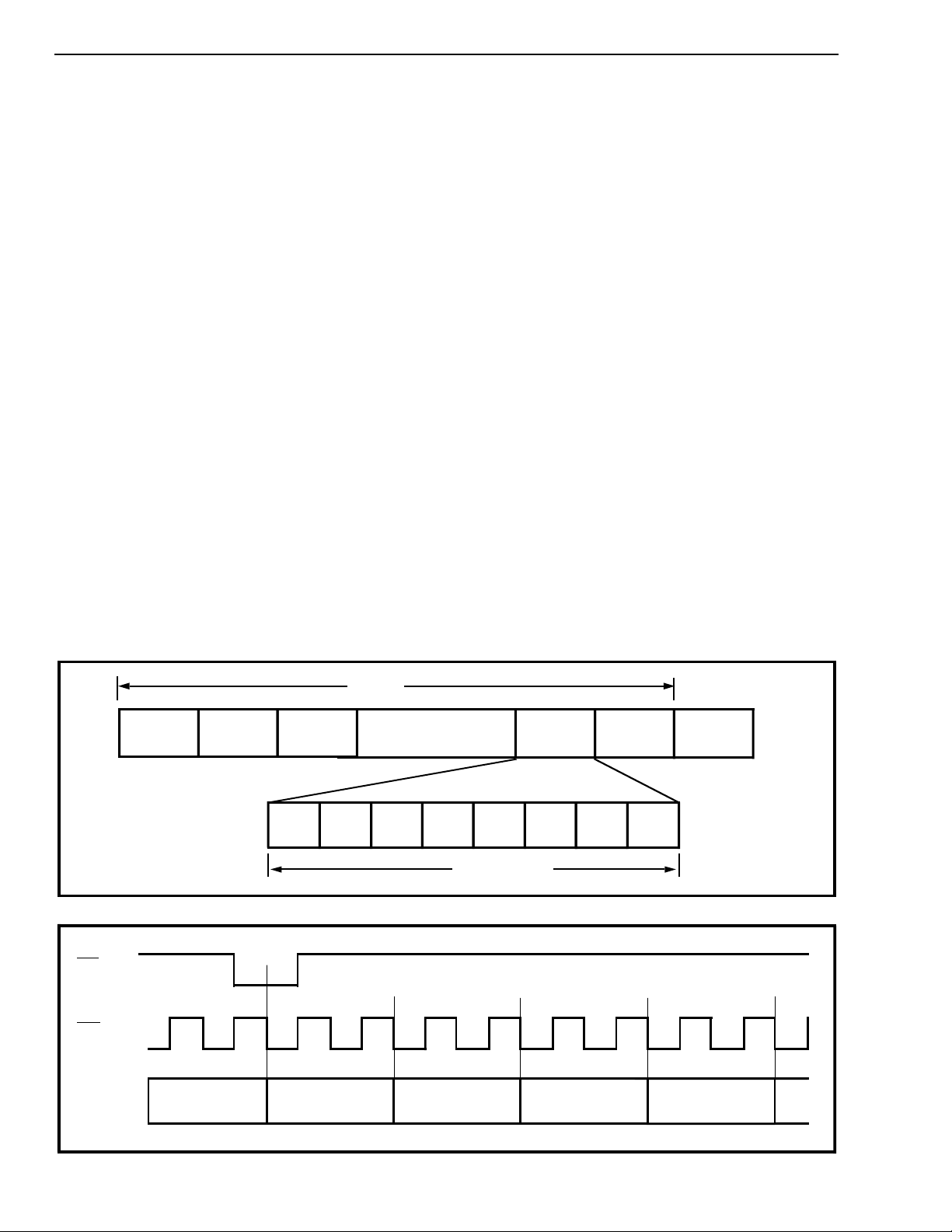

The S-Bus is a four wire, full duplex, time division

multiplexed transmission facility which exchanges

information at 192 kbit/s rate including two 64 kbit/s

PCM voice or data channels, a 16 kbit/s signalling

channel and 48 kbit/s for synchronization and

overhead. The relative position of these channels

with respect to the ST-BUS is shown in Figures 4

and 5.

The SNIC makes use of the first four channels on the

ST-BUS to transmit and receive control/status and

data to and from the S-interface port. These are the

B, D and C-channels (see Figure 4).

9-76

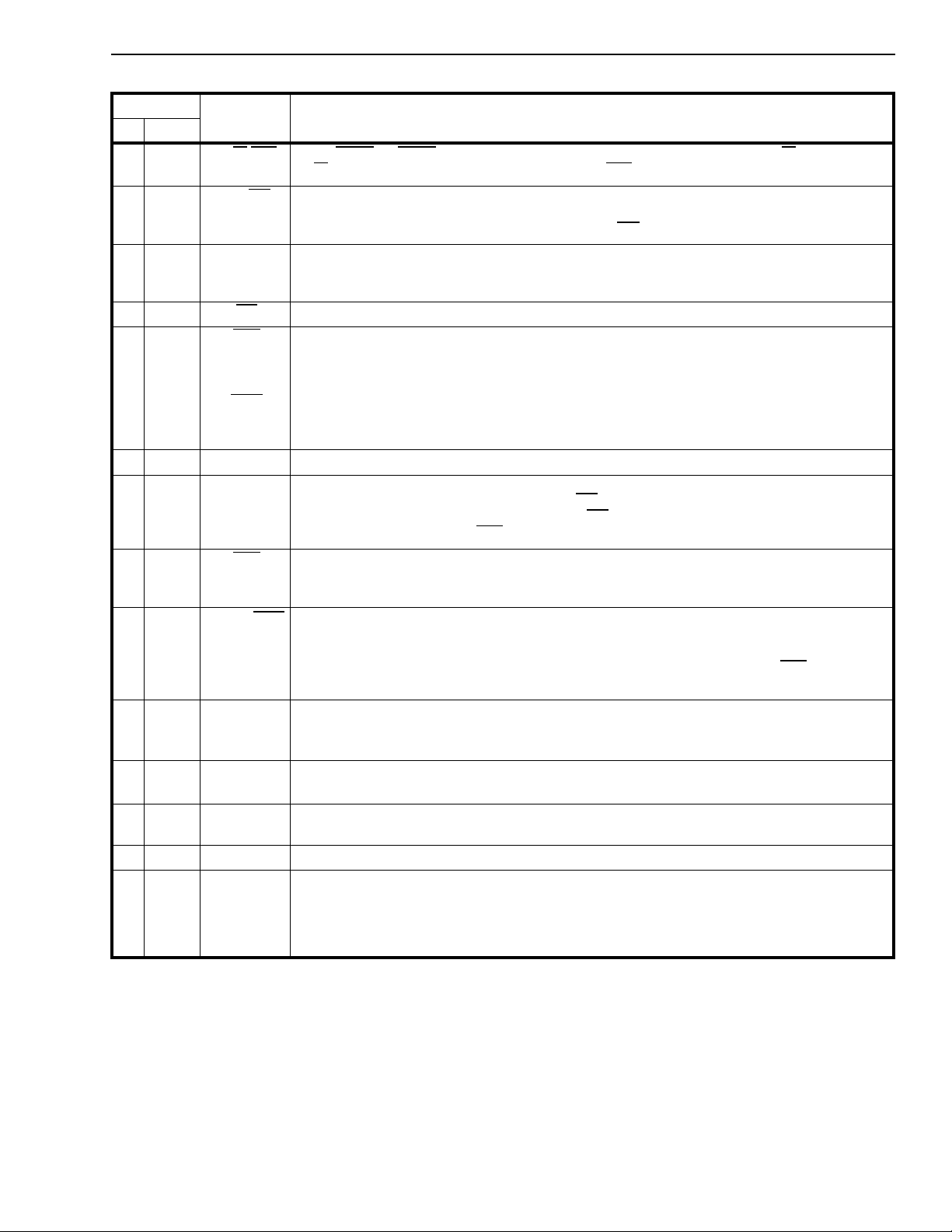

HALF

C4bi

F0bi

F0od

DSTi

DSTo

Cmode

NT

/WR

R/W

DS/RD

AS/ALE

CS

IRQ/NDA

VSS

NT MODE TE MODE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VDD

VBias

LTx

LRx

STAR

Rsti

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

HALF

C4bo

F0bo

F0od

DSTi

DSTo

XTAL2

XTAL1

/WR

R/W

DS/RD

AS/ALE

CS

IRQ/NDA

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Figure 3 - SNI C Pi n Co nn ec tion s

28

27

26

25

24

23

22

21

20

19

18

17

16

15

VDD

VBias

LTx

LRx

Rsto

Rsti

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

Preliminary Information MT8931C

A

A

AAAA

A

A

AAAA

A

A

A

The B1 and B2 channels each have a bandwidth of

AAA

AAA

AAA

AAA

64 kbit/s and are used to carry PCM voice or data

across the network.

The D-channel is primarily intended to carry

signalling information for circuit switching through

the ISDN network. The SNIC provides the capability

of having a 16 kbit/s or full 64 kbit/s D-channel by

allocating the B1-channel timeslot to the D-channel.

Access to the depacketized D-channel is only

granted through the parallel microprocessor port.

The C-channel provides a means for the system to

control and monitor the functionality of the SNIC.

This control/status channel is accessed by the

system through the ST-BUS or microprocessor

port. The C-channel provides access to two

registers which provide complete control over the

state activation machine, the D-channel priority

mechanism as well as the various maintenance

functions. A deta il e d de scr ip ti on o f th es e regis te r s is

discussed in the microprocessor port interface.

AAA

AAA

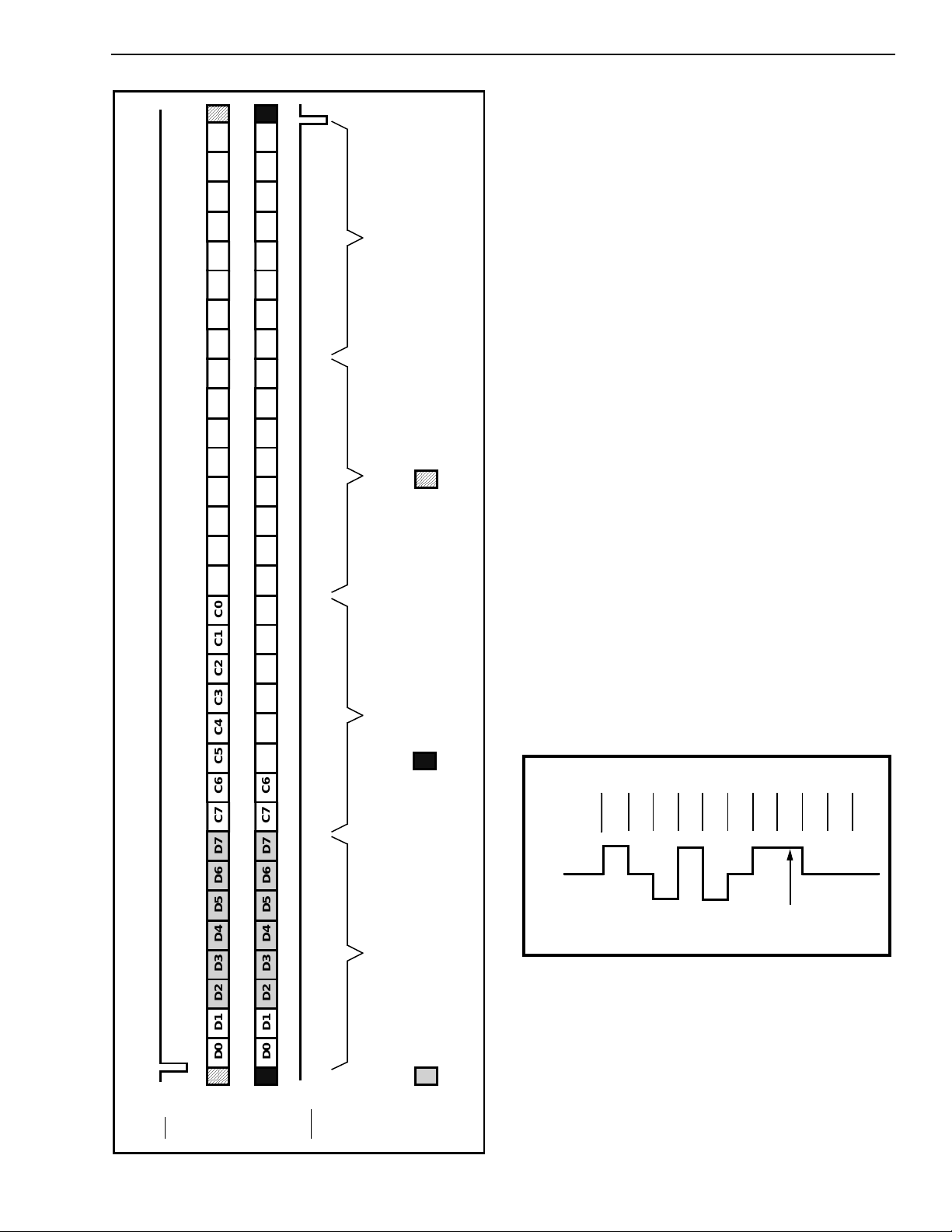

B1 B1 B1 B1 B1 B1 B1 B1 B2 B2 B2 B2 B2 B2 B2 B2

C7 C6 C5 C4 C3 C2 C1 C0

D0 D1 D2 D3 D4 D5 D6 D7

B1 B1 B1 B1 B1 B1 B1 B1 B2 B2 B2 B2 B2 B2 B2 B2

C7 C6 C5 C4 C3 C2 C1 C0

D0 D1 D2 D3 D4 D5 D6 D7

Line Code

The line code used on the S-interface is a Pseudo

ternary code with 100% pulse width as seen in

Figure 5 below. Binary zeros are represented as

marks on the line and successive marks will

alternate in polarity.

Channel 1 (C) Channel 2 (B1) Channel 3 (B2)Channel 0 (D)

BINARY

VALUE

0100010011

LINE

SIGNAL

Violation

Figur e 5 - Alte rn at e Ze ro I nve rsi on L ine Co de

A mark which does not adhere to the alternating

polarity is known as a bipolar violation.

Only val id w ith 64 kbit/s D-channel Output in hig h im pe dance state Don’t car e

F0b

DSTi

DSTo

F0od

Figure 4 - ST-BUS Chan nel Ass ignm ent

9-77

MT8931C Preliminary Information

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

AA

A

A

A

A

A

A

A

B1 B1B1

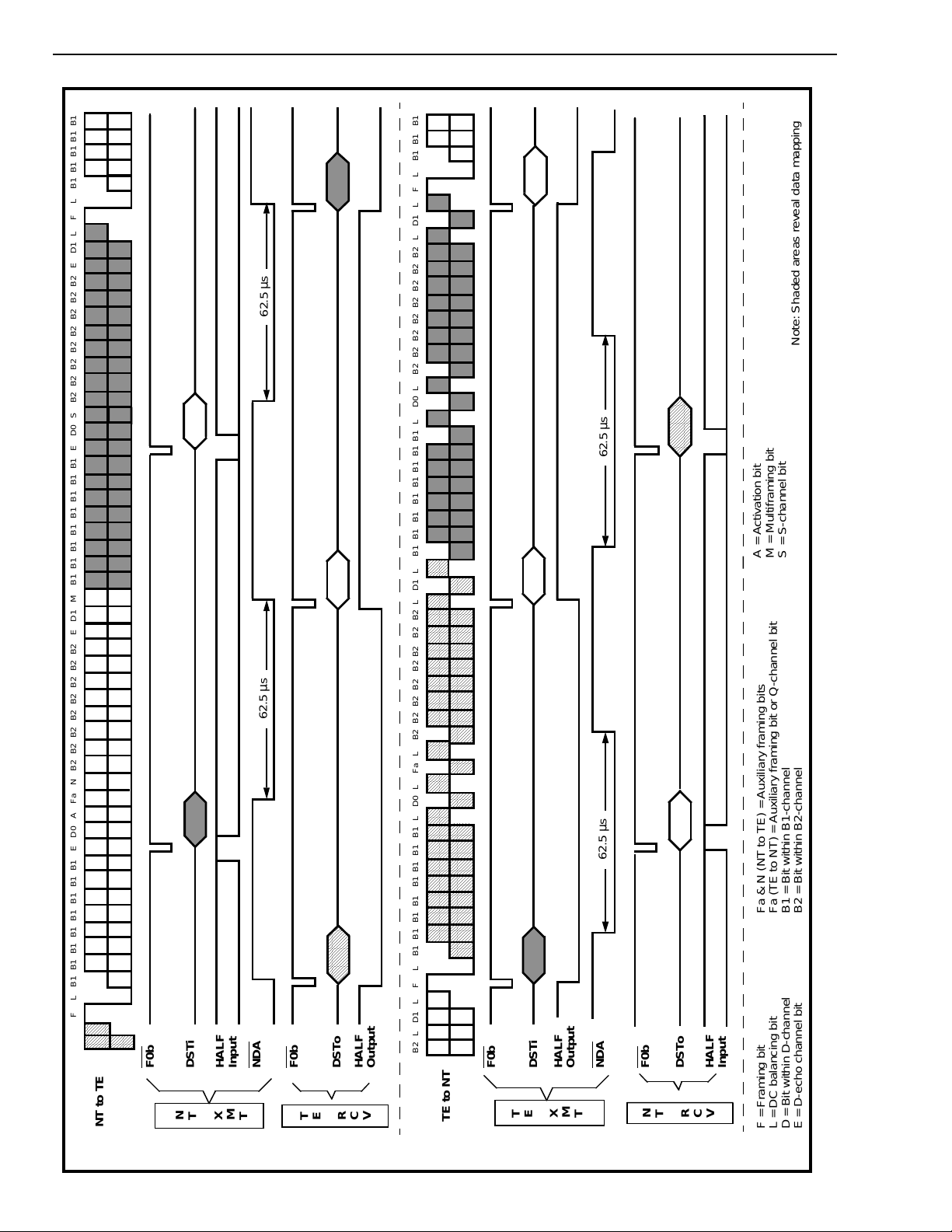

62.5 µs

Note: Shaded areas reveal data mapping

B1

AAA

AAA

AAA

AAA

AAA

B2 L LD1 B1B1 B1B1 B1 B1 B1 L D0 L B2 B2 B2 B2B1 B2 B2 B2 B2 L D1 LB2 L LD1 LFB1B1 B1 B1 B1 B1 B1 L D0 L Fa LB1 B2 B2 B2 B2 B2 B2 B2 FL

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

AAA

B1 B1 B1B1 B1B1 EB1 D0 B2 B2 B2 B2 B2 B2 B2 B2 ES D1 L F L B1 B1FL B1B1 B1B1 B1B1 B1 E D0 A Fa N B2B2B2B2B1 B2 B2 B2 B2 E D1 M B1 B1 B1

62.5 µs

62.5 µs

A = Activation bit

M = Multiframing bit

S = S-channel bit

62.5 µs

Fa & N (NT to TE) = Auxiliary framing bits

Fa (TE to NT) = Auxiliary framing bit or Q-channel bit

Figure 5 - S-Bus Frame Structure and Functional Timing

B1 = Bit within B1 -channel

B2 = Bit within B2 -channel

AAA

AAA

AAA

A

DSTi

TEX

HALF

NDA

F0b

DSTo

HALF

Output

M

T

NTR

Input

V

C

F = Framing bit

L = DC balancing bit

D = Bit within D-channel

E = D-echo channel bit

F0b

NT to TE

9-78

NTX

Input

DSTi

HALF

NDA

F0b

DSTo

HALF

Output

T

M

TER

C

V

F0b

TE to NT

Preliminary Information MT8931C

Fram ing

The valid frame structure transmitted by the NT and

TE contains the following (refer Fig. 6):

NT to TE:

- Framing bit (F)

- B1 and B2 channels (B1,B2)

- DC balancing bits (L)

- D-channel bits (D0, D1)

- Auxiliary framing and N bit (Fa, N), N=Fa

- Activation bit (A)

- D-echo channel bits (E)

- Multiframing bit (M)

- S-channel bit

TE to NT:

- Framing bit (F)

- B1 and B2 channels (B1, B2)

- DC balancing bits (L)

- D-channel bits (D0, D1)

- Auxiliary framing bit (Fa) or Q-channel bit

The framing mechanism on the S-interface makes

use of line code violations to identify frame

boundaries. The F-bit violates the alternating line

code sequence to allow for quick identification of the

frame boundaries. To secure the frame alignment,

the next mark following the frame balancing bit

(L) will also produce a line code violation. If the

data following the balancing bit is all binary ones,

the zero in the auxiliary framing bit (Fa) or N-bit (for

the direction NT to TE) will provide successive

violations to ensure that the 14 bit criterion (13 bit

criterion in the direction TE to NT) specified in

Recommendations I.430 and T1.605 is satisfied. If

the B1-channel is not all binary ones, the first zero

following the L-bit will violate the line code sequence,

thus allowing subsequent marks to alternate without

bipolar violations.

The Fa and N bits can also be used to identify a

multiframe structure (when this is done, the 14 bit

criterion may not be met). This multiframe structure

will make provisions for a low speed signalling

channel to be used in the TE to NT direction

(Q-channel). It will consist of a five frame multiframe

which can be identified by the binary inversion of the

Fa and N-bit on the first frame and consequently on

every fifth frame of the multiframe. Upon detection

of the multiframe signal, the TE will replace the next

Fa-bit to be transmitted w ith th e Q -bi t.

The A-bit is used by the NT during line activation

procedures (refer to state activation diagrams). The

state of the A-bit will advise the TE if the NT has

achieved synchronization.

The E-bit is the D-echo channel. The NT will reflect

the binary value of the received D-channel into the

E-bits. This is used to establish the access

contention resolution in a point-to-multipoint

configuration. This is described in more detail in the

section of the D-channel priority mechanism.

The M-bit is a second level of multiframing which is

used for structuring the Q-bits. The frame with Mbit=1 identifies frame #1 in the twenty frame

multiframe. The Q-channel is then received as

shown in Table 1. All synchronization with the

multiframes must be performed externally.

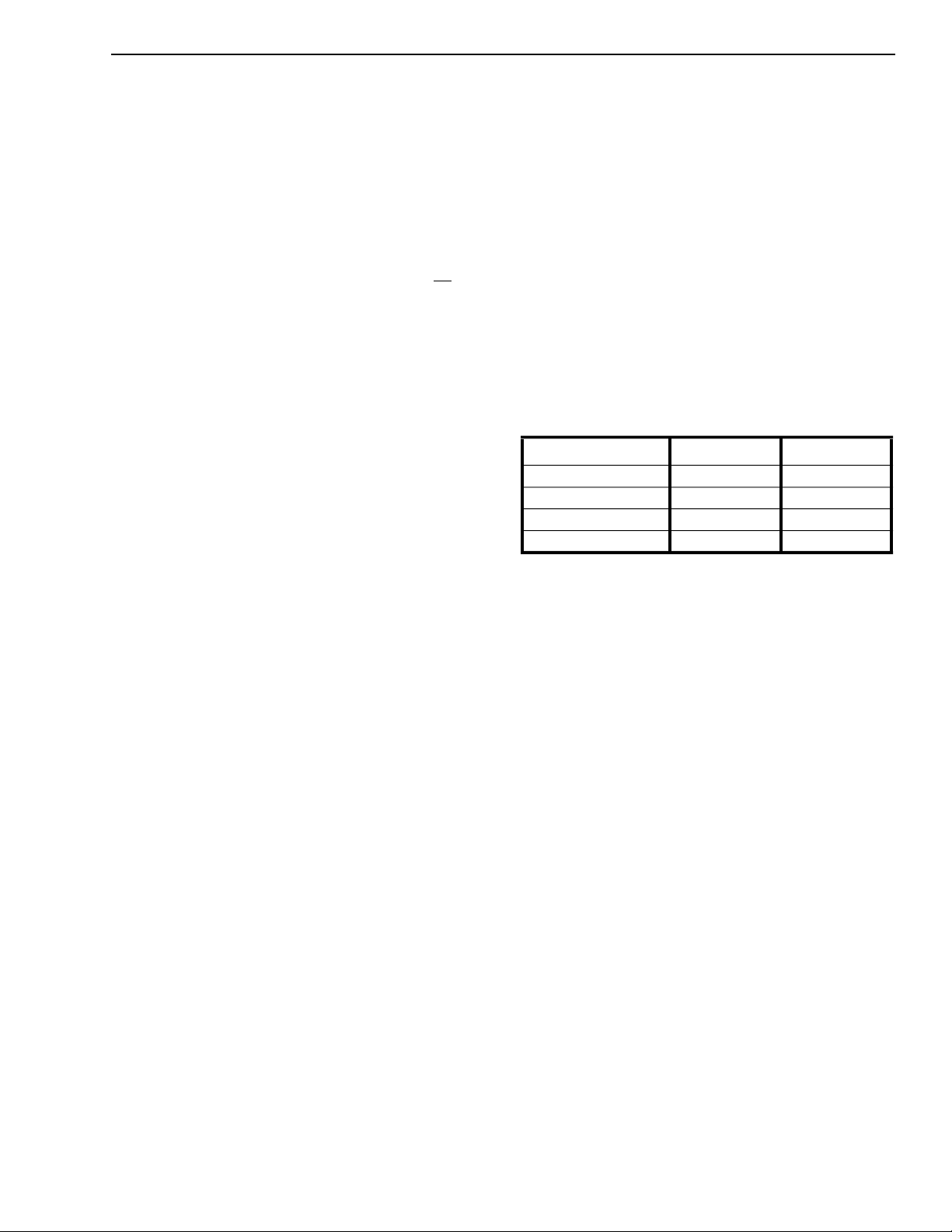

FRAME # Q-BIT M-BIT

1Q11

6Q20

11 Q3 0

16 Q4 0

Table 1. Q-channel Allocation

Bit Order

When using the B-channels for PCM voice, the first

bit to be transmitted on the S-Bus should be the sign

bit. This complies with the existing telecom

standards which transmit PCM voice as most

significa nt b it fir st. However, if the B-c h an n e ls a r e to

carry data, the bit ordering must be reversed to

comply with the existing datacom standards (i.e.,

least significant bit first).

These contradicting standards place a restriction on

all information input and output through the serial

and parallel ports. Information transferred through

the serial ports, will maintain the integrity of the bit

order. Data sent to either serial port from the parallel

port, will transmit the least significant bit first.

Therefore, a PCM byte input through the

microprocessor port must be reordered to have the

sign bit as th e l e a st significant bit.

When the microprocessor reads D, B1 or B2 channel

data of either ST-BUS or S-bus serial port, the least

significant bit read is the first bit received on that

particular channel of either serial port.

The DC balancing bits (L) are used to remove any

DC content from the line. The balancing bit will be a

mark if the number of preceding marks up to the

previous balancing bit is odd. If the number of marks

is even, the L-bit will be a space.

The D-channel received on the serial ST-BUS ports

must be ordered with the least significant bit first as

shown in Figure 4. This also applies to the

D-channel directed to the ST-BUS from the

microprocessor port.

9-79

MT8931C Preliminary Information

The C-channel bit mapping from the parallel port to

the ST-BUS is organized such that the most

significa n t b it i s tra n smitted or rec e ive d fi rs t.

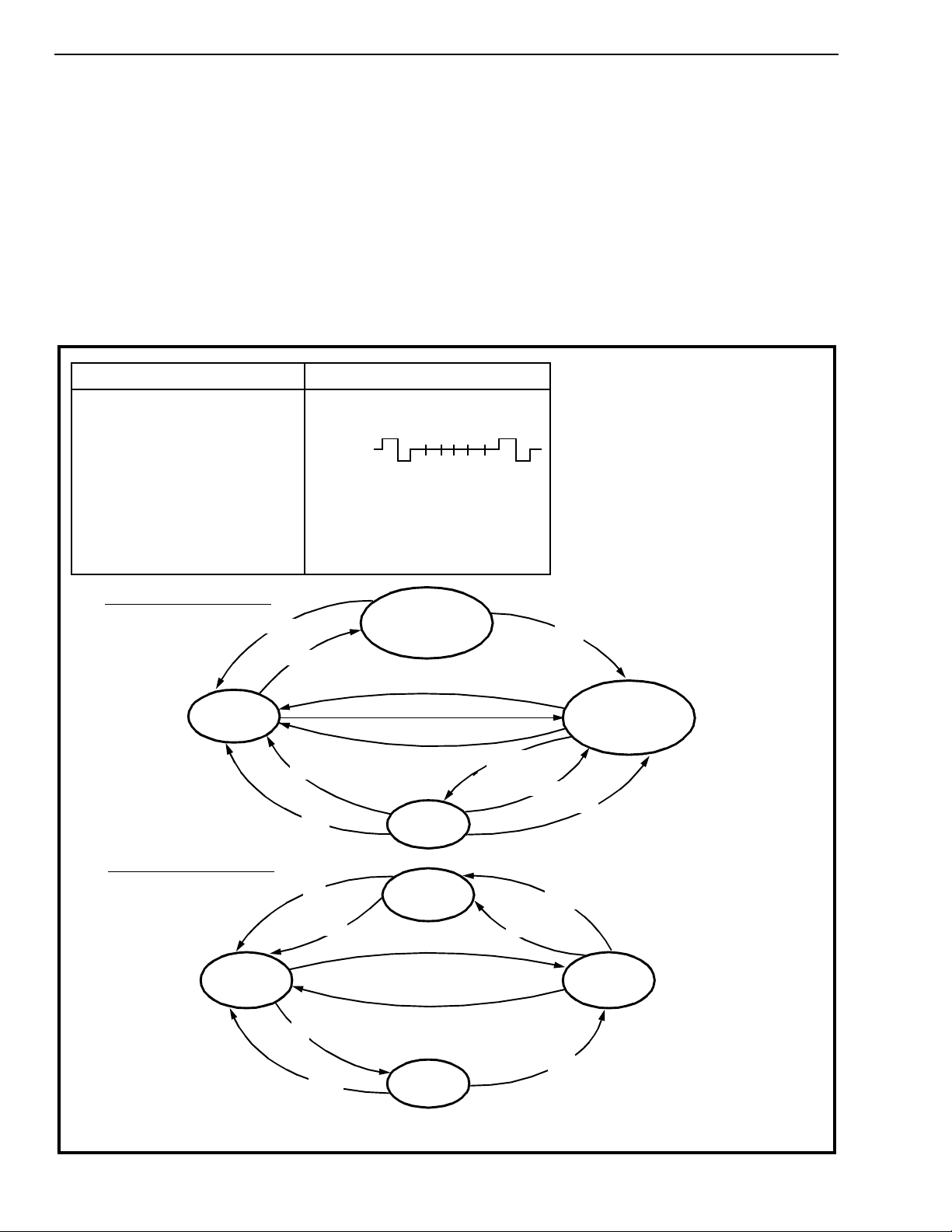

State Activation

The state activation controller activates or

deactivate s the SN IC in response to line activi ty or

external command. The controller is completely

hardware driven and need not be initialized by the

microprocessor. The state diagram for initialization

is shown in Figure 7.

Signals from NT to TE Signals from TE to NT

Info0

Info2

Info4

No Signal

Valid frame structure with

all B, D, D-echo and A bits

set to ‘0’

Valid frame with data in B,

D, D-echo channels. Bit A is

set to 1.

TE State Activati on Diag ram

DR = 1

Info0 No Signal

Info1 Continuous Signal of +‘0’, -‘0’

Info3 Valid frame with data in B & D

AR = 1

and six ‘1’s

Bits

Activation Request

send Info1 if BA = 0

send Info0 if BA = 1

The protocol used by the state activation controller is

defined as follows:

1) In the deactivated state, neither the NT nor TE

assert a signal on the line (Info0).

2) If the TE wa n ts to in i tia te a ctivation, it must begin

transmitting a continuous signal consisting of a

positive zero, a negative zero followed by six

ones (Info1).

3) Once the NT has detected Info1, it begins to

transmit Info2 which c onsists of an S-Bus frame

(2)

Where: BA

(1)

Note 1: signal is not timebase locked to NT.

Note 2: Sync/BA bit of the Status Register

Sync = 1

= Bus Activity

DR = Deactivation Request

AR = Activation Request

(2)

= Frame Sync Signal

Sync

A = Activation bit

Time out = 32 ms Timer Signal

is configured as Sync bit when

AR = 1 and DR = 0, or as BA bit

when AR = 0 or DR = 1. A change in

the state of the AR and/or DR bits

will cause a change in the function

of the Sync/BA bit in the following

ST-BUS frame.

Deactivated

send Info0

NT State Activation Diagram

Pending

Activation

send Info2

DR = 1

BA = 0

BA = 1

AR = 1

Sync = 1

Sync = 0

BA = 0

Sync = 1

DR = 1

Activated

send Info3

Deactivated

send Info0

DR = 1

AR = 1

Activated

send Info4

A = 1 &

Sync = 1

BA =0

Synchronized

send Info3 if Sync = 1

send Info0 if Sync = 0

Sync = 0

A = 0

Time out

Pending

Deactivation

Send Info0

DR = 1

9-80

Figure 7 - Link Activation Protocol, State Diagram

Preliminary Information MT8931C

with zeros in the B and D-channel and the

activation b it (A-bit) set to ze ro .

4) As soon as the TE synchronizes to Info2, it

responds with a valid S-Bus frame with data in

the B1, B2 and D-channel (Info3).

5) The NT will then transmit a valid frame with data

in the B1, B2 and D-channel. It will also set the

activation bit (A) to binary one once

synchroniz a ti on to Info3 is a ch i e ve d .

If the NT wishe s to initi a te th e a ct iva ti o n, step s 2 and

3 are ignored and the NT starts sending Info2. To

initiate a deactivation, either end begins to send

Info0 (Idle li ne) .

D-channel Priority Mechanism

The SNIC contains a hardware priority mechanism

for D-channel contention resolution. All TEs

connected in a point-to-multipoint configuration are

allocated the D-channel using a systematic

approach. Allocation of the D-channel is

accomplished by monitoring the D-echo channel

(E-bit) and incrementing the D-channel priority

counter with every consecutive one echoed back in

the E bit. Any zero found on the D-echo channel will

reset the priority counter.

There are two classes of priority within the SNIC,

one user accessible and the other being strictly

internal. The user accessible priority selects the

class of operation and has precedence over the

internal priority. The latter (internal priority), will

select the leve l of priority within ea ch class (i.e., th e

internal priority is a subsection of the user accessible

priority). User accessible priori ty selects the terminal

count as 8/9 or 10/11 consecutive ones on the E-bit

(8 being high priority while 10 being low priority).

The internal priority selects the terminal between 8

or 9 for high class and 10 or 11 for low class. The

first terminal equipment to attain the E-bit priority

count will immediately take control of the D-channel

by sending the opening flag. If more than one

terminal has the same priority, all but one of them will

eventually detect a collision. The TEs that detect a

collision will immediately stop trans-mitting on the Dchannel, generate an interrupt through the Dcoll bit,

reset the DCack bit on the next frame pulse, and

restart the counting process. The remainder of the

packet in the Tx FIFO is ignored.

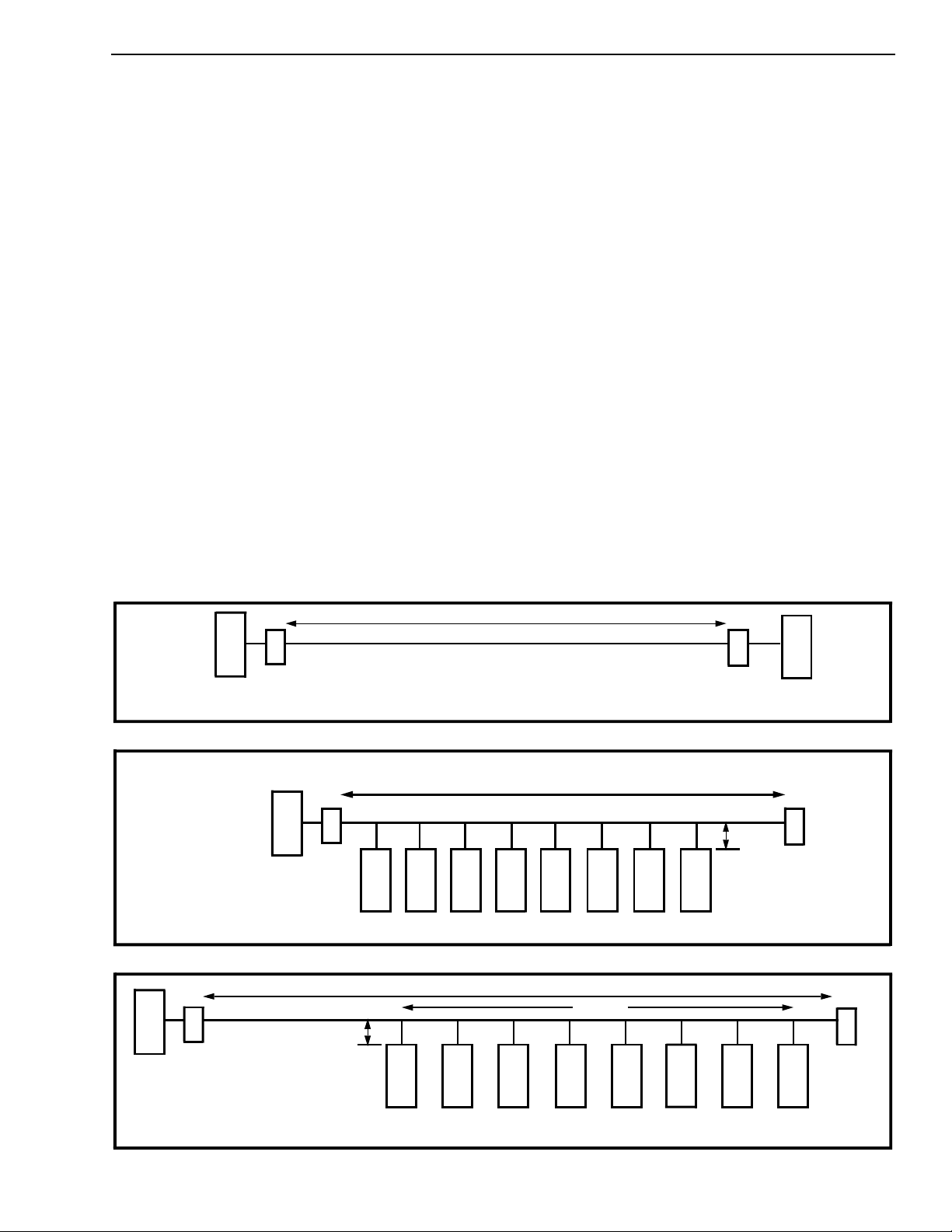

NT

NT is operating in adaptive timing

TR is the line terminat ion re sistor = 100 Ω

NT is operating in fixed timing

TR is the line termination resistor = 100 Ω

T

R

NT

T

R

Figure 9 - Short Passive Bus Configuration, up to 8 TEs can be supported

NT

T

R

0 - 10 m

0 - 1 Km

Figure 8 - Poin t-to-Po int Confi guratio n

100 m for 75 Ω impedance cable and 200 m for 150 Ω impedance cable

TE

TE TE TE TE TE TE TE

100 - 200 m

0-500 m

0-50 m

T

R

0 - 10 m

TE

T

R

T

R

NT is operating in adaptive timing

TR is the line termination resistor = 100 Ω

Figure 10 - Extended Passive Bus Configuration, up to 8 TEs can be supported

TE TE TE TE TE TE TE

TE

9-81

MT8931C Preliminary Information

After successfully completing a transmission, the

internal priority level is reduced from high to low.

The internal priority will only be increased once the

terminal count for the respective level of priority has

been achieved. (e.g., if TE has high priority

internally and externally, it must count 8 consecutive

ones in the D-echo channel. Once this is achieved

and successful transmission has been completed,

the internal priority is reduced to a lower level (i.e.,

count = 9). This terminal will not return to the high

internal priority until 9 consecutive ones have been

monitored on the D-echo channel).

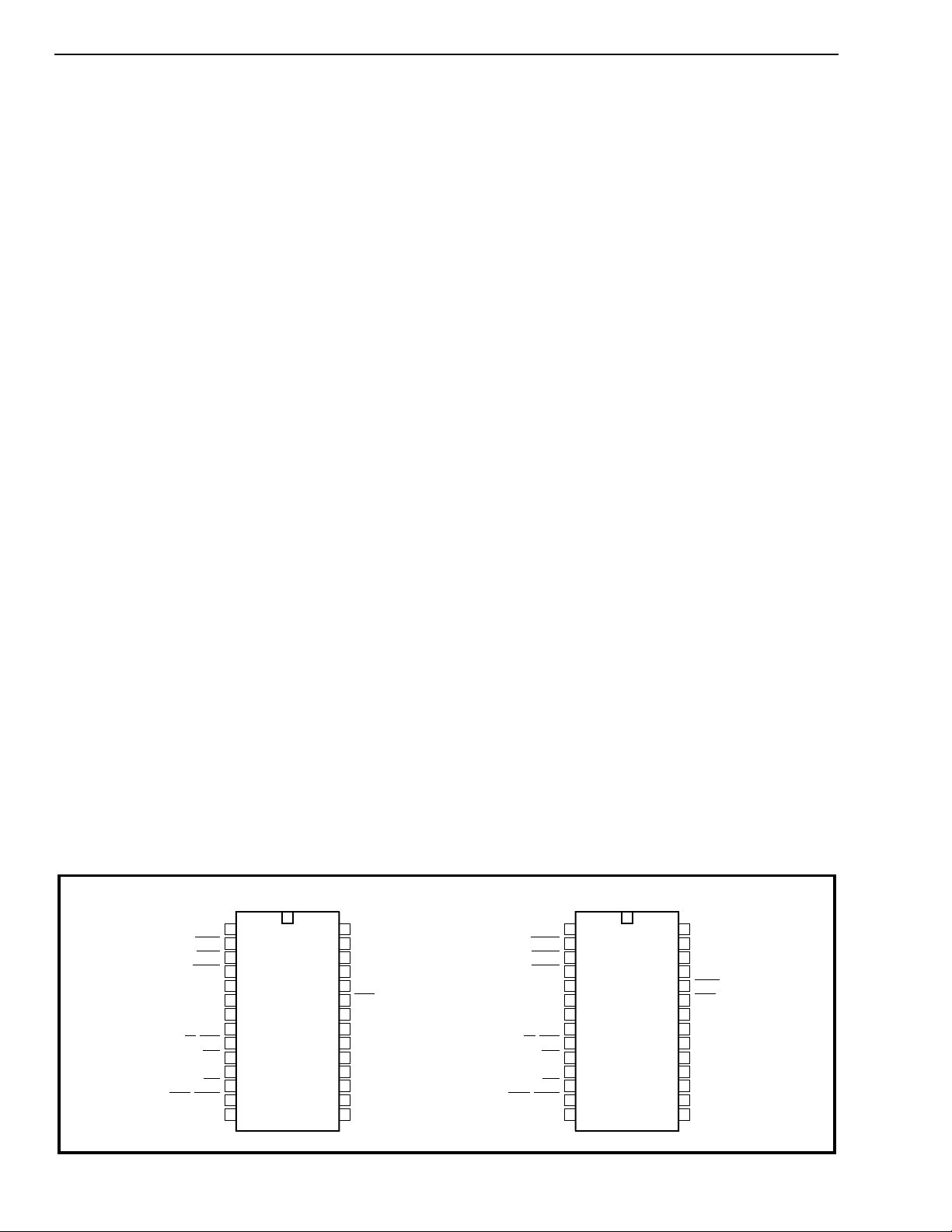

Line Wiring Configuration

The MT8931C can interface to any of the three

wiring configurations which are specified by the

CCITT Recommendation I.430 and ANSI T1.605

(refer to Figures 8 to 10). These consist of a

point-to-point or one of the two point-to- multipoint

configurations (i.e., short passive bus or the

extended passive bus). The selection of line

configurations is performed using the timing bit (B4

of NT Mode Control Register).

For the short passive bus, TE devices are connected

at random points along the cable. However, for the

extended passive bus all connection points are

grouped at the far end of the cable from the NT.

For an NT SNIC in fixed timing mode, the VCO and

Rx filters/peak detectors are disabled and the

threshold voltage is fixed. However, for a TE SNIC

or an NT SNIC (in adaptive timing mode), the VCO

and Rx filters/peak detectors are enabled. In this

manner, the device can compensate for variable

round trip delays and line attenuation using a

threshold voltage set to a fixed percentage of the

pulse peak amplitude.

Another operation can be implemented using the

SNIC in the star configuration as shown in Figure 14.

This mode allows multiple NTs, with physically

independent S-Busses, to share a common input

source and transfer information down the S-Bus to

all TEs . All NT devices connected into the star will

receive the information transmitted by all TEs on all

branches of the star, exactly as if they were on the

same physical S-Bus. All NTs in the star

configuration must be operating in fixed timing mode.

Refer to the description of the star configuration in

the ST-BUS section.

The SNIC has one last mode of operation called the

NT slave mode. This has the effect of operating the

SNIC in network termination mode (XTAL1/NT pin =

1) but having the frame structure and registers

description defined by the TE mode. This can be

used where multiple subscriber loops must carry a

fixed phase relation between each line. A typical

F0b

C4b

ST-BUS

BIT CELLS

Channel0Channel

1

Channel 31

Bit 0

125 µs

Channel

2

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

•••

(8/2048) ms

Channel30Channel31Channel

Figure 11 - ST-BUS Stream Format

Channel 0

Bit 7

Channel 0

Bit 6

Channel 0

Bit 5

0

Channel 0

Bit 4

9-82

Figure 12 - Cloc k & Fram e Alignm ent for ST-BUS Stream s

Preliminary Information MT8931C

situation is when the system is trying to synchronize

two nodes of a synchronous network. This allows

multiple TEs to share a common ST-BUS timebase.

The synchronization of the loops is established by

using the clock signals produced by a local TE as an

input timi ng source to the N T s l ave .

Adaptive Tim in g Operation

On power-up or after a reset, the SNIC in NT mode is

set to operate in fixed timing. To switch to adaptive

timing, the user should:

1) set the DR b it to 1

2) set the Timing bit to 1 in the C-channel

Control Register

3) wait for 100 ms period

4) proceed in using the AR and DR bits as

desired

Switching from adaptive timing mode is completed

by resetting the Timing bit.

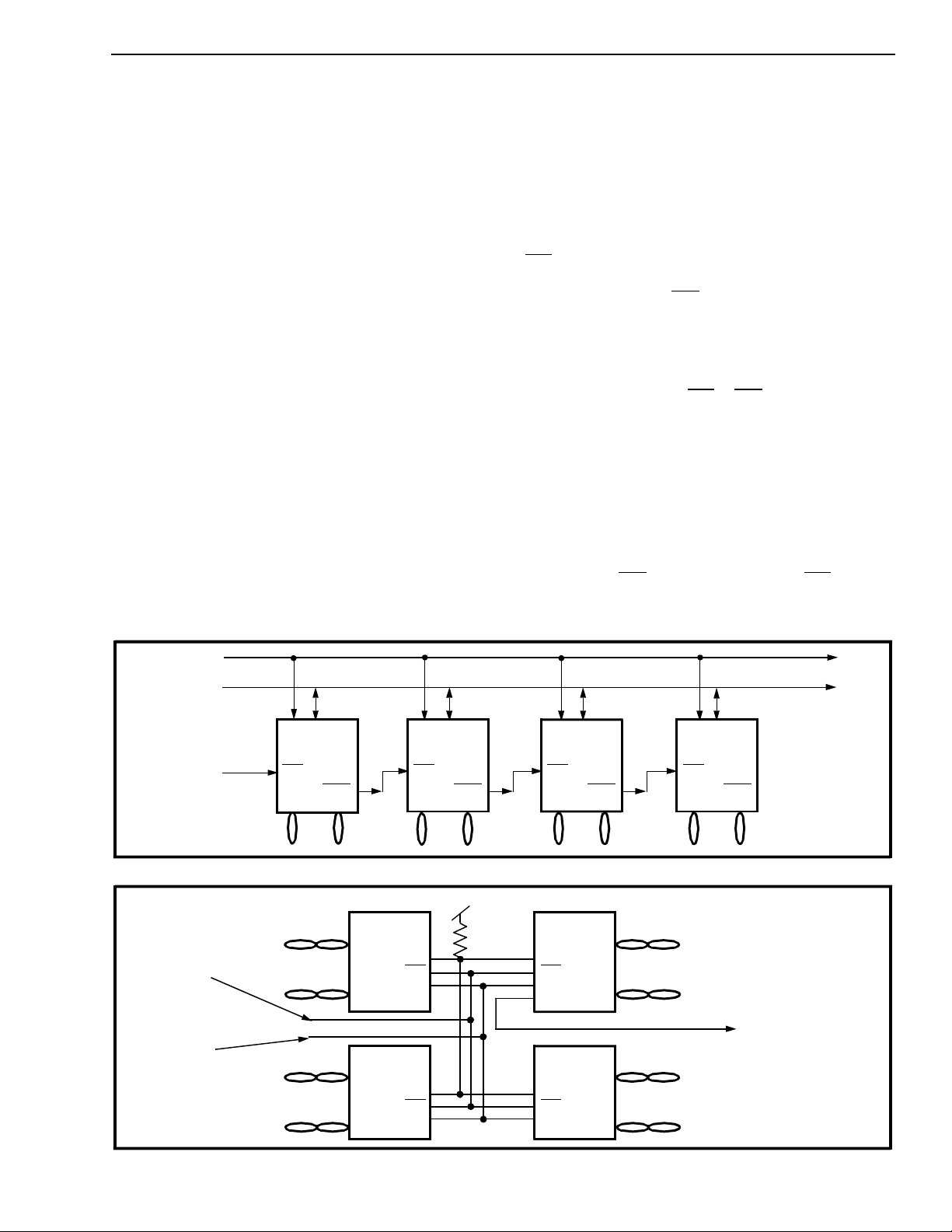

ST-BUS Interface

The ST-BUS is a synchronous time division

multiplexed serial bussing scheme with data streams

operating at 2048 kbit/s configured as 32, 64 kbit/s

channels (refer to Fig. 11). Synchroni-zation of the

data transfer is provided from a frame pulse which

identifies the frame boundaries and repeats at an 8

kHz rate. Figure 4 shows how the frame pulse

(F0b

) defines the ST-BUS frame boundaries. All

data is clocked into the device on the rising edge of

the 4096 kHz clock (C4b

into the bit cell, while data is clocked out on the

falling edge of the 4096 kHz clock at the start of the

bit cell.

All timing signals (i.e. F0b

bidirectional (denoted by the terminating b). The

I/O configuration of these pins is controlled by the

mode of operation (NT or TE). In the NT mode, all

synchronized signals are supplied from an external

source and the SNIC uses this timing while

transferring info rmat ion to and from th e S or

ST-BUS. In the TE mode, an on-board analog

phase-locked loop extracts timing from the received

data on the S-Bus and generates the system

4096 kHz (C4b

) and frame pulse (F0b). The

analog phase-locked loop also maintains proper

phase relation between the timing signals as well as

) three quarters of the way

& C4b) are identified as

ST-BUS Clock

ST-BUS

Stream

System

Frame Pulse

System

Frame Pulse

Input

ST-BUS Stream

Active on

Channel 0 - 3

MT8931C

NT

F0b

F0od

to TE to TE to TE to TE

MT8931C

F0b

Active on

Channels 4 - 7

NT

F0od

MT8931C

NT

F0b

Active on

Channels 8 - 11

F0od

Figure 13 - Daisy Chaining the SNIC

V

DD

to TE

to TE

MT8931C

NT

STAR

F0b

DSTi

MT8931C

NT

STAR

F0b

DSTi

MT8931C

NT

STAR

F0b

DSTi

DSTo

MT8931C

NT

STAR

F0b

DSTi

to TE

to TE

MT8931C

NT

F0b

Active on

Channels 12 - 15

F0od

Output

ST-BUS Stream

Figure 14 - NT in Star Configuration

9-83

MT8931C Preliminary Information

filtering out jitter which may be present on the

received line port.

The SNIC uses the first four channels on the

ST-BUS (as shown in Figure 4). To simplify the

distribution of the serial stream, the SNIC

provides a delayed frame pulse (F0od

the need for a channel assignment circuit. This

signal is used to drive subsequent devices in the

daisy chain (refer Figure 13). In this type of

arrangement, only the first SNIC in the chain will

receive the system fram e pulse (F0b) with the

following devices receiving its predecessor’s delayed

output frame pulse (F0od

The SNIC makes efficient use of its TDM bus

through the Star configuration. It does so by sharing

four common ST-BUS channels to multiple NT

devices. Up to eight SNICs in NT mode with

physically independent S-Busses can be connected

in parallel to realize a star configuration (as shown in

Figure 14). All devices connected into the star will

carry the same input, thus information is sent to all

TEs simultaneously. The 2B+D data received from

every TE is transmitted to all NTs through the STAR

pin. Consequently, all the DSTo streams will carry

identical 2B+D data reflecting what is being

transmitted by the various TEs.

).

) to eliminate

The flow of data in the direction of S-Bus to ST-BUS

is transparent to the SNIC, regardless of the state

machine status. On the other hand, the flow of data

in the direction of ST-BUS to S-Bus becomes

transparent only after the state machine is in the

active state (IS0, IS1=1,1), in case of an NT, or in the

synchronization sta te (IS 0, IS1 =1), in cas e of a TE.

Microprocessor/Control Interface

The microprocessor port is compatible with either

Motorola or Intel multiplexed bus signals and

timing. The MOTEL circuit (MOtorola and

InTEL Compa ti b le bu s) uses the leve l o f th e DS/

RD

pin at th e r isi n g ed ge of AS/ALE to select

the appropriate bus timing. If DS/RD

the rising edge of AS/ALE (refer to Figure 26) then

Motorola b u s timing is selecte d. Co n ver se l y, if DS/

RD

is high at the rising edge of AS/ALE (refer to

Figures 24 & 25), then Intel bus timing is selected.

This has the effect of redefining the microprocessor

port transparently to the user.

The user has the option of writing to the C-channel

Control or Diagnostic Register through the parallel

port interface or through the C-channel on DSTi. Bit

0 of th e Master Control Register provides this option.

is low at

Address Lines

A4 A3 A2 A1 A0

00000 Master Control Register verify

A 00001 ST-BUS Cont rol Regist er verify

S 00010 HDLC Control Register 1 verify

Y 00011 HDLC Control Register 2 HDLC Status Regist er

N 00100 HDLC Interrupt Mask Registe r HDLC Interrupt Status Register

C 00101 HDLC Tx FIFO HDLC Rx FIFO

00110 HDLC A ddress Byte #1 Register verify

00111 HDLC A ddress Byte #2 Register verify

01000 C-channel Control Register

01001 C-channel Status Register

10000 Control Register 1 Not Available

10010 Not Available Master Status Register

01000 DSTi C-channel

01001 DSTo C-channel

S 01010 S-Bus Tx D-channe l DSTi D-channel

Y 01011 DSTo D-channel S-Bus Rx D-channel

N 01100 S-Bus Tx B1-channel DSTi B1-channel

C01101 DSTo B1-channel S-Bus Rx B1-channel

01110 S-Bus Tx B2-channel DSTi B2-channel

01111 DSTo B2-channel S-Bus Rx B2-channel

Table 2. SNIC Add ress Map

Write Read

9-84

Preliminary Information MT8931C

The parallel port on the SNIC allows complete

control of the HDLC transceiver and access to all

data, control and status registers. Reading these

registers allows the microprocessor to monitor

incoming data on the S or ST-BUS without

interruptin g th e no r m a l d ata flow.

Some registers are classified as asynchronous and

others as synchronous. Synchronous registers are

single-buffered and require synchronous access.

Not all the synchronous registers have the same

access times, but all can be accessed

synchronously in the time during which the NDA

signal is low (refer to Fig. 5). Therefore, it is

recommended that the user make use of the NDA

signal to access these registers. Since the

synchronous registers use common circuitry, it is

essential that the register be read before being

written. This sequence is important as a write cycle

will overwrite the last data received. These parallel

accesses must be refreshed every frame.

Asynchronous registers, on the other hand, can be

accessed at any time.

The data in TE or NT Mode Status Register,

depending upon the mode selected, is always sent

out on the C-channel of DSTo. However, in

microprocessor control mode the user can overwrite

this data by writing to the DSTo C-channel Register.

This access can be done anytime outside the frame

pulse interval of the ST-BUS frame. Data written in

the current ST-BUS frame will only appear in the Cchannel of the following frame.

HDLC Transceiver

The HDLC Transceiver handles the bit oriented

protocol structure and formats the D-channel as per

level 2 of the X.25 packet switching protocol defined

by CCITT. It transmits and receives the packetized

data (information or control) serially in a format

shown in Figure 15, while providing data

transparency by zero insertion and deletion. It

generates and detects the flags, various link channel

states and the abort sequence. Further, it provides a

cyclic redundancy check on the data packets using

the CCITT defined polynomial. In addition, it can

recognize a single byte, dual byte or an all call

address in the received frame. There is also a

provision to disable the protocol functions and

provide transparent access to either serial port

through the microprocessor port. Other features

provided by the HDLC include, independent port

selection for transmit and received data (e.g.

transmit on S-Bus and receive from ST-BUS),

selectable 16 or 64 kbit/s D-channel as well as an

HDLC loopback from the transmit to the receive port.

These features are enabled through the HDLC

control registers (see Tables 6 and 7).

HDLC Frame For mat

All frames start with an opening flag and end with a

closing flag as shown in Figure 15. Between these

two flags, a frame contains the data and the frame

check sequence ( FC S) .

The least significant bit (B0) of the C-channel

Register, selects between the control register or the

diagnostic register. Setting the B0 of the C-channel

Register to ’0’ allow access to the control register.

Setting the LSB of the C-channel Register to ’1’ allow

access to the dia gnostic r egister. The i nterpreta tion

of each register is defined in Tables 13 and 14 for NT

mode or Tables 16 and 17 for the TE mode.

It is important to note that in TE mode, the C-channel

Diagnostic Register should be cleared while the

device is not in the active state (IS0, IS1

is accomplished by setting the ClrDia bit of the Cchannel Control Register to 1 until the device is

activated. In serial control mode, the C-channel on

the ST-BUS is loaded into the C-channel Control

Register in every ST-BUS frame; the user should

make sure that a 1 is written to the ClrDia bit in every

frame. However, in parallel control mode the user

needs to set the ClrDia bit only once to keep the

Diagnostic Register cleared. Once full activation is

achieved the Diagnostic Register can be written to in

order to enable the various test functions.

≠ 1,1) . This

FLAG DATA FIELD FCS FLAG

One

Byte

i) F lag

The flag is a unique pattern of 8 bits (0111111 0)

defining the frame boundary. The transmit section

generates the flags and appends them automatically

to the frame to be transmitted. The receive section

searches the incoming packets for flags on a

bit-by-bit basis and establishes frame

synchronization. The flags are used only to identify

and synchronize the received frame and are not

transferred to the FIFO.

n Bytes

(n ≥ 2)

Figure 15 - Frame Format

Two

Bytes

One

Byte

9-85

MT8931C Preliminary Information

ii) Data

The data field refers to the Address, Control and

Information fields defined in the CCITT

recommendations. A valid frame should have a data

field of at least 16 bits. The first and second byte in

the data field is the ad d re s s o f the frame.

iii) Frame C heck Se quenc e (FCS )

The 16 bits following the data field are the frame

check sequence bits. The generator polynomial is:

G(x)=x

The transmitter calculates the FCS on all bits of the

data field and transmits the complement of the FCS

with most si gnificant bit fi rst. The receiver performs

a similar computation on all bits of the received data

but also includes the FCS field. The generating

polynomial will assure that if the integrity of of the

transmitted data was maintained, the remainder will

have a consistent pattern and this can be used to

identify, with high probability, any bit errors occurred

during transmission. The error status of the received

packet is indicated by B7 and B6 bits in the HDLC

Status Register.

16+x12+x5

+1

Interframe Time Fill

When the HDLC Tranceiver is not sending packets,

the transmitter can be in one of two states mentioned

below depending on the status of the IFTF bit in the

HDLC Control Register 1.

i) Idle State

The Idle state is defined as 15 or more contiguous

ONEs. When the HDLC Protocoller is observing this

condition on the receiving channel, the Idle bit in the

HDLC Status Register is set HIGH. On the transmit

side, the Protocoller ends the transmission of all

ones (idle state) when data is loaded into the

transmit FIFO.

CCITT I.430 Specification requires every TE that

does not have layer 2 frames to transmit, to send

binary ONEs on the D-channel. In this manner, other

TEs on the line will have the opportunity to access

the D-channel using the priority mechanism circuitry.

ii) Flag Fill State

iv) Zero Insertion and Deletion

The transmitter, while sending either data from the

FIFO or the 16 bits FCS, checks the transmission on

a bit-by-bit basis and inserts a ZERO after every

sequence of five contiguous ONEs (including the last

five bits of FCS) to ensure that the flag sequence is

not imitated. Similarly the receiver examines the

incoming frame content and discards any ZERO

directly fol low in g th e fi ve contiguous ONEs.

v) Abort

The transmitter aborts a frame by sending a zero

followed by seven consecutive ONEs. The FA bit in

the HDLC Control Register 2 along with a write to the

HDLC Transmit FIFO enables the transmission of an

abort sequence instead of the byte written to the

register (to have a valid abort there must be at least

two bytes in the packet). On the receive side, a

frame abort is defined as seven or more contiguous

ONEs occurring after the start flag and before the

end flag of a packet. An interrupt can be generated

on reception of the abort sequence using FA bit in

the HDLC Interrupt Mask/Vector Registers (refer to

Tables 9 and 10).

The HDLC Protocoller transmits continuous flags

(7E

) in Interframe Time Fill state and ends this

Hex

state when data is loaded into the transmit FIFO.

The reception of the interframe time fill will have the

effect of setting the idle bit in the HDLC Status

Register is se t to ’ 0’.

HDLC Transmitter

On power up, the HDLC transmitter is disabled and

in the idle state. The transmitter is enabled by

setting the TxE N bit in the HDLC Control Register 1.

To s tart a packet, the data is written into the 19 byte

Transmit FIFO starting with the address field. All the

data must be written to the FIFO in a bytewide

manner. When the data is detected in the transmit

FIFO, the HDLC protocoller will proceed in one of the

following ways:

1) If the transmitter is in idle state, the present byte

of ones is completely transmitted before sending

the open ing flag. The data in the t ransmit F IFO

is then tran smi t ted . A TE transmitti n g on th e Dchannel will use the contention circuitry

described previously in

Mechanism

2) If the transmitter is in the flag fill state, the

flag presently being transmitted is used as the

opening fl a g for th e pa c ke t sto re d in th e tr an s m i t

FIFO.

to access this channel.

D-channel Priority

9-86

Preliminary Information MT8931C

3) If the HDLC tran smitter is in tra nsparent

data mode, the protocol functions are disabled

and the data in the transmit FIFO is transmitted

without a framing structure.

To indicate that the particular byte is the last byte of

the packet, the EOP bit in the HDLC Control Register

2 must be set before the last byte is written into the

transmit F IFO . T he EO P b it is clea red auto matic ally

when the data byte is writt en to the FIFO. After the

transmission of the last byte in the packet, the frame

check sequence (16 bits) is sent followed by a

closing flag. If there is any more data in the transmit

FIFO, it is immediately sent after the closing flag.

That is, the closing flag of a packet is also used as

the opening flag the the next packet.

However, CCITT I.430 and ANSI T1.605

Recommendations state that after the successful

transmission of a packet, a TE must lower its priority

level within the specified priority class. The user can

meet this requirement by loadi ng the Tx FIFO with no

more than one packet and then waiting for the

DCack bit t o go to zero, o r for an HDL C interrup t by

the TEOP bit in the HDLC Interrupt Status Register,

before attempting to load a new packet. If there is no

more data to be tran smitted, the transmitter as sum e s

the selected link channel state.

During the transmission of either the data or the

frame check sequence, the Protocol Controller

checks the transmitted information on a bit by bit

basis to insert a ZERO after every sequence of five

consecutive ONEs. This is required to eliminate the

possibility of imitating the opening or closing flag, the

idle code or an abort sequence.

i) Transmit Underrun

must be set HIGH, before writing the next byte into

the FIFO. This bit is cleared automatically once the

byte is written to the Transmit FIFO. When the

‘flagged’ byte reaches the bottom of the FIFO, a

frame abort sequence is sent instead of the byte and

the transmitter operation returns to normal. The

frame abort sequence is ignored if the packet has

less then two bytes.

iii) Transparent Data Transfer

The Trans bit (B4) in the HDLC Control Register 2

can be set to provide transparent data transfer by

disabling the protocol functions. The transmitter no

longer generates the Flag, Abort and Idle sequences

nor does it insert the zeros and calculate the FCS.

It should be noted that none of the protocol related

status or interrupt bits are applicable in transparent

data transfer state. However, the FIFO related

status and interrupt bits are pertinent and carry the

same meaning as they do while performing the

protocol functions.

HDLC Receiver

After a reset on power up, the receive section is

disabled. Address detection is also disabled when a

reset occurs. If address detection is required, the

Receiver Address Registers are loaded with the

desired address and the ADRec bit in the HDLC

Control Register 1 is set HIGH. The receive section

can then be enabled by RxEN bit in this same

Control Register 1. All HDLC interrupts are masked,

thus the desired interrupt signal must be unmasked

through the HDLC Interrupt Mask Register. All active

interrupts are cleared by reading the HDLC Interrupt

Status Register.

A transmit underrun occurs when the last byte

loaded into the transmit FIFO was not ‘flagged’ with

the ‘end of packet’ (EOP) bit and there are no more

bytes in the FIFO. In such a situation, the Protocol

Controller transmits the abort sequence (zero and

seven ones) and moves to the selected link channel

state.

Conversely, in the event that the transmit FIFO is full,

any further writes will overwrite the last byte in the

Transmit FIFO.

ii) Abort Transmissio n

If it is desired to abort the packet currently being

loaded into the tra nsmit FIFO, the next byte wr itten

to the FIFO should be ‘flagged’ to cause this to

happen. The FA bit of the HDLC Control Register 2

i) Normal P ackets

After initialization as explained above, the serial data

starts to be clocked in and the receiver checks for

the idle channel and flags. If an idle channel is

detected, the ‘Idle’ bit in the HDLC Status Register is

set HIGH. Once a flag is detected, the receiver

synchronizes itself in a bytewide manner to the

incoming data stream. The receiver keeps

resynchronizing to the flags until an incoming packet

appears. The incoming packet is examined on a

bit-by-bit basis, inserted zeros are deleted, the FCS

is calculated and the data bytes are written into the

19 byte Receive FIFO. However, the FCS and other

control characters, i.e., flag and abort , are never

stored in the Receive FIFO. If the address detection

is enabled, the address field following the flag is

compared to the bytes in the Receive Address

9-87

MT8931C Preliminary Information

Registers. If one byte address recognition is

enabled, the address field is one byte long and it is

compared with the six most significant bits in

address recognition register 1. If two byte address

recognition is enabled, the address field is two bytes

long and is compared with the address recognition

registers 1 and 2. The address byte can also be

recognized if it is an all call address (i.e., seven most

significant bits are 1). If a match is not found, the

entire packet is ignored, nothing is written to the

Receive FIFO and the receiver waits for the next

packet. If the active address byte is valid, the packet

is received in normal fashion.

All the bytes written to the receive FIFO are flagged

with two status bits. The status bits are found in the

HDLC status register and indicate whether the byte

to be read from the FIFO is the first byte of the

packet, the middle of the packet, the last byte of the

packet with good FCS or the last byte of the packet

with bad FCS. This status indication is valid for the

byte whic h is to be read f ro m the Receive F IFO.

The incoming data is always written to the FIFO in a

bytewide manner. However, in the event of data sent

not being a multiple of eight bits, the software

associated with the receiver should be able to pick

the data b its from th e LSB pos itions of the last byte

in the received data written to the FIFO. The

Protocoller does not provide any indication as to how

many bits this might be.

ii) Invalid Pac ket s

iii) Frame Abort

When a frame abort is received, the EOPD and FA

bits in the HDLC Interrupt Status Register are set.

The last byte of the aborted packet is written to the

FIFO with a status of “Packet Byte”. If there is more

than one packet in the FIFO, the aborted packet is

distinguished by the fact that it has no “Last Byte”

status on any of its bytes.

iv) Idle Channel

While receiving the idle channel, the idle bit in the

HDLC status register remains set.

v) Transparent Data Transfer

By setting the Trans bit in the HDLC Control Register

2 to select the transparent data transfer, the receive

section will disable the protocol functions like Flag/

Abort/Idle detection, zero deletion, CRC calculation

and address comparison. The received data is

shifted in from the active port and written to receive

FIFO in byte wid e format.

It should be noted that none of the protocol related

status or interrupt bits are applicable in transparent

data transfer state. However, the FIFO related

status and interrupt bits are pertinent and carry the

same meaning as they do while performing the

protocol functions.

In TE mode, if there are less than 25 data bits

between the opening and closing flags, the packet is

considered invalid and the data never enters the

receive FIFO (inserted zeros do not form part of the

valid bit count). This is true even with data and the

abort sequence, the total of which is less than 25

bits. The data packets that are at least 25 bits but

less than 32 bits long are also invalid, but not

ignored. They are clocked into the receive FIFO and

tagged as having bad FCS.

In NT mode, however, all the data packets that are

less than 32 bits long are considered invalid. They

are clocked into the receive FIFO with “Bad FCS”

status.

vi) Receive O verflo w

Receive overflow occurs when the receive section

attempts to load a byte to an already full receive

FIFO. All attempts to write to the full FIFO will be

ignored until the receive FIFO is read. When

overflow occurs, the rest of the present packet is

ignored as the receiver will be disabled until the

reception of the next opening flag.

9-88

Preliminary Information MT8931C

BIT NAME DESCRIPTION

B7 NA A ‘1’ will allow access to Control Register 1 and Master Status Registe r.

A ‘0’ will prevent it.

B6-B3 NA

(1)

Keep at ’0’ for normal operation.

B2 IRQ

/NDA The state of this pin will select the m ode of the IRQ/N D A pin.

A ’0’ will enable the IRQ

pin for HDLC interrupts.

A ’1’ will enable the New Data Available signal which ident ifies the access time to the

B1 M/Sen

synchronous registers. (If NDA

A ’0’ will enable the transmission of the M

is enabled, the HDLC interrup ts are disabled.)

(2)

or S bit as selected in the NT Mode C-channel

Register (refer to Table 13). The selection of M or S is determined by the HALF signal

(refer to functional timing).

A ’1’ will disable this feature forcing the M and S bits to binary zero.

B0 P/SC

The Parallel/Se rial Cont rol bit selects the so ur ce of the control channel. If ’0’, then the

C-channel Register is access through the ST-BUS stream. If ’1’, then the C-channel

Register is accessed through the microprocessor port.

Table 3. Mas ter Co ntro l Regi ster (Re ad/Writ e Add. 0 0000B)

Note 1: These bits have no designated memory space and will read as the last values written to the microprocessor port.

Note 2: The transmission of M=1 is used for a second level of multiframing.

BIT NAME DESCRIPTION

B7 NA Keep at ‘0’ for normal operation.

B6 RxDIS When set to ‘1’, this bit disables the S-Bus signal receive r. It can be used, for example, to

force INFO4 to INFO2 transitio n in the NT state mach ine while receiving INFO3 from the

TE.

B5-B0 NA Keep at ‘0’ for normal operation.

Table 4. Co ntro l Regis ter 1 (Write Add. 10000B)

9-89

MT8931C Preliminary Information

BIT NAME DESCRIPTION

B7 CH3i

B6 CH2 i

B5 CH1 i

B4 CH0 i

B3 CH3o

B2 CH2o

B1 CH1o

B0 CH0o

Note 3: All ST-BUS channels are enabled in controllerless mode.

(3)

If ’1’, then the ST-BUS channel 3 input port is enabled (B2-channel).

If ’0’, then the channel is disabled, and will read FF

(3)

If ’1’, then the ST-BUS channel 2 input port is enabled (B1-channel).

If ’0’, then the channel is disabled, and will read FF

(3)

If ’1’, then the ST-BUS channel 1 input port is enabled (C-channel).

If ’0’, then the channel is disabled, and will read 00

(3)

If ’1’, then the ST-BUS channel 0 input port is enabled (D-channel).

If ’0’, then the channel is disabled, and will read FF

(3)

If ’1’, then the ST-BUS channel 3 output port is enabled (B2-channel).

.

H

.

H

.

H

.

H

If ’0’, then the channel is disabled and it will be placed in High impedance .

(3)

If ’1’, then the ST-BUS channel 2 output port is enabled (B1-channel).

If ’0’, then the channel is disabled and it will be placed in High impedance .

(3)

If ’1’, then the ST-BUS channel 1 output port is enabled (C-channel).

If ’0’, then the channel is disabled and it will be placed in High impedance

(3)

If ’1’, then the ST-BUS channel 0 output port is enabled (D-channel).

If ’0’, then the channel is disabled and it will be placed in High impedance .

Table 5. ST-BUS Contro l Registe r (Read /Write Ad d. 0000 1B)

BIT NAME DESCRI PTION

B7 T xEn A ’1’ enables the HDLC transmitter for the selected D-channel (i. e., ST-BUS or S-Bus).

A ’0’ disables the HDLC transmitte r (i.e., an all 1s signal will be sent).

B6 RxEn A ’1’ enables the HDLC receiver for the selected D-channel (i.e., ST-BUS or S-Bus).

A ’0’ disables the HDLC receiver (i.e., an all 1s signal will be received).

B5 ADR ec If ’1’, then the address recognition is enabl ed. This forces the receiver to recognize only

those packets having the unique address as programmed in the Receive Address

Registers or if the address byte is the All-Call address (all 1s).

If ’0’, then the address recognition is disable d and every valid packet is stored in the

received FIFO.

B4 T xPrt Se l This bit selects the port of the HDLC transmit ted D-ch a nnel.

A’1’ selects the S-Bus port. A ’0’ selects the ST-BUS port.

B3 RxPrt S el T his bit selects the port of the HDLC received D-channel.

A ’1’ selects the S-Bus port. A ’0’ selects the ST-BUS port.

B2 IFTF T his bit selects the In ter Fram e Time Fill.

A ’1’ selects continuous flags. A ’0’ selects an all 1’s idle state.

B1 NA Keep at ’0’ fo r norm al operation.

B0 HLoop A ’1’ will activate the HDLC loopback where the transmitted D-channel is looped back to

the received D-channel

(1)

. In NT mode, the transmission of the packet is not affected. In

TE mode, however, the DReq bit of the C-channel Control Register must be set to ‘1’ for

the packet to be transmitted to the S-Bus.

A ’0’ disables the loopback.

Table 6. HDLC Control Re gis ter 1 (Re ad/Writ e Add. 0 0010B)

Note 1: The HDLC receiver must be enabled as well as the designated channel.

9-90

Preliminary Information MT8931C

BIT N AME DESCRIPTION

B7-B5 NA K eep at ’0’ for normal opera tio n.

B4 Trans A ’1’ will place the HDLC in a transparent mode. This will perform the serial to paral lel

or parallel to serial conversion witho ut inserting or delet ing the opening and closing

flags, CRC bytes or zero insertion. The source or destination of the data is determined

by the port selection bits in the HDLC Control Register 1.

B3 RxRst A transition from ‘0’ to ’1’ will reset the receive FIFO. This causes the receiver to be

disabled until the reception of the next flag. (The stat us Regist er will ident ify the

RxFIFO as being empty.) The device resets this bit to ‘0’ immediately after clearing the

receive FIFO.

B2 T xR st A transition from ‘0’ to ’1’ will reset the transmit FIFO. This causes the transmitter to

clear all data in the TxFIFO. The device resets this bit to ‘0’ immediately after clearing

the transmit FIFO.

B1 F A

B0 EO P

Note 2: Th es e b it s w ill b e r es et af ter a write to the TxFIFO

(2)

(2)

A ’1’ will ’tag’ the next byte written to the transmit FIFO and cause an abort sequence to

be transmitted once it reaches the bot tom of the FIFO.

A ’1’ will ’tag’ the next byte written to the transmit FIFO and cause an end of packet

sequence to be transmitted once it reaches the bottom of the FIFO.

Table 7. HDL C Contr ol R egister 2 (Write Add. 00 011B)

BIT NAME DESCRIPTION

B7-B6 RxByte

Status

These two bits indicate the status of the received byte which is ready to be read from the

19 deep received FIFO. The status is encoded as follows:

B7 - B6

0 - 0 - Packet Byte

0 - 1 - First Byte

1 - 0 - Last Byte (Good FCS)

1 - 1 - Last Byte (Bad FCS)

B5-B4 RxFIFO

Status

These two bits indicate the status of the 19 deep receive FIFO. This status is encoded as

follows:

B5 - B4

0 - 0 - Rx FIFO Empty

0 - 1 - ≤14 B ytes

1 - 0 - Rx FIFO Overflow

1 - 1 - ≥15 B ytes

B3-B2 TxFIFO

Status

These two bits indicate the status of the 19 deep transmit FIFO as fol lows:

B3 - B2

0 - 0 - Tx FIFO Full

0 - 1 - ≥5 Bytes

1 - 0 - Tx FIFO Empt y

1 - 1 - ≤4 B yt es

B1 Idl e If ’1’, an idle channel state has been detected .

B0 Int If ’1’ an unm as ked asynchronous interrupt has been detected.

Figure 8. HDLC Sta tus Regis ter (Rea d Add. 00011B)

9-91

MT8931C Preliminary Information

BIT NAME DESCRI PTION

B7 E nDcoll A ’1’ wil l enable the D-cha nnel colli sion inte rru pt.

A ’0’ will disable it. This bit is available only in TE mode.

B6 EnEOPD A ’1’ will enable the received End of Packet interrupt.

A ’0’ will disable it.

B5 EnTEOP A ’1’ will enable the transm it End of Packet interru pt.

A ’0’ will disable it.

B4 EnFA A ’1’ will enable the Frame Abort interrupt.

A ’0’ will disable it.

B3 EnTxF L A ’1’ will enable the Transmit FIFO Low interrupt.

A ’0’ will disable it.

B2 EnTxFun A ’1’ will enable the Transmit FIFO Underrun interrupt.

A ’0’ will disable it.

B1 EnRxFF A ’1’ will enable the Receive FIFO Fu ll interrupt.

A ’0’ will disable it.

B0 EnRxF ov A ’1’ wil l enable the Receive FIFO Overf low interrupt.

A ’0’ will disable it.

Table 9. HDL C Inter rupt Ma sk Reg iste r (Write Add . 00100B)

BIT NAME DESCRI PTION

B7 Dcoll

(1)

A ’1’ indicates that a collision has been detect ed on the D-channel (i.e., received E-bit

does not match with transmitted D-bit). This bit is available only in TE mode and when the

HDLC transmitter is enabled. It always reads ’0’ in NT mode.

B6 EOPD

(1)

A ’1’indicates that an end of packet has been detected on the HDLC receiver . This can be

in the form of a flag, an abort sequence or as an invalid packet.

B5 TEOP

(1)

A ’1’ indicates that the transmitter has finished sending the closing flag of the last packet in

the Tx FIFO, and the internal priorit y level is reduced from high to low.

B4 FA

(1)

A ’1’ indicates that the receiver has detected a frame abort sequence on the received data

stream.

B3 TxFL

(1)

A ’1’ indicates that the device has only four Byt es remaining in the Tx FIFO . This bit has

significance only when the Tx FIFO is being depleted and not when it is getting loaded.

B2 TxFun

(1)

A ’1’ indicates that the Tx FIFO is empty without being given the ’end of packet’ indication.

The HDLC will transmit an abort sequence after encounte ring an underrun co ndit ion.

B1 RxFF

(1)

A ’1’ indicates that the HDLC controller has accumulated at least 15 bytes in the Rx

FIFO.

B0 RxFov

(1)

A ’1’ indicates that the Rx FIFO has overflown (i.e., an attempt to write to a full Rx FIFO).

The HDLC will always disable the receiver once the receive overflow has been detecte d.

The receiver will be re-enabled upon detection of the next flag.

Table 10. HDL C Interr upt Sta tus Reg iste r (Read Add. 0 0100

)

B

Note 1: All inter rup ts w il l b e res e t a fte r a read to th e H DL C I nte rr u pt Sta tus R e gi st er.

9-92

Preliminary Information MT8931C

BIT NAME DESCRIPTION

B7-B2 R1A7-R1A2 A six bit mask used to interrogate the first byte of the received address (where B7 is MSB).

If address recognition is enabled, any packet failing the address compa rison will not be

stored in the Rx FIFO.

B1 NA Not applicable to address recognition.

B0 A1En If ’0’, the first byte of the address field will not be used during address recognition.

If ’1’ and the address recognit ion is enabled, th e six most signif icant bits of the first

address byte w ill be compared with the first six bits of this register.

Table 11. HDLC Address Recognition Register 1 (Read/Write Add. 00110B)

BIT NAME DESCRI PTION

B7-B1 R2A7-R2A1 A seven bit mask used to interrogate the second byte of the received address (where B7

is MSB). If address recognition is enabled, any packet failing the address comparison will

not be stored in the Rx FIFO. This mask is ignored if the address is a Broadcast (i.e., R2A

= 1111111).

B0 A2En If ’0’, the second byte of the address field will not be used during address recognition.

If ’1’ and the address recognition is enabled, the seven most significant bits of the second

address byte w ill be compared with the first seven bits of thi s registe r.

Table 12. HD LC Add ress Reco gnition Regis ter 2 (Rea d/Write Add. 00 111

)

B

BIT NAME DESCRI PTION

B7 AR Setting thi s bit will ini tia te the act ivat ion of the S-Bus.

If ’0’, the device will remain in the present state.

B6 DR Set t ing thi s bit will initia te th e deactivat ion of the S-Bus.

If ’0’, the device will remain in the present state. This bit has priority over AR .

B5 DinB If ’1’, the D-channel will be place d in the B1 timeslot allocat ing 64 kbit /s to th e

D-channel.

(1)

If ’0’, the D-channel will assume its position with a 16 kbit/s bandwidth.(1)

B4 Timing A ’0’ will set the NT in a short passive bus configuration using a fixed timing source (no

compensation for line length).

A ’1’ will set the NT in a point-to-point or extended passive bus configuration with adaptive

timing compensation.

B3 M/S T his bit represents the sta te of the transmitted M/S-bi t. M when HALF=0 and S when

HALF=1.

B2 HALF T he state of this bit identifies which half of the frame will be transmitted on th e

S-Bus. The operation of this signal is similar to that of the HALF pin.

B1 TxMFR A ’1’ in this bit, while HALF = 0, will force the transmission of a multiframe sequence in the

Fa and N bits, i.e., Fa=1 and N=0. A ‘0’ will resume normal operation, i.e., Fa=0 and N=1.

B0 RegS el If the register select bit is set to ’1’, the control register is redefined as the diagnost ic

register. A ’0’ give access to the control register.

Table 13. NT Mode C- channe l Control Reg ister

Note 1: Allow one ST-BUS frame to input the C-channel and one ST-BUS frame to establish the connection.

Note 2: The C-channel Control Register is updated once every ST-BUS frame. Therefore, this register should not be written to

more than once per frame, otherwise, the last access will override previous ones.

(2)

(Write Add. 01000B and B0 = 0)

9-93

MT8931C Preliminary Information

BIT NAME DESCRI PTION

B7-B6 Loop The status of the se two bits determine which type of loopback is to be performed:

B7 - B6

0 - 0 - no loopbac k active

0 - 1 - near end loopback LTx to LRx

1 - 0 - digital loopback DSTi to DSTo

1 - 1 - remote loopback LR x to LTx

B5 FSync If ’1’, the device will maintain frame synchronizati on even after losing the frame sync

sequence (i.e., if the device is transmitting INF O2 or INFO 4 and this bit is set, the same

INFO signal will still be transmitted even if the frame sync sequ ence in the received signal

is lost).

If ’0’, synchronization will be declared when three consecutive framing sequen ces have

been detected wit hout error.

B4 FL v I f ’1’, the frame sync sequence will violate the bipolar violation encoding rule.

If ’0’, the framing pattern resumes normal operatio n, i.e., Framing bit is a bipolar violation.

B3 Idle S et ting thi s bit to ’1’ will force an all 1s signal to be transm itt ed on the line.

B2 Echo Set t ing thi s bit to ’1’ will force all D-echo bits (E) to zero.

B1 Slave If ’1’, the device will operate in a NT slave mode. This allows the device to be used at the

terminal equipm ent end of the line while receiving its clocks from an external source.

B0 RegS el If the register select bit is set to ’1’, the control register is redefined as the diagnost ic

register. A ’0’ gives access to the control register.

Table 14. NT M ode C-c ha nnel Dia gno stic R egister (Write A dd. 010 00B and B0 = 1)

BIT NAME DESCRI PTIO N

B7 Sync/B A T his bit is set when the device has achieved frame synchronizati on while th e activation

request is asserted (DR = 0 and AR = 1). If there is a deactivation request or AR is low

(DR = 1 or AR = 0), this bit indicates the presence of bus activity

(1)

. A bus activity

identifies the recept ion of INFO frames (INFO 1 or INFO 3).

B6-B5 I S0-IS1 Bin a ry encoded stat e sequ ence.

IS0 - IS1

0 - 0 - deactivated

0 - 1 - pending deactivation

1 - 0 - pending activation

1 - 1 - activated

B4 RxM CH Following a ‘0’ inpu t at the HALF pin or HALF bit in the C-channel Cont ro l Register, the

state of this bit reflects the received maintenance Q-channel (received in the Fa bit

position during m ult ifram ing ).

This bit will always read ‘1’ if multiframing is not used.

B3-B0 NA These bits will read

Table 15. NT M ode S tatus Regi ster

Note 1: Bus activ ity i s set w h en th r e e zeros are r ecei ve d in a time perio d eq ui va le nt to 48 bits o r 2 50 µs . It i s res e t w h en 12 8

Note 2: The Status Re gi st er is upd at ed inte rna ll y on ce ev ery ST-BUS fra me . Ther efo r e , mor e tha n on e r ea d acc es s per fram e wi ll

consecu t iv e on es a r e rec ei ved.

return th e same value.

’1’.

(2)

(Read Add . 0100 1B)

9-94

Preliminary Information MT8931C

BIT NAME DESCRIPTION

B7 AR Setting thi s bit will ini tia te the act ivat ion of the S-Bus.

If ’0’, the device will remain in the present state.

B6 DR Set t ing thi s bit will initia te th e deactivat ion of the S-Bus.

If ’0’, the device will remain in the present state. This bit has priority over AR .